# (10) **DE 10 2015 107 272 A1** 2016.06.30

(12)

# Offenlegungsschrift

(21) Aktenzeichen: 10 2015 107 272.6

(22) Anmeldetag: 11.05.2015(43) Offenlegungstag: 30.06.2016

(51) Int Cl.: **H01L 29/49** (2006.01)

**H01L 21/283** (2006.01) **H01L 21/336** (2006.01) **H01L 21/302** (2006.01)

(30) Unionspriorität:

62/098,005 30.12.2014 US 14/687,447 15.04.2015 US

(71) Anmelder:

Taiwan Semiconductor Manufacturing Company, Ltd., Hsin-Chu, TW

(74) Vertreter:

BOEHMERT & BOEHMERT Anwaltspartnerschaft mbB - Patentanwälte Rechtsanwälte, 28209 Bremen, DE

(72) Erfinder:

Jang-Jian, Shiu-Ko, Hsinchu, TW; Wu, Chih-Nan, Hsinchu, TW; Wang, Ting-Chun, Hsin-Chu, TW; Lin, Chun Che, Hsinchu, TW

Prüfungsantrag gemäß § 44 PatG ist gestellt.

Die folgenden Angaben sind den vom Anmelder eingereichten Unterlagen entnommen

(54) Bezeichnung: Struktur und Verfahren für ein 3D-FinFET-Metallgate

(57) Zusammenfassung: Die vorliegende Offenbarung stellt gemäß einigen Ausführungsformen eine Halbleiterstruktur bereit. Die Halbleiterstruktur umfasst ein Halbleitersubstrat und einen Gate-Stapel, der auf dem Halbleitersubstrat angeordnet ist, wobei der Gate-Stapel eine Schicht aus einem high-k-dielektrischen Material aufweist und verschiedenartige Metallschichten auf der Schicht aus einem high-k-dielektrischen Material angeordnet sind, wobei die Gate-Struktur eine konvexe Deckfläche aufweist.

#### Beschreibung

#### ALLGEMEINER STAND DER TECHNIK

**[0001]** Diese Anmeldung beansprucht die Priorität der Vorläufigen US-Anmeldung 62/098,005 mit dem Titel "STRUCTURE AND METHOD FOR 3D FINFET METAL GATE", eingereicht am 30. Dezember 2014, die hier durch Nennung insgesamt als aufgenommen angesehen wird.

[0002] In den hochentwickelten Technologieknoten der Industrie zur Herstellung integrierter Schaltungen werden ein high-k-dielektrisches Material und ein Metall ausgewählt, um einen Gate-Stapel eines Feldeffekttransistors (FET), wie z. B. eines Metall-Oxid-Halbleiter-Feldeffekttransistors (MOSFET), auszubilden. Bei den existierenden Verfahren zum Ausbilden des Metallgate-Stapels werden die Metallgates in einem Gate-Austauschprozess ausgebildet, bei dem Dummygates entfernt und die Gate-Gräben mit Gate-Materialien ausgefüllt werden. Wegen der hohen Packungsdichte und der kleinen Merkmalsabmessungen ist es insbesondere für die FETs mit einer 3D-Struktur, wie z. B. die 3D-Fin-Feldeffekttransistoren (FinFETs), eine Herausforderung, eine ordnungsgemäße Spaltauffüllung und Profilsteuerung zu erreichen. Deshalb werden eine Struktur eines Metallgate-Stapels und ein Verfahren zur Herstellung desselben benötigt, um die oben angegebenen Probleme zu lösen.

#### KURZBESCHREIBUNG DER ZEICHNUNGEN

[0003] Ausbildungen der vorliegenden Offenbarung sind am besten anhand der nachfolgenden ausführlichen Beschreibung zu verstehen, wenn sie mitsamt den beigefügten Figuren gelesen wird. Es wird betont, dass im Einklang mit der üblichen Vorgehensweise in der Industrie die verschiedenen Merkmale nicht maßstabsgetreu gezeichnet sind. Tatsächlich können die Abmessungen der verschiedenartigen Merkmale aus Gründen der Verständlichkeit der Darlegung beliebig vergrößert oder verkleinert sein.

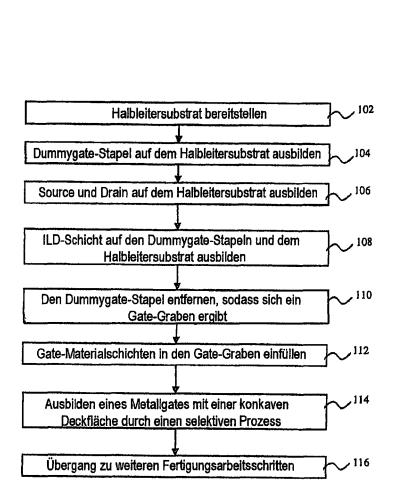

**[0004] Fig.** 1 ist ein Flussdiagramm eines Verfahrens zur Herstellung einer Halbleiterstruktur mit einem Metallgate-Stapel, die gemäß einigen Ausführungsformen konstruiert ist.

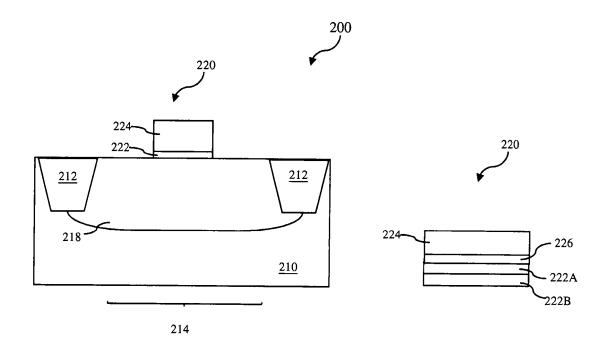

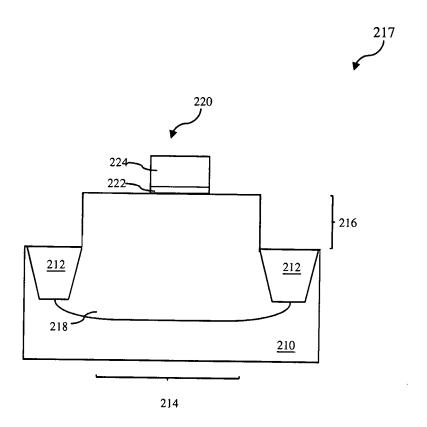

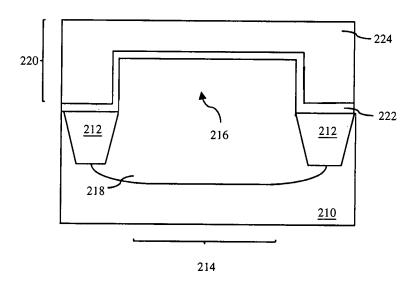

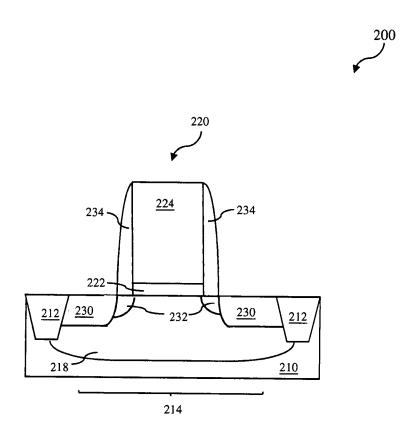

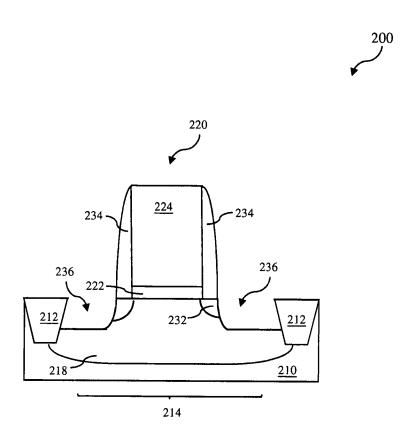

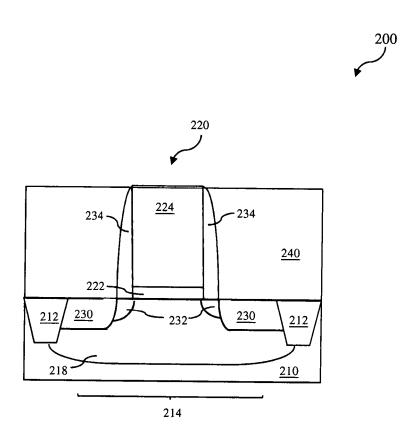

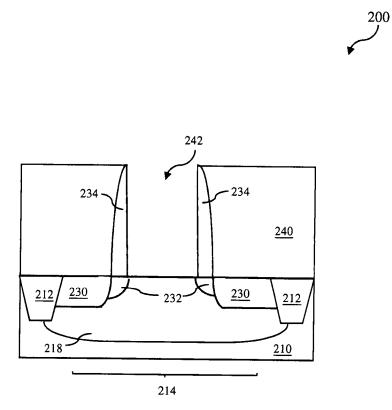

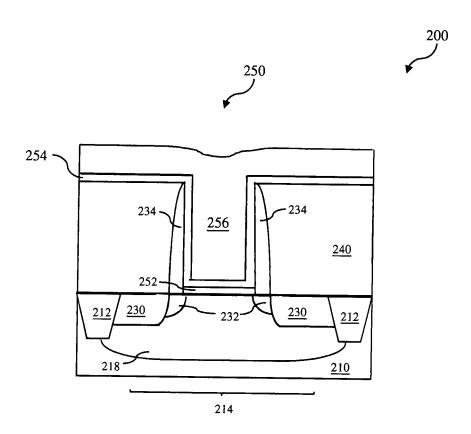

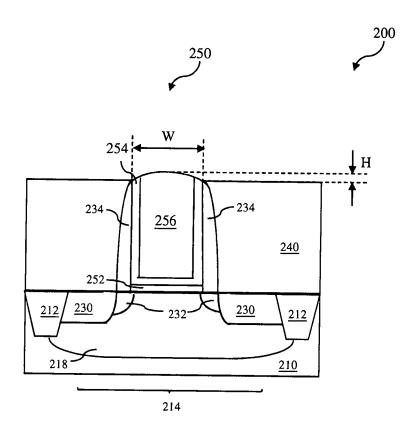

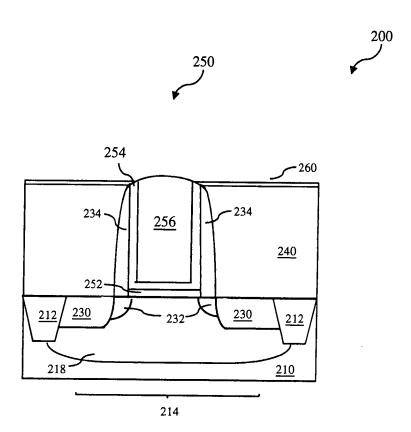

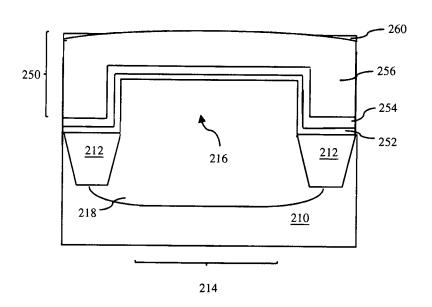

**[0005]** Die **Fig.** 2 und **Fig.** 4 bis **Fig.** 10 sind Schnittansichten einer gemäß einigen Ausführungsformen konstruierten Halbleiterstruktur in verschiedenartigen Fertigungsstufen.

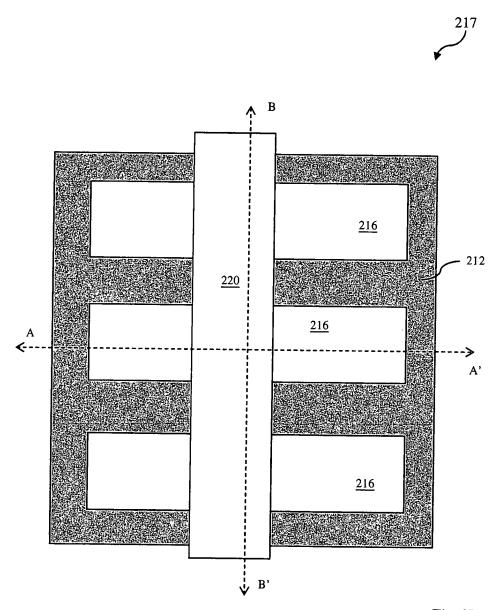

**[0006]** Die **Fig.** 3B und **Fig.** 13B sind Draufsichten einer gemäß einigen Ausführungsformen konstruierten Halbleiterstruktur in verschiedenartigen Fertigungsstufen.

**[0007]** Die **Fig.** 3A und **Fig.** 3C sind Schnittansichten der Halbleiterstruktur in **Fig.** 3B, die gemäß einigen Ausführungsformen konstruiert ist.

**[0008]** Die **Fig.** 13A und **Fig.** 13C sind Schnittansichten der Halbleiterstruktur in **Fig.** 13B, die gemäß einigen Ausführungsformen konstruiert ist.

[0009] Die Fig. 11 und Fig. 12 sind Schnittansichten des Gate-Stapels der Halbleiterstruktur in Fig. 10, die gemäß einigen Ausführungsformen konstruiert ist.

#### AUSFÜHRLICHE BESCHREIBUNG

[0010] Es ist so verstehen, dass die nachfolgende Offenbarung viele unterschiedliche Ausführungsformen oder Beispiele für die Realisierung unterschiedlicher Merkmale von verschiedenartigen Ausführungsformen verschafft. Nachstehend werden spezielle Beispiele für Komponenten und Anordnungen beschrieben, um die vorliegende Offenbarung zu vereinfachen. Selbstverständlich sind das lediglich Beispiele, und sie sind nicht zur Einschränkung vorgesehen. Außerdem können sich in der vorliegenden Offenbarung in den verschiedenartigen Beispielen Bezugsziffern und/oder Zeichen wiederholen. Diese Wiederholung dient der Vereinfachung und Übersichtlichkeit und schreibt von sich aus keine Beziehung zwischen den verschiedenartigen erörterten Ausführungsformen und/oder Konfigurationen vor. Darüber hinaus kann das Ausbilden eines ersten Merkmals über oder auf einem zweiten Merkmal in der nachfolgenden Beschreibung Ausführungsformen umfassen, bei denen das erste und zweite Merkmal in einem direkten Kontakt ausgebildet werden, und es kann auch Ausführungsformen umfassen, bei denen zwischen dem ersten und zweiten Merkmal zusätzliche Merkmale derart ausgebildet werden können, dass das erste und zweite Merkmal nicht unmittelbar kontaktieren können.

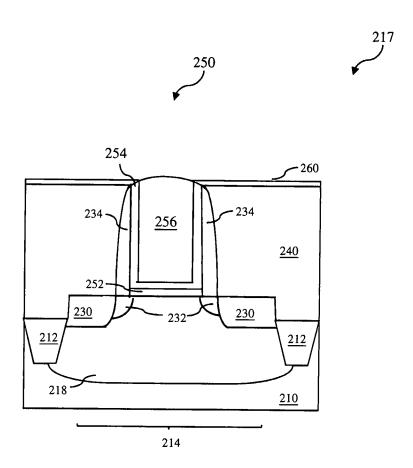

[0011] Fig. 1 ist ein Flussdiagramm eines Verfahrens 100 zur Herstellung einer Halbleiterstruktur mit einem Metallgate-Stapel, die gemäß Ausbildungen der vorliegenden Offenbarung konstruiert ist. Die Fig. 2 und Fig. 3-Fig. 10 sind Schnittansichten einer Halbleiterstruktur 200 bei verschiedenen Fertigungsstufen gemäß einigen Ausführungsformen. Die Fig. 11 und Fig. 12 sind Schnittansichten des Gate-Stapels in der Halbleiterstruktur 200 gemäß einigen Ausführungsformen. Die Fig. 3A-Fig. 3C und Fig. 13A-Fig. 13C stellen eine Halbleiterstruktur 217 mit einer Fin-Struktur dar, die gemäß einigen anderen Ausführungsformen konstruiert ist. Die Halbleiterstruktur 200 (oder 217) und das Verfahren 100 zum Herstellen derselben werden insgesamt mit Bezugnahme auf die Fig. 1 bis einschließlich Fig. 13 beschrieben.

[0012] Das Verfahren 100 startet bei 102 mit dem Bereitstellen eines Halbleitersubstrats 210. Das Halbleitersubstrat 210 weist Silizium auf. Alternativ weist das Substrat 210 Germanium oder Silizium-Germanium auf. In anderen Ausführungsformen kann im Substrat 210 ein weiteres Halbleitermaterial, wie z. B. Diamant, Siliziumkarbid, Gallium-Arsen, GaAsP, AllnAs, AlGaAs, GalnP oder eine andere geeignete Kombination davon, verwendet werden.

[0013] Das Halbleitermaterial umfasst auch verschiedenartige dotierte Bereiche, wie z. B. n-Wannen und p-Wannen, die durch geeignete Techniken, wie z. B. Ionenimplantation, ausgebildet werden. Das Halbleitersubstrat 210 weist auch verschiedenartige Isolationsmerkmale, wie z. B. Grabenisolation(STI)-Merkmale 212, auf, die in einem Substrat ausgebildet sind, um aktive Bereiche 214 festzulegen und verschiedenartige Bauelemente auf den aktiven Bereichen voneinander zu trennen. Das Ausbilden der STI kann das Ätzen eines Grabens in einem Substrat und das Auffüllen des Grabens mit Isolatormaterialien, wie z. B. Siliziumoxid, Siliziumnitrid oder Siliziumoxinitrid, umfassen. Der aufgefüllte Graben kann eine Mehrschichtstruktur aufweisen, wie z. B. eine Liner-Schicht aus thermischem Oxid mit Siliziumnitrid, die den Graben auffüllt. In einer Ausführungsform kann die STI-Struktur unter Einsatz einer Prozessabfolge erzeugt werden, wie z. B. durch: Aufwachsen eines Pufferoxids, Ausbilden einer Nitridschicht mittels chemischer Niederdruck-Gasphasenabscheidung (LPCVD), Strukturieren einer STI-Öffnung mittels Fotolack und Maskieren, Ätzen eines Grabens im Substrat, optionales Aufwachsen eines Graben-Liners aus thermischem Oxid, um die Grabengrenzfläche zu verbessern, Auffüllen des Grabens mit CVD-Oxid und Verwenden einer chemisch-mechanischen Planarisierung (CMP) zum Polieren und Planarisieren.

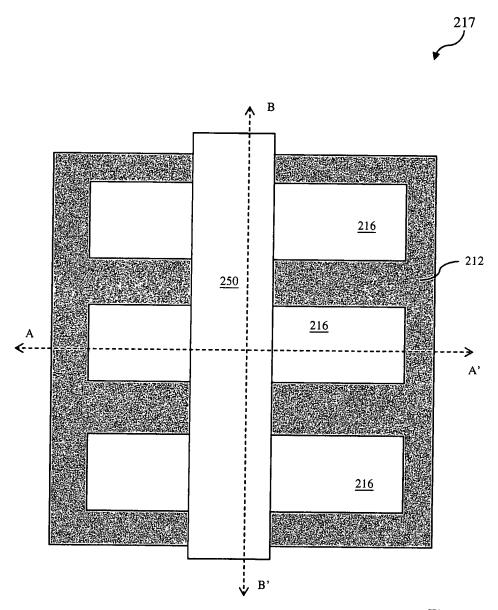

[0014] In einigen Ausführungsformen liegen die Deckfläche des Halbleitersubstrats 210 und die Deckflächen der STI-Merkmale 212 im Wesentlichen in einer Ebene, woraus sich eine gemeinsame Deckfläche ergibt. Dies wird als eine Planarstruktur bezeichnet. In anderen Ausführungsformen liegen die Deckfläche des Halbleitersubstrats 210 und die Deckflächen der STI-Merkmale 212 nicht in einer Ebene, sodass sich eine dreidimensionale Struktur ergibt, wie z. B. eine Fin-Struktur 216 in einer Halbleiterstruktur 217, die in Fig. 3A als eine Schnittansicht dargestellt ist. In der Halbleiterstruktur 217 erstreckt sich der aktive Bereich 214 oberhalb der Deckfläche der STI-Merkmale 212 und wird deshalb als die Fin-Struktur oder als der Fin-Aktivbereich bezeichnet. Auf der Fin-Struktur 216 werden somit verschiedenartige Bauelemente ausgebildet. Insbesondere werden auf der Fin-Struktur 216 Feldeffekttransistoren (FET) ausgebildet, und das entsprechende Gate des FET wird mit dem Kanal aus den mehreren Flächen

(Deckfläche und Seitenwände) der Fin-Struktur verbunden, sodass die Leistungsfähigkeit des Bauelements erhöht wird. Dementsprechend wird der auf der Fin-Struktur **216** ausgebildete FET als FinFET bezeichnet.

[0015] Die Halbleiterstruktur 217 wird weiter mit Bezugnahme auf die Fig. 3B und Fig. 3C beschrieben. Fig. 3B stellt die Halbleiterstruktur 217 in einer Draufsicht dar, und Fig. 3C stellt die gemäß einigen Ausführungsformen konstruierte Halbleiterstruktur 217 in einer Schnittansicht entlang der gestrichelten Linie BB' in Fig. 3B dar. Dementsprechend ist die Halbleiterstruktur 217 in Fig. 3A eine Schnittansicht entlang der gestrichelten Linie AA' in Fig. 3B.

[0016] Mit Bezugnahme auf Fig. 3B umfasst die Halbleiterstruktur 217 die Fin-Struktur 216, die den aktiven Bereich 214 festlegt. Auf dem Substrat 210 sind die Isolationsmerkmale 212 ausgebildet, und sie legen die Fin-Struktur 216 fest. Der aktive Bereich 214 ist in der Fin-Struktur 216 festgelegt. Die Fin-Struktur 216 weist ein oder mehrere Finger-Merkmale auf, die in einer ersten Richtung ausgerichtet sind. Über der Fin-Struktur 216 ist ein Gate 220 ausgebildet, das später beschrieben wird, und es ist in einer zweiten Richtung ausgerichtet, die sich von der ersten Richtung unterscheidet. In einem speziellen Beispiel sind die erste Richtung und die zweite Richtung senkrecht zueinander.

[0017] Mit Bezugnahme auf Fig. 3C umfasst die Halbleiterstruktur 217 die Fin-Struktur 216, die den aktiven Bereich festlegt. Auf dem Substrat 210 sind die Isolationsmerkmale 212 ausgebildet, und sie legen die Fin-Struktur 216 fest. Die Fin-Struktur 216 erstreckt sich oberhalb der Deckfläche der Isolationsmerkmale 212.

[0018] Die offenbarte Halbleiterstruktur (200 oder 217) und das Verfahren 100 zur Herstellung derselben stellen Verbesserungen für integrierte Schaltkreise, insbesondere für die FinFET, bereit. Die Fin-Struktur 216 kann mittels verschiedenartiger Techniken ausgebildet werden. In einigen Ausführungsformen wird die Fin-Struktur 216 durch Zurücksetzen der STI-Merkmale 212, wie z. B. durch selektives Ätzen, ausgebildet. In einigen anderen Ausführungsformen wird die Fin-Struktur 216 durch selektives epitaktisches Aufwachsen (SEG) ausgebildet. Im SEG-Prozess wird die Fin-Struktur 216 mit einem Halbleitermaterial ausgebildet, welches das gleiche wie das vom Substrat 210 (so z. B. Silizium) ist oder sich von ihm unterscheidet (so z. B. Silizium-Germanium oder Siliziumkarbid), um ferner andere Funktionen (z. B. einen Verformungseffekt) zu verwirklichen. Das Verfahren 100 ist auf die planare Halbleiterstruktur 200 und auf die nicht planare Halbleiterstruktur 217 anwendbar. In den meisten nachfolgenden Figuren wird

dennoch der Einfachheit halber die planare Struktur zur Beschreibung des Verfahrens **100** verwendet.

[0019] Mit einem Rückverweis auf Fig. 2 (sowie Fig. 3A, Fig. 3B und Fig. 3C) kann in einem oder mehreren aktiven Bereichen 214 eine dotierte Wanne 218 ausgebildet sein. In einigen Ausführungsformen ist der aktive Bereich 214 ausgelegt, einen FET, wie z. B. einen p-Kanal-FET (pFET) oder einen n-Kanal-FET (nFET) auszubilden. In einigen Beispielen ist ein pFET auf dem aktiven Bereich 214 auszubilden, und die dotierte Wanne 218 weist eine n-Dotiersubstanz, wie z. B. Phosphor (P), auf. In einigen anderen Beispielen ist ein nFET auf dem aktiven Bereich 214 auszubilden, und die dotierte Wanne 218 weist eine p-Dotiersubstanz, wie z. B. Bor (B), auf, die in einem aktiven Bereich verteilt ist. Die Dotiersubstanz kann über eine Offnung der Maskenschicht mittels eines geeigneten Dotierprozesses, wie z. B. eine oder mehrere Ionenimplantationen, in die dotierte Wanne 218 eingebracht werden. Die STI-Merkmale 212 tragen ferner zur Festlegung der Dotiersubstanzen in den gewünschten aktiven Bereichen bei. In einigen Ausführungsformen werden auf dem Substrat **210** sowohl nFETs als auch pFETs ausgebildet, so z. B. in komplementären Metall-Oxid-Halbleiter(CMOS) -Schaltkreisen.

[0020] Noch immer mit Bezugnahme auf Fig. 2 wird das Verfahren 100 mit einem Arbeitsschritt 104 fortgesetzt, in dem ein oder mehrere Dummygate-Stapel 220 auf dem Halbleitersubstrat 210 ausgebildet werden. Der Gate-Stapel 220 weist eine Gate-Dielektrikumschicht 222 und eine Gate-Leitschicht 224 auf. Das Ausbilden des Gate-Stapels 220 umfasst ein Abscheiden und Strukturieren. Das Strukturieren umfasst ferner einen Lithografieprozess und ein Ätzen. Zum Strukturieren des Gate-Stapels 220 kann ferner eine Hartmaskenschicht verwendet werden.

[0021] In einigen Ausführungsformen weist die Gate-Dielektrikumschicht 222 eine Schicht 222A aus einem high-k-dielektrischen Material auf, die auf dem Halbleitermaterial 210 ausgebildet ist, wie auf der linken Seite von Fig. 2 detaillierter dargestellt ist. Auf der Gate-Dielektrikumschicht 222 kann eine Abdeckschicht 226 ausgebildet werden. Auf der Abdeckschicht 226 wird als die Gate-Leitschicht eine Polysiliziumschicht ausgebildet. Die Gate-Dielektrikumschicht 222 kann ferner eine Grenzflächenschicht (IL) 222B umfassen, die zwischen dem Halbleitersubstrat 210 und der Schicht 222A aus einem high-k-dielektrischen Material eingefügt ist.

[0022] In Weiterführung der Ausführungsformen wird die Grenzflächenschicht 222B vor dem Ausbilden der Schicht 222A aus einem high-k-dielektrischen Material auf dem Substrat 210 ausgebildet. Die Grenzflächenschicht 222B kann Siliziumoxid aufweisen, das durch eine geeignete Technik, wie z. B. ei-

ne Atomlagenabscheidung (ALD), thermische Oxidation oder UV-Ozon-Oxidation, ausgebildet wird. Die Grenzflächenschicht kann eine Dicke von weniger als 10 Angström aufweisen.

[0023] Die high-k-dielektrische Schicht 222A weist ein dielektrisches Material auf, dessen Dielektrizitätskonstante größer ist als die von thermischem Siliziumoxid, die circa 3,9 ist. Die high-k-dielektrische Schicht 222A wird durch einen geeigneten Prozess, wie z. B. ALD, ausgebildet. Andere Verfahren zum Ausbilden des high-k-dielektrischen Materials schließen die metallorganische chemische Gasphasenabscheidung (MOCVD), die physikalische Gasphasenabscheidung (PVD), die UV-Ozon-Oxidation oder die Molekularstrahlepitaxie (MBE) ein. In einer Ausführungsform umfasst das high-k-dielektrische Material HfO2. Alternativ kann die Schicht 222A aus high-k-dielektrischem Material Metallnitride, Metallsilikate oder andere Metalloxide umfassen.

[0024] Auf der Schicht 222A aus einem high-kdielektrischen Material wird die Abdeckschicht 226

ausgebildet. In einer Ausführungsform weist die Abdeckschicht 226 Titannitrid (TiN) auf. In einem weiteren Beispiel liegt die Dicke der Titannitridschicht in

einem Bereich zwischen circa 5 Angström und circa

20 Angström. Die Abdeckschicht 226 kann alternativ

oder zusätzlich andere geeignete Materialien aufweisen. Die Abdeckschicht 226 wird durch eine geeignete Technik, wie z. B. PVD, ausgebildet.

[0025] Auf der Abdeckschicht 226 wird die Polysiliziumschicht 224 ausgebildet. Die Polysiliziumschicht 224 wird durch eine geeignete Technik, wie z. B. CVD, ausgebildet. In einem Beispiel ist die Polysiliziumschicht 224 nicht dotiert. In einem weiteren Beispiel liegt die Dicke der Polysiliziumschicht 224 in einem Bereich zwischen circa 500 Angström und circa 1000 Angström.

[0026] Ferner kann auf den mehreren Gate-Materialschichten eine strukturierte Maske ausgebildet werden, und sie wird verwendet, um den Gate-Stapel 220 auszubilden. Die strukturierte Maske wird auf der Polysiliziumschicht 224 ausgebildet. Die strukturierte Maske legt verschiedenartige Gate-Bereiche und verschiedenartige Öffnungen fest, welche die Gate-Stapelmaterialschichten freilegen, die zu beseitigen sind. Die strukturierte Maske weist eine Hartmaske, wie z. B. Siliziumnitrid und/oder Siliziumoxid, oder alternativ einen Fotolack auf. In einer Ausführungsform weist die strukturierte Maskenschicht eine strukturierte Hartmaskenschicht mit Siliziumnitrid und Siliziumoxid auf. Als ein Beispiel wird eine Siliziumnitridschicht mittels eines chemischen Niederdruck-Gasphasenabscheidungs(LPCVD)-Prozesses auf der Polysiliziumschicht abgeschieden. Die Siliziumnitridund Siliziumoxidschichten werden ferner strukturiert, indem ein Fotolithografieprozess verwendet wird, um

## DE 10 2015 107 272 A1 2016.06.30

eine strukturierte Fotolackschicht auszubilden, und indem ein Ätzprozess verwendet wird, um das Siliziumoxid und Siliziumnitrid in den Öffnungen der strukturierten Fotolackschicht zu ätzen. Alternativ kann ein anderes dielektrisches Material als die strukturierte Hartmaske verwendet werden. Zum Beispiel kann Siliziumoxinitrid als die Hartmaske verwendet werden. In einer weiteren Ausführungsform weist die strukturierte Maskenschicht eine strukturierte Fotolackschicht auf, die durch einen Fotolithografieprozess ausgebildet wurde. Ein Beispiel für einen Fotolithografieprozess kann die Prozessschritte zum Fotolackbeschichten, schwachen Tempern, Ausrichten der Maske, Belichten, Tempern nach der Belichtung, Entwickeln des Fotolacks und Einbrennen umfassen. Der fotolithografische Belichtungsprozess kann auch durch andere geeignete Verfahren, wie z. B. maskenlose Lithografie, Elektronenstrahlschreiben, Ionenstrahlschreiben und molekulares Prägen, realisiert oder ersetzt werden.

[0027] Das Verfahren umfasst das Strukturieren der Gate-Materialschichten. Durch die Öffnungen der strukturierten Maske hindurch werden ein oder mehrere Ätzprozesse auf die Gate-Materialschichten angewendet. Der Ätzprozess kann Trockenätzen, Nassätzen oder eine Kombination davon umfassen. In anderen Beispielen kann der Ätzprozess mehrere Schritte umfassen, um die verschiedenartigen Gate-Materialschichten wirksam zu ätzen.

[0028] In einigen anderen Ausführungsformen, wie z. B. im High-k-Last-Prozess, wird keine High-k-Dielektrikumschicht im Dummygate-Stapel 220 ausgebildet. In diesem Fall weist die Gate-Dielektrikumschicht 222 Siliziumoxid und die Gate-Leitschicht 224 Polysilizium auf. Die Abscheidungs- und Strukturierungsprozesse sind ähnlich zu den oben beschriebenen.

[0029] Auf die gleiche Weise wird der Gate-Stapel 220 auf der Fin-Struktur 216 der Halbleiterstruktur 217 in Fig. 3A-Fig. 3C ausgebildet. Insbesondere wird, wie in Fig. 3C dargestellt ist, der Gate-Stapel 220 über der Fin-Struktur 216 angeordnet und bis zu den Isolationsmerkmalen 212 ausgedehnt. Da die Deckfläche der Fin-Struktur 216 und die Deckfläche der Isolationsmerkmale 212 nicht auf einer Ebene liegen, weisen der Teil des Gate-Stapels 220, der auf der Fin-Struktur 216 angeordnet ist, und der Teil des Gate-Stapels 220, der auf den Isolationsmerkmalen 212 angeordnet ist, die jeweiligen Bodenflächen auf verschiedenen Ebenen auf (oder sind mit anderen Worten nicht komplanar).

[0030] Mit Bezugnahme auf Fig. 4 umfasst das Verfahren 100 einen Arbeitsschritt 106 zum Ausbilden von Source und Drain 232 im Substrat 210. Im Arbeitsschritt 106 kann ein Gate-Spacer 232 auf der Seitenwand des Gate-Stapels 220 ausgebildet wer-

den. Die Source und der Drain (S/D) **230** werden auf dem Substrat **210** ausgebildet, und der Gate-Stapel **220** steht dazwischen.

[0031] In noch einer weiteren Ausführungsform kann die Halbleiterstruktur 200 ferner schwach dotierte Drain(LDD)-Merkmale 232 mit demselben Leitfähigkeitstyp und einer geringeren Dotierungskonzentration aufweisen, welche auf dem Substrat 210 ausgebildet sind. Die LDD-Merkmale 232 und S/D 230 werden jeweils durch Ionenimplantation ausgebildet. Anschließend werden ein oder mehrere Temperungsprozesse ausgeführt, um die dotierten Spezies zu aktivieren.

[0032] Der Gate-Spacer 232 weist ein oder mehrere dielektrische Materialien, wie z. B. Siliziumoxid, Siliziumnitrid, Siliziumoxinitrid und Kombinationen davon, auf. In einer Ausführungsform weist der Gate-Spacer 232 einen auf der Seitenwand des Gate-Stapels angeordneten Abdichtspacer und einen auf dem Abdichtspacer angeordneten Hauptspacer auf, die jeweils durch einen Vorgang ausgebildet werden, der Abscheiden und Ätzen umfasst.

[0033] In einigen Beispielen weisen die Source und der Drain 230 beigefügte Dotierungsspezies auf, die durch eine geeignete Technik, wie z. B. die Ionenimplantation, in das Halbleitersubstrat eingebaut 210 worden sind. In einer Ausführungsform ist der Gate-Stapel 220 im aktiven Bereich für einen n-Kanal-Feldeffekttransistor (nFET) ausgelegt, wobei die Dotiersubstanz von Source und Drain eine n-Dotiersubstanz, wie z. B. Phosphor oder Arsen, ist. In einer weiteren Ausführungsform ist der Gate-Stapel im aktiven Bereich für einen p-Kanal-Feldeffekttransistor (pFET) ausgelegt, wobei die Dotiersubstanz von Source und Drain eine p-Dotiersubstanz, wie z. B. Bor oder Gallium, ist. In noch einer weiteren Ausführungsform umfassen Source und Drain 230 schwach dotierte Drain (LDD)-Merkmale und stark dotierte Source-Drain(S/ D)-Merkmale, die insgesamt als Source und Drain bezeichnet werden. Die LDD-Merkmale und S/D-Merkmale werden jeweils durch lonenimplantation ausgebildet. Anschließend werden ein oder mehrere Temperungsprozesse ausgeführt, um die dotierten Spezies zu aktivieren.

[0034] In einigen Ausführungsformen werden Source und Drain 230 durch epitaktisches Aufwachsen ausgebildet, um die Leistungsfähigkeit des Bauelements erhöhen, wie z. B. hinsichtlich eines Verformungseffekts zur Erhöhung der Beweglichkeit. In Weiterführung der Ausführungsformen umfasst das Ausbilden von Source und Drain 230 ein selektives Ätzen des Substrats 210 zum Ausbilden der Aussparungen 236, wie sie in Fig. 5 dargestellt sind, und ein epitaktisches Aufwachsen eines Halbleitermaterials in den Aussparungen 236 zum Ausbilden von Source und Drain 230 (so z. B. der in Fig. 4 dargestellten).

Die Aussparungen 236 können unter Verwendung eines Nass- und/oder Trockenätzprozesses ausgeführt werden, um das Material des Substrats 210 selektiv zu ätzen. In Weiterführung der Ausführungsformen wirken der Gate-Stapel 220, die Gate-Spacer 234 und die STI 212 gemeinsam als eine Ätz-Hartmaske, wodurch die Aussparungen 236 in den Source- und Drainbereichen ausgebildet werden. In einigen Beispielen wird ein Ätzmittel, wie z. B. Tetrafluorkohlenstoff (CF4), Tetramethylammoniumhydroxid (THMA), ein anderes geeignetes Ätzmittel oder eine Kombination davon verwendet, um die Aussparungen 236 auszubilden.

[0035] Danach werden die Aussparungen 132 durch epitaktisches Aufwachsen von Source- und Drain(S/ D)-Merkmalen 230 in einer kristallinen Struktur mit einem Halbleitermaterial gefüllt. Das epitaktische Aufwachsen kann ein Dotieren in situ umfassen, um S/ D mit der geeigneten Dotiersubstanz auszubilden. In einigen Ausführungsformen ist das epitaktische Aufwachsen ein selektiver Abscheideprozess, der ein Ätzen während des epitaktischen Abscheidens derart umfasst, dass das Halbleitermaterial im Wesentlichen auf den Halbleiteroberflächen in der Aussparung 236 aufwächst. Insbesondere bezieht der selektive Abscheideprozess Chlor für einen Ätzeffekt ein und macht die Abscheidung selektiv. Der selektive Abscheideprozess ist auf ein epitaktisches Aufwachsen derart ausgelegt und abgestimmt, dass die in den Aussparungen 236 ausgebildeten S/D 230 das Halbleitermaterial in einer kristallinen Struktur aufweisen. Das Halbleitermaterial unterscheidet sich von dem des Substrats 210. Zum Beispiel weist das Halbleitermaterial Siliziumcarbid oder Silizium-Germanium auf, während das Substrat 210 ein Siliziumsubstrat ist. In einigen Ausführungsformen wird das Halbleitermaterial für einen geeigneten Verformungseffekt im Kanalbereich derart ausgewählt, dass die entsprechende Ladungsträgerbeweglichkeit erhöht ist. In einem Beispiel, in dem der aktive Bereich 214 für einen pFET vorgesehen ist, ist das Halbleitermaterial für die S/D 230 mit Bor dotiertes Silizium-Germanium, während das Substrat 210 ein Siliziumsubstrat ist. In einem weiteren Beispiel, in dem der aktive Bereich 214 für einen nFET vorgesehen ist, ist das Halbleitermaterial für die S/D 230 mit Phosphor dotiertes Siliziumcarbid, während das Substrat 210 ein Siliziumsubstrat ist.

[0036] In noch einer weiteren Ausführungsform können ferner auf den Source- und Drain-Bereichen Silicid-Merkmale ausgebildet werden, um den Kontaktwiderstand zu verringern. Die Silicid-Merkmale können durch eine Technik, die als selbstjustierendes Silicid (Salicid) bezeichnet wird, ausgebildet werden, welche eine Metallabscheidung (wie z. B. Nickelabscheidung) auf einem Siliziumsubstrat, ein Tempern, um das Metall mit Silizium zum Ausbilden von Silicid reagieren zu lassen, und ein Ätzen zum Beseitigen

des Metalls umfasst, das keine Reaktion eingegangen ist.

[0037] Mit Bezugnahme auf Fig. 6 geht das Verfahren 100 zu einem Arbeitsschritt 108 über, in dem ein Zwischenschichtdielektrikum (ILD) 240 auf dem Substrat und dem Gate-Stapel 220 ausgebildet wird. Das ILD 240 wird durch eine geeignete Technik, wie z. B. CVD, ausgebildet. Das ILD 240 weist ein dielektrisches Material, wie z. B. Siliziumoxid, ein low-k-dielektrisches Material oder eine Kombination, auf. Dann kann anschließend ein chemisch-mechanischer Polier(CMP)-Prozess angewendet werden, um die Oberfläche des ILD 240 zu polarisieren. In einem Beispiel wird der Gate-Stapel durch den CMP-Prozess für die nachfolgenden Prozessschritte freigelegt. In einem weiteren Beispiel, in dem die Hartmaske zum Strukturieren des Gate-Stapels 220 im vorhergehenden Arbeitsschritt nicht beseitigt wurde, wird durch das CMP auch die Hartmaske beseitigt. Alternativ stoppt das CMP auf der Hartmaske, und die Hartmaske wird anschließend durch einen Ätzprozess beseitigt.

[0038] Mit Bezugnahme auf Fig. 7 geht das Verfahren 100 zu einem Arbeitsschritt 110 über, in dem der Gate-Stapel 220 teilweise oder vollständig beseitigt wird, was einen Gate-Graben 242 zur Folge hat. Der Arbeitsschritt 110 umfasst einen oder mehrere Ätzschritte, um selektiv die Gate-Leitschicht 224 oder alternativ den Gate-Stapel 220 durch einen geeigneten Ätzprozess, wie z. B. eines oder mehreres von einem Nassätzen, Trockenätzen oder einer Kombination, zu beseitigen.

[0039] Mit Bezugnahme auf Fig. 8 geht das Verfahren 100 zu einem Arbeitsschritt 112 über, in dem verschiedenartige Gate-Materialschichten in den Gate-Graben 242 eingefüllt werden, wobei im Gate-Graben 242 ein Metall-Gate 250 ausgebildet wird. In einigen Ausführungsformen, wie z. B. in einem High-k-Last-Prozess, umfassen die Gate-Materialschichten eine Gate-Dielektrikumschicht 254 und eine Gate-Leitschicht (oder Gate-Elektrode) 256. Die Gate-Dielektrikumschicht 254 weist ein high-k-dielektrisches Material auf. Die Gate-Leitschicht 256 weist Metall auf. In einigen Ausführungsformen umfasst die Gate-Leitschicht 256 mehrere Schichten, wie z. B. eine Abdeckschicht, eine Austrittsarbeit-Metallschicht, eine Sperrschicht und ein Füllmetallschicht (wie z. B. Aluminium oder Wolfram). Die Gate-Materialschichten können ferner eine Grenzflächenschicht 252, wie z. B. Siliziumoxid, umfassen, die zwischen dem Substrat 210 und dem high-k-dielektrischen Material eingefügt ist. Die Grenzflächenschicht 252 ist ein Teil der Gate-Dielektrikumschicht. Die verschiedenartigen Materialien werden durch Abscheiden, wie z. B. CVD, PVD, Plattieren, ALD oder andere geeignete Techniken, in den Gate-Graben 242 gefüllt.

[0040] Die High-k-Dielektrikumschicht 252 weist ein dielektrisches Material auf, dessen Dielektrizitätskonstante größer als die von thermischem Siliziumoxid ist, die circa 3,9 ist. Die high-k-dielektrische Schicht 252 wird durch einen geeigneten Prozess, wie z. B. ALD, ausgebildet. Andere Verfahren zum Ausbilden des high-k-dielektrischen Materials schließen MOCVD, PVD, die UV-Ozon-Oxidation oder die Molekularstrahlepitaxie MBE ein. In einer Ausführungsform umfasst das high-k-dielektrische Material HfO2. Alternativ kann die Schicht 252 aus einem high-k-dielektrischen Material Metallnitride, Metallsilikate oder andere Metalloxide aufweisen.

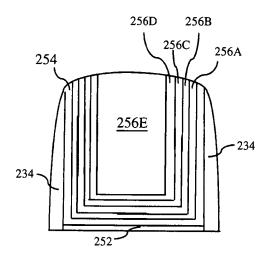

[0041] In einer Ausführungsform, die in Fig. 11 in einer Schnittansicht dargestellt ist, umfasst die Gate-Elektrode 256 eine Abdeckschicht 256A, eine Sperrschicht 256B, eine Austrittsarbeit-Metallschicht 256C, eine weitere Sperrschicht 256D und ein Füllmetallschicht 256E. In Weiterführung der Ausführungsformen weist die Abdeckschicht 156A Titannitrid, Tantalnitrid oder ein anderes geeignetes Material auf, das durch eine geeignete Abscheidetechnik, wie z. B. ALD, ausgebildet wird. Die Sperrschicht 256B weist Titannitrid, Tantalnitrid oder ein anderes geeignetes Material auf, das durch eine geeignete Abscheidetechnik, wie z. B. ALD, ausgebildet wird.

[0042] Die Austrittsarbeit-Metallschicht 256C weist eine leitfähige Schicht aus einem Metall oder einer Metalllegierung mit einer geeigneten Austrittsarbeit derart auf, dass der entsprechende FET hinsichtlich seiner Bauelementleistung verbessert wird. Die Austrittsarbeit(WF)-Metallschicht 256C ist für einen pFET und ein nFET unterschiedlich, sie wird entsprechend als ein n-Typ-WF-Metall und ein p-Typ-WF-Metall bezeichnet. Die Wahl des WF-Metalls hängt von dem FET ab, der auf dem aktiven Bereich 214 auszubilden ist. Zum Beispiel weist die Halbleiterstruktur 200 einen ersten aktiven Bereich 214 für eine n-FET und einen weiteren aktiven Bereich für einen pFET auf, und dementsprechend werden das n-Typ-WF-Metall bzw. das p-Typ-WF-Metall in den entsprechenden Gate-Stapeln ausgebildet. Insbesondere ist ein n-Typ-WF-Metall ein Metall, das eine erste Austrittsarbeit derart aufweist, dass die Schwellwertspannung des zugehörigen nFET herabgesetzt wird. Das n-Typ-WF-Metall ist nahe an der Silizium-Leitungsbandenergie (Ec) oder weist eine niedrigere Austrittsarbeit auf, was bedeutet, dass Elektronen leichter austreten können. Zum Beispiel weist das n-Typ-WF-Metall eine Austrittsarbeit von circa 4,2 eV oder weniger auf. Ein p-Typ-WF-Metall ist ein Metall, das eine zweite Austrittsarbeit derart aufweist, dass die Schwellwertspannung des zugehörigen pFET herabgesetzt wird. Das p-Typ-WF-Metall ist nahe an der Silizium-Valenzbandenergie (Ev) oder weist eine höhere Austrittsarbeit auf, was eine höhere Elektronenbindungsenergie an die Atomkerne anzeigt. Zum Beispiel weist das p-Typ-Austrittsarbeit-Metall eine Austrittsarbeit von circa 5,2 eV oder mehr auf.

[0043] In einigen Ausführungsformen umfasst das n-Typ-WF-Metall Tantal (Ta). In anderen Ausführungsformen umfasst das n-Typ-WF-Metall Titan-Aluminium (TiAI), Titan-Aluminium-Nitrid (TiAIN) oder Kombinationen davon. In anderen Ausführungsformen umfasst das n-Metall Ta, TiAI, TiAIN, Wolframnitrid (WN) oder Kombinationen davon. Das n-Typ-WF-Metall kann für ein optimiertes Bauelementleistungsvermögen und eine optimierte Verarbeitungskompatibilität verschiedenartige Filme auf Metallbasis als ein Stapel aufweisen. In einigen Ausführungsformen umfasst das p-Typ-WF-Metall Titannitrid (TiN) oder Tantalnitrid (TaN). In anderen Ausführungsformen umfasst das p-Metall TiN, TaN, Wolframnitrid (WN), Titan-Aluminium (TiAI) oder Kombinationen davon. Das p-Typ-WF-Metall kann für ein optimiertes Bauelementleistungsvermögen und eine optimierte Verarbeitungskompatibilität verschiedenartige Filme auf Metallbasis als ein Stapel aufweisen. Das Austrittsarbeit-Metall wird durch eine geeignete Technik, wie z. B. PVD, abgeschieden.

[0044] Die Sperrschicht 256D umfasst Titannitrid, Tantalnitrid oder ein anderes geeignetes Material, das durch ein geeignetes Abscheideverfahren, wie z. B. ALD, abgeschieden wird. In verschiedenartigen Ausführungsformen umfasst das Füllmetall 256E Aluminium, Wolfram oder ein anderes geeignetes Metall. Die Füllmetallschicht 256E wird durch eine geeignete Technik, wie z. B. PVD oder Plattieren, abgeschieden

[0045] Mit Bezugnahme auf Fig. 9 umfasst das Verfahren 100 einen Arbeitsschritt 114, in dem das Metall-Gate 250 ausgebildet wird, das eine konvexe Deckfläche aufweist. Nach dem Arbeitsschritt 112 sind die Gate-Materialschichten im Wesentlichen in den Gate-Graben 242 eingefüllt worden und können auch auf der ILD-Schicht 240 abgeschieden worden sein. Im Arbeitsschritt 114 werden die auf der ILD-Schicht 240 abgeschiedenen Gate-Materialien beseitigt, und er ist dafür konzipiert, die konvexe Deckfläche des Gate-Stapels 250 auszubilden. Das wird durch einen Selektivabtrageprozess erreicht, der unterschiedliche Abtragraten für die verschiedenartigen Gate-Materialien aufweist. Insbesondere weist der Selektivabtrageprozess höhere Abtragraten für die am Rand liegenden Gate-Materialschichten (wie z. B. das high-k-dielektrische Material und die Abdeckschicht) und niedrigere Abtragraten für die mittig liegenden Gate-Materialschichten (wie z. B. die Füllmetallschicht) auf. Insbesondere weist der Selektivabtrageprozess ausgewählte Abtragraten derart auf, dass die Abtragrate von den Metallschichten am Rand zu den Metallschichten in der Mitte abnimmt.

[0046] In einigen Ausführungsformen ist der Selektivabtrageprozess ein selektiver CMP-Prozess. Der CMP-Prozess wird angewendet, um die überschüssigen Gate-Materialien, wie z. B. die auf dem ILD 240 abgeschiedenen Materialien, zu entfernen. Der selektive CMP-Prozess ist so ausgelegt, dass er ausgewählte Abtragraten aufweist, um die konvexe Deckfläche auszubilden. In einigen Beispielen ist das Poliermittel, das im selektiven CMP-Prozess verwendet wird, so ausgelegt, dass es geeignete Chemikalien enthält, um eine derartige Polierselektivität zu erreichen. In einigen anderen Beispielen ist das Poliermittel, das im selektiven CMP-Prozess verwendet wird, so ausgelegt, dass es eine Chemikalie mit einer Ätzselektivität, Schleifpartikel mit geeigneten Größen, einen geeigneten Polierdruck, mehrere Polierschritte für die Polierselektivität oder eine Kombination davon aufweist.

[0047] In einigen Ausführungsformen weist der selektive CMP-Prozess einen ersten CMP-Schritt und einen zweiten CMP-Schritt auf. Der erste CMP-Schritt weist ein erstes Poliermittel, einen ersten Druck und eine erste Polierdauer auf. Der zweite CMP-Schritt weist ein zweites Poliermittel, einen zweiten Druck und eine zweite Polierdauer auf. Das zweite Poliermittel, der zweite Druck und die zweite Polierdauer unterscheiden sich jeweils vom ersten Poliermittel, ersten Druck und der ersten Polierdauer, oder eine dieser Größen (Poliermittel, Druck oder Polierdauer) ist unterschiedlich. Die zwei CMP-Schritte sind mit einer Polierselektivität derart ausgebildet, dass das Gate-Material am Rand stärker als das Gate-Material in der Mitte abgetragen wird. In einem ersten Beispiel ist der erste CMP-Schritt mit dem ersten Poliermittel und dem ersten Druck so ausgelegt, dass im Verhältnis zum Gate-Material in der Mitte im Wesentlichen das Gate-Material am Rand abgetragen wird, und der zweite CMP-Schritt mit dem zweiten Poliermittel und dem zweiten Druck ist so ausgelegt, dass im Verhältnis zum Gate-Material am Rand im Wesentlichen das Gate-Material in der Mitte abgetragen wird. Die erste Polierdauer im ersten CMP-Schritt ist größer als die zweite Polierdauer im zweiten CMP-Schritt. Dadurch wird mehr Gate-Material am Rand abgetragen und die konvexe Fläche des Gates 250 ausgebildet. In Weiterführung der Ausführungsformen unterscheiden sich das erste Poliermittel und das zweite Poliermittel voneinander hinsichtlich der Ätzchemikalien und der Schleifpartikel in dem entsprechenden Poliermittel.

[0048] In einigen Ausführungsformen ist der Selektivabtrageprozess ein selektiver Ätzprozess. Der selektive Ätzprozess wird eingesetzt, um überschüssige Gate-Materialien, wie z. B. die auf dem ILD 240 abgeschiedenen Metalle, zu beseitigen. Der selektive Ätzprozess ist so ausgelegt, dass er ausgewählte Abtragraten zum Ausbilden der konvexen Deckfläche aufweist. In einigen Beispielen wird das im se-

lektiven Ätzprozess verwendete Ätzmittel so ausgewählt, dass es eine Ätzselektivität aufweist. In einigen anderen Beispielen weist das Ätzmittel F2, Cl2 BCI3 oder ein Gemisch derselben auf. In einigen anderen Ausführungsformen weist der selektive Ätzprozess einen ersten Ätzschritt und einen zweiten Ätzschritt auf. Der erste Ätzschritt weist ein erstes Ätzmittel auf, das ausgelegt ist, selektiv das Gate-Material am Rand zu ätzen, und der zweite Ätzschritt weist ein zweites Ätzmittel auf. Das zweite Ätzmittel unterscheidet sich vom ersten Ätzmittel und ist ausgelegt, selektiv das Gate-Material in der Mitte zu ätzen. Zum Beispiel weist das erste Ätzmittel eine Flusssäure(HF)-Lösung auf, um selektiv das dielektrische Gate-Material abzutragen, und das zweite Ätzmittel weist H3PO4, HNO3, HCl oder eine Kombination derselben auf. In Weiterführung des Beispiels wird bei der HF-Lösung ein nichtwässriges Lösungsmittel verwendet, um das Ablösen der ILD-Schicht 240 einzuschränken. Der erste und der zweite Ätzschritt werden eingestellt, so z. B. durch Steuern der Ätzzeiten, dass das konvexe Profil des Gates 250 ausgebildet

[0049] In einigen anderen Ausführungsformen umfasst der Selektivabtrageprozess eine Kombination aus CMP und Ätzen, die für das Ausbilden der konvexen Deckfläche optimiert ist. Zum Beispiel umfasst der Abtrageprozess einen CMP-Prozess und anschließend einen selektiven Ätzprozess. Der CMP-Prozess beseitigt im Wesentlichen die überschüssigen Gate-Materialien über der ILD-Schicht. Der selektive Ätzprozess (wie z. B. die HF-Lösung) ist ausgelegt, selektiv das dielektrische Gate-Material abzutragen.

[0050] Der ausgeformte Gate-Stapel 250 weist eine konvexe Deckfläche auf. Die Höhendifferenz des Gate-Stapels 250 von der Mitte zum Rand ist H, und die Gate-Breite ist W. In einigen Beispielen liegt die Höhendifferenz H in einem Bereich von circa 2 nm bis zu circa 10 nm. In einigen Ausführungsformen liegt das Verhältnis H/W in einem Bereich von circa 10% bis zu circa 50%.

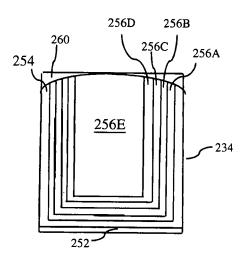

[0051] Mit Bezugnahme auf die Fig. 1 und Fig. 10 umfasst das Verfahren 100 einen weiteren Fertigungsschritt 116. In der vorliegenden Ausführungsform weist der Arbeitsschritt 116 einen Vorgang zum Ausbilden einer Abdeckschicht 260 auf dem Substrat 210 auf. In einem Beispiel umfasst das Ausbilden der Abdeckschicht 260 ein Abscheiden und Polieren. In Weiterführung des Beispiels wird durch ein geeignetes Verfahren, wie z. B. CVD, eine Abdeckschicht 260 aus einem dielektrischen Material auf dem Substrat abgeschieden. Das dielektrische Material der Abdeckschicht 260 umfasst ein geeignetes Material, wie z. B. Siliziumoxid, Siliziumnitrid, low-k-dielektrisches Material oder ein anderes geeignetes dielektrisches Material. Der Polierprozess kann

ein CMP-Prozess sein. Nach dem CMP-Prozess ist die Deckfläche der Halbleiterstruktur 200 planarisiert. Insbesondere wird, wie in Fig. 12 dargestellt ist, die Abdeckschicht auf der Deckfläche der Gate-Struktur 250 in den Randbereichen abgeschieden, sodass ein Schutz des Gate-Stapels 250 vor chemischen Beschädigungen oder anderen Beschädigungen während der nachfolgenden Herstellungsprozesse, wie z. B. vor einem chemischen Angriff von den Seitenwänden her, geschaffen wird. Die Abdeckschicht 260 wirkt als eine Sperrschicht. Zum Beispiel wird während des nachfolgenden Arbeitsschritts zum Ausbilden von Kontakten ein chemisches Ätzen ausgeführt, um die ILD-Schicht, die im Anschluss ausgebildet wurde, zu öffnen. Die Ätzchemikalie kann ferner den Gate-Stapel 250 von den Seitenwänden her ätzen und ihn dadurch beschädigen. Mit der Schutzwirkung der Abdeckschicht 260 ist der Gate-Stapel 250 geschützt und folglich frei von Beschädigungen.

[0052] Ebenso ist in den Fig. 13A-Fig. 13C auch die durch das Verfahren 100 hergestellte Halbleiterstruktur 217 nach dem Arbeitsschritt 116 dargestellt. Fig. 13B ist eine Draufsicht der Halbleiterstruktur 217. Die Fig. 13A und Fig. 13C sind Schnittansichten der Halbleiterstruktur 217 entlang der gestrichelten Linien AA' bzw. BB' von Fig. 12B. Insbesondere ist das konvexe Gate 250 auf der Fin-Struktur 216 und den Isolationsmerkmalen 212 angeordnet. Der erste Teil des Gates 250 auf der Fin-Struktur 216 und der zweite Teil des Gates 250 auf den Isolationsmerkmalen 212 weisen die jeweiligen Bodenflächen auf unterschiedlichen Ebenen auf (sind mit anderen Worten nicht komplanar). Die Deckfläche des Gates 250 ist nicht eben, sondern weist eine konvexe Form derart auf, dass es möglich ist, die Abdeckschicht 260 auf den Rändern des Gates 250 auszubilden.

[0053] Es können andere Verfahrensschritte folgen, um eine Funktionsschaltung auszubilden. Zum Beispiel wird auf dem Substrat eine Zusammenschaltungsstruktur ausgebildet, die ausgelegt ist, verschiedenartige Transistoren und andere Bauelemente zu koppeln, um eine Funktionsschaltung auszubilden. Die Zusammenschaltungsstruktur umfasst verschiedenartige Leitungsmerkmale, wie zum Beispiel Metallleiterbahnen für horizontale Verbindungen und Kontakte/Durchkontaktierungen für vertikale Verbindungen. Die verschiedenartigen Zusammenschaltungsmerkmale können verschiedenartige leitfähige Materialien, einschließlich Kupfer, Wolfram und Silizid, zur Anwendung bringen. In einem Beispiel wird ein Damascene-Prozess verwendet, um eine mehrschichtige Zusammenschaltungsstruktur auf Kupferbasis auszubilden. In einer weiteren Ausführungsform wird Wolfram verwendet, um in den Kontaktlöchern einen Wolframpropfen auszubilden.

[0054] Obwohl in den Figuren nur ein Gate-Stapel 250 dargestellt ist, werden jedoch auf dem Substrat

210 mehrere Gate-Stapel mit konvexen Deckflächen ausgebildet, und es werden auf dem Substrat 210 die verschiedenartigen entsprechenden nFETs, pFETs und anderen Schaltungsbauelemente erzeugt. In einigen Ausführungsformen wird der Gate-Stapel 250 auf dem aktiven 3D-Fin-Bereich ausgebildet, und er ist ein Teil eines FinFET.

[0055] Die vorliegende Offenbarung ist nicht auf Anwendungen beschränkt, in denen die Halbleiterstruktur einen Feldeffekttransistor, wie z. B. einen Metall-Oxid-Silizium(MOS)-Transistor umfasst, und sie kann auf eine andere integrierte Schaltung erweitert werden, die einen Metallgate-Stapel aufweist. Zum Beispiel kann die Halbleiterschaltung 200 eine dynamische Direktzugriffsspeicher(DRAM)-Zelle, einen Einzelelektronentransistor (SET) und/oder andere mikroelektronische Bauelemente (hier in ihrer Gesamtheit als mikroelektronische Bauelemente bezeichnet) aufweisen. In einer weiteren Ausführungsform umfasst die Halbleiterstruktur 200 FinFET-Transistoren. Natürlich sind die Ausbildungen der vorliegenden Offenbarung auch auf einen anderen Transistortyp anwendbar und/oder können an ihn angepasst werden, und sie können in vielen verschiedenen Anwendungen, einschließlich Sensorzellen, Speicherzellen, Logikzellen und andere, eingesetzt werden.

[0056] Obwohl die Ausführungsformen der vorliegenden Offenbarung im Detail beschrieben wurden, sollten Fachleute verstehen, dass sie verschiedenartige Veränderungen, Ersetzungen und Abwandlungen ausführen können, ohne vom Grundgedanken und Umfang der vorliegenden Offenbarung abzuweichen. In einer Ausführungsform kann die Gate-Elektrode alternativ oder zusätzlich ein anderes geeignetes Metall aufweisen. Beim Auflagerungsvorgang kann eine andere effektive Reinigungsprozedur ausgeführt werden. Das offenbarte Verfahren wird zur Ausbildung eines Transistors, wie z. B. eines n-Kanal-Metall-Oxid-Halbleiter-Feldeffekttransistors (nMOSFET) verwendet, ist aber nicht darauf beschränkt. Werden zum Beispiel mehrere nMOSFETs und mehrere p-Kanal-Metall-Oxid-Halbleiter-Feldeffekttransistoren (pMOSFETs) auf demselben Substrat ausgebildet, dann werden die nMOSFETs und die pMOSFETs in einem Gesamtverfahren ausgebildet, bei dem einige Merkmale entsprechend ausgebildet werden. In einem speziellen Beispiel wird in den nMOSFET-Bereichen ein n-Typ-WF-Metall ausgebildet, während die pMOSFET-Bereiche durch Abscheiden eines n-Metalls abgedeckt sind.

[0057] In einer weiteren Ausführungsform kann das Halbleitersubstrat eine Epitaxialschicht umfassen. Zum Beispiel kann das Substrat eine Epitaxialschicht aufweisen, die auf einem Halbleitersubstratkörper aufliegt. Außerdem kann das Substrat eine Halbleiter-auf-Isolator(SOI)-Struktur, wie z. B. eine dielektrische Einbettungsschicht, aufweisen. Alternativ kann

das Substrat eine dielektrische Einbettungsschicht, so z. B. eine Einbettungsoxid(BOX)-Schicht aufweisen, wie z. B. jene, die durch ein Verfahren, das als Separation durch Implantation von Sauerstoff (SIMOX)-Technologie bezeichnet wird, durch Waferbonden, selektives epitaktisches Aufwachsen (SEG) oder ein anderes geeignetes Verfahren ausgebildet wird

[0058] Die vorliegende Offenbarung verschafft eine Halbleiterstruktur und ein Verfahren zur Herstellung derselben. Die Halbleiterstruktur umfasst einen Gate-Stapel, der eine konvexe Deckfläche aufweist. Ferner kann auf den Randbereichen der konvexen Deckfläche des Gate-Stapels eine Abdeckschicht ausgebildet sein. Die Abdeckschicht wirkt als eine Sperrschicht, um den Gate-Stapel gegen verschiedenartige Beschädigungen, wie z. B. chemische Beschädigungen, während der nachfolgenden Herstellungsprozesse zu schützen. Das Ausbilden des konvexen Gate-Stapels umfasst einen Selektivabtrageprozess, wie z. B. ein selektives CMP oder einen selektiven Ätzprozess, der ausgelegt ist, unterschiedliche Ätzraten für unterschiedliche Metallschichten aufzuweisen, insbesondere höhere Abtragraten für die Metallschichten am Rand und niedrigere Abtragraten für die Metallschichten in der Mitte.

[0059] In einer oder mehreren Ausführungsformen des Verfahrens 100, der Halbleiterstruktur 200, können verschiedenartige Vorzüge vorliegen. Die Halbleiterstruktur 200 umfasst einen Gate-Stapel 250, der eine konvexe Deckfläche aufweist. Ferner wird die Abdeckschicht 260 auf der konvexen Deckfläche in den Randbereichen ausgebildet. Die Abdeckschicht 260 wirkt als eine Sperrschicht. Zum Beispiel wird während eines nachfolgenden Arbeitsschritts zum Ausbilden von Kontakten ein chemisches Ätzen ausgeführt, um die ILD-Schicht, die im Anschluss ausgebildet wurde, zu öffnen. Die Ätzchemikalie kann darüber hinaus den Gate-Stapel 250 von den Seitenwänden her ätzen und ihn dadurch beschädigen. Mit der Schutzwirkung der Abdeckschicht 260 ist der Gate-Stapel 250 geschützt und folglich frei von Beschädigungen. Dementsprechend wird die Bauelementqualität gewährleistet und die Leistungsfähigkeit des Bauelements verbessert.

[0060] Somit verschafft die vorliegende Offenbarung eine Halbleiterstruktur. Die Halbleiterstruktur umfasst ein Halbleitersubstrat, und einen Gate-Stapel, der auf dem Halbleitersubstrat angeordnet ist, wobei der Gate-Stapel eine Schicht aus einem high-k-dielektrischen Material aufweist und verschiedenartige Metallschichten auf der Schicht aus dem high-k-dielektrischen Material angeordnet sind, wobei der Gate-Stapel eine konvexe Deckfläche aufweist.

[0061] Die vorliegende Offenbarung verschafft auch eine Halbleiterstruktur gemäß einigen Ausführungs-

formen. Die Halbleiterstruktur umfasst ein Halbleitersubstrat und einen Gate-Stapel, der auf dem Halbleitersubstrat angeordnet ist. Der Gate-Stapel umfasst eine Gate-Dielektrikumschicht, die ein high-k-dielektrisches Material aufweist, eine Abdeckschicht, die auf der Schicht aus dem high-k-dielektrischen Material angeordnet ist, eine Austrittsarbeit-Metallschicht, die über der Deckschicht angeordnet ist, eine Sperrschicht, die auf der Austrittsarbeit-Metallschicht angeordnet ist und eine Füllmetallschicht, die auf der Sperrschicht angeordnet ist. Der Gate-Stapel weist eine konvexe Deckfläche auf.

[0062] Die vorliegende Offenbarung verschafft ein Verfahren gemäß einigen Ausführungsformen. Das Verfahren umfasst das Ausbilden eines Dummygates auf einem Halbleitersubstrat, das Ausbilden einer Zwischenschichtdielektrikum-Schicht auf dem Substrat, das Beseitigen des Dummygates, was einen Gate-Graben in der Zwischenschichtdielektrikum-Schicht zur Folge hat, das Ausbilden verschiedenartiger Gate-Materialschichten zum Einfüllen in den Gate-Graben, wobei die Gate-Materialschichten eine Gate-Dielektrikumschicht, verschiedenartige Metallschichten auf der Abdeckschicht umfasst, und das Ausführen eines Selektivabtrageprozesses, wodurch ein Gate-Stapel ausgebildet wird, der eine konvexe Deckfläche aufweist.

[0063] Vorangehend werden Merkmale verschiedener Ausführungsformen kurz dargestellt. Fachleute sollten anerkennen, dass sie die vorliegende Offenbarung leicht als eine Grundlage dafür einsetzen können, andere Prozesse und Strukturen zu konzipieren oder abzuwandeln, um die gleichen Zielstellungen zu realisieren und/oder die gleichen Vorteile der hier dargelegten Ausführungsformen zu erreichen. Fachleute sollten auch erkennen, dass derartige gleichwertige Konstruktionen nicht vom Grundgedanken und Umfang der vorliegenden Offenbarung abweichen und dass sie hierin verschiedenartige Veränderungen, Ersetzungen und Abwandlungen ausführen können, ohne vom Grundgedanken und Umfang der vorliegenden Offenbarung abzuweichen.

#### **Patentansprüche**

- 1. Halbleiterstruktur mit: einem Halbleitersubstrat und einem Gate-Stapel, der auf dem Halbleitersubstrat angeordnet ist, wobei der Gate-Stapel eine Schicht aus einem high-k-dielektrischen Material und verschiedenartige Metallschichten, die auf der Schicht aus einem high-k-dielektrischen Material angeordnet sind, aufweist, wobei der Gate-Stapel eine konvexe Deckfläche aufweist.

- 2. Halbleiterstruktur nach Anspruch 1, wobei die konvexe Deckfläche des Gate-Stapels eine Höhendifferenz H und eine Breite W aufweist und ein Ver-

hältnis H/W in einem Bereich von circa 10% bis zu circa 50% liegt.

- 3. Halbleiterstruktur nach Anspruch 2, wobei die Höhendifferenz H in einem Bereich von circa 2 nm bis zu circa 10 nm liegt.

- 4. Halbleiterstruktur nach einem der vorhergehenden Ansprüche, ferner mit einer oberen Abdeckschicht, die auf der konvexen Deckfläche des Gate-Stapels in den Randbereichen angeordnet ist.

- 5. Halbleiterstruktur nach Anspruch 4, wobei die obere Abdeckschicht ein dielektrisches Material aufweist, das aus der Gruppe ausgewählt ist, die aus Siliziumoxid, Siliziumnitrid, low-k-dielektrischem Material und einer Kombination davon besteht.

- 6. Halbleiterstruktur nach einem der vorhergehenden Ansprüche, wobei der Gate-Stapel umfasst: eine Grenzflächenschicht auf dem Halbleitersubstrat, eine Schicht aus einem high-k-dielektrischen Material auf der Grenzflächenschicht,

eine Abdeckschicht auf der Schicht aus einem highk-dielektrischen Material,

eine Austrittsarbeit-Metallschicht, die auf der Abdeckschicht angeordnet ist,

eine Sperrschicht auf der Austrittsarbeit-Metallschicht und

eine Füllmetallschicht.

- 7. Halbleiterstruktur nach Anspruch 6, ferner mit einer weiteren Sperrschicht, die zwischen der Austrittsarbeit-Metallschicht und der Abdeckschicht angeordnet ist.

- 8. Halbleiterstruktur nach einem der Ansprüche 5 bis 7, wobei

die Grenzflächenschicht Siliziumoxid aufweist,

die Abdeckschicht entweder Titannitrid oder Tantalnitrid aufweist,

die Sperrschicht entweder Titannitrid oder Tantalnitrid aufweist und

die Füllmetallschicht entweder Aluminium oder Wolfram aufweist.

Halbleiterstruktur mit:

einem Halbleitersubstrat und

einem Gate-Stapel, der auf dem Halbleitersubstrat angeordnet ist, wobei der Gate-Stapel umfasst: eine Gate-Dielektrikumschicht, die ein high-k-dielek-

eine Gate-Dielektrikumschicht, die ein high-k-dielek trisches Material aufweist,

eine Abdeckschicht, die auf der Schicht aus dem high-k-dielektrischen Material angeordnet ist,

eine Austrittsarbeit-Metallschicht, die über der Deckschicht angeordnet ist,

eine Sperrschicht, die auf der Austrittsarbeit-Metallschicht angeordnet ist, und eine Füllmetallschicht, die auf der Sperrschicht angeordnet ist, wobei der Gate-Stapel eine konvexe Deckfläche aufweist.

- 10. Halbleiterstruktur nach Anspruch 9, wobei die konvexe Deckfläche des Gate-Stapels eine Höhendifferenz H und eine Breite W aufweist und ein Verhältnis H/W in einem Bereich von circa 10% bis zu circa 50% liegt.

- 11. Halbleiterstruktur nach Anspruch 10, wobei die Höhendifferenz H in einem Bereich von circa 2 nm bis zu circa 10 nm liegt.

- 12. Halbleiterstruktur nach einem der Ansprüche 9 bis 11, ferner mit einer oberen Abdeckschicht, die auf der konvexen Deckfläche des Gate-Stapels in den Randbereichen angeordnet ist.

- 13. Halbleiterstruktur nach Anspruch 12, wobei die obere Abdeckschicht ein dielektrisches Material aufweist, das aus der Gruppe ausgewählt ist, die aus Siliziumoxid, Siliziumnitrid, low-k-dielektrischem Material und einer Kombination davon besteht.

- 14. Verfahren zum Ausbilden einer Halbleiterstruktur, umfassend:

Ausbilden eines Dummygates auf einem Halbleitersubstrat.

Ausbilden einer Zwischenschichtdielektrikum-Schicht auf dem Substrat,

Beseitigen des Dummygates, was einen Gate-Graben in der Zwischenschichtdielektrikum-Schicht zur Folge hat.

Ausbilden verschiedenartiger Gate-Materialschichten zum Einfüllen in den Gate-Graben, wobei die Gate-Materialschichten eine Gate-Dielektrikumschicht, verschiedenartige Metallschichten auf der Abdeckschicht umfassen, und

Ausführen eines Selektivabtrageprozesses, wodurch ein Gate-Stapel ausgebildet wird, der eine konvexe Deckfläche aufweist.

- 15. Verfahren nach Anspruch 14, wobei der Selektivabtrageprozess einen selektiven chemisch-mechanischen Polier(CMP)-Prozess umfasst, wobei der selektive CMP-Prozess ein Poliermittel einsetzt, das Chemikalien aufweist, um ausgewählte Abtragraten für die verschiedenartigen Metallschichten zu liefern.

- 16. Verfahren nach Anspruch 14 oder 15, wobei der Selektivabtrageprozess einen selektiven Ätzprozess umfasst, wobei der selektive Ätzprozess ein Ätzmittel einsetzt, das ausgewählte Ätzraten für die verschiedenartigen Metallschichten aufweist.

- 17. Verfahren nach Anspruch 16, wobei das Ätzmittel das erste Ätzmittel umfasst, das eine Chemikalie aufweist, die aus der Gruppe ausgewählt ist, die

aus F2, Cl2, BCl3 und einer Kombination davon besteht.

- 18. Verfahren nach einem der Ansprüche 14 bis 17, wobei das Ausbilden verschiedenartiger Gate-Materialschichten das Ausbilden umfasst von: einer Gate-Dielektrikumschicht, die ein high-k-dielektrisches Material aufweist, einer Abdeckschicht, die auf der Schicht aus dem high-k-dielektrischen Material angeordnet ist, einer Austrittsarbeit-Metallschicht, die über der Deckschicht angeordnet ist, einer Sperrschicht, die auf der Austrittsarbeit-Metallschicht angeordnet ist und einer Füllmetallschicht, die auf der Sperrschicht angeordnet ist, wobei der Gate-Stapel eine konvexe Deckfläche aufweist.

- 19. Verfahren nach einem der Ansprüche 14 bis 18, ferner umfassend, dass eine obere Abdeckschicht auf der konvexen Deckfläche des Gate-Stapels in den Randbereichen ausgebildet wird, wobei das Ausbilden der oberen Abdeckschicht ein Abscheiden einer dielektrischen Schicht auf dem Substrat und dem Gate-Stapel umfasst, und dass ein chemisch-mechanischer Polierprozess an der oberen Abdeckschicht ausgeführt wird.

- 20. Verfahren nach Anspruch 19, wobei das Abscheiden der oberen Abdeckschicht ein Abscheiden eines dielektrischen Materials umfasst, das aus der Gruppe ausgewählt ist, die aus Siliziumoxid, Siliziumnitrid, low-k-dielektrischem Material und einer Kombination davon besteht.

Es folgen 17 Seiten Zeichnungen

### Anhängende Zeichnungen

Fig. 1

Fig. 2

Fig. 3A

Fig. 3B

Fig. 3C

Fig. 4

Fig. 5

Fig. 6

**Fig.** 7

Fig. 8

Fig. 9

Fig. 10

Fig. 11

Fig. 12

Fig. 13A

Fig. 13B

**Fig. 13C**