(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7264669号**

**(P7264669)**

(45)発行日 令和5年4月25日(2023.4.25)

(24)登録日 令和5年4月17日(2023.4.17)

(51)国際特許分類

|         |                 |     |         |       |         |

|---------|-----------------|-----|---------|-------|---------|

| G 0 9 F | 9/30 (2006.01)  | F I | G 0 9 F | 9/30  | 3 3 0   |

| G 0 9 F | 9/33 (2006.01)  |     | G 0 9 F | 9/30  | 3 3 8   |

| H 0 1 L | 33/62 (2010.01) |     | G 0 9 F | 9/30  | 3 4 9 D |

|         |                 |     | G 0 9 F | 9/33  |         |

|         |                 |     | H 0 1 L | 33/62 |         |

請求項の数 11 (全21頁)

(21)出願番号 特願2019-37721(P2019-37721)

(22)出願日 平成31年3月1日(2019.3.1)

(65)公開番号 特開2020-140171(P2020-140171)

A)

(43)公開日 令和2年9月3日(2020.9.3)

審査請求日 令和4年2月28日(2022.2.28)

(73)特許権者 502356528

株式会社ジャパンディスプレイ

東京都港区西新橋三丁目7番1号

(74)代理人 110002147

弁理士法人酒井国際特許事務所

池田 雅延

(72)発明者 東京都港区西新橋三丁目7番1号 株式

会社ジャパンディスプレイ内

伊東 理

東京都港区西新橋三丁目7番1号 株式

会社ジャパンディスプレイ内

金谷 康弘

東京都港区西新橋三丁目7番1号 株式

会社ジャパンディスプレイ内

審査官 石本 努

最終頁に続く

(54)【発明の名称】 表示装置

**(57)【特許請求の範囲】****【請求項1】**

基板と、

前記基板に設けられた複数の画素と、

複数の前記画素の各々に設けられ、第1の面に設けられたアノード端子と、前記第1の面と対向する第2の面に設けられたカソード端子とを有する発光素子と、

前記発光素子に電気的に接続される第1電極と、

前記基板に設けられ、前記第1電極と電気的に接続されるトランジスタと、

前記基板に垂直な方向において、前記第1電極と前記アノード端子との間に設けられ、複数の導電性ナノ粒子を含む接続層と、

複数の前記発光素子の間に設けられ、前記発光素子と重なる位置に貫通孔を有する素子絶縁膜と、

前記発光素子の側面と対向して設けられ、複数の導電性ナノ粒子を含む反射層と、を有し、前記貫通孔の、前記発光素子の側面と対向する面は、上に凸形状の表面を有し、

前記反射層は、前記上に凸形状の表面を覆うように形成され、

前記接続層は、前記カソード端子と接することなく設けられている、

表示装置。

**【請求項2】**前記接続層は、複数の前記導電性ナノ粒子の間に空隙を有する

請求項1に記載の表示装置。

**【請求項 3】**

前記基板に垂直な方向からの平面視で、前記第1電極の面積は、前記発光素子の面積よりも大きい。

請求項1又は請求項2に記載の表示装置。

**【請求項 4】**

前記基板に垂直な方向からの平面視で、前記第1電極の面積は、前記アノード端子の面積よりも大きい。

請求項1又は請求項2に記載の表示装置。

**【請求項 5】**

複数の前記発光素子及び前記素子絶縁膜を覆って、複数の前記発光素子に電気的に接続される第2電極、を有する

10

請求項1に記載の表示装置。

**【請求項 6】**

前記反射層の下端は前記第1電極と電気的に接続され、前記反射層の上端は前記第2電極と離隔する。

請求項5に記載の表示装置。

**【請求項 7】**

前記導電性ナノ粒子は、銀又は銀合金を含む。

請求項1から請求項6のいずれか1項に記載の表示装置。

20

**【請求項 8】**

前記第1電極は、モリブデン、チタンの金属のいずれか1つ以上を含む、又は前記金属のいずれか1つ以上を含む合金、又は透光性導電材料のいずれかを有する。

請求項1から請求項7のいずれか1項に記載の表示装置。

**【請求項 9】**

前記第1電極は、複数の導電性ナノ粒子を含む。

請求項1から請求項7のいずれか1項に記載の表示装置。

**【請求項 10】**

発光素子基板と、前記発光素子基板に設けられた、少なくとも一つの前記発光素子と、前記発光素子基板に設けられ、前記発光素子を駆動する少なくとも一つの回路素子とを含むチップ部品を有し、

30

前記チップ部品は前記基板にアレイ状に配列するように複数設けられる。

請求項1から請求項9のいずれか1項に記載の表示装置。

**【請求項 11】**

前記チップ部品には、互いに異なる発光を呈する前記発光素子がそれぞれ少なくとも一つずつ設けられる。

請求項10に記載の表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、表示装置に関する。

40

**【背景技術】****【0002】**

近年、表示素子として微小サイズの発光ダイオード（マイクロLED（micro LED））を用いたディスプレイが注目されている（例えば、特許文献1参照）。複数の発光ダイオードは、例えばハンダなどの接続部材を介して、アレイ基板上の電極に接続される。

**【先行技術文献】****【特許文献】****【0003】**

【文献】特表2017-529557号公報

50

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

発光ダイオードは、熱圧着によりアレイ基板上に接続される。このため、発光ダイオードとアレイ基板との接続部分には、冷却後に残留応力が残る。また、発光ダイオードの小型化に伴い発光ダイオードの接続面積も小さくなるため、残留応力により接続信頼性が低下する可能性がある。

**【0005】**

本発明は、発光素子とアレイ基板との接続信頼性を向上させることができる表示装置を提供することを目的とする。

10

**【課題を解決するための手段】****【0006】**

本発明の一態様の表示装置は、基板と、前記基板に設けられた複数の画素と、複数の前記画素の各々に設けられる発光素子と、前記発光素子に電気的に接続される第1電極と、前記基板に設けられ、前記第1電極と電気的に接続されるトランジスタと、前記基板に垂直な方向において、前記第1電極と前記発光素子との間に設けられ、複数の導電性ナノ粒子を含む接続層と、を有する。

**【図面の簡単な説明】****【0007】**

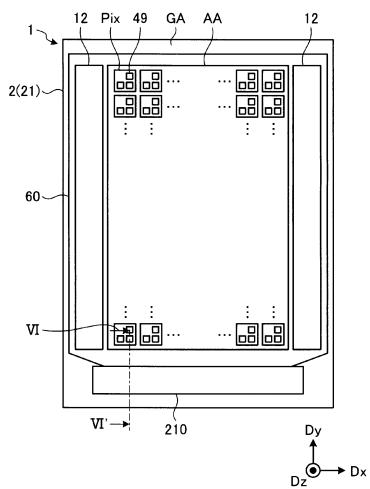

【図1】図1は、第1実施形態に係る表示装置を模式的に示す平面図である。

20

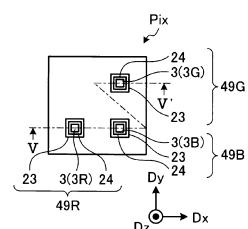

【図2】図2は、複数の画素を示す平面図である。

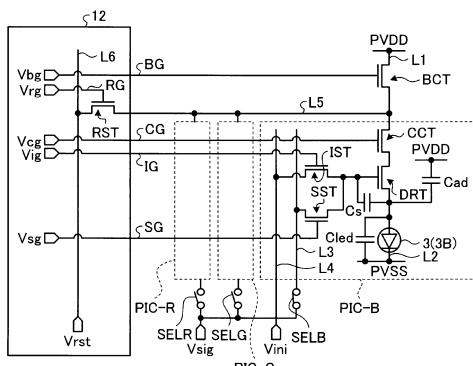

【図3】図3は、画素回路を示す回路図である。

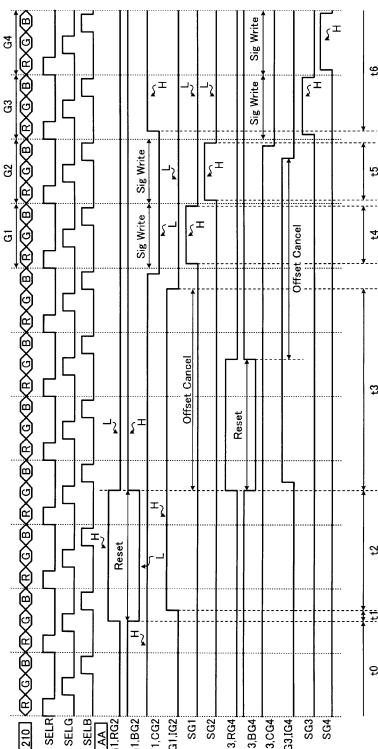

【図4】図4は、表示装置の動作例を示すタイミングチャートである。

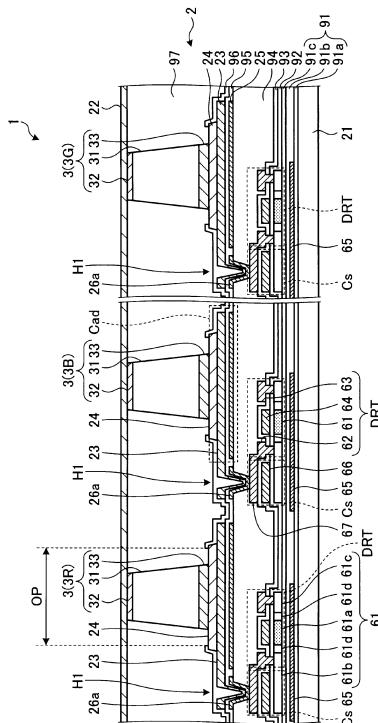

【図5】図5は、図2のV-V'断面図である。

【図6】図6は、図1のVI-VI'断面図である。

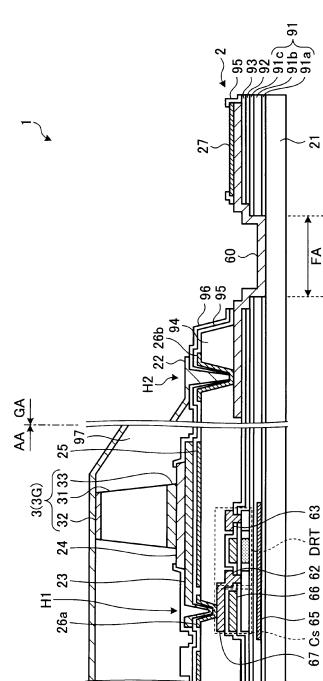

【図7】図7は、発光素子とアノード電極との接続工程を説明するための説明図である。

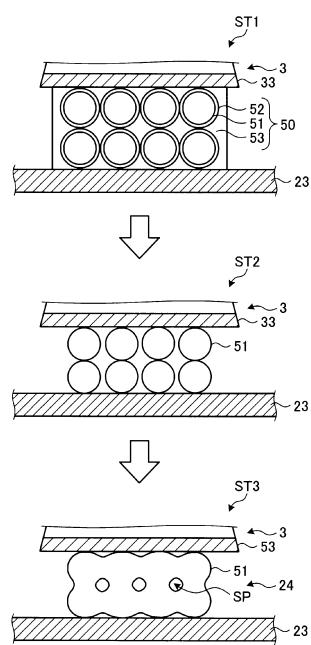

【図8】図8は、接続層のパターニング方法を説明するための説明図である。

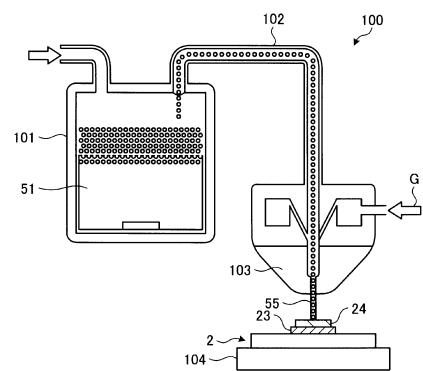

【図9】図9は、接続層のパターニング方法の第1変形例を説明するための説明図である。

【図10】図10は、接続層のパターニング方法の第2変形例を説明するための説明図である。

30

【図11】図11は、第2実施形態に係る表示装置を示す断面図である。

【図12】図12は、第3実施形態に係る表示装置を示す断面図である。

【図13】図13は、第4実施形態に係る表示装置を示す断面図である。

**【発明を実施するための形態】****【0008】**

本発明を実施するための形態(実施形態)につき、図面を参照しつつ詳細に説明する。以下の実施形態に記載した内容により本発明が限定されるものではない。また、以下に記載した構成要素には、当業者が容易に想定できるもの、実質的に同一のものが含まれる。さらに、以下に記載した構成要素は適宜組み合わせることが可能である。なお、開示はあくまで一例にすぎず、当業者において、発明の主旨を保っての適宜変更について容易に想到し得るものについては、当然に本発明の範囲に含有されるものである。また、図面は説明をより明確にするため、実際の態様に比べ、各部の幅、厚さ、形状等について模式的に表される場合があるが、あくまで一例であって、本発明の解釈を限定するものではない。また、本明細書と各図において、既出の図に関して前述したものと同様の要素には、同一の符号を付して、詳細な説明を適宜省略することがある。

40

**【0009】**

本明細書及び特許請求の範囲において、ある構造体の上に他の構造体を配置する態様を表現するにあたり、単に「上に」と表記する場合、特に断りの無い限りは、ある構造体に接するように、直上に他の構造体を配置する場合と、ある構造体の上方に、さらに別の構造体を介して他の構造体を配置する場合との両方を含むものとする。

50

**【 0 0 1 0 】**

(第1実施形態)

図1は、第1実施形態に係る表示装置を模式的に示す平面図である。図1に示すように、表示装置1は、アレイ基板2と、画素Pi×と、駆動回路12と、駆動IC(Integrated Circuit)210と、カソード配線60と、を含む。アレイ基板2は、各画素Pi×を駆動するための駆動回路基板であり、バックプレーン又はアクティブマトリックス基板とも呼ばれる。アレイ基板2は、基板21、複数のトランジスタ、複数の容量及び各種配線等を有する。

**【 0 0 1 1 】**

図1に示すように、表示装置1は、表示領域AAと、周辺領域GAとを有する。表示領域AAは、複数の画素Pi×と重なって配置され、画像を表示する領域である。周辺領域GAは、複数の画素Pi×と重ならない領域であり、表示領域AAの外側に配置される。

10

**【 0 0 1 2 】**

複数の画素Pi×は、基板21の表示領域AAにおいて、第1方向Dx及び第2方向Dyに配列される。なお、第1方向Dx及び第2方向Dyは、基板21の表面に対して平行な方向である。第1方向Dxは、第2方向Dyと直交する。ただし、第1方向Dxは、第2方向Dyと直交しないで交差してもよい。第3方向Dzは、第1方向Dx及び第2方向Dyと直交する方向である。第3方向Dzは、例えば、基板21の法線方向に対応する。なお、以下、平面視とは、第3方向Dzから見た場合の位置関係を示す。

**【 0 0 1 3 】**

駆動回路12は、駆動IC210からの各種制御信号に基づいて複数のゲート線（例えば、発光制御走査線BG、リセット制御走査線RG、補正制御走査線CG、初期化制御走査線IG、書き制御走査線SG（図3参照））を駆動する回路である。駆動回路12は、複数のゲート線を順次又は同時に選択し、選択されたゲート線にゲート駆動信号を供給する。これにより、駆動回路12は、ゲート線に接続された複数の画素Pi×を選択する。

20

**【 0 0 1 4 】**

駆動IC210は、表示装置1の表示を制御する回路である。駆動IC210は、基板21の周辺領域GAにCOG(Chip On Glass)として実装される。これに限定されず、駆動IC210は、基板21の周辺領域GAに接続されたフレキシブルプリント基板やリジット基板の上にCOF(Chip On Film)として実装されてもよい。

30

**【 0 0 1 5 】**

カソード配線60は、基板21の周辺領域GAに設けられる。カソード配線60は、表示領域AAの複数の画素Pi×及び周辺領域GAの駆動回路12を囲んで設けられる。複数の発光素子3のカソードは、共通のカソード配線60に電気的に接続され、固定電位（例えば、グランド電位）が供給される。より具体的には、発光素子3のカソード端子32（図5参照）は、カソード電極22（第2電極）を介して、カソード配線60に接続される。

**【 0 0 1 6 】**

図2は、複数の画素を示す平面図である。図2に示すように、1つの画素Pi×は、複数の副画素49を含む。例えば、画素Pi×は、第1副画素49Rと、第2副画素49Gと、第3副画素49Bとを有する。第1副画素49Rは、第1色としての原色の赤色を表示する。第2副画素49Gは、第2色としての原色の緑色を表示する。第3副画素49Bは、第3色としての原色の青色を表示する。図2に示すように、1つの画素Pi×において、第1副画素49Rと第3副画素49Bは第1方向Dxで並ぶ。また、第2副画素49Gと第3副画素49Bは第2方向Dyで並ぶ。なお、第1色、第2色、第3色は、それぞれ赤色、緑色、青色に限られず、補色などの任意の色を選択することができる。以下において、第1副画素49Rと、第2副画素49Gと、第3副画素49Bとをそれぞれ区別する必要がない場合、副画素49という。

40

**【 0 0 1 7 】**

副画素49は、それぞれ発光素子3と、アノード電極23（第1電極）と、接続層24

50

と、を有する。表示装置 1 は、第 1 副画素 49R、第 2 副画素 49G 及び第 3 副画素 49Bにおいて、発光素子 3R、3G、3B ごとに異なる光（例えば、赤色、緑色、青色の光）を出射することで画像を表示する。発光素子 3 は、複数の副画素 49 の各々に設けられる。発光素子 3 は、平面視で、 $3 \mu\text{m}$ 以上、 $300 \mu\text{m}$ 以下程度の大きさを有する発光ダイオード（LED : Light Emitting Diode）チップであり、マイクロ LED（micro LED）と呼ばれる。各画素にマイクロ LED を備える表示装置 1 は、マイクロ LED 表示装置とも呼ばれる。なお、マイクロ LED のマイクロは、発光素子 3 の大きさを限定するものではない。

#### 【0018】

なお、複数の発光素子 3 は、4 色以上の異なる光を出射してもよい。また、複数の副画素 49 の配置は、図 2 に示す構成に限定されない。例えば、第 1 副画素 49R は第 2 副画素 49G と第 1 方向 D<sub>X</sub> に隣り合っていてもよい。また、第 1 副画素 49R、第 2 副画素 49G 及び第 3 副画素 49B が、この順で第 1 方向 D<sub>X</sub> に繰り返し配列されてもよい。

10

#### 【0019】

図 3 は、画素回路を示す回路図である。図 3 に示す画素回路 P I C - R、P I C - G、P I C - B は、それぞれ第 1 副画素 49R、第 2 副画素 49G 及び第 3 副画素 49B に対応して設けられる。図 3 では、画素回路 P I C - B の回路図を示し、画素回路 P I C - R、P I C - G については省略して示しているが、画素回路 P I C - B についての説明は、画素回路 P I C - R、P I C - G にも適用できる。

20

#### 【0020】

図 3 に示すように、画素回路 P I C - B は、発光素子 3 と、5 つのトランジスタと、3 つの容量とを含む。具体的には、画素回路 P I C - B は、発光制御トランジスタ BCT、補正トランジスタ CCT、初期化トランジスタ IST、書きトランジスタ SST 及び駆動トランジスタ DRT を含む。一部のトランジスタは、隣接する複数の副画素 49 で共有されていてもよい。図 3 に示す例では、発光制御トランジスタ BCT は、共通配線 L5 を介して、3 つの副画素 49 で共有される。また、リセットトランジスタ RST は、周辺領域 GA に、例えば副画素 49 の各行に 1 つ設けられる。リセットトランジスタ RST のドレインは、共通配線 L5 を介して複数の画素回路 P I C - R、P I C - G、P I C - B に接続される。

30

#### 【0021】

発光制御トランジスタ BCT、補正トランジスタ CCT、初期化トランジスタ IST、書きトランジスタ SST、駆動トランジスタ DRT 及びリセットトランジスタ RST は、それぞれ n 型 TFT (Thin Film Transistor) で構成される。ただし、これに限定されず、各トランジスタは、それぞれ p 型 TFT で構成されてもよい。p 型 TFT を用いる場合は、適宜電源電位や保持容量 Cs の接続を適合させてもよい。

40

#### 【0022】

発光制御走査線 BG は、発光制御トランジスタ BCT のゲートに接続される。リセット制御走査線 RG は、リセットトランジスタ RST のゲートに接続される。補正制御走査線 CG は、補正トランジスタ CCT のゲートに接続される。初期化制御走査線 IG は、初期化トランジスタ IST のゲートに接続される。書き制御走査線 SG は、書きトランジスタ SST のゲートに接続される。

40

#### 【0023】

発光制御走査線 BG、リセット制御走査線 RG、補正制御走査線 CG、初期化制御走査線 IG 及び書き制御走査線 SG は、それぞれ、周辺領域 GA に設けられた駆動回路 12 に接続される。駆動回路 12 は、発光制御走査線 BG、リセット制御走査線 RG、補正制御走査線 CG、初期化制御走査線 IG 及び書き制御走査線 SG に、それぞれ、発光制御信号 Vbg、リセット制御信号 Vrg、補正制御信号 Vcg、初期化制御信号 Vig 及び書き制御信号 Vsg を供給する。

#### 【0024】

複数の画素回路 P I C - R、P I C - G、P I C - B には、スイッチ素子 SELR、S

50

E L G、S E L B を介して、映像信号 V s i g が供給される。駆動 I C 2 1 0 (図 1 参照)は、スイッチ素子 S E L R、S E L G、S E L B に制御信号を出力して、複数の画素回路 P I C - R、P I C - G、P I C - B に、時分割で映像信号 V s i g を供給する。映像信号 V s i g は、映像信号線 L 3 を介して書込トランジスタ S S T に供給される。また、駆動 I C 2 1 0 は、初期化信号線 L 4 を介して、初期化電位 V i n i を初期化トランジスタ I S T に供給する。駆動回路 1 2 は、リセット信号線 L 6 を介して、リセット電源電位 V r s t をリセットトランジスタ R S T に供給する。

#### 【 0 0 2 5 】

発光制御トランジスタ B C T、補正トランジスタ C C T、初期化トランジスタ I S T、書込トランジスタ S S T 及びリセットトランジスタ R S T は、2 ノード間の導通と非導通とを選択するスイッチング素子として機能する。駆動トランジスタ D R T は、ゲートとドレインとの間の電圧に応じて、発光素子 3 に流れる電流を制御する電流制御素子として機能する。

#### 【 0 0 2 6 】

発光素子 3 のカソード (カソード端子 3 2 ) は、カソード電源線 L 2 に接続される。また、発光素子 3 のアノード (アノード端子 3 3 ) は、駆動トランジスタ D R T、補正トランジスタ C C T 及び発光制御トランジスタ B C T を介してアノード電源線 L 1 に接続される。アノード電源線 L 1 には、アノード電源電位 P V D D が供給される。カソード電源線 L 2 には、カソード配線 6 0 及びカソード電極 2 2 を介してカソード電源電位 P V S S が供給される。アノード電源電位 P V D D は、カソード電源電位 P V S S よりも高い電位である。なお、発光素子 3 の発光動作については後述する。

#### 【 0 0 2 7 】

また、画素回路 P I C - B は、保持容量 C s 及び容量 C 1 e d、C a d を含む。保持容量 C s は、駆動トランジスタ D R T のゲートとソースとの間に形成される容量である。容量 C 1 e d は、発光素子 3 のアノードとカソードとの間に形成される寄生容量である。容量 C a d は、駆動トランジスタ D R T のソース及び発光素子 3 のアノードと、アノード電源線 L 1 との間に形成される付加容量である。

#### 【 0 0 2 8 】

図 4 は、表示装置の動作例を示すタイミングチャートである。図 4 に示す期間 G 1 から期間 G 4 のそれぞれが 1 水平期間である。なお、図 4 では、1 行目の副画素 4 9 から 4 行目の副画素 4 9 を駆動する動作を示しているが、5 行目以降、最終行の副画素 4 9 まで継続して駆動される。また、以下の説明では、1 行目の副画素 4 9 から最終行の副画素 4 9 までの駆動を行う期間をフレーム期間と表す。

#### 【 0 0 2 9 】

図 4 に示す期間 t 0 から期間 t 6 までの動作例について、以下詳細に説明する。期間 t 0 は、前フレーム発光期間である。つまり、あるフレーム期間での処理が開始されるまでの期間 t 0 では、副画素 4 9 は、前フレームの発光状態を継続している。

#### 【 0 0 3 0 】

次に、期間 t 1 は、駆動トランジスタ D R T のソース初期化期間である。具体的には、期間 t 1 では、駆動回路 1 2 から供給される各制御信号により、発光制御走査線 B G 1、B G 2 の電位が L (ロウ) レベルとなり、補正制御走査線 C G 1、C G 2 の電位が H (ハイ) レベルとなり、リセット制御走査線 R G 1、R G 2 の電位が H レベルとなる。これにより、発光制御トランジスタ B C T がオフ (非導通状態) となり、補正トランジスタ C C T 及びリセットトランジスタ R S T がオン (導通状態) となる。

#### 【 0 0 3 1 】

なお、発光制御走査線 B G 1 は、1 行目の副画素 4 9 に接続された発光制御走査線 B G を示し、発光制御走査線 B G 2 は、2 行目の副画素 4 9 に接続された発光制御走査線 B G を示す。発光制御走査線 B G 3 は、3 行目の副画素 4 9 に接続された発光制御走査線 B G を示し、発光制御走査線 B G 4 は、4 行目の副画素 4 9 に接続された発光制御走査線 B G を示す。補正制御走査線 C G 1、C G 2、リセット制御走査線 R G 1、R G 2 等の各走査

10

20

30

40

50

線も同様である。

#### 【 0 0 3 2 】

期間  $t_1$  では、1行目及び2行目に属する副画素49において、アノード電源線L1からの電流が発光制御トランジスタBCTにより遮断される。発光素子3の発光が停止するとともに、副画素49内に残留していた電荷が、リセットトランジスタRSTを通じて外部に流れる。これにより、駆動トランジスタDRTのソースがリセット電源電位Vrstに固定される。リセット電源電位Vrstは、カソード電源電位PVSSに対して所定の電位差を有して設定される。この場合、リセット電源電位Vrstとカソード電源電位PVSSとの電位差は、発光素子3が発光を開始する電位差よりも小さい。

#### 【 0 0 3 3 】

次に、期間  $t_2$  は、駆動トランジスタDRTのゲート初期化期間である。具体的には、期間  $t_2$  では、駆動回路12から供給される各制御信号により、初期化制御走査線IG1、IG2の電位がHレベルとなる。初期化トランジスタISTは、オンとなる。1行目及び2行目に属する副画素49において、初期化トランジスタISTを通して駆動トランジスタDRTのゲートが初期化電位Vininiに固定される。初期化電位Vininiは、リセット電源電位Vrstに対して、駆動トランジスタDRTのしきい値よりも大きい電位を有している。このため、駆動トランジスタDRTはオンとなる。ただし、期間  $t_2$  では、発光制御トランジスタBCTがオフの状態を維持しているので、駆動トランジスタDRTには電流が流れない。

#### 【 0 0 3 4 】

次に、期間  $t_3$  は、オフセットキャンセル動作期間である。具体的には、期間  $t_3$  では、駆動回路12から供給される各制御信号により、発光制御走査線BG1、BG2の電位がHレベルとなり、リセット制御走査線RG1、RG2の電位がLレベルとなる。これにより、発光制御トランジスタBCTがオンとなり、リセットトランジスタRSTがオフとなる。

#### 【 0 0 3 5 】

駆動トランジスタDRTは、期間  $t_2$  の動作によりオン状態となっている。このため、アノード電源線L1（アノード電源電位PVDD）から、発光制御トランジスタBCT及び補正トランジスタCCSを介して駆動トランジスタDRTに電流が供給される。

#### 【 0 0 3 6 】

この段階では、発光素子3のアノードとカソードとの間の電圧は、発光開始電圧よりも小さいので、電流が流れない。したがって、アノード電源電位PVDDによって駆動トランジスタDRTのソースが充電され、ソースの電位が上昇する。駆動トランジスタDRTのゲート電位は、初期化電位Vininiとなっている。このため、駆動トランジスタDRTのソース電位が( $V_{inini} - V_{th}$ )となった段階で駆動トランジスタDRTがオフになり、電位の上昇が停止する。ここで、 $V_{th}$ は、駆動トランジスタDRTのしきい値電圧 $V_{th}$ である。

#### 【 0 0 3 7 】

しきい値電圧 $V_{th}$ は、副画素49ごとにばらつきがある。このため、電位の上昇が停止したときの駆動トランジスタDRTのソースの電位は、副画素49ごとに異なる。つまり、期間  $t_3$  の動作によって、各副画素49で、駆動トランジスタDRTのしきい値電圧 $V_{th}$ に相当する電圧が取得される。このとき、発光素子3には、(( $V_{inini} - V_{th}$ ) - PVSS)の電圧が印加される。この電圧は、発光素子3の発光開始電圧よりも小さいので、発光素子3には電流が流れない。

#### 【 0 0 3 8 】

なお、図4に示す動作例では、期間  $t_1$  から期間  $t_3$  において、2行分の副画素49の駆動が同時に実施されているが、これに限定されない。駆動回路12は、1行の副画素49ごとに駆動してもよいし、3行分の副画素49を同時に駆動してもよい。

#### 【 0 0 3 9 】

次に、期間  $t_4$  及び期間  $t_5$  は、映像信号書き込み動作期間である。具体的には、期間  $t_4$

10

20

30

40

50

では、駆動回路 1 2 から供給される各制御信号により、補正制御走査線 C G 1、C G 2 の電位が L レベルとなり、初期化制御走査線 I G 1、I G 2 の電位が L レベルとなり、書込制御走査線 S G 1 が H レベルとなる。期間 t 5 では、駆動回路 1 2 から供給される各制御信号により、補正制御走査線 C G 1、C G 2 の電位が L レベルとなり、初期化制御走査線 I G 1、I G 2 の電位が L レベルとなり、書込制御走査線 S G 2 が H レベルとなる。

#### 【 0 0 4 0 】

これにより、補正トランジスタ C C T がオフになり、初期化トランジスタ I S T がオフになり、書込トランジスタ S S T がオンになる。期間 t 4 では、1 行目に属する副画素 4 9 において、映像信号 V s i g が駆動トランジスタ D R T のゲートに入力される。駆動トランジスタ D R T のゲート電位は、初期化電位 V i n i から映像信号 V s i g の電位に変化する。一方、駆動トランジスタ D R T のソースの電位は、( V i n i - V t h ) を維持している。この結果、駆動トランジスタ D R T のゲートとソースとの間の電圧は、( V s i g - ( V i n i - V t h ) ) となり、副画素 4 9 間のしきい値電圧 V t h のばらつきが反映されたものとなる。

#### 【 0 0 4 1 】

期間 t 5 では、同様に、2 行目に属する副画素 4 9 において、映像信号 V s i g が駆動トランジスタ D R T のゲートに入力され、駆動トランジスタ D R T のゲートとソースとの間の電圧は、( V s i g - ( V i n i - V t h ) ) となる。

#### 【 0 0 4 2 】

映像信号線 L 3 は、第 2 方向 D y ( 図 1 参照 ) に延在し、同列に属する複数行の副画素 4 9 に接続される。このため、映像書込動作を行う期間 t 4 及び期間 t 5 は、1 行ごとに実施される。

#### 【 0 0 4 3 】

次に、期間 t 6 は、発光動作期間である。具体的には、期間 t 6 では、駆動回路 1 2 から供給される各制御信号により、補正制御走査線 C G 1、C G 2 の電位が H レベルとなり書込制御走査線 S G 1、S G 2 が L レベルとなる。これにより、補正トランジスタ C C T がオンになり、書込トランジスタ S S T がオフになる。アノード電源線 L 1 ( アノード電源電位 P V D D ) から、発光制御トランジスタ B C T 及び補正トランジスタ C C T を介して駆動トランジスタ D R T に電流が供給される。

#### 【 0 0 4 4 】

駆動トランジスタ D R T は、期間 t 5 までに設定されたゲートソース間の電圧に応じた電流を、発光素子 3 に供給する。発光素子 3 は、この電流に応じた輝度で発光する。このとき、発光素子 3 のアノードとカソードとの間の電圧は、駆動トランジスタ D R T を通して供給された電流値に応じた電圧となる。これにより、発光素子 3 のアノードの電位が上昇する。ここで、駆動トランジスタ D R T のゲートとソースとの間の電圧は、保持容量 C s によって保持される。このため、保持容量 C s のカップリングにより、発光素子 3 のアノードの電位上昇に伴って、駆動トランジスタ D R T のゲート電位も上昇する。

#### 【 0 0 4 5 】

実際には、駆動トランジスタ D R T のゲートには、保持容量 C s に加えて容量 C a d 等の附加容量が存在するので、アノードの電位上昇よりも、駆動トランジスタ D R T のゲート電位の上昇はわずかに小さくなる。ただし、この値は既知であるため、最終的な駆動トランジスタ D R T のゲートとソースとの間の電圧において、所望の電流値となるように、映像信号 V s i g の電位を決定すればよい。

#### 【 0 0 4 6 】

以上の動作を 1 行目から最終行まで完了すると、1 フレーム分の画像の表示が行われる。例えば、3 行目及び 4 行目に属する副画素 4 9 のリセット動作は、期間 t 3 と重なる期間に実行される。3 行目及び 4 行目に属する副画素 4 9 のオフセットキャンセル動作は、期間 t 3 から期間 t 5 と重なる期間に実行される。3 行目及び 4 行目に属する副画素 4 9 の映像信号書込動作は、期間 t 6 と重なる期間に行われる。以後、このような動作を繰り返して映像の表示が行われる。

10

20

30

40

50

**【0047】**

なお、上述した図3に示す画素回路P I Cの構成及び図4に示す動作例はあくまで一例であり、適宜変更することができる。例えば1つの副画素49での配線の数及びトランジスタの数は異なっていてもよい。また、画素回路P I Cはカレントミラー回路等の構成を採用することもできる。

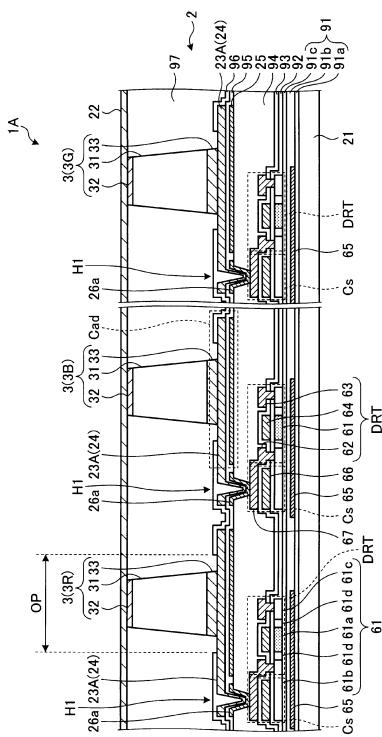

**【0048】**

次に、表示装置1の断面構成について説明する。図5は、図2のV-V'断面図である。図6は、図1のVI-VI'断面図である。図5に示すように、発光素子3は、アレイ基板2の上に設けられる。アレイ基板2は、基板21、アノード電極23、接続層24、対向電極25、接続電極26a、各種トランジスタ、各種配線及び各種絶縁膜を有する。

10

**【0049】**

基板21は絶縁基板であり、例えば、石英、無アルカリガラス等のガラス基板、又はポリイミド等の樹脂基板が用いられる。基板21として、可撓性を有する樹脂基板を用いた場合には、シートディスプレイとして表示装置1を構成することができる。また、基板21は、ポリイミドに限らず、他の樹脂材料を用いても良い。

**【0050】**

なお、本明細書において、基板21の表面に垂直な方向において、基板21から発光素子3に向かう方向を「上側」又は単に「上」とする。また、発光素子3から基板21に向かう方向を「下側」又は単に「下」とする。

20

**【0051】**

基板21の上にアンダーコート膜91が設けられる。アンダーコート膜91は、例えば、絶縁膜91a、91b、91cを有する3層積層構造である。絶縁膜91aはシリコン酸化膜であり、絶縁膜91bはシリコン窒化膜であり、絶縁膜91cはシリコン酸化膜である。下層の絶縁膜91aは、基板21とアンダーコート膜91との密着性向上のために設けられる。中層の絶縁膜91bは、外部からの水分及び不純物のブロック膜として設けられる。上層の絶縁膜91cは、絶縁膜91bのシリコン窒化膜中に含有する水素原子が半導体層61側に拡散しないようにするブロック膜として設けられる。

**【0052】**

アンダーコート膜91の構成は、図5に示すものに限定されない。例えば、アンダーコート膜91は、単層膜あるいは2層積層膜であってもよく、4層以上積層されていてもよい。また、基板21がガラス基板である場合、シリコン窒化膜は比較的密着性が良いため、基板21上に直接シリコン窒化膜を形成してもよい。

30

**【0053】**

遮光膜65は、絶縁膜91aの上に設けられる。遮光膜65は、半導体層61と基板21との間に設けられる。遮光膜65により、半導体層61のチャネル領域61aへの基板21側からの光の侵入を抑制することができる。あるいは、遮光膜65を導電性材料で形成して、所定の電位を与えることで、駆動トランジスタD R Tへのバックゲート効果を与えることができる。なお、遮光膜65は、基板21上に設けられ、遮光膜65を覆って絶縁膜91aが設けられていてもよい。

**【0054】**

駆動トランジスタD R Tは、アンダーコート膜91の上に設けられる。なお、図5では、複数のトランジスタのうち、駆動トランジスタD R Tを示しているが、画素回路P I Cに含まれる発光制御トランジスタB C T、初期化トランジスタI S T、補正トランジスタC C T、書込トランジスタS S T及び周辺領域G Aに設けられるリセットトランジスタR S Tも、駆動トランジスタD R Tと同様の積層構造を有する。

40

**【0055】**

駆動トランジスタD R Tは、半導体層61、ソース電極62、ドレイン電極63及びゲート電極64を有する。半導体層61は、アンダーコート膜91の上に設けられる。半導体層61は、例えば、ポリシリコンが用いられる。ただし、半導体層61は、これに限定されず、微結晶酸化物半導体、アモルファス酸化物半導体、低温ポリシリコン等であって

50

もよい。駆動トランジスタD R Tとして、n型T F Tのみ示しているが、p型T F Tを同時に形成しても良い。n型T F Tでは、半導体層6 1は、チャネル領域6 1 a、ソース領域6 1 b、ドレイン領域6 1 c及び低濃度不純物領域6 1 dを有する。低濃度不純物領域6 1 dは、チャネル領域6 1 aとソース領域6 1 bとの間に設けられ、また、チャネル領域6 1 aとドレイン領域6 1 cとの間に設けられる。

#### 【0056】

ゲート絶縁膜9 2は、半導体層6 1を覆ってアンダーコート膜9 1の上に設けられる。ゲート絶縁膜9 2は、例えばシリコン酸化膜である。ゲート電極6 4は、ゲート絶縁膜9 2の上に設けられる。また、ゲート電極6 4と同層に第1配線6 6が設けられる。ゲート電極6 4及び第1配線6 6は、例えば、モリブデンタングステン(MoW)が用いられる。図5に示す例では、駆動トランジスタD R Tは、ゲート電極6 4が半導体層6 1の上側に設けられたトップゲート構造である。ただし、これに限定されず、駆動トランジスタD R Tは、半導体層6 1の下側にゲート電極6 4が設けられたボトムゲート構造でもよく、半導体層6 1の上側及び下側の両方にゲート電極6 4が設けられたデュアルゲート構造でもよい。

10

#### 【0057】

層間絶縁膜9 3は、ゲート電極6 4を覆ってゲート絶縁膜9 2の上に設けられる。層間絶縁膜9 3は、例えば、シリコン窒化膜とシリコン酸化膜との積層構造を有する。ソース電極6 2及びドレイン電極6 3は、層間絶縁膜9 3の上に設けられる。ソース電極6 2は、ゲート絶縁膜9 2及び層間絶縁膜9 3に設けられたコンタクトホールを介して、ソース領域6 1 bに接続される。ドレイン電極6 3は、ゲート絶縁膜9 2及び層間絶縁膜9 3に設けられたコンタクトホールを介して、ドレイン領域6 1 cに接続される。ソース電極6 2には、引き回し配線となる第2配線6 7が接続される。ソース電極6 2、ドレイン電極6 3及び第2配線6 7は、例えば、チタン(Ti)、アルミニウム(Al)、チタン(Ti)の3層積層構造を採用することができる。

20

#### 【0058】

第2配線6 7の一部は、第1配線6 6と重なる領域に形成される。層間絶縁膜9 3を介して対向する第1配線6 6と第2配線6 7とで、保持容量C sが形成される。また、第1配線6 6は、半導体層6 1の一部と重なる領域に形成される。保持容量C sは、ゲート絶縁膜9 2を介して対向する半導体層6 1と第1配線6 6とで形成される容量も含む。

30

#### 【0059】

平坦化膜9 4は、駆動トランジスタD R T及び第2配線6 7を覆って層間絶縁膜9 3の上に設けられる。平坦化膜9 4としては感光性アクリル等の有機材料が用いられる。感光性アクリル等の有機材料は、CVD等により形成される無機絶縁材料に比べ、配線段差のカバレッジ性や、表面の平坦性に優れる。

#### 【0060】

平坦化膜9 4の上に、対向電極2 5、容量絶縁膜9 5、アノード電極2 3、接続層2 4、アノード電極絶縁膜9 6の順に積層される。対向電極2 5は、例えばITO(Indium Tin Oxide)等の透光性を有する導電性材料で構成される。対向電極2 5と同層に接続電極2 6 aが設けられる。接続電極2 6 aは、平坦化膜9 4に設けられたコンタクトホールH 1の内部を覆って設けられ、コンタクトホールH 1の底部で第2配線6 7と接続される。

40

#### 【0061】

容量絶縁膜9 5は、対向電極2 5及び接続電極2 6 aを覆って設けられ、コンタクトホールH 1と重なる領域に開口を有する。容量絶縁膜9 5は、例えば、シリコン窒化膜である。アノード電極2 3は、容量絶縁膜9 5を介して対向電極2 5と対向する。アノード電極2 3は、コンタクトホールH 1を介して接続電極2 6 a及び第2配線6 7と電気的に接続される。これにより、アノード電極2 3は、駆動トランジスタD R Tと電気的に接続される。アノード電極2 3は、モリブデン(Mo)、アルミニウム(Al)の積層構造をしている。ただし、これに限定されず、アノード電極2 3は、モリブデン、チタンの金属のいずれか1つ以上を含む材料であってもよい。又は、アノード電極2 3は、モリブデン、

50

チタンのいずれか 1 つ以上を含む合金、又は透光性導電材料であってもよい。

#### 【 0 0 6 2 】

容量絶縁膜 9 5 を介して対向するアノード電極 2 3 と対向電極 2 5 との間に容量 C ad が形成される。また、ITOで形成される対向電極 2 5 は、アノード電極 2 3 、接続層 2 4 を形成する工程において、第 2 配線 6 7 等の各種配線を保護するためのバリア膜としての機能も有する。ところで、アノード電極 2 3 のパターニング時、一部において対向電極 2 5 がエッティング環境にさらされるが、対向電極 2 5 の形成からアノード電極 2 3 の形成までの間に行われるアニール処理によって、対向電極 2 5 はアノード電極 2 3 のエッティングに対し十分な耐性を有する。

#### 【 0 0 6 3 】

接続層 2 4 は、アノード電極 2 3 の上に設けられる。接続層 2 4 は、複数の導電性ナノ粒子 5 1 を含む。接続層 2 4 は、複数の導電性ナノ粒子 5 1 を含む導電性インクや導電性ペーストを用いてインクジェット印刷やスクリーン印刷等によりパターニングすることができる。接続層 2 4 のパターニング方法については、後述する。

#### 【 0 0 6 4 】

アノード電極絶縁膜 9 6 は、アノード電極 2 3 及び接続層 2 4 を覆って設けられる。アノード電極絶縁膜 9 6 は、例えばシリコン窒化膜である。アノード電極絶縁膜 9 6 は、接続層 2 4 の周縁部を覆っており、隣り合う副画素 4 9 のアノード電極 2 3 を絶縁する。

#### 【 0 0 6 5 】

アノード電極絶縁膜 9 6 は、接続層 2 4 と重なる位置に、発光素子 3 を実装するための開口 O P を有する。開口 O P の大きさは、発光素子 3 の実装工程における実装ズレ量等を考慮し、発光素子 3 よりも大きい面積の開口とする。すなわち、基板 2 1 に垂直な方向からの平面視で、接続層 2 4 の面積は、発光素子 3 の面積よりも大きい。また、基板 2 1 に垂直な方向からの平面視で、アノード電極 2 3 の面積は、発光素子 3 の面積よりも大きい。さらに、発光素子 3 は、少なくとも 2 つの端子（アノード端子 3 3 及びカソード端子 3 2 ）を有し、基板 2 1 に垂直な方向からの平面視で、アノード電極 2 3 の面積は、少なくとも 2 つの端子（アノード端子 3 3 及びカソード端子 3 2 ）の一方の面積よりも大きい。例えば発光素子 3 が平面視で、 $10 \mu m \times 10 \mu m$  程度の実装面積である場合、開口 O P の面積として、 $20 \mu m \times 20 \mu m$  程度は確保されることが好ましい。

#### 【 0 0 6 6 】

発光素子 3 R、3 G、3 B は、それぞれに対応するアノード電極 2 3 に接続層 2 4 を介して実装される。つまり、基板 2 1 に垂直な方向において、接続層 2 4 は、アノード電極 2 3 と発光素子 3 との間に設けられる。発光素子 3 は、半導体層 3 1 、カソード端子 3 2 及びアノード端子 3 3 を有する。半導体層 3 1 は、n 型クラッド層、活性層及び p 型クラッド層が積層された構成を採用することができる。

#### 【 0 0 6 7 】

半導体層 3 1 は、例えば、窒化ガリウム (GaN) 、アルミニウムインジウム燐 (AlInP) 等の化合物半導体が用いられる。半導体層 3 1 は、発光素子 3 R、3 G、3 B ごとに異なる材料が用いられてもよい。また、活性層として、高効率化のために数原子層からなる井戸層と障壁層とを周期的に積層させた多重量子井戸構造 (MQW 構造) が採用されてもよい。また、発光素子 3 として、半導体基板上に半導体層 3 1 が形成された構成でもよい。あるいは、発光素子 3 単体がアレイ基板 2 に実装される構成に限定されず、発光素子 3 を含む LED チップがアレイ基板 2 に実装される構成であってもよい。LED チップは、例えば、発光素子基板と、発光素子基板に設けられた発光素子 3 と、発光素子基板に設けられ、発光素子 3 を駆動する回路素子群とを有し、発光素子基板、発光素子 3 及び回路素子群が 1 チップに集積された構成が挙げられる。LED チップ上には、発光素子 3 は複数設けられても良く、かつそれらは互いに異なる発光色を呈する物であっても良い。

#### 【 0 0 6 8 】

発光素子 3 は、アノード端子 3 3 が接続層 2 4 に接するように実装される。これにより、アノード電極 2 3 は、接続層 2 4 を介して発光素子 3 と電気的に接続される。複数の発

10

20

30

40

50

光素子 3 の間に素子絶縁膜 9 7 が設けられる。素子絶縁膜 9 7 は樹脂材料で形成される。素子絶縁膜 9 7 は、発光素子 3 の側面を覆っており、発光素子 3 のカソード端子 3 2 は、素子絶縁膜 9 7 から露出する。素子絶縁膜 9 7 の上面と、カソード端子 3 2 の上面とが同一面を形成するように、素子絶縁膜 9 7 は平坦に形成される。ただし、素子絶縁膜 9 7 の上面の位置は、カソード端子 3 2 の上面の位置と異なっていてもよい。

#### 【 0 0 6 9 】

カソード電極 2 2 は、素子絶縁膜 9 7 の上面と、カソード端子 3 2 の上面とに亘って設けられる。カソード電極 2 2 は、例えば I T O 等の透光性を有する導電性材料が用いられる。これにより、発光素子 3 からの出射光を効率よく外部に取り出すことができる。カソード電極 2 2 は、表示領域 A A に実装された複数の発光素子 3 のカソード端子 3 2 と電気的に接続される。10

#### 【 0 0 7 0 】

図 6 に示すように、カソード電極 2 2 は、表示領域 A A の外側に設けられた陰極コンタクト部（コンタクトホール H 2 ）で、アレイ基板 2 側に設けられたカソード配線 6 0 と接続される。なお、図 6 では、周辺領域 G A の断面構成と、表示領域 A A の断面構成との対応関係を分かりやすくするために、周辺領域 G A と表示領域 A A とを併せて示している。

#### 【 0 0 7 1 】

図 6 に示すように、表示装置 1 は、周辺領域 G A において、端子部 2 7 、折曲領域 F A 及び陰極コンタクト部（コンタクトホール H 2 ）を有する。端子部 2 7 は、駆動 I C 2 1 0 又はフレキシブルプリント基板等の配線基板と接続される端子である。折曲領域 F A は、アレイ基板 2 のうち、端子部 2 7 側の周辺領域 G A を折り曲げるため領域である。なお、折曲領域 F A が設けられる場合には、基板 2 1 として可撓性を有する樹脂材料が用いられる。20

#### 【 0 0 7 2 】

具体的には、アンダーコート膜 9 1 、ゲート絶縁膜 9 2 及び層間絶縁膜 9 3 は、表示領域 A A から周辺領域 G A に亘って、基板 2 1 の端部まで設けられている。アンダーコート膜 9 1 、ゲート絶縁膜 9 2 及び層間絶縁膜 9 3 は、折曲領域 F A で除去される。アンダーコート膜 9 1 、ゲート絶縁膜 9 2 及び層間絶縁膜 9 3 は、折曲領域 F A において、エッチングにより除去される。この場合、ポリイミド等の樹脂材料で構成される基板 2 1 の表面が一部エッチングにより浸食されて凹部が形成される場合がある。30

#### 【 0 0 7 3 】

カソード配線 6 0 は、層間絶縁膜 9 3 の上に設けられる。つまり、カソード配線 6 0 は、ソース電極 6 2 、ドレイン電極 6 3 及び第 2 配線 6 7 と同層に設けられ、同じ材料で形成される。カソード配線 6 0 は、折曲領域 F A に跨がって設けられ、アンダーコート膜 9 1 、ゲート絶縁膜 9 2 及び層間絶縁膜 9 3 と、基板 2 1 とで形成される段差に沿って設けられる。また、カソード配線 6 0 は、折曲領域 F A において基板 2 1 の上に設けられ、折曲領域 F A と基板 2 1 の端部との間ににおいて、層間絶縁膜 9 3 の上に設けられる。

#### 【 0 0 7 4 】

平坦化膜 9 4 は、周辺領域 G A の、折曲領域 F A 及び折曲領域 F A と基板 2 1 の端部との間の領域で除去される。平坦化膜 9 4 には、折曲領域 F A と表示領域 A A との間の領域にコンタクトホール H 2 が設けられる。カソード配線 6 0 はコンタクトホール H 2 の底面に露出する、また、素子絶縁膜 9 7 の厚さは、表示領域 A A の周縁部から周辺領域 G A に向かって、薄くなるように設けられる。カソード電極 2 2 は、コンタクトホール H 2 の内部に設けられた接続電極 2 6 b を介して、カソード配線 6 0 と電気的に接続される。接続電極 2 6 b は、対向電極 2 5 及び接続電極 2 6 a と同層に設けられ、対向電極 2 5 及び接続電極 2 6 a と同じ材料で形成される。40

#### 【 0 0 7 5 】

また、端子部 2 7 は、折曲領域 F A と基板 2 1 の端部との間の領域で、カソード配線 6 0 の上に設けられる。容量絶縁膜 9 5 は、端子部 2 7 を覆って設けられ、端子部 2 7 と重なる領域に開口を有する。

**【 0 0 7 6 】**

以上のように、表示素子として発光素子3を用いた表示装置1が構成される。なお、表示装置1は、必要に応じて、カソード電極22の上側に、カバーガラスやタッチパネル等を設けてもよい。また、この場合、表示装置1とカバーガラス等の部材との間に、樹脂などを用いた充填材が設けられていてもよい。また、表示装置1において、発光素子3の上部でカソード電極22に接続されるフェースアップ構造に限定されず、発光素子3の下部が、アノード電極23及びカソード電極22に接続される、いわゆるフェースダウン構造であってもよい。

**【 0 0 7 7 】**

次に、発光素子3とアノード電極23との接続方法について説明する。図7は、発光素子3とアノード電極との接続工程を説明するための説明図である。なお、図7では、発光素子3のアノード端子33側の一部のみ示している。

10

**【 0 0 7 8 】**

図7に示すように、アノード電極23の上に塗布膜50が形成され、塗布膜50上に発光素子3のアノード端子33が接する(ステップST1)。塗布膜50は、複数の導電性ナノ粒子51が溶剤53中に分散された導電性ペーストや導電性インクを用いて、印刷形成される。塗布膜50は、スクリーン印刷、フレキソ印刷又はインクジェット印刷により形成することができる。

**【 0 0 7 9 】**

導電性ナノ粒子51の表面には、有機樹脂材料である被膜52が形成されている。このため、アノード電極23とアノード端子33とは、被膜52により非導通状態となっている。

20

**【 0 0 8 0 】**

次に、塗布膜50に加熱処理を施することで、被膜52を分解、除去する(ステップST2)。これにより、複数の導電性ナノ粒子51の表面が接する。

**【 0 0 8 1 】**

さらに加熱を行うことで、導電性ナノ粒子51が焼結して、接続層24が形成される(ステップST3)。これにより、アノード電極23とアノード端子33とは、接続層24を介して電気的に接続される。

30

**【 0 0 8 2 】**

導電性ナノ粒子51は、例えば、銀(Ag)又は銀合金が用いられる。導電性ナノ粒子51は、それぞれの粒径がナノオーダー(例えば1nm以上、30nm以下程度)であり、高い表面エネルギーを有する。このため、導電性ナノ粒子51を焼結する際には、例えば、はんだ材料を用いたリフロー工程や、通常の銀粉末(例えば、粒径1μm以上)を含む導電ペーストの焼結に比べて低い温度で焼結することが可能である。したがって、発光素子3の接続工程の冷却時に、発光素子3の収縮量と接続層24の収縮量との差を抑制することができる。これにより、冷却後に、発光素子3とアノード電極23との接続部分における残留応力を抑制することができる。

**【 0 0 8 3 】**

また、図7に示すように、焼結後の接続層24の内部には、複数の導電性ナノ粒子51の間に微小な空隙SPが複数形成される。このため、接続層24に発生する残留応力を抑制することができる。この結果、表示装置1は、アレイ基板2と発光素子3との接続信頼性を向上させることができる。また、表示装置1が曲面ディスプレイとして構成される場合、アレイ基板2は曲面を有する。この場合であっても、接続層24は、発光素子3とアノード電極23との接続部分に発生する応力を抑制して、発光素子3とアレイ基板2との接続信頼性を向上させることができる。

40

**【 0 0 8 4 】**

なお、接続層24の材料として用いられる導電性ナノ粒子51の粒径は、例えば、レーザ回折散乱法により測定することができる。上述したように、接続層24は、スクリーン印刷、フレキソ印刷又はインクジェット印刷等の印刷方法によりパターンングすることができる。

50

できる。ただし、これに限定されず、接続層 24 のパターニングには種々の方法を適用することができる。

#### 【0085】

図 8 は、接続層のパターニング方法を説明するための説明図である。図 8 に示すように、成膜装置 100 は、エアロゾル発生装置 101 と、配管 102 と、ノズル 103 と、XYステージ 104 とを有する。成膜装置 100 は、エアロゾルデポジション法により接続層 24 を形成することができる。エアロゾル発生装置 101 には、原料となる導電性ナノ粒子 51 が投入される。導電性ナノ粒子 51 は、エアロゾル発生装置 101 内で攪拌、混合されてエアロゾル化される。エアロゾル粒子は、配管 102 を通して高密度化されてノズル 103 に搬送される。ノズル 103 に搬送されたエアロゾル粒子は、キャリアガス G によって加速される。これにより、ノズル 103 の開口からエアロゾルビーム 55 がアレイ基板 2 に向かって射出される。

10

#### 【0086】

エアロゾル粒子がアレイ基板 2 のアノード電極 23 に衝突することにより、エアロゾル粒子とアノード電極 23 とが結合され、かつ、エアロゾル粒子間の結合が実現される。これにより、成膜装置 100 は、アノード電極 23 上に接続層 24 を形成することができる。また、成膜装置 100 は、XYステージ 104 を駆動することにより、所定のパターンで接続層 24 を形成することができる。このように、成膜装置 100 は、エアロゾル化された導電性ナノ粒子 51 により直接、アノード電極 23 上に接続層 24 を形成することができる。

20

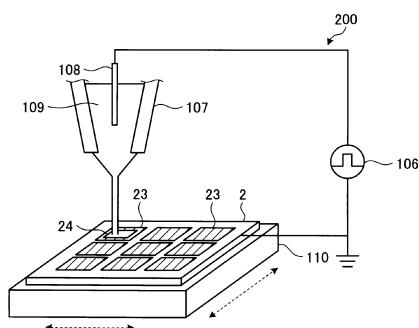

#### 【0087】

図 9 は、接続層のパターニング方法の第 1 変形例を説明するための説明図である。成膜装置 200 は、電源 106 と、ノズル 107 と、電極 108 と、XYステージ 110 とを有する。成膜装置 200 は、静電塗布法により接続層 24 を形成することができる。ノズル 107 内に、導電性ナノ粒子 51 が分散された溶液 109 が投入される。電極 108 は、ノズル 107 内に設けられて溶液 109 と接する。電源 106 は、アレイ基板 2 とノズル 107 内の溶液 109との間に正極性の高電圧を印加する。

#### 【0088】

ノズル 107 の先端部の溶液 109 にはプラスの電荷が生じ、アレイ基板 2 側にはマイナスの電荷が生じる。溶液 109 とアレイ基板 2 との間に発生する静電力により、溶液 109 の一部がアレイ基板 2 に向かって射出される。溶液 109 の導電性ナノ粒子 51 は、静電力によりアノード電極 23 上に引き寄せられて、接続層 24 が形成される。成膜装置 200 は、電源 106 が印加する電圧を変更することで、ノズル 107 から射出される溶液 109 の量や、形状等を調整することができる。これにより、成膜装置 200 は、微細な形状に接続層 24 をパターニングすることができる。

30

#### 【0089】

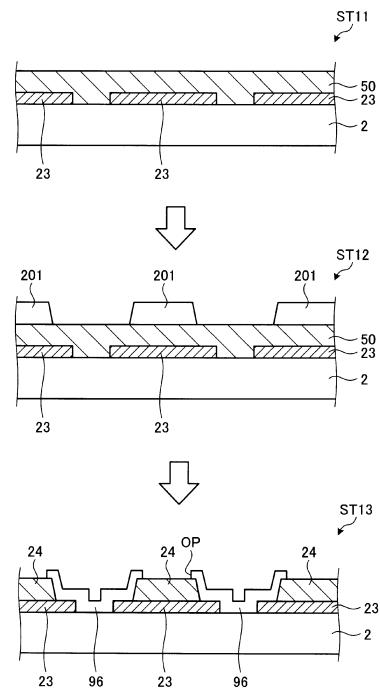

図 10 は、接続層のパターニング方法の第 2 変形例を説明するための説明図である。第 2 変形例において、接続層 24 は、フォトリソグラフィ技術により形成される。図 10 に示すように、成膜装置は、アレイ基板 2 の全面に、導電性ナノ粒子 51 を含む塗布膜 50 を塗布形成する（ステップ ST11）。塗布膜 50 は、複数のアノード電極 23 を覆って形成される。塗布膜 50 は、加熱処理が施されて、導電性ナノ粒子 51 の表面を覆う被膜 52 及び溶剤 53（図 7 参照）が除去される。この場合、複数の導電性ナノ粒子 51 の焼結温度よりも低い温度で加熱処理が施される。これにより、アレイ基板 2 の上に複数の導電性ナノ粒子 51 が堆積された状態となる。

40

#### 【0090】

次に、成膜装置は、アノード電極 23 と重なる領域、すなわち、接続層 24 が設けられる予定の領域において、複数の導電性ナノ粒子 51 の上にレジスト 201 を形成する（ステップ ST12）。

#### 【0091】

次に、成膜装置は、レジスト 201 と重ならない領域の複数の導電性ナノ粒子 51 を、

50

エッティングにより除去する（ステップST13）。ステップST12の状態では、複数の導電性ナノ粒子51は焼結されていないので、複数の導電性ナノ粒子51はアノード電極23に比べてエッティングレートが高い。これにより、アノード電極23の上に、複数の導電性ナノ粒子51を含む接続層24が形成される。その後、接続層24及びアノード電極23を覆ってアノード電極絶縁膜96が形成される。アノード電極絶縁膜96には、接続層24と重なる領域に開口OPが形成される。

#### 【0092】

以上のように、第2変形例では、フォトリソグラフィ技術により接続層24が形成されるので、アレイ基板2の製造工程と同じ工程で接続層24を形成することができる。このため、表示装置1は、製造コストを抑制することができる。

10

#### 【0093】

##### (第2実施形態)

図11は、第2実施形態に係る表示装置を示す断面図である。なお、以下の説明においては、上述した実施形態で説明したものと同じ構成要素には同一の符号を付して重複する説明は省略する。

#### 【0094】

第2実施形態の表示装置1Aは、第1実施形態に対して、アノード電極23Aが複数の導電性ナノ粒子51により形成されている構成が異なる。発光素子3のアノード端子33は、アノード電極23Aの上に接続される。言い換えると、アノード電極23Aは、接続層24の機能を兼ねる。

20

#### 【0095】

第2実施形態においても、アノード電極23Aが複数の導電性ナノ粒子51を含んでいるので、アノード電極23Aと発光素子3とを接続する際に、低い温度で導電性ナノ粒子51を焼結することができる。これにより、発光素子3とアノード電極23Aとの接続部分における残留応力を抑制することができる。また、アノード電極23Aが接続層24を兼ねるので、表示装置1Aは、第1実施形態に比べてアレイ基板2の積層数を少なくすることができる。

#### 【0096】

また、第2実施形態においても、アノード電極23Aと発光素子3との接続方法及びアノード電極23Aのパターニング方法は、上述した第1実施形態及び各変形例と同様の方法を採用することができる。

30

#### 【0097】

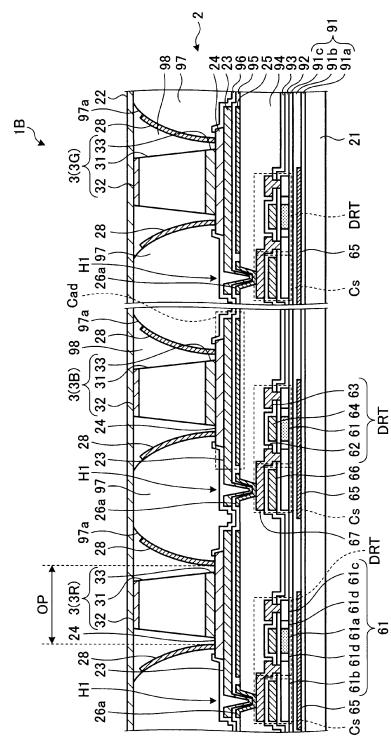

##### (第3実施形態)

図12は、第3実施形態に係る表示装置を示す断面図である。第3実施形態の表示装置1Bは、上述した実施形態に対して、反射層28を有する構成が異なる。図12に示すように、反射層28は、発光素子3の側面と対向して設けられ、複数の導電性ナノ粒子51を含む。

#### 【0098】

より具体的には、素子絶縁膜97には、発光素子3と重なる領域に貫通孔97aが設けられる。発光素子3は、貫通孔97aの内壁に囲まれて接続層24の上に配置される。反射層28は、貫通孔97aの内壁に沿って設けられる。反射層28の下端は、接続層24を介してアノード電極23と電気的に接続される。また、反射層28の上端は、カソード電極22と離隔している。本実施形態では、発光素子3を実装するための開口OPの面積は、反射層28の下端で囲まれた領域となる。

40

#### 【0099】

貫通孔97aの内部には、反射層絶縁膜98が設けられる。反射層絶縁膜98は、発光素子3の側面を覆うとともに、反射層28を覆う。カソード電極22は、素子絶縁膜97、反射層絶縁膜98及び発光素子3を覆って設けられ、カソード端子32と電気的に接続される。反射層絶縁膜98は、反射層28の上端とカソード電極22との間に設けられる。

50

**【0100】**

反射層28は、光沢を有する複数の導電性ナノ粒子51で形成される。また、反射層28は、基板21の法線方向に対して傾斜して設けられる。これにより、反射層28は、発光素子3の出射光のうち横方向（側面方向）に出射された光を反射して、基板21の法線方向に沿った方向に反射光を出射する。これにより、表示装置1Bは、発光素子3からの光の取り出し効率を向上させることができる。

**【0101】**

なお、反射層28は、発光素子3の周囲を囲んで設けられていてもよいし、発光素子3の側面の一部と対向して設けられていてもよい。また、表示装置1Bにおいて、第2実施形態の構成を適用することも可能である。

10

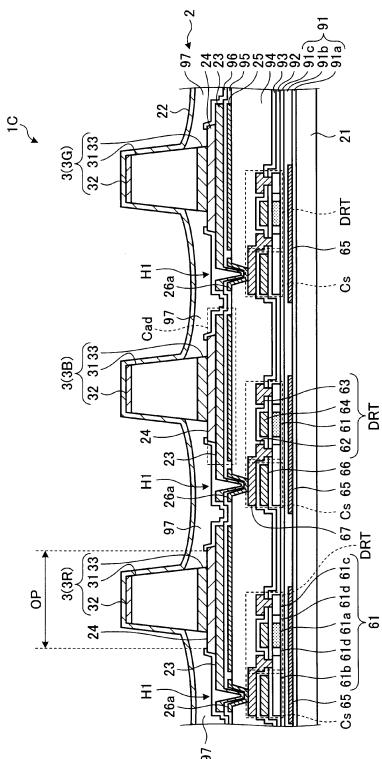

**【0102】****(第4実施形態)**

図13は、第4実施形態に係る表示装置を示す断面図である。上述した第1実施形態から第3実施形態では、素子絶縁膜97の上面と、カソード端子32の上面とが同一面を形成するように、素子絶縁膜97が設けられているがこれに限定されない。図13に示すように、第4実施形態の表示装置1Cにおいて、素子絶縁膜97の高さは、発光素子3の高さよりも低い。

**【0103】**

素子絶縁膜97は、アノード電極23及び接続層24を覆う。また、素子絶縁膜97は、発光素子3の側面の一部を覆って設けられ、少なくともアノード端子33の側面を覆う。カソード電極22は、素子絶縁膜97の上面、発光素子3のカソード端子32及び発光素子3の側面の一部を覆う。

20

**【0104】**

第4実施形態においても、素子絶縁膜97は、隣り合う副画素49において、アノード電極23の絶縁を確保することができる。また、素子絶縁膜97は、発光素子3とアノード電極23との接続強度を確保することができる。また、表示装置1Cにおいて、第2実施形態の構成を適用することも可能である。

30

**【0105】**

これまでの説明において、アノード端子33、カソード端子32として表記してきた部分においては、発光素子3の接続方向、及び電圧の印加方向によっては明細書中の記載に限定するものではなく、逆転していても良い。また、図5、図11、図12等においては、発光素子3の一方の電極が下側に、他方の電極が上側にある構成を示しているが、その両方が下側、つまりアレイ基板2に対面する側に有る構成であっても良い。

**【0106】**

以上、本発明の好適な実施の形態を説明したが、本発明はこのような実施の形態に限定されるものではない。実施の形態で開示された内容はあくまで一例にすぎず、本発明の趣旨を逸脱しない範囲で種々の変更が可能である。本発明の趣旨を逸脱しない範囲で行われた適宜の変更についても、当然に本発明の技術的範囲に属する。上述した各実施形態及び各変形例の要旨を逸脱しない範囲で、構成要素の種々の省略、置換及び変更のうち少なくとも1つを行うことができる。

40

**【符号の説明】****【0107】**

- 1、1A、1B、1C 表示装置

- 2 アレイ基板

- 3、3R、3G、3B 発光素子

- 12 駆動回路

- 21 基板

- 22 カソード電極

- 23、23A アノード電極

- 24 接続層

50

2 7 端子部

2 8 反射層

3 1 半導体層

3 2 カソード端子

3 3 アノード端子

4 9 副画素

5 1 導電性ナノ粒子

6 0 カソード配線

1 0 0、2 0 0 成膜装置

2 1 0 駆動 I C

D R T 駆動トランジスタ

B C T 発光制御トランジスタ

I S T 初期化トランジスタ

C C T 補正トランジスタ

S S T 書込トランジスタ

P i x 画素

R S T リセットトランジスタ

B G 発光制御走査線

S G 書込制御走査線

R G リセット制御走査線

I G 初期化制御走査線

C G 補正制御走査線

## 【図面】

## 【図 1】

## 【図 2】

10

20

30

40

50

【図3】

【 四 4 】

【 四 5 】

〔 図 6 〕

10

20

30

40

50

【図 7】

【図 8】

10

20

【図 9】

【図 10】

30

40

50

【 図 1 1 】

【図12】

10

20

【図13】

30

40

50

---

フロントページの続き

(56)参考文献

特表2016-512347(JP,A)

国際公開第2011/114747(WO,A1)

特開2011-021255(JP,A)

特開2018-182282(JP,A)

特表2018-523848(JP,A)

特表2016-503958(JP,A)

米国特許出願公開第2018/0076182(US,A1)

特開2018-206532(JP,A)

特開2003-017149(JP,A)

米国特許出願公開第2017/0187976(US,A1)

(58)調査した分野 (Int.Cl., DB名)

G02F1/1343-1/1345

1/135-1/1368

G09F9/00-9/46

H01B1/00-1/24

5/00-5/16

H01L21/447-21/449

21/60-21/607

23/12-23/15

25/00-25/07

25/10-25/11

25/16-25/18

33/00-33/64