(19)

OFICINA ESPAÑOLA DE

PATENTES Y MARCAS

ESPAÑA

(11) Número de publicación: **3 014 635**

(21) Número de solicitud: 202330859

(51) Int. Cl.:

**C09D 11/30** (2014.01)

(12)

## SOLICITUD DE PATENTE

A1

(22) Fecha de presentación:

**18.10.2023**

(43) Fecha de publicación de la solicitud:

**23.04.2025**

(71) Solicitantes:

**CONSEJO SUPERIOR DE INVESTIGACIONES

CIENTÍFICAS (CSIC) (100.00%)

C/ Serrano, 117

28006 Madrid (Madrid) ES**

(72) Inventor/es:

**PLAZA PLAZA, José Antonio y

AGUSIL ANTONOFF, Juan Pablo**

(74) Agente/Representante:

**PONS ARIÑO, Ángel**

(54) Título: **SUSPENSIÓN DE CHIPS EN TINTAS, PINTURAS O BARNICES, PROCEDIMIENTO DE OBTENCIÓN Y USO PARA TRANSFERIR LOS CHIPS A SUPERFICIES COMPLEJAS MEDIANTE DISPOSITIVOS DE ESCRITURA, IMPRESIÓN O PINTURA**

(57) Resumen:

Suspensión de chips en tintas, pinturas o barnices, procedimiento de obtención y uso para transferir los chips a superficies complejas mediante dispositivos de escritura, impresión o pintura.

La presente invención describe una suspensión de chips susceptible de ser aplicada directamente sobre superficies espacial y geométricamente complejas para dotar a estas superficies con dichos chips mediante dispositivos de escritura, pintura o impresión y a su procedimiento de obtención. Además, la presente invención se refiere al uso de la suspensión para la decoración, el marcaje, la anti-falsificación o antifraude, la codificación, como sensores, como actuadores, y para la fabricación de dispositivos electrónicos y al uso de la suspensión para la determinación de las dimensiones de los canales de un dispositivo de escritura, pintura o impresión.

**DESCRIPCIÓN**

**SUSPENSIÓN DE CHIPS EN TINTAS, PINTURAS O BARNICES, PROCEDIMIENTO**

**DE OBTENCIÓN Y USO PARA TRANSFERIR LOS CHIPS A SUPERFICIES**

5       **COMPLEJAS MEDIANTE DISPOSITIVOS DE ESCRITURA, IMPRESIÓN O

PINTURA**

La presente invención describe una suspensión de chips susceptible de ser aplicada directamente sobre superficies espacial y geométricamente complejas para dotar a 10 estas superficies con dichos chips mediante dispositivos de escritura, pintura o impresión y a su procedimiento de obtención. Además, la presente invención se refiere al uso de la suspensión para la decoración, el marcaje, la anti-falsificación o antifraude, la codificación, como sensores, como actuadores, y para la fabricación de dispositivos 15 electrónicos y al uso de la suspensión para la determinación de las dimensiones de los canales de un dispositivo de escritura, pintura o impresión.

**Estado de la técnica**

Actualmente hay necesidad de que los dispositivos de la industria electrónica en 20 general, incluyendo micro y nanosistemas (MEMS, NEMS), sean omnipresentes. La electrónica tradicional, que produce chips en el orden de los milímetros o centímetros, no puede suprir esta necesidad cuando se trata de poner estos chips en superficies 3D o no planares ya que están limitados por su tamaño y rigidez. Recientemente la electrónica impresa, y en especial la electrónica flexible, permiten solucionar en parte 25 esta problemática. Pero estas tecnologías están limitadas en funcionalidad, control dimensiones y versatilidad, si se las compara con las tecnologías microelectrónicas. Además, y dado su tamaño en orden de milímetros o centímetros, también están limitados en la colocación de estos dispositivos en superficies 3D complejas o con radios 30 de curvaturas por debajo del milímetro. Por ello, lo ideal sería poder fabricar estos dispositivos con tecnologías microelectrónicas o de fabricación de micro y nanosistemas que presentan un mayor desarrollo y versatilidad para poder colocar estos dispositivos en cualquier superficie.

El cubrir superficies 3D complejas (ej. formadas por microfibra como papel, telas... con 35 topologías complicadas con radios de curvatura pequeños o bordes abruptos por debajo

- del milímetro) con chips a modo de motivos decorativos, códigos, sensores, electrónica, chips de test, entre otros, conlleva una serie de requerimientos tales como la necesidad de utilizar un equipo que sirva para todos los tipos de geometrías y materiales, la necesidad de adaptar dicho equipo a la superficie, la necesidad de que dicho equipo

- 5 sea compatible para cada dispositivo, la necesidad de que el equipo y el dispositivo sea compatible con las características del material, o la necesidad de poder colocar múltiples dispositivos a la vez y no tener que realizar una operación de colocación del chip por cada superficie que se quiere aplicar.

- 10 Bajo estas circunstancias, es necesario el desarrollo de nuevas técnicas de colocación de estos dispositivos en superficies que superen estas limitaciones en cuanto a la adaptabilidad, facilidad, y rapidez de realización de la colocación de los dispositivos en prácticamente cualquier objeto o superficie.

- 15 Además, en el campo particular de la identificación de objetos y superficies, actualmente hay necesidad de poder identificar correctamente diferentes superficies y objetos, tales como por ejemplo documentos o billetes, de forma rápida, automatizada y segura. Para ello, existen diferentes opciones como por ejemplo diferentes tipos de marcas a aplicar sobre esos objetos tales como billetes, como son por ejemplo las marcas de agua que

- 20 inequívocamente identifican los billetes como veraces (ver por ejemplo el artículo "Magnetically responsive photonic watermarks on banknotes" de Haibo Hu et al; *J. Mater. Chem. C*, 2014, 2, 3695-3702)).

- No obstante, este tipo de marcaje de los objetos tales como billetes para su verificación

- 25 rápida y segura, conlleva una serie de limitaciones tales como la necesidad de utilizar un equipo de marcaje que marque cada uno de los billetes, la necesidad de adaptar dicho equipo a la superficie o billete específico que se quiere marcar, la necesidad de que la marca sea compatible con las características del material del billete para su aplicación sobre este, la necesidad de adaptar el tipo de marcaje en función de las

- 30 características del material o superficie a marcar, o el hecho de tener que realizar una operación de marcaje por cada marca individual que se quiere aplicar sobre el billete.

- Bajo estas circunstancias, es necesario el desarrollo de nuevas técnicas de marcaje de superficies que superen estas limitaciones en cuanto a la adaptabilidad, facilidad, y

rapidez de realización de los marcajes de dichos objetos o superficies tales como billetes.

### Descripción de la invención

5

La presente invención describe una suspensión de chips susceptible de ser aplicada directamente sobre superficies espacial y geométricamente complejas mediante dispositivos de escritura, pintura o impresión con el objetivo de escribir, dibujar, pintar, o imprimir dichos chips y por tanto dotar a estas superficies con dichos microchips como 10 dispositivos de electrónica o microelectrónica, o como pueden ser sensores y actuadores. Otro objetivo de escribir, dibujar, pintar o imprimir chips en superficies es el de marcar superficies de textiles, papel, cartón, cerámicas, metálicas, billetes, etc. para incluir motivos decorativos, o para codificarlas, identificarlas, calibrarlas, etc.

15 A modo de ejemplo no limitativo, la suspensión de la presente invención sería susceptible de ser aplicada como:

- Suspensión decorativa: donde los chips tienen formas o motivos decorativos a escala micrométrica, por ejemplo, nombres de personas, pequeñas estructuras representadas (emoticonos, símbolos, letras, números, bocetos, ...). Siendo de interés 20 en la industria papelera para: bolígrafos, pinturas óleo, acrílico, acuarela, impresoras, etc.

- Suspensiones para marcas: donde los chips tienen forma de logos (logos de empresas, ciudades, etc.) siendo de interés en la industria del *merchandising*, para 25 propaganda, para identidades corporativas, etc.)

- Suspensiones antifraude o antifalsificación: para escribir, pintar o imprimir y trasladar así los chips a superficies a modo de códigos geométricos, o códigos electromagnéticos como los tags (bobinas), o a modo de códigos ópticos con 30 fluorescencia, o a modo de puntos cuánticos (quantum dots) siendo de interés en las industrias relacionadas con la protección de documentos, firmas personales, billetes, obras de arte, cuadros, artículos de colección, artículos personales de valor, autenticación de marcas, medicamentos, ropa, etc.

- Electrónica en suspensión: donde los chips están dotados de electrónica o con propiedades mecánicas, electromagnéticas, térmicas, (bio)químicas útiles para la industria electrónica en general.

5 Además, la presente invención se refiere al uso de la suspensión para la determinación de las dimensiones de los canales de un dispositivo de escritura, pintura o impresión.

Por tanto, un primer aspecto de la invención se refiere a una suspensión caracterizada por que comprende:

- 10           ○ **una fase sólida que comprende** chips seleccionados de entre materiales semiconductores, óxidos o nitruros aislantes o semiconductores, metales, materiales magnéticos, un polímero, una fotoresina, o cualquiera de sus combinaciones; donde los materiales semiconductores se seleccionan de entre silicio (Si), silicio amorfo, silicio monocrystalino, polisilicio, germanio (Ge), arseniuro de galio (GaAs); donde los óxidos o nitruros aislantes o semiconductores se seleccionan de entre óxido de silicio, óxido de aluminio, nitruro de aluminio o nitruro de silicio; donde los metales se seleccionan de entre aluminio, oro, platino o cobre; donde los materiales magnéticos se seleccionan de entre Co, Ni, o NiCo; donde el polímero se selecciona de entre polidimetilsiloxano (PDMS), polimetilfenilsiloxano y polidifenilsiloxano; y donde el fotoresina se selecciona de entre SU-8, SU-8 2000, SU-8 3000, SU-8 GLM2060, SU-8 GLM3060, SU-8 GMC10xx, SU-8 GMJB10XX, SU-8 GM10XX; o cualquiera de sus combinaciones;

- 15           donde los chips presentan un tamaño de entre 1 – 250 µm en su eje X (ancho), 1 – 250 µm en su eje Y (largo), y 10 nm – 50 µm en su eje Z (alto o espesor), dicho tamaño determinado por medidas de microscopía óptica, confocal, atómica o de barrido de electrones, o por medidas de *focused ion beam* (FIB o haz de iones focalizado en español), perfilómetros o elipsómetros, y

- 20           opcionalmente al menos una superficie planar de dichos chips está funcionalizada por al menos un compuesto seleccionado de entre moléculas, biomoléculas, nanopartículas, o cualquiera de sus combinaciones;

- 25           ○ una fase continua liquida o semilíquida como medio de suspensión de los chips seleccionado de entre tintas, pinturas o barnices;

- 30           y donde el porcentaje en peso de la fase sólida es de entre 0,000001-60% respecto al peso total de la suspensión.

Por "suspensión" se entiende en la presente invención a una mezcla heterogénea formada por un sólido no soluble (fase sólida) que comprende los chips descritos previamente y que se dispersan en un medio líquido o semilíquido (fase continua líquida o semilíquida) que se selecciona entre tintas, pinturas o barnices.

5

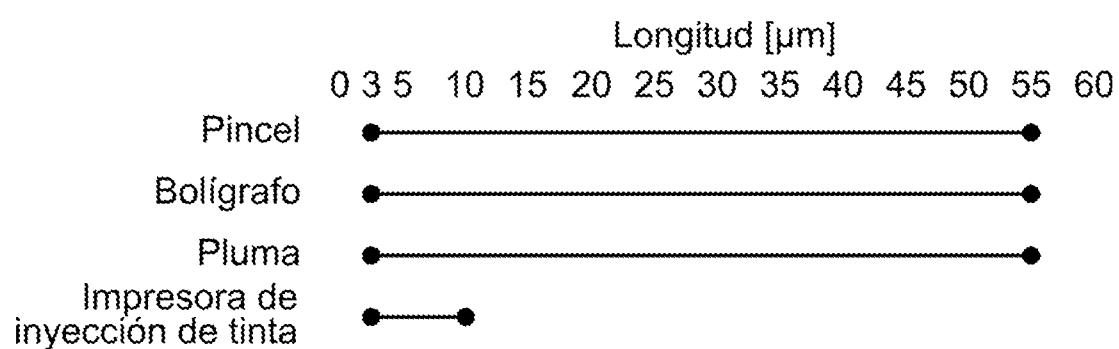

Los chips de la invención presentan tamaños micrométricos en las tres direcciones del espacio X, Y y Z comprendidos entre 1 - 250 µm en su eje X, 1 – 250 µm en su eje Y, y 10 nm – 50 µm en su eje Z (espesor). Este tamaño se puede determinar mediante cualquier técnica de medición del tamaño de los chips, por ejemplo, microscopía óptica como ejemplo no limitativo. Tamaños en X y en Y mayores van a ser difícil que se puedan manipular por canales abiertos o cerrados de instrumentos de escritura (bolígrafos, plumas) impresión (impresoras de inyección de tinta) o pintura (pinceles). Chips con dimensiones en X y en Y más pequeños se puede fabricar, pero con las tecnologías actuales son tan pequeños que pueden tener poca funcionalidad. El rango de espesores entre 10 nm y 50 µm en Z, es el rango de espesores que típicamente se pueden crecer, depositar, obtener capas en la industria microelectrónica. En particular los chips de la invención se refieren a los chips que realizan funciones propias del campo de la electrónica en general.

20 En una realización particular, los chips están funcionalizados en al menos una de sus superficies planares, superior o inferior, por al menos un compuesto seleccionado de entre moléculas, biomoléculas, nanopartículas, o cualquier combinación de las anteriores, cuya funcionalidad quiera transmitirse al propio chip. Esta funcionalización puede realizarse mediante quimisorción, fisisorción y/o enlaces covalentes, 25 preferiblemente mediante enlaces covalentes. Se ha observado que la funcionalización específica de los chips con estos compuestos permite concentrar la funcionalización en zonas específicas de los chips, lo que permite definir la forma y tamaño de la zona a funcionalizar, o incluso funcionalizar diversas zonas con diferentes tipos de compuestos funcionalizadores permitiendo así combinar diferentes propiedades.

30

El término "moléculas" se refiere a un compuesto seleccionado entre compuestos luminiscentes, compuestos anti-aglomerantes, compuestos anti-adherentes y compuestos de entrecruzamiento, que contienen una o más terminaciones químicas que permitan que el compuesto se una con enlaces covalentes a la superficie de los chips.

35 Los compuestos luminiscentes comprenden sustancias fluorescentes por ejemplo los

fluoróforos derivados de las familias xanteno, cianina, squaraina, naftalena, coumarina, oxidiazola, antracena, pirena, oxazina, acridina, arilmetina, tetrapirrola o dipirrometana; y sustancias fosforescentes por ejemplo sulfuro de zinc, aluminato de estroncio, tierras raras como europio o terbio dopadas. Los compuestos anti-aglomerantes proporcionan 5 características favorables para evitar la formación de aglomeraciones por la polaridad superficial de los chips en suspensión. Los compuestos anti-adherentes previenen la unión física entre los chips en suspensión, por ejemplo, el óxido de silicio, el silicato de calcio, el carbonato de magnesio, el ferrocianuro de sodio, el ferrocianuro de potasio, la celulosa o el poli-etilenglicol (PEG). Los compuestos de entrecruzamiento generan una 10 red molecular sobre la superficie de los chips. Esta red puede tener terminaciones moleculares reactivas para entrecruzar más compuestos hacia la superficie de los chips, por ejemplo, entrecruzadores de amina-a-amina, entrecruzadores de sulfhidrilo a carbohidrato, entrecruzadores de sulfhidrilo a sulfhidrilo, entrecruzadores de amina a sulfhidrilo o entrecruzadores de carboxilo a amina. Las moléculas pueden dotar a los 15 chips de propiedades químicas, por ejemplo, como sensores o actuadores químicos.

El término “biomoléculas” se refiere a compuestos seleccionado entre proteínas, cadenas de nucleótidos o anticuerpos, que contienen una o más terminaciones químicas que permita que el compuesto se una con enlaces covalentes a la superficie de los 20 chips. Las proteínas dotan de actividad y procesos biológicos a los chips. Las cadenas de nucleótidos integran ADN y ARN a los chips, generando superficies codificadas biológicamente y con capacidades de reconocimiento de cadenas de nucleótidos secundarias. Los anticuerpos generan puntos de enlace entre los chips y antígenos para su detección e identificación. Al igual que las moléculas, las biomoléculas pueden dotar 25 a los chips de propiedades anti-adherentes, anti-aglomerantes o luminiscentes o como sensores o actuadores bioquímicos.

El término “nanopartículas” se refiere a partículas comprendidas entre 1 y 100 nm, que contengan grupos reactivos en su superficie y que puedan ser inmovilizadas sobre los 30 chips mediante enlaces covalentes. Por ejemplo, se pueden seleccionar los puntos cuánticos. Los puntos cuánticos (o QDs Quantum Dots en inglés) son nanopartículas semiconductoras de unos pocos nanómetros formados por 100 a 10000 átomos. Tienen propiedades optoelectrónicas únicas que permiten sintonizar los niveles de energía con su longitud de onda o color, y pueden ser depositados sobre los chips para dotarles de 35 dichas propiedades. Los inventores de la presente invención han observado que la

incorporación de dichos puntos cuánticos a los chips de la invención es útil a la hora de utilizarlos como elementos de identificación o codificación de superficies u objetos a los que se aplican dichos chips.

- 5 En una realización preferida de la suspensión, los chips son de fotoresina, más preferiblemente SU-8, y la forma y tamaño del chip se obtiene mediante fotolitografía, habiendo sido previamente definida por una fotomáscara diseñada ad hoc. El tamaño y forma del chip viene predefinido mediante la fotomáscara ya prediseñada con la forma y dimensiones que debe tener el chip, de forma que mediante fotolitografía se consigue

10 obtener los chips de dicha forma y dimensiones. Esto permite personalizar la forma y tamaño de los chips, así como las características físicas de las que derivan de su forma y tamaño.

La fotoresina SU-8 es una fotoresina negativa a base de epoxi de uso común. Negativa

15 se refiere a un fotoresina mediante el cual las partes expuestas a los rayos UV se polimerizan, mientras que el resto de la fotoresina permanece soluble y se puede lavar durante el revelado. SU-8 deriva su nombre de la presencia de 8 grupos epoxi en su estructura. Algunas variantes del SU-8 que pueden usarse como fotoresina según la invención de forma no limitativa, son SU-8 2000 (resiste el uso de ciclopentanona como

20 disolvente primario, presenta adhesión mejorada respecto al SU-8), SU-8 3000 (también usan ciclopentanona como disolvente primario, y se puede hilar en películas más gruesas que el SU-8), SU-8 GLM2060 (fotoresina de bajo estrés que consta de epoxi GBL y formulación de sílice CTE 14), SU-8 GLM3060 (SU-8 con nanopartículas de plata), SU-8 GMC10xx (serie SU-8 de colores rojo, azul, verde, negro, etc), SU-8

25 GMJB10XX (serie SU-8 de epoxi de baja viscosidad para aplicación de inyección de tinta), SU8 GM10XX (serie de epoxi clásica), o sus combinaciones.

En otra realización preferida de la suspensión, los chips son de silicio, y la forma y tamaño de los chips se ha determinado mediante un proceso de grabado que estructura

30 a dichos chips, habiendo sido previamente definidos la forma y tamaño por una fotomáscara diseñada ad hoc.

La suspensión de la presente invención comprende una fase sólida que comprende chips seleccionados de entre materiales semiconductores, óxidos o nitruros aislantes o

35 semiconductores, metales, materiales magnéticos, un polímero, una fotoresina, o

cualquiera de sus combinaciones; donde los materiales semiconductores se seleccionan de entre silicio (Si), silicio amorfo, silicio monocristalino, polisilicio, germanio (Ge), arseniuro de galio (GaAs); donde los óxidos o nitruros aislantes o semiconductores se seleccionan de entre óxido de silicio, óxido de aluminio, nitruro de aluminio o nitruro de silicio; donde los metales se seleccionan de entre aluminio, oro, platino o cobre; donde los materiales magnéticos se seleccionan de entre Co, Ni, o NiCo; donde el polímero se selecciona de entre polidimetilsiloxano (PDMS), polimetilfenilsiloxano y polidifenilsiloxano; y donde el fotoresina se selecciona de entre SU-8, SU-8 2000, SU-8 3000, SU-8 GLM2060, SU-8 GLM3060, SU-8 GMC10xx, SU-8 GMJB10XX, SU-8 GM10XX; o cualquiera de sus combinaciones. En otra realización de la suspensión, los chips están formados por una combinación de los materiales mencionados anteriormente, y, preferiblemente dichos chips son fabricados mediante técnicas de la microelectrónica o de la fabricación de micro y nanosistemas, usando principalmente procesos fotolitográficos para el control de sus dimensiones, con el objeto de fabricar chips electrónicos, magnéticos, o sensores o actuadores mecánicos, térmicos, magnéticos, (bio)químicos, etc.

Respecto a la forma de los chips, esta puede ser cualquiera en función de las propiedades eléctricas, físicas, magnéticas, etc., y forma que se deseé, tales como por ejemplo en forma de voladizo, de puente, de palanca, para formar baldosas, código de barras, estrellas, o cualquiera de sus combinaciones, entre otras, con además cualquier geometría plana. También se contempla cualquier forma correspondiente a la de dispositivos electrónicos conocidos.

En una realización preferida de los chips de la presente invención, la forma de los chips se selecciona de entre voladizo, puente, palanca, por ejemplo, y sin limitarse, para formar código de barras, estrella, cualquier dibujo o esquema, número, secuencia de números, letras o secuencia de letras, palabras, etc.; y/o cualquier forma geométrica plana, por ejemplo y sin limitarse a ellas, círculos, discos, coronas, triángulo, cuadrados, rectángulos, pentágonos, hexágonos, heptágonos, dodecágonos, paralelepípedos, formas planas irregulares, etc; y cualquier combinación de las anteriores.

Preferiblemente la forma del chip es de voladizo o pluralidad de voladizos. Más preferiblemente el tamaño de los chips es de entre 1 y 250 µm en lateral (X, Y) y de entre 10 nm a 50 µm en espesor (Z).

Los chips en forma de voladizo o pluralidad de voladizos son útiles como sensores de ruptura al momento de ser expuestas a estreses mecánicos. Esta forma permite el uso de estos chips para testear la resistencia a estreses mecánicos, por ejemplo, los estreses que son capaces de resistir los chips, y que estreses máximos conllevan la 5 rotura de los chips.

Por otro lado, los chips de la suspensión de la invención con forma de voladizos o pluralidad de voladizos y con dimensiones laterales preferentemente en el orden de 1-5 µm de ancho, 10-100 µm de largo y espesores nanométricos de entre 10 nm a 100 nm 10 son particularmente interesantes puesto que su espesor dota a estos chips de una extraordinaria flexibilidad facilitando la adherencia del mismo chip a superficies curvas o microfibras.

En otra realización aún más preferida, el chip tiene forma de disco y el tamaño de los 15 chips en forma de disco, es de 3 µm de diámetro × 0,5 µm de espesor hasta 248 µm de diámetro × 5 µm de espesor.

En la suspensión de presente invención, la fase liquida o semilíquida utilizada como medio de suspensión es preferiblemente una tinta. Se entiende por "tinta" a una 20 sustancia de color o transparente, fluida o viscosa, que sirve para escribir, pintar, dibujar o imprimir, e incluye de forma genérica no limitante tintas de bolígrafo, de rotulador, de plumas, de sello polimérico, de impresoras.

Otro aspecto de la invención se refiere a un método de obtención de la suspensión de 25 chips de fotoresina descrita anteriormente (a partir de aquí primer método de la invención), caracterizado por que comprende las siguientes etapas secuenciales:

- a) proveer un sustrato, preferiblemente un sustrato plano, que puede ser de cualquier material y forma, preferiblemente el sustrato será de silicio, de vidrio, polimérico o metálico;

- b) recubrir el sustrato de la etapa (a), total o parcialmente, con una capa de material sacrificial, preferiblemente el material sacrificial se selecciona de entre polímeros solubles en agua tales como PVOH (poli(alcohol vinílico)), PEG (polietilenglicol), PAA (ácido poli(acrílico)), PAM (poliacrilamida), HEC (hidroxietil celulosa), PVP (polivinilpirrolidona), PEO 30 (óxido de polietileno) o alginato de sodio;

- c) depositar sobre la capa sacrificial de la etapa (b) la capa estructural de un fotoresina seleccionado de entre SU-8, SU-8 2000, SU-8 3000, SU-8 GLM2060, SU-8 GLM3060, SU-8 GMC10xx, SU-8 GMJB10XX, SU-8 GM10XX, o cualquiera de sus combinaciones;

- 5 d) definir el tamaño y forma de la capa estructural mediante fotolitografía, preferiblemente el tamaño y forma de la capa estructural se determinar mediante el uso de una máscara diseñada ad hoc, para diseñar la forma que el tamaño y forma del chip;

- 10 e) opcionalmente aplicar sobre la capa obtenida en la etapa (d) una capa superior de al menos un compuesto, preferiblemente seleccionado de entre moléculas, biomoléculas, nanopartículas, o cualquiera de sus combinaciones, más preferiblemente el compuesto se selecciona de entre fluoróforos, anti-aglomerantes, anti-adherentes, biomoléculas, puntos cuánticos, o cualquiera de sus combinaciones;

- 15 f) liberar los chips obtenidos en la etapa (d) o (e) del sustrato mediante disolución de las mismas en agua o disolución acuosa cuando la capa sacrificial es soluble en agua durante un tiempo de entre 5 y 60 min, a una temperatura de entre 5 y 80 °C. Opcionalmente, en caso de que los chips se adhieran al sustrato, se pueden agitar o dar golpes de ultrasonido para liberar los chips; y

- 20 g) dispersar los chips obtenidas en la etapa (f), en una fase líquida o semilíquida seleccionada de entre tintas, pinturas o barnices, donde el porcentaje en peso de los chips, es de entre 0,000001-60% respecto al peso total de la suspensión.

25

La función de la etapa (b) de recubrir el sustrato con una capa sacrificial, es poder construir sobre dicha capa lo/s chip/s de interés, de forma que cuando la capa sacrificial sea finalmente disuelta, el chip construido encima de esta sea liberado del sustrato de la etapa (a).

30

En la etapa (c) se deposita la fotoresina, material principal del que está compuesto el chip, por lo que a la capa resultante se le denomina "capa estructural".

Tras la etapa (f) se obtienen chips de capa estructural de fotoresina que pueden estar 35 recubiertos en una de sus partes inferior y/o superior o en ambas superior e inferior por

un compuesto de funcionalización química descrito previamente en la presente invención, preferiblemente seleccionado de entre fluoróforos, anti-aglomerantes, anti-adherentes, biomoléculas, puntos cuánticos, o cualquiera de sus combinaciones.

5 Opcionalmente, posteriormente a la etapa (b) y previamente a la etapa (c) se añade una capa sobre al menos una parte de la superficie de la capa de material sacrificial de al menos un compuesto, donde dicho compuesto puede ser seleccionado de entre moléculas, biomoléculas, nanopartículas, o cualquiera de sus combinaciones, más preferiblemente puede ser seleccionado de entre fluoróforos, anti-aglomerantes, anti-10 adherentes, biomoléculas, puntos cuánticos, o cualquiera de sus combinaciones.

Por tanto, las chips pueden funcionalizarse según se describe en la etapa (e) y/o entre la etapa (b) y (c), tal y como se describe previamente.

Otro aspecto de la invención se refiere a un método de obtención de la suspensión 15 descrita anteriormente (a partir de aquí el segundo método de la invención) caracterizado por que los chips son de materiales semiconductores o de óxidos o nitruros aislantes o semiconductores, o de metales o de materiales magnéticos o de polímeros o sus combinaciones, y comprende las siguientes etapas secuenciales:

- i. proveer un sustrato, preferiblemente un sustrato plano, de silicio;

- 20 ii. oxidar térmicamente la superficie del sustrato de silicio de la etapa (i), o depositar óxido de silicio sobre el sustrato de la etapa (i) hasta obtener una capa sacrificial de óxido de silicio de 0,1-1 µm de espesor;

- 25 iii. depositar una capa sacrificial de aluminio sobre el sustrato de la etapa (i), hasta obtener una capa sacrificial de Al de 0,1-1 µm de espesor;

- 30 iv. depositar sobre la capa sacrificial obtenida en la etapa (ii) una capa estructural de silicio amorfo, silicio monocristalino, polisilicio, germanio, arseniuro de galio, óxido de silicio, nitruro de silicio, aluminio, oro, platino, cobre, Co, Ni, NiCo, PDMS, polimetilfenilsiloxano y polidifenilsiloxano o sus combinaciones, preferiblemente una capa de espesor de 25 nm a 50 µm;

- 35 v. definir el tamaño y forma de la capa estructural mediante eliminación parcial de la capa estructural por un proceso de grabado, preferiblemente el tamaño y forma de la capa estructural se determina

- mediante el uso de una máscara diseñada ad hoc, para diseñar la forma y el tamaño de los chips, de forma que el tamaño y forma del chip puede pre-diseñarse según se desee o según las necesidades;

- v. opcionalmente, aplicar sobre la capa estructural obtenida en (iii) una capa superior de funcionalización química mediante al menos un compuesto químico, preferiblemente seleccionado de entre compuestos de moléculas, biomoléculas, o nanopartículas, o sus combinaciones; y opcionalmente aplicar una o varias capas estructurales de silicio, de óxidos o nitruros aislantes o semiconductores, de metales, de materiales magnéticos, fotoresinas, o cualquiera de sus combinaciones; donde el silicio se selecciona de entre silicio amorfo, silicio monocrystalino o polisilicio; donde los óxidos o nitruros aislantes o semiconductores se seleccionan de entre óxido de silicio, óxido de aluminio, nitruro de aluminio o nitruro de silicio; donde los metales se seleccionan de entre aluminio, oro, platino o cobre; donde los materiales magnéticos se seleccionan de entre Co, Ni, o NiCo, y donde la fotoresina se selecciona de entre SU-8, SU-8 2000, SU-8 3000, SU-8 GLM2060, SU-8 GLM3060, SU-8 GMC10xx, SU-8 GMJB10XX, SU-8 GM10XX; o cualquiera de sus combinaciones; y

- vi. liberar los chips obtenidas en la etapa (iv) o (v) del sustrato, mediante grabado con vapores de ácido, preferiblemente vapores de ácido hidrofluorhídrico, de la capa sacrificial de óxido de silicio incorporada o generada en la etapa (ii), que servía de interfaz entre el sustrato y el chip a fabricar, hasta eliminar la capa sacrificial totalmente; o mediante grabado con una solución de KOH al 50%, de la capa sacrificial de Al incorporada en la etapa (ii), que servía de interfaz entre el sustrato y el chip a fabricar, hasta eliminar la capa sacrificial totalmente; y

- vii. dispersar los chips obtenidos en la etapa (vi), en una fase líquida o semilíquida seleccionada de entre tintas, pinturas o barnices, donde el porcentaje en peso de la fase sólida es de entre 0,000001-60% respecto al peso total de la suspensión.

La elección de capa sacrificial a elegir, óxido de silicio, aluminio, o sus combinaciones dependerá del material de la capa estructural, teniendo en cuenta que al liberar los chips del sustrato mediante disolución preferiblemente en vapores de HF para cuando la capa sacrificial es de óxido de silicio o bien en disoluciones de KOH para cuando la capa sacrificial es de aluminio, durante un tiempo de entre 5 y 60 min, a una temperatura de entre 5 °C y 80 °C, será la capa sacrificial la que se disuelva sin disolverse o afectarse la integridad de la capa estructural. Por ejemplo, si la capa estructural es polisilicio, silicio amorfo, la capa sacrificial puede ser preferentemente de óxido de silicio. Por ejemplo, si la capa estructural es óxido de silicio, la capa sacrificial puede ser preferente de aluminio.

En una realización aún más preferida del método de la invención los chips son de silicio.

En una realización preferente del método de la invención, la forma y tamaño del chip se ha determinado mediante un proceso de grabado que estructura los chips. El tamaño y forma es previamente definido por una fotomáscara diseñada ad hoc, con lo cual se consigue personalizar el tamaño y forma de los chips según se desee o requiera.

En el caso particular de que la capa estructural sea de óxido de silicio, esta puede a su vez ser recubierta por otro material estructural de los arriba mencionados que no son disueltos por grabado con vapores de ácido HF. Con ello, se consigue proteger la capa estructural tras la etapa (vi).

En una realización preferida del método de obtención de suspensión de los chips, posteriormente a la etapa (ii) y previamente a la etapa (iii) se añade una capa de un compuesto parcial o totalmente sobre la superficie de la capa sacrificial, donde dicho compuesto puede estar seleccionado de entre moléculas, biomoléculas, nanopartículas, o cualquiera de sus combinaciones, preferiblemente el compuesto seleccionado de entre fluoróforos, anti-aglomerantes, anti-adherentes, biomoléculas, puntos cuánticos, o cualquiera de sus combinaciones, más preferiblemente la superficie funcionalizada es la que una vez deposita se encuentra en la capa opuesta al sustrato y está configurada para estar en contacto con material de la capa estructural.

Tanto el primer como el segundo método de la invención, descritos previamente, son procesos de fabricación que permiten definir los chips con dimensiones laterales muy

controladas, con precisión en el orden de las decenas de nanómetros y espesores que pueden llegar a tener una precisión en el orden de pocos nanómetros.

En los métodos de obtención de las suspensiones descritos previamente, la

5 funcionalización química de los chips (por ejemplo, etapas (v) o (e)) se aplica preferentemente como una capa de espesor homogénea y continua por encima y/o debajo del chip, si bien la invención contempla también aplicar dicha capa de funcionalización en cualquier superficie del chip, tanto como una capa homogénea, no homogénea, continua, o discontinua.

10

La funcionalización química puede realizarse mediante cualquier técnica del estado de la técnica que permita funcionalizar superficies químicamente, como por ejemplo mediante sistemas de impresión por litografía blanda o química en solución.

15 En la presente invención se entiende por “impresión por litografía blanda” a cualquier técnica para imprimir moléculas, biomoléculas o nanopartículas, por medio del contacto de un sello elastomérico que ha sido cubierto previamente el compuesto seleccionado entre dichas moléculas, biomoléculas o nanopartículas, sobre la superficie de los chips.

En la presente invención se contempla imprimir estos compuestos en la superficie de

20 los chips, con técnicas de impresión por microcontacto (“microcontact printing” en inglés) y litografía por plumas poliméricas (“polymer pen lithography” en inglés). En el caso de la impresión por microcontacto, se utiliza un sello elastomérico de polydimethylsiloxano (PDMS) plano y en el caso de litografía por plumas poliméricas se utiliza el sello elastomérico de PDMS estructurado con elementos en forma de pirámide en donde las

25 puntas de las pirámides entrarán en contacto con la superficie a imprimir. En ambos casos, el sello se incuba con la tinta a imprimir. Después de secar el exceso de la solución de la tinta sobre el sello, el sello se pone en contacto sobre los chips en la porción de oblea que se quiera funcionalizar. Se aplica una ligera presión para que todo el sello esté en contacto con los chips, y se deja reaccionar durante 2 min.

30

Se entiende por “química en solución” a aquel proceso de funcionalización de la superficie de los chips mediante exposición a una solución reactiva donde el reactivo queda unido covalentemente a la superficie del chip.

Otro aspecto de la invención se refiere al uso de la suspensión de la presente invención, para trasferir los chips comprendidos en la suspensión a superficies espacial y geométricamente complejas.

- 5   Otro aspecto de la presente invención se refiere a un procedimiento para transferir los chips comprendidos en la suspensión de la presente invención a una superficie caracterizado por que comprende una etapa de depositar la suspensión de la invención sobre la superficie mediante medios de escritura, pintura o impresión, donde los medios de escritura, pintura o impresión comprenden canales para distribuir la suspensión a la

10   superficie, y donde los chips de la suspensión tienen un tamaño menor que los canales del dispositivo de escritura, pintura o impresión.

Aplicando la suspensión sobre una superficie según el procedimiento descrito, los chips comprendidos en ella no se rompen ni se atascan en los canales del dispositivo además

15   de asegurar que los chips que son transferidos manteniendo su integridad estructural.

Por tanto, el procedimiento para transferir los chips comprendidos en la suspensión a una superficie de la presente invención es susceptible de ser utilizado para aplicaciones que incluyen la decoración, el marcaje, la anti-falsificación o antifraude, la codificación y

20   la fabricación de dispositivos electrónicos, como se mencionaba con anterioridad.

Otro aspecto de la invención se refiere al uso de la suspensión de la presente invención para la determinación como test de caracterización de las dimensiones de los canales de un dispositivo de escritura, pintura o impresión. preferiblemente la suspensión

25   comprende chips en forma de discos.

Otro aspecto de la presente invención se refiere a un procedimiento para determinar las dimensiones de los canales de un dispositivo de escritura, pintura o impresión caracterizado por que comprende una etapa de hacer pasar la suspensión según

30   cualquiera de las reivindicaciones 1 a 7 por un canal de un dispositivo de escritura, pintura o impresión, donde los chips comprendidos en la suspensión tienen un tamaño mayor que el canal del dispositivo y donde dichos chips son incapaces de atravesar el canal y se rompen.

Por ejemplo, el procedimiento descrito permite determinar el diámetro del conducto (canal) cerrado de dispositivos como son una impresora de inyección, bolígrafo o rotulador.

- 5 En la presente invención, el término “canal” también se refiere a los espacios abiertos entre las cerdas de un pincel o en una pluma estilográfica. Por tanto, el procedimiento descrito también permite determinar este espacio por el cual se conduce la suspensión que comprende los chips.

- 10 El último aspecto de la invención se refiere a un dispositivo capaz de aplicar o suministrar una suspensión sobre superficies espacial y geométricamente complejas por un canal de salida, donde dicho dispositivo comprende la suspensión de la invención y donde el canal de salida tiene un diámetro mayor a la mayor de las dimensiones de los chips de la suspensión. Preferiblemente el dispositivo se selecciona de entre un dispositivo de escritura, pintura o impresión, más preferiblemente de entre una impresora inkjet, un bolígrafo, una pluma, un sello polimérico o un pincel.

- 15

#### Breve descripción de las Figuras

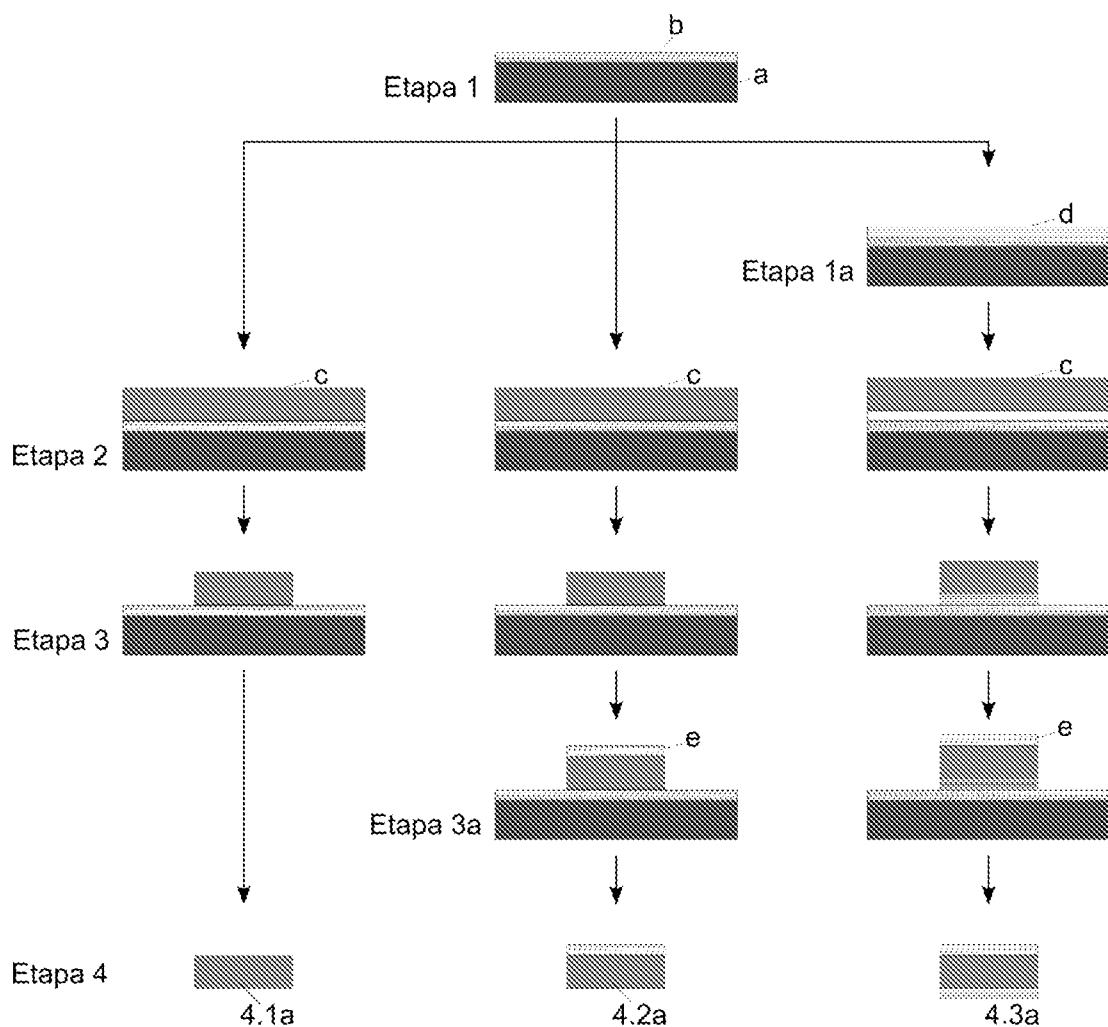

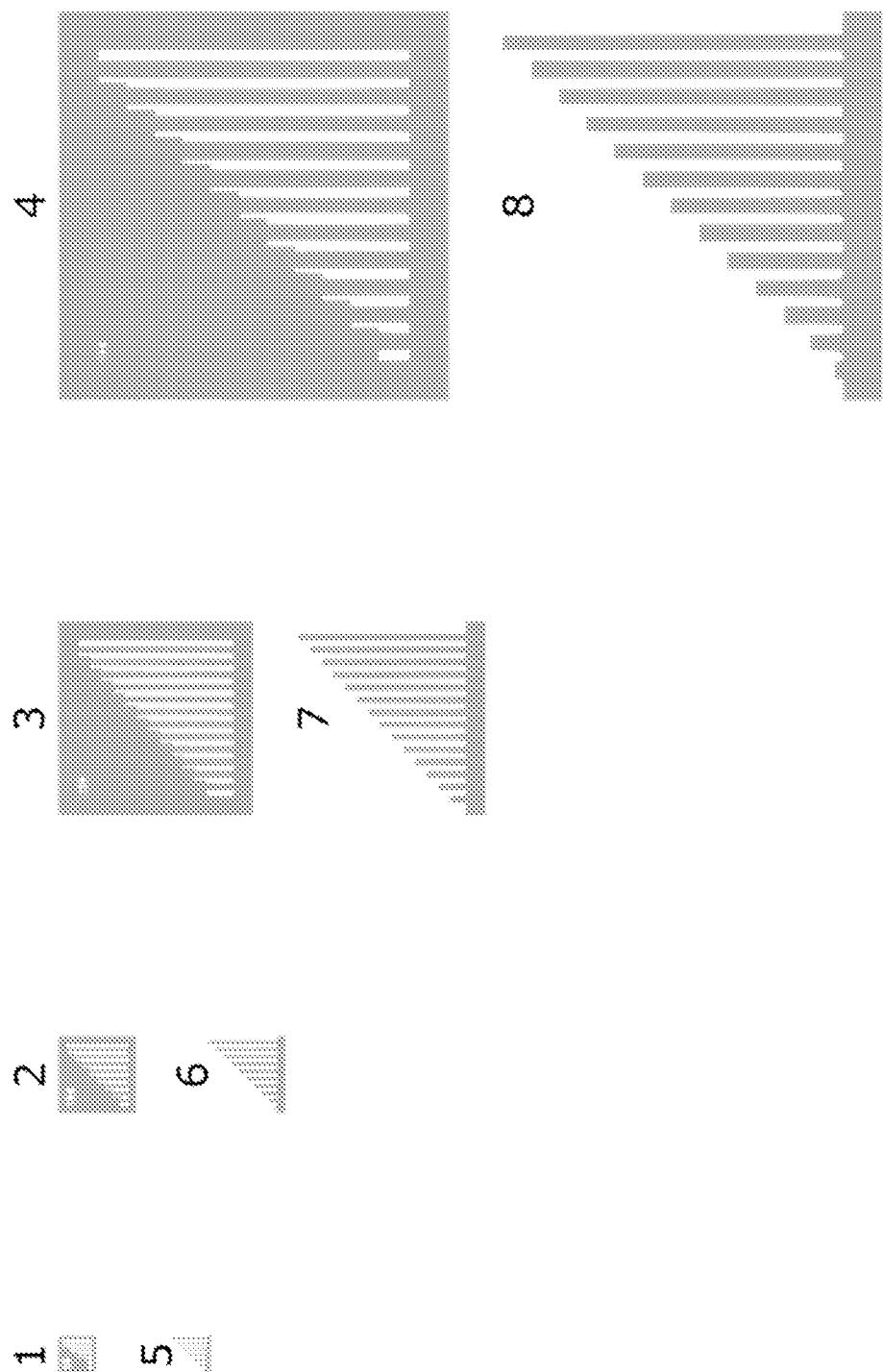

- 20 **Fig. 1** Muestra un esquema general del método de fabricación de la suspensión de los chips de acuerdo a la presente invención.

**Fig. 2** Muestra una tabla comparativa de las longitudes más largas de chips probados y que fueron escritos, pintados o impresos correctamente sobre cualquier sustrato.

- 25

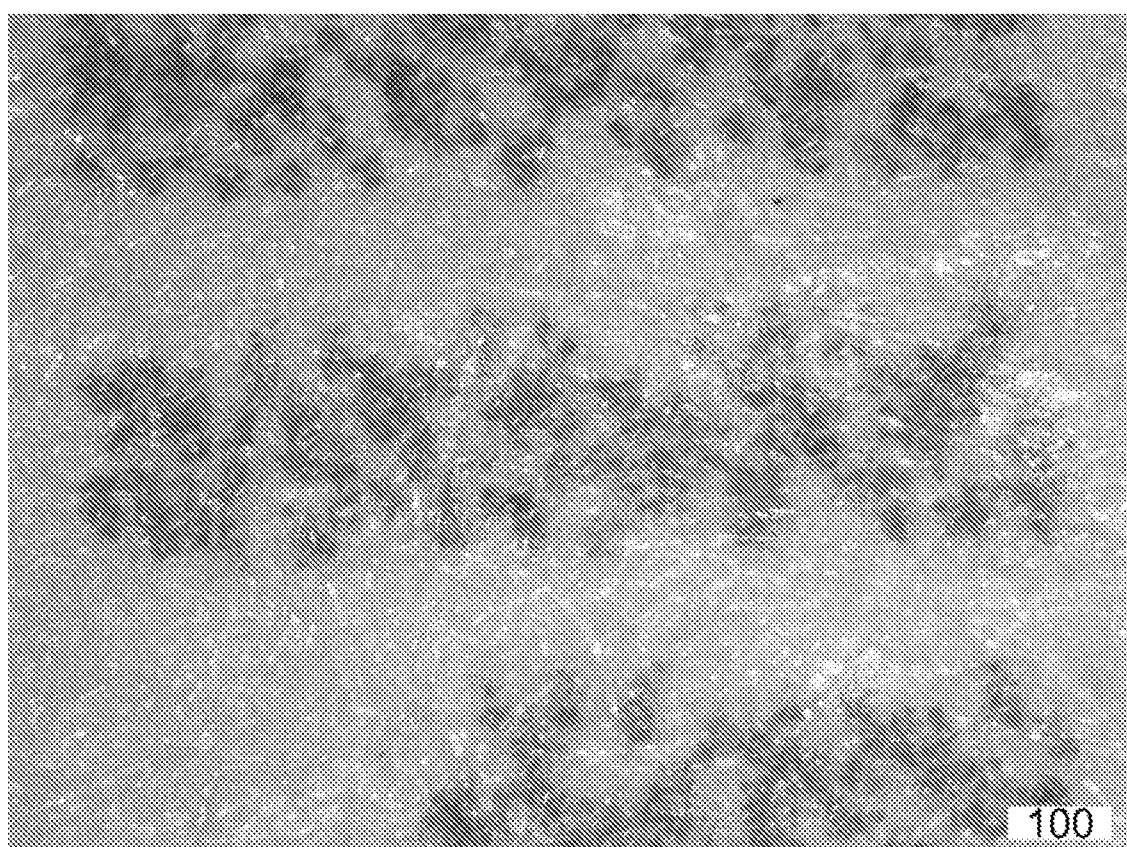

- 30 **Fig. 3** Muestra una imagen de microscopía óptica en escala micrométrica de una prueba de impresión de un testeo de canales de una impresora EPSON ET-2710 con chips de silicio re-suspendidos en tinta de impresora de inyección de tinta (EPSON 104). Los espacios en blanco representan los canales obturados de la impresión de inyección que no han permitido que pasara la tinta de impresión.

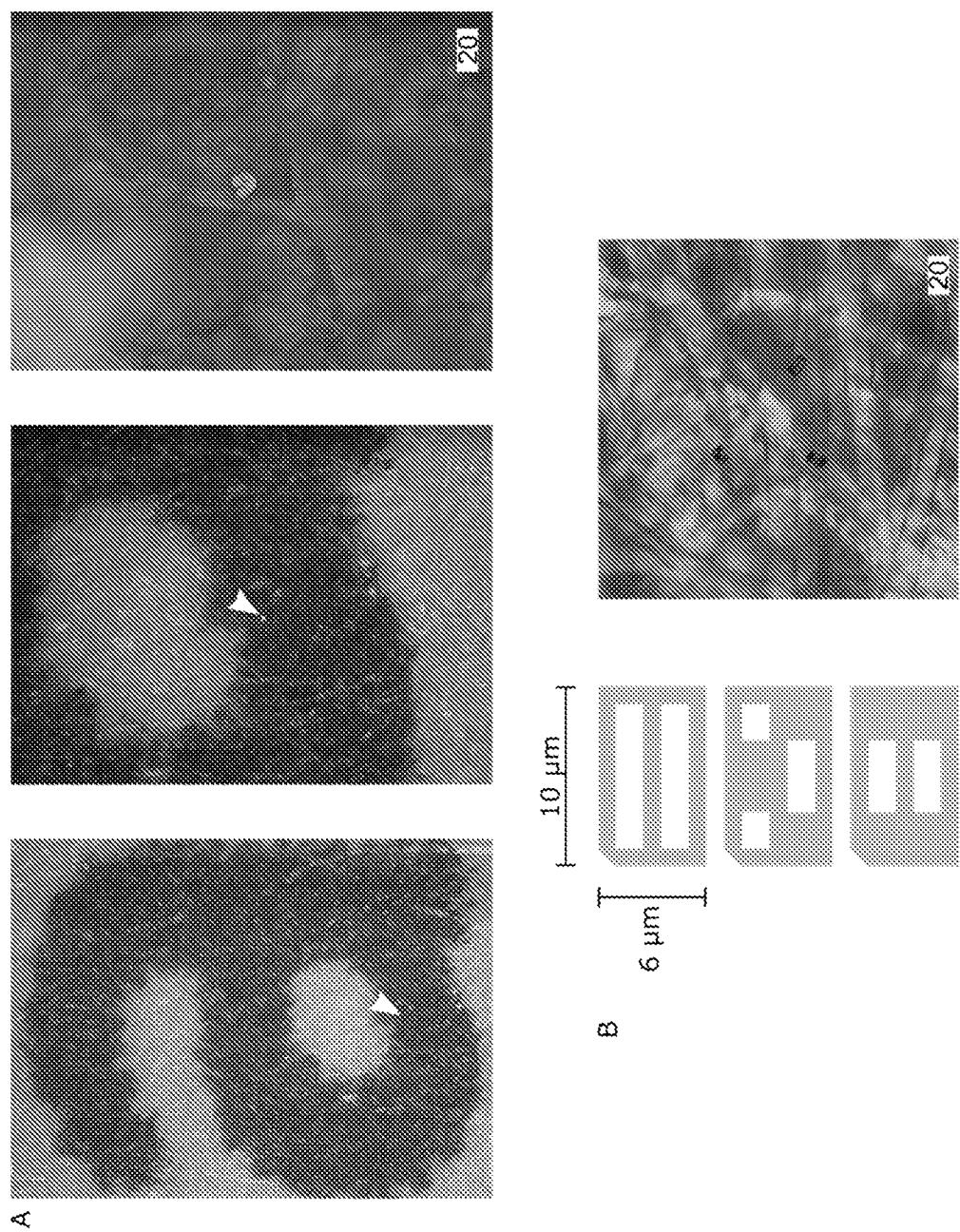

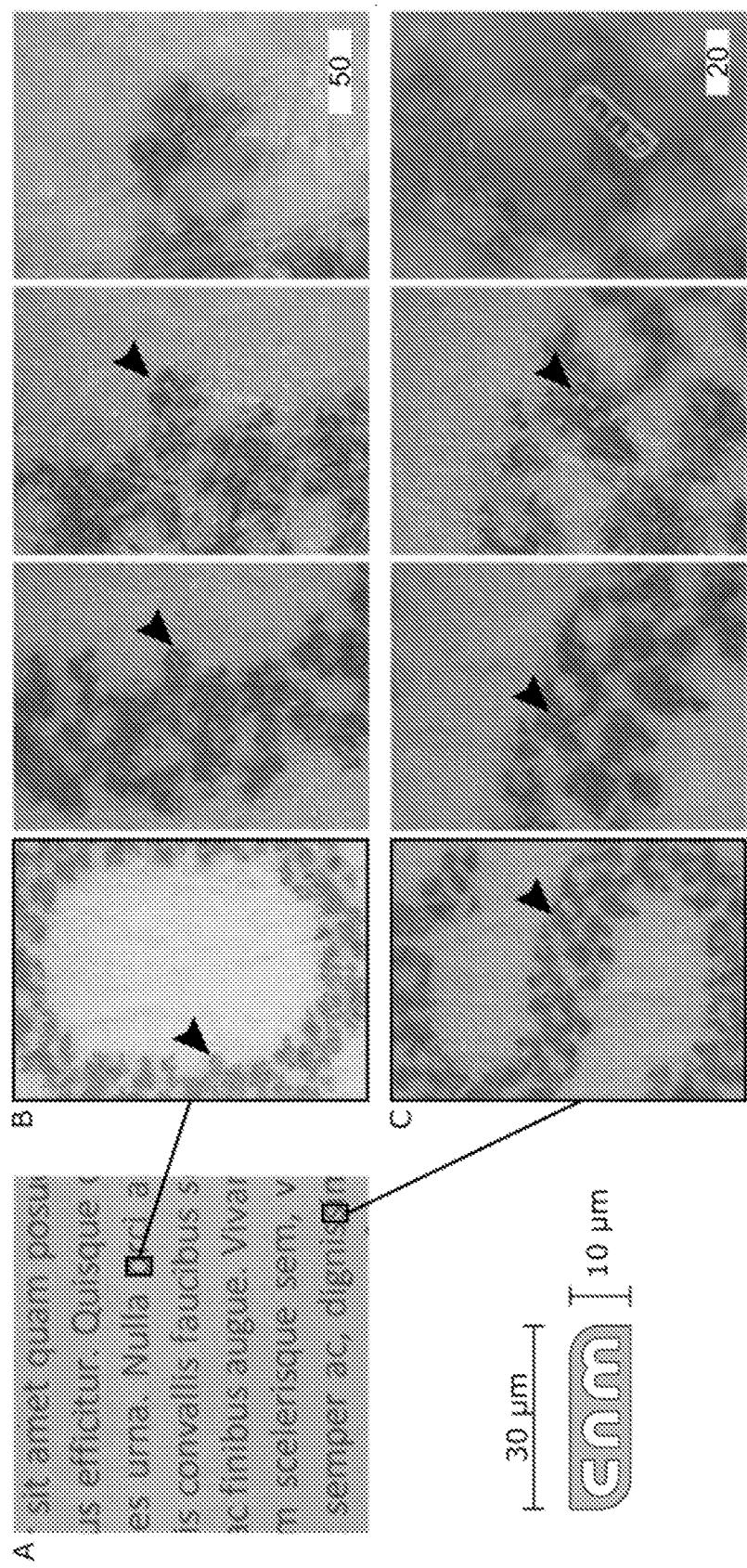

- 35 **Fig. 4** Muestra una imagen de microscopía óptica en escala micrométrica (4A) de una prueba de impresión de una impresora EPSON ET-2710 con chips de silicio re-suspendidos en tinta de impresora de inyección de tinta (EPSON 104) en donde los chips de polisilicio en forma circular con diámetro de 3, 5 y 10 µm y espesor de 0.5 µm

han sido impresos en un texto. Igualmente se muestra una imagen de microscopía óptica (4B) de chips de polisilicio de  $6 \mu\text{m} \times 10 \mu\text{m}$  y espesor de  $1 \mu\text{m}$  con forma de códigos de barra suspendidos en tinta de impresora e impresos con la misma impresora.

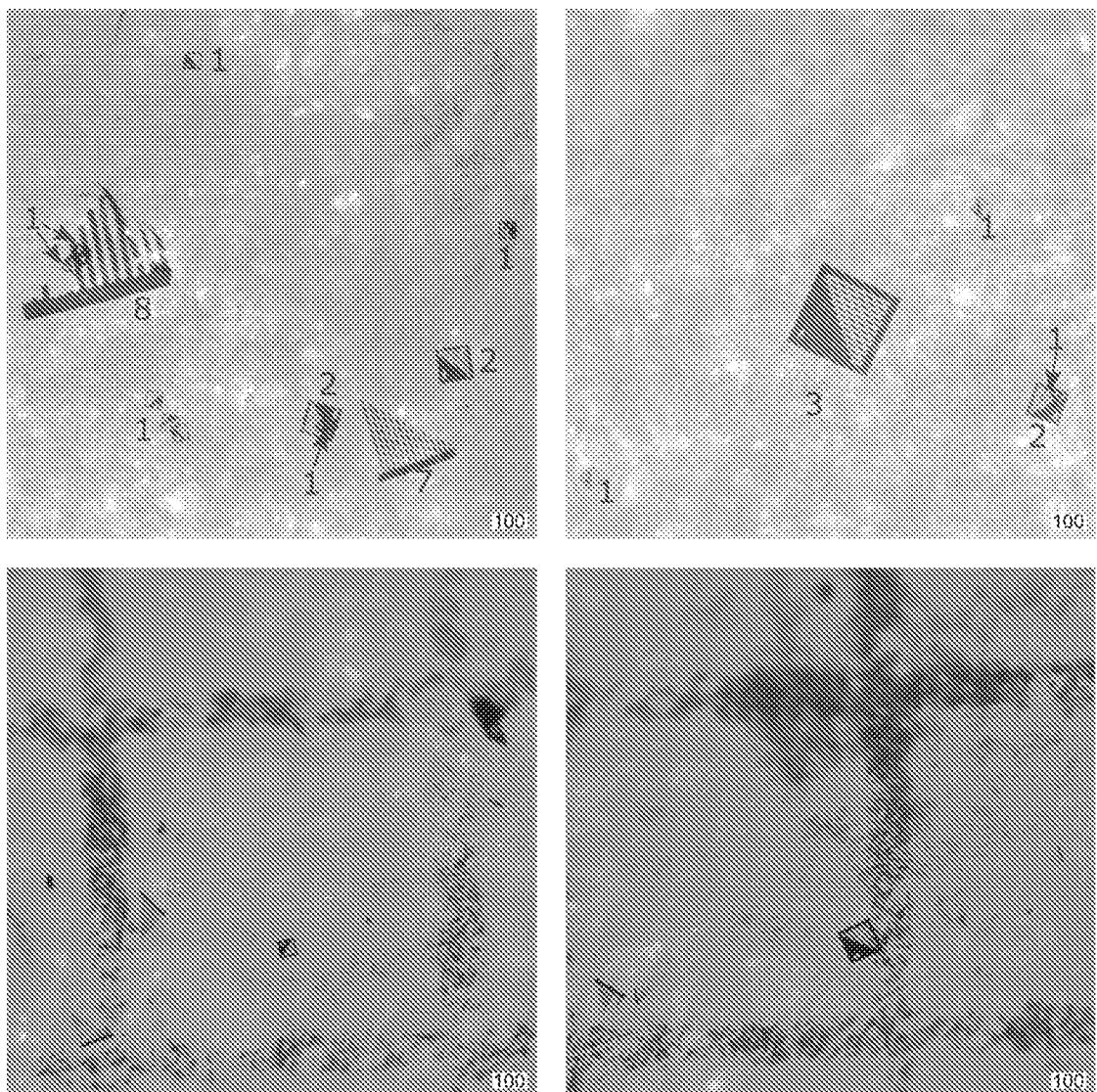

- 5   **Fig. 5** Muestra chips en forma de voladizo, con forma de estructuras de test de ruptura, con dimensiones de  $50 \times 50 \mu\text{m}^2$ ,  $100 \times 100 \mu\text{m}^2$ ,  $250 \times 250 \mu\text{m}^2$  y  $500 \times 500 \mu\text{m}^2$  re-suspendidos en pintura a base de agua roja y azul y pintados sobre papel milimétrico mediante pincel. Las imágenes de microscopía muestran la localización final de varios chips. Los números muestran el tipo de chips presente en la imagen y su integridad

10   estructural. Las escalas representan  $\mu\text{m}$ .

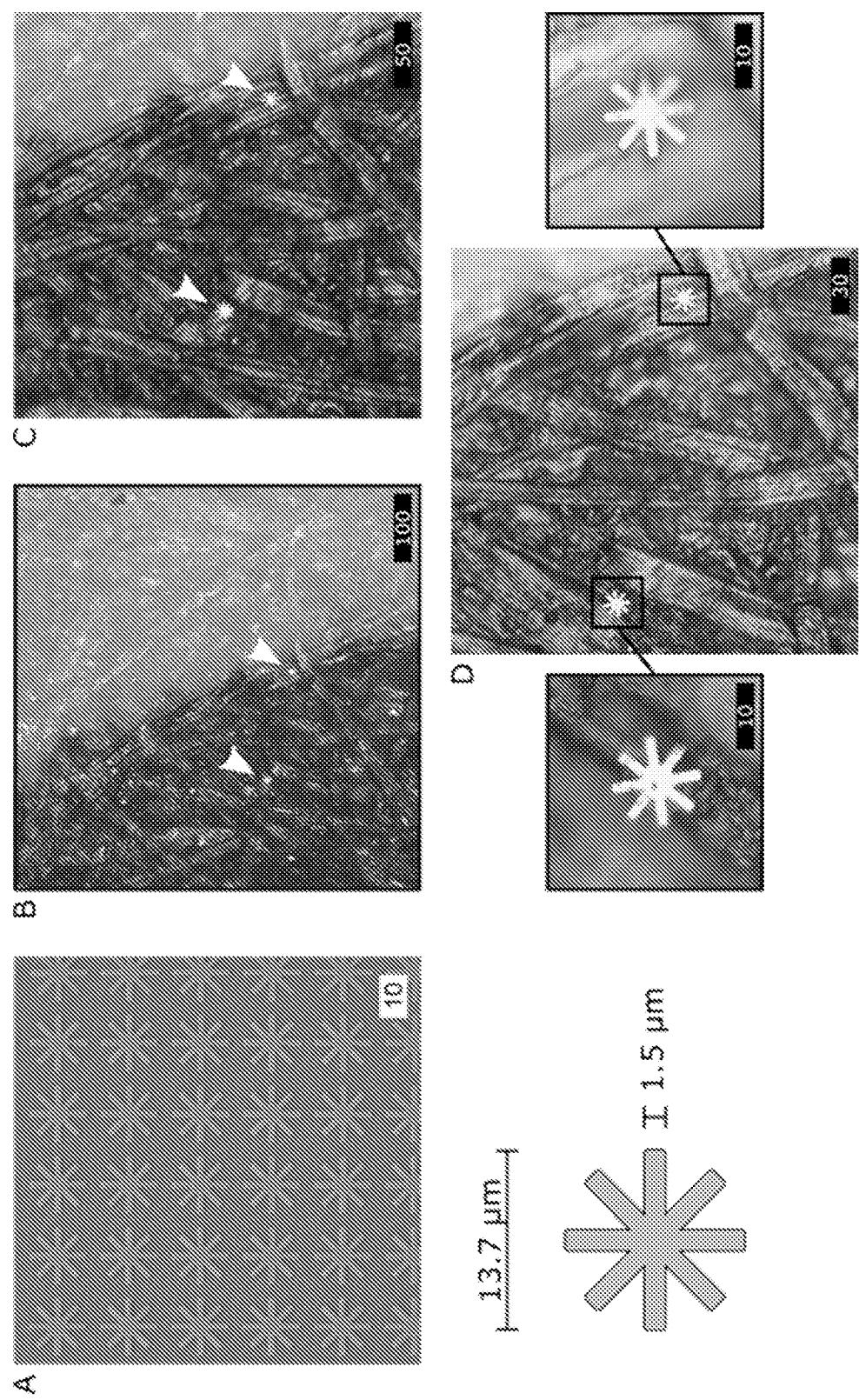

- Fig. 6 Muestra una imagen de microscopía de barrido de electrones (6A) de chips de polisilicio con forma de estrella de 8 puntas de  $13.7 \mu\text{m}$  de largo y de ancho, inmovilizados sobre una oblea. También muestra un esquema de los chips de polisilicio

15   con forma de estrella suspendidos en la tinta de bolígrafo que se utilizó para escribir sobre papel estándar. La figura 6B) – D) muestran imágenes de microscopía óptica a diferentes aumentos mostrando la localización final de dos chips en el texto escrito. Las flechas blancas apuntan a los chips en las imágenes. Las escalas representan  $\mu\text{m}$ .

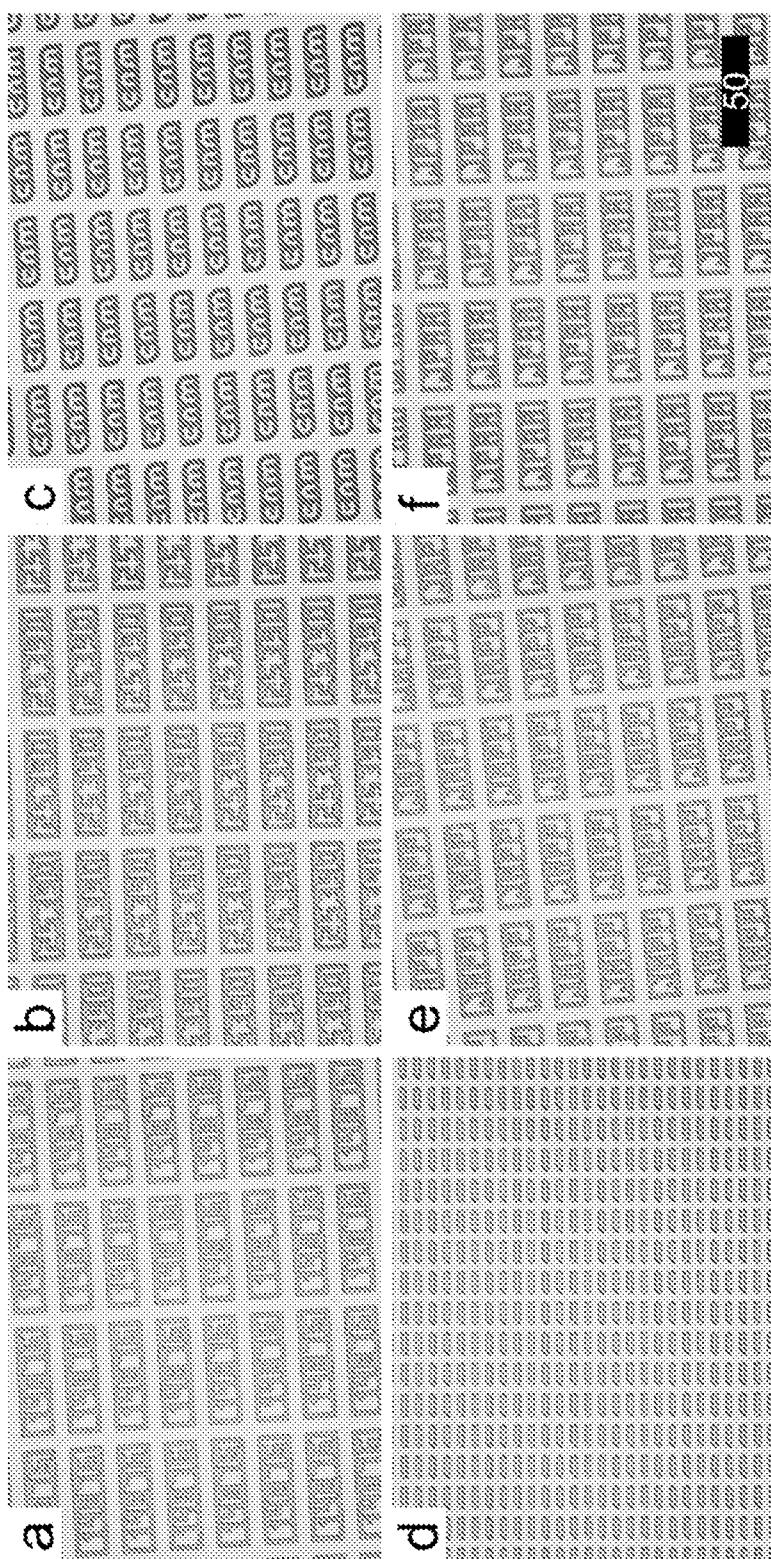

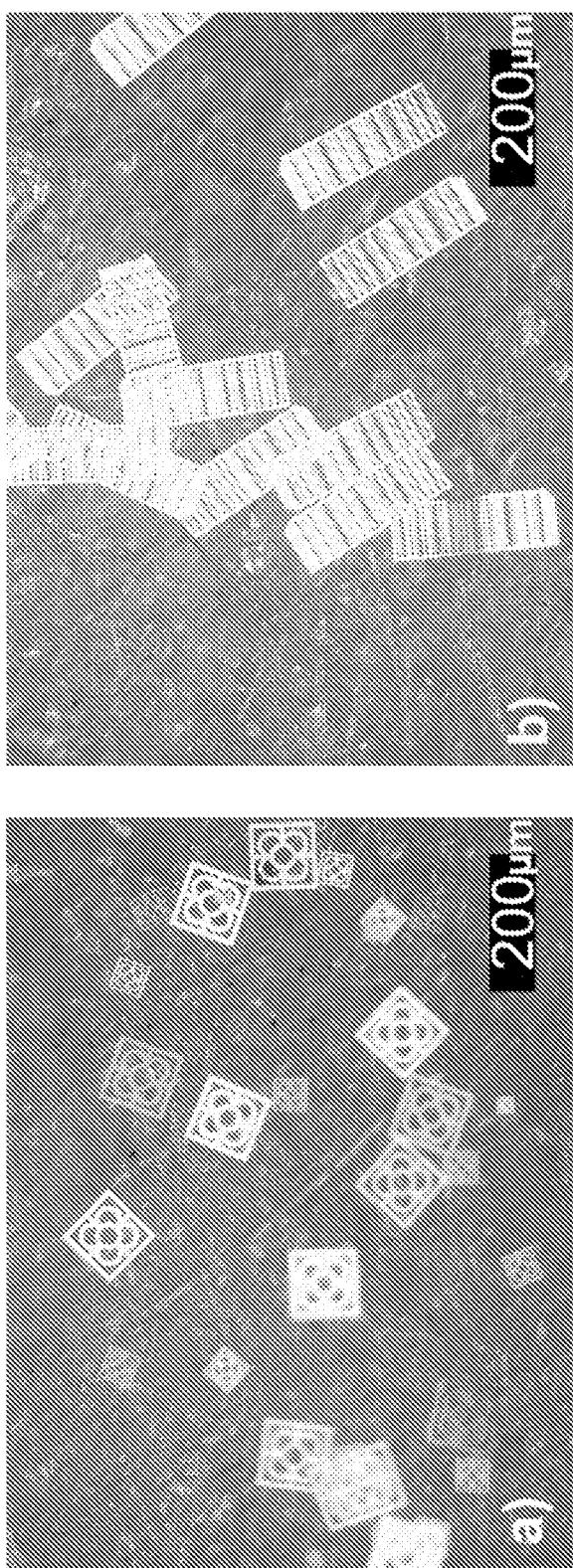

- 20   **Fig. 7** Muestra imágenes de microscopía óptica de chips de fotoresina inmovilizados sobre el sustrato y la capa sacrificial soluble, antes de que se disuelva la capa sacrificial soluble y se liberen los chips de fotoresina. La figura 7a muestra chips con el código numérico 14876, la figura 7b muestra chips con el código numérico 25390, la figura 7c muestra chips con el logo del CNM. La figura 7d muestra chips con una marca de inicio

25   de lectura en su esquina, la figura 7e muestra chips con el código alfabético JAPP, y la figura 7f muestra chips con el código alfabético JPAA. La escala representa  $\mu\text{m}$ .

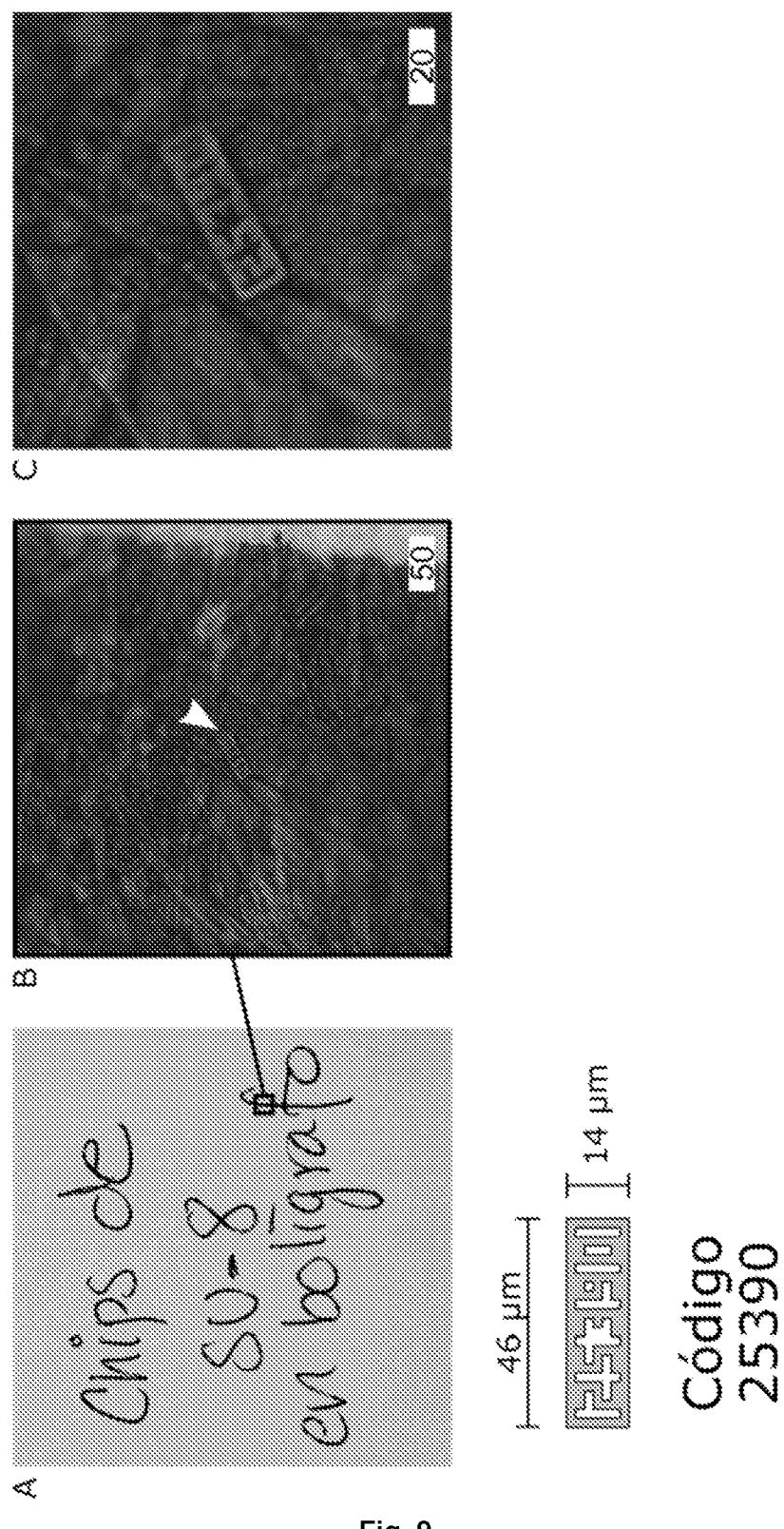

- Fig. 8** A) Chips de SU-8 con forma del logo del CNM  $30 \mu\text{m}$ , de largo y  $10 \mu\text{m}$  de ancho, suspendidos en la tinta que se utilizó para imprimir sobre papel estándar. B) – C)

30   imágenes de microscopía a diferentes aumentos mostrando la localización final de dos chips en el texto impreso. Las flechas negras apuntan a los chips en las fotos. Las escalas representan  $\mu\text{m}$ .

- Fig. 9** A) Chips de SU-8 con forma de código 25390 de  $46 \mu\text{m}$  de largo y  $14 \mu\text{m}$  de ancho

35   suspendidos en la tinta de bolígrafo que se utilizó para escribir sobre papel estándar. B)

– C) imágenes de microscopía a diferentes aumentos mostrando la localización final de un chip en el texto escrito. La flecha blanca apunta al chip en la imagen. Las escalas representan  $\mu\text{m}$ .

- 5 **Fig. 10** Chips de SU-8 con forma de baldosa de Barcelona y de Panda funcionalizados con puntos cuánticos de emisión a 585 nm y 655 nm, respectivamente. Se utilizó pintura acuarela y un pincel para pintar sobre papel estándar. Las escalas representan  $\mu\text{m}$ .

10 **Fig. 11** Imagen de microscopía óptica de los chips suspendidos en una tinta y posteriormente depositados sobre papel con una pluma. A la izquierda (Figura 11a) se muestran los chips con la forma de la baldosa de Barcelona de diferentes tamaños, aplicadas en forma de suspensión sobre papel blanco utilizando tinta de impresora amarilla como medio líquido de depósito. A la derecha (Figura 11b), se muestran chips 15 en forma de código de barras aplicados en forma de suspensión sobre papel, utilizando agua como líquido de depósito. Las escalas representan  $\mu\text{m}$ .

## EJEMPLOS

20 A continuación, se presenta un ejemplo de realización de la invención, en el que se define el proceso de producción de los chips. Se presenta una descripción/caracterización de los chips fabricados con este método, y se describe como se prepara una suspensión con dichos chips.

### Ejemplo 1

- 25 **Fabricación de chips de polisilicio.**

Para producir los chips de polisilicio, se partió de un sustrato de oblea de silicio de 100 mm de diámetro y de 500  $\mu\text{m}$  de espesor.

30 Etapa 1: A continuación, se oxida térmicamente la superficie de un sustrato de silicio hasta obtener una capa de 1  $\mu\text{m}$  de espesor de óxido de silicio sacrificial. En la Figura 1 (etapa 1) se puede observar la aplicación la “capa sacrificial” (b) sobre un sustrato (a).

35 Etapa 2: A continuación, se aplicó por encima de la superficie de la capa sacrificial la “capa estructural” de polisilicio de espesores desde 25 nm hasta 2.25  $\mu\text{m}$ , como puede verse en la Figura 1, etapa 2, de deposición de polisilicio (c) utilizando la técnica de

Deposición Química de Vapor o CVD (de sus siglas en inglés Chemical Vapor Deposition). Los parámetros del depósito son: Temperatura = 1000 °C, Presión = 4 atm, Velocidad de inyección = 3.5 m/s, Fracción molar del H<sub>2</sub> = 0.91

- 5 Etapa 3: A continuación, mediante fotolitografía, se determinó la forma y dimensiones del chip resultante. Para ello se expone el dispositivo a luz UV a través de la fotomáscara ad hoc que ha sido fijada en una alineadora.

10 En la figura 6A se muestran imágenes de microscopía de barrido de electrones de chips de polisilicio inmovilizadas sobre el sustrato, antes de que se disuelva la capa sacrificial y se liberen los chips.

15 Finalmente, la etapa 4 de la Figura 1 representa el paso de eliminación de la capa sacrificial mediante la disolución de la capa sacrificial soluble con vapores de ácido hidrofluorhídrico. Para realizar este paso, se divide la oblea en porciones de alrededor 1×1 cm<sup>2</sup> y se exponen a la atmósfera saturada del ácido. Se deja grabar por 20 min o hasta que el óxido térmico haya sido eliminado por completo. Los chips resultantes por tanto son separados del sustrato inicial (4.1a) y son recolectados y re-suspendidos en etanol.

20

### Ejemplo 2

#### Tinta + chips de test de silicio impresos para caracterizar los microcanales de la impresora de inyección

Siguiendo el ejemplo 1 de obtención de los chips de silicio de forma circular de  $\Phi$  15 – 25  $\mu\text{m}$  y espesor de 0.5  $\mu\text{m}$ , éstos se re-suspendieron en tinta de impresora de inyección de tinta (EPSON 104). La suspensión de tinta con los chips de silicio se introdujo a la impresora (EPSON ET-2710) y se imprimió un documento sobre papel de impresión. Al imprimir, no se observan chips en la impresión (figura 3), con lo que se puede argumentar que los chips quedan atascados en los canales por su tamaño. De igual manera, se observa que el patrón impreso tiene espacios en blanco, indicando obturación de los canales de impresión, ya que los dispositivos no han salido por los tubos al momento de la impresión. Por otro lado, se utilizó una mezcla de varios chips de silicio de forma circular que comprende 33.33% del total de los chips de 3  $\mu\text{m}$  de diámetro, 33.33% de 5  $\mu\text{m}$  de diámetro y 33.33% de 10  $\mu\text{m}$  de diámetro y todos con un espesor de 0.5  $\mu\text{m}$  que se re-suspendieron en tinta de impresora de inyección de tinta

(EPSON 104). La suspensión de tinta con los chips de silicio se introdujo a la impresora (EPSON ET-2710) y se imprimió un documento sobre papel de impresión. Al imprimir, se observan chips de 3, 5 y 10 µm de diámetro en la impresión (figura 4A), indicando que las dimensiones de estos chips son adecuadas para atravesar canales de impresión

5 de la impresora. Las escalas en las figuras representan µm.

### Ejemplo 3

#### Tinta + chips de silicio en forma de código de barras impresos con impresora de inyección

10 Siguiendo el ejemplo 1 de obtención de los chips de silicio, la “capa estructural” tiene forma de código de barras y éstos se re-suspendieron en tinta de impresora de inyección de tinta (EPSON 104). La suspensión de tinta con los chips de silicio se introdujo a la impresora (EPSON ET-2710) y se imprimió un documento sobre papel de impresión. Al imprimir, se observan chips en la impresión (figura 4B). De esta manera se puede

15 argumentar que la hoja impresa ha quedado codificada con los chips en forma de código de barras. La escala de la Figura 4B representa µm.

### Ejemplo 4

#### Tinta + chips de polisilicio pintados con pincel para test de ruptura

20 Siguiendo el ejemplo 1 de obtención de los chips de polisilicio que se fabricaron y se re-suspendieron en la pintura a base acuosa (acuarelas) y se utilizó un pincel de 8 mm (Staedtler) sobre papel estándar. Se obtienen los chips de silicio con forma de estructuras de test de fuerza con dimensiones de  $50\times50\text{ }\mu\text{m}^2$ ,  $100\times100\text{ }\mu\text{m}^2$ ,  $250\times250\text{ }\mu\text{m}^2$  y  $500\times500\text{ }\mu\text{m}^2$  re-suspendidas en pintura a base de agua roja y azul y pintadas

25 sobre papel milimétrico. La figura 5 muestra una imagen de microscopía que localiza varios chips. Los números muestran el tipo de chips presentes en la imagen y su integridad estructural. Las escalas representan µm.

### Ejemplo 5

#### Tinta + chips de silicio escritos con bolígrafo

Los chips de silicio se fabricaron siguiendo el protocolo de fabricación establecido en el Ejemplo 1, y se re-suspendieron en la tinta de un bolígrafo con una punta de 0.7 mm (MP Colours, Madrid Papel Import, S.L.). Con este bolígrafo se escribió sobre papel de impresora estándar (ver fig. 6).

**Ejemplo 6****Fabricación de chips de fotoresina SU-8**

Para producir los chips de fotoresina, se partió de un sustrato de oblea de silicio de 100 mm de diámetro y de 500 µm de espesor.

5

Etapa 1: A continuación, se aplicó encima del sustrato de silicio la “capa sacrificial” de PVOH de 50 µm de espesor que recubrió todo el sustrato de silicio. Para ello, se aplicó una solución al 10% de PVOH en agua desionizada que se dejó secar a 100 °C durante 5 min. La solución al 10% de PVOH en agua desionizada se obtiene a partir de disolver 10 10% de PVOH en agua desionizada en porcentaje de masa. En la Figura 1 (etapa 1) se puede observar la aplicación de una capa sacrificial (b) sobre un sustrato (a).

Etapa 1a: Opcionalmente, según otro ejemplo, se puede realizar la etapa 1a de funcionalización de la capa sacrificial antes de la etapa 2. Se expone la capa sacrificial 15 a plasma de oxígeno a 500 W durante 30 s y se deposita posteriormente una solución etanólica al 2% del fluoróforo cloruro de ácido de sulforrodamina 101 “Texas Red” funcionalizado con una molécula del grupo amino. Esta solución se deposita por medio de una micropipeta. Después se deja reaccionar durante 30 min y se seca con nitrógeno. Este proceso puede verse en la Figura 1, etapa 1a, de deposición de fluoróforo (d).

20

Etapa 2: A continuación, se aplicó por encima de la superficie de la capa sacrificial la “capa estructural” de 2 µm de espesor del fotoresina SU-8. El fotoresina está en fase líquida y se deposita sobre el sustrato y se recubre la capa sacrificial por centrifugación a 3000 rpm. Seguidamente, se seca el sustrato a 90 °C por 5 minutos utilizando una 25 placa calefactora, como puede verse en la Figura 1, etapa 2, de deposición de fotoresina (c).

Etapa 3: A continuación, mediante fotolitografía, se determinó la forma y dimensiones del chip resultante. Para ello se expone el dispositivo a luz UV a través de la fotomáscara 30 ad hoc que ha sido fijada en una alineadora con una dosis de 445 mJ/cm<sup>2</sup>. Posteriormente, se utiliza un segundo secado a 90 °C por 5 min y el revelado final durante 1 min elimina todo el fotoresina no polimerizado, dejando el chip estructurado.

En la figura 8 se muestran imágenes de microscopía óptica de chips de fotoresina inmovilizados sobre el sustrato y la capa sacrificial soluble, antes de que se disuelva la capa sacrificial soluble y se liberen los chips de fotoresina.

- 5      Etapa 3a: Funcionalización de la capa estructural. Se expone una porción de la oblea con chips a plasma de oxígeno a 500 W durante 30 s y se sumerge posteriormente en una solución etanólica al 2% del silano heterobifuncional 3- glicidoxipropiltrimetoxisilano y se deja reaccionar durante 30 min. Posteriormente, la porción de oblea se lava con etanol y se seca a 100 °C durante 30 min. Al mismo tiempo, se incuba un sello

10     elastomérico de polidimetilsiloxano (PDMS) plano con una solución etanólica al 2% del fluoróforo fluoresceína sulfonada “Alexa Fluor 488” funcionalizado con una molécula del grupo amino. Después de secar el exceso de la solución del fluoróforo sobre el sello, éste se pone en contacto sobre los chips en la porción de oblea que está funcionalizada con el silano. Se aplica una ligera presión para que todo el sello esté en contacto con

15     los chips y se deja reaccionar durante 2 min. Los chips se caracterizan con microscopía de fluorescencia. Este proceso puede verse en la Figura 1, etapa 3a, de deposición de fluoróforo (e).

Finalmente, la etapa 4 de la Figura 1 representa el paso de eliminación de la capa sacrificial mediante la disolución de la capa sacrificial soluble en el caso de los chips de fotoresina SU-8 fabricados sobre PVOH soluble en agua. Para realizar este paso, se deposita una gota de 30 µL de agua desionizada o cualquier solución acuosa sobre la porción de oblea que contiene los chips y se esperan 10 minutos para que se disuelva la capa de PVOH a una temperatura de 21 °C. Opcionalmente, en caso de que los chips

20     se adhieran al sustrato, se puede agitar o dar golpes de ultrasonido para desprender los chips. Los chips resultantes por tanto son separados del sustrato inicial (4.1a). La superficie superior de los chips de SU-8 puede ser funcionalizada siguiendo el protocolo descrito en la etapa 3a (chips 4.2a y 4.3a).

30     Los chips resultantes fueron caracterizados mediante microscopía óptica y de fluorescencia, resultando ser de tamaños que abarcan diseños desde  $3 \times 10 \times 0.5 \mu\text{m}^3$  hasta  $85 \times 248 \times 5 \mu\text{m}^3$ .

A continuación, la pluralidad de chips se dispersa en agua desionizada o medio acuoso, 35     incluyéndose al menos un chip por cada 30 µL de agua desionizada, utilizando una

micropipeta para succionar la solución y depositarla en otro contenedor como un tubo eppendorf.

**Ejemplo 7**

5 **Impresión de chips SU-8 con impresora de inyección**

Siguiendo el ejemplo 6 de obtención de los chips de SU-8 que se fabricaron, se liberaron aproximadamente 20.000 chips de SU-8 en 1 mL de tinta de impresora (EPSON) y se inyectó la suspensión de tinta con chips directamente al cartucho de impresión de la impresora. La suspensión resultante se aplicó sobre la superficie de papel de impresión (80 g/m<sup>2</sup>) mediante una impresora de inyección de tinta (EPSON 104). Se imprimió el papel normalmente. El resultado de la impresión de la suspensión del presente ejemplo sobre el papel mediante la impresora EPSON 104 como se ha indicado arriba, se puede observar en la Figura 8 de microscopía óptica.

15 **Ejemplo 8**

**Tinta + chips de polímero SU-8 escritos con bolígrafo**

Los chips de SU-8 se fabricaron siguiendo el ejemplo 6 y se re-suspendieron en la tinta de un bolígrafo con una punta de 0.7 mm (MP Colours, Madrid Papel Import, S.L.). Con este bolígrafo se escribió sobre papel de impresora estándar (Ver Fig. 9)

20

**Ejemplo 9**

**Tinta + chips de polímero SU-8, chips de polímero SU-8 funcionalizados y pintados con pincel**

Los chips de SU-8 se fabricaron siguiendo el ejemplo 6, y se funcionalizaron con puntos cuánticos en su superficie. A continuación, se re-suspendieron en una pintura tipo acuarelas. Con un pincel se depositaron los chips funcionalizados sobre papel de impresora estándar (Ver Fig. 10). De la misma manera, se utilizó una suspensión de agua con chips de SU-8 de dimensiones más grandes (248×85 µm<sup>2</sup>) y depositados en papel de impresión con un pincel (Fig. 11).

30

## REIVINDICACIONES

1. Suspensión caracterizada por que comprende:

- una fase sólida que comprende

- chips seleccionados de entre materiales semiconductores, óxidos o nitruros aislantes o semiconductores, metales, materiales magnéticos, un polímero, una fotoresina, o cualquiera de sus combinaciones; donde los materiales semiconductores se seleccionan de entre silicio (Si), silicio amorfo, silicio monocristalino, polisilicio, germanio (Ge), arseniuro de galio (GaAs); donde los óxidos o nitruros aislantes o semiconductores se seleccionan de entre óxido de silicio, óxido de aluminio, nitruro de aluminio o nitruro de silicio; donde los metales se seleccionan de entre aluminio, oro, platino o cobre; donde los materiales magnéticos se seleccionan de entre Co, Ni, o NiCo; donde el polímero se selecciona de entre polidimetilsiloxano (PDMS), polimetilfenilsiloxano y polidifenilsiloxano; y donde el fotoresina se selecciona de entre SU-8, SU-8 2000, SU-8 3000, SU-8 GLM2060, SU-8 GLM3060, SU-8 GMC10xx, SU-8 GMJB10XX, SU-8 GM10XX; o cualquiera de sus combinaciones; donde los chips presentan un tamaño de entre 1 – 250 µm en su eje X, 1 – 250 µm en su eje Y, y 10 nm – 50 µm en su eje Z, dicho tamaño determinado por medidas de microscopía óptica, confocal, atómica o de barrido de electrones, o por medidas de haz de iones focalizado, perfilómetros o elipsómetros, y opcionalmente al menos una superficie planar de dichos chips está funcionalizada por al menos un compuesto seleccionado de entre moléculas, biomoléculas, nanopartículas, o cualquiera de sus combinaciones;

- una fase continua liquida o semilíquida como medio de suspensión de los chips seleccionado de entre tintas, pinturas o barnices;

- y donde el porcentaje en peso de la fase sólida es de entre 0,000001-60% respecto al peso total de la suspensión.

2. Suspensión según la reivindicación 1 donde los chips son de fotoresina y la forma y tamaño de los chips se han determinado mediante fotolitografía, habiendo sido previamente definida por una fotomáscara diseñada ad hoc.

3. Suspensión según la reivindicación 1, donde los chips son de silicio, y la forma y tamaño de los chips se han determinado mediante un proceso de grabado que estructura a los chips, habiendo sido previamente definidos por una fotomáscara diseñada ad hoc.

5

4. Suspensión según cualquiera de las reivindicaciones 1 a 3, donde el chip tiene forma de voladizo, puente, palanca, y cualquiera de sus combinaciones; y/o con forma geométrica plana, preferiblemente seleccionado de entre círculos, discos, coronas, triángulo, cuadrados, rectángulos, pentágonos, hexágonos, heptágonos, dodecágonos, paralelepípedos y formas planas irregulares.

10

5. Suspensión según la reivindicación 4, donde la forma del chip es de voladizo o pluralidad de voladizos.

15

6. Suspensión según cualquiera de las reivindicaciones 1 a 5, donde el chip tiene forma de disco y el tamaño de los chips en forma de disco es de 3 µm de diámetro × 0.5 µm y hasta 248 µm de diámetro × 5 µm de espesor.

20

7. Suspensión según cualquiera de las reivindicaciones 1 a 6, donde la fase continua líquida o semilíquida de la suspensión es una tinta seleccionada entre tintas de bolígrafo, de rotulador, de plumas, de sello polimérico o de impresoras.

25

8. Método de obtención de la suspensión según cualquiera de las reivindicaciones 1, 2, 4 a 7, caracterizadas por que los chips son de fotoresina y comprende las siguientes etapas secuenciales:

30

a) proveer un sustrato, preferiblemente el sustrato es de silicio, de vidrio, polimérico, o metálico;

b) recubrir el sustrato de la etapa (a), total o parcialmente, con una capa de material sacrificial, preferiblemente el material sacrificial se selecciona de entre polímeros solubles en agua, más preferiblemente se selecciona entre PVOH, PEG, PAA, PAM, HEC, PVP, PEO o alginato de sodio;

c) depositar sobre la capa sacrificial de la etapa (b) la capa estructural de un fotoresina seleccionado de entre SU-8, SU-8 2000, SU-8 3000, SU-8 GLM2060, SU-8 GLM3060, SU-8 GMC10xx, SU-8 GMJB10XX, SU-8 GM10XX, o cualquiera de sus combinaciones;

35

- d) definir el tamaño y forma de la capa estructural mediante fotolitografía, preferiblemente el tamaño y forma de la capa estructural se determina mediante el uso de una máscara diseñada ad hoc, para diseñar la forma que el tamaño y forma del chip;

- 5 e) opcionalmente, aplicar sobre la capa obtenida en la etapa (d) una capa superior de al menos un compuesto, preferiblemente el compuesto se selecciona de entre fluoróforos, anti-aglomerantes, anti-adherentes, biomoléculas, puntos cuánticos, o cualquiera de sus combinaciones;

- 10 f) liberar los chips obtenidos en la etapa (d) o (e) del sustrato mediante disolución de las mismas en agua o disolución acuosa, durante un tiempo de entre 5 y 60 min, a una temperatura de entre 5 y 80 °C; y

- 15 g) dispersar los chips obtenidos en la etapa (f), en una fase líquida o semilíquida seleccionada de entre tintas, pinturas o barnices, donde el porcentaje en peso de los chips está comprendido entre 0,000001-60% respecto al peso total de la suspensión.

9. Método según la reivindicación 8, donde posteriormente a la etapa (b) y previamente a la etapa (c) se añade una capa sobre al menos una parte de la superficie de la capa de material sacrificial de al menos un compuesto, preferiblemente el compuesto se selecciona de entre fluoróforos, anti-aglomerantes, anti-adherentes, biomoléculas, puntos cuánticos o cualquiera de sus combinaciones.

- 20

10. Método de obtención de la suspensión según cualquiera de las reivindicaciones 1, 25 3 a 7, caracterizado por que los chips son de materiales semiconductores o de óxidos o nitruros aislantes o semiconductores, o de metales o de materiales magnéticos o de polímeros o sus combinaciones, y comprende las siguientes etapas secuenciales:

- i. proveer un sustrato de silicio;

- 30 ii. oxidar térmicamente la superficie del sustrato de silicio de la etapa (i); o depositar óxido de silicio sobre el sustrato de la etapa (i) hasta obtener una capa sacrificial de óxido de silicio de 0,1-1 µm de espesor;

- o depositar una capa sacrificial de aluminio sobre el sustrato de la etapa (i), hasta obtener una capa sacrificial de Al de 0,1-1 µm de espesor

- iii. depositar sobre la capa sacrificial obtenida en la etapa (ii) una capa estructural de silicio amorfo, silicio monocristalino, polisilicio, germanio, arseniuro de galio, óxido de silicio, nitruro de silicio, aluminio, oro, platino, cobre, Co, Ni, NiCo, PDMS, polimetilfenilsiloxano y polidifenilsiloxano o sus combinaciones;

- 5 iv. definir el tamaño y forma de la capa estructural mediante eliminación parcial de la capa estructural por un proceso de grabado, preferiblemente el tamaño y forma de la capa estructural se determina mediante el uso de una máscara diseñada ad hoc, para diseñar la forma y el tamaño de los chips;

- 10 v. opcionalmente, aplicar sobre la capa estructural obtenida en (iii) una capa superior de funcionalización química mediante al menos un compuesto químico, preferiblemente seleccionado de entre compuestos de moléculas, biomoléculas, o nanopartículas, o sus combinaciones; y

- 15 vi. opcionalmente aplicar una o varias capas estructurales de silicio, de óxidos o nitruros aislantes o semiconductores, de metales, de materiales magnéticos, fotoresinas, o cualquiera de sus combinaciones; y

- 20 vii. liberar los chips obtenidos en la etapa (iv) o (v) del sustrato, mediante grabado con vapores de ácido, preferiblemente vapores de ácido hidrofluorhídrico, de la capa sacrificial de óxido de silicio incorporada o generada en la etapa (ii), que servía de interfaz entre el sustrato y el chip a fabricar, hasta eliminar la capa sacrificial totalmente; o mediante grabado con una solución de KOH al 50%, de la capa sacrificial de Al incorporada en la etapa (ii), que servía de interfaz entre el sustrato y el chip a fabricar, hasta eliminar la capa sacrificial totalmente y

- 25 viii. dispersar los chips obtenidos en la etapa (vi), en una fase líquida o semilíquida seleccionada de entre tintas, pinturas o barnices, donde el porcentaje en peso de la fase sólida es de entre 0,000001-60% respecto al peso total de la suspensión.

- 30 11. Método según la reivindicación 10, donde posteriormente a la etapa (ii) y previamente a la etapa (iii) se añade una capa de un compuesto parcial o totalmente sobre la superficie de la capa sacrificial, preferiblemente el compuesto seleccionado de entre fluoróforos, anti-aglomerantes, anti-adherentes, biomoléculas, puntos cuánticos, o cualquiera de sus combinaciones.

- 35

12. Uso de la suspensión descrita según cualquiera de las reivindicaciones 1 a 7, para trasferir los chips comprendidos en la suspensión a superficies espacial y geométricamente complejas.

- 5    13. Un procedimiento para transferir los chips comprendidos en la suspensión según cualquiera de las reivindicaciones 1 a 7 a una superficie caracterizado por que comprende una etapa de:

- depositar la suspensión descrita según cualquiera de las reivindicaciones 1 a 7 sobre la superficie mediante medios de escritura, pintura o impresión,

- 10    donde los medios de escritura, pintura o impresión comprenden canales para distribuir la suspensión a la superficie, y donde los chips de la suspensión tienen un tamaño menor que los canales del dispositivo de escritura, pintura o impresión.

14. Uso de la suspensión de acuerdo con cualquiera de las reivindicaciones 1 a 7 para

- 15    la determinación de las dimensiones de los canales de un dispositivo de escritura, pintura o impresión, preferiblemente la suspensión comprende chips en forma de discos.

15. Un procedimiento para determinar las dimensiones de los canales de un dispositivo

- 20    de escritura, pintura o impresión caracterizado por que comprende una etapa de hacer pasar la suspensión según cualquiera de las reivindicaciones 1 a 7 por un canal de un dispositivo de escritura, pintura o impresión, donde los chips comprendidos en la suspensión tienen un tamaño mayor que el canal del dispositivo y donde dichos chips son incapaces de atravesar el canal y se rompen.

- 25

16. Un dispositivo capaz de aplicar o suministrar una suspensión sobre superficies espacial y geométricamente complejas por un canal de salida, donde dicho dispositivo comprende la suspensión según cualquiera de las reivindicaciones 1 a 7 y donde el canal de salida tiene un diámetro mayor a la mayor de las dimensiones

- 30    de los chips de la suspensión.

17. El dispositivo según la reivindicación 16, donde dicho dispositivo se selecciona de entre un dispositivo de escritura, pintura o impresión, preferiblemente de entre una impresora inkjet, un bolígrafo, una pluma, un sello polimérico, o un pincel.

Fig. 1

Fig. 2

Fig. 3

**Fig. 4**

ES 3 014 635 A1

**Fig. 5**

**Fig. 5 Continuación**

Fig. 6

Fig. 7

Fig. 8

Fig. 9

**Fig. 10**

Fig. 11

(21) N.º solicitud: 202330859

(22) Fecha de presentación de la solicitud: 18.10.2023

(32) Fecha de prioridad:

## INFORME SOBRE EL ESTADO DE LA TECNICA

(5) Int. Cl.: C09D11/30 (2014.01)

### DOCUMENTOS RELEVANTES

| Categoría | 66                                                                                                                                                                                                                                          | Documentos citados | Reivindicaciones afectadas |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------------|

| X         | WO 2008039791 A1 (SOMARK INNOVATIONS INC et al.) 03/04/2008, resumen, párrafos [0038]-[0053].                                                                                                                                               |                    | 1-4, 7-13, 16,17           |

| A         | WO 2022018314 A1 (CSIC) 27/01/2022, resumen y ejemplos.                                                                                                                                                                                     |                    | 1-17                       |

| A         | WO 2011044708 A1 (BIOCARTIS SA et al.) 21/04/2011, resumen; apartados [0030]- [0038].                                                                                                                                                       |                    | 1-17                       |

| A         | AGUSIL, J.P., et al., Multidimensional Anisotropic Architectures on Polymeric Microparticles, Small, 31/10/2020, Vol. 16, Nº 46, Páginas e2004691, ISSN 1613-6829 (Electronic), <DOI: doi:10.1002/smll.202004691 pubmed:33079486>; resumen. |                    | 1-17                       |

| A         | US 2015091210 A1 (CHEN JIUN-TAI et al.) 02/04/2015, resumen.                                                                                                                                                                                |                    | 1-17                       |

#### Categoría de los documentos citados

X: de particular relevancia

Y: de particular relevancia combinado con otro/s de la misma categoría

A: refleja el estado de la técnica

O: referido a divulgación no escrita

P: publicado entre la fecha de prioridad y la de presentación de la solicitud

E: documento anterior, pero publicado después de la fecha de presentación de la solicitud

#### El presente informe ha sido realizado

para todas las reivindicaciones

para las reivindicaciones nº:

|                                                |                                 |               |

|------------------------------------------------|---------------------------------|---------------|

| Fecha de realización del informe<br>13.09.2024 | Examinador<br>M. d. García Poza | Página<br>1/2 |

|------------------------------------------------|---------------------------------|---------------|

Documentación mínima buscada (sistema de clasificación seguido de los símbolos de clasificación)

C09D

Bases de datos electrónicas consultadas durante la búsqueda (nombre de la base de datos y, si es posible, términos de búsqueda utilizados)

INVENES, EPODOC, WPI, NPL, MEDLINE