### (19) 日本国特許庁(JP)

# 再 公 表 特 許(A1)

(11) 国際公開番号

W02013/061679

発行日 平成27年4月2日(2015.4.2)

(43) 国際公開日 平成25年5月2日(2013.5.2)

(51) Int. Cl. FIテーマコード (参考) HO3F 3/195 (2006, 01) H03F 5J500 3/195

H03F 3/213 (2006, 01)H03F 3/213

#### 審查請求 有 予備審查請求 未請求 (全 51 頁)

出願番号 特願2013-540690 (P2013-540690) (71) 出願人 000006013 (21) 国際出願番号 PCT/JP2012/071423 三菱電機株式会社 (22) 国際出願日 平成24年8月24日 (2012.8.24) 東京都千代田区丸の内二丁目7番3号 特願2011-236119 (P2011-236119) (31) 優先権主張番号 (74)代理人 100123434 平成23年10月27日 (2011.10.27) 弁理士 田澤 英昭 (32) 優先日 (33) 優先権主張国 日本国(JP) (74)代理人 100101133 弁理士 濱田 初音 (74)代理人 100173934 弁理士 久米 輝代 (74)代理人 100156351 弁理士 河村 秀央 (72) 発明者 向井 謙治 東京都千代田区丸の内二丁目7番3号 三 菱電機株式会社内 最終頁に続く

(54) 【発明の名称】高周波増幅器モジュール及び高周波増幅器モジュールユニット

### (57)【要約】

RF入力端子1から入力されたRF信号を増幅するド ライバ段増幅器3と、そのドライバ段増幅器3により増 幅された信号を増幅し、増幅後の信号を R F 出力端子 7 に出力する最終段増幅器5とを備え、そのドライバ段増 幅器3がシリコン基板11上に形成され、その最終段増 幅器5がガリウム砒素基板上に形成されている。これに より、モジュールの全体がガリウム砒素基板71上に形 成されている場合と同等の高周波特性を維持しながら、 低コスト化を実現することができる。

- 2... INPUT MATCHING CIRCUIT

4... INTER-STAGE MATCHING CIRCUIT

6... OUTPUT MATCHING CIRCUIT

10... BIAS CIRCUIT

11... SILICON SUBSTRATE

AA... RF OUTPUT

BB... VCC POWER SUPPLY

CC... RF INPUT

#### 【特許請求の範囲】

### 【請求項1】

入力端子から入力された信号を増幅する多段構成のドライバ段増幅器と、上記ドライバ段増幅器により増幅された信号を増幅し、増幅後の信号を出力端子に出力する最終段増幅器とを備えた高周波増幅器モジュールにおいて、

上記ドライバ段増幅器がシリコン基板上に形成され、上記最終段増幅器がガリウム砒素 基板上に形成されていることを特徴とする高周波増幅器モジュール。

### 【請求項2】

一端がドライバ段増幅器の入力側に接続され、他端が最終段増幅器の出力側に接続されているバイパス経路と、上記バイパス経路上に配置されているバイパス増幅器とを備え、

上記バイパス増幅器がシリコン基板上に形成されていることを特徴とする請求項 1 記載の高周波増幅器モジュール。

### 【請求項3】

一端がドライバ段増幅器の出力側に接続され、他端が最終段増幅器の出力側に接続されているバイパス経路と、上記バイパス経路上に配置され、上記最終段増幅器よりサイズが小さいバイパス増幅器とを備え、

上記バイパス増幅器がシリコン基板上に形成されていることを特徴とする請求項1記載の高周波増幅器モジュール。

## 【請求項4】

一端がドライバ段増幅器の入力側に接続され、他端が最終段増幅器の出力側に接続されているバイパス経路と、上記バイパス経路上に配置され、上記入力端子から入力された信号を増幅する多段構成のバイパスドライバ段増幅器と、上記バイパス経路上配置され、上記バイパスドライバ段増幅器により増幅された信号を増幅し、増幅後の信号を出力端子に出力するバイパス最終段増幅器とを備え、

上記バイパスドライバ段増幅器がシリコン基板上に形成され、上記バイパス最終段増幅器がガリウム砒素基板上に形成されていることを特徴とする請求項 1 記載の高周波増幅器モジュール。

### 【請求項5】

一端がドライバ段増幅器の入力側に接続され、他端がドライバ段増幅器の出力側に接続されている第1のバイパス経路と、一端が最終段増幅器の入力側に接続され、他端が上記最終段増幅器の出力側に接続されている第2のバイパス経路と、上記第1のバイパス経路上に配置され、上記ドライバ段増幅器よりサイズが小さいバイパス増幅器とを備え、

上記バイパス増幅器がシリコン基板上に形成されていることを特徴とする請求項 1 記載の高周波増幅器モジュール。

### 【請求項6】

ガリウム砒素基板上に形成されている最終段増幅器が、ドライバ段増幅器の出力側に複数並列に接続されていることを特徴とする請求項1記載の高周波増幅器モジュール。

### 【請求項7】

一端がドライバ段増幅器の出力側に接続され、他端が最終段増幅器の出力側に接続されているバイパス経路を備えていることを特徴とする請求項 1 記載の高周波増幅器モジュール。

#### 【請求項8】

ドライバ段増幅器の入力側に入力整合回路、上記ドライバ段増幅器と最終段増幅器の間に段間整合回路、上記最終段増幅器の出力側に出力整合回路が配置されており、上記入力整合回路、上記段間整合回路及び上記出力整合回路の一部又は全部がガリウム砒素基板上に形成されていることを特徴とする請求項1記載の高周波増幅器モジュール。

### 【請求項9】

ドライバ段増幅器の入力側に入力整合回路、上記ドライバ段増幅器と最終段増幅器の間に段間整合回路、上記最終段増幅器の出力側に出力整合回路が配置されており、上記入力整合回路、上記段間整合回路及び上記出力整合回路の一部又は全部がシリコン基板上又は

10

20

30

30

40

外 部 の モ ジュ ー ル 上 に 形 成 さ れ て い る こ と を 特 徴 と す る 請 求 項 1 記 載 の 高 周 波 増 幅 器 モ ジュ ー ル 。

## 【請求項10】

ドライバ段増幅器及び最終段増幅器が配置されている主経路又はバイパス経路のうち、信号を流す経路を選択する経路切替用スイッチが設けられており、上記経路切替用スイッチがシリコン基板上に形成されていることを特徴とする請求項2記載の高周波増幅器モジュール。

### 【請求項11】

経路切替用スイッチを制御する切替制御回路が設けられており、上記切替制御回路がシリコン基板上に形成されていることを特徴とする請求項10記載の高周波増幅器モジュール。

【請求項12】

複数の最終段増幅器のうち、ドライバ段増幅器により増幅された信号を与える最終段増幅器を切り替える経路切替用スイッチが設けられており、上記経路切替用スイッチがシリコン基板上に形成されていることを特徴とする請求項 6 記載の高周波増幅器モジュール。

経路切替用スイッチを制御する切替制御回路が設けられており、上記切替制御回路がシリコン基板上に形成されていることを特徴とする請求項12記載の高周波増幅器モジュール。

【請求項14】

【請求項13】

ドライバ段増幅器及び最終段増幅器のバイアスを設定するバイアス回路が設けられており、上記バイアス回路がシリコン基板上に形成されていることを特徴とする請求項 1 記載の高周波増幅器モジュール。

【請求項15】

ドライバ段増幅器及び最終段増幅器の電源電圧を制御する電源電圧制御回路が設けられており、上記電源電圧制御回路がシリコン基板上に形成されていることを特徴とする請求項 1 記載の高周波増幅器モジュール。

【請求項16】

ガリウム砒素基板上に形成されており、バイアス回路により設定されるバイアスを調整するバイアス調整手段を備えていることを特徴とする請求項14記載の高周波増幅器モジュール。

【請求項17】

バイアス調整手段が、ガリウム砒素基板の温度を検知する温度検知回路で構成されており、上記温度検知回路が、上記ガリウム砒素基板の温度に応じてバイアス回路により設定されるバイアスを調整することを特徴とする請求項16記載の高周波増幅器モジュール。

【請求項18】

バイアス調整手段が、バイポーラトランジスタを含むカレントミラー型のバイアス回路 で構成されていることを特徴とする請求項16記載の高周波増幅器モジュール。

【請求項19】

バイアス調整手段が、バイポーラトランジスタを含むエミッタフォロア型のバイアス回路で構成されていることを特徴とする請求項16記載の高周波増幅器モジュール。

【請求項20】

請求項1記載の高周波増幅器モジュールが複数個実装されている高周波増幅器モジュールユニット。

【発明の詳細な説明】

【技術分野】

[ 0 0 0 1 ]

この発明は、例えば、高周波信号であるRF信号を増幅する高周波増幅器モジュールと、その高周波増幅器モジュールが複数個実装されている高周波増幅器モジュールユニットとに関するものである。

20

10

30

40

#### 【背景技術】

### [0002]

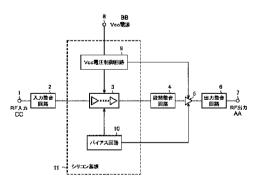

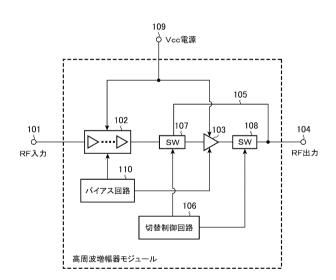

図12は以下の非特許文献1に開示されている従来の高周波増幅器モジュールを示す構成図である。

従来の高周波増幅器モジュールでは、RF入力端子101からRF信号が入力されると、多段構成のドライバ段増幅器102がRF信号を増幅し、最終段増幅器103がドライバ段増幅器102により増幅されたRF信号を更に増幅して、増幅後のRF信号をRF出力端子104に出力する。

### [0003]

ただし、最終段増幅器103と並列にバイパス経路105が設けられており、切替制御回路106の制御の下で、切替スイッチ107の出力先がバイパス経路105側に切り替えられ、切替スイッチ108がオフの状態になっていれば、ドライバ段増幅器102により増幅されたRF信号は、最終段増幅器103では増幅されずに、バイパス経路105を経由してRF出力端子104から出力される。

なお、ドライバ段増幅器102及び最終段増幅器103の電源電圧は、Vcc電源109から供給されており、ドライバ段増幅器102及び最終段増幅器103のバイアスは、バイアス回路110により設定されている。

### [0004]

高周波増幅器モジュールでは、各構成要素がシリコン基板上に形成されることが一般的であったが、非特許文献1に開示されている高周波増幅器モジュールでは、高効率化を図るために、ドライバ段増幅器102や最終段増幅器103を高周波特性に優れている化合物半導体であるガリウム砒素基板上に形成するようにしている。

また、切替制御回路106やバイアス回路110についても、モジュール全体のサイズの要求からガリウム砒素基板上に形成するようにしている。

即ち、非特許文献 1 に開示されている高周波増幅器モジュールでは、モジュールの全体をガリウム砒素基板上に形成するようにしている。

## 【先行技術文献】

#### 【非特許文献】

### [0005]

【非特許文献 1】G.Hau et al., "Multi-Mode WCDMA Power Amplifier Module with Improved Low-Power Efficiency using Stage-Bypass," IEEE RFIC Symposium Dig., pp.1 63-166, June 2010

### 【発明の概要】

## 【発明が解決しようとする課題】

### [0006]

従来の高周波増幅器モジュールは以上のように構成されているので、モジュールの全体がガリウム砒素基板上に形成されて高効率化が図られている。しかし、高周波特性に優れている化合物半導体であるガリウム砒素基板はチップ単価が高いため、製造コストが高価になってしまう課題があった。

### [0007]

この発明は上記のような課題を解決するためになされたもので、モジュールの全体がガリウム砒素基板上に形成されている場合と同等の高周波特性を維持しながら、低コスト化を実現することができる高周波増幅器モジュール及び高周波増幅器モジュールユニットを得ることを目的とする。

### 【課題を解決するための手段】

## [0008]

この発明に係る高周波増幅器モジュールは、入力端子から入力された信号を増幅する多段構成のドライバ段増幅器と、そのドライバ段増幅器により増幅された信号を増幅し、増幅後の信号を出力端子に出力する最終段増幅器とを備え、そのドライバ段増幅器がシリコン基板上に形成され、その最終段増幅器がガリウム砒素基板上に形成されているようにし

10

20

30

30

40

たものである。

【発明の効果】

[0009]

この発明によれば、入力端子から入力された信号を増幅する多段構成のドライバ段増幅 器と、そのドライバ段増幅器により増幅された信号を増幅し、増幅後の信号を出力端子に 出力する最終段増幅器とを備え、そのドライバ段増幅器がシリコン基板上に形成され、そ の最終段増幅器がガリウム砒素基板上に形成されているように構成したので、モジュール の全体がガリウム砒素基板上に形成されている場合と同等の高周波特性を維持しながら、 低コスト化を実現することができる効果がある。

【図面の簡単な説明】

[ 0 0 1 0 ]

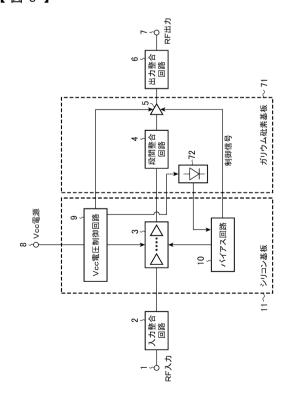

- 【図1】この発明の実施の形態1による高周波増幅器モジュールを示す構成図である。

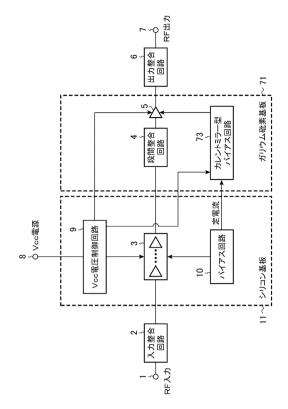

- 【 図 2 】 こ の 発 明 の 実 施 の 形 態 2 に よ る 高 周 波 増 幅 器 モ ジ ュ ー ル を 示 す 構 成 図 で あ る 。

- 【図3】この発明の実施の形態3による高周波増幅器モジュールを示す構成図である。

- 【 図 4 】 こ の 発 明 の 実 施 の 形 態 4 に よ る 高 周 波 増 幅 器 モ ジ ュ ー ル を 示 す 構 成 図 で あ る 。

- 【 図 5 】 こ の 発 明 の 実 施 の 形 態 5 に よ る 高 周 波 増 幅 器 モ ジ ュ ー ル を 示 す 構 成 図 で あ る 。

- 【図6】この発明の実施の形態6による高周波増幅器モジュールを示す構成図である。

- 【 図 7 】 こ の 発 明 の 実 施 の 形 態 7 に よ る 高 周 波 増 幅 器 モ ジ ュ ー ル ユ ニ ッ ト を 示 す 構 成 図 で

- 【 図 8 】 こ の 発 明 の 実 施 の 形 態 8 に よ る 高 周 波 増 幅 器 モ ジ ュ ー ル ユ ニ ッ ト を 示 す 構 成 図 で

- 【 図 9 】 こ の 発 明 の 実 施 の 形 態 9 に よ る 高 周 波 増 幅 器 モ ジ ュ ー ル を 示 す 構 成 図 で あ る 。

- 【図10】この発明の実施の形態10による高周波増幅器モジュールを示す構成図である

- 【 図 1 1 】 こ の 発 明 の 実 施 の 形 態 1 1 に よ る 高 周 波 増 幅 器 モ ジ ュ ー ル を 示 す 構 成 図 で あ る

- 【図12】非特許文献1に開示されている従来の高周波増幅器モジュールを示す構成図で ある。

【発明を実施するための形態】

[ 0 0 1 1 ]

以下、この発明をより詳細に説明するために、この発明を実施するための形態について 、添付の図面に従って説明する。

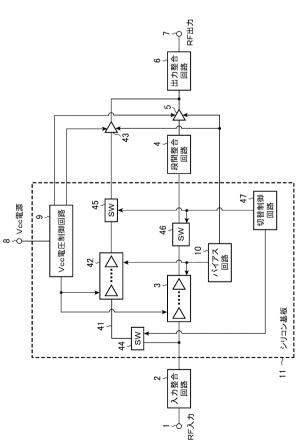

実施の形態1.

- 図1はこの発明の実施の形態1による高周波増幅器モジュールを示す構成図である。

- 図1において、RF入力端子1はRF信号を入力する端子である。

入力整合回路2はドライバ段増幅器3の入力側の整合回路である。

[0012]

ドライバ段増幅器3は1~N段の増幅素子から構成されている多段の増幅器であり、R F 入力端子 1 から入力された R F 信号を増幅し、増幅後の R F 信号を段間整合回路 4 に出 力するデバイスである。

段間整合回路4はドライバ段増幅器3と最終段増幅器5の間に配置されている整合回路 である。

[0013]

最終段増幅器5はドライバ段増幅器3により増幅されたRF信号を更に増幅して、増幅 後のRF信号を出力整合回路6に出力するデバイスである。

出力整合回路6は最終段増幅器5の出力側の整合回路である。

RF出力端子7は最終段増幅器5により増幅されたRF信号を出力する端子である。

- Vcc電源8は電源電圧Vccを出力する電源である。

- Vcc電圧制御回路9はドライバ段増幅器3及び最終段増幅器5のドレイン又はコレク

10

20

30

40

夕に供給する直流電圧を制御する電源電圧制御回路である。

なお、ドライバ段増幅器 3 及び最終段増幅器 5 のドレイン又はコレクタに供給する直流電圧は、Vcc電源 8 から出力される電源電圧Vccと同じ電圧であってもよいし、その電源電圧Vccを可変した電圧であってもよい。

バイアス回路 1 0 はドライバ段増幅器 3 及び最終段増幅器 5 のゲート又はベースに供給する直流電圧又は直流電流を制御することで、ドライバ段増幅器 3 及び最終段増幅器 5 のバイアスを設定する回路である。

### [0015]

シリコン基板11はシリコンで形成されている基板であり、シリコン基板11にはドライバ段増幅器3、Vcc電圧制御回路9及びバイアス回路10が形成されている。

入力整合回路 2 、段間整合回路 4 及び出力整合回路 6 と最終段増幅器 5 は、ガリウム砒素基板上に形成されている。

#### [0016]

次に動作について説明する。

まず、Vcc電圧制御回路9は、Vcc電源8から電源電圧Vccの供給を受けると、ドライバ段増幅器3及び最終段増幅器5のドレイン又はコレクタに供給する直流電圧を制御することで、ドライバ段増幅器3及び最終段増幅器5を駆動可能な状態に設定する。

バイアス回路10は、ドライバ段増幅器3及び最終段増幅器5におけるRF信号の増幅率等を所望値に設定するため、例えば、外部から与えられる増幅率の設定情報等にしたがって、ドライバ段増幅器3及び最終段増幅器5のゲート又はベースに供給する直流電圧又は直流電流を制御することで、ドライバ段増幅器3及び最終段増幅器5のバイアスを設定する。

### [0017]

バイアス回路10によりドライバ段増幅器3及び最終段増幅器5のバイアスが設定されている状態で、RF入力端子1からRF信号が入力されると、そのRF信号は入力整合回路2を通過してドライバ段増幅器3に入力される。

ドライバ段増幅器 3 は、入力整合回路 2 を通過してきた R F 信号を増幅し、増幅後の R F 信号を段間整合回路 4 に出力する。

### [0018]

ドライバ段増幅器 3 から出力された R F 信号は、段間整合回路 4 を通過して最終段増幅器 5 に入力される。

最終段増幅器 5 は、段間整合回路 4 を通過してきた R F 信号を増幅し、増幅後の R F 信号を出力整合回路 6 に出力する。

最終段増幅器 5 から出力された R F 信号は、出力整合回路 6 を通過して、 R F 出力端子 7 から外部に出力される。

#### [ 0 0 1 9 ]

図1の高周波増幅器モジュールでは、ドライバ段増幅器3がシリコン基板11上に形成され、最終段増幅器5がガリウム砒素基板上に形成されているが、高周波特性に支配的な増幅器は最終段増幅器5であり、ドライバ段増幅器3は高周波特性に特段の影響を与えない増幅器である。

このため、高周波特性に優れているガリウム砒素基板上に最終段増幅器 5 を形成すれば、ドライバ段増幅器 3 をシリコン基板 1 1 上に形成しても、モジュールの全体がガリウム砒素基板上に形成されている場合と同等の高周波特性を維持することができる。

このように、ドライバ段増幅器 3 をシリコン基板 1 1 上に形成することで、ガリウム砒素基板で形成するチップの面積を削減することができるため、低コスト化を実現することができる。

### [0020]

この実施の形態 1 では、入力整合回路 2 、段間整合回路 4 及び出力整合回路 6 をガリウム砒素基板上に形成しているものを示したが、その全てをガリウム砒素基板上に形成せずに、その一部をシリコン基板 1 1 (あるいは、外部のモジュール)上に形成するようにし

10

20

30

40

ても、モジュールの全体がガリウム砒素基板上に形成されている場合と同等の高周波特性 を維持することができる。

例えば、入力整合回路 2 と段間整合回路 4 をシリコン基板 1 1 (あるいは、外部のモジュール)上に形成して、出力整合回路 6 をガリウム砒素基板上に形成するようにしてもよいし、入力整合回路 2 をシリコン基板 1 1 (あるいは、外部のモジュール)上に形成して、段間整合回路 4 と出力整合回路 6 をガリウム砒素基板上に形成するようにしてもよい。また、出力整合回路 6 をシリコン基板 1 1 (あるいは、外部のモジュール)上に形成して、入力整合回路 2 と段間整合回路 4 をガリウム砒素基板上に形成するようにしてもよい

### [0021]

なお、この実施の形態 1 では、高周波増幅器モジュールが入力整合回路 2 、段間整合回路 4 及び出力整合回路 6 を実装しているものを示したが、入力整合回路 2 、段間整合回路 4 及び出力整合回路 6 の一部又は全部を実装していない高周波増幅器モジュールであってもよい。

### [0022]

実施の形態2.

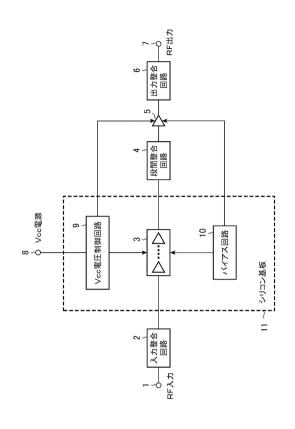

図2はこの発明の実施の形態2による高周波増幅器モジュールを示す構成図であり、図において、図1と同一符号は同一または相当部分を示すので説明を省略する。

バイパス経路21は一端がドライバ段増幅器3の入力側に接続され、他端が最終段増幅器5の出力側に接続されている経路である。

この実施の形態 2 では、ドライバ段増幅器 3 及び最終段増幅器 5 が配置されている経路を「主経路」と称する。

バイパス増幅器 2 2 はバイパス経路 2 1 上に配置されているドライバ段増幅器であり、バイパス増幅器 2 2 のサイズは、信号の増幅率が、ドライバ段増幅器 3 及び最終段増幅器 5 のトータルの増幅率より小さくなるように設計されている。

### [0023]

経路切替用スイッチ 2 3 はバイパス経路 2 1 上で、バイパス増幅器 2 2 の入力側に配置され、切替制御回路 2 6 の制御の下でオン / オフするスイッチである。

経路切替用スイッチ 2 4 はバイパス経路 2 1 上で、バイパス増幅器 2 2 の出力側に配置され、切替制御回路 2 6 の制御の下でオン / オフするスイッチである。

経路切替用スイッチ 2 5 は主経路上で、ドライバ段増幅器 3 の出力側に配置され、切替制御回路 2 6 の制御の下でオン / オフするスイッチである。

#### [0024]

切替制御回路 2 6 は経路切替用スイッチ 2 3 , 2 4 , 2 5 をオン / オフすることで、 R F 信号を流す経路として、主経路又はバイパス経路 2 1 を選択する回路である。

この実施の形態 2 では、バイパス増幅器 2 2 、経路切替用スイッチ 2 3 , 2 4 , 2 5 及び切替制御回路 2 6 がシリコン基板 1 1 上に形成されている。

### [0025]

次に動作について説明する。

まず、Vcc電圧制御回路9は、Vcc電源8から電源電圧Vccの供給を受けると、ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器22のドレイン又はコレクタに供給する直流電圧を制御することで、ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器22を駆動可能な状態に設定する。

バイアス回路10は、ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器22におけるRF信号の増幅率等を所望値に設定するため、例えば、外部から与えられる増幅率の設定情報等にしたがって、ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器22のゲート又はベースに供給する直流電圧又は直流電流を制御することで、ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器22のバイアスを設定する。

### [0026]

バイアス回路10によりドライバ段増幅器3、最終段増幅器5及びバイパス増幅器22

10

20

30

40

のバイアスが設定されている状態で、RF入力端子1からRF信号が入力されると、その RF信号は入力整合回路2を通過する。

切替制御回路26は、例えば、外部からRF信号を低出力電力で駆動する旨を示す制御 情報を入力すると、経路切替用スイッチ23,24をオンに制御して、経路切替用スイッ チ25をオフに制御することで、RF信号を流す経路として、バイパス経路21を選択す る。

#### [0027]

これにより、入力整合回路2を通過したRF信号がバイパス増幅器22に入力される。 バイパス増幅器22は、入力整合回路2を通過してきたRF信号を増幅し、増幅後のR F信号を出力整合回路6に出力する。

バイパス増幅器22から出力されたRF信号は、出力整合回路6を通過して、RF出力 端子フから外部に出力される。

#### [0028]

切替制御回路26は、例えば、外部からRF信号を高出力電力で駆動する旨を示す制御 情 報 を 入 力 す る と 、 経 路 切 替 用 ス イ ッ チ 2 3 , 2 4 を オ フ に 制 御 し て 、 経 路 切 替 用 ス イ ッ チ25をオンに制御することで、RF信号を流す経路として、主経路を選択する。

これにより、入力整合回路2を通過したRF信号がドライバ段増幅器3に入力される。 ドライバ段増幅器3は、入力整合回路2を通過してきたRF信号を増幅し、増幅後のR F信号を段間整合回路 4 に出力する。

### [0029]

ドライバ段増幅器3から出力されたRF信号は、段間整合回路4を通過して最終段増幅 器5に入力される。

最終段増幅器5は、段間整合回路4を通過してきたRF信号を増幅し、増幅後のRF信 号を出力整合回路6に出力する。

最終段増幅器5から出力されたRF信号は、出力整合回路6を通過して、RF出力端子 7から外部に出力される。

### [0030]

図 2 の 高 周 波 増 幅 器 モ ジュ ー ル で は 、 ド ラ イ バ 段 増 幅 器 3 及 び バ イ パ ス 増 幅 器 2 2 が シ リコン基板11上に形成され、最終段増幅器5がガリウム砒素基板上に形成されているが 、高周波特性に支配的な増幅器は最終段増幅器5であり、ドライバ段増幅器3及びバイパ ス増幅器22は高周波特性に特段の影響を与えない増幅器である。

このため、高周波特性に優れているガリウム砒素基板上に最終段増幅器5を形成すれば 、ドライバ段増幅器3及びバイパス増幅器22をシリコン基板11上に形成しても、モジ ュールの全体がガリウム砒素基板上に形成されている場合と同等の高周波特性を維持する ことができる。

このように、ドライバ段増幅器3及びバイパス増幅器22をシリコン基板11上に形成 することで、ガリウム砒素基板で形成するチップの面積を削減することができるため、低 コスト化を実現することができる。

### [0031]

なお、この実施の形態 2 では、経路切替用スイッチ 2 3 , 2 4 , 2 5 がシリコン基板 1 1上に形成されているが、経路切替用スイッチ23,24,25がガリウム砒素基板上に 形成されていてもよい。

また、この実施の形態2では、高周波増幅器モジュールが入力整合回路2、段間整合回 路4及び出力整合回路6を実装しているものを示したが、入力整合回路2、段間整合回路 4 及び出力整合回路 6 の一部又は全部を実装していない高周波増幅器モジュールであって もよい。

### [0032]

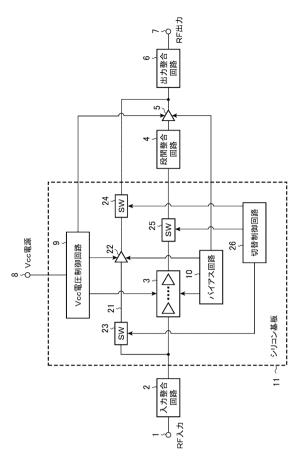

### 実施の形態3.

図3はこの発明の実施の形態3による高周波増幅器モジュールを示す構成図であり、図 において、図1と同一符号は同一または相当部分を示すので説明を省略する。

10

20

30

40

バイパス経路31は一端がドライバ段増幅器3の出力側に接続され、他端が最終段増幅器5の出力側に接続されている経路である。

この実施の形態 3 では、ドライバ段増幅器 3 及び最終段増幅器 5 が配置されている経路を「主経路」と称する。

バイパス増幅器 3 2 はバイパス経路 3 1 上に配置されている最終段増幅器であり、バイパス増幅器 3 2 のサイズは、最終段増幅器 5 のサイズより小さくなるように設計されている。

### [ 0 0 3 3 ]

経路切替用スイッチ33はバイパス経路31上で、バイパス増幅器32の入力側に配置され、切替制御回路36の制御の下でオン/オフするスイッチである。

経路切替用スイッチ34はバイパス経路31上で、バイパス増幅器32の出力側に配置され、切替制御回路36の制御の下でオン/オフするスイッチである。

経路切替用スイッチ 3 5 は主経路上で、ドライバ段増幅器 3 の出力側に配置され、切替制御回路 3 6 の制御の下でオン / オフするスイッチである。

### [0034]

切替制御回路 3 6 は経路切替用スイッチ 3 3 , 3 4 , 3 5 をオン / オフすることで、 R F 信号を流す経路として、主経路又はバイパス経路 3 1 を選択する回路である。

この実施の形態3では、バイパス増幅器32、経路切替用スイッチ33,34,35及び切替制御回路36がシリコン基板11上に形成されている。

### [0035]

次に動作について説明する。

まず、Vcc電圧制御回路9は、Vcc電源8から電源電圧Vccの供給を受けると、ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器32のドレイン又はコレクタに供給する直流電圧を制御することで、ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器32を駆動可能な状態に設定する。

バイアス回路10は、ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器32におけるRF信号の増幅率等を所望値に設定するため、例えば、外部から与えられる増幅率の設定情報等にしたがって、ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器32のゲート又はベースに供給する直流電圧又は直流電流を制御することで、ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器32のバイアスを設定する。

#### [0036]

バイアス回路10によりドライバ段増幅器3、最終段増幅器5及びバイパス増幅器32のバイアスが設定されている状態で、RF入力端子1からRF信号が入力されると、そのRF信号は入力整合回路2を通過する。

ドライバ段増幅器3は、入力整合回路2を通過してきたRF信号を増幅する。

#### [0037]

切替制御回路 3 6 は、例えば、外部から R F 信号を低出力電力で駆動する旨を示す制御情報を入力すると、経路切替用スイッチ 3 3 , 3 4 をオンに制御して、経路切替用スイッチ 3 5 をオフに制御することで、 R F 信号を流す経路として、バイパス経路 3 1 を選択する。

これにより、ドライバ段増幅器 3 により増幅された R F 信号がバイパス増幅器 3 2 に入 力される。

バイパス増幅器 3 2 は、入力整合回路 2 を通過してきた R F 信号を増幅し、増幅後の R F 信号を出力整合回路 6 に出力する。

バイパス増幅器32から出力されたRF信号は、出力整合回路6を通過して、RF出力端子7から外部に出力される。

### [0038]

切替制御回路36は、例えば、外部からRF信号を高出力電力で駆動する旨を示す制御情報を入力すると、経路切替用スイッチ33,34をオフに制御して、経路切替用スイッチ35をオンに制御することで、RF信号を流す経路として、主経路を選択する。

10

20

30

40

これにより、ドライバ段増幅器 3 により増幅された R F 信号は、段間整合回路 4 を通過して最終段増幅器 5 に入力される。

最終段増幅器 5 は、段間整合回路 4 を通過してきた R F 信号を増幅し、増幅後の R F 信号を出力整合回路 6 に出力する。

最終段増幅器5から出力されたRF信号は、出力整合回路6を通過して、RF出力端子7から外部に出力される。

### [0039]

図3の高周波増幅器モジュールでは、ドライバ段増幅器3及びバイパス増幅器32がシリコン基板11上に形成され、最終段増幅器5がガリウム砒素基板上に形成されているが、高周波特性に支配的な増幅器は最終段増幅器5であり、ドライバ段増幅器3及びバイパス増幅器32は高周波特性に特段の影響を与えない増幅器である。

このため、高周波特性に優れているガリウム砒素基板上に最終段増幅器 5 を形成すれば、ドライバ段増幅器 3 及びバイパス増幅器 3 2 をシリコン基板 1 1 上に形成しても、モジュールの全体がガリウム砒素基板上に形成されている場合と同等の高周波特性を維持することができる。

このように、ドライバ段増幅器 3 及びバイパス増幅器 3 2 をシリコン基板 1 1 上に形成することで、ガリウム砒素基板で形成するチップの面積を削減することができるため、低コスト化を実現することができる。

## [0040]

なお、この実施の形態 3 では、経路切替用スイッチ 3 3 , 3 4 , 3 5 がシリコン基板 1 1 上に形成されているが、経路切替用スイッチ 3 3 , 3 4 , 3 5 がガリウム砒素基板上に形成されていてもよい。

また、この実施の形態 3 では、高周波増幅器モジュールが入力整合回路 2 、段間整合回路 4 及び出力整合回路 6 を実装しているものを示したが、入力整合回路 2 、段間整合回路 4 及び出力整合回路 6 の一部又は全部を実装していない高周波増幅器モジュールであってもよい。

### [0041]

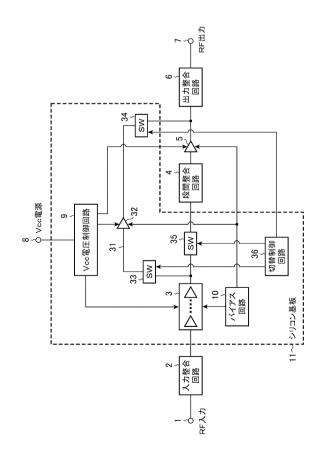

実施の形態4.

図4はこの発明の実施の形態4による高周波増幅器モジュールを示す構成図であり、図において、図1と同一符号は同一または相当部分を示すので説明を省略する。

バイパス経路41は一端がドライバ段増幅器3の入力側に接続され、他端が最終段増幅器5の出力側に接続されている経路である。

この実施の形態 4 では、ドライバ段増幅器 3 及び最終段増幅器 5 が配置されている経路を「主経路」と称する。

### [0042]

バイパスドライバ段増幅器42はバイパス経路41上に配置され、1~N段の増幅素子から構成されている多段の増幅器であり、バイパスドライバ段増幅器42はRF入力端子 1から入力されたRF信号を増幅するデバイスである。

バイパス最終段増幅器43はバイパス経路41上に配置され、バイパスドライバ段増幅器42により増幅されたRF信号を更に増幅して、増幅後のRF信号を出力整合回路6に出力するデバイスである。

なお、バイパス最終段増幅器 4 3 のサイズは、最終段増幅器 5 のサイズより小さくなるように設計されている。

## [ 0 0 4 3 ]

経路切替用スイッチ44はバイパス経路41上で、バイパスドライバ段増幅器42の入力側に配置され、切替制御回路47の制御の下でオン/オフするスイッチである。

経路切替用スイッチ 4 5 はバイパス経路 4 1 上で、バイパスドライバ段増幅器 4 2 の出力側に配置され、切替制御回路 4 7 の制御の下でオン / オフするスイッチである。

経路切替用スイッチ46は主経路上で、ドライバ段増幅器3の出力側に配置され、切替制御回路47の制御の下でオン/オフするスイッチである。

10

20

30

40

#### [0044]

切替制御回路47は経路切替用スイッチ44,45,46をオン/オフすることで、 RF信号を流す経路として、主経路又はバイパス経路41を選択する回路である。

この実施の形態 4 では、バイパスドライバ段増幅器 4 2 、経路切替用スイッチ 4 4 , 4 5 , 4 6 及び切替制御回路 4 6 がシリコン基板 1 1 上に形成されている。

バイパス最終段増幅器43は、ガリウム砒素基板上に形成されている。

### [0045]

次に動作について説明する。

まず、Vcc電圧制御回路9は、Vcc電源8から電源電圧Vccの供給を受けると、ドライバ段増幅器3、最終段増幅器5、バイパスドライバ段増幅器42及びバイパス最終段増幅器43のドレイン又はコレクタに供給する直流電圧を制御することで、ドライバ段増幅器3、最終段増幅器5、バイパスドライバ段増幅器42及びバイパス最終段増幅器43を駆動可能な状態に設定する。

バイアス回路10は、ドライバ段増幅器3、最終段増幅器5、バイパスドライバ段増幅器42及びバイパス最終段増幅器43におけるRF信号の増幅率等を所望値に設定するため、例えば、外部から与えられる増幅率の設定情報等にしたがって、ドライバ段増幅器3、最終段増幅器5、バイパスドライバ段増幅器42及びバイパス最終段増幅器43のゲート又はベースに供給する直流電圧又は直流電流を制御することで、ドライバ段増幅器3、最終段増幅器5、バイパスドライバ段増幅器42及びバイパス最終段増幅器43のバイアスを設定する。

### [0046]

バイアス回路10によりドライバ段増幅器3、最終段増幅器5、バイパスドライバ段増幅器42及びバイパス最終段増幅器43のバイアスが設定されている状態で、RF入力端子1からRF信号が入力されると、そのRF信号は入力整合回路2を通過する。

切替制御回路46は、例えば、外部からRF信号を低出力電力で駆動する旨を示す制御情報を入力すると、経路切替用スイッチ44,45をオンに制御して、経路切替用スイッチ46をオフに制御することで、RF信号を流す経路として、バイパス経路41を選択する。

### [0047]

これにより、入力整合回路 2 を通過した R F 信号がバイパスドライバ段増幅器 4 2 に入力される。

バイパスドライバ段増幅器42は、入力整合回路2を通過してきたRF信号を増幅し、 増幅後のRF信号をバイパス最終段増幅器43に出力する。

バイパス最終段増幅器 4 3 は、バイパスドライバ段増幅器 4 2 により増幅された R F 信号を更に増幅し、増幅後の R F 信号を出力整合回路 6 に出力する。

バイパス最終段増幅器 4 3 から出力された R F 信号は、出力整合回路 6 を通過して、 R F 出力端子 7 から外部に出力される。

### [0048]

切替制御回路46は、例えば、外部からRF信号を高出力電力で駆動する旨を示す制御情報を入力すると、経路切替用スイッチ44,45をオフに制御して、経路切替用スイッチ46をオンに制御することで、RF信号を流す経路として、主経路を選択する。

これにより、入力整合回路 2 を通過した R F 信号がドライバ段増幅器 3 に入力される。ドライバ段増幅器 3 は、入力整合回路 2 を通過してきた R F 信号を増幅し、増幅後の R F 信号を段間整合回路 4 に出力する。

#### [0049]

ドライバ段増幅器 3 から出力された R F 信号は、段間整合回路 4 を通過して最終段増幅器 5 に入力される。

最終段増幅器 5 は、段間整合回路 4 を通過してきた R F 信号を増幅し、増幅後の R F 信号を出力整合回路 6 に出力する。

最終段増幅器5から出力されたRF信号は、出力整合回路6を通過して、RF出力端子

20

10

30

40

7から外部に出力される。

### [0050]

図4の高周波増幅器モジュールでは、ドライバ段増幅器3及びバイパスドライバ段増幅器42がシリコン基板11上に形成され、最終段増幅器5及びバイパス最終段増幅器43がガリウム砒素基板上に形成されているが、高周波特性に支配的な増幅器は最終段増幅器5及びバイパス最終段増幅器43であり、ドライバ段増幅器3及びバイパスドライバ段増幅器42は高周波特性に特段の影響を与えない増幅器である。

このため、高周波特性に優れているガリウム砒素基板上に最終段増幅器5及びバイパス最終段増幅器43を形成すれば、ドライバ段増幅器3及びバイパスドライバ段増幅器42をシリコン基板11上に形成しても、モジュールの全体がガリウム砒素基板上に形成されている場合と同等の高周波特性を維持することができる。

このように、ドライバ段増幅器 3 及びバイパスドライバ段増幅器 4 2 をシリコン基板 1 1 上に形成することで、ガリウム砒素基板で形成するチップの面積を削減することができる。

### [0051]

なお、この実施の形態 4 では、経路切替用スイッチ 4 4 , 4 5 , 4 6 がシリコン基板 1 1 上に形成されているが、経路切替用スイッチ 4 4 , 4 5 , 4 6 がガリウム砒素基板上に形成されていてもよい。

また、この実施の形態 4 では、高周波増幅器モジュールが入力整合回路 2 、段間整合回路 4 及び出力整合回路 6 を実装しているものを示したが、入力整合回路 2 、段間整合回路 4 及び出力整合回路 6 の一部又は全部を実装していない高周波増幅器モジュールであってもよい。

### [0052]

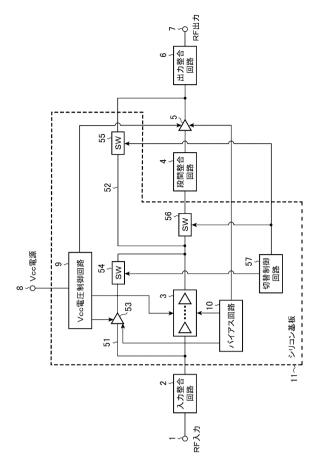

実施の形態5.

図 5 はこの発明の実施の形態 5 による高周波増幅器モジュールを示す構成図であり、図において、図 1 と同一符号は同一または相当部分を示すので説明を省略する。

第 1 のバイパス経路 5 1 は一端がドライバ段増幅器 3 の入力側に接続され、他端がドライバ段増幅器 3 の出力側に接続されている経路である。

第2のバイパス経路52は一端が最終段増幅器5の入力側に接続され、他端が最終段増幅器5の出力側に接続されている経路である。

この実施の形態 5 では、ドライバ段増幅器 3 及び最終段増幅器 5 が配置されている経路を「主経路」と称する。

バイパス増幅器53は第1のバイパス経路51上に配置されているドライバ段増幅器であり、バイパス増幅器52のサイズは、ドライバ段増幅器3のサイズより小さくなるように設計されている。

### [0053]

経路切替用スイッチ54は第1のバイパス経路51上で、バイパス増幅器53の出力側に配置され、切替制御回路57の制御の下でオン/オフするスイッチである。

経路切替用スイッチ55は第2のバイパス経路52上に配置され、切替制御回路57の 制御の下でオン/オフするスイッチである。

経路切替用スイッチ 5 6 は主経路上で、ドライバ段増幅器 3 の出力側に配置され、切替制御回路 5 7 の制御の下でオン / オフするスイッチである。

### [0054]

切替制御回路 5 7 は経路切替用スイッチ 5 4 , 5 5 , 5 6 をオン / オフすることで、 R F 信号を流す経路として、主経路又はバイパス経路 5 1 , 5 2 を選択する回路である。

この実施の形態 5 では、バイパス増幅器 5 3 、経路切替用スイッチ 5 4 , 5 5 , 5 6 及び切替制御回路 5 7 がシリコン基板 1 1 上に形成されている。

### [0055]

次に動作について説明する。

まず、Vcc電圧制御回路9は、Vcc電源8から電源電圧Vccの供給を受けると、

20

10

30

40

ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器53のドレイン又はコレクタに供給する直流電圧を制御することで、ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器53を駆動可能な状態に設定する。

バイアス回路10は、ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器53におけるRF信号の増幅率等を所望値に設定するため、例えば、外部から与えられる増幅率の設定情報等にしたがって、ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器53のゲート又はベースに供給する直流電圧又は直流電流を制御することで、ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器53のバイアスを設定する。

### [0056]

バイアス回路10によりドライバ段増幅器3、最終段増幅器5及びバイパス増幅器53のバイアスが設定されている状態で、RF入力端子1からRF信号が入力されると、そのRF信号は入力整合回路2を通過する。

切替制御回路 5 7 は、例えば、外部から R F 信号を低出力電力で駆動する旨を示す制御情報を入力すると、経路切替用スイッチ 5 4 , 5 5 をオンに制御して、経路切替用スイッチ 5 6 をオフに制御することで、 R F 信号を流す経路として、第 1 のバイパス経路 5 1 と第 2 のバイパス経路 5 2 を選択する。

### [0057]

これにより、入力整合回路 2 を通過した R F 信号がバイパス増幅器 5 3 に入力される。 バイパス増幅器 5 3 は、入力整合回路 2 を通過してきた R F 信号を増幅し、増幅後の R F 信号を出力する。

バイパス増幅器 5 3 から出力された R F 信号は、第 2 のバイパス経路 5 2 経由で出力整合回路 6 に入力される。

バイパス増幅器22から出力されたRF信号は、出力整合回路6を通過して、RF出力端子7から外部に出力される。

#### [0058]

切替制御回路 5 7 は、例えば、外部から R F 信号を中出力電力で駆動する旨を示す制御情報を入力すると、経路切替用スイッチ 5 5 をオンに制御して、経路切替用スイッチ 5 4 , 5 6 をオフに制御することで、 R F 信号を流す経路として、主回路と第 2 のバイパス経路 5 2 を選択する。

これにより、入力整合回路2を通過したRF信号がドライバ段増幅器3に入力される。

#### [0059]

ドライバ段増幅器 3 は、入力整合回路 2 を通過してきた R F 信号を増幅し、増幅後の R F 信号を出力する。

ドライバ段増幅器3から出力されたRF信号は、第2のバイパス経路52経由で出力整合回路6に入力される。

ドライバ段増幅器3から出力されたRF信号は、出力整合回路6を通過して、RF出力端子7から外部に出力される。

### [0060]

切替制御回路 5 7 は、例えば、外部から R F 信号を高出力電力で駆動する旨を示す制御情報を入力すると、経路切替用スイッチ 5 6 をオンに制御して、経路切替用スイッチ 5 4 をオフに制御することで、 R F 信号を流す経路として、主回路を選択する。

これにより、入力整合回路 2 を通過した R F 信号がドライバ段増幅器 3 に入力される。ドライバ段増幅器 3 は、入力整合回路 2 を通過してきた R F 信号を増幅し、増幅後の R F 信号を段間整合回路 4 に出力する。

#### [0061]

ドライバ段増幅器 3 から出力された R F 信号は、段間整合回路 4 を通過して最終段増幅器 5 に入力される。

最終段増幅器 5 は、段間整合回路 4 を通過してきた R F 信号を増幅し、増幅後の R F 信号を出力整合回路 6 に出力する。

最終段増幅器5から出力されたRF信号は、出力整合回路6を通過して、RF出力端子

10

20

30

40

7から外部に出力される。

### [0062]

図5の高周波増幅器モジュールでは、ドライバ段増幅器3及びバイパス増幅器53がシリコン基板11上に形成され、最終段増幅器5がガリウム砒素基板上に形成されているが、高周波特性に支配的な増幅器は最終段増幅器5であり、ドライバ段増幅器3及びバイパス増幅器53は高周波特性に特段の影響を与えない増幅器である。

このため、高周波特性に優れているガリウム砒素基板上に最終段増幅器 5 を形成すれば、ドライバ段増幅器 3 及びバイパス増幅器 5 3 をシリコン基板 1 1 上に形成しても、モジュールの全体がガリウム砒素基板上に形成されている場合と同等の高周波特性を維持することができる。

このように、ドライバ段増幅器 3 及びバイパス増幅器 5 3 をシリコン基板 1 1 上に形成することで、ガリウム砒素基板で形成するチップの面積を削減することができるため、低コスト化を実現することができる。

### [0063]

なお、この実施の形態 5 では、経路切替用スイッチ 5 4 , 5 5 , 5 6 がシリコン基板 1 1 上に形成されているが、経路切替用スイッチ 5 4 , 5 5 , 5 6 がガリウム砒素基板上に形成されていてもよい。

また、この実施の形態 5 では、高周波増幅器モジュールが入力整合回路 2 、段間整合回路 4 及び出力整合回路 6 を実装しているものを示したが、入力整合回路 2 、段間整合回路 4 及び出力整合回路 6 の一部又は全部を実装していない高周波増幅器モジュールであってもよい。

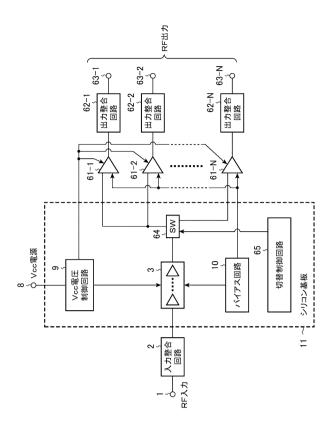

### [0064]

実施の形態 6.

図 6 はこの発明の実施の形態 6 による高周波増幅器モジュールを示す構成図であり、図において、図 1 と同一符号は同一または相当部分を示すので説明を省略する。

最終段増幅器61-1~61-Nはドライバ段増幅器3の出力側にN個並列に接続されており、ドライバ段増幅器3により増幅されたRF信号を更に増幅して、増幅後のRF信号を出力整合回路62-1~62-Nに出力するデバイスである。

出力整合回路 6 2 - 1 ~ 6 2 - N は最終段増幅器 6 1 - 1 ~ 6 1 - N の出力側の整合回路である。

R F 出力端子 6 3 - 1 ~ 6 3 - N は最終段増幅器 6 1 - 1 ~ 6 1 - N により増幅された R F 信号を出力する端子である。

#### [0065]

経路切替用スイッチ 6 4 は切替制御回路 6 5 の制御の下で、ドライバ段増幅器 3 により 増幅された R F 信号を何れかの最終段増幅器 6 1 に出力するスイッチである。

切替制御回路65は経路切替用スイッチ64の出力先を切り替える回路である。

### [0066]

この実施の形態6では、ドライバ段増幅器3、Vcc電圧制御回路9、バイパス回路10、経路切替用スイッチ64及び切替制御回路65がシリコン基板11上に形成されている。

入力整合回路 2 及び出力整合回路 6 2 - 1 ~ 6 2 - N と最終段増幅器 6 1 - 1 ~ 6 1 - N は、ガリウム砒素基板上に形成されている。

### [0067]

次に動作について説明する。

まず、Vcc電圧制御回路9は、Vcc電源8から電源電圧Vccの供給を受けると、ドライバ段増幅器3及び最終段増幅器61-1~61-Nのドレイン又はコレクタに供給する直流電圧を制御することで、ドライバ段増幅器3及び最終段増幅器61-1~61-Nを駆動可能な状態に設定する。

バイアス回路10は、ドライバ段増幅器3及び最終段増幅器61-1~61-NにおけるRF信号の増幅率等を所望値に設定するため、例えば、外部から与えられる増幅率の設

10

20

30

40

定情報等にしたがって、ドライバ段増幅器3及び最終段増幅器61-1~61-Nのゲート又はベースに供給する直流電圧又は直流電流を制御することで、ドライバ段増幅器3及び最終段増幅器61-1~61-Nのバイアスを設定する。

### [0068]

バイアス回路10によりドライバ段増幅器3及び最終段増幅器61-1~61-Nのバイアスが設定されている状態で、RF入力端子1からRF信号が入力されると、そのRF信号は入力整合回路2を通過する。

この実施の形態 6 では、 R F 入力端子 1 から周波数が異なる R F 信号が順次入力される場合を想定する。

切替制御回路65は、例えば、外部からRF信号の周波数を示す情報を入力すると、経路切替用スイッチ64の出力先を上記RF信号の周波数に対応する最終段増幅器61に切り替えて、そのRF信号が当該最終段増幅器61に入力されるようにする。

例えば、RF信号の周波数がAHzならば、経路切替用スイッチ64の出力先を最終段増幅器61-1に切り替え、RF信号の周波数がBHzならば、経路切替用スイッチ64の出力先を最終段増幅器61-2に切り替え、RF信号の周波数がCHzならば、経路切替用スイッチ64の出力先を最終段増幅器61-Nに切り替えるようにする。

### [0069]

最終段増幅器61-1~61-Nのうち、ドライバ段増幅器3から経路切替用スイッチ64を介してRF信号が入力された最終段増幅器61は、そのRF信号を増幅し、増幅後のRF信号を出力整合回路62に出力する。

最終段増幅器 6 1 - 1 ~ 6 1 - Nから出力された R F 信号は、出力整合回路 6 2 - 1 ~ 6 2 - Nを通過して、 R F 出力端子 6 3 - 1 ~ 6 3 - Nから外部に出力される。

#### [0070]

図6の高周波増幅器モジュールでは、ドライバ段増幅器3がシリコン基板11上に形成され、最終段増幅器61-1~61-Nがガリウム砒素基板上に形成されているが、高周波特性に支配的な増幅器は最終段増幅器61-1~61-Nであり、ドライバ段増幅器3は高周波特性に特段の影響を与えない増幅器である。

このため、高周波特性に優れているガリウム砒素基板上に最終段増幅器 6 1 - 1 ~ 6 1 - Nを形成すれば、ドライバ段増幅器 3 をシリコン基板 1 1 上に形成しても、モジュールの全体がガリウム砒素基板上に形成されている場合と同等の高周波特性を維持することができる。

このように、ドライバ段増幅器 3 をシリコン基板 1 1 上に形成することで、ガリウム砒素基板で形成するチップの面積を削減することができるため、低コスト化を実現することができる。

### [0071]

なお、この実施の形態 6 では、経路切替用スイッチ 6 4 がシリコン基板 1 1 上に形成されているが、経路切替用スイッチ 6 4 がガリウム砒素基板上に形成されていてもよい。

また、この実施の形態 6 では、高周波増幅器モジュールが入力整合回路 2 及び最終段増幅器 6 1 - 1 ~ 6 1 - Nを実装しているものを示したが、入力整合回路 2 及び最終段増幅器 6 1 - 1 ~ 6 1 - Nの一部又は全部を実装していない高周波増幅器モジュールであってもよい。

また、段間整合回路を実装している高周波増幅器モジュールであってもよい。

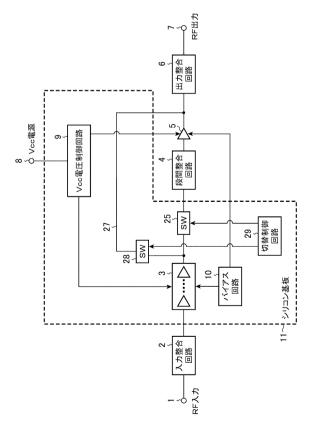

### [0072]

## 実施の形態 7.

図7はこの発明の実施の形態7による高周波増幅器モジュールを示す構成図であり、図において、図2と同一符号は同一または相当部分を示すので説明を省略する。

バイパス経路27は一端がドライバ段増幅器3の出力側に接続され、他端が最終段増幅器5の出力側に接続されている経路である。

この実施の形態 7 では、ドライバ段増幅器 3 及び最終段増幅器 5 が配置されている経路を「主経路」と称する。

10

20

30

40

#### [ 0 0 7 3 ]

経路切替用スイッチ 2 8 はバイパス経路 2 7 上に配置され、切替制御回路 2 9 の制御の下でオン / オフするスイッチである。

切替制御回路 2 9 は経路切替用スイッチ 2 5 , 2 8 をオン / オフすることで、 R F 信号を流す経路として、主経路又はバイパス経路 2 7 を選択する回路である。

この実施の形態 7 では、経路切替用スイッチ 2 5 , 2 8 及び切替制御回路 2 9 がシリコン基板 1 1 上に形成されている。

### [0074]

次に動作について説明する。

まず、Vcc電圧制御回路9は、Vcc電源8から電源電圧Vccの供給を受けると、ドライバ段増幅器3及び最終段増幅器5のドレイン又はコレクタに供給する直流電圧を制御することで、ドライバ段増幅器3及び最終段増幅器5を駆動可能な状態に設定する。

バイアス回路 1 0 は、ドライバ段増幅器 3 及び最終段増幅器 5 における R F 信号の増幅率等を所望値に設定するため、例えば、外部から与えられる増幅率の設定情報等にしたがって、ドライバ段増幅器 3 及び最終段増幅器 5 のゲート又はベースに供給する直流電圧又は直流電流を制御することで、ドライバ段増幅器 3 及び最終段増幅器 5 のバイアスを設定する。

### [0075]

バイアス回路10によりドライバ段増幅器3及び最終段増幅器5のバイアスが設定されている状態で、RF入力端子1からRF信号が入力されると、そのRF信号は入力整合回路2を通過する。

切替制御回路29は、例えば、外部からRF信号を低出力電力で駆動する旨を示す制御情報を入力すると、経路切替用スイッチ28をオンに制御して、経路切替用スイッチ25をオフに制御することで、RF信号を流す経路として、バイパス経路27を選択する。

#### [0076]

これにより、入力整合回路 2 を通過した R F 信号がバイパス経路 2 7 経由で出力整合回路 6 に入力される。

バイパス経路27から出力されたRF信号は、出力整合回路6を通過して、RF出力端子7から外部に出力される。

## [0077]

切替制御回路 2 9 は、例えば、外部から R F 信号を高出力電力で駆動する旨を示す制御情報を入力すると、経路切替用スイッチ 2 5 をオンに制御して、経路切替用スイッチ 2 8をオフに制御することで、 R F 信号を流す経路として、主経路を選択する。

これにより、入力整合回路 2 を通過した R F 信号がドライバ段増幅器 3 に入力される。 ドライバ段増幅器 3 は、入力整合回路 2 を通過してきた R F 信号を増幅し、増幅後の R F 信号を段間整合回路 4 に出力する。

## [0078]

ドライバ段増幅器 3 から出力された R F 信号は、段間整合回路 4 を通過して最終段増幅器 5 に入力される。

最終段増幅器 5 は、段間整合回路 4 を通過してきた R F 信号を増幅し、増幅後の R F 信号を出力整合回路 6 に出力する。

最終段増幅器5から出力されたRF信号は、出力整合回路6を通過して、RF出力端子7から外部に出力される。

## [0079]

図7の高周波増幅器モジュールでは、ドライバ段増幅器3がシリコン基板11上に形成され、最終段増幅器5がガリウム砒素基板上に形成されているが、高周波特性に支配的な増幅器は最終段増幅器5であり、ドライバ段増幅器3は高周波特性に特段の影響を与えない増幅器である。

このため、 高周波特性に優れているガリウム砒素基板上に最終段増幅器 5 を形成すれば、ドライバ段増幅器 3 をシリコン基板 1 1 上に形成しても、モジュールの全体がガリウム

10

20

30

40

砒素基板上に形成されている場合と同等の高周波特性を維持することができる。

このように、ドライバ段増幅器 3 をシリコン基板 1 1 上に形成することで、ガリウム砒素基板で形成するチップの面積を削減することができるため、低コスト化を実現することができる。

## [0080]

なお、この実施の形態 7 では、経路切替用スイッチ 2 5 , 2 8 がシリコン基板 1 1 上に形成されているが、経路切替用スイッチ 2 5 , 2 8 がガリウム砒素基板上に形成されていてもよい。

また、この実施の形態 7 では、高周波増幅器モジュールが入力整合回路 2 、段間整合回路 4 及び出力整合回路 6 を実装しているものを示したが、入力整合回路 2 、段間整合回路 4 及び出力整合回路 6 の一部又は全部を実装していない高周波増幅器モジュールであってもよい。

### [0081]

実施の形態8.

図8はこの発明の実施の形態8による高周波増幅器モジュールを示す構成図であり、図において、図2と同一符号は同一または相当部分を示すので説明を省略する。

ガリウム砒素基板 7 1 はガリウム砒素で形成されている基板であり、段間整合回路 4、最終段増幅器 5 及び温度検知回路 7 2 が形成されている。

温度検知回路72はガリウム砒素基板71の温度を検知する機能を有し、ガリウム砒素基板71の温度に応じてバイアス回路10により設定されるバイアスを調整する処理を実施する。なお、温度検知回路72はバイアス調整手段を構成している。

#### [0082]

次に動作について説明する。

ただし、温度検知回路 7 2 が実装されている点以外は、上記実施の形態 1 と同様であるため、ここでは、主に温度検知回路 7 2 の処理内容について説明する。

バイアス回路10は、ドライバ段増幅器3及び最終段増幅器5におけるRF信号の増幅率等を所望値に設定するため、上記実施の形態1と同様に、例えば、外部から与えられる増幅率の設定情報等にしたがって、ドライバ段増幅器3及び最終段増幅器5のゲート又はベースに供給する直流電圧又は直流電流を制御することで、ドライバ段増幅器3及び最終段増幅器5のバイアスを設定する。

### [0083]

このとき、温度検知回路72は、ガリウム砒素基板71の温度を検知する機能を有し、 ガリウム砒素基板71の温度Tを検知する。

例えば、温度検知回路72が、ガリウム砒素基板71と略同一の温度特性を有するダイオード又はバイポーラトランジスタを備えることで、ガリウム砒素基板71の温度を検知することができる。

温度検知回路72は、ガリウム砒素基板71の温度Tを検知すると、ガリウム砒素基板71の温度Tと予め設定されている基準温度Trefとの差分 Tを算出し、その差分 Tに対応する調整信号をバイアス回路10に出力する。

T = T - T r e f

## [ 0 0 8 4 ]

バイアス回路10は、温度検知回路72から差分 Tに対応する調整信号を受けると、その調整信号にしたがって、ドライバ段増幅器3及び最終段増幅器5に対する制御信号(ドライバ段増幅器3及び最終段増幅器5のゲート又はベースに供給する直流電圧又は直流電流を制御する制御電圧)を調整するが、例えば、ガリウム砒素基板71の温度Tが基準温度Trefより高い場合、その差分 Tの絶対値が大きい程、その制御電圧が小さくなるように調整する。

逆に、ガリウム砒素基板71の温度Tが基準温度Trefより低い場合、その差分 Tの絶対値が大きい程、その制御電圧が大きくなるように調整する。

これにより、温度補償が可能なバイアス供給が可能になる。

10

20

30

#### [0085]

図8の高周波増幅器モジュールは、ドライバ段増幅器3がシリコン基板11上に形成され、最終段増幅器5はガリウム砒素基板71上に形成されているが、高周波特性に支配的な増幅器は最終段増幅器5であり、ドライバ段増幅器3は高周波特性に特段の影響を与えない増幅器である。

このため、高周波特性に優れているガリウム砒素基板71上に最終段増幅器5を形成すれば、ドライバ段増幅器3をシリコン基板11上に形成しても、モジュールの全体がガリウム砒素基板71上に形成されている場合と同等の高周波特性を維持することができる。 【0086】

さらに、ガリウム砒素基板71の温度を検知する機能を有し、ガリウム砒素基板71の温度に応じてバイアス回路10により設定されるバイアスを調整する温度検知回路72をガリウム砒素基板71上に形成しているので、バイアス回路10をシリコン基板11上に形成していても、温度補償が可能な高周波増幅器モジュールを得ることができる。

この場合、バイアス回路10をガリウム砒素基板71上に形成する必要がないため、ガリウム砒素基板71で形成するチップの面積を削減することができるようになり、温度補償が可能な高周波増幅器モジュールであっても、低コスト化を実現することができる。

### [0087]

実施の形態9.

図9はこの発明の実施の形態9による高周波増幅器モジュールを示す構成図であり、図において、図2と同一符号は同一または相当部分を示すので説明を省略する。

カレントミラー型バイアス回路73はガリウム砒素基板71上に形成され、バイアス回路10から出力される定電流の制御信号によってカレントミラーを形成する回路であり、バイアス回路10により設定されるバイアスを調整するバイアス調整手段を構成している

なお、カレントミラー型バイアス回路 7 3 を構成しているカレントミラー用トランジスタは、最終段トランジスタ 5 と同デバイスで構成されているものとする。

#### [0088]

図9の高周波増幅器モジュールでは、カレントミラー型バイアス回路73がガリウム砒素基板71上に形成されており、バイアス回路10から出力される定電流の制御信号によってカレントミラーを形成している。

このため、カレントミラー型バイアス回路73を構成しているカレントミラー用トランジスタが、最終段トランジスタ5と同デバイスで構成されていれば、カレントミラー型バイアス回路73によって、バイアス回路10の出力信号である制御信号が、ガリウム砒素基板71の温度に応じて調整され、温度調整後の制御信号が最終段増幅器5に与えられる

因みに、上記実施の形態 2 では、シリコン基板 1 1 上に形成されているバイアス回路 1 0 の出力信号である制御信号が、直接、ガリウム砒素基板 7 1 上に形成されている最終段増幅器 5 に与えられる。

これにより、温度補償が可能なバイアス供給が可能になる。

### [0089]

図9の高周波増幅器モジュールは、ドライバ段増幅器3がシリコン基板11上に形成され、最終段増幅器5はガリウム砒素基板71上に形成されているが、高周波特性に支配的な増幅器は最終段増幅器5であり、ドライバ段増幅器3は高周波特性に特段の影響を与えない増幅器である。

このため、高周波特性に優れているガリウム砒素基板71上に最終段増幅器5を形成すれば、ドライバ段増幅器3をシリコン基板11上に形成しても、モジュールの全体がガリウム砒素基板71上に形成されている場合と同等の高周波特性を維持することができる。

### [0090]

さらに、バイアス回路 1 0 から出力される定電流の制御信号によってカレントミラーを 形成するカレントミラー型バイアス回路 7 3 をガリウム砒素基板 7 1 上に形成しているの 10

20

30

- -

40

で、バイアス回路10をシリコン基板11上に形成していても、温度補償が可能な高周波 増幅器モジュールを得ることができる。

この場合、バイアス回路10をガリウム砒素基板71上に形成する必要がないため、ガ リウム砒素基板 71で形成するチップの面積を削減することができるようになり、温度補 償が可能な高周波増幅器モジュールであっても、低コスト化を実現することができる。

### [0091]

この実施の形態9では、バイアス回路10から出力される定電流の制御信号によってカ レントミラーを形成するカレントミラー型バイアス回路73をガリウム砒素基板71上に 形成するものを示したが、カレントミラー型バイアス回路73の代わりに、最終段トラン ジ ス タ 5 と 同 デ バ イ ス で 構 成 さ れ て い る バ イ ポ ー ラ ト ラ ン ジ ス タ を 含 む エ ミ ッ タ フ ォ ロ ア 型バイアス回路をガリウム砒素基板71上に形成するようにしてもよい。

この場合、エミッタフォロア型バイアス回路によって、バイアス回路10の出力信号で ある定電圧の制御信号が、ガリウム砒素基板71の温度に応じて調整され、温度調整後の 制御信号が最終段増幅器5に与えられるようになる。

したがって、カレントミラー型バイアス回路73がガリウム砒素基板71上に形成され ている場合と同様に、温度補償が可能なバイアス供給が可能になり、温度補償が可能な高 周波増幅器モジュールであっても、低コスト化を実現することができる。

#### [0092]

実施の形態10.

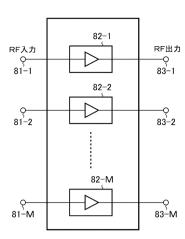

図10はこの発明の実施の形態10による高周波増幅器モジュールユニットを示す構成 図である。

図 1 0 において、 R F 入力端子 8 1 - 1 ~ 8 1 - M は R F 信号を入力する端子である。 この実施の形態 1 0 では、RF入力端子 8 1 - 1 ~ 8 1 - M から周波数が異なるRF信 号が入力される場合を想定する。

高周波増幅器モジュール82-1~82-Mは、上記実施の形態1~5,7~9のいず れかに記載されている高周波増幅器モジュール(図1~図5、図7~図9に記載の高周波 増幅器モジュール)であり、高周波増幅器モジュール82-1~82-Mにより増幅され たRF信号がRF出力端子83-1~83-Mから出力される。

### [0093]

複 数 の 高 周 波 増 幅 器 モ ジ ュ ー ル を 実 装 し て い る 高 周 波 増 幅 器 モ ジ ュ ー ル ユ ニ ッ ト を 構 築 する場合でも、図10に示すように、シリコン基板とガリウム砒素基板で形成されている 高 周 波 増 幅 器 モ ジュ ー ル 8 2 ・ 1 ~ 8 2 ・ M を 実 装 す る こ と で 、 上 記 実 施 の 形 態 1 ~ 5 , 7~9と同様に、優れた高周波特性を維持しながら、低コスト化を実現することができる 効果を奏する。

## [0094]

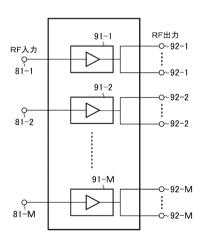

実施の形態11.

図 1 1 はこの発明の実施の形態 1 1 による高周波増幅器モジュールユニットを示す構成 図であり、図において、図10と同一符号は同一または相当部分を示すので説明を省略す

高周波増幅器モジュール91-1~91-Mは、上記実施の形態6に記載されている高 周 波 増 幅 器 モ ジ ュ ー ル ( 図 6 に 記 載 の 高 周 波 増 幅 器 モ ジ ュ ー ル ) で あ り 、 高 周 波 増 幅 器 モ ジュール91-1~91-Mにより増幅されたRF信号がRF出力端子92-1~92-Mから出力される。

## [0095]

複 数 の 高 周 波 増 幅 器 モ ジ ュ ー ル を 実 装 し て い る 高 周 波 増 幅 器 モ ジ ュ ー ル ユ ニ ッ ト を 構 築 する場合でも、図10に示すように、シリコン基板とガリウム砒素基板で形成されている 高 周 波 増 幅 器 モ ジ ュ ー ル 9 1 - 1 ~ 9 1 - M を 実 装 す る こ と で 、 上 記 実 施 の 形 態 6 と 同 様 に、優れた高周波特性を維持しながら、低コスト化を実現することができる効果を奏する

[0096]

10

20

30

なお、本願発明はその発明の範囲内において、各実施の形態の自由な組み合わせ、ある いは各実施の形態の任意の構成要素の変形、もしくは各実施の形態において任意の構成要 素の省略が可能である。

### 【産業上の利用可能性】

### [0097]

この発明は、例えば、高周波信号であるRF信号を増幅する際、モジュールの全体がガ リウム砒素基板上に形成されている場合と同等の高周波特性を維持しながら、低コスト化 を実現する必要性が高い高周波増幅器モジュールに適している。

### 【符号の説明】

### [0098]

RF入力端子、 2 入力整合回路、 3 ドライバ段増幅器、 4 段間整合回路、 5 最終段增幅器、6 出力整合回路、7 RF出力端子、8 Vcc電源、9 Vcc電 圧制御回路(電源電圧制御回路)、10 バイアス回路、11 シリコン基板、21,2 7,31,41 バイパス経路、22,32 バイパス増幅器、23,24,25,28 , 3 3 , 3 4 , 3 5 , 4 4 , 4 5 , 4 6 経路切替用スイッチ、 2 6 , 2 9 , 3 6 , 4 7 切替制御回路、42 バイパスドライバ段増幅器、43 バイパス最終段増幅器、51 第 1 のバイパス経路、 5 2 第 2 のバイパス経路、 5 3 バイパス増幅器、 5 4 , 5 5 , 5 6 経路切替用スイッチ、5 7 切替制御回路、6 1 - 1 ~ 6 1 - N 最終段増幅器 、 6 2 - 1 ~ 6 2 - N 出力整合回路、 6 3 - 1 ~ 6 3 - N R F 出力端子、 6 4 切替用スイッチ、 6 5 切替制御回路、 7 1 ガリウム砒素基板、 7 2 温度検知回路( バイアス調整手段)、73 カレントミラー型バイアス回路(バイアス調整手段)、81 - 1 ~ 8 1 - M R F 入力端子、 8 2 - 1 ~ 8 2 - M 高周波増幅器モジュール、 8 3 -1 ~ 8 3 - M R F 出力端子、 9 1 - 1 ~ 9 1 - M 高周波増幅器モジュール、 9 2 - 1 ~92-M RF出力端子、101 RF入力端子、102 ドライバ段増幅器、103 最終段増幅器、104 RF出力端子、105 バイパス経路、106 切替制御回路 、 1 0 7 , 1 0 8 切替スイッチ、 1 0 9 V c c 電源、 1 1 0 バイアス回路。

10

【図1】 【図2】

【図3】

【図5】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

#### 【手続補正書】

【提出日】平成25年10月9日(2013.10.9)

#### 【手続補正1】

【補正対象書類名】明細書

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【発明の詳細な説明】

【技術分野】

[0001]

この発明は、例えば、高周波信号であるRF信号を増幅する高周波増幅器モジュールと、その高周波増幅器モジュールが複数個実装されている高周波増幅器モジュールユニットとに関するものである。

## 【背景技術】

### [0002]

図 1 2 は以下の非特許文献 1 に開示されている従来の高周波増幅器モジュールを示す構成図である。

従来の高周波増幅器モジュールでは、RF入力端子101からRF信号が入力されると、多段構成のドライバ段増幅器102がRF信号を増幅し、最終段増幅器103がドライバ段増幅器102により増幅されたRF信号を更に増幅して、増幅後のRF信号をRF出力端子104に出力する。

### [0003]

ただし、最終段増幅器 1 0 3 と並列にバイパス経路 1 0 5 が設けられており、切替制御回路 1 0 6 の制御の下で、切替スイッチ 1 0 7 の出力先がバイパス経路 1 0 5 側に切り替えられ、切替スイッチ 1 0 8 がオフの状態になっていれば、ドライバ段増幅器 1 0 2 により増幅された R F 信号は、最終段増幅器 1 0 3 では増幅されずに、バイパス経路 1 0 5 を経由して R F 出力端子 1 0 4 から出力される。

なお、ドライバ段増幅器102及び最終段増幅器103の電源電圧は、Vcc電源109から供給されており、ドライバ段増幅器102及び最終段増幅器103のバイアスは、バイアス回路110により設定されている。

#### [00004]

高周波増幅器モジュールでは、各構成要素がシリコン基板上に形成されることが一般的であったが、非特許文献1に開示されている高周波増幅器モジュールでは、高効率化を図るために、ドライバ段増幅器102や最終段増幅器103を高周波特性に優れている化合物半導体であるガリウム砒素基板上に形成するようにしている。

また、切替制御回路106やバイアス回路110についても、モジュール全体のサイズの要求からガリウム砒素基板上に形成するようにしている。

即ち、非特許文献 1 に開示されている高周波増幅器モジュールでは、モジュールの全体をガリウム砒素基板上に形成するようにしている。

### 【先行技術文献】

## 【非特許文献】

#### [0005]

【非特許文献 1】G.Hau et al., "Multi-Mode WCDMA Power Amplifier Module with Improved Low-Power Efficiency using Stage-Bypass," IEEE RFIC Symposium Dig., pp.163-166, June 2010

### 【発明の概要】

【発明が解決しようとする課題】

### [0006]

従来の高周波増幅器モジュールは以上のように構成されているので、モジュールの全体がガリウム砒素基板上に形成されて高効率化が図られている。しかし、高周波特性に優れ

ている化合物半導体であるガリウム砒素基板はチップ単価が高いため、製造コストが高価になってしまう課題があった。

### [0007]

この発明は上記のような課題を解決するためになされたもので、モジュールの全体がガリウム砒素基板上に形成されている場合と同等の高周波特性を維持しながら、低コスト化を実現することができる高周波増幅器モジュール及び高周波増幅器モジュールユニットを得ることを目的とする。

### 【課題を解決するための手段】

### [0008]

この発明に係る高周波増幅器モジュールは、入力端子から入力された信号を増幅する多段構成のドライバ段増幅器と、そのドライバ段増幅器により増幅された信号を増幅し、増幅後の信号を出力端子に出力する最終段増幅器とを備え、一端がドライバ段増幅器の入力側に接続され、他端が最終段増幅器の出力側に接続されているバイパス経路と、バイパス経路上に配置されているバイパス増幅器とをさらに備え、そのドライバ段増幅器がシリコン基板上に形成され、その最終段増幅器がガリウム砒素基板上に形成され、バイパス増幅器の少なくとも一部がシリコン基板上に形成されているようにしたものである。

### 【発明の効果】

## [0009]

この発明によれば、入力端子から入力された信号を増幅する多段構成のドライバ段増幅器と、そのドライバ段増幅器により増幅された信号を増幅し、増幅後の信号を出力端子に出力する最終段増幅器とを備え、一端がドライバ段増幅器の入力側に接続され、他端が最終段増幅器の出力側に接続されているバイパス経路と、バイパス経路上に配置されているバイパス増幅器とをさらに備え、そのドライバ段増幅器がシリコン基板上に形成され、その最終段増幅器がガリウム砒素基板上に形成され、バイパス増幅器の少なくとも一部がシリコン基板上に形成されているように構成したので、モジュールの全体がガリウム砒素基板上に形成されている場合と同等の高周波特性を維持しながら、低コスト化を実現することができる効果がある。

### 【図面の簡単な説明】

### [0010]

- 【図1】この発明の実施の形態1による高周波増幅器モジュールを示す構成図である。

- 【図2】この発明の実施の形態2による高周波増幅器モジュールを示す構成図である。

- 【 図 3 】 こ の 発 明 の 実 施 の 形 態 3 に よ る 高 周 波 増 幅 器 モ ジ ュ ー ル を 示 す 構 成 図 で あ る 。

- 【図4】この発明の実施の形態4による高周波増幅器モジュールを示す構成図である。

- 【図5】この発明の実施の形態5による高周波増幅器モジュールを示す構成図である。

- 【図6】この発明の実施の形態6による高周波増幅器モジュールを示す構成図である。

- 【 図 7 】 こ の 発 明 の 実 施 の 形 態 7 に よ る 高 周 波 増 幅 器 モ ジ ュ ー ル ユ ニ ッ ト を 示 す 構 成 図 で あ る 。

- 【図8】この発明の実施の形態8による高周波増幅器モジュールユニットを示す構成図で ある。

- 【図9】この発明の実施の形態9による高周波増幅器モジュールを示す構成図である。

- 【図10】この発明の実施の形態10による高周波増幅器モジュールを示す構成図である

- 【図11】この発明の実施の形態11による高周波増幅器モジュールを示す構成図である

【図12】非特許文献1に開示されている従来の高周波増幅器モジュールを示す構成図である。

### 【発明を実施するための形態】

### [0011]

以下、この発明をより詳細に説明するために、この発明を実施するための形態について、添付の図面に従って説明する。

#### 実施の形態1.

図1はこの発明の実施の形態1による高周波増幅器モジュールを示す構成図である。

図1において、RF入力端子1はRF信号を入力する端子である。

入力整合回路2はドライバ段増幅器3の入力側の整合回路である。

### [0012]

ドライバ段増幅器 3 は 1 ~ N 段の増幅素子から構成されている多段の増幅器であり、 R F 入力端子 1 から入力された R F 信号を増幅し、増幅後の R F 信号を段間整合回路 4 に出力するデバイスである。

段間整合回路 4 はドライバ段増幅器 3 と最終段増幅器 5 の間に配置されている整合回路である。

### [0013]

最終段増幅器 5 はドライバ段増幅器 3 により増幅された R F 信号を更に増幅して、増幅後の R F 信号を出力整合回路 6 に出力するデバイスである。

出力整合回路6は最終段増幅器5の出力側の整合回路である。

RF出力端子 7 は最終段増幅器 5 により増幅されたRF信号を出力する端子である。

### [0014]

Vcc電源8は電源電圧Vccを出力する電源である。

Vcc電圧制御回路9はドライバ段増幅器3及び最終段増幅器5のドレイン又はコレクタに供給する直流電圧を制御する電源電圧制御回路である。

なお、ドライバ段増幅器 3 及び最終段増幅器 5 のドレイン又はコレクタに供給する直流電圧は、Vcc電源 8 から出力される電源電圧Vccと同じ電圧であってもよいし、その電源電圧Vccを可変した電圧であってもよい。

バイアス回路 1 0 はドライバ段増幅器 3 及び最終段増幅器 5 のゲート又はベースに供給する直流電圧又は直流電流を制御することで、ドライバ段増幅器 3 及び最終段増幅器 5 のバイアスを設定する回路である。

### [0015]

シリコン基板 1 1 はシリコンで形成されている基板であり、シリコン基板 1 1 にはドライバ段増幅器 3 、 V c c 電圧制御回路 9 及びバイアス回路 1 0 が形成されている。

入力整合回路 2 、段間整合回路 4 及び出力整合回路 6 と最終段増幅器 5 は、ガリウム砒素基板上に形成されている。

### [0016]

次に動作について説明する。

まず、Vcc電圧制御回路9は、Vcc電源8から電源電圧Vccの供給を受けると、ドライバ段増幅器3及び最終段増幅器5のドレイン又はコレクタに供給する直流電圧を制御することで、ドライバ段増幅器3及び最終段増幅器5を駆動可能な状態に設定する。

バイアス回路10は、ドライバ段増幅器3及び最終段増幅器5におけるRF信号の増幅率等を所望値に設定するため、例えば、外部から与えられる増幅率の設定情報等にしたがって、ドライバ段増幅器3及び最終段増幅器5のゲート又はベースに供給する直流電圧又は直流電流を制御することで、ドライバ段増幅器3及び最終段増幅器5のバイアスを設定する。

## [0017]

バイアス回路10によりドライバ段増幅器3及び最終段増幅器5のバイアスが設定されている状態で、RF入力端子1からRF信号が入力されると、そのRF信号は入力整合回路2を通過してドライバ段増幅器3に入力される。

ドライバ段増幅器 3 は、入力整合回路 2 を通過してきた R F 信号を増幅し、増幅後の R F 信号を段間整合回路 4 に出力する。

### [0018]

ドライバ段増幅器 3 から出力された R F 信号は、段間整合回路 4 を通過して最終段増幅器 5 に入力される。

最終段増幅器5は、段間整合回路4を通過してきたRF信号を増幅し、増幅後のRF信

号を出力整合回路6に出力する。

最終段増幅器5から出力されたRF信号は、出力整合回路6を通過して、RF出力端子7から外部に出力される。

### [0019]

図1の高周波増幅器モジュールでは、ドライバ段増幅器3がシリコン基板11上に形成され、最終段増幅器5がガリウム砒素基板上に形成されているが、高周波特性に支配的な増幅器は最終段増幅器5であり、ドライバ段増幅器3は高周波特性に特段の影響を与えない増幅器である。

このため、高周波特性に優れているガリウム砒素基板上に最終段増幅器5を形成すれば、ドライバ段増幅器3をシリコン基板11上に形成しても、モジュールの全体がガリウム砒素基板上に形成されている場合と同等の高周波特性を維持することができる。

このように、ドライバ段増幅器 3 をシリコン基板 1 1 上に形成することで、ガリウム砒素基板で形成するチップの面積を削減することができるため、低コスト化を実現することができる。

### [0020]

この実施の形態 1 では、入力整合回路 2 、段間整合回路 4 及び出力整合回路 6 をガリウム砒素基板上に形成しているものを示したが、その全てをガリウム砒素基板上に形成せずに、その一部をシリコン基板 1 1 (あるいは、外部のモジュール)上に形成するようにしても、モジュールの全体がガリウム砒素基板上に形成されている場合と同等の高周波特性を維持することができる。

例えば、入力整合回路 2 と段間整合回路 4 をシリコン基板 1 1 (あるいは、外部のモジュール)上に形成して、出力整合回路 6 をガリウム砒素基板上に形成するようにしてもよいし、入力整合回路 2 をシリコン基板 1 1 (あるいは、外部のモジュール)上に形成して、段間整合回路 4 と出力整合回路 6 をガリウム砒素基板上に形成するようにしてもよい。また、出力整合回路 6 をシリコン基板 1 1 (あるいは、外部のモジュール)上に形成して、入力整合回路 2 と段間整合回路 4 をガリウム砒素基板上に形成するようにしてもよい

#### [0021]

なお、この実施の形態 1 では、高周波増幅器モジュールが入力整合回路 2 、段間整合回路 4 及び出力整合回路 6 を実装しているものを示したが、入力整合回路 2 、段間整合回路 4 及び出力整合回路 6 の一部又は全部を実装していない高周波増幅器モジュールであってもよい。

### [0022]

### 実施の形態2.

図 2 はこの発明の実施の形態 2 による高周波増幅器モジュールを示す構成図であり、図において、図 1 と同一符号は同一または相当部分を示すので説明を省略する。

バイパス経路21は一端がドライバ段増幅器3の入力側に接続され、他端が最終段増幅器5の出力側に接続されている経路である。

この実施の形態 2 では、ドライバ段増幅器 3 及び最終段増幅器 5 が配置されている経路を「主経路」と称する。

バイパス増幅器 2 2 はバイパス経路 2 1 上に配置されているドライバ段増幅器であり、バイパス増幅器 2 2 のサイズは、信号の増幅率が、ドライバ段増幅器 3 及び最終段増幅器 5 のトータルの増幅率より小さくなるように設計されている。

## [0023]

経路切替用スイッチ 2 3 はバイパス経路 2 1 上で、バイパス増幅器 2 2 の入力側に配置され、切替制御回路 2 6 の制御の下でオン / オフするスイッチである。

経路切替用スイッチ 2 4 はバイパス経路 2 1 上で、バイパス増幅器 2 2 の出力側に配置され、切替制御回路 2 6 の制御の下でオン / オフするスイッチである。

経路切替用スイッチ 2 5 は主経路上で、ドライバ段増幅器 3 の出力側に配置され、切替制御回路 2 6 の制御の下でオン / オフするスイッチである。

#### [0024]

切替制御回路 2 6 は経路切替用スイッチ 2 3 , 2 4 , 2 5 をオン / オフすることで、 R F 信号を流す経路として、主経路又はバイパス経路 2 1 を選択する回路である。

この実施の形態 2 では、バイパス増幅器 2 2 、経路切替用スイッチ 2 3 , 2 4 , 2 5 及び切替制御回路 2 6 がシリコン基板 1 1 上に形成されている。

#### [0025]

次に動作について説明する。

まず、Vcc電圧制御回路9は、Vcc電源8から電源電圧Vccの供給を受けると、ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器22のドレイン又はコレクタに供給する直流電圧を制御することで、ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器22を駆動可能な状態に設定する。

バイアス回路10は、ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器22におけるRF信号の増幅率等を所望値に設定するため、例えば、外部から与えられる増幅率の設定情報等にしたがって、ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器22のゲート又はベースに供給する直流電圧又は直流電流を制御することで、ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器22のバイアスを設定する。

### [0026]

バイアス回路10によりドライバ段増幅器3、最終段増幅器5及びバイパス増幅器22のバイアスが設定されている状態で、RF入力端子1からRF信号が入力されると、そのRF信号は入力整合回路2を通過する。

切替制御回路26は、例えば、外部からRF信号を低出力電力で駆動する旨を示す制御情報を入力すると、経路切替用スイッチ23,24をオンに制御して、経路切替用スイッチ25をオフに制御することで、RF信号を流す経路として、バイパス経路21を選択する。

### [0027]

これにより、入力整合回路 2 を通過した R F 信号がバイパス増幅器 2 2 に入力される。 バイパス増幅器 2 2 は、入力整合回路 2 を通過してきた R F 信号を増幅し、増幅後の R F 信号を出力整合回路 6 に出力する。

バイパス増幅器 2 2 から出力された R F 信号は、出力整合回路 6 を通過して、 R F 出力端子 7 から外部に出力される。

### [0028]

切替制御回路26は、例えば、外部からRF信号を高出力電力で駆動する旨を示す制御情報を入力すると、経路切替用スイッチ23,24をオフに制御して、経路切替用スイッチ25をオンに制御することで、RF信号を流す経路として、主経路を選択する。

これにより、入力整合回路 2 を通過した R F 信号がドライバ段増幅器 3 に入力される。ドライバ段増幅器 3 は、入力整合回路 2 を通過してきた R F 信号を増幅し、増幅後の R F 信号を段間整合回路 4 に出力する。

### [0029]

ドライバ段増幅器 3 から出力された R F 信号は、段間整合回路 4 を通過して最終段増幅器 5 に入力される。

最終段増幅器 5 は、段間整合回路 4 を通過してきた R F 信号を増幅し、増幅後の R F 信号を出力整合回路 6 に出力する。

最終段増幅器 5 から出力された R F 信号は、出力整合回路 6 を通過して、 R F 出力端子 7 から外部に出力される。

#### [0030]

図2の高周波増幅器モジュールでは、ドライバ段増幅器3及びバイパス増幅器22がシリコン基板11上に形成され、最終段増幅器5がガリウム砒素基板上に形成されているが、高周波特性に支配的な増幅器は最終段増幅器5であり、ドライバ段増幅器3及びバイパス増幅器22は高周波特性に特段の影響を与えない増幅器である。

このため、高周波特性に優れているガリウム砒素基板上に最終段増幅器5を形成すれば

、ドライバ段増幅器 3 及びバイパス増幅器 2 2 をシリコン基板 1 1 上に形成しても、モジュールの全体がガリウム砒素基板上に形成されている場合と同等の高周波特性を維持することができる。

このように、ドライバ段増幅器 3 及びバイパス増幅器 2 2 をシリコン基板 1 1 上に形成することで、ガリウム砒素基板で形成するチップの面積を削減することができるため、低コスト化を実現することができる。

### [ 0 0 3 1 ]

なお、この実施の形態 2 では、経路切替用スイッチ 2 3 , 2 4 , 2 5 がシリコン基板 1 1 上に形成されているが、経路切替用スイッチ 2 3 , 2 4 , 2 5 がガリウム砒素基板上に形成されていてもよい。

また、この実施の形態 2 では、高周波増幅器モジュールが入力整合回路 2 、段間整合回路 4 及び出力整合回路 6 を実装しているものを示したが、入力整合回路 2 、段間整合回路 4 及び出力整合回路 6 の一部又は全部を実装していない高周波増幅器モジュールであってもよい。

### [0032]

実施の形態3.

図3はこの発明の実施の形態3による高周波増幅器モジュールを示す構成図であり、図において、図1と同一符号は同一または相当部分を示すので説明を省略する。

バイパス経路31は一端がドライバ段増幅器3の出力側に接続され、他端が最終段増幅器5の出力側に接続されている経路である。

この実施の形態3では、ドライバ段増幅器3及び最終段増幅器5が配置されている経路を「主経路」と称する。

バイパス増幅器 3 2 はバイパス経路 3 1 上に配置されている最終段増幅器であり、バイパス増幅器 3 2 のサイズは、最終段増幅器 5 のサイズより小さくなるように設計されている。

### [0033]

経路切替用スイッチ33はバイパス経路31上で、バイパス増幅器32の入力側に配置され、切替制御回路36の制御の下でオン/オフするスイッチである。

経路切替用スイッチ34はバイパス経路31上で、バイパス増幅器32の出力側に配置され、切替制御回路36の制御の下でオン/オフするスイッチである。

経路切替用スイッチ35は主経路上で、ドライバ段増幅器3の出力側に配置され、切替制御回路36の制御の下でオン/オフするスイッチである。

#### [0034]

切替制御回路 3 6 は経路切替用スイッチ 3 3 , 3 4 , 3 5 をオン / オフすることで、 R F 信号を流す経路として、主経路又はバイパス経路 3 1 を選択する回路である。

この実施の形態3では、バイパス増幅器32、経路切替用スイッチ33,34,35及び切替制御回路36がシリコン基板11上に形成されている。

### [0035]

次に動作について説明する。

まず、Vcc電圧制御回路9は、Vcc電源8から電源電圧Vccの供給を受けると、ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器32のドレイン又はコレクタに供給する直流電圧を制御することで、ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器32を駆動可能な状態に設定する。

バイアス回路10は、ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器32におけるRF信号の増幅率等を所望値に設定するため、例えば、外部から与えられる増幅率の設定情報等にしたがって、ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器32のゲート又はベースに供給する直流電圧又は直流電流を制御することで、ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器32のバイアスを設定する。

### [0036]

バイアス回路10によりドライバ段増幅器3、最終段増幅器5及びバイパス増幅器32

のバイアスが設定されている状態で、 R F 入力端子 1 から R F 信号が入力されると、その R F 信号は入力整合回路 2 を通過する。

ドライバ段増幅器 3 は、入力整合回路 2 を通過してきた R F 信号を増幅する。

#### [ 0 0 3 7 ]

切替制御回路 3 6 は、例えば、外部から R F 信号を低出力電力で駆動する旨を示す制御情報を入力すると、経路切替用スイッチ 3 3 , 3 4 をオンに制御して、経路切替用スイッチ 3 5 をオフに制御することで、 R F 信号を流す経路として、バイパス経路 3 1 を選択する。

これにより、ドライバ段増幅器 3 により増幅された R F 信号がバイパス増幅器 3 2 に入力される。

バイパス増幅器 3 2 は、入力整合回路 2 を通過してきた R F 信号を増幅し、増幅後の R F 信号を出力整合回路 6 に出力する。

バイパス増幅器32から出力されたRF信号は、出力整合回路6を通過して、RF出力端子7から外部に出力される。

### [0038]

切替制御回路36は、例えば、外部からRF信号を高出力電力で駆動する旨を示す制御情報を入力すると、経路切替用スイッチ33,34をオフに制御して、経路切替用スイッチ35をオンに制御することで、RF信号を流す経路として、主経路を選択する。

これにより、ドライバ段増幅器 3 により増幅された R F 信号は、段間整合回路 4 を通過して最終段増幅器 5 に入力される。

最終段増幅器 5 は、段間整合回路 4 を通過してきた R F 信号を増幅し、増幅後の R F 信号を出力整合回路 6 に出力する。

最終段増幅器5から出力されたRF信号は、出力整合回路6を通過して、RF出力端子7から外部に出力される。

#### [0039]

図3の高周波増幅器モジュールでは、ドライバ段増幅器3及びバイパス増幅器32がシリコン基板11上に形成され、最終段増幅器5がガリウム砒素基板上に形成されているが、高周波特性に支配的な増幅器は最終段増幅器5であり、ドライバ段増幅器3及びバイパス増幅器32は高周波特性に特段の影響を与えない増幅器である。

このため、高周波特性に優れているガリウム砒素基板上に最終段増幅器 5 を形成すれば、ドライバ段増幅器 3 及びバイパス増幅器 3 2 をシリコン基板 1 1 上に形成しても、モジュールの全体がガリウム砒素基板上に形成されている場合と同等の高周波特性を維持することができる。

このように、ドライバ段増幅器 3 及びバイパス増幅器 3 2 をシリコン基板 1 1 上に形成することで、ガリウム砒素基板で形成するチップの面積を削減することができるため、低コスト化を実現することができる。

## [0040]

なお、この実施の形態 3 では、経路切替用スイッチ 3 3 , 3 4 , 3 5 がシリコン基板 1 1 上に形成されているが、経路切替用スイッチ 3 3 , 3 4 , 3 5 がガリウム砒素基板上に形成されていてもよい。

また、この実施の形態 3 では、高周波増幅器モジュールが入力整合回路 2 、段間整合回路 4 及び出力整合回路 6 を実装しているものを示したが、入力整合回路 2 、段間整合回路 4 及び出力整合回路 6 の一部又は全部を実装していない高周波増幅器モジュールであってもよい。

### [0041]

### 実施の形態4.

図4はこの発明の実施の形態4による高周波増幅器モジュールを示す構成図であり、図において、図1と同一符号は同一または相当部分を示すので説明を省略する。

バイパス経路41は一端がドライバ段増幅器3の入力側に接続され、他端が最終段増幅器5の出力側に接続されている経路である。

この実施の形態 4 では、ドライバ段増幅器 3 及び最終段増幅器 5 が配置されている経路を「主経路」と称する。

#### [0042]

バイパスドライバ段増幅器42はバイパス経路41上に配置され、1~N段の増幅素子から構成されている多段の増幅器であり、バイパスドライバ段増幅器42はRF入力端子 1から入力されたRF信号を増幅するデバイスである。

バイパス最終段増幅器43はバイパス経路41上に配置され、バイパスドライバ段増幅器42により増幅されたRF信号を更に増幅して、増幅後のRF信号を出力整合回路6に出力するデバイスである。

なお、バイパス最終段増幅器 4 3 のサイズは、最終段増幅器 5 のサイズより小さくなるように設計されている。

### [0043]

経路切替用スイッチ44はバイパス経路41上で、バイパスドライバ段増幅器42の入力側に配置され、切替制御回路47の制御の下でオン/オフするスイッチである。

経路切替用スイッチ45はバイパス経路41上で、バイパスドライバ段増幅器42の出力側に配置され、切替制御回路47の制御の下でオン/オフするスイッチである。

経路切替用スイッチ46は主経路上で、ドライバ段増幅器3の出力側に配置され、切替制御回路47の制御の下でオン/オフするスイッチである。

#### [0044]

切替制御回路47は経路切替用スイッチ44,45,46をオン/オフすることで、 RF信号を流す経路として、主経路又はバイパス経路41を選択する回路である。

この実施の形態 4 では、バイパスドライバ段増幅器 4 2 、 経路切替用スイッチ 4 4 , 4 5 , 4 6 及び切替制御回路 4 6 がシリコン基板 1 1 上に形成されている。

バイパス最終段増幅器43は、ガリウム砒素基板上に形成されている。

#### [0045]

次に動作について説明する。

まず、Vcc電圧制御回路9は、Vcc電源8から電源電圧Vccの供給を受けると、ドライバ段増幅器3、最終段増幅器5、バイパスドライバ段増幅器42及びバイパス最終段増幅器43のドレイン又はコレクタに供給する直流電圧を制御することで、ドライバ段増幅器3、最終段増幅器5、バイパスドライバ段増幅器42及びバイパス最終段増幅器43を駆動可能な状態に設定する。

バイアス回路10は、ドライバ段増幅器3、最終段増幅器5、バイパスドライバ段増幅器42及びバイパス最終段増幅器43におけるRF信号の増幅率等を所望値に設定するため、例えば、外部から与えられる増幅率の設定情報等にしたがって、ドライバ段増幅器3、最終段増幅器5、バイパスドライバ段増幅器42及びバイパス最終段増幅器43のゲート又はベースに供給する直流電圧又は直流電流を制御することで、ドライバ段増幅器3、最終段増幅器5、バイパスドライバ段増幅器42及びバイパス最終段増幅器43のバイアスを設定する。

### [0046]

バイアス回路10によりドライバ段増幅器3、最終段増幅器5、バイパスドライバ段増幅器42及びバイパス最終段増幅器43のバイアスが設定されている状態で、RF入力端子1からRF信号が入力されると、そのRF信号は入力整合回路2を通過する。

切替制御回路46は、例えば、外部からRF信号を低出力電力で駆動する旨を示す制御情報を入力すると、経路切替用スイッチ44,45をオンに制御して、経路切替用スイッチ46をオフに制御することで、RF信号を流す経路として、バイパス経路41を選択する。

### [0047]

これにより、入力整合回路 2 を通過した R F 信号がバイパスドライバ段増幅器 4 2 に入力される。

バイパスドライバ段増幅器42は、入力整合回路2を通過してきたRF信号を増幅し、

増幅後のRF信号をバイパス最終段増幅器43に出力する。

バイパス最終段増幅器43は、バイパスドライバ段増幅器42により増幅されたRF信号を更に増幅し、増幅後のRF信号を出力整合回路6に出力する。

バイパス最終段増幅器43から出力されたRF信号は、出力整合回路6を通過して、RF出力端子7から外部に出力される。

### [0048]

切替制御回路46は、例えば、外部からRF信号を高出力電力で駆動する旨を示す制御情報を入力すると、経路切替用スイッチ44,45をオフに制御して、経路切替用スイッチ46をオンに制御することで、RF信号を流す経路として、主経路を選択する。

これにより、入力整合回路 2 を通過した R F 信号がドライバ段増幅器 3 に入力される。 ドライバ段増幅器 3 は、入力整合回路 2 を通過してきた R F 信号を増幅し、増幅後の R F 信号を段間整合回路 4 に出力する。

### [0049]

ドライバ段増幅器3から出力されたRF信号は、段間整合回路4を通過して最終段増幅器5に入力される。

最終段増幅器 5 は、段間整合回路 4 を通過してきた R F 信号を増幅し、増幅後の R F 信号を出力整合回路 6 に出力する。

最終段増幅器5から出力されたRF信号は、出力整合回路6を通過して、RF出力端子7から外部に出力される。

### [0050]

図4の高周波増幅器モジュールでは、ドライバ段増幅器3及びバイパスドライバ段増幅器42がシリコン基板11上に形成され、最終段増幅器5及びバイパス最終段増幅器43がガリウム砒素基板上に形成されているが、高周波特性に支配的な増幅器は最終段増幅器5及びバイパス最終段増幅器43であり、ドライバ段増幅器3及びバイパスドライバ段増幅器42は高周波特性に特段の影響を与えない増幅器である。

このため、高周波特性に優れているガリウム砒素基板上に最終段増幅器 5 及びバイパス最終段増幅器 4 3 を形成すれば、ドライバ段増幅器 3 及びバイパスドライバ段増幅器 4 2 をシリコン基板 1 1 上に形成しても、モジュールの全体がガリウム砒素基板上に形成されている場合と同等の高周波特性を維持することができる。

このように、ドライバ段増幅器 3 及びバイパスドライバ段増幅器 4 2 をシリコン基板 1 1 上に形成することで、ガリウム砒素基板で形成するチップの面積を削減することができる。

#### [0051]

なお、この実施の形態 4 では、経路切替用スイッチ 4 4 , 4 5 , 4 6 がシリコン基板 1 1 上に形成されているが、経路切替用スイッチ 4 4 , 4 5 , 4 6 がガリウム砒素基板上に形成されていてもよい。

また、この実施の形態 4 では、高周波増幅器モジュールが入力整合回路 2 、段間整合回路 4 及び出力整合回路 6 を実装しているものを示したが、入力整合回路 2 、段間整合回路 4 及び出力整合回路 6 の一部又は全部を実装していない高周波増幅器モジュールであってもよい。

## [0052]

## 実施の形態5.

図5はこの発明の実施の形態5による高周波増幅器モジュールを示す構成図であり、図において、図1と同一符号は同一または相当部分を示すので説明を省略する。

第 1 のバイパス経路 5 1 は一端がドライバ段増幅器 3 の入力側に接続され、他端がドライバ段増幅器 3 の出力側に接続されている経路である。

第2のバイパス経路52は一端が最終段増幅器5の入力側に接続され、他端が最終段増幅器5の出力側に接続されている経路である。

この実施の形態 5 では、ドライバ段増幅器 3 及び最終段増幅器 5 が配置されている経路を「主経路」と称する。

バイパス増幅器53は第1のバイパス経路51上に配置されているドライバ段増幅器であり、バイパス増幅器52のサイズは、ドライバ段増幅器3のサイズより小さくなるように設計されている。

### [0053]

経路切替用スイッチ54は第1のバイパス経路51上で、バイパス増幅器53の出力側に配置され、切替制御回路57の制御の下でオン/オフするスイッチである。

経路切替用スイッチ55は第2のバイパス経路52上に配置され、切替制御回路57の制御の下でオン/オフするスイッチである。

経路切替用スイッチ 5 6 は主経路上で、ドライバ段増幅器 3 の出力側に配置され、切替制御回路 5 7 の制御の下でオン / オフするスイッチである。

### [0054]

切替制御回路 5 7 は経路切替用スイッチ 5 4 , 5 5 , 5 6 をオン / オフすることで、 R F 信号を流す経路として、主経路又はバイパス経路 5 1 , 5 2 を選択する回路である。

この実施の形態 5 では、バイパス増幅器 5 3 、経路切替用スイッチ 5 4 , 5 5 , 5 6 及び切替制御回路 5 7 がシリコン基板 1 1 上に形成されている。

#### [0055]

次に動作について説明する。

まず、Vcc電圧制御回路9は、Vcc電源8から電源電圧Vccの供給を受けると、ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器53のドレイン又はコレクタに供給する直流電圧を制御することで、ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器53を駆動可能な状態に設定する。

バイアス回路10は、ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器53におけるRF信号の増幅率等を所望値に設定するため、例えば、外部から与えられる増幅率の設定情報等にしたがって、ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器53のゲート又はベースに供給する直流電圧又は直流電流を制御することで、ドライバ段増幅器3、最終段増幅器5及びバイパス増幅器53のバイアスを設定する。

#### [0056]

バイアス回路10によりドライバ段増幅器3、最終段増幅器5及びバイパス増幅器53のバイアスが設定されている状態で、RF入力端子1からRF信号が入力されると、そのRF信号は入力整合回路2を通過する。

切替制御回路 5 7 は、例えば、外部から R F 信号を低出力電力で駆動する旨を示す制御情報を入力すると、経路切替用スイッチ 5 4 , 5 5 をオンに制御して、経路切替用スイッチ 5 6 をオフに制御することで、 R F 信号を流す経路として、第 1 のバイパス経路 5 1 と第 2 のバイパス経路 5 2 を選択する。

### [0057]

これにより、入力整合回路 2 を通過した R F 信号がバイパス増幅器 5 3 に入力される。 バイパス増幅器 5 3 は、入力整合回路 2 を通過してきた R F 信号を増幅し、増幅後の R F 信号を出力する。

バイパス増幅器 5 3 から出力された R F 信号は、第 2 のバイパス経路 5 2 経由で出力整合回路 6 に入力される。

バイパス増幅器22から出力されたRF信号は、出力整合回路6を通過して、RF出力端子7から外部に出力される。

### [0058]

切替制御回路 5 7 は、例えば、外部から R F 信号を中出力電力で駆動する旨を示す制御情報を入力すると、経路切替用スイッチ 5 5 をオンに制御して、経路切替用スイッチ 5 4 , 5 6 をオフに制御することで、 R F 信号を流す経路として、主回路と第 2 のバイパス経路 5 2 を選択する。

これにより、入力整合回路2を通過したRF信号がドライバ段増幅器3に入力される。 ´^^5┓

### [0059]

ドライバ段増幅器3は、入力整合回路2を通過してきたRF信号を増幅し、増幅後のR

F信号を出力する。

ドライバ段増幅器3から出力されたRF信号は、第2のバイパス経路52経由で出力整合回路6に入力される。

ドライバ段増幅器3から出力されたRF信号は、出力整合回路6を通過して、RF出力端子7から外部に出力される。

#### [0060]

切替制御回路 5 7 は、例えば、外部から R F 信号を高出力電力で駆動する旨を示す制御情報を入力すると、経路切替用スイッチ 5 6 をオンに制御して、経路切替用スイッチ 5 4 をオフに制御することで、 R F 信号を流す経路として、主回路を選択する。

これにより、入力整合回路 2 を通過した R F 信号がドライバ段増幅器 3 に入力される。ドライバ段増幅器 3 は、入力整合回路 2 を通過してきた R F 信号を増幅し、増幅後の R F 信号を段間整合回路 4 に出力する。

### [0061]

ドライバ段増幅器3から出力されたRF信号は、段間整合回路4を通過して最終段増幅器5に入力される。

最終段増幅器 5 は、段間整合回路 4 を通過してきた R F 信号を増幅し、増幅後の R F 信号を出力整合回路 6 に出力する。

最終段増幅器 5 から出力された R F 信号は、出力整合回路 6 を通過して、 R F 出力端子 7 から外部に出力される。

### [0062]

図5の高周波増幅器モジュールでは、ドライバ段増幅器3及びバイパス増幅器53がシリコン基板11上に形成され、最終段増幅器5がガリウム砒素基板上に形成されているが、高周波特性に支配的な増幅器は最終段増幅器5であり、ドライバ段増幅器3及びバイパス増幅器53は高周波特性に特段の影響を与えない増幅器である。

このため、高周波特性に優れているガリウム砒素基板上に最終段増幅器 5 を形成すれば、ドライバ段増幅器 3 及びバイパス増幅器 5 3 をシリコン基板 1 1 上に形成しても、モジュールの全体がガリウム砒素基板上に形成されている場合と同等の高周波特性を維持することができる。

このように、ドライバ段増幅器 3 及びバイパス増幅器 5 3 をシリコン基板 1 1 上に形成することで、ガリウム砒素基板で形成するチップの面積を削減することができるため、低コスト化を実現することができる。

## [0063]

なお、この実施の形態 5 では、経路切替用スイッチ 5 4 , 5 5 , 5 6 がシリコン基板 1 上に形成されているが、経路切替用スイッチ 5 4 , 5 5 , 5 6 がガリウム砒素基板上に形成されていてもよい。

また、この実施の形態 5 では、高周波増幅器モジュールが入力整合回路 2 、段間整合回路 4 及び出力整合回路 6 を実装しているものを示したが、入力整合回路 2 、段間整合回路 4 及び出力整合回路 6 の一部又は全部を実装していない高周波増幅器モジュールであってもよい。

### [0064]

実施の形態 6.

図6はこの発明の実施の形態6による高周波増幅器モジュールを示す構成図であり、図において、図1と同一符号は同一または相当部分を示すので説明を省略する。

最終段増幅器 6 1 - 1 ~ 6 1 - Nはドライバ段増幅器 3 の出力側にN個並列に接続されており、ドライバ段増幅器 3 により増幅されたRF信号を更に増幅して、増幅後のRF信号を出力整合回路 6 2 - 1 ~ 6 2 - Nに出力するデバイスである。

出力整合回路 6 2 - 1 ~ 6 2 - N は最終段増幅器 6 1 - 1 ~ 6 1 - N の出力側の整合回路である。

R F 出力端子 6 3 - 1 ~ 6 3 - N は最終段増幅器 6 1 - 1 ~ 6 1 - N により増幅された R F 信号を出力する端子である。

#### [0065]

経路切替用スイッチ 6 4 は切替制御回路 6 5 の制御の下で、ドライバ段増幅器 3 により 増幅された R F 信号を何れかの最終段増幅器 6 1 に出力するスイッチである。

切替制御回路65は経路切替用スイッチ64の出力先を切り替える回路である。

### [0066]

この実施の形態6では、ドライバ段増幅器3、Vcc電圧制御回路9、バイパス回路10、経路切替用スイッチ64及び切替制御回路65がシリコン基板11上に形成されている。

入力整合回路 2 及び出力整合回路 6 2 - 1 ~ 6 2 - N と最終段増幅器 6 1 - 1 ~ 6 1 - N は、ガリウム砒素基板上に形成されている。

### [0067]

次に動作について説明する。

まず、Vcc電圧制御回路9は、Vcc電源8から電源電圧Vccの供給を受けると、ドライバ段増幅器3及び最終段増幅器61-1~61-Nのドレイン又はコレクタに供給する直流電圧を制御することで、ドライバ段増幅器3及び最終段増幅器61-1~61-Nを駆動可能な状態に設定する。

バイアス回路10は、ドライバ段増幅器3及び最終段増幅器61-1~61-NにおけるRF信号の増幅率等を所望値に設定するため、例えば、外部から与えられる増幅率の設定情報等にしたがって、ドライバ段増幅器3及び最終段増幅器61-1~61-Nのゲート又はベースに供給する直流電圧又は直流電流を制御することで、ドライバ段増幅器3及び最終段増幅器61-1~61-Nのバイアスを設定する。

#### [0068]

バイアス回路10によりドライバ段増幅器3及び最終段増幅器61-1~61-Nのバイアスが設定されている状態で、RF入力端子1からRF信号が入力されると、そのRF信号は入力整合回路2を通過する。

この実施の形態 6 では、 R F 入力端子 1 から周波数が異なる R F 信号が順次入力される場合を想定する。

切替制御回路65は、例えば、外部からRF信号の周波数を示す情報を入力すると、経路切替用スイッチ64の出力先を上記RF信号の周波数に対応する最終段増幅器61に切り替えて、そのRF信号が当該最終段増幅器61に入力されるようにする。

例えば、RF信号の周波数がAHzならば、経路切替用スイッチ64の出力先を最終段増幅器61-1に切り替え、RF信号の周波数がBHzならば、経路切替用スイッチ64の出力先を最終段増幅器61-2に切り替え、RF信号の周波数がCHzならば、経路切替用スイッチ64の出力先を最終段増幅器61-Nに切り替えるようにする。

## [0069]

最終段増幅器 6 1 - 1 ~ 6 1 - Nのうち、ドライバ段増幅器 3 から経路切替用スイッチ 6 4 を介して R F 信号が入力された最終段増幅器 6 1 は、その R F 信号を増幅し、増幅後の R F 信号を出力整合回路 6 2 に出力する。

最終段増幅器 6 1 - 1 ~ 6 1 - Nから出力された R F 信号は、出力整合回路 6 2 - 1 ~ 6 2 - Nを通過して、 R F 出力端子 6 3 - 1 ~ 6 3 - Nから外部に出力される。

## [0070]

図6の高周波増幅器モジュールでは、ドライバ段増幅器3がシリコン基板11上に形成され、最終段増幅器61-1~61-Nがガリウム砒素基板上に形成されているが、高周波特性に支配的な増幅器は最終段増幅器61-1~61-Nであり、ドライバ段増幅器3は高周波特性に特段の影響を与えない増幅器である。

このため、高周波特性に優れているガリウム砒素基板上に最終段増幅器 6 1 - 1 ~ 6 1 - Nを形成すれば、ドライバ段増幅器 3 をシリコン基板 1 1 上に形成しても、モジュールの全体がガリウム砒素基板上に形成されている場合と同等の高周波特性を維持することができる。

このように、ドライバ段増幅器3をシリコン基板11上に形成することで、ガリウム砒

素基板で形成するチップの面積を削減することができるため、低コスト化を実現すること ができる。

### [0071]

なお、この実施の形態 6 では、経路切替用スイッチ 6 4 がシリコン基板 1 1 上に形成されているが、経路切替用スイッチ 6 4 がガリウム砒素基板上に形成されていてもよい。

また、この実施の形態6では、高周波増幅器モジュールが入力整合回路2及び最終段増幅器61-1~61-Nを実装しているものを示したが、入力整合回路2及び最終段増幅器61-1~61-Nの一部又は全部を実装していない高周波増幅器モジュールであってもよい。

また、段間整合回路を実装している高周波増幅器モジュールであってもよい。

### [0072]

実施の形態7.

図 7 はこの発明の実施の形態 7 による高周波増幅器モジュールを示す構成図であり、図において、図 2 と同一符号は同一または相当部分を示すので説明を省略する。

バイパス経路27は一端がドライバ段増幅器3の出力側に接続され、他端が最終段増幅器5の出力側に接続されている経路である。

この実施の形態 7 では、ドライバ段増幅器 3 及び最終段増幅器 5 が配置されている経路を「主経路」と称する。

### [0073]

経路切替用スイッチ 2 8 はバイパス経路 2 7 上に配置され、切替制御回路 2 9 の制御の下でオン / オフするスイッチである。

切替制御回路 2 9 は経路切替用スイッチ 2 5 , 2 8 をオン / オフすることで、 R F 信号を流す経路として、主経路又はバイパス経路 2 7 を選択する回路である。

この実施の形態 7 では、経路切替用スイッチ 2 5 , 2 8 及び切替制御回路 2 9 がシリコン基板 1 1 上に形成されている。

### [0074]

次に動作について説明する。

まず、Vcc電圧制御回路9は、Vcc電源8から電源電圧Vccの供給を受けると、ドライバ段増幅器3及び最終段増幅器5のドレイン又はコレクタに供給する直流電圧を制御することで、ドライバ段増幅器3及び最終段増幅器5を駆動可能な状態に設定する。

バイアス回路10は、ドライバ段増幅器3及び最終段増幅器5におけるRF信号の増幅率等を所望値に設定するため、例えば、外部から与えられる増幅率の設定情報等にしたがって、ドライバ段増幅器3及び最終段増幅器3のゲート又はベースに供給する直流電圧又は直流電流を制御することで、ドライバ段増幅器3及び最終段増幅器5のバイアスを設定する。

#### [0075]

バイアス回路10によりドライバ段増幅器3及び最終段増幅器5のバイアスが設定されている状態で、RF入力端子1からRF信号が入力されると、そのRF信号は入力整合回路2を通過する。

切替制御回路29は、例えば、外部からRF信号を低出力電力で駆動する旨を示す制御情報を入力すると、経路切替用スイッチ28をオンに制御して、経路切替用スイッチ25をオフに制御することで、RF信号を流す経路として、バイパス経路27を選択する。

### [0076]

これにより、入力整合回路 2 を通過した R F 信号がバイパス経路 2 7 経由で出力整合回路 6 に入力される。

バイパス経路27から出力されたRF信号は、出力整合回路6を通過して、RF出力端子7から外部に出力される。

### [0077]

切替制御回路 2 9 は、例えば、外部から R F 信号を高出力電力で駆動する旨を示す制御情報を入力すると、経路切替用スイッチ 2 5 をオンに制御して、経路切替用スイッチ 2 8

をオフに制御することで、RF信号を流す経路として、主経路を選択する。

これにより、入力整合回路 2 を通過した R F 信号がドライバ段増幅器 3 に入力される。ドライバ段増幅器 3 は、入力整合回路 2 を通過してきた R F 信号を増幅し、増幅後の R F 信号を段間整合回路 4 に出力する。

## [0078]

ドライバ段増幅器 3 から出力された R F 信号は、段間整合回路 4 を通過して最終段増幅器 5 に入力される。

最終段増幅器 5 は、段間整合回路 4 を通過してきた R F 信号を増幅し、増幅後の R F 信号を出力整合回路 6 に出力する。

最終段増幅器 5 から出力された R F 信号は、出力整合回路 6 を通過して、 R F 出力端子 7 から外部に出力される。

## [0079]

図7の高周波増幅器モジュールでは、ドライバ段増幅器3がシリコン基板11上に形成され、最終段増幅器5がガリウム砒素基板上に形成されているが、高周波特性に支配的な増幅器は最終段増幅器5であり、ドライバ段増幅器3は高周波特性に特段の影響を与えない増幅器である。

このため、高周波特性に優れているガリウム砒素基板上に最終段増幅器 5 を形成すれば、ドライバ段増幅器 3 をシリコン基板 1 1 上に形成しても、モジュールの全体がガリウム砒素基板上に形成されている場合と同等の高周波特性を維持することができる。

このように、ドライバ段増幅器 3 をシリコン基板 1 1 上に形成することで、ガリウム砒素基板で形成するチップの面積を削減することができるため、低コスト化を実現することができる。

## [0800]

なお、この実施の形態 7 では、経路切替用スイッチ 2 5 , 2 8 がシリコン基板 1 1 上に 形成されているが、経路切替用スイッチ 2 5 , 2 8 がガリウム砒素基板上に形成されてい てもよい。

また、この実施の形態 7 では、高周波増幅器モジュールが入力整合回路 2 、段間整合回路 4 及び出力整合回路 6 を実装しているものを示したが、入力整合回路 2 、段間整合回路 4 及び出力整合回路 6 の一部又は全部を実装していない高周波増幅器モジュールであってもよい。

## [0081]

## 実施の形態8.

図8はこの発明の実施の形態8による高周波増幅器モジュールを示す構成図であり、図において、図2と同一符号は同一または相当部分を示すので説明を省略する。

ガリウム砒素基板 7 1 はガリウム砒素で形成されている基板であり、段間整合回路 4 、 最終段増幅器 5 及び温度検知回路 7 2 が形成されている。

温度検知回路72はガリウム砒素基板71の温度を検知する機能を有し、ガリウム砒素 基板71の温度に応じてバイアス回路10により設定されるバイアスを調整する処理を実 施する。なお、温度検知回路72はバイアス調整手段を構成している。

## [0082]

次に動作について説明する。

ただし、温度検知回路 7 2 が実装されている点以外は、上記実施の形態 1 と同様であるため、ここでは、主に温度検知回路 7 2 の処理内容について説明する。

バイアス回路10は、ドライバ段増幅器3及び最終段増幅器5におけるRF信号の増幅率等を所望値に設定するため、上記実施の形態1と同様に、例えば、外部から与えられる増幅率の設定情報等にしたがって、ドライバ段増幅器3及び最終段増幅器5のゲート又はベースに供給する直流電圧又は直流電流を制御することで、ドライバ段増幅器3及び最終段増幅器5のバイアスを設定する。

## [0083]

このとき、温度検知回路72は、ガリウム砒素基板71の温度を検知する機能を有し、

ガリウム砒素基板 7 1 の温度 T を検知する。

例えば、温度検知回路72が、ガリウム砒素基板71と略同一の温度特性を有するダイオード又はバイポーラトランジスタを備えることで、ガリウム砒素基板71の温度を検知することができる。

温度検知回路72は、ガリウム砒素基板71の温度Tを検知すると、ガリウム砒素基板71の温度Tと予め設定されている基準温度Trefとの差分 Tを算出し、その差分Tに対応する調整信号をバイアス回路10に出力する。

T = T - T r e f

## [0084]

バイアス回路10は、温度検知回路72から差分 Tに対応する調整信号を受けると、その調整信号にしたがって、ドライバ段増幅器3及び最終段増幅器5に対する制御信号(ドライバ段増幅器3及び最終段増幅器5のゲート又はベースに供給する直流電圧又は直流電流を制御する制御電圧)を調整するが、例えば、ガリウム砒素基板71の温度Tが基準温度Trefより高い場合、その差分 Tの絶対値が大きい程、その制御電圧が小さくなるように調整する。

逆に、ガリウム砒素基板 7 1 の温度 T が基準温度 T r e f より低い場合、その差分 T の絶対値が大きい程、その制御電圧が大きくなるように調整する。

これにより、温度補償が可能なバイアス供給が可能になる。

#### [0085]

図8の高周波増幅器モジュールは、ドライバ段増幅器3がシリコン基板11上に形成され、最終段増幅器5はガリウム砒素基板71上に形成されているが、高周波特性に支配的な増幅器は最終段増幅器5であり、ドライバ段増幅器3は高周波特性に特段の影響を与えない増幅器である。

このため、高周波特性に優れているガリウム砒素基板 7 1 上に最終段増幅器 5 を形成すれば、ドライバ段増幅器 3 をシリコン基板 1 1 上に形成しても、モジュールの全体がガリウム砒素基板 7 1 上に形成されている場合と同等の高周波特性を維持することができる。

#### [0086]

さらに、ガリウム砒素基板 7 1 の温度を検知する機能を有し、ガリウム砒素基板 7 1 の温度に応じてバイアス回路 1 0 により設定されるバイアスを調整する温度検知回路 7 2 をガリウム砒素基板 7 1 上に形成しているので、バイアス回路 1 0 をシリコン基板 1 1 上に形成していても、温度補償が可能な高周波増幅器モジュールを得ることができる。

この場合、バイアス回路10をガリウム砒素基板71上に形成する必要がないため、ガリウム砒素基板71で形成するチップの面積を削減することができるようになり、温度補償が可能な高周波増幅器モジュールであっても、低コスト化を実現することができる。

## [0087]

実施の形態9.

図 9 はこの発明の実施の形態 9 による高周波増幅器モジュールを示す構成図であり、図において、図 2 と同一符号は同一または相当部分を示すので説明を省略する。

カレントミラー型バイアス回路 7 3 はガリウム砒素基板 7 1 上に形成され、バイアス回路 1 0 から出力される定電流の制御信号によってカレントミラーを形成する回路であり、バイアス回路 1 0 により設定されるバイアスを調整するバイアス調整手段を構成している

なお、カレントミラー型バイアス回路73を構成しているカレントミラー用トランジスタは、最終段トランジスタ5と同デバイスで構成されているものとする。

#### [0088]

図9の高周波増幅器モジュールでは、カレントミラー型バイアス回路73がガリウム砒素基板71上に形成されており、バイアス回路10から出力される定電流の制御信号によってカレントミラーを形成している。

このため、カレントミラー型バイアス回路 7 3 を構成しているカレントミラー用トランジスタが、最終段トランジスタ 5 と同デバイスで構成されていれば、カレントミラー型バ

イアス回路73によって、バイアス回路10の出力信号である制御信号が、ガリウム砒素 基板71の温度に応じて調整され、温度調整後の制御信号が最終段増幅器5に与えられる

因みに、上記実施の形態 2 では、シリコン基板 1 1 上に形成されているバイアス回路 1 0 の出力信号である制御信号が、直接、ガリウム砒素基板 7 1 上に形成されている最終段増幅器 5 に与えられる。

これにより、温度補償が可能なバイアス供給が可能になる。

## [0089]

図9の高周波増幅器モジュールは、ドライバ段増幅器3がシリコン基板11上に形成され、最終段増幅器5はガリウム砒素基板71上に形成されているが、高周波特性に支配的な増幅器は最終段増幅器5であり、ドライバ段増幅器3は高周波特性に特段の影響を与えない増幅器である。

このため、高周波特性に優れているガリウム砒素基板71上に最終段増幅器5を形成すれば、ドライバ段増幅器3をシリコン基板11上に形成しても、モジュールの全体がガリウム砒素基板71上に形成されている場合と同等の高周波特性を維持することができる。 【0090】

さらに、バイアス回路10から出力される定電流の制御信号によってカレントミラーを 形成するカレントミラー型バイアス回路73をガリウム砒素基板71上に形成しているの で、バイアス回路10をシリコン基板11上に形成していても、温度補償が可能な高周波 増幅器モジュールを得ることができる。

この場合、バイアス回路10をガリウム砒素基板71上に形成する必要がないため、ガリウム砒素基板71で形成するチップの面積を削減することができるようになり、温度補償が可能な高周波増幅器モジュールであっても、低コスト化を実現することができる。

#### [0091]

この実施の形態 9 では、バイアス回路 1 0 から出力される定電流の制御信号によってカレントミラーを形成するカレントミラー型バイアス回路 7 3 をガリウム砒素基板 7 1 上に形成するものを示したが、カレントミラー型バイアス回路 7 3 の代わりに、最終段トランジスタ 5 と同デバイスで構成されているバイポーラトランジスタを含むエミッタフォロア型バイアス回路をガリウム砒素基板 7 1 上に形成するようにしてもよい。

この場合、エミッタフォロア型バイアス回路によって、バイアス回路10の出力信号である定電圧の制御信号が、ガリウム砒素基板71の温度に応じて調整され、温度調整後の制御信号が最終段増幅器5に与えられるようになる。

したがって、カレントミラー型バイアス回路73がガリウム砒素基板71上に形成されている場合と同様に、温度補償が可能なバイアス供給が可能になり、温度補償が可能な高周波増幅器モジュールであっても、低コスト化を実現することができる。

## [0092]

実施の形態10.

図10はこの発明の実施の形態10による高周波増幅器モジュールユニットを示す構成図である。

図10において、RF入力端子81-1~81-MはRF信号を入力する端子である。 この実施の形態10では、RF入力端子81-1~81-Mから周波数が異なるRF信 号が入力される場合を想定する。

高周波増幅器モジュール82-1~82-Mは、上記実施の形態1~5,7~9のいずれかに記載されている高周波増幅器モジュール(図1~図5、図7~図9に記載の高周波増幅器モジュール)であり、高周波増幅器モジュール82-1~82-Mにより増幅されたRF信号がRF出力端子83-1~83-Mから出力される。

#### [0093]

複数の高周波増幅器モジュールを実装している高周波増幅器モジュールユニットを構築する場合でも、図10に示すように、シリコン基板とガリウム砒素基板で形成されている高周波増幅器モジュール82-1~82-Mを実装することで、上記実施の形態1~5,

7~9と同様に、優れた高周波特性を維持しながら、低コスト化を実現することができる 効果を奏する。

#### [0094]

実施の形態11.

図11はこの発明の実施の形態11による高周波増幅器モジュールユニットを示す構成 図であり、図において、図10と同一符号は同一または相当部分を示すので説明を省略す

高周波増幅器モジュール91-1~91-Mは、上記実施の形態6に記載されている高 周波増幅器モジュール(図6に記載の高周波増幅器モジュール)であり、高周波増幅器モ ジュール91-1~91-Mにより増幅されたRF信号がRF出力端子92-1~92-Mから出力される。

#### [0095]

複数の高周波増幅器モジュールを実装している高周波増幅器モジュールユニットを構築 する場合でも、図10に示すように、シリコン基板とガリウム砒素基板で形成されている 高 周 波 増 幅 器 モ ジュ ー ル 9 1 - 1 ~ 9 1 - M を 実 装 す る こ と で 、 上 記 実 施 の 形 態 6 と 同 様 に、優れた高周波特性を維持しながら、低コスト化を実現することができる効果を奏する

### [0096]

なお、本願発明はその発明の範囲内において、各実施の形態の自由な組み合わせ、ある いは各実施の形態の任意の構成要素の変形、もしくは各実施の形態において任意の構成要 素の省略が可能である。

## 【符号の説明】

## [0097]

RF入力端子、 2 入力整合回路、 3 ドライバ段増幅器、 4 段間整合回路、 5 最終段増幅器、6 出力整合回路、7 RF出力端子、8 Vcc電源、9 Vcc電 圧制御回路(電源電圧制御回路)、10 バイアス回路、11 シリコン基板、21,2 7 , 3 1 , 4 1 バイパス経路、2 2 , 3 2 バイパス増幅器、2 3 , 2 4 , 2 5 , 2 8 , 3 3 , 3 4 , 3 5 , 4 4 , 4 5 , 4 6 経 路 切 替 用 ス イ ッ チ 、 2 6 , 2 9 , 3 6 , 4 7 切替制御回路、42 バイパスドライバ段増幅器、43 バイパス最終段増幅器、51 第 1 のバイパス経路、 5 2 第 2 のバイパス経路、 5 3 バイパス増幅器、 5 4 , 5 5 経路切替用スイッチ、57 切替制御回路、61-1~61-N 最終段増幅器 62-1~62-N 出力整合回路、63-1~63-N RF出力端子、64 切替用スイッチ、 6 5 切替制御回路、 7 1 ガリウム砒素基板、 7 2 温度検知回路( バイアス調整手段)、 7 3 カレントミラー型バイアス回路(バイアス調整手段)、 8 1 - 1~81-M RF入力端子、82-1~82-M 高周波増幅器モジュール、83-1~83-M RF出力端子、91-1~91-M 高周波増幅器モジュール、92-1 ~ 9 2 - M R F 出力端子、 1 0 1 R F 入力端子、 1 0 2 ドライバ段増幅器、 1 0 3 最終段増幅器、104 RF出力端子、105 バイパス経路、106 切替制御回路 、107,108 切替スイッチ、109 Vcc電源、110 バイアス回路。

#### 【 手 続 補 正 2 】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

## 【請求項1】

入力端子から入力された信号を増幅する多段構成のドライバ段増幅器と、上記ドライバ 段増幅器により増幅された信号を増幅し、増幅後の信号を出力端子に出力する最終段増幅 器とを備えた高周波増幅器モジュールにおいて、

一端が上記ドライバ段増幅器の入力側に接続され、他端が上記最終段増幅器の出力側に

接続されているバイパス経路と、上記バイパス経路上に配置されているバイパス増幅器と をさらに備え、

上記ドライバ段増幅器がシリコン基板上に形成され、上記最終段増幅器がガリウム砒素 基板上に形成され、上記バイパス増幅器の少なくとも一部が上記シリコン基板上に形成さ れていることを特徴とする高周波増幅器モジュール。

## 【請求項2】

上記バイパス増幅器は、上記最終段増幅器よりサイズが小さ<u>いこ</u>とを特徴とする請求項 1 記載の高周波増幅器モジュール。

### 【請求項3】

上記バイパス経路上に配置され、上記入力端子から入力された信号を増幅する多段構成のバイパスドライバ段増幅器と、上記バイパス経路上配置され、上記バイパスドライバ段増幅器により増幅された信号を増幅し、増幅後の信号を出力端子に出力するバイパス最終段増幅器とを備え、

上記バイパスドライバ段増幅器がシリコン基板上に形成され、上記バイパス最終段増幅器が<u>上記</u>ガリウム砒素基板上に形成されていることを特徴とする請求項 1 記載の高周波増幅器モジュール。

## 【請求項4】

一端が<u>上記</u>ドライバ段増幅器の入力側に接続され、他端が<u>上記</u>ドライバ段増幅器の出力側に接続されている第1のバイパス経路と、一端が<u>上記</u>最終段増幅器の入力側に接続され、他端が上記最終段増幅器の出力側に接続されている第2のバイパス経路と、上記第1のバイパス経路上に配置され、上記ドライバ段増幅器よりサイズが小さいバイパス増幅器とを備え、

上記バイパス増幅器が<u>上記</u>シリコン基板上に形成されていることを特徴とする請求項 1 記載の高周波増幅器モジュール。

#### 【請求項5】

上記ガリウム砒素基板上に形成されている<u>上記</u>最終段増幅器が、<u>上記</u>ドライバ段増幅器の出力側に複数並列に接続されていることを特徴とする請求項 1 記載の高周波増幅器モジュール。

## 【請求項6】

一端が<u>上記</u>ドライバ段増幅器の出力側に接続され、他端が<u>上記</u>最終段増幅器の出力側に接続されているバイパス経路を備えていることを特徴とする請求項 1 記載の高周波増幅器 モジュール。

### 【請求項7】

上記ドライバ段増幅器の入力側に入力整合回路、上記ドライバ段増幅器と<u>上記</u>最終段増幅器の間に段間整合回路、上記最終段増幅器の出力側に出力整合回路が配置されており、上記入力整合回路、上記段間整合回路及び上記出力整合回路の一部又は全部が<u>上記</u>ガリウム砒素基板上に形成されていることを特徴とする請求項1記載の高周波増幅器モジュール

## 【請求項8】

上記ドライバ段増幅器の入力側に入力整合回路、上記ドライバ段増幅器と上記最終段増幅器の間に段間整合回路、上記最終段増幅器の出力側に出力整合回路が配置されており、上記入力整合回路、上記段間整合回路及び上記出力整合回路の一部又は全部が上記シリコン基板上又は外部のモジュール上に形成されていることを特徴とする請求項1記載の高周波増幅器モジュール。

#### 【請求項9】

上記ドライバ段増幅器及び上記最終段増幅器が配置されている主経路又はバイパス経路のうち、信号を流す経路を選択する経路切替用スイッチが設けられており、上記経路切替用スイッチが上記シリコン基板上に形成されていることを特徴とする請求項<u>1</u>記載の高周波増幅器モジュール。

## 【請求項10】

上記経路切替用スイッチを制御する切替制御回路が設けられており、上記切替制御回路が上記シリコン基板上に形成されていることを特徴とする請求項<u>9</u>記載の高周波増幅器モジュール。

### 【請求項11】

複数の最終段増幅器のうち、<u>上記</u>ドライバ段増幅器により増幅された信号を与える最終段増幅器を切り替える経路切替用スイッチが設けられており、上記経路切替用スイッチが 上記シリコン基板上に形成されていることを特徴とする請求項<u>5</u>記載の高周波増幅器モジュール。

## 【請求項12】

上記経路切替用スイッチを制御する切替制御回路が設けられており、上記切替制御回路が上記シリコン基板上に形成されていることを特徴とする請求項<u>1 1</u>記載の高周波増幅器モジュール。

#### 【請求項13】

上記ドライバ段増幅器及び上記最終段増幅器のバイアスを設定するバイアス回路が設けられており、上記バイアス回路が上記シリコン基板上に形成されていることを特徴とする請求項1記載の高周波増幅器モジュール。

## 【請求項14】

上記ドライバ段増幅器及び上記最終段増幅器の電源電圧を制御する電源電圧制御回路が設けられており、上記電源電圧制御回路が上記シリコン基板上に形成されていることを特徴とする請求項1記載の高周波増幅器モジュール。

### 【請求項15】

上記ガリウム砒素基板上に形成されており、上記バイアス回路により設定されるバイアスを調整するバイアス調整手段を備えていることを特徴とする請求項<u>13</u>記載の高周波増幅器モジュール。

#### 【請求項16】

上記バイアス調整手段が、上記ガリウム砒素基板の温度を検知する温度検知回路で構成されており、上記温度検知回路が、上記ガリウム砒素基板の温度に応じて上記バイアス回路により設定されるバイアスを調整することを特徴とする請求項<u>15</u>記載の高周波増幅器モジュール。

## 【請求項17】

上記バイアス調整手段が、バイポーラトランジスタを含むカレントミラー型のバイアス回路で構成されていることを特徴とする請求項15記載の高周波増幅器モジュール。

#### 【請求項18】

上記バイアス調整手段が、バイポーラトランジスタを含むエミッタフォロア型のバイアス回路で構成されていることを特徴とする請求項<u>15</u>記載の高周波増幅器モジュール。

#### 【請求項19】

請求項1記載の高周波増幅器モジュールが複数個実装されている高周波増幅器モジュールユニット。

## 【手続補正書】

【提出日】平成26年9月22日(2014.9.22)

## 【手続補正1】

【補正対象書類名】明細書

【補正対象項目名】0008

# 【補正方法】変更

## 【補正の内容】

## [0008]

この発明に係る高周波増幅器モジュールは、入力端子から入力された信号を増幅する多段構成のドライバ段増幅器と、そのドライバ段増幅器により増幅された信号を増幅し、増幅後の信号を出力端子に出力する最終段増幅器と、一端がドライバ段増幅器の入力側に接続され、他端が最終段増幅器の出力側に接続されているバイパス経路と、バイパス経路上

に配置されているバイパス増幅器と<u>を備え</u>、そのドライバ段増幅器がシリコン基板上に形成され、その最終段増幅器がガリウム砒素基板上に形成され、バイパス増幅器の少なくとも一部がシリコン基板上に形成されて<u>おり、さらに、そのドライバ段増</u>幅器及び最終段増幅器のバイアスを設定するバイアス回路がシリコン基板上に形成され、そのバイアス回路により設定されるバイアスを調整するバイアス調整手段がガリウム砒素基板上に形成され、そのバイアス調整手段が、そのガリウム砒素基板の温度を検知する温度検知回路で構成されており、その温度検知回路が、そのガリウム砒素基板の温度に応じてバイアス回路により設定されるバイアスを調整するようにしたものである。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0009

【補正方法】変更

【補正の内容】

[0009]

この発明によれば、入力端子から入力された信号を増幅する多段構成のドライバ段増幅器と、そのドライバ段増幅器により増幅された信号を増幅し、増幅後の信号を出力端子に出力する最終段増幅器とを備え、一端がドライバ段増幅器の入力側に接続され、他端が最終段増幅器の出力側に接続されているバイパス経路と、バイパス経路上に配置されているバイパス増幅器とをさらに備え、そのドライバ段増幅器がシリコン基板上に形成され、その最終段増幅器がガリウム砒素基板上に形成され、バイパス増幅器の少なくとも一部がシリコン基板上に形成されているように構成したので、モジュールの全体がガリウム砒素基板上に形成されている場合と同等の高周波特性を維持しながら、低コスト化を実現することができる効果がある。

また、バイアス調整手段が、ガリウム砒素基板の温度を検知する温度検知回路で構成されており、その温度検知回路が、そのガリウム砒素基板の温度に応じてバイアス回路により設定されるバイアスを調整するように構成したので、温度補償が可能な高周波増幅器モジュールであっても、低コスト化を実現することができる効果がある。

【手続補正3】

【補正対象書類名】明細書

【補正対象項目名】0044

【補正方法】変更

【補正の内容】

[0044]

切替制御回路47は経路切替用スイッチ44,45,46をオン/オフすることで、 RF信号を流す経路として、主経路又はバイパス経路41を選択する回路である。

この実施の形態 4 では、バイパスドライバ段増幅器 4 2 、経路切替用スイッチ 4 4 , 4 5 , 4 6 及び切替制御回路 <u>4 7</u> がシリコン基板 1 1 上に形成されている。

バイパス最終段増幅器43は、ガリウム砒素基板上に形成されている。

【手続補正4】

【補正対象書類名】明細書

【補正対象項目名】0046

【補正方法】変更

【補正の内容】

[0046]

バイアス回路10によりドライバ段増幅器3、最終段増幅器5、バイパスドライバ段増幅器42及びバイパス最終段増幅器43のバイアスが設定されている状態で、RF入力端子1からRF信号が入力されると、そのRF信号は入力整合回路2を通過する。

切替制御回路<u>47</u>は、例えば、外部からRF信号を低出力電力で駆動する旨を示す制御情報を入力すると、経路切替用スイッチ44,45をオンに制御して、経路切替用スイッチ46をオフに制御することで、RF信号を流す経路として、バイパス経路41を選択す

る。

【手続補正5】

【補正対象書類名】明細書

【補正対象項目名】0048

【補正方法】変更

【補正の内容】

[0048]

切替制御回路47は、例えば、外部からRF信号を高出力電力で駆動する旨を示す制御情報を入力すると、経路切替用スイッチ44,45をオフに制御して、経路切替用スイッチ46をオンに制御することで、RF信号を流す経路として、主経路を選択する。

これにより、入力整合回路 2 を通過した R F 信号がドライバ段増幅器 3 に入力される。ドライバ段増幅器 3 は、入力整合回路 2 を通過してきた R F 信号を増幅し、増幅後の R F 信号を段間整合回路 4 に出力する。

【手続補正6】

【補正対象書類名】明細書

【補正対象項目名】0052

【補正方法】変更

【補正の内容】

[0052]

実施の形態5.

図5はこの発明の実施の形態5による高周波増幅器モジュールを示す構成図であり、図において、図1と同一符号は同一または相当部分を示すので説明を省略する。

第 1 のバイパス経路 5 1 は一端がドライバ段増幅器 3 の入力側に接続され、他端がドライバ段増幅器 3 の出力側に接続されている経路である。

第2のバイパス経路52は一端が最終段増幅器5の入力側に接続され、他端が最終段増幅器5の出力側に接続されている経路である。

この実施の形態 5 では、ドライバ段増幅器 3 及び最終段増幅器 5 が配置されている経路を「主経路」と称する。

バイパス増幅器 5 3 は第 1 のバイパス経路 5 1 上に配置されているドライバ段増幅器であり、バイパス増幅器 5 3 のサイズは、ドライバ段増幅器 3 のサイズより小さくなるように設計されている。

【手続補正7】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

入力端子から入力された信号を増幅する多段構成のドライバ段増幅器と、

上記ドライバ段増幅器により増幅された信号を増幅し、増幅後の信号を出力端子に出力する最終段増幅器と、

一端が上記ドライバ段増幅器の入力側に接続され、他端が上記最終段増幅器の出力側に接続されているバイパス経路と、

上記バイパス経路上に配置されているバイパス増幅器とを備え、

上記ドライバ段増幅器がシリコン基板上に形成され、上記最終段増幅器がガリウム砒素基板上に形成され、上記バイパス増幅器の少なくとも一部が上記シリコン基板上に形成されており、

<u>さらに、上記ドライバ段増幅器及び上記最終段増幅器のバイアスを設定するバイアス回</u>路が上記シリコン基板上に形成され、

上記バイアス回路により設定されるバイアスを調整するバイアス調整手段が上記ガリウ

#### ム砒素基板上に形成され、

上記バイアス調整手段が、上記ガリウム砒素基板の温度を検知する温度検知回路で構成されており、上記温度検知回路が、上記ガリウム砒素基板の温度に応じて上記バイアス回路により設定されるバイアスを調整することを特徴とする高周波増幅器モジュール。

## 【請求項2】

上記バイパス増幅器は、上記最終段増幅器よりサイズが小さいことを特徴とする請求項1 記載の高周波増幅器モジュール。

## 【請求項3】

上記バイパス経路上に配置され、上記入力端子から入力された信号を増幅する多段構成のバイパスドライバ段増幅器と、上記バイパス経路上配置され、上記バイパスドライバ段増幅器により増幅された信号を増幅し、増幅後の信号を出力端子に出力するバイパス最終段増幅器とを備え、

上記バイパスドライバ段増幅器がシリコン基板上に形成され、上記バイパス最終段増幅器が上記ガリウム砒素基板上に形成されていることを特徴とする請求項 1 記載の高周波増幅器モジュール。

#### 【請求項4】

一端が上記ドライバ段増幅器の入力側に接続され、他端が上記ドライバ段増幅器の出力側に接続されている第1のバイパス経路と、一端が上記最終段増幅器の入力側に接続され、他端が上記最終段増幅器の出力側に接続されている第2のバイパス経路と、上記第1のバイパス経路上に配置され、上記ドライバ段増幅器よりサイズが小さいバイパス増幅器とを備え、

上記バイパス増幅器が上記シリコン基板上に形成されていることを特徴とする請求項 1 記載の高周波増幅器モジュール。

#### 【請求項5】

上記ガリウム砒素基板上に形成されている上記最終段増幅器が、上記ドライバ段増幅器の出力側に複数並列に接続されていることを特徴とする請求項 1 記載の高周波増幅器モジュール。

#### 【請求項6】

一端が上記ドライバ段増幅器の出力側に接続され、他端が上記最終段増幅器の出力側に接続されているバイパス経路を備えていることを特徴とする請求項 1 記載の高周波増幅器モジュール。

## 【請求項7】

上記ドライバ段増幅器の入力側に入力整合回路、上記ドライバ段増幅器と上記最終段増幅器の間に段間整合回路、上記最終段増幅器の出力側に出力整合回路が配置されており、上記入力整合回路、上記段間整合回路及び上記出力整合回路の一部又は全部が上記ガリウム砒素基板上に形成されていることを特徴とする請求項1記載の高周波増幅器モジュール

## 【請求項8】

上記ドライバ段増幅器の入力側に入力整合回路、上記ドライバ段増幅器と上記最終段増幅器の間に段間整合回路、上記最終段増幅器の出力側に出力整合回路が配置されており、上記入力整合回路、上記段間整合回路及び上記出力整合回路の一部又は全部が上記シリコン基板上又は外部のモジュール上に形成されていることを特徴とする請求項1記載の高周波増幅器モジュール。

# 【請求項9】

上記ドライバ段増幅器及び上記最終段増幅器が配置されている主経路又はバイパス経路のうち、信号を流す経路を選択する経路切替用スイッチが設けられており、上記経路切替用スイッチが上記シリコン基板上に形成されていることを特徴とする請求項 1 記載の高周波増幅器モジュール。

## 【請求項10】

上記経路切替用スイッチを制御する切替制御回路が設けられており、上記切替制御回路

が上記シリコン基板上に形成されていることを特徴とする請求項9記載の高周波増幅器モジュール。

## 【請求項11】

複数の最終段増幅器のうち、上記ドライバ段増幅器により増幅された信号を与える最終段増幅器を切り替える経路切替用スイッチが設けられており、上記経路切替用スイッチが上記シリコン基板上に形成されていることを特徴とする請求項 5 記載の高周波増幅器モジュール。

## 【請求項12】

上記経路切替用スイッチを制御する切替制御回路が設けられており、上記切替制御回路が上記シリコン基板上に形成されていることを特徴とする請求項11記載の高周波増幅器 モジュール。

#### 【請求項13】

上記ドライバ段増幅器及び上記最終段増幅器の電源電圧を制御する電源電圧制御回路が設けられており、上記電源電圧制御回路が上記シリコン基板上に形成されていることを特徴とする請求項1記載の高周波増幅器モジュール。

#### 【請求項14】

入力端子から入力された信号を増幅する多段構成のドライバ段増幅器と、

上記ドライバ段増幅器により増幅された信号を増幅し、増幅後の信号を出力端子に出力 する最終段増幅器と、

一端が上記ドライバ段増幅器の入力側に接続され、他端が上記最終段増幅器の出力側に接続されているバイパス経路と、

上記バイパス経路上に配置されているバイパス増幅器とを備え、

上記ドライバ段増幅器がシリコン基板上に形成され、上記最終段増幅器がガリウム砒素 基板上に形成され、上記バイパス増幅器の少なくとも一部が上記シリコン基板上に形成さ れており、

<u>さらに、上記ドライバ段増幅器及び上記最終段増幅器のバイアスを設定するバイアス回</u>路が上記シリコン基板上に形成され、

上記バイアス調整手段が、バイポーラトランジスタを含むカレントミラー型のバイアス 回路で構成されていることを特徴とする高周波増幅器モジュール。

## 【請求項15】

入力端子から入力された信号を増幅する多段構成のドライバ段増幅器と、

上記ドライバ段増幅器により増幅された信号を増幅し、増幅後の信号を出力端子に出力 する最終段増幅器と、

一端が上記ドライバ段増幅器の入力側に接続され、他端が上記最終段増幅器の出力側に接続されているバイパス経路と、

上記バイパス経路上に配置されているバイパス増幅器とを備え、

上記ドライバ段増幅器がシリコン基板上に形成され、上記最終段増幅器がガリウム砒素 基板上に形成され、上記バイパス増幅器の少なくとも一部が上記シリコン基板上に形成さ れており、

さらに、上記ドライバ段増幅器及び上記最終段増幅器のバイアスを設定するバイアス回路が上記シリコン基板上に形成され、

上記バイアス回路により設定されるバイアスを調整するバイアス調整手段が上記ガリウム 仏素基板上に形成され、

<u>上記バイアス調整手段が、バイポーラトランジスタを含むエミッタフォロア型のバイア</u>ス回路で構成されていることを特徴とする高周波増幅器モジュール。

## 【請求項16】

請求項1<u>、請求項14又は請求項15</u>記載の高周波増幅器モジュールが複数個実装されている高周波増幅器モジュールユニット。

## INTERNATIONAL SEARCH REPORT

International application No.

PCT/JP2012/071423

| A. CLASSIFICATION OF SUBJECT MA | ATTER |

|---------------------------------|-------|

|---------------------------------|-------|

H03F3/195(2006.01)i, H03F3/213(2006.01)i

According to International Patent Classification (IPC) or to both national classification and IPC

# B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

H03F3/195, H03F3/213

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Jitsuyo Shinan Koho 1922–1996 Jitsuyo Shinan Toroku Koho 1996–2012

Kokai Jitsuyo Shinan Koho 1971–2012 Toroku Jitsuyo Shinan Koho 1994–2012

(47)

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                         | Relevant to claim No. |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X<br>Y    | JP 5-152978 A (Hitachi, Ltd.),<br>18 June 1993 (18.06.1993),<br>paragraphs [0009] to [0016]; fig. 1, 2, 7<br>& EP 481741 A3 & EP 481741 A2 | 1<br>2-10             |

| Y         | JP 2010-154512 A (Epcos AG.), 08 July 2010 (08.07.2010), paragraphs [0035] to [0037]; fig. 1 & US 2010/0117738 A1 & DE 102009051627 A      | 2,10,11               |

| Y         | JP 2010-41634 A (Hitachi Metals, Ltd.),<br>18 February 2010 (18.02.2010),<br>paragraphs [0016] to [0020]; fig. 1<br>(Family: none)         | 3-7,12,13             |

| ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Further do | cuments are listed in the continuation of Box C.                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | See patent family annex.                                      |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--|

| Special categories of cited documents:  document defining the general state of the art which is not considered to be of particular relevance  "E" earlier application or patent but published on or after the international filing date  "C" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)  "O" document referring to an oral disclosure, use, exhibition or other means document published prior to the international filing date but later than the priority date claimed |            | "T"<br>"Y"<br>"&"                                                 | date and not in conflict with the application but cited to understand the principle or theory underlying the invention.  document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone.  document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art |                                                               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            | d completion of the international search<br>ober, 2012 (15.10.12) | Date                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | e of mailing of the international sear<br>23 October, 2012 (2 |  |