(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5302644号

(P5302644)

(45) 発行日 平成25年10月2日(2013.10.2)

(24) 登録日 平成25年6月28日(2013.6.28)

|               |            |

|---------------|------------|

| (51) Int.Cl.  | F 1        |

| HO 1 L 27/146 | (2006.01)  |

| HO 1 L 27/14  | (2006.01)  |

| HO 4 N 5/369  | (2011.01)  |

| HO 4 N 5/374  | (2011.01)  |

| HO 1 L        | 27/14      |

| HO 1 L        | 27/14      |

| HO 4 N        | 5/335 69 O |

| HO 4 N        | 5/335 74 O |

請求項の数 8 (全 16 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2008-308999 (P2008-308999)  |

| (22) 出願日  | 平成20年12月3日 (2008.12.3)        |

| (65) 公開番号 | 特開2010-135509 (P2010-135509A) |

| (43) 公開日  | 平成22年6月17日 (2010.6.17)        |

| 審査請求日     | 平成23年11月29日 (2011.11.29)      |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 100076428<br>弁理士 大塚 康徳                     |

| (74) 代理人  | 100112508<br>弁理士 高柳 司郎                     |

| (74) 代理人  | 100115071<br>弁理士 大塚 康弘                     |

| (74) 代理人  | 100116894<br>弁理士 木村 秀二                     |

| (74) 代理人  | 100130409<br>弁理士 下山 治                      |

| (74) 代理人  | 100134175<br>弁理士 永川 行光                     |

最終頁に続く

(54) 【発明の名称】撮像装置、及び撮像システム

## (57) 【特許請求の範囲】

## 【請求項 1】

撮像領域と前記撮像領域の周辺に配された周辺領域とを有し、前記撮像領域が、遮光されていない光電変換部を含む有効画素が複数配列された有効領域と、前記有効領域に隣接した領域であって遮光された光電変換部を含むオプティカルブラック画素が複数配列されたオプティカルブラック領域とを含む撮像装置であって、

半導体基板と、

前記半導体基板の上方に配され、前記オプティカルブラック領域と前記周辺領域とを遮光する遮光層と、

前記周辺領域における前記遮光層と前記半導体基板との間に配され、前記有効画素又は前記オプティカルブラック画素から出力された信号を一時的に保持するための第1の容量素子と、

前記オプティカルブラック領域における前記遮光層と前記半導体基板との間に前記オプティカルブラック画素の光電変換部を遮光するように配された第2の容量素子と、を備えたことを特徴とする撮像装置。

## 【請求項 2】

前記第2の容量素子は、前記有効領域と前記オプティカルブラック領域との境界に隣接して配された前記オプティカルブラック画素の光電変換部の上方に配されていることを特徴とする請求項1に記載の撮像装置。

## 【請求項 3】

10

20

前記第2の容量素子は、

前記遮光層の下面に沿った方向へ延びた上部電極と、

前記半導体基板の表面に沿った方向へ延びた下部電極と、

前記上部電極と前記下部電極との間に配された絶縁膜と、

を含む

ことを特徴とする請求項2に記載の撮像装置。

【請求項4】

前記第1の容量素子は、

前記半導体基板からの高さが前記上部電極と同一である他の上部電極と、

前記半導体基板からの高さが前記下部電極と同一である他の下部電極と、

前記半導体基板からの高さが前記絶縁膜と同一である他の絶縁膜と、

を含む

ことを特徴とする請求項3に記載の撮像装置。

【請求項5】

前記オプティカルブラック領域における前記遮光層と前記半導体基板との間に配線層が設けられ、前記配線層に、オプティカルブラック画素で蓄積された信号を伝達するとともに前記第2の容量素子の前記下部電極として機能する配線パターンが配置されている、

ことを特徴とする請求項3又は4に記載の撮像装置。

【請求項6】

前記絶縁膜は、酸化膜、窒化膜、及び酸窒化膜のいずれかで形成され、

前記上部電極及び前記下部電極は、アルミニウム、アルミニウム合金、チタン、窒化チタン、タンタル、窒化タンタル、タンゲステン、タンゲステンシリサイド、及び銅の少なくとも1つで形成されている

ことを特徴とする請求項3から5のいずれか1項に記載の撮像装置。

【請求項7】

前記第1の容量素子および前記第2の容量素子は、MIM素子を含む、

ことを特徴とする請求項1から6のいずれか1項に記載の撮像装置。

【請求項8】

請求項1から7のいずれか1項に記載の撮像装置と、

前記撮像装置の撮像面へ像を形成する光学系と、

前記撮像装置から出力された信号を処理して画像データを生成する信号処理部と、

を備えたことを特徴とする撮像システム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、撮像装置、及び撮像システムに関する。

【背景技術】

【0002】

撮像装置は、近年、デジタルスチルカメラ、ビデオカムコーダを中心とする2次元画像入力装置として、あるいはファクシミリ、スキャナを中心とする1次元画像読み取り装置として利用され、急速に需要が高まっている。この撮像装置としてCCD(C charge Coupled Device:電荷結合素子)型センサやMOS型センサが用いられている。MOS型センサの代表としては、CMOSセンサが実用化されている。

【0003】

特許文献1には、特許文献1の図2に示すように、固体撮像素子1において、画素部10が、光電変換素子であるフォトダイオード12、メモリ群14、及び増幅器16を有することが記載されている。メモリ群14は、N個(N:整数)の記憶素子であるメモリを含む。各メモリは、光電変換素子から出力された信号電荷をアナログ量として保持・記憶する。メモリ群14は、N個のメモリから1以上のメモリから選択的に信号を読み出す。増幅器16は、メモリ群14から選択的に読み出された信号を増幅する。特許文献1には

、メモリ群14における各メモリが、特許文献1の図14に示すように、MIM(Metal Insulator Metal)型キャパシタであってもよいことが記載されている。

【特許文献1】特開2008-42825号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

撮像装置は、撮像領域と、撮像領域の周辺に配された周辺領域とを有する。この撮像領域は、遮光されていない光電変換部を含む有効画素が複数配列された有効領域と、有効領域に隣接した領域であって遮光された光電変換部を含むオプティカルブラック画素が複数配列されたオプティカルブラック領域とを含むように構成されることがある。10

【0005】

ここで、本発明者は、遮光層とその直下の配線層との間に容量素子としてMIM素子を配置することを考えた。このMIM素子は、例えば、周辺回路において、画素から出力された信号を保持するための保持容量として、又は、画素から出力されたノイズ信号と光信号との差分信号を生成するためのクランプ容量として機能する。

【0006】

この場合、周辺領域において、MIM素子を設けない場合に比べて、半導体基板の表面から遮光層までの高さが高くなるので、オプティカルブラック領域でも、半導体基板の表面から遮光層までの高さが高くなる傾向にある。これにより、有効領域とオプティカルブラック領域との境界近傍において、半導体基板の表面と遮光層との間からオプティカルブラック画素への迷光が発生するので、オプティカルブラック画素が正しい黒レベルの基準信号を出力できない。20

【0007】

本発明の目的は、周辺領域における遮光層と半導体基板との間に容量素子を設けた場合でも、オプティカルブラック領域におけるオプティカルブラック画素への迷光を低減することにある。

【課題を解決するための手段】

【0008】

本発明の第1側面に係る撮像装置は、撮像領域と前記撮像領域の周辺に配された周辺領域とを有し、前記撮像領域が、遮光されていない光電変換部を含む有効画素が複数配列された有効領域と、前記有効領域に隣接した領域であって遮光された光電変換部を含むオプティカルブラック画素が複数配列されたオプティカルブラック領域とを含む撮像装置であって、半導体基板と、前記半導体基板の上方に配され、前記オプティカルブラック領域と前記周辺領域とを遮光する遮光層と、前記周辺領域における前記遮光層と前記半導体基板との間に配され、前記有効画素又は前記オプティカルブラック画素から出力された信号を一時的に保持するための第1の容量素子と、前記オプティカルブラック領域における前記遮光層と前記半導体基板との間に前記オプティカルブラック画素の光電変換部を遮光するように配された第2の容量素子とを備えたことを特徴とする。30

【0009】

本発明の第2側面に係る撮像システムは、本発明の第1側面に係る撮像装置と、前記撮像装置の撮像面へ像を形成する光学系と、前記撮像装置から出力された信号を処理して画像データを生成する信号処理部とを備えたことを特徴とする。

【発明の効果】

【0010】

本発明によれば、周辺領域における遮光層と半導体基板との間に容量素子を設けた場合でも、オプティカルブラック領域におけるオプティカルブラック画素への迷光を低減することができる。

【発明を実施するための最良の形態】

【0011】

10

20

30

40

50

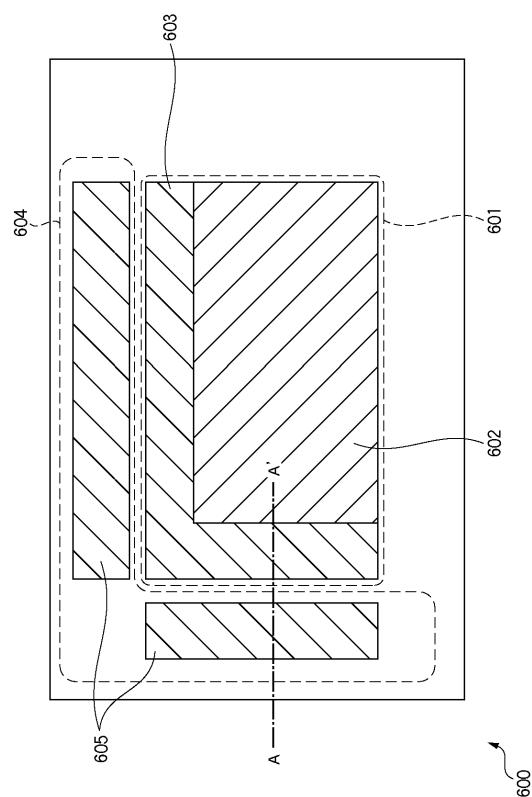

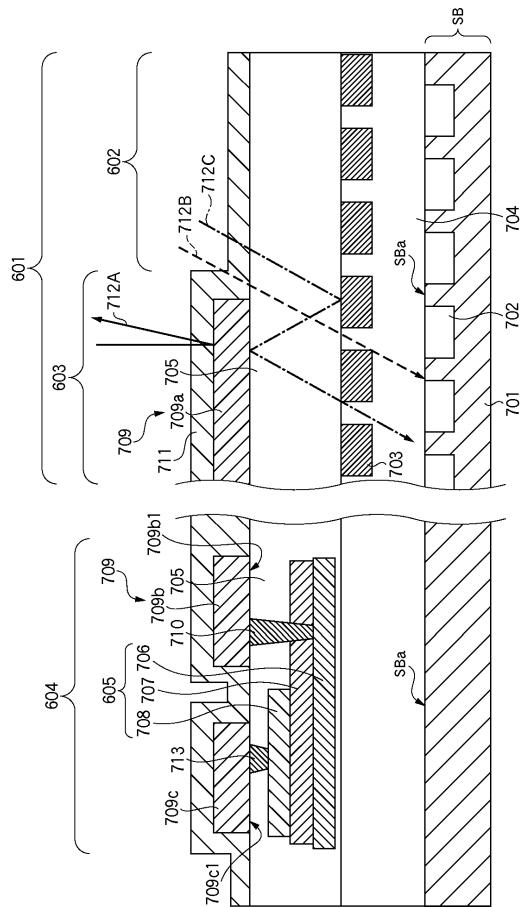

本発明者は、図7～図9に示す撮像装置600において、オプティカルブラック画素への迷光が発生することを見出した。以下、具体的に説明する。

【0012】

撮像装置600は、図7に示すように、撮像領域601と周辺領域604とを有する。図7は、撮像装置600のレイアウト構成を示す平面図である。

【0013】

撮像領域601は、有効領域602とオプティカルブラック(Optical Black)領域603とを含む。有効領域602には、遮光されていない光電変換部を含む有効画素が複数配列されている。オプティカルブラック領域603は、有効領域602に隣接した領域である。オプティカルブラック領域603には、遮光された光電変換部を含むオプティカルブラック画素が複数配列されている。

10

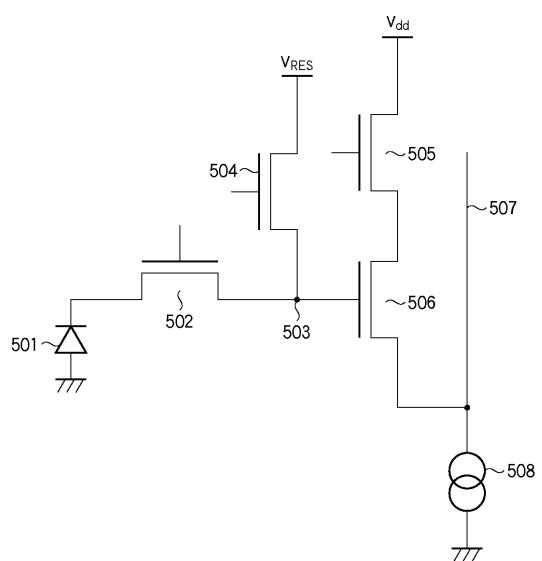

【0014】

有効画素又はオプティカルブラック画素は、図8に示すように、光電変換部501、転送部502、電荷電圧変換部503、リセット部504、出力部506、選択部505を含む。図8は、撮像装置600における画素の回路構成を示す図である。

【0015】

有効画素における光電変換部501は、遮光されておらず、光に応じた電荷(信号)を発生させて蓄積する。オプティカルブラック画素における光電変換部501は、遮光されており、黒レベルの基準信号となるべき電荷を蓄積する。

【0016】

20

転送部502は、光電変換部501で発生した電荷を電荷電圧変換部503へ転送する。転送部502は、例えば、転送トランジスタであり、アクティブルーレベルの転送制御信号TXがゲートに供給された際にオンすることにより、光電変換部501で発生した電荷を電荷電圧変換部503へ転送する。

【0017】

電荷電圧変換部503は、転送された電荷を電圧に変換する。電荷電圧変換部503は、例えば、フローティングディフュージョンである。

【0018】

リセット部504は、電荷電圧変換部503をリセットする。リセット部504は、例えば、リセットトランジスタであり、アクティブルーレベルのリセット制御信号RESがゲートに供給された際にオンすることにより、電荷電圧変換部503をリセットする。

30

【0019】

出力部506は、電荷電圧変換部503の電圧に応じた信号を垂直出力線507へ出力する。出力部506は、例えば、増幅トランジスタであり、垂直出力線507に接続された定電流源508とともにソースフォロワ動作を行うことにより、電荷電圧変換部503の電圧に応じた信号を垂直出力線507へ出力する。すなわち、出力部506は、リセット部504により電荷電圧変換部503がリセットされた状態で、電荷電圧変換部503の電圧に応じたノイズ信号を垂直出力線507へ出力する。出力部506は、転送部502により光電変換部501の電荷が電荷電圧変換部503へ転送された状態で、電荷電圧変換部503の電圧に応じた光信号を垂直出力線507へ出力する。

40

【0020】

選択部505は、画素(有効画素又はオプティカルブラック画素)を選択状態/非選択状態にする。選択部505は、例えば、選択トランジスタであり、アクティブルーレベルの選択制御信号SELがゲートに供給された際にオンすることにより、画素を選択状態にする。選択部505は、ノンアクティブルーレベルの選択制御信号SELがゲートに供給された際にオフすることにより、画素を非選択状態にする。

【0021】

周辺領域604には、垂直走査回路620(図6参照)や水平走査回路(図示せず)や保持回路(図示せず)が配されている。垂直走査回路620、水平走査回路や保持回路は、トランジスタ、抵抗素子(図示せず)、容量素子等で構成されている。

50

## 【0022】

垂直走査回路は、撮像領域 601 に配列された複数の画素（有効画素又はオプティカルブラック画素）を垂直方向に走査して、その走査している行の画素に上記のような転送制御信号 TX、リセット制御信号 RES、及び選択制御信号 SEL を供給する。

## 【0023】

保持回路は、画素から垂直出力線 507 へ出力された信号（ノイズ信号、光信号）を一時的に保持して出力する。保持回路は、MIM 素子（第 1 の容量素子）605 を含む。MIM 素子 605 は、後述のように、Metal - Insulator - Metal 構造をしており容量として機能する素子である。すなわち、MIM 素子 605 は、有効画素又はオプティカルブラック画素から出力された信号（ノイズ信号又は光信号）を一時的に保持するための保持容量として用いられる。10

## 【0024】

なお、MIM 素子 605 は、垂直出力線 507 と列アンプとに接続されたクランプ容量として用いられても良い。

## 【0025】

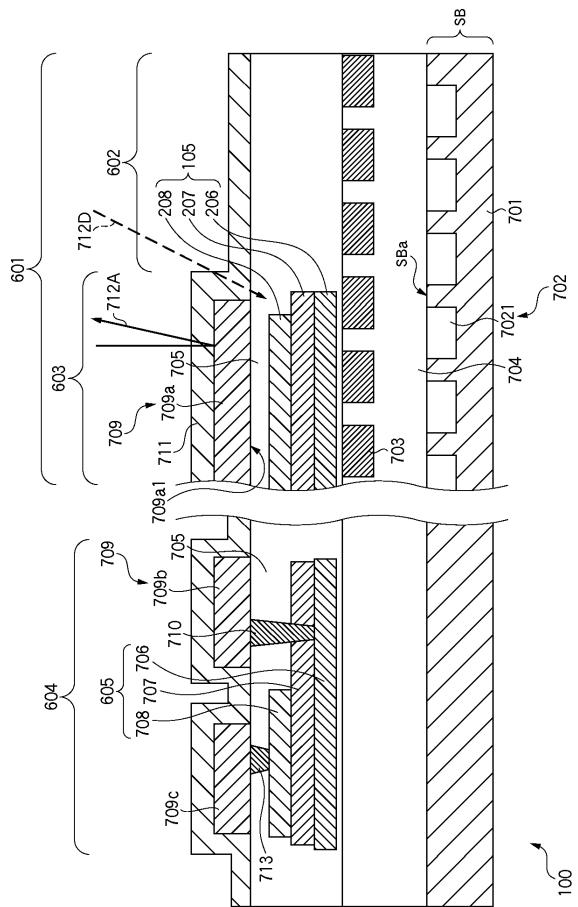

図 9 は、撮像装置 600 の断面構成を示す図である。図 9 では、撮像装置 600 における有効領域 602、オプティカルブラック領域 603、及び周辺領域 604 の断面構成が示されている。

## 【0026】

撮像装置 600 は、半導体基板 SB、遮光層 709、配線層 703、層間膜 704、層間膜 705、MIM 素子 605、プラグ 710、プラグ 713、及びパッシベーション膜 711 を備える。20

## 【0027】

半導体基板 SB は、ウエル領域 701 及び光電変換部 702 を含む。有効領域 602 及びオプティカルブラック領域 603 には、半導体基板 SB の表面近傍に複数の光電変換部 702 が配列されている。ウエル領域 701 は、複数の光電変換部 702 のそれぞれを囲むように半導体基板 SB 内に配されている。半導体基板 SB は、例えば、シリコンで形成されている。

## 【0028】

遮光層 709 は、オプティカルブラック領域 603 と周辺領域 604 とに配されている。遮光層 709 は、少なくともオプティカルブラック領域 603 を遮光する。遮光層 709 は、配線パターン 709a ~ 709c を含む。配線パターン 709a は、オプティカルブラック領域 603 を遮光するためのパターンである。配線パターン 709b 及び配線パターン 709c は、所定の信号を伝達するためのパターンである。30

## 【0029】

配線層 703 は、半導体基板 SB と遮光層 709 との間に配されている。配線層 703 は、有効画素又はオプティカルブラック画素の光電変換部 501 で蓄積された信号（電荷）を後段へ伝達するために用いられる。また、例えば、配線層 703 は、電荷電圧変換部 503 の電圧を出力部 506 へ伝達するために用いられる。

## 【0030】

層間膜 704 は、半導体基板 SB と配線層 703 とを絶縁するように、半導体基板 SB と配線層 703 との間に配されている。層間膜 704 は、例えば、酸化シリコンで形成される。

## 【0031】

層間膜 705 は、配線層 703 と遮光層 709 とを絶縁するように、配線層 703 と遮光層 709 との間に配されている。層間膜 705 は、例えば、酸化シリコンで形成される。

## 【0032】

MIM 素子 605 は、周辺領域 604 における遮光層 709 と半導体基板 SB との間に配されている。MIM 素子 605 は、上部電極（他の上部電極）708、下部電極（他の

下部電極 706、及び絶縁膜（他の絶縁膜）707を含む。

【0033】

上部電極 708は、遮光層 709の下面 709b1, 709c1に沿った方向へ延びている。上部電極 708は、例えば、アルミニウム、アルミニウム合金、チタン、窒化チタン、タンタル、窒化タンタル、タングステン、タングステンシリサイド、及び銅の少なくとも 1つで形成されている。

【0034】

下部電極 706は、半導体基板 SB の表面 SBa にそった方向へ延びている。下部電極 706は、例えば、アルミニウム、アルミニウム合金、チタン、窒化チタン、タンタル、窒化タンタル、タングステン、タングステンシリサイド、及び銅の少なくとも 1つで形成されている。

10

【0035】

絶縁膜 707は、上部電極 708と下部電極 706との間に配されている。絶縁膜 707は、例えば、Si、Ta、Hf、Alのいずれかを主成分とする酸化膜、窒化膜、及び酸窒化膜のいずれかで形成されている。

【0036】

すなわち、MIM 素子 605 は、Metal - Insulator - Metal 構造をしている。この構造は、容量値の電圧依存性が少ない構造である。

【0037】

プラグ 710 は、遮光層 709 の配線パターン 709b と MIM 素子 605 の下部電極 706 とを接続する。プラグ 710 は、例えば、W（タングステン）で形成されている。

20

【0038】

プラグ 713 は、遮光層 709 の配線パターン 709c と MIM 素子 605 の上部電極 708 とを接続する。プラグ 713 は、例えば、W（タングステン）で形成されている。

【0039】

これにより、例えば、配線パターン 709b 及びプラグ 710 を介して MIM 素子 605 の下部電極 706 へ基準電圧（例えば、グランド電圧）を供給することができる。また、配線パターン 709c 及びプラグ 713 を介して MIM 素子 605 の上部電極 708 へ信号（例えば、ノイズ信号又は光信号）に応じた電荷を蓄積して上部電極 708 がその信号を一時的に保持するようにすることができる。

30

【0040】

あるいは、例えば、配線パターン 709c 及びプラグ 713 を介して MIM 素子 605 の上部電極 708 へ基準電圧（例えば、グランド電圧）を供給することができる。また、配線パターン 709b 及びプラグ 710 を介して MIM 素子 605 の下部電極 706 へ信号（例えば、ノイズ信号又は光信号）に応じた電荷を蓄積して下部電極 706 がその信号を一時的に保持するようにすることができる。

【0041】

MIM 素子 605 は、配線形成におけるプロセス負荷の影響や、他の配線やデバイス素子からの寄生容量による変動をさけるために、配線層間ではなく、遮光層 709 を形成する前に形成される。素子形成後は、その後形成される層間膜 705 を通して W プラグ 710 で遮光層 709 と接続されるため、MIM 素子 605 は、遮光層 709 と直下の配線層 703 との間に形成されることになる。

40

【0042】

パッシベーション膜 711 は、遮光層 709 を覆うように配されている。

【0043】

ここで、遮光層 709 下の層間膜 705 は、少なくとも MIM 素子 605 を含むような膜厚に設定せざるを得ないので MIM 素子 605 が無い場合に比べ厚くなってしまう。このとき、有効領域 602 とオプティカルブラック領域 603 との境界近傍における撮像領域 601 に垂直に入射する光 712A は、遮光層 709 によって遮光される。それに対して、有効領域 602 とオプティカルブラック領域 603 との境界近傍における撮像領域 6

50

01に斜めに入射した光712Bは、半導体基板SBと遮光層709との間からオプティカルブラック画素の光電変換部702へ入射してしまう。あるいは、有効領域602とオプティカルブラック領域603との境界近傍における撮像領域601に斜めに入射した光712Cは、配線層703と遮光層709とで反射した後にオプティカルブラック画素の光電変換部へ入射してしまう。

【0044】

このように、周辺領域604において、遮光層903とその直下の配線層703との間にMIM素子が設けられた場合、MIM素子を設けない場合に比べて、半導体基板SBの表面SBaから遮光層709までの高さが高くなる。このため、オプティカルブラック領域603でも、半導体基板SBの表面SBaから遮光層709までの高さが高くなる傾向にある。これにより、有効領域602とオプティカルブラック領域603との境界近傍において、半導体基板SBと遮光層709との間からオプティカルブラック画素への迷光が発生するので、オプティカルブラック画素が正しい黒レベルの基準信号を出力できない。

【0045】

次に、本発明の第1実施形態に係る撮像装置100を、図1を用いて説明する。図1は、本発明の第1実施形態に係る撮像装置100の断面構成を示す図である。以下では、図7～図9に示す撮像装置600と異なる部分を中心に説明する。

【0046】

撮像装置100は、MIM素子(第2の容量素子)105を備える。

【0047】

MIM素子105は、オプティカルブラック領域603における遮光層903と半導体基板SBとの間にオプティカルブラック画素の光電変換部を遮光するように配されている。MIM素子105は、有効領域602とオプティカルブラック領域603との境界に隣接して配されたオプティカルブラック画素の光電変換部7021の上方に配されている。

【0048】

MIM素子105は、上部電極208、下部電極206、及び絶縁膜207を含む。

【0049】

上部電極208は、遮光層709の下面709a1に沿った方向へ延びている。上部電極208は、MIM素子605における上部電極708と同様な材料で形成されている。上部電極208は、例えば、アルミニウム、アルミニウム合金、チタン、窒化チタン、タンタル、窒化タンタル、タンゲステン、タンゲステンシリサイド、及び銅の少なくとも1つで形成されている。上部電極208の厚さは、MIM素子605における上部電極708の厚さと同様である。

【0050】

下部電極206は、半導体基板SBの表面SBaにそった方向へ延びている。下部電極206は、MIM素子605における下部電極706と同様な材料で形成されている。下部電極206は、例えば、アルミニウム、アルミニウム合金、チタン、窒化チタン、タンタル、窒化タンタル、タンゲステン、タンゲステンシリサイド、及び銅の少なくとも1つで形成されている。下部電極206の厚さは、MIM素子605における下部電極706の厚さと同様である。

【0051】

絶縁膜207は、上部電極708と下部電極706との間に配されている。絶縁膜207は、例えば、Si、Ta、Hf、ALのいずれかを主成分とする酸化膜、窒化膜、及び酸窒化膜のいずれかで形成されている。絶縁膜207の厚さは、MIM素子605における絶縁膜707の厚さと同様である。

【0052】

すなわち、MIM素子105は、Metal-Insulator-Metal構造をしている。

【0053】

このように、MIM素子105は、有効領域602とオプティカルブラック領域603

10

20

30

40

50

との境界近傍において、半導体基板SBと遮光層709との間からオプティカルブラック画素へ向けて入射した光を遮ることができる。これにより、周辺領域604において、遮光層903とその直下の配線層703との間にMIM素子が設けられたことにより、半導体基板SBの表面SBaから遮光層709までの高さが高くなつた場合でも、オプティカルブラック画素への迷光を低減できる。すなわち、周辺領域604における遮光層709と半導体基板SBとの間に容量素子(MIM素子)を設けた場合でも、オプティカルブラック領域におけるオプティカルブラック画素への迷光を低減することができる。

#### 【0054】

また、オプティカルブラック領域603に配されるMIM素子105が周辺領域604に配されるMIM素子605と同様な構造及び厚さを有している。具体的には、MIM素子105の上部電極208とMIM素子605の上部電極708とは、半導体基板SBからの高さが同一である。MIM素子105の下部電極206とMIM素子605の下部電極706とは、半導体基板SBからの高さが同一である。MIM素子105の絶縁膜207とMIM素子605の絶縁膜707とは、半導体基板SBからの高さが同一である。これにより、本実施形態に係る撮像装置100は、層間膜705の上面を平坦化した際に段差を低減するのに適した構造をしている。

#### 【0055】

例えは、オプティカルブラック領域603に配されるMIM素子105と周辺領域604に配されるMIM素子605とは、以下のようなプロセスフローにより形成される。

#### 【0056】

配線層703のパターンを形成した後、配線層703上に、層間膜705におけるMIM素子105及びMIM素子605と配線層703との間の部分となるべき絶縁膜を形成し、必要に応じて、その絶縁膜をCMPなどで平坦化する。その後、その絶縁膜の上に、下部電極706, 206となるべき金属層、絶縁膜707, 207となるべき絶縁層、上部電極708, 208となるべき金属層を、順に、PVD法又はCVD法などにより成膜する。

#### 【0057】

そして、フォトリソグラフィー及びドライエッチング法などを用いてパターニングを行うことにより、下部電極706, 206、絶縁膜707, 207、上部電極708, 208のそれぞれを形成する。これにより、MIM素子105がMIM素子605と同様な構造及び厚さを有するようになる。

#### 【0058】

その後、MIM素子605及びMIM素子105を覆うように絶縁膜を成膜し、成膜された絶縁膜の上面をCMPなどにより平坦化することにより、層間膜705を形成する。このとき、MIM素子105がMIM素子605と同様な構造及び厚さを有しているので、周辺領域604と撮像領域601との段差を生じさせずに絶縁膜の上面を平坦化できる。

#### 【0059】

そして、層間膜705の平坦化された上面の上に、遮光層709となるべき金属層を成膜し、その後、その金属層をパターニングする。これにより、遮光層709を形成する。さらに、層間膜705及び遮光層709を覆うようにパッシベーション膜711を形成する。

#### 【0060】

以上のように、本実施形態によれば、MIM素子を形成するための層間膜705があつても、PVDにより近い高さで遮光を実現できるため、特に斜め光712Dのオプティカルブラック領域への迷光成分を遮光できる。これにより、オプティカルブラック画素が黒レベルを安定して出力するようになる。

#### 【0061】

さらに、本実施形態によれば、PVDにより近い高さで遮光するための遮光膜は、MIM素子形成膜をそのまま使用するため、成膜プロセスやパターニングなどの工程を新たに追

10

20

30

40

50

加する必要もない。また、MIM素子の絶縁膜207をCVD方法で形成した場合には、絶縁膜207中に含まれる未結合水素が製造過程の熱処理によって拡散し、効率的に、且つ、一様にオプティカルブラック領域603に供給される。このため、オプティカルブラック領域603の暗電流を低減することが可能となる。

【0062】

なお、本実施形態では、オプティカルブラック領域603に遮光層709を従来例と同様に形成しているが、MIM素子による遮光性能がスペックを満たせば、オプティカルブラック領域に遮光層709を配置しなくともかまわない。

【0063】

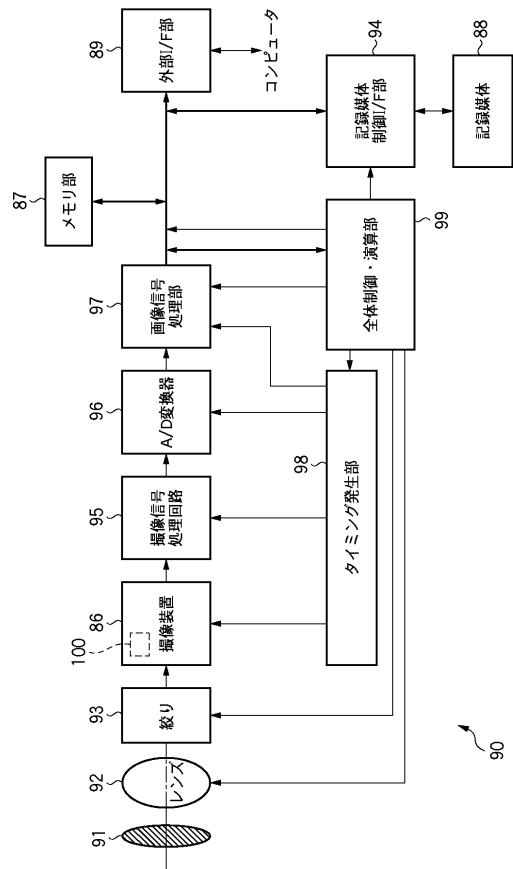

次に、本発明の撮像装置を適用した撮像システムの一例を図2に示す。

10

【0064】

撮像システム90は、図2に示すように、主として、光学系、撮像装置100及び信号処理部を備える。光学系は、主として、シャッター91、レンズ92及び絞り93を備える。信号処理部は、主として、撮像信号処理回路95、A/D変換器96、画像信号処理部97、メモリ部87、外部I/F部89、タイミング発生部98、全体制御・演算部99、記録媒体88及び記録媒体制御I/F部94を備える。なお、信号処理部は、記録媒体88を備えなくても良い。

【0065】

シャッター91は、光路上においてレンズ92の手前に設けられ、露出を制御する。

【0066】

レンズ92は、入射した光を屈折させて、撮像装置100の撮像面に被写体の像を形成する。

20

【0067】

絞り93は、光路上においてレンズ92と撮像装置100との間に設けられ、レンズ92を通過後に撮像装置100へ導かれる光の量を調節する。

【0068】

撮像装置100は、撮像面(画素配列)に形成された被写体の像を画像信号に変換する。撮像装置100は、その画像信号を画素配列から読み出して出力する。

【0069】

撮像信号処理回路95は、撮像装置100に接続されており、撮像装置100から出力された画像信号を処理する。

30

【0070】

A/D変換器96は、撮像信号処理回路95に接続されており、撮像信号処理回路95から出力された処理後の画像信号(アナログ信号)を画像信号(デジタル信号)へ変換する。

【0071】

画像信号処理部97は、A/D変換器96に接続されており、A/D変換器96から出力された画像信号(デジタル信号)に各種の補正等の演算処理を行い、画像データを生成する。この画像データは、メモリ部87、外部I/F部89、全体制御・演算部99及び記録媒体制御I/F部94などへ供給される。

40

【0072】

メモリ部87は、画像信号処理部97に接続されており、画像信号処理部97から出力された画像データを記憶する。

【0073】

外部I/F部89は、画像信号処理部97に接続されている。これにより、画像信号処理部97から出力された画像データを、外部I/F部89を介して外部の機器(パソコン等)へ転送する。

【0074】

タイミング発生部98は、撮像装置100、撮像信号処理回路95、A/D変換器96及び画像信号処理部97に接続されている。これにより、撮像装置100、撮像信号処理

50

回路 9 5、A / D 変換器 9 6 及び画像信号処理部 9 7 へタイミング信号を供給する。そして、撮像装置 1 0 0 、撮像信号処理回路 9 5、A / D 変換器 9 6 及び画像信号処理部 9 7 がタイミング信号に同期して動作する。

【 0 0 7 5 】

全体制御・演算部 9 9 は、タイミング発生部 9 8、画像信号処理部 9 7 及び記録媒体制御 I / F 部 9 4 に接続されており、タイミング発生部 9 8、画像信号処理部 9 7 及び記録媒体制御 I / F 部 9 4 を全体的に制御する。

【 0 0 7 6 】

記録媒体 8 8 は、記録媒体制御 I / F 部 9 4 に取り外し可能に接続されている。これにより、画像信号処理部 9 7 から出力された画像データを、記録媒体制御 I / F 部 9 4 を介して記録媒体 8 8 へ記録する。 10

【 0 0 7 7 】

以上の構成により、撮像装置 1 0 0 において良好な画像信号が得られれば、良好な画像(画像データ)を得ることができる。

【 0 0 7 8 】

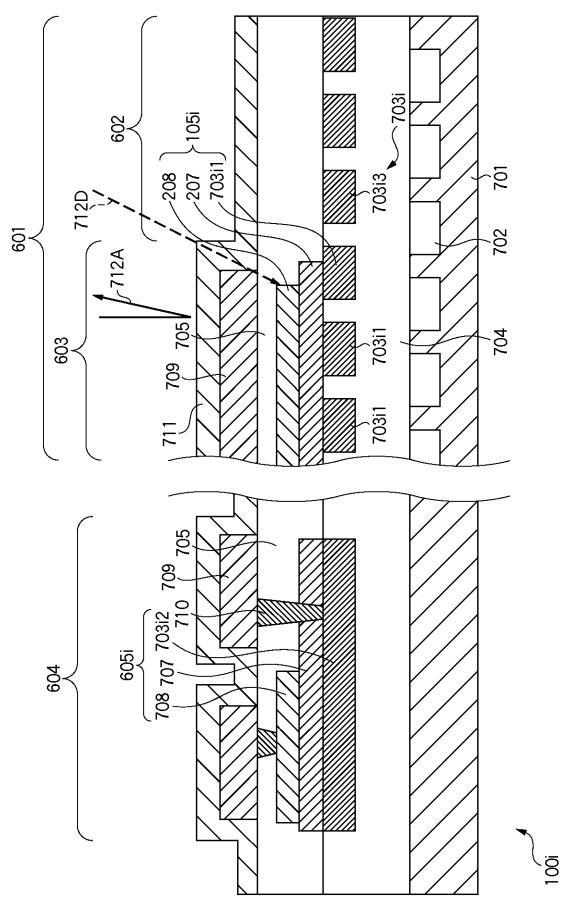

次に、本発明の第 2 実施形態に係る撮像装置 1 0 0 i を、図 3 を用いて説明する。図 3 は、本発明の第 2 実施形態に係る撮像装置 1 0 0 i の断面構成を示す図である。以下では、第 1 実施形態と異なる部分を中心に説明する。

【 0 0 7 9 】

撮像装置 1 0 0 i は、配線層 7 0 3 i 、MIM 素子 6 0 5 i 、及び MIM 素子 1 0 5 i を備える。 20

【 0 0 8 0 】

配線層 7 0 3 i は、配線パターン(第 1 の配線パターン) 7 0 3 i 1 、配線パターン 7 0 3 i 2 、及び配線パターン 7 0 3 i 3 を含む。配線パターン 7 0 3 i 1 は、所定の信号を伝達するためのパターンであるとともに、MIM 素子 1 0 5 i の下部電極として兼用されている。配線パターン 7 0 3 i 2 は、所定の基準電圧又は信号を伝達するためのパターンであるとともに、MIM 素子 6 0 5 i の下部電極として兼用されている。

【 0 0 8 1 】

このように、遮光層 7 0 9 と半導体基板 S B との間に配された配線層 7 0 3 i における配線パターンを MIM 素子 6 0 5 i 及び MIM 素子 1 0 5 i の下部電極としている。これにより、MIM 素子 6 0 5 i 及び MIM 素子 1 0 5 i の上部電極の半導体基板 S B の表面 S B a からの高さを低くすることができる。この結果、MIM 素子 1 0 5 i は、オプティカルブラック画素の光電変換部にさらに近い高さで遮光を行うことができる。 30

【 0 0 8 2 】

次に、本発明の第 3 実施形態に係る撮像装置 1 0 0 j を、図 4 を用いて説明する。図 4 は、本発明の第 3 実施形態に係る撮像装置 1 0 0 j の断面構成を示す図である。以下では、第 1 実施形態と異なる部分を中心に説明する。

【 0 0 8 3 】

撮像装置 1 0 0 j は、層間膜 7 0 5 j を備える。層間膜 7 0 5 j は、有効領域 6 0 2 A において一部除去され、低背化された部分 7 0 5 j 1 を有する。これにより、有効画素への効率のよい集光が可能となる。 40

【 0 0 8 4 】

この層間膜 7 0 5 j は、次のような工程により形成される。

【 0 0 8 5 】

層間膜 7 0 5 j となるべき絶縁膜の平坦化された上面の上に遮光層 7 0 9 を形成する工程までは、第 1 実施形態と同様である。

【 0 0 8 6 】

その後、周辺領域 6 0 4 及びオプティカルブラック領域 6 0 3 における絶縁膜及び遮光層 7 0 9 を覆うようにレジストパターンを形成する。そのレジストパターンをマスクとして異方性ドライエッチングを行うことにより、すぐ下の配線層 7 0 3 が露出しない条件( 50

エッティング時間等)で、層間膜705jとなるべき絶縁膜における有効領域602Aの部分を除去する。これにより、有効領域602Aにおける低背化された部分705j1が形成される。

【0087】

そして、レジストパターンを薬液等により剥離して除去した後、層間膜705j及び遮光層709を覆うようにパッシベーション膜711を形成する。

【0088】

ここで、更に図4においては、オプティカルブラック領域603に配されたMIM素子105と遮光層709とが有効領域602Aからオプティカルブラック領域603にかけて階段状になっている。つまりMIM素子105の上部電極と層間膜705jと遮光層709との端面が、MIM素子105の下部電極206及び絶縁膜207の端面よりも有効領域602Aから離れる方向に設けられている。このような構成によれば、有効領域602Aとオプティカルブラック領域603との間の段差が緩やかになるため、パッシベーション膜711やその後形成されうる平坦化層の膜厚が薄くても容易に平坦化が可能となる。

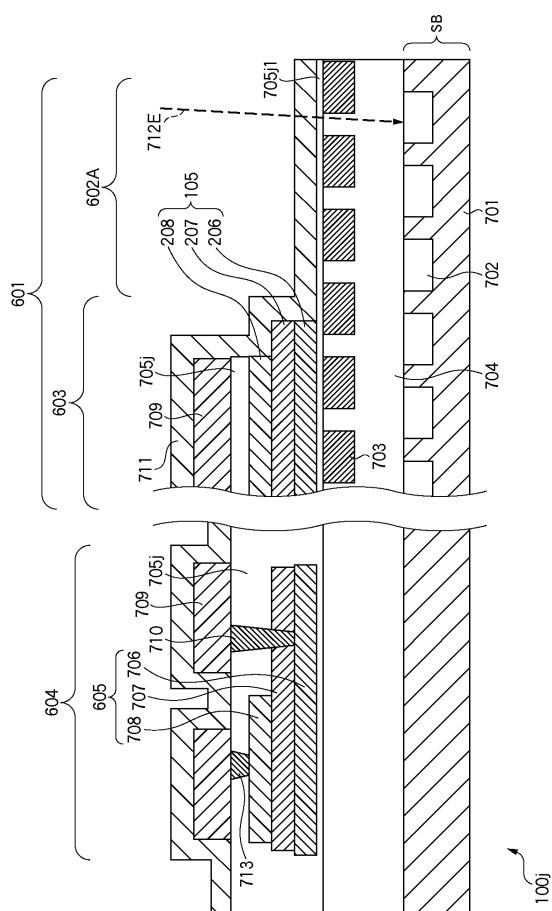

【0089】

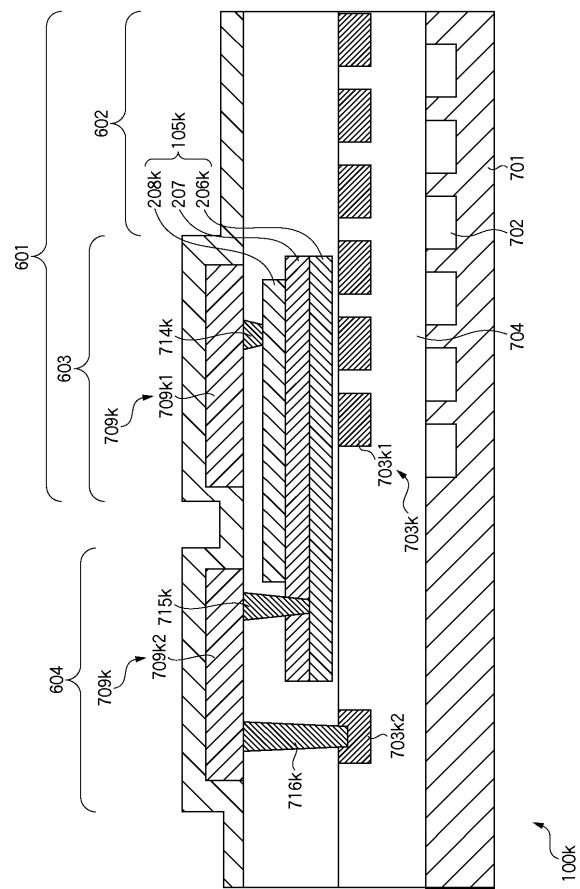

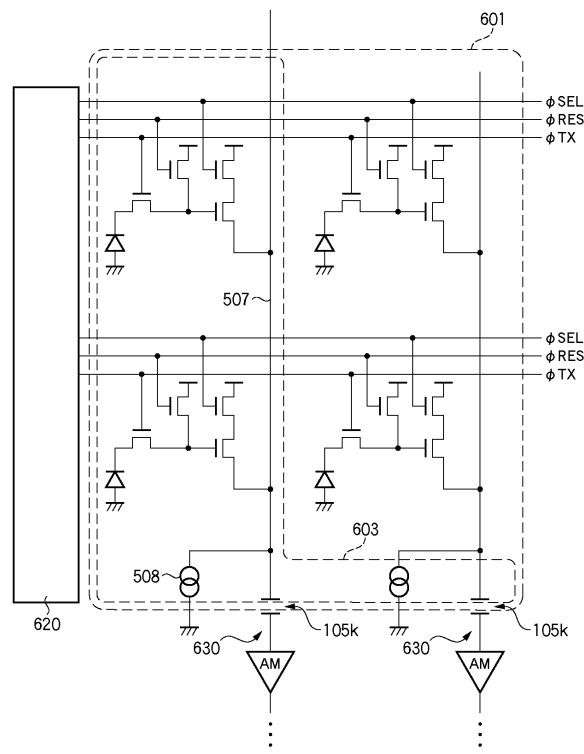

次に、本発明の第4実施形態に係る撮像装置100kを、図5及び図6を用いて説明する。図5は、本発明の第4実施形態に係る撮像装置100kの断面構成を示す図である。図6は、本発明の第4実施形態に係る撮像装置100kの回路構成を示す図である。

【0090】

撮像装置100kは、図5に示すように、遮光層709k、配線層703k、MIM素子105k、プラグ714k、プラグ715k、及びプラグ716kを備える。

【0091】

遮光層709kは、配線パターン(第2の配線パターン)709k1及び配線パターン709k2を含む。配線パターン709k1は、オプティカルブラック領域603を遮光するためのパターンであるとともに、垂直出力線507(図6参照)として兼用されている。配線パターン709k2は、MIM素子105kと列アンプAM(図6参照)とを接続するライン630の一部として用いられている。

【0092】

配線層703kは、配線パターン703k1及び配線パターン703k2を含む。配線パターン703k1は、所定の信号を伝達する。配線パターン703k2は、MIM素子105kと列アンプAM(図6参照)とを接続するライン630の他の一部として用いられている。配線パターン703k2は、プラグ716kを介して配線パターン709k2に接続されている。

【0093】

MIM素子105kは、オプティカルブラック領域603から周辺領域604におけるオプティカルブラック領域603に隣接した部分まで延在している。MIM素子105kは、垂直出力線507に接続されたクランプ容量として用いられる(図6参照)。すなわち、MIM素子105kは、垂直出力線507を介して画素(オプティカルブラック画素又は有効画素)からノイズ信号と光信号とを異なるタイミングで受けて列アンプAMとともにクランプ動作を行うことによりノイズ信号と光信号との差分信号を生成する。

【0094】

MIM素子105kは、上部電極208k及び下部電極206kを含む。上部電極208kは、プラグ714kを介して配線パターン709k1に接続されている。下部電極206kは、プラグ715kを介して配線パターン709k2に接続されている。

【0095】

プラグ714kは、遮光層709kの配線パターン709k1とMIM素子105kの上部電極208kとを接続する。プラグ714kは、例えば、W(タングステン)で形成されている。

【0096】

10

20

30

40

50

プラグ 715k は、遮光層 709k の配線パターン 709k2 と MIM 素子 105k の下部電極 206k とを接続する。プラグ 715k は、例えば、W(タングステン)で形成されている。

【0097】

プラグ 716k は、遮光層 709k の配線パターン 709k2 と配線層 703k の配線パターン 703k2 とを接続する。プラグ 716k は、例えば、W(タングステン)で形成されている。

【0098】

本実施形態によれば、クランプ容量としての MIM 素子をオプティカルブラック領域から周辺領域におけるオプティカルブラック領域に隣接した領域まで延在させるので、クランプ容量を形成した場合におけるチップ面積の増大を抑制できる。また、大容量のクランプ容量を用いるため、画素から出力された信号を列アンプへ伝達する際ににおける電源や GND 電位の振られによる微少振幅を有した高周波ノイズが信号に混入することを抑制できる。

【図面の簡単な説明】

【0099】

【図1】本発明の第1実施形態に係る撮像装置 100 の断面構成を示す図。

【図2】第1実施形態に係る撮像装置を適用した撮像システムの構成図。

【図3】本発明の第2実施形態に係る撮像装置 100i の断面構成を示す図。

【図4】本発明の第3実施形態に係る撮像装置 100j の断面構成を示す図。

【図5】本発明の第4実施形態に係る撮像装置 100k の断面構成を示す図。

【図6】本発明の第4実施形態に係る撮像装置 100k の回路構成を示す図。

【図7】撮像装置 600 のレイアウト構成を示す平面図。

【図8】撮像装置 600 における画素の回路構成を示す図。

【図9】撮像装置 600 の断面構成を示す図。

【符号の説明】

【0100】

100、100i、100j、100k、600 撮像装置

10

20

【 义 1 】

【 四 3 】

【 図 2 】

【 図 4 】

【図5】

【図6】

【図7】

【図8】

【 図 9 】

---

フロントページの続き

(72)発明者 田村 清一

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 小川 将之

(56)参考文献 特開平5-110045(JP,A)

特開2001-15725(JP,A)

特開平6-89992(JP,A)

特開平6-97414(JP,A)

特開昭64-64354(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/14-27/146

H04N 5/369

H04N 5/374