US009645829B2

# (12) United States Patent

Jayakumar et al.

(10) Patent No.: US 9,645,829 B2 (45) Date of Patent: May 9, 2017

# (54) TECHNIQUES TO COMMUNICATE WITH A CONTROLLER FOR A NON-VOLATILE DUAL IN-LINE MEMORY MODULE

(71) Applicant: **INTEL CORPORATION**, Santa Clara, CA (US)

(72) Inventors: Sarathy Jayakumar, Portland, OR (US); Mohan J. Kumar, Aloha, OR (US); Adam J. Brooks, Phoenix, AZ (US); George Vergis, Portland, OR (US)

(73) Assignee: **INTEL CORPORATION**, Santa Clara, CA (US)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 44 days.

(21) Appl. No.: 14/319,361

(22) Filed: Jun. 30, 2014

#### (65) Prior Publication Data

US 2015/0378841 A1 Dec. 31, 2015

(51) **Int. Cl. G06F 11/14** (2006.01) **G06F 9/44** (2006.01) **G06F 11/20** (2006.01)

(52) **U.S. Cl.** CPC ....... *G06F 9/4401* (2013.01); *G06F 11/1441* (2013.01); *G06F 11/2015* (2013.01)

#### (58) Field of Classification Search

See application file for complete search history.

## (56) References Cited

#### U.S. PATENT DOCUMENTS

| 2010/0202237 | A1*   | 8/2010  | Moshayedi G11C 5/141     |

|--------------|-------|---------|--------------------------|

|              |       |         | 365/228                  |

| 2010/0202239 |       | 8/2010  | Moshayedi et al.         |

| 2010/0205470 | Al*   | 8/2010  | Moshayedi G11C 5/141     |

|              |       | 0.00044 | 713/340                  |

| 2011/0239021 | A1*   | 9/2011  | Vedder G06F 1/263        |

| 2012/012125  |       | # (2012 | 713/323                  |

| 2012/0131253 | Al*   | 5/2012  | McKnight G06F 1/30       |

| 2012/0151110 | 414   | C/2012  | 710/308                  |

| 2012/0151118 | AIT   | 6/2012  | Flynn G06F 11/1008 711/6 |

| 2012/0198136 | A 1 * | 9/2012  | Moshayedi G06F 11/1658   |

| 2012/0198130 | AI.   | 8/2012  | 711/103                  |

| 2013/0086309 | A 1 * | 4/2013  | Lee G06F 12/0246         |

| 2013/0080303 | AI    | 4/2013  | 711/103                  |

| 2015/0186278 | A1*   | 7/2015  |                          |

| 2013/01002/0 | 711   | 112013  | 711/103                  |

|              |       |         | /11/103                  |

#### OTHER PUBLICATIONS

International Search Report and Written Opinion received for PCT Patent Application No. PCT/US2015/032922, mailed Aug. 31, 2015, 14 pages.

\* cited by examiner

Primary Examiner - Nadeem Iqbal

#### (57) ABSTRACT

Examples may include communicating with a controller for a non-volatile dual in-line memory module through a system management bus (SMBus) interface. In some examples, selective assertion of bits maintained in registers accessible through the SMBus interface may enable communication with the controller. The selective assertion may be based on a register map.

#### 25 Claims, 19 Drawing Sheets

FIG. 1

# Register Map Portion 200 (Header)

| Field Name         | Offset       | Length | Access | Description                                                           |

|--------------------|--------------|--------|--------|-----------------------------------------------------------------------|

| PAGE_NUM           | 0x00         | 1      | RW     | BIT[2:0]: Page Number                                                 |

|                    |              |        |        | BIT[5:3]: Maximum Number of pages                                     |

|                    |              |        |        | BIT[7:6]: Reserved                                                    |

| HWREV              | 0x01         | 1      | RO     | Hardware Revision Info                                                |

| FWREV              | 0x02         | 2      | RO     | Firmware Revision Info                                                |

| GENCAP             | 0x04         | 1      | RO     | BIT 0: SAVE Command Class Supported                                   |

|                    |              |        |        | BIT 1: RESTORE Command Class Supported                                |

|                    |              |        |        | BIT 2: ERASE Command Class Supported                                  |

|                    |              |        |        | BIT 3: Enable Catastrophic SAVE (ARM)                                 |

|                    |              |        |        | Command Class Supported                                               |

|                    |              |        |        | BIT 4: Health Check Command Class Supported                           |

|                    |              |        |        | BIT [6:5]: Reserved. Must be 0                                        |

|                    |              |        |        | BIT 7: Extended Capabilities Supported                                |

| EXTCAP             | 0x05         | 1      | RO     | Extended Capabilities Structure.                                      |

| Validation Bits    | 0x06         | 1      | RO     | Specifies which of these fields have valid data                       |

|                    |              |        |        | BIT 0: Number of SAVE regions                                         |

|                    |              |        |        | BIT 1: Save Latency Valid                                             |

|                    |              |        |        | BIT 2: Restore Latency Valid                                          |

|                    |              |        |        | BIT 3: Controller Ready latency Valid                                 |

|                    |              |        |        | BIT 4: Command Accepted (CA) Latency Valid                            |

|                    |              |        |        | BIT 5: Super Cap Charging time Valid                                  |

| Number of SAVE     | 0x07         | 1      | RO     | SAVE regions in the NVDIMM                                            |

| regions            |              | _      |        | Valid Values = 1 to N                                                 |

| SAVE Latency       | 0x08         | 2      | RO     | Worst case - default region (REGION-0)                                |

| RESTORE            | 0x0A         | 2      | RO     | Worst case - default region (REGION -0)                               |

| Latency            |              | _      |        |                                                                       |

| Controller Ready   | 0x0C         | 2      | RO     | Worst case - NVDIMM controller ready after                            |

| Latency T (CR)     |              |        |        | power-up or reset.                                                    |

|                    |              |        |        | BIT15: 0 – Indicates Time-out in ms                                   |

|                    |              |        |        | 1 – Indicates time-out in secs                                        |

| G 1                | 0.00         | _      | D.O.   | BIT[14:0]: Time-out value                                             |

| Command            | 0x0E         | 2      | RO     | Worst case - CA bit to be set by the controller on                    |

| Accepted Latency   |              |        |        | receipt of a command. Used by requestor to time-                      |

| T(CA)              |              |        |        | out. BIT15: 0 – Time-out in μs                                        |

|                    |              |        |        | 1 – Time-out in ms                                                    |

|                    |              |        |        |                                                                       |

| Capacitor charging | 0x10         | 2.     | RO     | BIT[14:0]: Time-out value  Worst case capacitor charging time in secs |

| time               | UXIU         | ~      | NO N   | (0V to Peak V).                                                       |

| EXTCAP             | 0x12         | 1      | RO     | Extended Capabilities Structure.                                      |

| Page switching     | 0x12<br>0x13 | 1      | RO     | Amount of time requestor has to wait for page                         |

| latency            | UXIS         | 1      | I KU   | switching to happen, before it times-out, in ms                       |

| Energy Required    | 0x14         | 2      | RO     | Energy required by the NVDIMM for                                     |

| Energy Required    | UX 14        | -      | I NO   | Catastrophic SAVE operation, in Joules.                               |

| Reserved           | 0x16         | 10     | RO     | Reserved                                                              |

| Reserveu           | UXIO         | [ 1U   | LVO.   | Reserveu                                                              |

*FIG. 2*

# Register Map Portion 300 (NVDIMM STATE Class)

| Field Name       | Offset | Length | Access | Description                                    |

|------------------|--------|--------|--------|------------------------------------------------|

| GET_NVDIMM_STATE | 0X20   | 1      | RW     | Get NVDIMM state command                       |

|                  |        |        |        | BIT7 – (RA ) Request Accepted.                 |

|                  |        |        |        | BIT6 – (SV) Status Valid                       |

|                  |        |        |        | BIT5 – Reserved                                |

|                  |        |        |        | BIT[4:0] - 0x00 - No Operation                 |

|                  |        |        |        | 0x01: Return NVDIMM status                     |

|                  |        |        |        | 0x02: Clear NVDIMM status                      |

|                  |        |        |        | 0x03: Reset controller                         |

|                  |        |        |        | 0x04 to 0x7F: Reserved                         |

|                  |        |        |        | 0x80 - 0xFF: Vendor defined                    |

| Reserved         | 0x21   | 1      | RO     | Reserved                                       |

| T(NvState.SV)    | 0x22   | 2      | RO     | Valid only when GET_NVDIMM_STATE.CA            |

| , ,              |        |        |        | == 1.                                          |

|                  |        |        |        | BIT15: 0 – Time-out in ms                      |

|                  |        |        |        | 1 – Time-out in seconds.                       |

|                  |        |        |        | BIT[14:0]: Time-out value for requestor        |

|                  |        |        |        | while waiting for corresponding SV bit to be   |

|                  |        |        |        | set.                                           |

| NVDIMM_STATUS    | 0x24   | 2      | RO     | Valid only when GET_NVDIMM_STATE.              |

|                  |        |        |        | SV                                             |

|                  |        |        |        | == 1                                           |

|                  |        |        |        | BIT0: 0 - Controller NOT busy                  |

|                  |        |        |        | 1 - Controller busy                            |

|                  |        |        |        | BIT 1: SAVE in progress, if set                |

|                  |        |        |        | BIT 2: ABORT SAVE in progress, if set          |

|                  |        |        |        | BIT 3: RESTORE in progress, if set             |

|                  |        |        |        | BIT 4: ABORT_RESTORE in progress ,if set       |

|                  |        |        |        | BIT 5: ERASE in progress, if set               |

|                  |        |        |        | BIT 6: ABORT_ERASE in progress, if set         |

|                  |        |        |        | BIT 7: 0 – SAVE# pin not asserted on           |

|                  |        |        |        | previous boot                                  |

|                  |        |        |        | 1 – SAVE# pin asserted on previous             |

|                  |        |        |        | boot, triggering a catastrophic save           |

|                  |        |        |        | BIT 8: 0 – Catastrophic SAVE successful        |

|                  |        |        |        | 1 - Catastrophic SAVE not successful           |

|                  |        |        |        | (This BIT is valid only if either BIT7 or BIT8 |

|                  |        |        |        | is set)                                        |

|                  |        |        |        | BIT[15:9]: Reserved                            |

| BUSY_TIMEOUT     | 0x26   | 2      | RO     | Valid only when NVDIMM_STATUS.BUSY             |

| T(Busy)          |        |        |        | == 1.                                          |

|                  |        |        |        | BIT15: 0 –Time-out in ms                       |

|                  |        |        |        | 1 –Time-out in sec.                            |

|                  |        |        |        | BIT [14:0]: Time-out value that requestor uses |

|                  |        |        |        | waiting for NVDIMM_STATUS.BUSY == 0.           |

*FIG. 3*

# Register Map Portion 400 (SAVE Class)

| Field Name      | Offset | Length | Access | Description                                                     |

|-----------------|--------|--------|--------|-----------------------------------------------------------------|

| SAVE CMD        | 0x28   | 1      | RW     | SAVE command                                                    |

| _               |        |        |        | BIT7: (CA) Command Accepted                                     |

|                 |        |        |        | BIT6: (SV) Status Valid.                                        |

|                 |        |        |        | BIT5: (GUID_V) Image GUID Valid.                                |

|                 |        |        |        | 0 - Image GUID not valid. SAVE to                               |

|                 |        |        |        | default region                                                  |

|                 |        |        |        | 1- Image GUID is valid                                          |

|                 |        |        |        | BIT[4:0]: Command                                               |

|                 |        |        |        | 0x00: No Operation                                              |

|                 |        |        |        | 0x01: Start the SAVE operation                                  |

|                 |        |        |        | 0x00 - 0xFF: Reserved                                           |

|                 |        |        |        | 0x100 - 0x1FF: Vendor Defined                                   |

| ABORT SAVE      | 0x29   | 1      | RW     | ABORT SAVE command                                              |

| / IBORT_BATTE   | UAZ    | *      | 12.11  | BIT7: (CA) Command Accepted                                     |

|                 |        |        |        | BIT6: (SV) Status Valid                                         |

|                 |        |        |        | BIT5: (GUID V) Image GUID Valid                                 |

|                 |        |        |        | 0 - Image GUID not valid. Abort Save                            |

|                 |        |        |        | to default region                                               |

|                 |        |        |        | 1 - Image GUID is valid                                         |

|                 |        |        |        | BIT[4:0]: Command                                               |

|                 |        |        |        | 0x00: No Operation                                              |

|                 |        |        |        | 0x01: ABORT the SAVE operation                                  |

|                 |        |        |        | 0x00 - 0xFF: Reserved                                           |

|                 |        |        |        | 0x100 - 0x1FF: Vendor Defined                                   |

| T(Save.SV)      | 0x2A   | 2      | RO     | Valid only when SAVE_CMD.CA == 1 OR                             |

| 1 (Save.SV)     | UXZA   | -      | I KO   | ABORT SAVE.CA == 1                                              |

|                 |        |        |        | BIT15: 0 – Indicates Time-out in ms                             |

|                 |        |        |        | 1 – Indicates Time-out in iss                                   |

|                 |        |        |        | BIT[14:0]: Time-out value that the requestor will               |

|                 |        |        |        | use while waiting for corresponding SV bit to be                |

|                 |        |        |        | set                                                             |

| Reserved        | 0x2C   | 2      | RO     | Reserved                                                        |

| SAVE STATUS     | 0x2E   | 2      | RO     | Status Field. Valid only if SAVE CMD.SV == 1                    |

| SAVE_STATUS     | UXZE   | 2      | I KO   | OR ABORT SAVE.SV == 1                                           |

|                 |        |        |        | 0x0000: SAVE Successfully completed                             |

|                 |        |        |        | 0x0000: SAVE successfully completed 0x0001: ERROR. SAVE failure |

|                 |        |        |        | 0x0001: ERROR. SAVE faiture<br>0x0002: ABORT successful         |

|                 |        |        |        | 0x0002: ABORT successiul<br>0x0003: ERROR. Abort Failure        |

|                 |        |        |        | 0x0003. ERROR. About Failure<br>0x0004 – 0x7FFF: Reserved       |

|                 |        |        |        | 0x8000 - 0xFFFF: Reserved                                       |

| CAVE IMAGE CLUB | 0.20   | 8      | RW     |                                                                 |

| SAVE_IMAGE_GUID | 0x30   | l °    | KW     | IMAGE_GUID associated with the SAVE/ABORT SAVE/GET SAVE STS     |

|                 |        |        |        |                                                                 |

|                 |        |        |        | command                                                         |

FIG. 4

# Register Map Portion 500 (RESTORE Class)

| Field Name         | Offset | Length       | Access | Description                                                          |

|--------------------|--------|--------------|--------|----------------------------------------------------------------------|

| RESTORE_CMD        | 0x38   | 1            | RW     | RESTORE command                                                      |

| _                  |        |              |        | BIT7: (CA) Command Accepted                                          |

|                    |        |              |        | BIT6: (SV) Status Valid.                                             |

|                    |        |              |        | BIT5: (GUID_V) Image GUID Valid.                                     |

|                    |        |              |        | 0 - Image GUID not valid.                                            |

|                    |        |              |        | RESTORE default region                                               |

|                    |        |              |        | 1 - Image GUID is valid                                              |

|                    |        |              |        | BIT[4:0]: Command                                                    |

|                    |        |              |        | 0x00: No Operation                                                   |

|                    |        |              |        | 0x01: Start the RESTORE operation                                    |

|                    |        |              |        | 0x00 - 0xFF: Reserved                                                |

|                    |        |              |        | 0x100 - 0x1FF: Vendor Defined                                        |

| ABORT_RESTORE      | 0x39   | 1            | RW     | ABORT RESTORE command                                                |

| 1100111_1001101    | 0.125  |              |        | BIT7: (CA) Command Accepted                                          |

|                    |        |              |        | BIT6: (SV) Status Valid                                              |

|                    |        |              |        | BIT5: (GUID_V) Image GUID Valid                                      |

|                    |        |              |        | 0 - Image GUID not valid. Abort                                      |

|                    |        |              |        | Restore to default region                                            |

|                    |        |              |        | 1 - Image GUID is valid                                              |

|                    |        |              |        | BIT[4:0]: Command                                                    |

|                    |        |              |        | 0x00: No Operation                                                   |

|                    |        |              |        | 0x01: ABORT the RESTORE                                              |

|                    |        |              |        | operation                                                            |

|                    |        |              |        | 0x00 - 0xFF: Reserved                                                |

|                    |        |              |        | 0x100 - 0x1FF: Vendor Defined                                        |

| T(Restore.SV)      | 0x3A   | 2            | RO     | Valid only when RESTORE CMD.CA == 1                                  |

| T(Resiote.5 v)     | UNDIT  |              | RO     | OR ABORT RESTORE.CA == 1                                             |

|                    |        |              |        | BIT15: 0 – Indicates Time-out in ms                                  |

|                    |        |              |        | 1 – Indicates Time-out in secs                                       |

|                    |        |              |        | BIT[14:0]: Time-out value that the requestor                         |

|                    |        |              |        | will use while waiting for corresponding SV                          |

|                    |        |              |        | bit to be set                                                        |

| Reserved           | 0x3C   | 2            | RO     | Reserved                                                             |

| RESTORE_STATUS     | 0x3E   | 2            | RO     | Status Field. Valid only if                                          |

| RESTORE_STATUS     | UX3E   | <sup>Z</sup> | KO     | RESTORE CMD.SV == 1                                                  |

|                    |        |              |        | OR ABORT_RESTORE.SV == 1                                             |

|                    |        |              |        | 0x0000: RETORE Successfully completed                                |

|                    |        |              |        | 0x0000: RETORE Successfully completed 0x0001: ERROR. RESTORE failure |

|                    |        |              |        | 0x0001: ERROR. RESTORE failure 0x0002: ABORT successful              |

|                    |        |              |        | 0x0002: ABORT successful<br>0x0003: ERROR. Abort Failure             |

|                    |        |              |        | 0x0003: ERROR. About Failure<br>0x0004 - 0x7FFF: Reserved            |

|                    |        |              |        |                                                                      |

| DECTODE MAAGE OUR  | 040    | 0            | DW     | 0x8000 – 0xFFFF: Reserved                                            |

| RESTORE_IMAGE_GUID | 0x40   | 8            | RW     | IMAGE_GUID_associated with the                                       |

|                    |        |              |        | RESTORE/ABORT_RESTORE/GET_REST                                       |

|                    |        |              |        | ORE_STS command                                                      |

*FIG.* 5

US 9,645,829 B2

# Register Map Portion 600

(ERASE Class)

| Field Name       | Offset | Length | Access | Description                                             |

|------------------|--------|--------|--------|---------------------------------------------------------|

| ERASE CMD        | 0x48   | 1      | RW     | ERASE command                                           |

| _                |        |        |        | BIT7: (CA) Command Accepted                             |

|                  |        |        |        | BIT6: (SV) Status Valid.                                |

|                  |        |        |        | BIT5: (GUID V) Image GUID Valid.                        |

|                  |        |        |        | 0 - Image GUID not valid. ERASE                         |

|                  |        |        |        | default region                                          |

|                  |        |        |        | 1 - Image GUID is valid                                 |

|                  |        |        |        | BIT[4:0]: Command                                       |

|                  |        |        |        | 0x00: No Operation                                      |

|                  |        |        |        | 0x01: Start the ERASE operation                         |

|                  |        |        |        | 0x00 - 0xFF: Reserved                                   |

|                  |        |        |        | 0x100 - 0x11. Reserved<br>0x100 - 0x1FF: Vendor Defined |

| ADORT EDACE      | 0x49   | 1      | RW     | ABORT RESTORE command                                   |

| ABORT_ERASE      | UX49   | 1      | KW     |                                                         |

|                  |        |        |        | BIT7: (CA) Command Accepted                             |

|                  |        |        |        | BIT6: (SV) Status Valid                                 |

|                  |        |        |        | BIT5: (GUID_V) Image GUID Valid                         |

|                  |        |        |        | 0 - Image GUID not valid. Abort Erase                   |

|                  |        |        |        | to default region                                       |

|                  |        |        |        | 1 - Image GUID is valid                                 |

|                  |        |        |        | BIT[4:0]: Command                                       |

|                  |        |        |        | 0x00: No Operation                                      |

|                  |        |        |        | 0x01: ABORT the RESTORE                                 |

|                  |        |        |        | operation                                               |

|                  |        |        |        | 0x00 - 0xFF: Reserved                                   |

|                  |        |        |        | 0x100 - 0x1FF: Vendor Defined                           |

| T(Erase.SV)      | 0x4A   | 2      | RO     | Valid only when ERASE_CMD.CA == 1 OR                    |

|                  |        |        |        | ABORT_ERASE.CA == 1                                     |

|                  |        |        |        | BIT15: 0 – Indicates Time-out in ms                     |

|                  |        |        |        | 1 – Indicates Time-out in secs                          |

|                  |        |        |        | BIT[14:0]: Time-out value that the requestor            |

|                  |        |        |        | will use while waiting for corresponding SV bit         |

|                  |        |        |        | to be set                                               |

| Reserved         | 0x4C   | 2      | RO     | Reserved                                                |

| ERASE_STATUS     | 0x4E   | 2      | RO     | Status Field. Valid only if ERASE_CMD.SV ==             |

| _                |        |        |        | 1 OR ABORT_ERASÉ.SV == 1                                |

|                  |        |        |        | 0x0000: ERASE Successfully completed                    |

|                  |        |        |        | 0x0001: ERROR. ERASE failure                            |

|                  |        |        |        | 0x0002: ABORT successful                                |

|                  |        |        |        | 0x0003: ERROR. Abort Failure                            |

|                  |        |        |        | 0x0004 - 0x7FFF: Reserved                               |

|                  |        |        |        | 0x8000 - 0xFFFF: Reserved                               |

| ERASE IMAGE GUID | 0x50   | 8      | RW     | IMAGE_GUID associated with the                          |

|                  |        |        |        | ERASE/ABORT ERASE/GET ERASE STS                         |

|                  |        |        |        | command                                                 |

|                  |        |        |        | command                                                 |

*FIG.* 6

# Register Map Portion 700 (ARM/DISARM Class)

| Field Name       | Offset | Length | Access | Description                                     |

|------------------|--------|--------|--------|-------------------------------------------------|

| ENABLE_CATASTRO  | 0x58   | 1      | RW     | Enables catastrophic save                       |

| PHIC_SAVE (ARM)  |        |        |        | BIT7: (CA) Command Accepted                     |

|                  |        |        |        | BIT6: (SV) Status Valid.                        |

|                  |        |        |        | BIT5: Reserved                                  |

|                  |        |        |        | BIT[4:0]: Command                               |

|                  |        |        |        | 0x00: No Operation                              |

|                  |        |        |        | 0x01: Start the ARM operation                   |

|                  |        |        |        | 0x00 - 0xFF: Reserved                           |

|                  |        |        |        | 0x100 - 0x1FF: Vendor Defined                   |

| DISABLE_CATASTRO | 0x59   | 1      | RW     | Disables catastrophic save                      |

| PHIC_SAVE        |        |        |        | BIT7: (CA) Command Accepted                     |

| (DISARM)         |        |        |        | BIT6: (SV) Status Valid                         |

|                  |        |        |        | BIT5: Reserved                                  |

|                  |        |        |        | BIT[4:0] – Command                              |

|                  |        |        |        | 0x00: No Operation                              |

|                  |        |        |        | 0x01: Start the DISARM operation                |

|                  |        |        |        | 0x00 - 0xFF: Reserved                           |

|                  |        |        |        | 0x100 - 0x1FF: Vendor Defined                   |

| T(Arm.SV)        | 0x5A   | 2      | RO     | Valid only when ARM_CMD.CA == 1 OR              |

|                  |        |        |        | $DISARM\_CMD.CA == 1$                           |

|                  |        |        |        | BIT15: 0 – Indicates Time-out in ms             |

|                  |        |        |        | 1 – Indicates Time-out in secs                  |

|                  |        |        |        | BIT[14:0]: Time-out value that the requestor    |

|                  |        |        |        | will use while waiting for corresponding SV bit |

|                  |        |        |        | to be set                                       |

| Reserved         | 0x5C   | 2      | RO     | Reserved                                        |

| CATASTROPHIC_SAV | 0x5E   | 2      | RO     | Status Field. Valid only if ARM_CMD.SV == 1     |

| E_STATUS         |        |        |        | OR DISARM_CMD.SV == 1                           |

|                  |        |        |        | 0x0000: ARM Successfully completed              |

|                  |        |        |        | 0x0001: ERROR. ARM failure                      |

|                  |        |        |        | 0x0002: DISARM successful                       |

|                  |        |        |        | 0x0003: ERROR. DISARM Failure                   |

|                  |        |        |        | 0x0004 - 0x7FFF: Reserved                       |

|                  |        |        |        | 0x8000 - 0xFFFF: Reserved                       |

US 9,645,829 B2

# Register Map Portion 800 (Self-Refresh Save Class)

| Field Name       | Offset | Length | Access | Description                                     |

|------------------|--------|--------|--------|-------------------------------------------------|

| ENABLE_SELFREFRE | 0x60   | 1      | RW     | Enables SAVE on Self-refresh                    |

| SH_SAVE          |        |        |        | BIT7: (CA) Command Accepted                     |

|                  |        |        |        | BIT6: (SV) Status Valid.                        |

|                  |        |        |        | BIT5: Reserved                                  |

|                  |        |        |        | BIT[4:0]: Command                               |

|                  |        |        |        | 0x00: No Operation                              |

|                  |        |        |        | 0x01: Enable SAVE on Self-refresh               |

|                  |        |        |        | 0x00 - 0xFF: Reserved                           |

|                  |        |        |        | 0x100 - 0x1FF: Vendor Defined                   |

| DISABLE SELFREFR | 0x61   | 1      | RW     | Disables SAVE operation on Self-refresh         |

| ESH SAVE         |        |        |        | BIT7: (CA ) Command Accepted                    |

| _                |        |        |        | BIT6: (SV) Status Valid                         |

|                  |        |        |        | BIT5: Reserved                                  |

|                  |        |        |        | BIT[4:0]: Command                               |

|                  |        |        |        | 0x00: No Operation                              |

|                  |        |        |        | 0x01: Disable SAVE on Self-refresh              |

|                  |        |        |        | 0x00 - 0xFF: Reserved                           |

|                  |        |        |        | 0x100 - 0x1FF: Vendor Defined                   |

| T(SrSave.SV)     | 0x62   | 2      | RO     | Valid only when                                 |

|                  |        |        |        | ENABLE SELFREFRESH SAVE.CA == 1                 |

|                  |        |        |        | OR DISABLE_SELFREFRESH_SAVE.CA ==               |

|                  |        |        |        | 1                                               |

|                  |        |        |        | BIT15: 0 – Indicates Time-out in ms             |

|                  |        |        |        | 1 – Indicates Time-out in secs                  |

|                  |        |        |        | BIT[14:0]: Time-out value that the requestor    |

|                  |        |        |        | will use while waiting for corresponding SV bit |

|                  |        |        |        | to be set                                       |

| Reserved         | 0x64   | 2      | RO     | Reserved                                        |

| SRSAVE_STATUS    | 0x66   | 2      | RO     | Status Field. Valid only if                     |

|                  |        |        |        | ENABLE_SELFREFRESH_SAVE.SV == 1                 |

|                  |        |        |        | OR DISABLE_SELFREFRESH_SAVE.SV ==               |

|                  |        |        |        |                                                 |

|                  |        |        |        | 0x0000: SR SAVE enable                          |

|                  |        |        |        | 0x0001: ERROR. SR SAVE enable failure           |

|                  |        |        |        | 0x0002: SR SAVE disabled                        |

|                  |        |        |        | 0x0003: ERROR. SR SAVE disable Failure          |

|                  |        |        |        | 0x0004 – 0x7FFF: Reserved                       |

|                  |        |        |        | 0x8000 – 0xFFFF: Reserved                       |

US 9,645,829 B2

# Register Map Portion 900 (Health Check Class)

| Field Name        | Offset | Length | Access | Description                                  |

|-------------------|--------|--------|--------|----------------------------------------------|

| GET_HEALTH_STATUS | 0x68   | 1      | RW     | Get Health Status                            |

|                   |        |        |        | BIT7: (RA) Request Accepted                  |

|                   |        |        |        | BIT6: (SV) Status Valid.                     |

|                   |        |        |        | BIT5: Reserved                               |

|                   |        |        |        | BIT[4:0]: Command                            |

|                   |        |        |        | 0x00: No Operation                           |

|                   |        |        |        | 0x01: Start the Health Check Operation       |

|                   |        |        |        | 0x00 - 0xFF: Reserved                        |

|                   |        |        |        | 0x100 - 0x1FF: Vendor Defined                |

| T(Health.SV)      | 0x69   | 2      | RO     | Valid only when                              |

|                   |        |        |        | GET_HEALTH_STATUS.CA == 1                    |

|                   |        |        |        | BIT15: 0 – Indicates Time-out in ms          |

|                   |        |        |        | 1 – Indicates Time-out in secs               |

|                   |        |        |        | BIT[14:0]: Time-out value that the requestor |

|                   |        |        |        | will use while waiting for corresponding SV  |

|                   |        |        |        | bit to be set                                |

| HEALTH_STATUS     | 0x6B   | 2      | RO     | Status Field. Valid only if                  |

|                   |        |        |        | GET_HEALTH_STATUS.SV == 1                    |

|                   |        |        |        | 0x0000: Health Check Complete                |

|                   |        |        |        | 0x0001: ERROR. Health Check failure          |

|                   |        |        |        | 0x0002 - 0x7FFF: Reserved                    |

|                   |        |        |        | 0x8000 - 0xFFFF: Reserved                    |

FIG. 9

FIG. 11

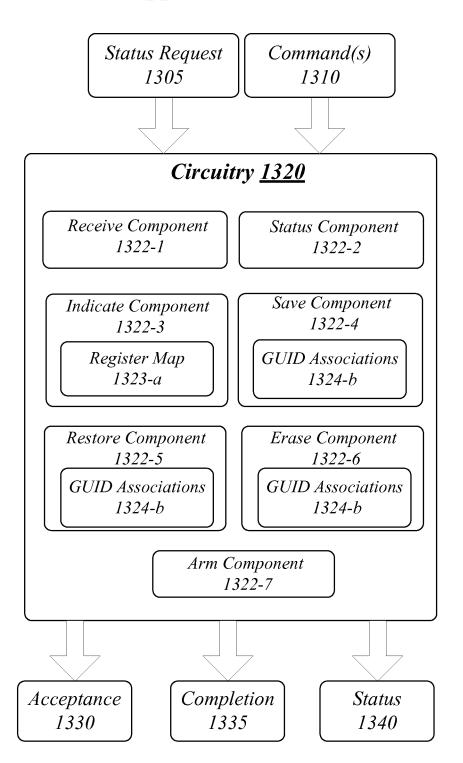

# Apparatus <u>1300</u>

FIG. 13

RECEIVE, AT A CONTROLLER, A STATUS REQUEST, THE CONTROLLER FOR A NON-VOLATILE MEMORY CAPABLE OF PRESERVING DATA MAINTAINED IN VOLATILE MEMORY, THE NON-VOLATILE AND THE VOLATILE MEMORY RESIDENT ON A **NVDIMM**

1402

DETERMINE A STATUS RESPONSIVE TO THE STATUS REQUEST 1404

INDICATE THE STATUS VIA SELECTIVE ASSERTION OF A FIRST SET OF BITS MAINTAINED IN A FIRST SET OF REGISTERS, THE SELECTIVE ASSERTION BASED ON A REGISTER MAP, THE FIRST SET OF REGISTERS ACCESSIBLE TO A REQUESTOR OF THE STATUS REQUEST THROUGH A SMBUS INTERFACE 1406

RECEIVE A FIRST COMMAND FROM THE REQUESTOR VIA ASSERTION OF A SECOND SET OF BITS MAINTAINED IN A SECOND SET OF REGISTERS, THE ASSERTION OF THE SECOND SET OF BITS BASED ON THE REGISTER MAP, THE SECOND SET OF REGISTERS ACCESSIBLE TO THE REQUESTOR THROUGH THE SMBUS INTERFACE

1408

INDICATE ACCEPTANCE AND COMPLETION STATUS OF THE FIRST COMMAND VIA ASSERTION OF A THIRD SET OF BITS MAINTAINED IN A THIRD SET OF REGISTERS, THE ASSERTION OF THE THIRD SET OF BITS BASED ON THE REGISTER MAP, THE THIRD SET OF REGISTERS ACCESSIBLE TO THE REQUESTOR THROUGH THE SMBUS INTERFACE

*1410*

INDICATING A FIRST COMPLETION STATUS OF THE FIRST COMMAND VIA ASSERTION OF A FOURTH SET OF BITS MAINTAINED IN A FOURTH SET OF REGISTERS, THE ASSERTION OF THE FOURTH SET OF BITS BASED ON THE REGISTER MAP. THE FIRST COMPLETION STATUS INCLUDING A SUCCESSFUL COMPLETION OF THE FIRST COMMAND OR A FAILURE TO COMPLETE THE FIRST COMMAND, THE FOURTH SET OF REGISTERS ACCESSIBLE TO THE REQUESTOR THROUGH THE SMBUS INTERFACE

1412

FIG. 14

# Storage Medium <u>1500</u>

Computer Executable Instructions for 1400

FIG. 15

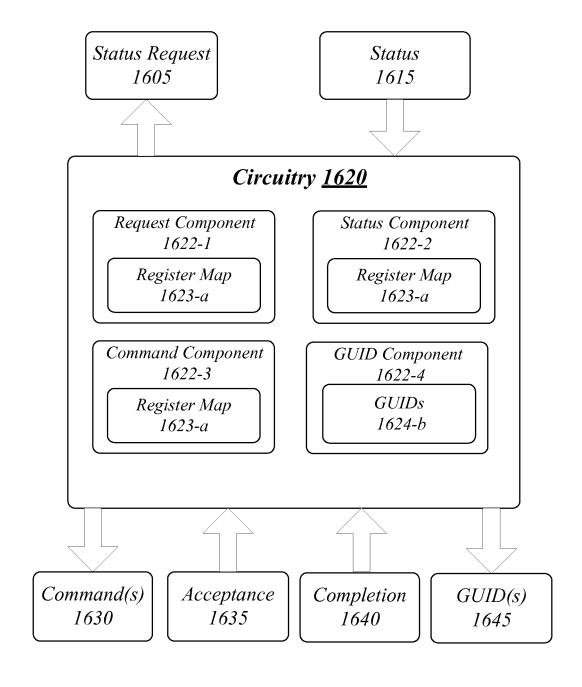

# Apparatus 1600

FIG. 16

SEND A STATUS REQUEST TO A CONTROLLER FOR A NON-VOLATILE MEMORY CAPABLE OF PRESERVING DATA MAINTAINED IN VOLATILE MEMORY, THE NON-VOLATILE AND THE VOLATILE MEMORY RESIDENT ON A NVDIMM COUPLED WITH THE HOST COMPUTING DEVICE 1702 ACCESS A FIRST SET OF BITS MAINTAINED IN A FIRST SET OF REGISTERS THROUGH A SMBUS INTERFACE, THE FIRST SET OF BITS INDICATING A STATUS INDICATED BY THE CONTROLLER RESPONSIVE TO THE STATUS REQUEST VIA SELECTIVE ASSERT OF THE FIRST SET OF BITS BASED ON A REGISTER MAP 1704 SEND A FIRST COMMAND VIA ASSERTION OF A SECOND SET OF BITS MAINTAINED IN A SECOND SET OF REGISTERS. THE ASSERTION OF THE SECOND SET OF BITS BASED ON THE REGISTER MAP. THE SECOND SET OF REGISTERS ACCESSIBLE THROUGH THE SMBUS INTERFACE 1706 RECEIVE AN INDICATION OF A FIRST COMPLETION STATUS OF THE FIRST COMMAND VIA ASSERTION BY THE CONTROLLER OF A FOURTH SET OF BITS MAINTAINED IN A FOURTH SET OF REGISTERS, THE FOURTH SET OF BITS ASSERTED BASED ON THE REGISTER MAP, THE FIRST COMPLETION STATUS INCLUDING A SUCCESSFUL COMPLETION OF THE FIRST COMMAND OR A FAILURE TO COMPLETE THE FIRST **COMMAND**

FIG. 17

*1708*

May 9, 2017

# Storage Medium 1800

Computer Executable Instructions for 1700

FIG. 18

# FIG. 19

FIG. 20

# TECHNIQUES TO COMMUNICATE WITH A CONTROLLER FOR A NON-VOLATILE **DUAL IN-LINE MEMORY MODULE**

#### TECHNICAL FIELD

Examples described herein are generally related to a non-volatile dual in-line memory module (NVDIMM).

#### BACKGROUND

Memory modules coupled with computing platforms or systems such as those configured as a server may include dual in-line memory modules (DIMMs). DIMMs may include types of volatile memory such dynamic random 15 access memory (DRAM). As DRAM technologies have advanced to include memory cells having higher and higher densities, memory capacities for DIMMs have also substantially increased. Since DRAM is a volatile memory, power failures or resets may result in loss of most if not all data 20 maintained in DRAM at the time of power failure or reset. Also, large memory capacities for DRAMs presents a challenge for an operating system (OS) or an application (e.g., device driver) to sense a power failure and attempt to prevent or reduce data loss.

In order to mitigate or reduce data loss in the event of a power failure or reset, a type of memory module that includes both volatile and non-volatile memory has been developed. This type of memory module is commonly referred to as a non-volatile DIMM (NVDIMM). Typically, 30 NVDIMMs are a combination of DRAM and NAND flash. NVDIMMs may provide persistent storage by backing up DRAM contents in a non-volatile memory such as NAND flash in event of a power failure or sudden system reset. A super-capacitor package may be coupled with an NVDIMM 35 to maintain power to the NVDIMM for long enough to back-up data from the DRAM to the non-volatile memory.

An NVDIMM may have a controller resident on or with the NVDIMM to manage or control NVDIMM activities. The NVDIMM controller may manage saving of DRAM 40 contents to non-volatile memory at the NVDIMN. The NVDIMM controller may also manage restoration of the DRAM contents from the non-volatile memory back to the DRAM once system power has been restored. The NVDIMM controller may be arranged to operate in coordi- 45 nation with an OS, device driver, application or basic input/output system (BIOS) for a computing platform coupled with the NVDIMM to save or restore DRAM contents.

#### BRIEF DESCRIPTION OF THE DRAWINGS

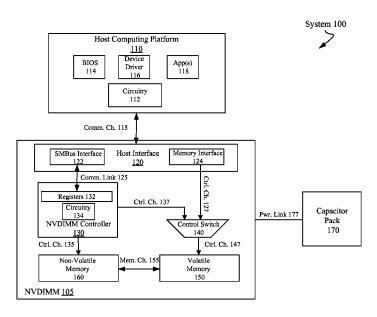

- FIG. 1 illustrates an example system.

- FIG. 2 illustrates a first example register map portion.

- FIG. 3 illustrates a second example register map portion. 55

- FIG. 4 illustrates a third example register map portion.

- FIG. 5 illustrates a fourth example register map portion.

- FIG. 6 illustrates a fifth example register map portion.

- FIG. 7 illustrates a sixth example register map portion.

- FIG. 8 illustrates a seventh example register map portion. 60

- FIG. 9 illustrates an eighth example register map portion.

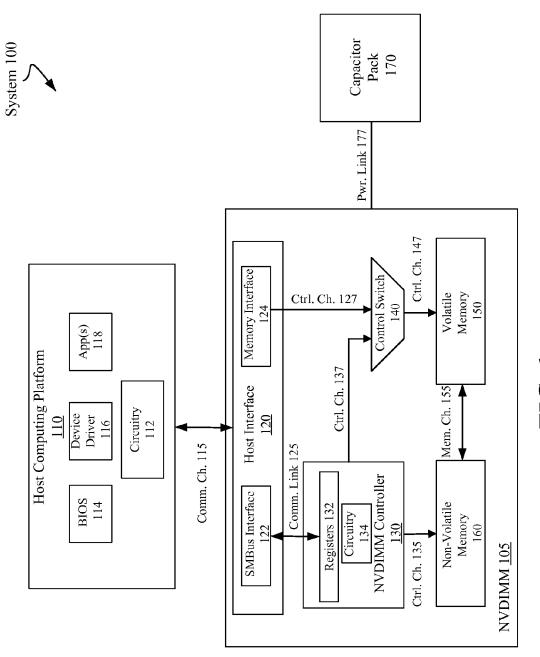

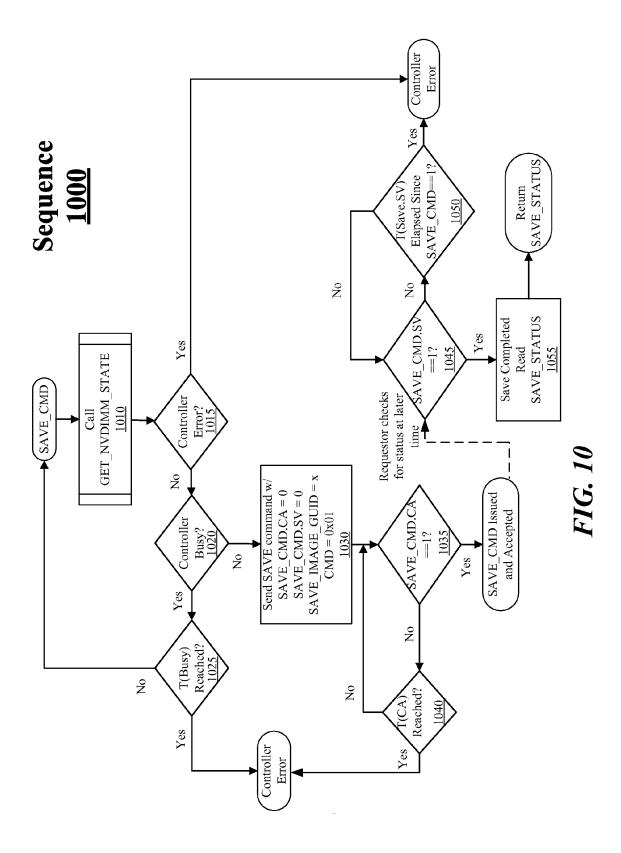

- FIG. 10 illustrates a first example sequence.

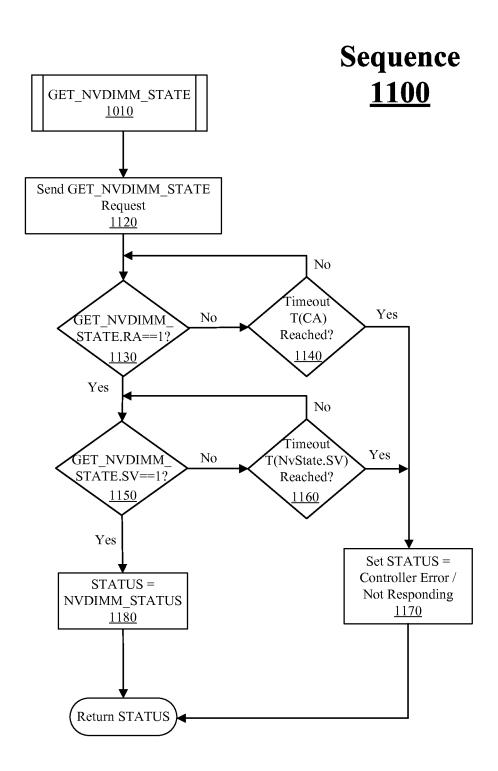

- FIG. 11 illustrates a second example sequence.

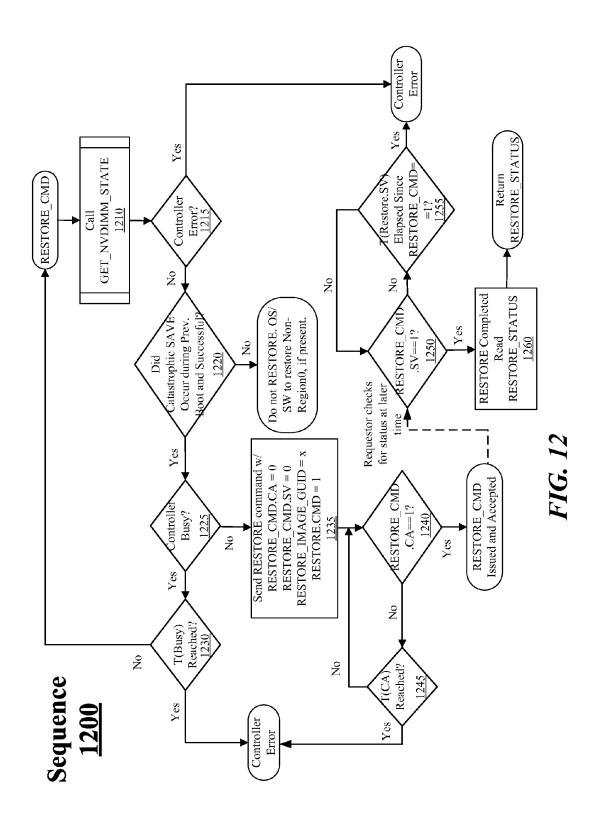

- FIG. 12 illustrates a third example sequence.

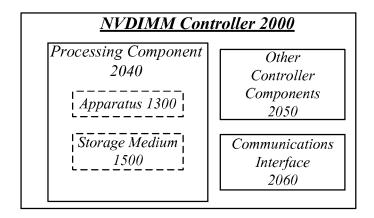

- FIG. 13 illustrates an example block diagram for a first 65 apparatus.

- FIG. 14 illustrates an example of a first logic flow.

2

FIG. 15 illustrates an example of a first storage medium. FIG. 16 illustrates an example block diagram for a second apparatus.

FIG. 17 illustrates an example of a second logic flow.

FIG. 18 illustrates an example of a second storage

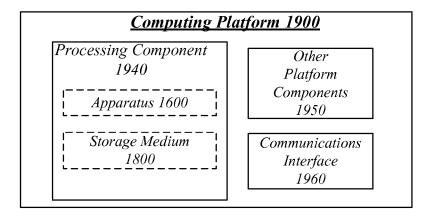

FIG. 19 illustrates an example computing platform.

FIG. 20 illustrates an example non-volatile dual in-line memory module controller.

#### DETAILED DESCRIPTION

As contemplated in the present disclosure, an NVDIMM may have a NVDIMM controller arranged to operate in coordination with an OS, device driver application or BIOS for a computing platform coupled with the NVDIMM. In some examples, an application, device driver and/or BIOS may interface or communicate through one or more communication interfaces with the NVDIMM controller. When interfacing or communicating with the NVDIMM controller the application, device driver and/or BIOS may issue commands to the NVDIMM controller to save DRAM contents to non-volatile memory at the NVDIMM, restore nonvolatile memory content to the DRAM, etc. Numerous manufacturers of NVDIMMs may implement their own proprietary interfaces to communicate with computing platform elements such as an application, device driver and/or BIOS. The use of numerous proprietary interfaces may be an impediment to interoperability and may be problematic to designers of computing platform elements such as an application, device driver and/or BIOS that are designed to support NVDIMMS. It is with respect to these and other challenges that the examples described herein are needed.

Techniques to communicate with a controller for an NVDIMM may be implemented via one or more example methods. A first example method may include a controller receiving a status request. The controller may be for a non-volatile memory capable of preserving data maintained in volatile memory, the non-volatile and the volatile memory resident on an NVDIMM. A status may be determined by the controller responsive to the status request and the status indicated via selective assertion of a first set of bits maintained in a first set of registers. For this first example method, the first set of registers may be accessible to a requestor (e.g., application, device driver or BIOS) of the status request through a system management bus (SMBus)

A second example may include a device driver arranged 50 to be implemented by circuitry at a host computing device. The device driver may send a status request to a controller for a non-volatile memory capable of preserving data maintained in volatile memory, the non-volatile and the volatile memory may be resident on a an NVDIMM coupled with the host computing platform. For this second example method, the device driver may access a first set of bits maintained in a first set of registers through an SMBus interface. The first set of bits may indicate a status provided by the controller responsive to the status request via selective assertion of the first set of bits based on a register map.

FIG. 1 illustrates an example system 100. As shown in FIG. 1, system 100 includes a host computing platform 110 coupled to a non-volatile dual in-line memory module (NVDIMM) 105 via communication channel 115. Also shown in FIG. 1, a capacitor pack 170 may couple to NVDIMM 105 via a power link 177. In some examples, as shown in FIG. 1, NVDIMM 105 may also include a host

interface 120, an NVDIMM controller 130, a control switch 140, a volatile memory 150 or a non-volatile memory 160.

In some examples, host computing platform 110 may include circuitry 112 capable of executing various functional elements of host computing platform 110 that may include, 5 but is not limited to a basic input/output system (BIOS) 114, a device driver 116 or an application(s) (App(s)) 118. For these examples, host computing platform 110 may include, but is not limited to, a server, a server array or server farm, a web server, a network server, an Internet server, a work station, a mini-computer, a main frame computer, a supercomputer, a network appliance, a web appliance, a distributed computing system, multiprocessor systems, processor-based systems, or combination thereof.

According to some examples, as shown in FIG. 1, host 15 interface 120 at NVDIMM 105 may include a system management bus (SMBus) interface 122 and a memory interface 124. SMBus interface 122 may be designed or operated in compliance with one or more standards or specifications (including progenies or variants) to include 20 the SMBus Specification, version 2.0, published in August 2000 ("SMBus Specification"). As described more below, elements of host computing platform 110 may communicate with NVDIMM controller 130 through SMBus interface 122. Also, elements of computing platform 110 may have 25 access to volatile memory 150 through memory interface 124 over control channel 127 through control switch 140 and then over control channel 147. In some examples, access to volatile memory 150 may be switched by control switch **140** to NVDIMM controller **130** over control channel **137** to 30 save or restore contents of volatile memory 150 from or to non-volatile memory 160 using memory channel 155 coupled between volatile memory 150 and non-volatile

According to some examples, as shown in FIG. 1, 35 NVDIMM controller 130 may include registers 132 and circuitry 134. Circuitry 134 may be capable of executing components or features to receive a status request from elements of host computing platform 110. As described more below, the status request may pertain to a status of 40 NVDIMM controller 130 or other elements of NVDIMM 105 (e.g., non-volatile memory 160). The components or features may also be capable of determining a status responsive to the status request and then indicate that status via selective assertion of bits maintained in registers 132 based 45 on a register map. The requesting element of host computing platform 110 such as device driver 116 (requestor) may have access to registers 132 through SMBus interface 122 and over communication link 125 to determine which bits have been asserted. The requestor may then use the register map 50 to determine what status was indicated by the components or features implemented by circuitry 134.

In some examples, volatile memory 150 may include volatile memory designed or operated in compliance with one or more standards or specifications (including progenies 55 or variants) associated with various types of volatile memory such as DRAM. For example, types of DRAM such as synchronous double data rate DRAM (DDR DRAM) may be included in volatile memory 150 and standards or specifications associated with DDR DRAM may include those 60 published by the JEDEC Solid State Technology Association ("JEDEC") for various generations of DDR such as DDR2, DDR3, DDR4 or future DDR generations. Some example standards or specifications may include, but are not limited to, JESD79-3F—"DDR3 SDRAM Standard", published in 5 July 2012 or JESD79-4—"DDR4 SDRAM Standard", published in September 2012.

4

According to some examples, non-volatile memory 160 may include one or more types of non-volatile memory to include, but not limited to, NAND flash memory, NOR flash memory, 3-D cross-point memory, ferroelectric memory, silicon-oxide-nitride-oxide-silicon (SONOS) memory, polymer memory such as ferroelectric polymer memory, ferroelectric transistor random access memory (FeTRAM) or FeRAM), ovonic memory or nanowire. Also, in some examples, non-volatile memory 160 may include enough memory capacity to receive the full contents of volatile memory 150 or possibly multiple copies of contents of volatile memory 150. For these examples, non-volatile memory 160 sized for multiple copies may allow for images of time-based data maintained in volatile memory 150 to be saved to regions of non-volatile memory 160. As described more below, global unique identifiers (GUIDs) may be assigned or associated with data to be saved or restored from a non-volatile memory such as non-volatile memory 160. NVDIMM controller 130 may use these assigned GUIDs to facilitate saving or restoring time-based data from or to volatile memory 150.

In some examples, capacitor pack 170 may include one or more capacitors to provide at least temporary power to NVDIMM 105 via power link 177. The one or more capacitors may be capable of storing enough energy to power NVDIMM 105 for a sufficient time for NVDIMM controller 130 to cause data maintained in volatile memory 150 to be saved to non-volatile memory 160 if a sudden power failure or system reset caused the main power supply to NVDIMM 105 to be cut or shut off. The saving of the data contents to non-volatile memory 160 due to the sudden power failure or system reset may be referred to as a "catastrophic save".

FIG. 2 illustrates a first example register map portion. In some examples, as shown in FIG. 2, the first example register map portion includes register map portion 200. In some examples, elements of a system such as system 100 shown in FIG. 1 may use register map portion 200 to communicate or exchange information with an NVDIMM controller for an NVDIMM such as NVDIMM controller 130 for NVDIMM 105. For these examples, selective assertion of various sets of bits maintained in corresponding sets of registers (e.g., maintained with registers 132) may be based, at least in part, on register map portion 200. Also, elements of the system may have read-only (RO) or read/ write (RW) access to the registers through an SMBus interface such as SMBus interface 122. Examples are not limited to elements of a system such as system 100 shown in FIG. 1, other elements of a computing platform (e.g., an operating system) may also use register map portion 200 to communicate with the NVDIMM controller.

According to some examples, register map portion 200 may be associated with a header. The header, for example, may be used to indicate capabilities and/or operating parameters of an NVDIMM and/or an NVDIMM controller. The header may also include information to interpret one or more other portions of an entire register map for use to communicate requests or commands to the NVDIMM controller. As shown in FIG. 2, various sets of bits may be associated with corresponding field names having specified offsets, lengths (in bytes) and access rights such a read/write (RW) or read-only (RO) from the perspective of elements of the host computing platform (requestor). A description is also shown in FIG. 2 for each sets of bits that may be selectively asserted either individually (e.g., a single bit) or in a group (e.g., multiple bits).

In some examples, as shown in FIG. 2, PAGE\_NUM has an offset value of 0x00 (hexadecimal), a length of 1 and a RW access. For these examples, the bits in the PAGE\_NUM field are the only bits in register map portion 200 that has RW access to allow a requestor to indicate a page number in 5 BIT[2:0], maximum number of pages in BIT[5:0] and reserves BIT[7:6] for possible future changes.

According to some examples, as shown in FIG. 2, the fields associated with offsets 0x01 to 0x03 indicate hardware and firmware revision information, respectively. The fields 10 associated with offsets 0x04 to 0x19 may be used to indicate operating parameters associated with elements of the NVDIMM such as the NVDIMM controller, non-volatile memory, volatile memory and capacitor package.

In some examples, the Number of SAVE regions field 15 may specify the number of SAVE regions in the NVDIMM for saving multiple copies of the volatile memory (DRAM) contents at various points of time. For these examples, the NVDIMM may be capable of supporting at least one region (e.g., identified as REGION-0). In other words, the non- 20 volatile memory (e.g., NAND flash) may have a memory capacity large enough to save a copy of all the contents of the DRAM in the at least one region. Also, the SAVE Latency and RESTORE Latency indicated at offsets 0x08 and 0x0A may indicate the respective worst case SAVE 25 latency in seconds (secs) and RESTORE latency in secs for REGION-0. The worst case SAVE and RESTORE latencies may take into consideration write or read latencies primarily associated with the non-volatile memory.

FIG. 3 illustrates a second example register map portion. 30 In some examples, as shown in FIG. 3, the second example register map portion includes register map portion 300. In some examples, elements of a system such as system 100 shown in FIG. 1 may use register map portion 300 to communicate or exchange information with an NVDIMM 35 controller for an NVDIMM. For these examples, selective assertion of various sets of bits maintained in corresponding sets of registers may be based, at least in part, on register map portion 300. As mentioned previously, elements of the an SMBus interface. Examples are not limited to elements of a system such as system 100 shown in FIG. 1, other elements of a computing platform may also use register map portion 300 to communicate or exchange information with the NVDIMM controller.

According to some examples, register portion 300 may be associated with an NVDIMM STATE class of requests received by the NVDIMM controller from elements of the host computing platform (requestor) to receive a status of the NVDIMM. For these examples, as shown in FIG. 3, the 50 bits in the GET\_NVDIMM\_STATE field are the only bits in register map portion 300 that has RW access to allow a requestor to indicate a request associated with an NVDIMM status or state.

In some examples, BIT7 of the GET\_NVDIMM\_STATE 55 field may be cleared (e.g., de-asserts the bit) by the requestor while issuing this request. For these examples, the NVDIMM controller sets (e.g., asserts) BIT7 to indicate the request has been accepted and bits associated with the T(NvState.SV) field shown in FIG. 3 have been populated or 60 selectively asserted. The bits selectively asserted for T(NvState.SV) may indicate a time-out in either milliseconds (ms) or secs for the requestor to wait for the NVDIMM controller to complete the request.

According to some examples, BIT6 of the GET\_ 65 NVDIMM\_STATE field may be cleared while the requestor is issuing this request. For these examples, the NVDIMM

controller sets BIT6 to indicate this request has been completed and NVDIMM status is indicated by selective assertion of bits associated with the NVDIMM\_STATUS field based on register map portion 300. In some examples, if BIT0 is set or asserted in the NVDIMM\_STATUS field, this may indicate that the NVDIMM controller is busy executing a previously received command (e.g., such as a SAVE, ERASE or RESTORE. However, the NVDIMM may still receive a new request or command and queue that new request or command for execution after completing the previous request or command.

In some examples, the BUSY\_TIMEOUT T(Busy) may indicate a time-out in either ms or secs for a requestor to wait for the NVDIMM controller to no longer be busy before determining that the NVDIMM controller is locked-up or malfunctioning. For these examples, the NVDIMM controller may populate or selectively assert the bits associated with this field before setting the corresponding NVDIMM\_STA-TUS.BUSY bit (e.g., BIT0 of the NVDIMM\_STATUS field) . The NVDIMM controller may update the BUSY\_TIM-EOUT T(Busy) field each time a GET\_NVDIMM\_STATUS request is received from the requestor.

FIG. 4 illustrates a third example register map portion. In some examples, as shown in FIG. 4, the third example register map portion includes register map portion 400. In some examples, elements of a system such as system 100 shown in FIG. 1 may use register map portion 400 to communicate or exchange information with an NVDIMM controller for an NVDIMM. For these examples, selective assertion of various sets of bits maintained in corresponding sets of registers may be based, at least in part, on register map portion 400. As mentioned previously, elements of the system may have RO or RW access to the registers through an SMBus interface. Examples are not limited to elements of a system such as system 100 shown in FIG. 1, other elements of a computing platform may also use register map portion 400 to communicate or exchange information with the NVDIMM controller.

According to some examples, register portion 400 may be system may have RO or RW access to the registers through 40 associated with a SAVE class of commands received by the NVDIMM controller from elements of the host computing platform (requestor) to cause the NVDIMM controller to save contents stored in the volatile memory to the nonvolatile memory. For these examples, as shown in FIG. 4, the bits in the SAVE\_CMD and ABORT\_SAVE fields in register map portion 400 both have RW access to allow a requestor to indicate a command either to execute a SAVE operation or ABORT a SAVE operation. Also, the SAVE\_IMAGE\_GUID field may allow for RW access for a requestor to indicate a global unique identifier (GUID) for an image or content to save to the non-volatile memory.

> In some examples, BIT7 of the SAVE CMD field may be cleared by the requestor while issuing this command. For these examples, the NVDIMM controller sets BIT7 to indicate the command has been accepted and bits associated with the T(Save.SV) field shown in FIG. 4 have been populated or selectively asserted. The bits selectively asserted for T(Save.SV) may indicate a time-out in either ms or secs for the requestor to wait for the NVDIMM controller to complete the SAVE command.

> According to some examples, BIT6 of the SAVE\_CMD field may be cleared while the requestor is issuing this command. For these examples, the NVDIMM controller sets BIT6 to indicate this command has been completed and a SAVE operation status is indicated by selective assertion of bits associated with the SAVE\_STATUS field based on register map portion 400.

In some examples, BIT5 of the SAVE\_CMD field may be asserted to indicate whether a valid image GUID has been associated with the content to be saved to the non-volatile memory as indicated in bits selectively asserted in the SAVE\_IMAGE\_GUID fields. For these examples, the 5 requestor may have indicated a GUID in the SAVE\_IM-AGE\_GUID for the NVDIMM controller to associate with content to be saved to the non-volatile memory. If the GUID is valid (e.g., doesn't match a previously associated GUID for another image) BIT5 may be asserted and the NVDIMM 10 controller may save the image/contents to an available region of the non-volatile memory. The NVDIMM controller may preserve the association between the GUID and the region saved, until an ERASE command is issued to this GUID. If GUID is not valid, BIT5 is not asserted and the 15 contents may be saved to a default region of the non-volatile memory (e.g., REGION-0).

In some examples, BIT7 of the ABORT\_SAVE field may be cleared by the requestor while issuing this command. For these examples, the NVDIMM controller sets BIT 7 to 20 indicate the command has been accepted and bits associated with the T(Save.SV) field shown in FIG. 4 have been populated or selectively asserted. The bits selectively asserted for T(Save.SV) may indicate a time-out in either ms or secs for the requestor to wait for the NVDIMM controller 25 to complete the ABORT\_SAVE command.

According to some examples, BIT6 of the ABORT\_SAVE field may be cleared while the requestor is issuing this command. For these examples, the NVDIMM controller sets BIT6 to indicate this command has been completed and an 30 ABORT SAVE operation status is indicated by selective assertion of bits associated with the SAVE\_STATUS field based on register map portion 400.

In some examples, BIT5 of the ABORT\_SAVE field may be asserted to indicate whether a valid image GUID has been 35 associated with the content for aborting the SAVE operation to the non-volatile memory as indicated in bits selectively asserted in the SAVE\_IMAGE\_GUID fields. If the GUID is valid (e.g., doesn't match a previously associated GUID for another image) BIT5 may be asserted and the NVDIMM 40 controller may abort the SAVE operation for the image/contents to an available region of the non-volatile memory. If GUID is not valid, BIT5 is not asserted and the NVDIMM controller may abort the SAVE operation for contents to be saved to a default region of the non-volatile memory (e.g., 45 REGION-0).

FIG. 5 illustrates a fourth example register map portion. In some examples, as shown in FIG. 5, the fourth example register map portion includes register map portion 500. In some examples, elements of a system such as system 100 50 shown in FIG. 1 may use register map portion 500 to communicate or exchange information with an NVDIMM controller for an NVDIMM. For these examples, selective assertion of various sets of bits maintained in corresponding sets of registers may be based, at least in part, on register 55 map portion 500. As mentioned previously, elements of the system may have RO or RW access to the registers through an SMBus interface. Examples are not limited to elements of a system such as system 100 shown in FIG. 1, other elements of a computing platform may also use register map portion 60 500 to communicate or exchange information with the NVDIMM controller.

According to some examples, register portion **500** may be associated with a RESTORE class of commands received by the NVDIMM controller from elements of the host computing platform (requestor) to cause the NVDIMM controller to RESTORE contents stored in the non-volatile memory to the

8

volatile memory. For these examples, as shown in FIG. 5, the bits in the RESTORE\_CMD and ABORT\_RESTORE fields in register map portion 500 both have RW access to allow a requestor to indicate a command either to execute a RESTORE operation or ABORT a RESTORE operation. Also, the RESTORE\_IMAGE\_GUID field may allow for RW access for a requestor to indicate a GUID for an image or content to restore to the volatile memory. The requestor or caller of a RESTORE\_CMD or ABORT\_RESTORE may setup the image GUID before invoking the command.

In some examples, BIT7 of the RESTORE\_CMD field may be cleared by the requestor while issuing this command. For these examples, the NVDIMM controller sets BIT7 to indicate the command has been accepted and bits associated with the T(Restore.SV) field shown in FIG. 5 have been populated or selectively asserted. The bits selectively asserted for T(Restore.SV) may indicate a time-out in either ms or secs for the requestor to wait for the NVDIMM controller to complete the RESTORE command.

According to some examples, BIT6 of the RESTO-RE\_CMD field may be cleared while the requestor is issuing this command. For these examples, the NVDIMM controller sets BIT6 to indicate this command has been completed and a RESTORE operation status is indicated by selective assertion of bits associated with the RESTORE\_STATUS field based on register map portion **500**.

In some examples, BIT5 of the RESTORE\_CMD field may be asserted to indicate whether a valid image GUID has been associated with the content to be restored to the volatile memory as indicated in bits selectively asserted in the RESTORE\_IMAGE\_GUID fields. For these examples, the requestor may have indicated a GUID in the RESTORE\_IMAGE\_GUID for the NVDIMM controller to associate with content to be restored to the volatile memory. If the GUID is valid (matches a previously associated GUID) BIT5 may be asserted and the NVDIMM controller may restore the image/contents to the volatile memory. If GUID is not valid, BIT5 is not asserted and the contents may be restored from a default region of the non-volatile memory (e.g., REGION-0) to the volatile memory.

In some examples, BIT7 of the ABORT\_RESTORE field may be cleared by the requestor while issuing this command. For these examples, the NVDIMM controller sets BIT7 to indicate the command has been accepted and bits associated with the T(RESTORE.SV) field shown in FIG. 5 have been populated or selectively asserted. The bits selectively asserted for T(RESTORE.SV) may indicate a time-out in either ms or secs for the requestor to wait for the NVDIMM controller to complete the ABORT\_RESTORE command.

According to some examples, BIT6 of the ABORT\_RE-STORE field may be cleared while the requestor is issuing this command. For these examples, the NVDIMM controller sets BIT6 to indicate this command has been completed and an ABORT RESTORE operation status is indicated by selective assertion of bits associated with the RESTORE\_STATUS field based on register map portion **500**.

In some examples, BIT5 of the ABORT\_RESTORE field may be asserted to indicate whether a valid image GUID has been associated with the content for aborting the RESTORE operation to the volatile memory as indicated in bits selectively asserted in the RESTORE\_IMAGE\_GUID fields. If the GUID is valid (matches a previously associated GUID) BIT5 may be asserted and the NVDIMM controller may abort the restore operation for the image/contents to the volatile memory. If GUID is not valid, BIT5 is not asserted and the restore operation for the contents being restored

from a default region of the non-volatile memory (e.g., REGION-0) to the volatile memory is aborted.

FIG. 6 illustrates a fifth example register map portion. In some examples, as shown in FIG. 6, the fifth example register map portion includes register map portion 600. In 5 some examples, elements of a system such as system 100 shown in FIG. 1 may use register map portion 600 to communicate or exchange information with an NVDIMM controller for an NVDIMM. For these examples, selective assertion of various sets of bits maintained in corresponding sets of registers may be based, at least in part, on register map portion 600. As mentioned previously, elements of the system may have RO or RW access to the registers through an SMBus interface. Examples are not limited to elements of a system such as system 100 shown in FIG. 1, other elements 15 of a computing platform may also use register map portion 600 to communicate or exchange information with the NVDIMM controller.

According to some examples, register portion 600 may be associated with an ERASE class of commands received by 20 the NVDIMM controller from elements of the host computing platform (requestor) to cause the NVDIMM controller to ERASE contents stored in the non-volatile memory. For these examples, as shown in FIG. 6, the bits in the ERASE\_CMD and ABORT\_ERASE fields in register map 25 portion 600 both have RW access to allow a requestor to indicate a command either to execute an ERASE operation or ABORT an ERASE operation. Also, the ERASE\_IMAGE\_GUID field may allow for RW access for a requestor to indicate a GUID for an image or content to erase from the 30 non-volatile memory.

In some examples, BIT7 of the ERASE\_CMD field may be cleared by the requestor while issuing this command. For these examples, the NVDIMM controller sets BIT7 to indicate the command has been accepted and bits associated 35 with the T(Erase.SV) field shown in FIG. 6 have been populated or selectively asserted. The bits selectively asserted for T(Erase.SV) may indicate a time-out in either ms or secs for the requestor to wait for the NVDIMM controller to complete the ERASE command.

According to some examples, BIT6 of the ERASE\_CMD field may be cleared while the requestor is issuing this command. For these examples, the NVDIMM controller sets BIT6 to indicate this command has been completed and an ERASE operation status is indicated by selective assertion 45 of bits associated with the ERASE\_STATUS field based on register map portion 600.

In some examples, BIT5 of the ERASE\_CMD field may be asserted to indicate whether a valid image GUID has been associated with the content to be erased from the non-volatile memory as indicated in bits selectively asserted in the ERASE\_IMAGE\_GUID fields. For these examples, the requestor may have indicated a GUID in the ERASE\_IMAGE\_GUID for the NVDIMM controller to determine what content and/or regions to erase from the non-volatile 55 memory. If the GUID is valid (e.g., matches a previously associated GUID) BIT5 may be asserted and the NVDIMM controller may ERASE the image/contents from the region of the non-volatile memory associated with the valid GUID. If GUID is not valid, BIT5 is not asserted and the contents 60 may be erased from a default region of the non-volatile memory (e.g., REGION-0).

In some examples, BIT7 of the ABORT\_ERASE field may be cleared by the requestor while issuing this command. For these examples, the NVDIMM controller sets BIT 7 to 65 indicate the command has been accepted and bits associated with the T(Erase.SV) field shown in FIG. 6 have been

10

populated or selectively asserted. The bits selectively asserted for T(Erase.SV) may indicate a time-out in either ms or secs for the requestor to wait for the NVDIMM controller to complete the ABORT ERASE command.

According to some examples, BIT6 of the ABORT\_ERASE field may be cleared while the requestor is issuing this command. For these examples, the NVDIMM controller sets BIT6 to indicate this command has been completed and an ABORT ERASE operation status is indicated by selective assertion of bits associated with the ERASE\_STATUS field based on register map portion **600**.

In some examples, BIT5 of the ABORT\_ERASE field may be asserted to indicate whether a valid image GUID has been associated with the content for aborting the ERASE operation to the non-volatile memory as indicated in bits selectively asserted in the SAVE\_IMAGE\_GUID fields. If the GUID is valid (e.g., matches a previously associated GUID) BIT5 may be asserted and the NVDIMM controller may abort the ERASE operation for the image/contents to the region of the non-volatile memory associated with the valid GUID. If GUID is not valid, BIT5 is not asserted and the NVDIMM controller may abort the ERASE operation for contents to be erased from a default region of the non-volatile memory (e.g., REGION-0).

FIG. 7 illustrates a sixth example register map portion. In some examples, as shown in FIG. 7, the sixth example register map portion includes register map portion 700. In some examples, elements of a system such as system 100 shown in FIG. 1 may use register map portion 700 to communicate or exchange information with an NVDIMM controller for an NVDIMM. For these examples, selective assertion of various sets of bits maintained in corresponding sets of registers may be based, at least in part, on register map portion 700. As mentioned previously, elements of the system may have RO or RW access to the registers through an SMBus interface. Examples are not limited to elements of a system such as system 100 shown in FIG. 1, other elements of a computing platform may also use register map portion 700 to communicate or exchange information with the NVDIMM controller.