(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5039368号

(P5039368)

(45) 発行日 平成24年10月3日(2012.10.3)

(24) 登録日 平成24年7月13日(2012.7.13)

(51) Int.Cl.

F 1

HO1L 27/115 (2006.01)

HO1L 21/8247 (2006.01)

HO1L 27/10 (2006.01)

HO1L 29/792 (2006.01)

HO1L 29/788 (2006.01)

HO1L 27/10 434

HO1L 27/10 481

HO1L 29/78 371

請求項の数 29 (全 41 頁) 最終頁に続く

(21) 出願番号

特願2006-325510 (P2006-325510)

(22) 出願日

平成18年12月1日 (2006.12.1)

(65) 公開番号

特開2007-189204 (P2007-189204A)

(43) 公開日

平成19年7月26日 (2007.7.26)

審査請求日

平成21年2月24日 (2009.2.24)

(31) 優先権主張番号

特願2005-358969 (P2005-358969)

(32) 優先日

平成17年12月13日 (2005.12.13)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000005821

パナソニック株式会社

大阪府門真市大字門真1006番地

(74) 代理人 110001427

特許業務法人前田特許事務所

(74) 代理人 100077931

弁理士 前田 弘

(74) 代理人 100110939

弁理士 竹内 宏

(74) 代理人 100110940

弁理士 嶋田 高久

(74) 代理人 100113262

弁理士 竹内 祐二

(74) 代理人 100115059

弁理士 今江 克実

最終頁に続く

(54) 【発明の名称】半導体記憶装置、その製造方法及びその駆動方法

(57) 【特許請求の範囲】

【請求項 1】

第1の半導体領域に形成され、複数のメモリセルが行列状に配置されたメモリセルアレイ領域と、

前記複数のメモリセルのうち、同一の行に並ぶメモリセル同士を共通に接続する複数のワード線と、

第2の半導体領域に前記メモリセルアレイ領域と分離して形成された保護ダイオード領域とを備え、

前記保護ダイオード領域には、前記第2の半導体領域の上部に形成された第1の拡散層と前記第2の半導体領域とが接合してなる保護ダイオード素子が構成され、

前記各ワード線は、前記保護ダイオード領域に延伸して前記第1の拡散層と直接に接続されることにより、前記保護ダイオード素子と電気的に接続されており、

前記第1の半導体領域は、第1導電型であり、

前記第2の半導体領域は、第1導電型ウエルを含み、

前記第1の拡散層は、第2導電型であって、且つ前記第1導電型ウエル内に形成されており、

前記保護ダイオード領域は、前記第1導電型ウエルと、該第1導電型ウエルに隣接して形成された第1の第2導電型ウエルと、前記第1導電型ウエルと前記第1の第2導電型ウエルとの上部で且つ接合部を跨ぐように形成された第1の第1導電型拡散層とを有し、

前記保護ダイオード素子は、前記第1の第2導電型拡散層、第1導電型ウエル、第1の

10

20

第1導電型拡散層及び第1の第2導電型ウエルにより構成されていることを特徴とする半導体記憶装置。

【請求項2】

前記第1導電型ウエル及び第1の第2導電型ウエルは、第1導電型の半導体基板に形成されており、

前記保護ダイオード領域は、前記第1導電型ウエル及び第1の第2導電型ウエルを内包し且つ前記第1導電型ウエル及び第1の第2導電型ウエルよりも接合面が深い第2の第2導電型ウエルと、前記第1の第2導電型ウエルと前記半導体基板との上部で且つ接合部を跨ぐように形成された第2の第2導電型拡散層とを有し、

前記保護ダイオード素子は、前記第1の第2導電型拡散層、第1導電型ウエル、第1の第1導電型拡散層、第1の第2導電型ウエル、第2の第2導電型ウエル及び第2の第2導電型拡散層により構成されていることを特徴とする請求項1に記載の半導体記憶装置。 10

【請求項3】

前記第1導電型ウエル及び第1の第2導電型ウエルは、第1導電型の半導体基板に形成されており、

前記保護ダイオード領域は、前記第1導電型ウエル及び第1の第2導電型ウエルを内包し且つ前記第1導電型ウエル及び第1の第2導電型ウエルよりも接合面が深い第2の第2導電型ウエルと、前記第1の第1導電型拡散層の上部に形成された金属による第1のシリサイド領域と、前記第1の第2導電型ウエルと前記半導体基板との上部で且つ接合部を跨ぐように形成された金属による第2のシリサイド領域とを有し、 20

前記保護ダイオード素子は、前記第1の第2導電型拡散層、第1導電型ウエル、第1の第1導電型拡散層、第1のシリサイド領域、第1の第2導電型ウエル、第2の第2導電型ウエル及び第2のシリサイド領域により構成されていることを特徴とする請求項1に記載の半導体記憶装置。

【請求項4】

前記第1導電型ウエル及び第1の第2導電型ウエルは、第1導電型の半導体基板に形成されており、

前記保護ダイオード領域は、前記第1導電型ウエル及び第1の第2導電型ウエルを内包し且つ前記第1導電型ウエル及び第1の第2導電型ウエルよりも接合面が深い第2の第2導電型ウエルと、前記第1の第2導電型ウエルにおける前記第1の第1導電型拡散層と反対側の上部に形成された第2の第2導電型拡散層と、前記半導体基板の上部における前記第2の第2導電型拡散層と隣接して形成された第2の第1導電型拡散層とを有し、 30

前記保護ダイオード素子は、前記第1の第2導電型拡散層、第1導電型ウエル、第1の第1導電型拡散層、第1の第2導電型ウエル、第2の第2導電型ウエル、第2の第2導電型拡散層及び第2の第1導電型拡散層により構成されていることを特徴とする請求項1に記載の半導体記憶装置。

【請求項5】

前記第1の第1導電型拡散層の上部には金属による第1のシリサイド領域が形成され、前記第2の第2導電型拡散層の上部には金属による第2のシリサイド領域が形成されていることを特徴とする請求項2に記載の半導体記憶装置。 40

【請求項6】

前記第1の第1導電型拡散層の上部には金属による第1のシリサイド領域が形成され、前記第2の第2導電型拡散層の上部及び前記第2の第1導電型拡散層の上部に跨るように、金属による第2のシリサイド領域が形成されていることを特徴とする請求項4に記載の半導体記憶装置。

【請求項7】

前記メモリセルアレイ領域における互いに隣接する前記メモリセル同士の間には絶縁膜が形成され、

前記保護ダイオード領域における前記第1の拡散層の上には前記絶縁膜が形成されていないことを特徴とする請求項1に記載の半導体記憶装置。 50

## 【請求項 8】

第1の半導体領域に形成され、複数のメモリセルが行列状に配置されたメモリセルアレイ領域と、

前記複数のメモリセルのうち、同一の行に並ぶメモリセル同士を共通に接続する複数のワード線と、

第2の半導体領域に前記メモリセルアレイ領域と分離して形成された保護ダイオード領域とを備え、

前記保護ダイオード領域には、前記第2の半導体領域の上部に形成された第1の拡散層と前記第2の半導体領域とが接合してなる保護ダイオード素子が構成され、

前記各ワード線は、前記保護ダイオード領域に延伸して前記第1の拡散層と直接に接続されることにより、前記保護ダイオード素子と電気的に接続されており、

前記第1の半導体領域は、第1導電型であり、

前記第2の半導体領域は、第2導電型ウエルを含み、

前記第1の拡散層は、第1導電型であって、且つ前記第2導電型ウエル内に形成されており、

前記保護ダイオード領域は、前記第2導電型ウエルと、該第2導電型ウエルに隣接して形成された第1の第1導電型ウエルと、前記第2導電型ウエルと前記第1の第1導電型ウエルとの上部で且つ接合部を跨ぐように形成された第1の第2導電型拡散層とを有し、

前記保護ダイオード素子は、前記第1の第1導電型拡散層、第2導電型ウエル、第1の第2導電型拡散層及び第1の第1導電型ウエルにより構成されていることを特徴とする半導体記憶装置。

## 【請求項 9】

前記第2導電型ウエル及び第1の第1導電型ウエルは、第1導電型の半導体基板に形成されており、

前記保護ダイオード領域は、前記第1の第1導電型ウエルにおける前記第1の第2導電型拡散層と反対側の上部に形成された第2の第1導電型拡散層を有し、

前記保護ダイオード素子は、前記第1の第1導電型拡散層、第2導電型ウエル、第1の第2導電型拡散層、第1の第1導電型ウエル及び第2の第1導電型拡散層により構成されていることを特徴とする請求項8に記載の半導体記憶装置。

## 【請求項 10】

前記第1の第2導電型拡散層の上部には金属による第1のシリサイド領域が形成され、

前記第2の第1導電型拡散層の上部には金属による第2のシリサイド領域が形成されていることを特徴とする請求項9に記載の半導体記憶装置。

## 【請求項 11】

前記メモリセルアレイ領域における互いに隣接する前記メモリセル同士の間には絶縁膜が形成され、

前記保護ダイオード領域における前記第1の拡散層の上には前記絶縁膜が形成されていないことを特徴とする請求項8に記載の半導体記憶装置。

## 【請求項 12】

前記各ワード線は、前記複数のメモリセルにそれぞれ形成された第1の導電層と、前記複数の第1の導電層のうち同一の行に並ぶ第1の導電層同士を共通に接続する第2の導電層とから構成されていることを特徴とする請求項1～11のいずれか1項に記載の半導体記憶装置。

## 【請求項 13】

前記各メモリセルは、前記第1の半導体領域と前記各第1の導電層との間に形成され、酸化膜の間に窒化膜が挟まれてなる積層絶縁膜を有するMONOS型メモリセルであることを特徴とする請求項12に記載の半導体記憶装置。

## 【請求項 14】

前記各ワード線は、前記複数のメモリセルにそれぞれ形成された第1の導電層と、前記複数の第1の導電層のうち同一の行に並ぶ第1の導電層同士を絶縁膜を介在させて容量結

10

20

30

40

50

合する第2の導電層とから構成されていることを特徴とする請求項1～11のいずれか1項に記載の半導体記憶装置。

【請求項15】

前記各メモリセルは、前記第1の半導体領域と前記各第1の導電層との間に形成されたトンネル絶縁膜を有する浮遊ゲート電極型メモリセルであることを特徴とする請求項14に記載の半導体記憶装置。

【請求項16】

第1導電型の半導体領域の上に、複数のメモリセルを行列状に配置したメモリセルアレイ領域と保護ダイオード領域とを分離して形成する半導体記憶装置の製造方法であって、

前記半導体領域に素子分離絶縁膜を選択的に形成する工程(a)と、

10

前記素子分離絶縁膜を含む前記半導体領域の上に、第1のシリコン酸化膜、シリコン窒化膜及び第2のシリコン酸化膜からなるONO膜、並びに第1の導電層を順次形成する工程(b)と、

前記メモリセルアレイ領域において、前記第1の導電層及びONO膜を列方向に延びる短冊状にパターニングすると共に、前記保護ダイオード領域において、前記第1の導電層を除去するようにパターニングする工程(c)と、

前記工程(c)よりも後に、パターニングされた前記第1の導電層をマスクとして、前記半導体領域の前記メモリセルアレイ領域においては、第2導電型拡散層からなり前記メモリセルのソースドレイン領域を形成すると共に、前記半導体領域の前記保護ダイオード領域においては、保護ダイオード素子を構成する第2導電型拡散層を形成する工程(d)と、

20

前記工程(d)よりも後に、パターニングされた前記第1の導電層を含む前記半導体領域の上に絶縁膜を形成した後、前記メモリセルアレイ領域において、パターニングされた前記第1の導電層の上面を露出する工程(e)と、

前記工程(d)よりも後に、前記保護ダイオード領域において、前記第2導電型拡散層の少なくとも一部を露出する工程(f)と、

前記工程(f)よりも後に、前記半導体領域における前記メモリセルアレイ領域及び保護ダイオード領域の上に第2の導電層を形成する工程(g)と、

前記工程(g)よりも後に、前記メモリセルアレイ領域において、前記第2の導電層及び第1の導電層を行方向にパターニングすることにより、それぞれ前記第1の導電層を含む行列状に配置された複数の前記メモリセルと、前記第2の導電層からなり同一の行に並ぶ複数の前記メモリセルを共通に接続する複数のワード線とを形成すると共に、前記保護ダイオード領域において、前記保護ダイオード素子の第2導電型拡散層と前記ワード線の端部とを直接に接続する工程(h)とを備えていることを特徴とする半導体記憶装置の製造方法。

30

【請求項17】

前記工程(e)及び工程(f)は、形成された前記絶縁膜に対してエッチングを行なうことにより、前記メモリセルアレイ領域において、前記各第1の導電層の上面を露出し且つ互いに隣接する前記第1の導電層及びONO膜の間を埋め込むと共に、前記保護ダイオード領域において、前記第2導電型拡散層の少なくとも一部を露出する工程であることを特徴とする請求項16に記載の半導体記憶装置の製造方法。

40

【請求項18】

前記工程(e)は、形成された前記絶縁膜に対して、化学機械研磨法により研磨することにより、前記メモリセルアレイ領域において、前記各第1の導電層の上面を露出する工程であり、

前記工程(f)は、前記保護ダイオード領域において、前記絶縁膜に対してエッチングを行なうことにより、前記第2導電型拡散層の少なくとも一部を露出する工程であることを特徴とする請求項16に記載の半導体記憶装置の製造方法。

【請求項19】

前記工程(c)において、前記保護ダイオード領域における前記ONO膜をさらに除去

50

するようにパターニングすることを特徴とする請求項16～18のいずれか1項に記載の半導体記憶装置の製造方法。

【請求項20】

前記工程(b)は、前記保護ダイオード領域における前記ONO膜を選択的に除去する工程と、

前記ONO膜が除去された前記保護ダイオード領域に第3のシリコン酸化膜を選択的に形成する工程とを含むことを特徴とする請求項16～18のいずれか1項に記載の半導体記憶装置の製造方法。

【請求項21】

第1導電型の半導体領域の上に、複数のメモリセルを行列状に配置したメモリセルアレイ領域と保護ダイオード領域とを分離して形成する半導体記憶装置の製造方法であって、10

前記半導体領域に素子分離絶縁膜を選択的に形成する工程(a)と、

前記素子分離絶縁膜を含む前記半導体領域の上に、トンネル絶縁膜及び第1の導電層を順次形成する工程(b)と、

前記メモリセルアレイ領域において、前記第1の導電層を列方向に延びる短冊状にパターニングすると共に、前記保護ダイオード領域において、前記第1の導電層を除去するようパターニングする工程(c)と、

前記工程(c)よりも後に、パターニングされた前記第1の導電層をマスクとして、前記半導体領域の前記メモリセルアレイ領域においては、第2導電型拡散層からなり前記メモリセルのソースドレイン領域を形成すると共に、前記半導体領域の前記保護ダイオード領域においては、保護ダイオード素子を構成する第2導電型拡散層を形成する工程(d)と、20

前記工程(d)よりも後に、パターニングされた前記第1の導電層を含む前記半導体領域の上に絶縁膜を形成した後、前記メモリセルアレイ領域において、パターニングされた前記第1の導電層の上面を露出する工程(e)と、

前記工程(d)よりも後に、前記保護ダイオード領域において、前記第2導電型拡散層の少なくとも一部を露出する工程(f)と、

前記メモリセルアレイ領域において、上面が露出した前記第1の導電層の上に、結合容量絶縁膜を選択的に形成する工程(g)と、

前記工程(g)よりも後に、前記半導体領域における前記メモリセルアレイ領域及び保護ダイオード領域の上に第2の導電層を形成する工程(h)と、30

前記工程(h)よりも後に、前記メモリセルアレイ領域において、前記第2の導電層、結合容量絶縁膜及び第1の導電層を行方向にパターニングすることにより、それぞれ前記第1の導電層及び結合容量絶縁膜を含む行列状に配置された複数の前記メモリセルと、前記第2の導電層からなり同一の行に並ぶ複数の前記メモリセルを共通に接続する複数のワード線とを形成すると共に、前記保護ダイオード領域において、前記保護ダイオード素子の第2導電型拡散層と前記ワード線の端部とを直接に接続する工程(i)とを備えていることを特徴とする半導体記憶装置の製造方法。

【請求項22】

前記工程(e)及び工程(f)は、形成された前記絶縁膜に対してエッチングを行なうことにより、前記メモリセルアレイ領域において、前記各第1の導電層の上面を露出し且つ互いに隣接する前記第1の導電層の間を埋め込むと共に、前記保護ダイオード領域において、前記第2導電型拡散層の少なくとも一部を露出する工程であることを特徴とする請求項21に記載の半導体記憶装置の製造方法。40

【請求項23】

前記工程(e)は、形成された前記絶縁膜に対して、化学機械研磨法により研磨することにより、前記メモリセルアレイ領域において、前記各第1の導電層の上面を露出する工程であり、

前記工程(f)及び(g)は、前記保護ダイオード領域において、前記結合容量絶縁膜及び絶縁膜に対してエッチングを行なうことにより、前記第2導電型拡散層の少なくとも50

一部を露出する工程であることを特徴とする請求項2\_1に記載の半導体記憶装置の製造方法。

【請求項 2\_4】

請求項4又は6に記載の半導体記憶装置の駆動方法であって、

前記ワード線に第1の端子を接続し、前記第1の第1導電型拡散層に第2の端子を接続し、前記第2の第2導電型拡散層及び第2の第1導電型拡散層に第3の端子を接続する工程と、

前記第1の端子に正のバイアス電圧を印加する際に、前記第2の端子及び第3の端子は接地状態とする工程とを備えていることを特徴とする半導体記憶装置の駆動方法。

【請求項 2\_5】

10

前記第1の端子に正のバイアス電圧を印加することにより、選択されたメモリセルに対して書き込み動作又は読み出し動作を行なう工程をさらに備えていることを特徴とする請求項2\_4に記載の半導体記憶装置の駆動方法。

【請求項 2\_6】

請求項4又は6に記載の半導体記憶装置の駆動方法であって、

前記ワード線に第1の端子を接続し、前記第1の第1導電型拡散層に第2の端子を接続し、前記第2の第2導電型拡散層及び第2の第1導電型拡散層に第3の端子を接続する工程と、

前記第1の端子に負のバイアス電圧を印加する際に、前記第2の端子には前記第1の端子と同一の電圧を印加し、且つ前記第3の端子は接地状態とする工程とを備えていることを特徴とする半導体記憶装置の駆動方法。

20

【請求項 2\_7】

前記第1の端子に負のバイアス電圧を印加することにより、選択されたメモリセルに対して消去動作を行なう工程をさらに備えていることを特徴とする請求項2\_6に記載の半導体記憶装置の駆動方法。

【請求項 2\_8】

請求項2又は5に記載の半導体記憶装置の駆動方法であって、

前記ワード線に第1の端子を接続し、前記第1の第1導電型拡散層に第2の端子を接続し、前記第2の第2導電型拡散層に第3の端子を接続する工程と、

前記第1の端子に正のバイアス電圧を印加することにより、選択されたメモリセルに対して書き込み動作又は読み出し動作を行なう工程と、

30

前記第1の端子に負のバイアス電圧を印加することにより、選択されたメモリセルに対して消去動作を行なう工程とを備えていることを特徴とする半導体記憶装置の駆動方法。

【請求項 2\_9】

請求項3に記載の半導体記憶装置の駆動方法であって、

前記ワード線に第1の端子を接続し、前記第1のシリサイド領域に第2の端子を接続し、前記第2のシリサイド領域に第3の端子を接続する工程と、

前記第1の端子に正のバイアス電圧を印加することにより、選択されたメモリセルに対して書き込み動作又は読み出し動作を行なう工程と、

前記第1の端子に負のバイアス電圧を印加することにより、選択されたメモリセルに対して消去動作を行なう工程とを備えていることを特徴とする半導体記憶装置の駆動方法。

40

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体記憶装置、特にEEPROM (electrically erasable programmable read-only memory) 等の不揮発性半導体記憶装置に関する。

【背景技術】

【0002】

半導体記憶装置は、読み出し対象となるメモリセルのゲート電極に所定の電圧を加えることにより、電荷蓄積層の電荷量の違いによる閾値電圧の変化を利用してデータとしての

50

「0」又は「1」を区別する。そのため、複数のメモリセルのゲート電極同士、ドレイン領域同士及びソース領域同士をそれぞれ共通に接続し、半導体基板上に複数のメモリセルを行列状に配置してメモリセルアレイを構成している。各メモリセルのゲート電極は、メモリセルアレイの行方向に沿って連続的に延設されてワード線として用いられる。各メモリセルのドレイン領域はメモリセルアレイの列方向に沿ってビット線と共に接続され、ソース領域はメモリセルアレイの列方向に沿ってソース線と共に接続されている。

【0003】

メモリセルアレイにおいては、以降に詳述するように製造工程中にゲート電極の帯電を防止することを目的として、通常、ワード線はその端部に保護ダイオードが接続されている。

10

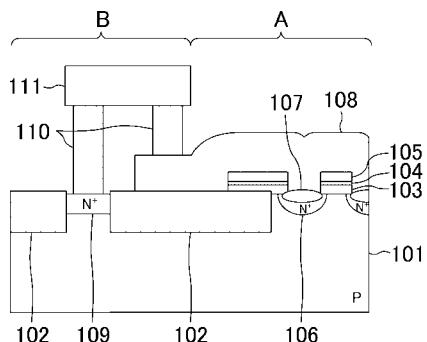

【0004】

図32は従来の一般的なメモリセルアレイにおけるワード線と保護ダイオードとの接続部分の断面構成を示している（例えば、特許文献1を参照。）。

【0005】

図32に示すように、P型半導体基板（又はP型ウェル）101の上部には、素子分離絶縁膜102により区画されたメモリセルアレイ領域Aと保護ダイオード領域Bとが形成されている。メモリセルアレイ領域Aには、P型半導体基板101の上に第1ゲート酸化膜103、電荷蓄積層104及び第2ゲート酸化膜105が順次形成された複数のゲート絶縁膜が行列状に配置されている。また、各第2ゲート酸化膜105の上には行方向に形成されたゲート電極を兼ねる複数のワード線108が形成されている。

20

【0006】

P型半導体基板101の上部における列方向に延びるゲート絶縁膜同士の間の領域にはソースドレイン拡散層106が形成され、該ソースドレイン拡散層106とワード線108との間には、絶縁膜107が形成されている。

【0007】

メモリセルアレイ領域Aに隣接する保護ダイオード領域Bには、P型半導体基板101の上部に形成されたN型拡散層109が形成されて、該N型拡散層109とP型半導体基板101とから保護ダイオード素子が形成されている。

【0008】

保護ダイオード素子におけるN型拡散層109とワード線108の端部とは、第1メタル配線111及び高融点金属からなるコンタクト110を介して電気的に接続されている。

30

【0009】

ところで、半導体記憶装置の製造工程、特にプラズマを使用する製造工程において、ワード線108の帯電により、該ワード線108の電位が高くなることがある。このとき、ワード線108に電流パスが存在しないと、ワード線108の電圧降下が起こらず、ワード線108に高い電位が保たれることになる。例えば、ワード線108が正に帯電した場合は、ワード線108に正の電圧が印加される状態と同等であるため、ソースドレイン拡散層106から電荷蓄積層104に電子が注入される。また、ワード線108が負に帯電した場合は、ワード線108に負の電圧が印加される状態と同等であるため、ソースドレイン拡散層106から電荷蓄積層104にホールが注入されるか、又はワード線108から電荷蓄積層104に電子が注入される。

40

【0010】

前述したように、メモリセルは、電荷蓄積層104に電荷を蓄積させることによる閾値電圧の変化を検出してデータである「1」又は「0」を判別する。従って、製造直後のメモリセルの閾値は、製造工程におけるワード線108の帯電による電荷蓄積層104の電荷量の変化の影響を受けることになり、データを判別する際の誤動作の原因となる。さらに、ワード線108が帯電により高電位となることは、各ゲート酸化膜103、105へのストレスとなるため、各ゲート酸化膜103、105の膜質が低下して、該酸化膜103、105の寿命が短縮してしまうという問題もある。

50

**【0011】**

このため、一般には、図32に示すように、ワード線108は例えば第1メタル配線111を介して保護ダイオード領域Bと接続されることにより、ワード線形成工程以降の各製造工程における高電圧の印加から保護されている。

【特許文献1】特開平10-173157号公報

**【発明の開示】****【発明が解決しようとする課題】****【0012】**

しかしながら、前記従来の半導体記憶装置の製造方法において、第1メタル配線111等の配線層を介してワード線108と保護ダイオード領域Bとを接続する方法は、配線層を形成するまで、より具体的には、最初の配線層を形成するための導電膜を堆積するまでの工程において、保護ダイオード領域Bの機能を活用することができない。

10

**【0013】**

特に、図32に示すコンタクト110の形成工程において、コンタクト110の構成材料である例えばタンクスチン等からなる高融点金属膜を形成する以前であれば、比較的に高温の熱処理(650以上)が可能であり、たとえ製造工程中のワード線108の帯電により、電荷蓄積層104に電荷が蓄積されたとしても、高温の熱処理を追加することにより、蓄積された電荷を放出させることができある。しかしながら、コンタクト形成用の高融点金属膜を形成した後は、高温の熱処理を実施できないため、電荷蓄積層104に蓄積された電荷を放出することができない。

20

**【0014】**

通常、コンタクト形成工程では、コンタクトホールのドライエッティングを含め、金属膜をスパッタリング成長する際等にプラズマを使用する。このため、配線層を介したワード線と保護ダイオード領域との接続は、ワード線形成用の導電層を堆積した後で且つコンタクト形成工程における高融点金属膜を形成した時点からその配線層を形成するまで、より具体的には、最初の配線層を形成するための導電膜を堆積するまでの間に生じるワード線の帯電による電荷蓄積層への電荷の注入を防ぐことができないという問題がある。

**【0015】**

本発明は、前記従来の問題を解決し、ワード線形成用の導電層を堆積した後の工程においても、ワード線の帯電による高電圧の印加からメモリセルを保護することができるようすることを目的とする。

30

**【課題を解決するための手段】****【0016】**

前記の目的を達成するため、本発明は、半導体記憶装置を、ワード線形成用の導電膜を保護ダイオード領域と直接に接する構成とする。

**【0017】**

具体的に、本発明に係る半導体記憶装置は、第1導電型の半導体領域に形成され、複数のメモリセルが行列状に配置されたメモリセルアレイ領域と、複数のメモリセルのうち、同一の行に並ぶメモリセル同士を共通に接続する複数のワード線と、半導体領域にメモリセルアレイ領域と分離して形成された保護ダイオード領域とを備え、保護ダイオード領域には、半導体領域の上部に形成された第1の第2導電型拡散層と半導体領域とが接合してなる保護ダイオード素子が構成され、各ワード線は、保護ダイオード領域に延伸して第1の第2導電型拡散層と直接に接続されることにより、保護ダイオード素子と電気的に接続されていることを特徴とする。

40

**【0018】**

本発明の半導体記憶装置によると、各ワード線は、保護ダイオード領域に延伸して第1の第2導電型拡散層と直接に接続されることにより、保護ダイオード素子と電気的に接続されているため、ワード線形成用の導電膜が形成された後は保護ダイオード素子が機能するようになる。すなわち、ワード線が保護ダイオード領域の第1の第2導電型拡散層と接続された後は、例えば第1導電型がP型で且つ第2導電型がN型の場合は、製造工程で発

50

生するワード線（ゲート電極）の負の帯電は P N 接合の順方向電圧となる電流パスを持つため、ワード線は絶対値が大きい負の電位とはならない。また、製造工程で発生するワード線の正の帯電に対しても、P N 接合の逆方向電圧以上の電位となることはない。このため、従来では配線層を介したワード線と保護ダイオードとの接続法では防ぐことができなかった、コンタクト形成工程の高融点金属膜の形成後から配線層の堆積までの間においてもワード線の帯電による電荷蓄積層への電荷の注入を防止することができる。なお、上記の効果は、第 1 導電型が P 型で且つ第 2 導電型が N 型の場合を説明したが、これとは逆に、第 1 導電型が N 型で且つ第 2 導電型が P 型である場合についても、順方向及び逆方向の帯電の方向が逆になるだけであり、上記と同様の効果を得られることはいうまでもない。

【0019】

10

本発明の半導体記憶装置において、保護ダイオード領域は、半導体領域からなる第 1 導電型ウェルと、該第 1 導電型ウェルに対してメモリセルアレイ領域の反対側に隣接して形成された第 1 の第 2 導電型ウェルと、第 1 導電型ウェルと第 1 の第 2 導電型ウェルとの上部で且つ接合部を跨ぐように形成された第 1 の第 1 導電型拡散層とを有し、保護ダイオード素子は、第 1 の第 2 導電型拡散層、第 1 導電型ウェル、第 1 の第 1 導電型拡散層及び第 1 の第 2 導電型ウェルにより構成されていることが好ましい。

【0020】

このようにすると、ワード線が保護ダイオード領域の第 1 導電型ウェル内の第 1 の第 2 導電型拡散層と接続された後は、例えば第 1 導電型が P 型で且つ第 2 導電型が N 型の場合は、製造工程で発生するワード線の負の帯電は、保護ダイオード領域における第 1 導電型ウェルと第 1 の第 2 導電型ウェルとの接合部の上部で且つ接合部を跨ぐように形成された第 1 の第 1 導電型拡散層と第 1 の第 2 導電型ウェルとの接合部分において P N 接合の逆方向電圧となるため、ワード線は逆方向電圧よりも絶対値が大きい負の電位とはならない。また、製造工程で発生するワード線の正の帯電も、保護ダイオード領域における第 1 導電型ウェルと該第 1 導電型ウェルの上部の第 1 の第 2 導電型拡散層との接合部分において P N 接合の逆方向電圧となるため、ワード線は逆方向電圧以上の正の高い電位とはならない。このため、ワード線の帯電による電荷蓄積層への電荷の注入を防止することができる。また、ワード線に負の電圧を印加した場合においても、ワード線の負の電位の絶対値を高めることができるために、ワード線に負電圧を印加可能なデバイスを実現できる。

【0021】

20

本発明の半導体記憶装置において、第 1 導電型ウェル及び第 1 の第 2 導電型ウェルは、第 1 導電型の半導体基板に形成されており、保護ダイオード領域は、第 1 導電型ウェル及び第 1 の第 2 導電型ウェルを内包し且つ第 1 導電型ウェル及び第 1 の第 2 導電型ウェルよりも接合面が深い第 2 の第 2 導電型ウェルと、第 1 の第 2 導電型ウェルと半導体基板との上部で且つ接合部を跨ぐように形成された第 2 の第 2 導電型拡散層とを有し、保護ダイオード素子は、第 1 の第 2 導電型拡散層、第 1 導電型ウェル、第 1 の第 1 導電型拡散層、第 1 の第 2 導電型ウェル、第 2 の第 2 導電型ウェル及び第 2 の第 2 導電型拡散層により構成されていることが好ましい。

【0022】

30

このようにすると、ワード線が保護ダイオード領域の第 1 の第 2 導電型拡散層と接続された後は、例えば第 1 導電型が P 型で且つ第 2 導電型が N 型の場合は、製造工程で発生するワード線の負の帯電は、保護ダイオード領域における第 1 導電型ウェルと第 1 の第 2 導電型ウェルとの接合部を跨ぐように形成された第 1 の第 1 導電型拡散層と、第 1 の第 2 導電型ウェルとの接合部分において P N 接合の逆方向電圧となるため、ワード線は逆方向電圧よりも絶対値が大きい負の電位とはならない。また、製造工程で発生するワード線の正の帯電については、保護ダイオード領域における第 1 導電型ウェルと該第 1 導電型ウェル内の第 1 の第 2 導電型拡散層との接合部分と、保護ダイオード領域における第 1 導電型の半導体基板と第 1 の第 2 導電型ウェルとの上部で且つ接合部を跨ぐように形成された第 2 の第 2 導電型拡散層と半導体基板との接合部分との 2 箇所で P N 接合の逆方向電圧となるため、ワード線は逆方向電圧以上の正の高い電位とはならない。このため、ワ

40

50

ード線の帯電による電荷蓄積層への電荷の注入を防止することが可能となる。その上、ワード線に負の電圧を印加した場合においても、ワード線の負の電位の絶対値を高めることができるため、ワード線に負電圧を印加可能なデバイスを実現できる。

#### 【0023】

本発明の半導体記憶装置において、第1導電型ウェル及び第1の第2導電型ウェルは、第1導電型の半導体基板に形成されており、保護ダイオード領域は、第1導電型ウェル及び第1の第2導電型ウェルを内包し且つ第1導電型ウェル及び第1の第2導電型ウェルよりも接合面が深い第2の第2導電型ウェルと、第1の第1導電型拡散層の上部に形成された金属による第1のシリサイド領域と、第1の第2導電型ウェルと半導体基板との上部で且つ接合部を跨ぐように形成された金属による第2のシリサイド領域とを有し、保護ダイオード素子は、第1の第2導電型拡散層、第1導電型ウェル、第1の第1導電型拡散層、第1のシリサイド領域、第1の第2導電型ウェル、第2の第2導電型ウェル及び第2のシリサイド領域により構成されていることが好ましい。10

#### 【0024】

このようにすると、ワード線が保護ダイオード領域の第1の第2導電型拡散層と接続された後は、例えば第1導電型がP型で且つ第2導電型がN型の場合は、製造工程で発生するワード線の負の帯電は、保護ダイオード領域における第1導電型ウェルと第1の第2導電型ウェルとの上部で且つ接合部を跨ぐように形成された第1の第1導電型拡散層と第1の第2導電型ウェルとの接合部分においてPN接合の逆方向電圧となるため、ワード線は逆方向電圧よりも絶対値が大きい負の電位とはならない。また、製造工程で発生するワード線の正の帯電については、保護ダイオード領域における第1導電型ウェルと該第1導電型ウェル内の第1の第2導電型拡散層との接合部分においてPN接合の逆方向電圧となるため、ワード線は逆方向電圧以上の正の高い電位とはならない。このため、ワード線の帯電による電荷蓄積層への電荷の注入を防止することが可能となる。その上、ワード線に負の電圧を印加した場合においても、ワード線の負の電位の絶対値を高めることができため、ワード線に負電圧を印加可能なデバイスを実現できる。また、ワード線に正の高電圧が印加された場合は、電流が半導体基板に流れるまでに逆方向電圧となる箇所が1箇所のみであるため、耐圧の制御が容易となり且つ動作が安定する。20

#### 【0025】

本発明の半導体記憶装置において、第1導電型ウェル及び第1の第2導電型ウェルは、第1導電型の半導体基板に形成されており、保護ダイオード領域は、第1導電型ウェル及び第1の第2導電型ウェルを内包し且つ第1導電型ウェル及び第1の第2導電型ウェルよりも接合面が深い第2の第2導電型ウェルと、第1の第2導電型ウェルにおける第1の第1導電型拡散層と反対側の上部に形成された第2の第2導電型拡散層と、半導体基板の上部における第2の第2導電型拡散層と隣接して形成された第2の第1導電型拡散層とを有し、保護ダイオード素子は、第1の第2導電型拡散層、第1導電型ウェル、第1の第1導電型拡散層、第1の第2導電型ウェル、第2の第2導電型ウェル、第2の第2導電型拡散層及び第2の第1導電型拡散層により構成されていることが好ましい。30

#### 【0026】

このようにすると、ワード線が保護ダイオード領域の第2導電型拡散層と接続された後は、例えば第1導電型がP型で且つ第2導電型がN型の場合は、製造工程で発生するワード線の負の帯電は、保護ダイオード領域における第1導電型ウェルと第1の第2導電型ウェルとの上部で且つ接合部を跨ぐように形成された第1の第1導電型拡散層と第1の第2導電型ウェルとの接合部分においてPN接合の逆方向電圧となるため、ワード線は逆方向電圧よりも絶対値が大きい負の電位とはならない。また、製造工程で発生するワード線の正の帯電については、保護ダイオード領域における第1導電型ウェルと該第1導電型ウェル内の第1の第2導電型拡散層との接合部分と、保護ダイオード領域における第1の第2導電型ウェル内の第2の第2導電型拡散層と第1導電型の半導体基板における第2の第1導電型拡散層との接合部分との2箇所でPN接合の逆方向電圧となるため、ワード線は逆方向電圧以上の正の高い電位とはならない。このため、ワード線の帯電による電荷蓄積層4050

への電荷の注入を防止することが可能となる。また、ワード線に負の電圧を印加した場合においてもワード線の負の電位の絶対値を高めることができるために、ワード線に負の電圧を印加可能なデバイスを実現できる。また、保護ダイオード領域における第1の第2導電型ウェル内の第2の第2導電型拡散層と、半導体基板中の第2の第1導電型拡散層とのP-N接合は、不純物濃度を容易に高くすることができるため、この部分のP-N接合耐圧をより低く設計することができるので、耐圧の制御が容易となり且つ動作が安定する。

【0027】

本発明の半導体記憶装置において、第1の第1導電型拡散層の上部には金属による第1のシリサイド領域が形成され、第2の第2導電型拡散層の上部には金属による第2のシリサイド領域が形成されていることが好ましい。

10

【0028】

このようにすると、第1の第1導電型拡散層及び第2の第2導電型拡散層がシリサイドにより低抵抗化することが可能となるため、製造工程においてワード線が正又は負に帯電して、該ワード線に保護ダイオード素子の逆方向耐圧以上の電圧が印加された場合に、発生した電流を半導体基板に容易に流すことができる。その結果、例えばゲート絶縁膜へのストレス又はメモリセルの電荷蓄積層への電荷の注入を確実に抑制することができる。

【0029】

本発明の半導体記憶装置において、第1の第1導電型拡散層の上部には金属による第1のシリサイド領域が形成され、第2の第2導電型拡散層の上部及び第2の第1導電型拡散層の上部に跨るように、金属による第2のシリサイド領域が形成されていることが好ましい。

20

【0030】

このようにすると、保護ダイオード領域における第2の第2導電型拡散層と第2の第1導電型拡散層とが金属シリサイドにより接続されるため、ワード線に正の高電圧が印加された場合に、電流が半導体基板に流れるまでに逆方向電圧となる箇所が保護ダイオード領域の第1導電型ウェル領域と第1導電型ウェル領域内の第2導電型拡散層との接合部分の1箇所のみとなる。その結果、耐圧の制御が容易となり且つ動作が安定する。

【0031】

本発明の半導体記憶装置において、メモリセルアレイ領域における互いに隣接するメモリセル同士の間には絶縁膜が形成され、保護ダイオード領域における第1の第2導電型拡散層の上には絶縁膜が形成されていないことが好ましい。

30

【0032】

このようにすると、メモリセルアレイ領域においては、互いに隣接するメモリセル同士の間に絶縁膜が確実に埋め込まれると共に、保護ダイオード領域においては、第1の第2導電型拡散層の上に絶縁膜が形成されないことから、第1の第2導電型拡散層の上に絶縁膜が形成される場合と比べて、ワード線と第2導電型拡散層とをより小さいサイズで直接に接続することができる。

【0033】

本発明の半導体記憶装置において、各ワード線は、複数のメモリセルにそれぞれ形成された第1の導電層と、複数の第1の導電層のうち同一の行に並ぶ第1の導電層同士を共通に接続する第2の導電層とから構成されていることが好ましい。

40

【0034】

このようにすると、ワード線と保護ダイオード領域における第1の第2導電型拡散層とが自己整合的に接続されると共に、ワード線と第1の導電層もそれぞれ直接に接続される。

【0035】

本発明の半導体記憶装置において、各メモリセルは、第1の半導体領域と各第1の導電層との間に形成され、酸化膜の間に窒化膜が挟まれてなる積層絶縁膜を有するMONOS型メモリセルであることが好ましい。

50

**【 0 0 3 6 】**

また、本発明の半導体記憶装置において、各ワード線は、複数のメモリセルにそれぞれ形成された第1の導電層と、複数の第1の導電層のうち同一の行に並ぶ第1の導電層同士を絶縁膜を介在させて容量結合する第2の導電層とから構成されていることが好ましい。

**【 0 0 3 7 】**

このようにすると、ワード線と保護ダイオード領域における第1の第2導電型拡散層とが自己整合的に接続されると共に、ワード線と第1の導電層は絶縁膜を介在させて容量結合される。

**【 0 0 3 8 】**

この場合に、各メモリセルは、第1の半導体領域と各第1の導電層との間に形成されたトンネル絶縁膜を有する浮遊ゲート電極型メモリセルであることが好ましい。 10

**【 0 0 3 9 】**

本発明に係る第1の半導体記憶装置の製造方法は、第1導電型の半導体領域の上に、複数のメモリセルを行列状に配置したメモリセルアレイ領域と保護ダイオード領域とを分離して形成する半導体記憶装置の製造方法を対象とし、半導体領域に素子分離絶縁膜を選択的に形成する工程(a)と、素子分離絶縁膜を含む半導体領域の上に、第1のシリコン酸化膜、シリコン窒化膜及び第2のシリコン酸化膜からなるONO膜、並びに第1の導電層を順次形成する工程(b)と、メモリセルアレイ領域において、第1の導電層及びONO膜を列方向に延びる短冊状にパターニングすると共に、保護ダイオード領域において、第1の導電層を除去するようにパターニングする工程(c)と、工程(c)よりも後に、パターニングされた第1の導電層をマスクとして、半導体領域のメモリセルアレイ領域においては、第2導電型拡散層からなりメモリセルのソースドレイン領域を形成すると共に、半導体領域の保護ダイオード領域においては、保護ダイオード素子を構成する第2導電型拡散層を形成する工程(d)と、工程(d)よりも後に、パターニングされた第1の導電層を含む半導体領域の上に絶縁膜を形成した後、メモリセルアレイ領域において、パターニングされた第1の導電層の上面を露出する工程(e)と、工程(e)よりも後に、保護ダイオード領域において、第2導電型拡散層の少なくとも一部を露出する工程(f)と、工程(f)よりも後に、半導体領域におけるメモリセルアレイ領域及び保護ダイオード領域の上に第2の導電層を形成する工程(g)と、工程(g)よりも後に、メモリセルアレイ領域において、第2の導電層及び第1の導電層を行方向にパターニングすることにより、それぞれ第1の導電層を含む行方向に配置された複数のメモリセルと、第2の導電層からなり同一の行に並ぶ複数のメモリセルを共通に接続する複数のワード線とを形成すると共に、保護ダイオード領域において、保護ダイオード素子の第2導電型拡散層とワード線の端部とを直接に接続する工程(h)とを備えていることを特徴とする。 20

**【 0 0 4 0 】**

第1の半導体記憶装置の製造方法によると、メモリセルアレイ領域において、第2の導電層及び第1の導電層を行方向にパターニングすることにより、それぞれ第1の導電層を含む行方向に配置された複数のメモリセルと、第2の導電層からなり同一の行に並ぶ複数のメモリセルを共通に接続する複数のワード線とを形成すると共に、表面が露出した保護ダイオード領域において、保護ダイオード素子の第2導電型拡散層とワード線の端部とを直接に接続する。このため、メモリセル形成工程において、ワード線と保護ダイオード素子とが同時に且つ自己整合的に接続されるため、製造過程に新たな工程を追加することなく、メモリセルの安定した電気的特性を実現できる。また、ワード線形成用の第2の導電層を堆積した後の工程においては保護ダイオード素子が機能するため、従来では配線層を介したワード線と保護ダイオード素子の接続では防ぐことができなかった、コントラクト形成工程の高融点金属膜形成以降から配線層堆積までの間においても、ワード線の帯電による電荷蓄積層への電荷の注入を防止することが可能となる。 30

**【 0 0 4 1 】**

第1の半導体記憶装置の製造方法において、工程(e)及び工程(f)は、形成された絶縁膜に対してエッチングを行なうことにより、メモリセルアレイ領域において、各第1 50

の導電層の上面を露出し且つ互いに隣接する第1の導電層及びONO膜の間を埋め込むと共に、保護ダイオード領域において、第2導電型拡散層の少なくとも一部を露出する工程であることが好ましい。

【0042】

また、第1の半導体記憶装置の製造方法において、工程(e)は、形成された絶縁膜に対して、化学機械研磨法により研磨することにより、メモリセルアレイ領域において、各第1の導電層の上面を露出する工程であり、工程(f)は、保護ダイオード領域において、絶縁膜に対してエッティングを行なうことにより、第2導電型拡散層の少なくとも一部を露出する工程であることが好ましい。

【0043】

第1の半導体記憶装置の製造方法は、工程(c)において、保護ダイオード領域における前記ONO膜をさらに除去するようにパターニングすることが好ましい。

【0044】

また、第1の半導体記憶装置の製造方法において、工程(b)は、保護ダイオード領域におけるONO膜を選択的に除去する工程と、ONO膜が除去された保護ダイオード領域に第3のシリコン酸化膜を選択的に形成する工程とを含むことが好ましい。

【0045】

本発明に係る第2の半導体記憶装置の製造方法は、第1導電型の半導体領域の上に、複数のメモリセルを行列状に配置したメモリセルアレイ領域と保護ダイオード領域とを分離して形成する半導体記憶装置の製造方法を対象とし、半導体領域に素子分離絶縁膜を選択的に形成する工程(a)と、素子分離絶縁膜を含む半導体領域の上に、トンネル絶縁膜及び第1の導電層を順次形成する工程(b)と、メモリセルアレイ領域において、第1の導電層を列方向に延びる短冊状にパターニングすると共に、保護ダイオード領域において、第1の導電層を除去するようにパターニングする工程(c)と、工程(c)よりも後に、パターニングされた第1の導電層をマスクとして、半導体領域のメモリセルアレイ領域においては、第2導電型拡散層からなりメモリセルのソースドレイン領域を形成すると共に、半導体領域の保護ダイオード領域においては、保護ダイオード素子を構成する第2導電型拡散層を形成する工程(d)と、工程(d)よりも後に、パターニングされた第1の導電層を含む半導体領域の上に絶縁膜を形成した後、メモリセルアレイ領域において、パターニングされた第1の導電層の上面を露出する工程(e)と、工程(d)よりも後に、保護ダイオード領域において、第2導電型拡散層の少なくとも一部を露出する工程(f)と、メモリセルアレイ領域において、上面が露出した第1の導電層の上に、結合容量絶縁膜を選択的に形成する工程(g)と、工程(g)よりも後に、半導体領域におけるメモリセルアレイ領域及び保護ダイオード領域の上に第2の導電層を形成する工程(h)と、工程(h)よりも後に、メモリセルアレイ領域において、第2の導電層、結合容量絶縁膜及び第1の導電層を行方向にパターニングすることにより、それぞれ第1の導電層及び結合容量絶縁膜を含む行列状に配置された複数のメモリセルと、第2の導電層からなり同一の行に並ぶ複数のメモリセルを共通に接続する複数のワード線とを形成すると共に、保護ダイオード領域において、保護ダイオード素子の第2導電型拡散層とワード線の端部とを直接に接続する工程(i)とを備えていることを特徴とする。

【0046】

第2の半導体記憶装置の製造方法によると、メモリセルアレイ領域において、第2の導電層、結合容量絶縁膜及び第1の導電層を行方向にパターニングすることにより、それぞれ第1の導電層及び結合容量絶縁膜を含む行列状に配置された複数のメモリセルと、第2の導電層からなり同一行に並ぶ複数のメモリセルを共通に接続するワード線とを形成すると共に、表面が露出した保護ダイオード領域において、保護ダイオード素子の第2導電型拡散層とワード線の端部とを直接に接続させる。このため、メモリセル形成工程において、ワード線と保護ダイオードとが同時に且つ自己整合的に接続されるため、製造過程に新たな工程を追加することなく、メモリセルの安定した電気的特性を実現できる。また、ワード線形成用の第2の導電層を堆積した後の工程において保護ダイオード素子が機能する

10

20

30

40

50

ため、従来のように配線層を介したワード線と保護ダイオード素子との接続では防ぐことができなかった、コンタクト形成工程の高融点金属膜形成以降から配線層堆積までの間ににおいても、ワード線の帯電によるトンネル絶縁膜へのストレスを抑制することが可能となる。

【0047】

第2の半導体記憶装置の製造方法において、工程(e)及び工程(f)は、形成された絶縁膜に対してエッティングを行なうことにより、メモリセルアレイ領域において、各第1の導電層の上面を露出し且つ互いに隣接する第1の導電層の間を埋め込むと共に、保護ダイオード領域において、第2導電型拡散層の少なくとも一部を露出する工程であることが好ましい。

10

【0048】

また、第2の半導体記憶装置の製造方法において、工程(e)は、形成された絶縁膜に対して、化学機械研磨法により研磨することにより、メモリセルアレイ領域において、各第1の導電層の上面を露出する工程であり、工程(f)及び(g)は、保護ダイオード領域において、結合容量絶縁膜及び絶縁膜に対してエッティングを行なうことにより、第2導電型拡散層の少なくとも一部を露出する工程であることが好ましい。

【0049】

このようにすると、微細パターンにおいても、メモリセルアレイ領域において互いに隣接する第1の導電層同士の間の領域を絶縁膜で確実に埋め込むことができる。また、保護ダイオード領域においても、保護ダイオード領域の第2導電型拡散層を確実に露出させることができが可能となる。従って、メモリセルの間隔を狭めることができると共に、保護ダイオード領域のサイズをも縮小することができる。

20

【0050】

本発明に係る第1の半導体記憶装置の駆動方法は、本発明に係る半導体記憶装置のうち、第1導電型ウェル及び第1の第2導電型ウェルは、第1導電型の半導体基板に形成されており、保護ダイオード領域は、第1導電型ウェル及び第1の第2導電型ウェルを内包し且つ第1導電型ウェル及び第1の第2導電型ウェルよりも接合面が深い第2の第2導電型ウェルと、第1の第2導電型ウェルにおける第1の第1導電型拡散層と反対側の上部に形成された第2の第2導電型拡散層と、半導体基板の上部における第2の第2導電型拡散層と隣接して形成された第2の第1導電型拡散層とを有し、保護ダイオード素子は、第1の第2導電型拡散層、第1導電型ウェル、第1の第1導電型拡散層、第1の第2導電型ウェル、第2の第2導電型ウェル、第2の第2導電型拡散層及び第2の第1導電型拡散層により構成された半導体記憶装置を対象とし、ワード線に第1の端子を接続し、第1の第1導電型拡散層に第2の端子を接続し、第2の第2導電型拡散層及び第2の第1導電型拡散層に第3の端子を接続する工程と、第1の端子に正のバイアス電圧を印加する際に、第2の端子及び第3の端子は接地状態とする工程とを備えていることを特徴とする。

30

【0051】

第1の半導体記憶装置の駆動方法によると、保護ダイオード領域において深い接合面を持つ第2の第2導電型ウェル中に形成された第1導電型ウェルの電位が安定化するため、メモリセルの書き込み、消去及び読み出しの各動作を安定的に行なうことができる。

40

【0052】

第1の半導体記憶装置の駆動方法は、第1の端子に正のバイアス電圧を印加することにより、選択されたメモリセルに対して書き込み動作又は読み出し動作を行なう工程をさらに備えていることが好ましい。

【0053】

本発明に係る第2の半導体記憶装置の駆動方法は、本発明に係る半導体記憶装置のうち、第1導電型ウェル及び第1の第2導電型ウェルは、第1導電型の半導体基板に形成されており、保護ダイオード領域は、第1導電型ウェル及び第1の第2導電型ウェルを内包し且つ第1導電型ウェル及び第1の第2導電型ウェルよりも接合面が深い第2の第2導電型ウェルと、第1の第2導電型ウェルにおける第1の第1導電型拡散層と反対側の上部に形

50

成された第2の第2導電型拡散層と、半導体基板の上部における第2の第2導電型拡散層と隣接して形成された第2の第1導電型拡散層とを有し、保護ダイオード素子は、第1の第2導電型拡散層、第1導電型ウェル、第1の第1導電型拡散層、第1の第2導電型ウェル、第2の第2導電型ウェル、第2の第2導電型拡散層及び第2の第1導電型拡散層により構成された半導体記憶装置を対象とし、ワード線に第1の端子を接続し、第1の第1導電型拡散層に第2の端子を接続し、第2の第2導電型拡散層及び第2の第1導電型拡散層に第3の端子を接続する工程と、第1の端子に負のバイアス電圧を印加する際に、第2の端子には第1の端子と同一の電圧を印加し、且つ第3の端子は接地状態とする工程とを備えていることを特徴とする。

## 【0054】

10

第2の半導体記憶装置の駆動方法は、第1の端子に負のバイアス電圧を印加することにより、選択されたメモリセルに対して消去動作を行なう工程をさらに備えていることが好ましい。

## 【0055】

20

本発明に係る第3の半導体記憶装置の駆動方法は、本発明に係る半導体記憶装置のうち、第1導電型ウェル及び第1の第2導電型ウェルは、第1導電型の半導体基板に形成されており、保護ダイオード領域は、第1導電型ウェル及び第1の第2導電型ウェルを内包し且つ第1導電型ウェル及び第1の第2導電型ウェルよりも接合面が深い第2の第2導電型ウェルと、第1の第2導電型ウェルと半導体基板との上部で且つ接合部を跨ぐように形成された第2の第2導電型拡散層とを有し、保護ダイオード素子は、第1の第2導電型拡散層、第1導電型ウェル、第1の第1導電型拡散層、第1の第2導電型ウェル、第2の第2導電型ウェル及び第2の第2導電型拡散層により構成された半導体記憶装置を対象とし、ワード線に第1の端子を接続し、第1の第1導電型拡散層に第2の端子を接続し、第2の第2導電型拡散層に第3の端子を接続する工程と、第1の端子に正のバイアス電圧を印加することにより、選択されたメモリセルに対して書き込み動作又は読み出し動作を行なう工程と、第1の端子に負のバイアス電圧を印加することにより、選択されたメモリセルに対して消去動作を行なう工程とを備えていることを特徴とする。

## 【0056】

30

本発明に係る第4の半導体記憶装置の駆動方法は、本発明に係る半導体記憶装置のうち、第1導電型ウェル及び第1の第2導電型ウェルは、第1導電型の半導体基板に形成されており、保護ダイオード領域は、第1導電型ウェル及び第1の第2導電型ウェルを内包し且つ第1導電型ウェル及び第1の第2導電型ウェルよりも接合面が深い第2の第2導電型ウェルと、第1の第1導電型拡散層の上部に形成された第1のシリサイド領域と、第1の第2導電型ウェルと半導体基板との上部で且つ接合部を跨ぐように形成された第2のシリサイド領域とを有し、保護ダイオード素子は、第1の第2導電型拡散層、第1導電型ウェル、第1の第1導電型拡散層、第1のシリサイド領域、第1の第2導電型ウェル、第2の第2導電型ウェル及び第2のシリサイド領域により構成された半導体記憶装置を対象とし、ワード線に第1の端子を接続し、第1のシリサイド領域に第2の端子を接続し、第2のシリサイド領域に第3の端子を接続する工程と、第1の端子に正のバイアス電圧を印加することにより、選択されたメモリセルに対して書き込み動作又は読み出し動作を行なう工程と、第1の端子に負のバイアス電圧を印加することにより、選択されたメモリセルに対して消去動作を行なう工程とを備えていることを特徴とする。

## 【発明の効果】

40

## 【0057】

本発明に係る半導体記憶装置及びその製造方法によると、ワード線形成用の導電層を堆積した後の工程においても、ワード線の帯電による高電圧の印加からメモリセルを保護することができる。

## 【発明を実施するための最良の形態】

## 【0058】

(第1の実施形態)

50

本発明の第1の実施形態について図面を参照しながら説明する。第1の実施形態においては、ゲート絶縁膜に電荷蓄積層を有する不揮発性半導体記憶装置を一例として取り上げる。

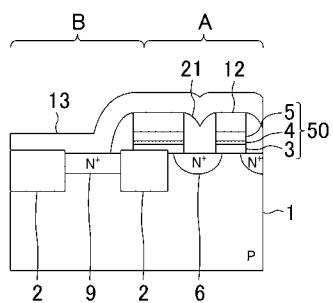

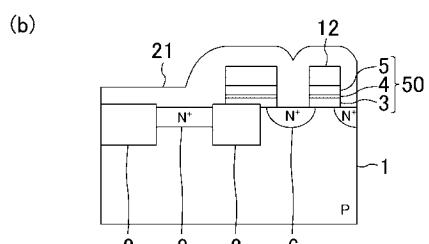

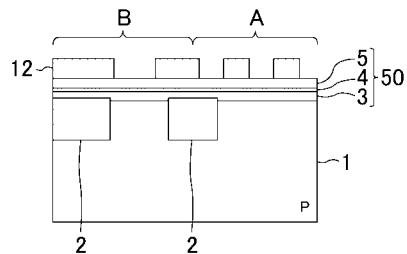

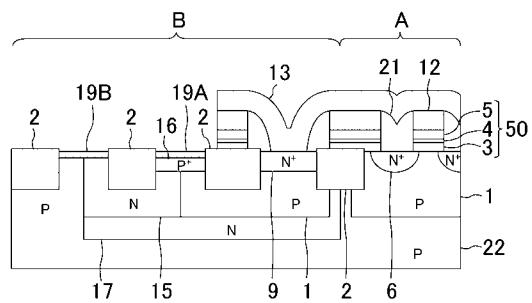

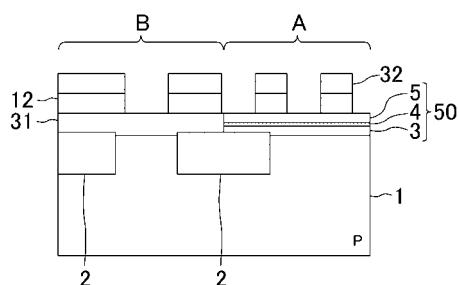

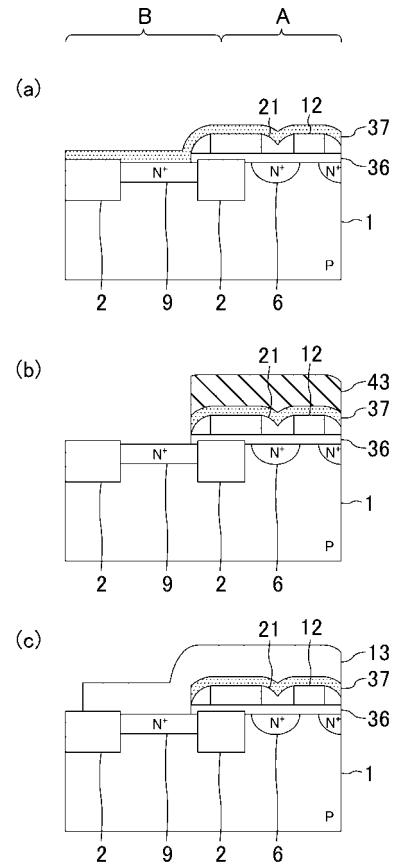

#### 【0059】

図1は本発明の第1の実施形態に係る半導体記憶装置の断面構成を示している。図1に示すように、例えばシリコンからなるP型ウェル(又はP型半導体基板)1の上部には、素子分離絶縁膜2により区画されたメモリセルアレイ領域Aと保護ダイオード領域Bとが形成されている。

#### 【0060】

メモリセルアレイ領域Aには、例えば酸化シリコンからなる第1ゲート絶縁膜3、窒化シリコンからなる電荷蓄積層4及び酸化シリコンからなる第2ゲート絶縁膜5が順次形成されてなる、いわゆるONO膜50と、該ONO膜50の上に形成された多結晶シリコン等からなり、ゲート電極を構成する第1導電層12とを有するMONOS(metal oxide-nitride-oxide-semiconductor)型メモリセルが行列状に配置されている。

10

#### 【0061】

P型ウェル1の上部における列方向(紙面に垂直な方向)に延びるONO膜50同士の間の領域にはソースドレイン拡散層6が形成され、該ソースドレイン拡散層6と第2導電層13との間には絶縁膜21が形成されている。

#### 【0062】

メモリセルアレイ領域Aに隣接する保護ダイオード領域Bには、P型ウェル1の上部に形成されたN型拡散層9が形成されて、該N型拡散層9とP型ウェル1とから保護ダイオード素子が形成されている。

20

#### 【0063】

メモリセルアレイ領域Aには、メモリセルアレイの行方向に並ぶ複数のメモリセルのゲート電極を共通に接続する例えば多結晶シリコンからなり、ワード線及びゲート電極を構成する第2導電層13が形成されている。第2導電層13は保護ダイオード領域Bにまで延伸して、保護ダイオード領域BにおけるN型拡散層9と直接に接続されている。

#### 【0064】

第1の実施形態によると、第2導電層13が保護ダイオード領域BにおけるP型ウェル1内のN型拡散層9と直接に接続された後は、製造工程で発生する第2導電層13の負の帯電は、PN接合の順方向電圧となる電流バスを持つため、第2導電層13は絶対値が大きい負の電位とならない。また、製造工程で発生するゲート電極の正の帯電に対しても、PN接合の逆方向電圧以上の電位となることはなく、逆方向電圧(耐圧)を10V程度に制御することにより、高電圧の印加によるONO膜50へのストレス又は該ONO膜50の電荷蓄積層4への電荷の注入を防止又は抑制することができる。

30

#### 【0065】

なお、上記の説明は、ゲート電極が第1導電層12と第2導電層13との積層膜により構成され、ワード線が第2導電層13により構成された場合の例である。図2に示すように、ゲート電極及びワード線を第1導電層12のみで形成した場合においても、上記と同様の効果を得ることができる。このことは、第1の実施形態のみならず、以下の各実施形態においても同様にいえる。

40

#### 【0066】

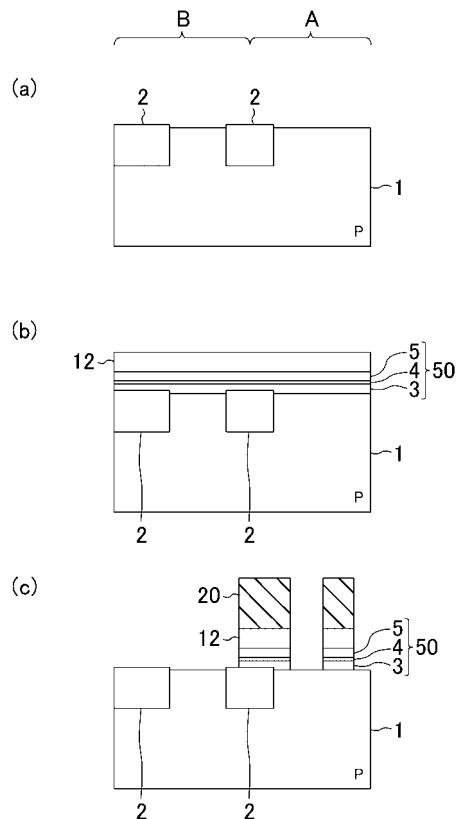

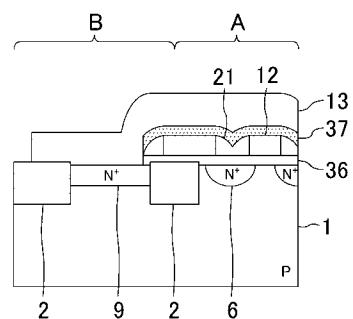

以下、前記のように構成された第1の実施形態に係る半導体記憶装置の製造方法について図面を参照しながら説明する。

#### 【0067】

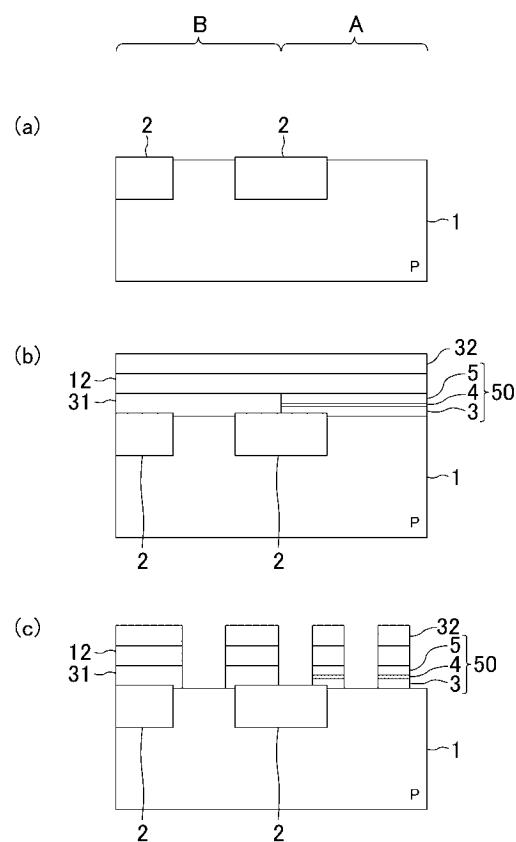

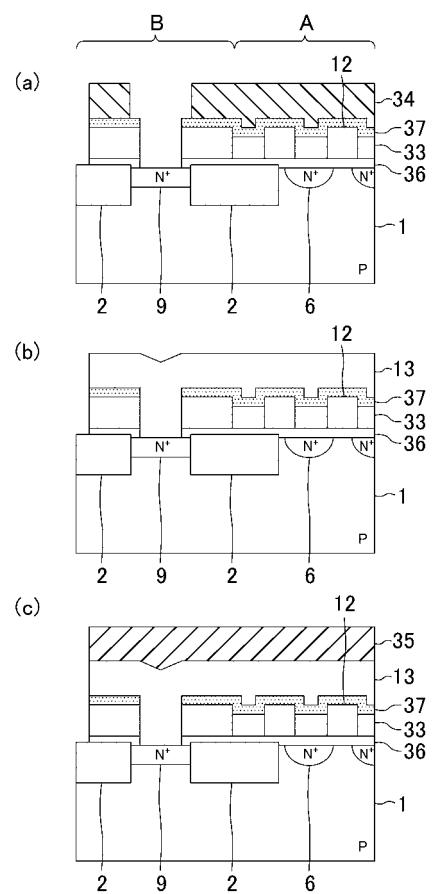

まず、図3(a)に示すように、P型ウェル1の上部にシャロウトレーンチ分離(Shallow Trench Isolation: STI)構造を持つ素子分離絶縁膜2を選択的に形成する。

#### 【0068】

次に、図3(b)に示すように、例えば化学気相堆積(Chemical Vapor Deposition: CVD)法により、P型ウェル(又はP型半導体基板)1の上に素子分離絶縁膜2を含む

50

全面にわたって、第1ゲート絶縁膜3、電荷蓄積層4、第2ゲート絶縁膜5及び多結晶シリコンからなる第1導電層12を順次形成する。

【0069】

次に、図3(c)に示すように、リソグラフィ法によるレジストパターン20を用いてドライエッチングにより、メモリセルアレイ領域Aにおける第1導電層12、第2ゲート絶縁膜5、電荷蓄積層4、第1ゲート絶縁膜3を列方向に且つ短冊状にパターニングする。このとき、保護ダイオード領域Bにおいては、P型ウェル1の上面の少なくとも一部が露出する。

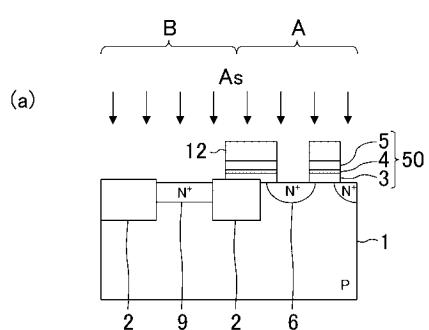

【0070】

次に、図4(a)に示すように、第1導電層12をマスクとして砒素(As)イオン等からなるN型不純物イオンをP型ウェル1に注入することにより、メモリセルアレイ領域Aにはソースドレイン拡散層6を形成し、保護ダイオード領域Bには保護ダイオード素子を構成するN型拡散層9を形成する。

10

【0071】

次に、図4(b)に示すように、例えば低圧CVD(low pressure CVD)法により、短冊状にパターニングされた第1導電層12を覆うように、P型ウェル1の上に酸化シリコンからなる絶縁膜21を形成する。

【0072】

次に、図4(c)に示すように、形成された絶縁膜21に対してドライエッチングによるエッチバックを行なって、メモリセルアレイ領域Aにおいては、絶縁膜21から第1導電層12を露出すると共に、保護ダイオード領域Bからは、N型拡散層9を露出する。

20

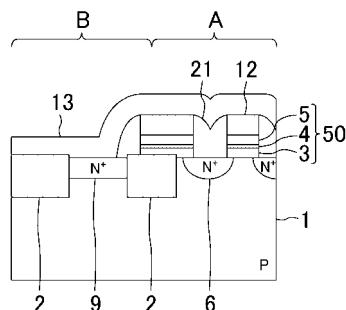

【0073】

次に、図5に示すように、CVD法により、露出された第1導電層12及びN型拡散層9を含めP型ウェル1の上すなわちウェハ上の全面に多結晶シリコンからなる第2導電層13を形成する。続いて、リソグラフィ法により、第2導電層13の上に行方向(紙面に平行な方向)に延伸する複数の開口パターンを有するレジストパターン(図示せず)を形成し、形成したレジストパターンをマスクとして、行方向に並ぶ複数の第1導電層12同士が電気的に接続されるように、第2導電層13及び第1導電層12をドライエッチングしてワード線を形成する。このとき、ワード線の端部においては、第2導電層13が保護ダイオード領域Bから露出したN型拡散層9に直接に接続された状態が維持されるよう、第2導電層13、第1導電層12、ONO膜50及び絶縁膜21をパターニングする。

30

【0074】

なお、その後の製造工程については、図示は省略するが、ワード線の上方を含む半導体基板の全体にわたって上層の絶縁膜を形成し、その後、上層の絶縁膜の所定の位置に必要なコンタクトホールを形成する。続いて、コンタクトホールの内部を含む上層の絶縁膜上に配線層を形成する。

【0075】

ここで、製造方法の第1変形例として、図3(b)に示したように、保護ダイオード領域Bに、第1ゲート絶縁膜3、電荷蓄積層4及び第2ゲート絶縁膜5からなるONO膜50を形成する代わりに、図6に示すように、少なくともP型ウェル1の全面に、一旦ONO膜50を形成した後、形成したONO膜50における保護ダイオード領域Bに含まれる部分を選択的に除去する。続いて、保護ダイオード領域Bの上に酸化シリコンからなる第3ゲート絶縁膜31を形成し、その後、第1導電層12及び第3ゲート絶縁膜31を形成してもよい。その際、保護ダイオード領域B上における第3ゲート絶縁膜31の除去は、図3(c)に示すドライエッチング又は図4(b)に示す絶縁膜21のドライエッチング時に同時にに行なえばよい。このようにすると、図3(c)に示すONO膜50をエッチングする際に、エッチング不足で窒化シリコンからなる電荷蓄積層4が残ってしまい、さらには、その後の図4(b)における絶縁膜21に対するエッチバックを行なう際にも、エッチングレートの違いから窒化シリコンからなる電荷蓄積層4がエッチングされずに残ってしまい、保護ダイオード領域BにおけるN型拡散層9を露出できなくなるという事態を

40

50

回避することができる。

【0076】

また、製造方法の第2変形例として、図3(c)において、図7に示すように第1導電層12のみをドライエッティングにより除去し、ONO膜50は残したままでもよい。この場合には、図4(c)において、保護ダイオード領域Bにおける絶縁膜21をドライエッティングによりエッチバックする際に、保護ダイオード領域B上の第1ゲート絶縁膜3、電荷蓄積層4及び第2ゲート絶縁膜5からなるONO膜50を除去することにより、保護ダイオード領域BにおけるN型拡散層9を露出することができる。

【0077】

以上のような製造方法とすることにより、メモリセルアレイ領域Aにおける第1導電層12の上面を露出すると同時に、拡散ビット線となるソースドレイン拡散層6の上に絶縁膜21を埋め込むことができる。さらに、保護ダイオード領域Bにおいては、第2導電型拡散層9の上の絶縁膜21が除去されて、該第2導電型拡散層9を露出することができる。また、ワード線を構成する第2導電層13を堆積することにより、ワード線と保護ダイオード領域Bの第2導電型拡散層9とが自己整合的に且つ直接に接続されると共に、ワード線は第1導電層12に対しても直接に接続される。

10

【0078】

従って、図4(a)～図4(c)に示すメモリセル形成工程において、保護ダイオード領域Bにおける第2導電型拡散層9の形成及び該第2導電型拡散層9上の絶縁膜21の除去を同時に行なえるため、保護ダイオード素子を形成するための新たな工程が不要となる。

20

【0079】

以上説明したように、第1の実施形態によると、ワード線を構成する第2導電層13の端部は、保護ダイオード領域Bと直接に接続されているため、ワード線形成用の第2導電層13を堆積した後の製造工程において保護ダイオード素子が機能し、その後のゲート電極及びワード線の帯電による電荷蓄積層4への電荷の注入及びONO膜50へのストレスを防止することができる。

【0080】

(第2の実施形態)

以下、本発明の第2の実施形態について図面を参照しながら説明する。

30

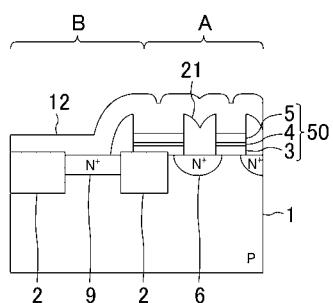

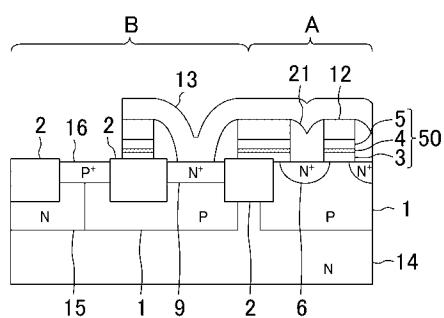

【0081】

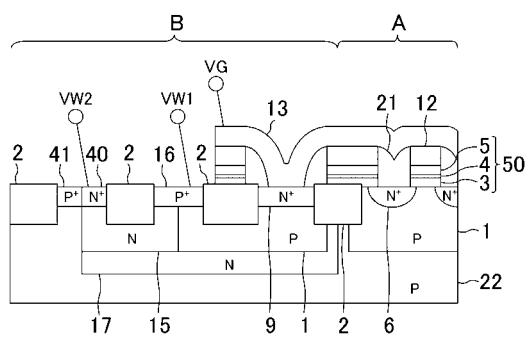

図8は本発明の第2の実施形態に係る半導体記憶装置の断面構成を示している。第2の実施形態に係る半導体記憶装置は、第1の実施形態に係る半導体記憶装置におけるデバイス仕様及び保護ダイオード素子の構造を変更している。図8において、図1に示す構成部材と同一の構成部材には同一の符号を付すことにより説明を省略する。

【0082】

図8に示すように、P型ウェル1は、例えばN型シリコンからなるN型半導体基板14におけるメモリセルアレイ領域A及び保護ダイオード領域Bに分かれて形成されている。

【0083】

N型半導体基板14の保護ダイオード領域Bには、P型ウェル1のメモリセルアレイ領域Aに対して反対側の領域にN型ウェル15がP型ウェル1と接して形成されている。さらに、保護ダイオード領域BにおけるP型ウェル1とN型ウェル15との接合部の上部には、P型拡散層16が形成されている。

40

【0084】

従って、保護ダイオード領域Bには、N型半導体基板14に形成され、P型ウェル1の上部に形成されたN型拡散層9と、互いに隣接するP型ウェル1及びN型ウェル15と、該P型ウェル1及びN型ウェル15の接合部に跨がるように形成されたP型拡散層16とによって保護ダイオード素子が構成される。

【0085】

メモリセルアレイ領域Aにおいてワード線を構成する第2導電層13は、保護ダイオー

50

ド領域Bにまで延伸し、保護ダイオード領域BにおけるP型ウェル1の上部に形成されたN型拡散層9と直接に接続されている。

【0086】

第2の実施形態によると、ワード線となる第2導電層13が保護ダイオード領域BにおけるP型ウェル1の上部に形成されたN型拡散層9と接続された後は、製造工程で発生するワード線（ゲート電極）に対する負の帯電は、保護ダイオード領域BにおけるP型ウェル1及びN型ウェル15の上部で且つ接合部を跨ぐように形成されたP型拡散層16とN型ウェル15との接合部分においてPN接合の逆方向電圧を生じさせる。従って、逆方向電圧（耐圧）を10V程度に制御することにより、第2導電層13は逆方向電圧よりも絶対値が大きい負の電位とはならない。

10

【0087】

また、製造工程で発生するワード線（ゲート電極）に対する正の帯電においても、保護ダイオード領域BにおけるP型ウェル1と該P型ウェル1の上部に形成されたN型拡散層9との接合部分でPN接合の逆方向電圧を生じさせる。このため、逆方向電圧（耐圧）を10V程度に制御することにより、ワード線は逆方向電圧以上の正の高い電位とはならない。その結果、高電圧の印加によるONO膜50へのストレス又は該ONO膜50の電荷蓄積層4への電荷の注入を抑制することができる。

【0088】

さらに、第1の実施形態においては、デバイスの動作時にワード線に負の電圧を印加した場合に、ワード線の負の電位の絶対値を上げることはできないが、第2の実施形態によると、ワード線に負の電圧を印加した場合においても、ワード線の負の電位の絶対値を上げることが可能であるため、ワード線に負電圧を印加可能なデバイスを実現できる。

20

【0089】

以上説明したように、第2の実施形態によると、ワード線を構成する第2導電層13の端部は、保護ダイオード領域Bと直接に接続されているため、ワード線形成用の第2導電層13を堆積した後の製造工程において保護ダイオード素子が機能し、その後のゲート電極及びワード線の帯電による電荷蓄積層4への電荷の注入及びONON膜50へのストレスを防止することができる。

【0090】

また、ワード線に負電圧を印加する場合においても、保護ダイオード素子が機能するため、ワード線に負電圧を印加するデバイス動作が可能となる。

30

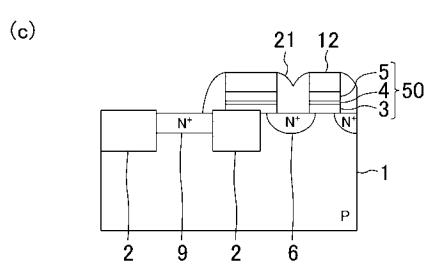

【0091】

（第3の実施形態）

以下、本発明の第3の実施形態について図面を参照しながら説明する。

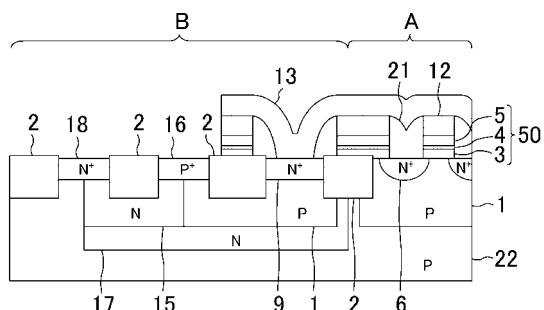

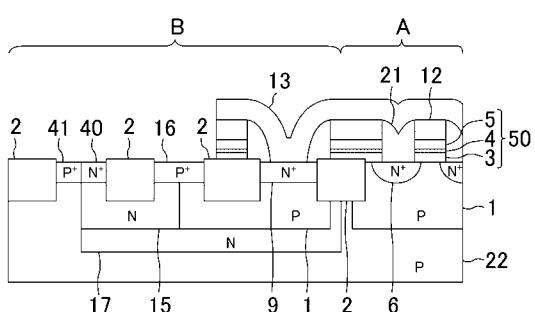

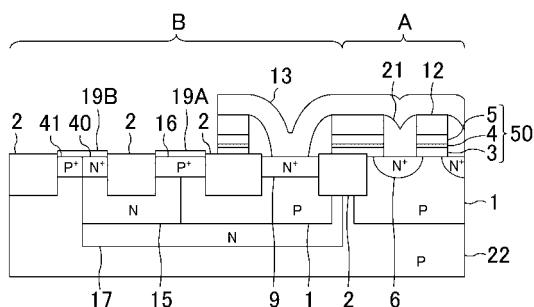

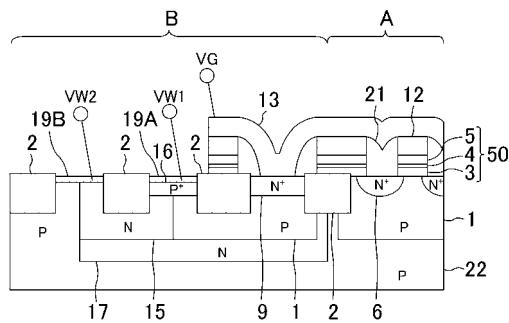

【0092】

図9は本発明の第3の実施形態に係る半導体記憶装置の断面構成を示している。第3の実施形態に係る半導体記憶装置は、第2の実施形態に係る半導体記憶装置の第1変形例である。図9において、図8に示す構成部材と同一の構成部材には同一の符号を付すことにより説明を省略する。

【0093】

図9に示すように、保護ダイオード領域Bにおいて互いに隣接するP型ウェル1及びN型ウェル15は、例えばP型シリコンからなるP型半導体基板22に形成された深いN型ウェル17の上部に形成されている。また、保護ダイオード領域Bにおいて、N型ウェル15とP型半導体基板22との上部で且つ接合部を跨ぐようにN型拡散層18が形成されている。

40

【0094】

従って、保護ダイオード領域Bには、P型半導体基板22におけるP型ウェル1の上部に形成されたN型拡散層9と、互いに隣接するP型ウェル1及びN型ウェル15と、該P型ウェル1及びN型ウェル15に跨がるように形成されたP型拡散層16と、深いN型ウェル17と、N型ウェル15及びP型半導体基板22の接合部に跨がるように形成された

50

N型拡散層18とによって保護ダイオード素子が構成される。

【0095】

第3の実施形態においては、ワード線となる第2導電層13が保護ダイオード領域BにおけるP型ウェル1の上部に形成されたN型拡散層9と接続された後は、製造工程で発生するワード線(ゲート電極)に対する負の帯電は、保護ダイオード領域BにおけるP型ウェル1及びN型ウェル15の上部で且つ接合部を跨ぐように形成されたP型拡散層16とN型ウェル15との接合部分においてPN接合の逆方向電圧を生じさせる。従って、逆方向電圧(耐圧)を10V程度に制御することにより、第2導電層13は逆方向電圧よりも絶対値が大きい負の電位とはならない。

【0096】

また、製造工程で発生するワード線(ゲート電極)に対する正の帯電は、保護ダイオード領域BにおけるP型ウェル1と該P型ウェル1の上部に形成されたN型拡散層9との接合部分と、保護ダイオード領域BにおけるN型ウェル15とP型半導体基板22との接合部に跨ぐように形成されたN型拡散層18とP型半導体基板22との接合部分の2箇所においてPN接合の逆方向電圧を生じさせる。このため、逆方向電圧(耐圧)を10V程度に制御することにより、ワード線は逆方向電圧以上の正の高い電位とはならない。その結果、高電圧の印加によるONO膜50へのストレス又は該ONO膜50の電荷蓄積層4への電荷の注入を抑制することができる。

【0097】

他の変形例として、図10に示すように、保護ダイオード領域Bにおいて、P型ウェル1とN型ウェル15とに跨がるように形成されたP型拡散層16の上部と、N型ウェル15とP型半導体基板22とに跨がるように形成されたN型拡散層18の上部とに、チタン(Ti)、コバルト(Co)又はニッケル(Ni)等の金属とシリコンとの金属化合物からなる第1のシリサイド領域19A及び第2のシリサイド領域19Bをそれぞれ形成してもよい。このようにすると、P型拡散層16及びN型拡散層18を低抵抗化できるため、製造工程においてワード線(ゲート電極)が正又は負に帯電して、ワード線に保護ダイオード素子の逆方向電圧以上の絶対値を持つ電圧が印加された場合に、印加された電圧により発生した電流は、P型半導体基板22に容易に流れようになる。このため、ONO膜50へのストレス又は該ONO膜50の電荷蓄積層4への電荷の注入をより確実に抑制することが可能となる。

【0098】

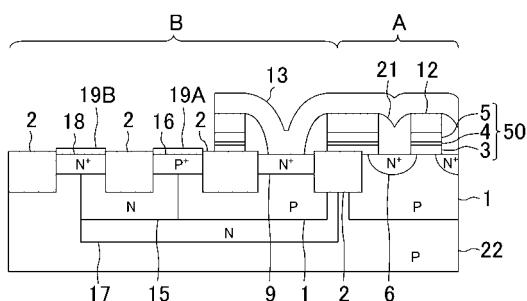

(第4の実施形態)

以下、本発明の第4の実施形態について図面を参照しながら説明する。

【0099】

図11は本発明の第4の実施形態に係る半導体記憶装置の断面構成を示している。第4の実施形態に係る半導体記憶装置は、第2の実施形態に係る半導体記憶装置の第2変形例である。図11において、図8に示す構成部材と同一の構成部材には同一の符号を付すことにより説明を省略する。

【0100】

図11に示すように、保護ダイオード領域Bにおいて互いに隣接するP型ウェル1及びN型ウェル15は、P型シリコンからなるP型半導体基板22に形成された深いN型ウェル17の上部に形成されている。また、保護ダイオード領域Bにおいて、P型拡散層16の上部と、N型ウェル15とP型半導体基板22との接合部分の上部とには、それぞれTiシリサイド等からなる第1のシリサイド領域19A及び第2のシリサイド領域19Bが形成されている。

【0101】

従って、保護ダイオード領域Bには、P型半導体基板22におけるP型ウェル1の上部に形成されたN型拡散層9と、互いに隣接するP型ウェル1及びN型ウェル15と、該P型ウェル1及びN型ウェル15に跨がるように形成されたP型拡散層16及び第1のシリサイド領域19Aと、深いN型ウェル17と、N型ウェル15及びP型半導体基板22の

10

20

30

40

50

接合部に跨るように形成された第2のシリサイド領域19Bとによって保護ダイオード素子が構成される。

【0102】

第4の実施形態においては、ワード線となる第2導電層13が保護ダイオード領域BにおけるP型ウェル1の上部に形成されたN型拡散層9と接続された後は、製造工程で発生するワード線(ゲート電極)に対する負の帯電は、保護ダイオード領域BにおけるP型ウェル1及びN型ウェル15の上部で且つ接合部を跨ぐように形成されたP型拡散層16とN型ウェル15との接合部分においてPN接合の逆方向電圧を生じさせる。従って、逆方向電圧(耐圧)を10V程度に制御することにより、第2導電層13は逆方向電圧よりも絶対値が大きいの負の電位とはならない。

10

【0103】

また、製造工程で発生するワード線(ゲート電極)に対する正の帯電は、保護ダイオード領域BにおけるP型ウェル1と該P型ウェル1の上部に形成されたN型拡散層9との接合部分においてPN接合の逆方向電圧を生じさせる。このため、逆方向電圧(耐圧)を10V程度に制御することにより、ワード線は逆方向電圧以上の正の高い電位とはならない。その結果、高電圧の印加によるONO膜50へのストレス又は該ONO膜50の電荷蓄積層4への電荷の注入を抑制することができる。

【0104】

さらに、ワード線に正の高電圧が印加された場合に、第4の実施形態は第3の実施形態と比べて、高電圧による電流がP型半導体基板22に流れるまでに逆方向電圧となる箇所が1箇所のみであるため、耐圧の制御が容易で且つデバイス動作が安定するという効果を有する。

20

【0105】

(第5の実施形態)

以下、本発明の第5の実施形態について図面を参照しながら説明する。

【0106】

図12は本発明の第5の実施形態に係る半導体記憶装置の断面構成を示している。第5の実施形態に係る半導体記憶装置は、第3の実施形態に係る半導体記憶装置の第1変形例である。図12において、図9に示す構成部材と同一の構成部材には同一の符号を付すことにより説明を省略する。

30

【0107】

図12に示すように、保護ダイオード領域Bにおいて、N型ウェル15におけるP型拡散層16の反対側の上端部にはN型拡散層40が形成され、さらに、P型半導体基板22におけるN型拡散層40に対してP型拡散層16の反対側の上端部には、P型拡散層41が形成されている。ここで、N型拡散層40とP型拡散層41との接合部分は、N型ウェル15とP型半導体基板22との接合部分とほぼ一致している。

【0108】

従って、保護ダイオード領域Bには、P型半導体基板22におけるP型ウェル1の上部に形成されたN型拡散層9と、互いに隣接するP型ウェル1及びN型ウェル15と、該P型ウェル1及びN型ウェル15に跨るように形成されたP型拡散層16と、深いN型ウェル17と、N型ウェル15におけるP型拡散層16と反対側の上端部に形成されたN型拡散層40と、P型半導体基板22におけるN型拡散層40に対してP型拡散層16と反対側の上端部に形成されたP型拡散層41とによって保護ダイオード素子が構成される。

40

【0109】

第5の実施形態においては、ワード線となる第2導電層13が保護ダイオード領域BにおけるP型ウェル1の上部に形成されたN型拡散層9と接続された後は、製造工程で発生するワード線(ゲート電極)に対する負の帯電は、保護ダイオード領域BにおけるP型ウェル1及びN型ウェル15の上部で且つ接合部を跨ぐように形成されたP型拡散層16とN型ウェル15との接合部分においてPN接合の逆方向電圧を生じさせる。従って、逆方向電圧(耐圧)を10V程度に制御することにより、第2導電層13は逆方向電圧よりも

50

絶対値が大きいの負の電位とはならない。

【0110】

また、製造工程で発生するワード線（ゲート電極）に対する正の帯電は、保護ダイオード領域BにおけるP型ウェル1と該P型ウェル1の上部に形成されたN型拡散層9との接合部分と、保護ダイオード領域BにおけるN型ウェル15の上部に形成されたN型拡散層40とP型半導体基板22の上部に形成されたP型拡散層41との接合部分との2箇所においてPN接合の逆方向電圧を生じさせる。このため、逆方向電圧（耐圧）を10V程度に制御することにより、ワード線は逆方向電圧以上の正の高い電位とはならない。その結果、高電圧の印加によるONO膜50へのストレス又は該ONO膜50の電荷蓄積層4への電荷の注入を抑制することができる。

10

【0111】

ところで、図9に示した第3の実施形態に係る半導体記憶装置の場合、N型拡散層18とP型半導体基板22とのPN接合部は、N型拡散層18を形成した後に高温熱処理が施され、N型拡散層18からN型不純物が拡散する場合に、N型拡散層18とP型半導体基板22とのPN接合付近におけるP型不純物濃度が低くなるため、耐圧を10V程度に低く制御することが困難となるおそれがある。このとき、製造工程においてワード線が正に帯電して、P型ウェル1と該P型ウェル1内のN型拡散層9とのPN接合が10V程度でクランプしたとする。しかしながら、N型拡散層18とP型半導体基板22とのPN接合は耐圧が高いためにクランプせず、P型ウェル1が充電される結果、ワード線の電位は10V以上にまで上昇してしまう場合がある。

20

【0112】

第5の実施形態においては、P型半導体基板22に形成され、N型拡散層40と接合部を有するP型拡散層41の不純物濃度をP型ウェル1よりも高くすることができるため、上記の問題を回避することができる。

【0113】

具体的には、P型拡散層41の不純物濃度をP型ウェル1よりも高くすると、N型拡散層40とP型拡散層41とのPN接合の耐圧を第3の実施形態に係るN型拡散層18とP型半導体基板22とのPN接合の耐圧よりも大幅に低く設定することができる。その結果、上記のような問題を生じることがない、実用的な耐圧を持つ保護ダイオード素子を得ることができる。また、N型拡散層40とP型拡散層41とのPN接合の耐圧を大幅に低く設定することができるため、ワード線が正に帯電した場合の逆方向電圧（耐圧）をP型ウェル1と該P型ウェル1に形成されたN型拡散層9とのPN接合の耐圧のみで制御することが可能となる。

30

【0114】

また、一変形例として、図13に示すように、保護ダイオード領域Bにおいて、P型ウェル1とN型ウェル15とに跨るように形成されたP型拡散層16の上部と、互いに隣接するN型拡散層40及びP型拡散層41の上部とに、第4の実施形態と同様に第1のシリサイド領域19A及び第2のシリサイド領域19Bをそれぞれ形成してもよい。このようにすると、ワード線が正に帯電した場合の逆方向電圧（耐圧）を、P型ウェル1と該P型ウェル1内のN型拡散層9とのPN接合の耐圧のみで制御することが、より容易となり且つデバイス動作が安定する。

40

【0115】

（第6の実施形態）

以下、本発明の第6の実施形態について図面を参照しながら説明する。

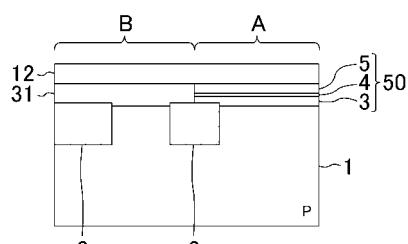

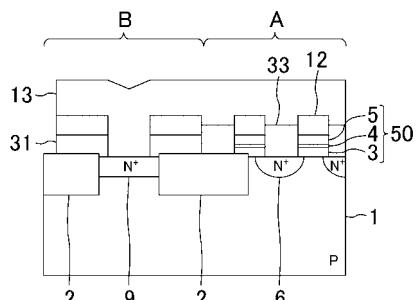

【0116】

図14は本発明の第6の実施形態に係る半導体記憶装置の断面構成を示している。図14において、図1に示す構成部材と同一の構成部材には同一の符号を付すことにより説明を省略する。第6の実施形態に係る半導体記憶装置は、第1～第5の実施形態に係る半導体記憶装置と比べて微細化を可能にする構造を有している。

【0117】

50

ところで、図4(c)に示したように、第1の実施形態に係る半導体記憶装置の製造方法においては、P型ウェル1を覆う絶縁膜21をドライエッチングによりエッチバックすることにより、メモリセルアレイ領域Aにおける第1導電膜12を露出すると共に、保護ダイオード領域BにおけるN型拡散層9を露出している。このとき、メモリセルアレイ領域Aにおいては、互いに隣接するメモリセルを構成する第1導電層12同士の間は絶縁膜21で埋め込まれている必要がある。仮に、第1導電層12同士の間の領域に絶縁膜21が埋め込まれていないとすると、第2導電層13がソースドレイン拡散層6と電気的に接続するおそれがあるため、メモリセルを正常に動作させることができない。通常、図4(c)を含む製造方法の場合は、絶縁膜21は低圧CVD法で形成されるが、微細化が進むとメモリセル同士の間隔が小さくなるため、低圧CVD法では第1導電層12の間の領域を完全に埋め込むことができなくおそれがある。

#### 【0118】

また、図4(c)に示す工程において、保護ダイオード領域BにおけるN型拡散層9の表面に絶縁膜21が残った状態となると、第2導電層13がN型拡散層9と接続されない状態となるため、保護ダイオード素子が機能しなくなるおそれがある。微細化が進むと、保護ダイオード領域Bのサイズの縮小が求められる。このため、低圧CVD法で絶縁膜21を堆積した後に、エッチングにより絶縁膜21をエッチバックすると、ONO膜50及び第1導電層12の側面上に形成される絶縁膜21からなるサイドウォールがN型拡散層9を覆ってしまい、前述したような第2導電層13とN型拡散層9が接続できない状態となるおそれがある。

#### 【0119】

そこで、第6の実施形態においては、本発明の特徴を有し且つ微細化が可能な半導体記憶装置及びその製造方法を説明する。

#### 【0120】

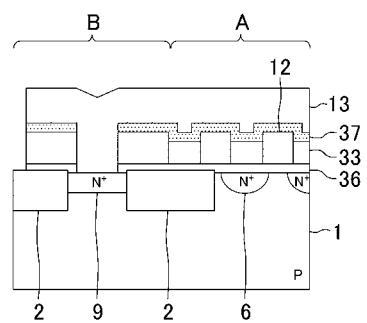

図14に示すように、P型ウェル1の上部における列方向に延びるONO膜50同士の間の領域にはソースドレイン拡散層6が形成され、該ソースドレイン拡散層6と第2導電層13との間には、上面が平坦化されたソースドレイン拡散層上絶縁膜33(以下、絶縁膜33と略称する。)が形成されている。第6の実施形態の特徴として、該絶縁膜33は、メモリセルアレイ領域Aにのみに形成され、保護ダイオード領域Bには形成されない。

#### 【0121】

メモリセルアレイ領域Aに隣接する保護ダイオード領域Bには、第1の実施形態と同様に、P型ウェル1の上部に形成されたN型拡散層9が形成されて、該N型拡散層9とP型ウェル1とから保護ダイオード素子が形成されている。また、N型拡散層9の側端部上には、第1ゲート絶縁膜3、電荷蓄積層4及び第2ゲート絶縁膜からなるONO膜50に代えて、酸化シリコンからなる第3ゲート絶縁膜31が形成されている。

#### 【0122】

メモリセルアレイ領域Aには、メモリセルアレイの行方向に並ぶ複数のメモリセルのゲート電極を共通に接続する例えば多結晶シリコンからなり、ワード線及びゲート電極を構成する第2導電層13が形成されている。第2導電層13は保護ダイオード領域Bにまで延伸して、保護ダイオード領域BにおけるN型拡散層9と直接に接続されている。

#### 【0123】

第6の実施形態によると、第1の実施形態と同様に、製造工程においてONO膜50へのストレス又は該ONO膜50の電荷蓄積層4への電荷の注入を抑制することができる。その上、保護ダイオード領域BにおけるN型拡散層9の上には、サイドウォール状の絶縁膜が形成されないことから、保護ダイオード領域Bのサイズを縮小することができるため、半導体記憶装置の微細化が可能となる。

#### 【0124】

以下、前記のように構成された半導体記憶装置の製造方法について図面を参照しながら説明する。

#### 【0125】

10

20

30

40

50

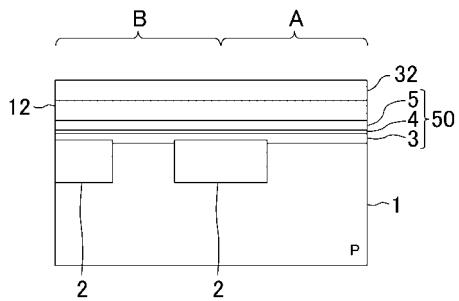

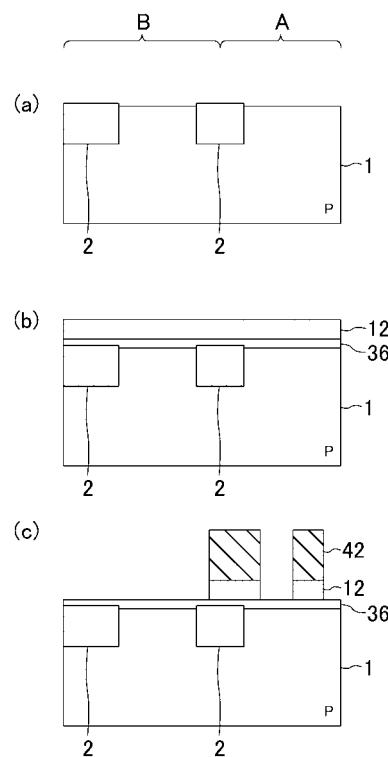

まず、図15(a)に示すように、P型ウェル(又はP型半導体基板)1の上部にSTI構造を持つ素子分離絶縁膜2を選択的に形成する。

【0126】

次に、図15(b)に示すように、例えばCVD法により、P型ウェル1の上に素子分離絶縁膜2を含む全面にわたって、第1ゲート絶縁膜3、電荷蓄積層4及び第2ゲート絶縁膜5を順次形成してONO膜50を形成する。その後、形成されたONO膜50における保護ダイオード領域Bに含まれる部分を選択的に除去する。続いて、保護ダイオード領域Bに露出したP型ウェル1及び素子分離絶縁膜2の上に第3ゲート絶縁膜31を選択的に形成する。続いて、メモリセルアレイ領域A及び保護ダイオード領域Bの上に全面にわたって多結晶シリコンからなる第1導電層12及び窒化シリコンからなるゲート電極加工用絶縁膜32を順次形成する。

【0127】

次に、図15(c)に示すように、リソグラフィ法及びエッチング法により、メモリセルアレイ領域Aにおいては、ゲート電極加工用絶縁膜32を列方向に且つ短冊状にパターニングすると共に、保護ダイオード領域Bにおいては、ゲート電極加工用絶縁膜32におけるP型ウェル1の上側部分を除去する。その後、パターニングされたゲート電極加工用絶縁膜32をマスクとして、第1導電層12及びその下側の第1ゲート絶縁膜3、電荷蓄積層4、第2ゲート絶縁膜5からなるONO膜50、及び第3ゲート絶縁膜31をドライエッチングによりパターニングする。

【0128】

次に、図16(a)に示すように、ゲート電極加工用絶縁膜32をマスクとして砒素(As)等のN型不純物をP型ウェル1に注入して、メモリセルアレイ領域AにはN型のソースドレイン領域6を形成し、保護ダイオード領域Bには保護ダイオード素子を構成するN型拡散層9を形成する。

【0129】

次に、図16(b)に示すように、例えば高密度プラズマCVD(High Density Plasma CVD)法により、酸化シリコンからなる絶縁膜33を、P型ウェル1の全面にゲート電極加工用絶縁膜32を覆うように形成する。

【0130】

次に、図16(c)に示すように、化学機械研磨(Chemical Mechanical Polish: CMP)法により、絶縁膜33をゲート電極加工用絶縁膜32が露出するまで研磨し、その後、ゲート電極加工用絶縁膜32を熱リン酸等を用いたウェットエッチングによって除去する。

【0131】

次に、図16(d)に示すように、リソグラフィ法により、保護ダイオード領域BにおけるN型拡散層9の上側部分に開口部を持つ第1のレジストパターン34を形成する。続いて、形成した第1のレジストパターン34をマスクとして、保護ダイオード領域Bにおける絶縁膜33をドライエッチングすることにより、保護ダイオード領域BからN型拡散層9を露出する。

【0132】

次に、図17(a)に示すように、第1のレジストパターン34を除去した後、CVD法により、露出された第1導電層12及びN型拡散層9を含めP型ウェル1の上すなわちウェハ上の全面に、多結晶シリコンからなる第2導電層13を堆積する。これにより、保護ダイオード領域Bにおいて、第2導電層13がN型拡散層9と直接に接続される。

【0133】

次に、図17(b)に示すように、第2導電層13の上に行方向に延伸する複数の開口パターンを持つ第2のレジストパターン35を形成する。続いて、形成した第2のレジストパターン35をマスクとして、行方向に並ぶ複数の第1導電層12同士が電気的に接続されるように、第2導電層13及び第1導電層12をドライエッチングしてワード線を形成する。このとき、ワード線の端部においては、第2導電層13が保護ダイオード領域B

から露出したN型拡散層9に直接に接続された状態を維持するように、第2導電層13、第1導電層12、ONO膜50及び絶縁膜33をパターニングする。

【0134】

ここで、第1変形例として、図18に示すように、図15(b)に示す工程において保護ダイオード領域Bに第3ゲート絶縁膜を形成する代わりに、保護ダイオード領域BからONO膜50を除去せずに、該ONO膜50を残したまま、第1導電層12及びゲート電極加工用絶縁膜32を形成してもよい。第1変形例の場合には、保護ダイオード領域Bに残るONO膜50は、図15(c)に示す工程におけるドライエッチング、又は図16(d)に示す工程におけるドライエッチングの際に同時に除去することにより、保護ダイオード領域BにおけるN型拡散層9を露出することが可能となる。

10

【0135】

また、第2変形例として、図19に示すように、図15(c)に示す工程において第1導電層12のみをドライエッチングにより除去し、メモリセル領域AにおいてはONO膜50を残した状態とし、保護ダイオード領域Bにおいては第3ゲート絶縁膜31を残した状態としてもよい。第2の変形例の場合には、図16(d)において、保護ダイオード領域Bにおける絶縁膜33をドライエッチングにより除去する際に、第3ゲート絶縁膜31をも連続して除去することにより、保護ダイオード領域BにおけるN型拡散層9を露出することが可能となる。

【0136】

なお、第6の実施形態においては、図16(b)において、高密度プラズマCVD法を用いることにより、低圧CVD法を用いた場合よりも高アスペクト比となる領域への絶縁膜33の埋め込みをより確実に行なえるようにしている。しかしながら、高密度プラズマCVD法により絶縁膜を形成した場合は、成膜直後の絶縁膜の形状が低圧CVD法の場合のように下地膜の形状を反映した形状とはならない。すなわち、ゲート電極加工用絶縁膜32上に形成される絶縁膜33の膜厚は、メモリセル同士の間及び保護ダイオード領域BにおけるP型ウェル1上に形成される絶縁膜33の膜厚よりも小さくなる。

20

【0137】

従って、第1の実施形態の図4(c)の工程に示したように、保護ダイオード領域Bに形成された絶縁膜33をエッチングにより除去し、且つメモリセルアレイ領域Aにおける第1導電層12をも露出させようとすると、メモリセル同士の間に形成された絶縁膜33も同時に除去されてしまう。

30

【0138】

そこで、第6の実施形態においては、図16(c)に示すように、CMP法を用いて第1導電層12上の絶縁膜33を除去している。その後は、図16(d)に示すように、第2のレジストパターン34を用いたエッチングにより、メモリセルアレイ領域Aにおけるメモリセル同士の間の絶縁膜33を残しながら、保護ダイオード領域Bにおける絶縁膜33を確実に除去することができる。

【0139】

以上説明したように、第6の実施形態に係る半導体記憶装置の製造方法によると、図14に示すように、ワード線を構成する第2導電層13は、保護ダイオード素子を構成するP型拡散層9と直接に接続されているため、ワード線形成用の第2の導電層13を堆積した後の工程において保護ダイオード素子が機能する。このため、第2導電層13を堆積した後は、ONO膜50へのストレスを抑制することができる。さらに、メモリセル同士の間の間隔を縮小することができると共に、保護ダイオード領域Bのサイズをも縮小できる。

40

【0140】

なお、第6の実施形態においても、保護ダイオード領域Bの構成は、第2～第5の各実施形態のいずれかと同様の構成を採ってもよい。これは、以下の第7の実施形態及び第8の実施形態においても同様である。

【0141】

50

## (第7の実施形態)

以下、本発明の第7の実施形態について図面を参照しながら説明する。

## 【0142】

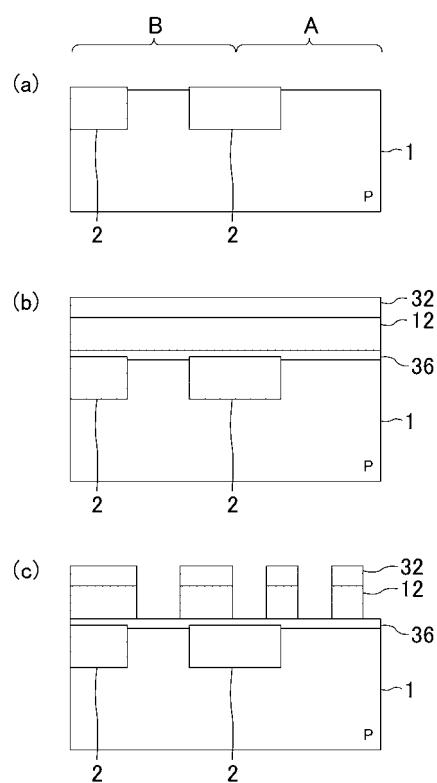

図20は本発明の第7の実施形態に係る浮遊ゲート電極型メモリセルを有する半導体記憶装置の断面構成を示している。図20において、図1に示す構成部材と同一の構成部材には同一の符号を付すことにより説明を省略する。

## 【0143】

前述した第1～第6の各実施形態においては、メモリセルとして、いずれもゲート絶縁膜50を構成する電荷蓄積層4にシリコン窒化膜を用いたMONOS型を説明した。しかしながら、本発明は、MONOS型メモリセルに限定されず、電荷蓄積層に例え多結晶シリコンを用いた浮遊ゲート電極型メモリセルに対しても適用可能である。そこで、第7の実施形態においては、浮遊ゲート電極型メモリセルを用いた半導体記憶装置装置とその製造方法について説明する。

## 【0144】

図20に示すように、メモリセルアレイ領域Aにおいて、浮遊ゲート電極型メモリセルは、P型ウェル1と第1導電層12との間にトンネル絶縁膜としてのトンネル酸化膜36が形成され、また、第1導電層12と第2導電層13との間に結合容量絶縁膜37が形成されている。これにより、第1導電層12は結合容量絶縁膜37を介して第2導電層13と容量結合する結果、第1導電層12は浮遊ゲート電極として機能する。

## 【0145】

また、第1～第6の実施形態と同様に、保護ダイオード領域Bには、P型ウェル1の上部に形成されたN型拡散層9とP型ウェル1とによって保護ダイオード素子が構成されている。ここで、メモリセルアレイ領域Aには、メモリセルアレイの行方向に並ぶ複数のメモリセルのゲート電極を共通に接続する第2導電層13からなるワード線が形成されている。ワード線となる第2導電層13は保護ダイオード領域Bにまで延伸し、保護ダイオード領域BにおけるP型ウェル1の上部に形成されたN型拡散層9と直接に接続されている。

## 【0146】

第7の実施形態によると、第1～第6の実施形態と同様に、製造工程においてゲート絶縁膜(トンネル酸化膜36)へのストレスを抑制することができる。

## 【0147】

以下、前記のように構成された半導体記憶装置の製造方法について図面を参照しながら説明する。

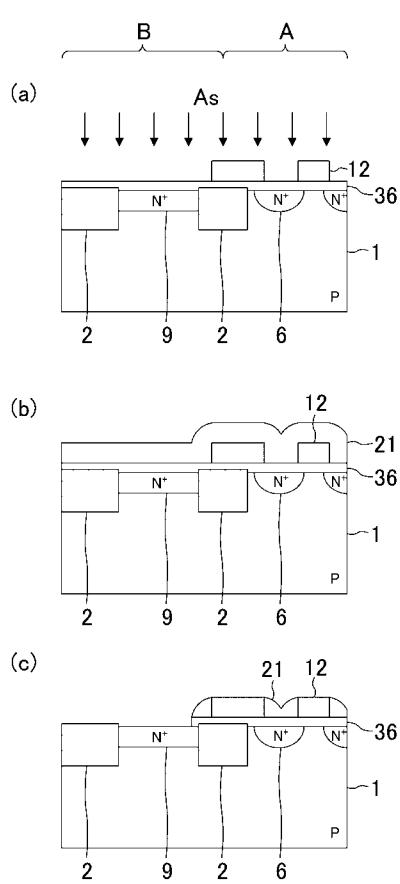

## 【0148】

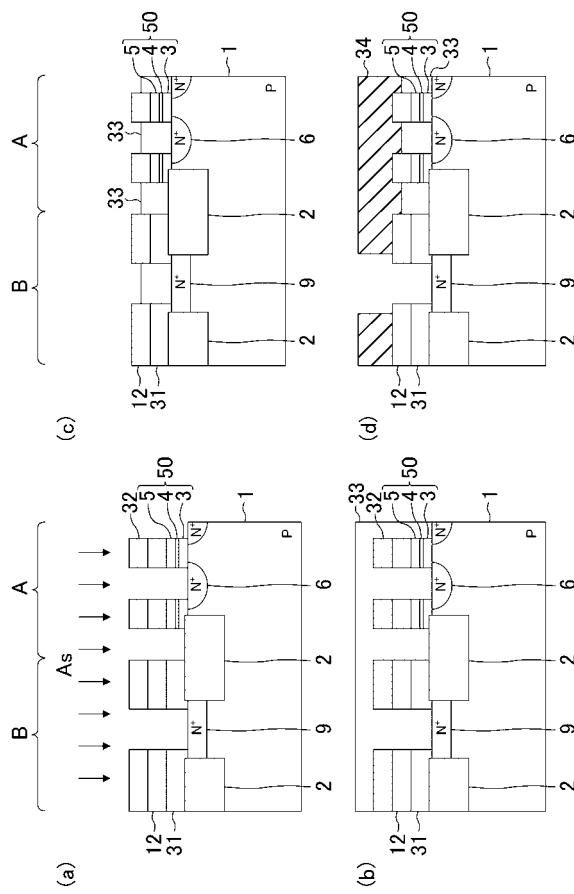

まず、図21(a)に示すように、P型ウェル(又はP型半導体基板)1の上部にSTI構造を持つ素子分離絶縁膜2を選択的に形成する。

## 【0149】

次に、図21(b)に示すように、例えば熱酸化法又はCVD法により、P型ウェル1の上に素子分離絶縁膜2を含む全面にわたって、酸化シリコンからなるトンネル酸化膜36を形成する。続いて、形成したトンネル酸化膜36の上に、CVD法により多結晶シリコンからなる第1導電層12を形成する。

## 【0150】

次に、図21(c)に示すように、リソグラフィ法により形成された第1のレジストパターン42を用いて、ドライエッチングにより、メモリセルアレイ領域Aに形成された第1導電層12に対して列方向に且つ短冊状にパターニングすると共に、保護ダイオード領域Bに形成された第1導電層12の少なくとも一部を除去する。

## 【0151】

次に、図22(a)に示すように、第1のレジストパターン42を除去した後、第1導電層12をマスクとして砒素(As)等のN型不純物をP型ウェル1に注入して、メモリセルアレイ領域AにはN型のソースドレイン領域6を形成し、保護ダイオード領域Bには

10

20

30

40

50

保護ダイオード素子を構成するN型拡散層9を形成する。

【0152】

次に、図22(b)に示すように、例えば低圧CVD法により、短冊状にパターニングされた第1導電層12を覆うように、トンネル酸化膜36の上に酸化シリコンからなる絶縁膜21を形成する。

【0153】

次に、図22(c)に示すように、形成された絶縁膜21に対してドライエッチングによるエッチバックを行なって、メモリセルアレイ領域Aにおいては絶縁膜21から第1導電層12を露出させると共に、保護ダイオード領域BにおいてはN型拡散層9を露出する。

【0154】

次に、図23(a)に示すように、CVD法により、露出された第1導電層12及びN型拡散層9を含めP型ウェル1すなわちウェハの全面にONO膜構造を有する結合容量絶縁膜37を形成する。

【0155】

次に、図23(b)に示すように、リソグラフィ法により、保護ダイオード領域Bの結合容量絶縁膜37を露出する開口パターンを有する第2のレジストパターン43を形成し、形成した第2のレジストパターン43をマスクとして、ドライエッチングにより、保護ダイオード領域Bから結合容量絶縁膜37を除去する。これにより、保護ダイオード領域BのN型拡散層9が露出する。

【0156】

次に、図23(c)に示すように、第2のレジストパターン43を除去した後、CVD法により、結合容量絶縁膜37及び露出されたN型拡散層9を含めP型ウェル1の上すなわちウェハ上の全面に多結晶シリコンからなる第2導電層13を形成する。続いて、リソグラフィ法により、第2導電層13の上に行方向に延伸する複数の開口パターンを有する第3のレジストパターン(図示せず)を形成し、形成した第3のレジストパターンをマスクとして、行方向に並ぶ複数の第1導電層12同士が同一電位となるように、第2導電層13、結合容量絶縁膜37及び第1導電層12をドライエッチングしてワード線を形成する。このとき、ワード線の端部においては、第2導電層13が保護ダイオード領域Bから露出したN型拡散層9に直接に接続された状態を維持するように、第2導電層13、結合容量絶縁膜37、第1導電層12及び絶縁膜21をパターニングする。

【0157】

以上説明したように、第7の実施形態に係る半導体記憶装置の製造方法によると、図20に示すように、浮遊ゲート電極型メモリセルにおいても、ワード線形成用の第2の導電層13を堆積した後の工程において保護ダイオード素子が機能する。このため、第2の導電層13を堆積した後は、トンネル酸化膜36及び結合容量絶縁膜37へのストレスを抑制することができる。

【0158】

(第8の実施形態)

以下、本発明の第8の実施形態について図面を参照しながら説明する。

【0159】

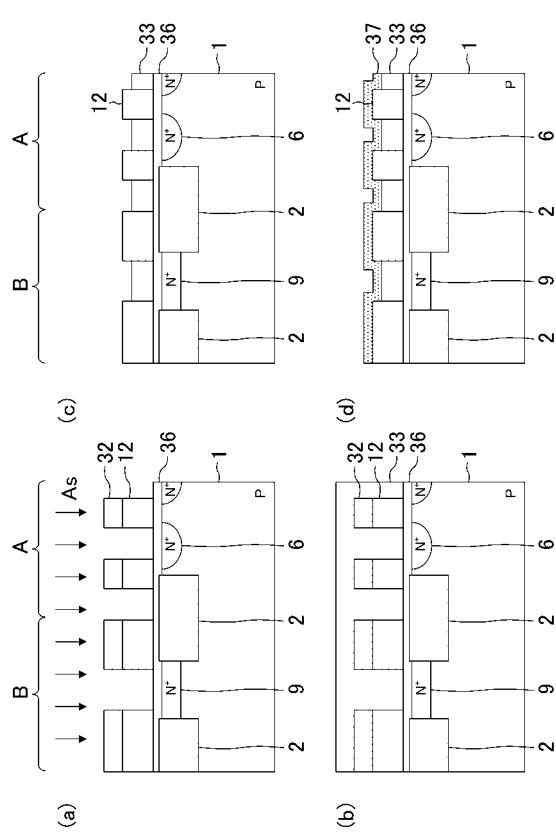

図24は本発明の第8の実施形態に係る浮遊ゲート電極型メモリセルを有する半導体記憶装置の断面構成を示している。図24において、図1及び図20に示す構成部材と同一の構成部材には同一の符号を付すことにより説明を省略する。

【0160】

第8の実施形態は、第7の実施形態と同様に浮遊ゲート電極型メモリセルを有し、さらに第7の実施形態に係る半導体記憶装置よりも微細化が可能な半導体記憶装置とその製造方法について説明する。

【0161】

第8の実施形態に係る半導体記憶装置は、第7の実施形態と同様に、メモリセルアレイ

10

20

30

40

50

領域 A において浮遊ゲート電極型メモリセルを有している。浮遊ゲート電極型メモリセルは、P型ウェル 1 の上に、トンネル酸化膜 3 6、第 1 導電層 1 2、結合容量絶縁膜 3 7 及び第 2 導電層 1 3 からなる積層構造を持つ。第 1 導電層 1 2 は第 2 導電層 1 3 と容量結合絶縁膜 3 7 を介して容量結合し、浮遊ゲート電極として機能する。

【 0 1 6 2 】

また、微細化を可能とするため、第 6 の実施形態と同様に、ソースドレイン拡散層上絶縁膜（絶縁膜）3 3 は、メモリセルアレイ領域 A にのみに形成されており、保護ダイオード領域 B には形成されていない。

【 0 1 6 3 】

保護ダイオード領域 B には、P型ウェル 1 の上部に形成された N型拡散層 9 と P型ウェル 1 とによって保護ダイオード素子が構成されている。ここで、メモリセルアレイ領域 A には、メモリセルアレイの行方向に並ぶ複数のメモリセルのゲート電極を共通に接続する第 2 導電層 1 3 からなるワード線が形成されている。ワード線となる第 2 導電層 1 3 は保護ダイオード領域 B にまで延伸し、保護ダイオード領域 B における P型ウェル 1 の上部に形成された N型拡散層 9 と直接に接続されている。

【 0 1 6 4 】

第 8 の実施形態によると、第 1 ~ 第 7 の実施形態と同様に、製造工程においてゲート絶縁膜（トンネル酸化膜 3 6）へのストレスを抑制することができる。また、図 2 4 に示す構造により、第 6 の実施形態と同様に、保護ダイオード領域 B にサイドウォール状の絶縁膜が形成されないことから、保護ダイオード領域 B のサイズを縮小することができるため、半導体記憶装置の微細化が可能となる。

【 0 1 6 5 】

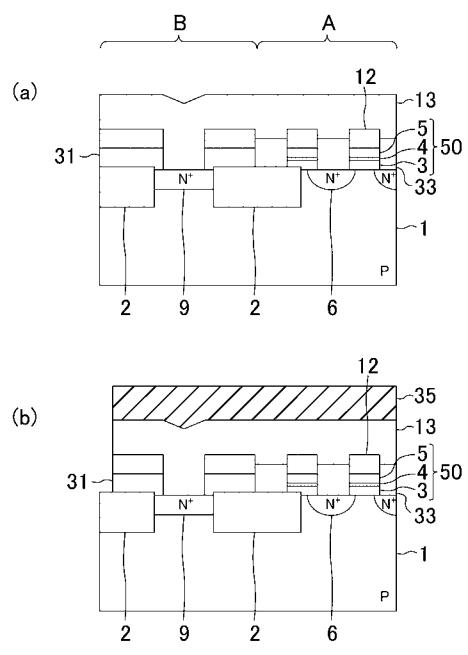

以下、前記のように構成された半導体記憶装置の製造方法について図面を参照しながら説明する。

【 0 1 6 6 】

まず、図 2 5 ( a ) に示すように、P型ウェル 1 ( 又は P型半導体基板 ) の上部に S T I 構造を持つ素子分離絶縁膜 2 を選択的に形成する。

【 0 1 6 7 】

次に、図 2 5 ( b ) に示すように、例えば熱酸化法又は C V D 法により、P型ウェル 1 の上に素子分離絶縁膜 2 を含む全面にわたって、酸化シリコンからなるトンネル酸化膜 3 6 を形成する。続いて、形成したトンネル酸化膜 3 6 の上に、C V D 法により多結晶シリコンからなる第 1 導電層 1 2 及び窒化シリコンからなるゲート電極加工用絶縁膜 3 2 を順次を形成する。

【 0 1 6 8 】

次に、図 2 5 ( c ) に示すように、リソグラフィ法及びエッチング法により、メモリセルアレイ領域 A においては、ゲート電極加工用絶縁膜 3 2 を列方向に且つ短冊状にパターニングすると共に、保護ダイオード領域 B においては、ゲート電極加工用絶縁膜 3 2 における P型ウェル 1 の上側部分を除去する。その後、パターニングされたゲート電極加工用絶縁膜 3 2 をマスクとして、第 1 導電層 1 2 をドライエッチングによりパターニングする。

【 0 1 6 9 】

次に、図 2 6 ( a ) に示すように、ゲート電極加工用絶縁膜 3 2 をマスクとして砒素 ( A s ) 等の N型不純物を P型ウェル 1 に注入して、メモリセルアレイ領域 A には N型のソースドレイン領域 6 を形成し、保護ダイオード領域 B には保護ダイオード素子を構成する N型拡散層 9 を形成する。

【 0 1 7 0 】

次に、図 2 6 ( b ) に示すように、例えば高密度プラズマ C V D 法により、酸化シリコンからなるソースドレイン拡散層上絶縁膜（絶縁膜）3 3 を、P型ウェル 1 の全面にゲート電極加工用絶縁膜 3 2 を覆うように形成する。

【 0 1 7 1 】

10

20

30

40

50

次に、図26(c)に示すように、化学機械研磨(CMP)法により、絶縁膜33をゲート電極加工用絶縁膜32が露出するまで研磨し、その後、ゲート電極加工用絶縁膜32を熱リン酸等を用いたウェットエッチングによって除去する。

【0172】

次に、図26(d)に示すように、CVD法により、露出された第1導電層12及び絶縁膜33を含めP型ウェル1すなわちウェハの全面にONO膜構造を有する結合容量絶縁膜37を形成する。

【0173】

次に、図27(a)に示すように、リソグラフィ法により、保護ダイオード領域BにおけるN型拡散層9の上側部分に開口部を持つ第1のレジストパターン34を形成する。続いて、形成した第1のレジストパターン34をマスクとして、保護ダイオード領域Bにおける結合容量絶縁膜37、絶縁膜33及びトンネル酸化膜36をドライエッチングすることにより、保護ダイオード領域BからN型拡散層9を露出する。

10

【0174】

次に、図27(b)に示すように、第1のレジストパターン34を除去した後、CVD法により、露出されたN型拡散層9を含めP型ウェル1の上すなわちウェハ上の全面に、多結晶シリコンからなる第2導電層13を堆積する。これにより、保護ダイオード領域Bにおいて、第2導電層13がN型拡散層9と直接に接続される。

【0175】

次に、図27(c)に示すように、第2導電層13の上に行方向に延伸する複数の開口パターンを持つ第2のレジストパターン35を形成する。続いて、形成した第2のレジストパターン35をマスクとして、行方向に並ぶ複数の第1導電層12同士が同一電位となるように、第2導電層13、結合容量絶縁膜37及び第1導電層12をドライエッチングしてワード線を形成する。このとき、ワード線の端部においては、第2導電層13が保護ダイオード領域Bから露出したN型拡散層9に直接に接続された状態を維持するよう、第2導電層13、結合容量絶縁膜37、第1導電層12及び絶縁膜33をパターニングする。

20

【0176】

以上説明したように、第8の実施形態に係る半導体記憶装置の製造方法によると、図24に示すように、浮遊ゲート電極型メモリセルにおいても、ワード線を構成する第2導電層13は、保護ダイオード素子を構成するP型拡散層9と直接に接続されているため、ワード線形成用の第2の導電層13を堆積した後の工程において保護ダイオード素子が機能する。このため、第2導電層13を堆積した後は、トンネル酸化膜36及び結合容量絶縁膜37へのストレスを抑制することができる。さらに、第6の実施形態と同様に、メモリセル同士の間の間隔を縮小することができると共に、保護ダイオード領域Bのサイズをも縮小できる。

30

【0177】

(第9の実施形態)

以下、本発明の第9の実施形態について図面を参照しながら説明する。

【0178】

40

第9の実施形態においては、第3～第5及び第7の各実施形態で説明した半導体記憶装置に関し、メモリセルに対する書き込み動作、消去動作及び読み出し動作時の駆動方法を説明する。特に、本発明に係る保護ダイオード領域に形成した保護ダイオード素子の場合、複数のPN接合が存在するため、PN接合ごとのノードが不安定な電位とならないよう、各ノードの電位を適切に印加する必要がある。

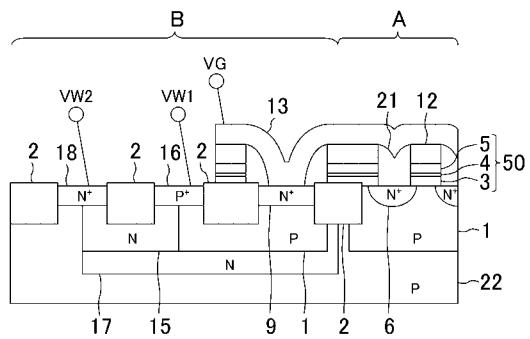

【0179】

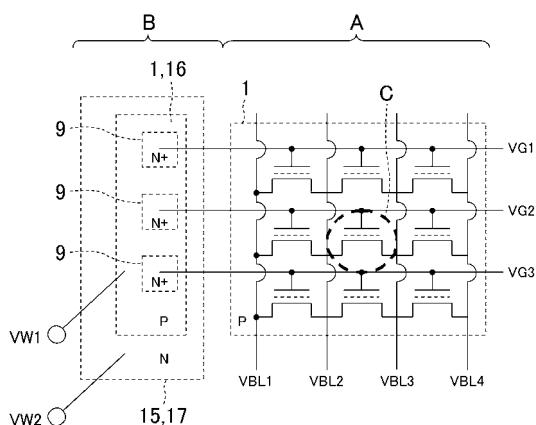

図28は第5の実施形態に示した半導体記憶装置において、メモリセルを動作させる場合に必要な端子の構成を示している。VGは、ワード線及びゲート電極を構成する第2導電層13と接続されたゲート端子であり、各メモリセルと接続されたワード線の電位を制御する。VW1は、保護ダイオード領域BにおけるP型ウェル1及びN型ウェル1の上部

50

で且つ接合部に跨るように形成されたP型拡散層16と接続された第1のウェル端子であり、P型ウェル1の電位を制御する。VW2は、保護ダイオード領域BにおけるP型拡散層40及びN型拡散層41と接続された第2のウェル端子であり、深いN型ウェル17、N型ウェル15及びP型半導体基板22の電位を制御する。

【0180】

図29は第3の実施形態に示した半導体記憶装置において、メモリセルを動作させる場合に必要な端子の構成を示している。VGは、図28と同様に、第2導電層13と接続されたゲート端子であり、各メモリセルのワード線の電位を制御する。VW1は、保護ダイオード領域BのP型拡散層16と接続された第1のウェル端子であり、P型ウェル1の電位を制御する。VW2は、保護ダイオード領域BのN型拡散層18と接続された第2のウェル端子であり、深いN型ウェル17、N型ウェル15及びP型半導体基板22の電位を制御する。

10

【0181】

図30は第4の実施形態に示した半導体記憶装置において、メモリセルを動作させる場合に必要な端子の構成を示している。VGは、図28と同様に、第2導電層13と接続されたゲート端子であり、メモリセルのワード線の電位を制御する。VW1は、保護ダイオード領域BのP型拡散層16と第1シリサイド領域19Aを介して接続された第1のウェル端子であり、P型ウェル1の電位を制御する。VW2は、第2シリサイド領域19Bを介して保護ダイオード領域BのN型ウェル15とP型半導体基板22とに接続された第2のウェル端子であり、深いN型ウェル17、N型ウェル15及びP型半導体基板22の電位を制御する。

20

【0182】

このように、図28、図29及び図30のいずれにおいても、ゲート端子VGはメモリセルのワード線の電位を制御し、第1のウェル端子VW1はP型ウェル1の電位を制御し、第2のウェル端子VW2は深いN型ウェル17、N型ウェル15及びP型半導体基板22の電位を制御する端子である。

【0183】

図31は本発明に係る半導体記憶装置におけるメモリセルアレイ領域Aと保護ダイオード領域Bとを模式的に示している。ここで、第1のウェル端子VW1及び第2のウェル端子端子VW2は、図28、図29及び図30とそれぞれ対応しており、他の符号も図28、図29又は図30と対応している。また、図28、図29及び図30に示すゲート端子VGは、図31において各ワード線と接続された第1のゲート端子VG1、第2のゲート端子VG2及び第3のゲート端子VG3と対応する。また、ビット線端子VBL1～VBL4は各ソースドレイン拡散層6と接続された端子である。

30

【0184】

[表1]に書き込み動作、消去動作及び読み出し動作時における各端子のバイアス条件を示す。いずれも図31に示した選択セルCに対して、書き込み動作及び読み出し動作を行なう。消去動作は選択されたソースドレイン拡散層と接続されたすべてのメモリセルに対して行なわれる。

40

【0185】

なお、ここでは、MONOS型メモリセルを想定した動作を示しており、書き込み動作はCHE(Channel Hot Electron)により電子を電荷蓄積層4に注入し、消去動作はBTB (Band To Band Tunneling)電流によりホールを電荷蓄積層4に注入することにより行なう。

【0186】

## 【表1】

|      | VW1 | VW2 | VG1 | VG2 | VG3 | VBL1 | VBL2 | VBL3 | VBL4 |

|------|-----|-----|-----|-----|-----|------|------|------|------|

| 書き込み | 0V  | 0V  | 0V  | 9V  | 0V  | 0V   | 0V   | 5V   | 開放   |

| 消去   | -5V | 0V  | -5V | -5V | -5V | 開放   | 開放   | 5V   | 開放   |

| 読み出し | 0V  | 0V  | 0V  | 4V  | 0V  | 開放   | 1V   | 0V   | 開放   |

10

## 【0187】

## (書き込み動作)

まず、書き込み動作について説明する。

## 【0188】

書き込み動作は、所定の1ビット、すなわち一のメモリセルに対して行なう必要があるため、選択セルCと接続されたワード線にのみ、正の高電圧を印加する。ここでは、選択ワード線と接続された第2のゲート端子VG2に9Vの電圧を印加する。非選択ワード線と接続された第1のゲート端子VG1及び第2のゲート端子VG3は接地状態(0V)とする。第1のウェル端子VW1及び第2のウェル端子VW2は、接地状態とすることにより、保護ダイオード領域BにおけるP型ウェル1、深いN型ウェル17、N型ウェル15及びP型半導体基板22を0Vの電位とする。このとき、保護ダイオード領域BにおけるN型拡散層9とP型ウェル1とのPN接合には、第2のゲート端子VG2と第1のウェル端子VW1の電位差が逆方向に印加された状態にある。しかしながら、N型拡散層9とP型ウェル1とのPN接合の耐圧が10V程度に設定されていることから、第2のゲート端子VG2と第1のウェル端子VW1との電圧差が9Vであれば、該PN接合がクランプすることなく、常にP型ウェル1は0Vを保った状態となる。

20

## 【0189】

30

仮に、第1のウェル端子VW1を接地状態とせずに開放状態とした場合は、保護ダイオード領域BのP型ウェル1が不安定な電位となって、選択ワード線の電位の立ち上がりが遅れるおそれがあるため、書き込み速度の低下を招くことにもなる。また、第1のウェル端子VW1を正電位に固定すると、第2のウェル端子VW2と順方向電圧となることから、保護ダイオード領域Bの各ウェル電位が不安定になるため望ましくない。これとは逆に、第1のウェル端子VW1を負電圧に固定すると、ワード線との電位差が大きくなるため、保護ダイオード領域BにおけるN型拡散層9とP型ウェル1とのPN接合との耐圧を高く設定する必要がある。しかしながら、このようにすると、製造中にワード線が受ける帯電による電圧を高くすることになり、電荷蓄積層4への電荷の注入やゲート絶縁膜へのストレスを助長することになる。従って、第1のウェル端子VW1は開放状態とせずに、第2のウェル端子VW2と同一電位の接地状態にする必要がある。

40

## 【0190】

## (消去動作)

次に、消去動作について説明する。

## 【0191】

消去動作は、複数ビットを同時に消去する必要がある。本実施形態においては、一のソースドレイン拡散層6と接続されたすべてのメモリセルが消去されるように、全ワード線に絶対値が大きい負の電圧を印加する。ここでは、全ワード線のゲート端子VG1～VG3に-5Vを印加する。第1のウェル端子VW1には各ゲート端子VG1～VG3と同一の-5Vを印加する。第2のウェル端子VW2は接地状態として、保護ダイオード領域B

50

における深いN型ウェル17、N型ウェル15及びP型半導体基板22を0Vとする。このとき、保護ダイオード領域BにおけるP型ウェル1とN型ウェル15との電位差は、保護ダイオード領域におけるP型拡散層16とN型ウェル15とのPN接合に対して逆方向電圧となり、且つ耐圧がこの電位差以上に大きく設定されているため、ワード線の負電位がより低下することはない。

【0192】

仮に、第1のウェル端子VW1をワード線と同一の-5Vに設定しない場合は、保護ダイオード領域BのP型ウェル1が不安定な電位となることにより、選択ワード線の電位の立ち上がりが遅れるおそれがあるため、消去速度が低下することにもなる。従って、第1のウェル端子VW1はワード線と同一電位にする必要がある。

10

【0193】

(読み出し動作)

次に、読み出し動作について説明する。

【0194】

読み出し動作は、所定の1ビット、すなわち一のメモリセルに対して行なう必要があるため、選択セルCと接続されたワード線にのみ正の電圧を印加する。ここでは、選択ワード線と接続された第2のゲート端子VG2に4Vの電圧を印加する。非選択ワード線と接続された第1のゲートの端子VG1及び第3のゲート端子VG3は接地状態(0V)とする。また、第1のウェル端子VW1及び第2のウェル端子VW2は、書き込み動作時と同様に接地状態として、保護ダイオード領域BにおけるP型ウェル1、深いN型ウェル17、N型ウェル15及びP型半導体基板22を0Vとする。このとき、保護ダイオード領域BにおけるN型拡散層9とP型ウェル1とのPN接合には、第2のゲート端子VG2と第1のウェル端子VW1との電位差が逆方向に印加された状態にある。しかしながら、前述した書き込み動作時にPN接合がクランプしないように設定されていれば、読み出し動作はそれ以下の電位差であるため問題は生じない。

20

【0195】

仮に、第1のウェル端子VW1を接地状態とせずに開放状態とした場合は、書き込み動作時と同様に、保護ダイオード領域BにおけるP型ウェル1が不安定な電位となることから、選択ワード線の電位の立ち上がりが遅れるおそれがあるため、書き込み速度の低下を招くことにもなる。従って、第1のウェル端子VW1は開放状態とせずに、所定の電位を印加しておく必要がある。

30

【0196】

なお、第9の実施形態においては、MONOS型メモリセルについて説明したが、第7の実施形態又は第8の実施形態に示す浮遊ゲート電極型メモリセルを用いる場合であっても、書き込み動作等の各動作において、ワード線への印加電圧の極性はMONOS型メモリセルと同等であることから、第1のウェル端子VW1及び第2のウェル端子VW2に印加する電位は第9の実施形態と同等とすればよい。このとき、書き込み動作はCHE(Channel Hot Electron)によって電子を電荷蓄積層に注入して行ない、消去動作はF-N(Fowler-Nordheim)電流によって電子を電荷蓄積層から除去することにより行なう。

40

【0197】

以上のように、第9の実施形態に係る半導体記憶装置の駆動方法によると、各ノードの電位を安定に保つことができるため、メモリセルに対する書き込み動作、消去動作及び読み出し動作を安定して行なうことが可能となる。

【0198】

なお、上述した第1～9の各実施形態においてはMONOS型の不揮発性半導体記憶装置又は浮遊ゲート電極型の不揮発性半導体記憶装置を例として挙げたが、これに限定されない。

【産業上の利用可能性】

【0199】

本発明に係る半導体記憶装置及びその製造方法は、高融点金属を含むコンタクトの形成

50

工程から配線層となる導電膜を堆積するまでの間においても、ゲート電極の帶電による高電圧の印加からメモリセルを保護することを可能とし、特に、EEPROM等の不揮発性半導体記憶装置等に有用である。

【図面の簡単な説明】

【0200】

【図1】本発明の第1の実施形態に係る半導体記憶装置を示す断面図である。

【図2】本発明の第1の実施形態の一変形例に係る半導体記憶装置を示す断面図である。

【図3】(a)～(c)は本発明の第1の実施形態に係る半導体記憶装置の製造方法を示す工程順の断面図である。

【図4】(a)～(c)は本発明の第1の実施形態に係る半導体記憶装置の製造方法を示す工程順の断面図である。10

【図5】本発明の第1の実施形態に係る半導体記憶装置の製造方法を示す一工程の断面図である。

【図6】本発明の第1の実施形態に係る半導体記憶装置の製造方法の第1変形例を示す一工程の断面図である。

【図7】本発明の第1の実施形態に係る半導体記憶装置の製造方法の第2変形例を示す一工程の断面図である。

【図8】本発明の第2の実施形態に係る半導体記憶装置を示す断面図である。

【図9】本発明の第3の実施形態に係る半導体記憶装置を示す断面図である。

【図10】本発明の第3の実施形態の他の変形例に係る半導体記憶装置の断面図である。

20

【図11】本発明の第4の実施形態に係る半導体記憶装置を示す断面図である。

【図12】本発明の第5の実施形態に係る半導体記憶装置を示す断面図である。

【図13】本発明の第5の実施形態の一変形例に係る半導体記憶装置の断面図である。

【図14】本発明の第6の実施形態に係る半導体記憶装置を示す断面図である。

【図15】(a)～(c)は本発明の第6の実施形態に係る半導体記憶装置の製造方法を示す工程順の断面図である。

【図16】(a)～(d)は本発明の第6の実施形態に係る半導体記憶装置の製造方法を示す工程順の断面図である。

【図17】(a)及び(b)は本発明の第6の実施形態に係る半導体記憶装置の製造方法を示す工程順の断面図である。

30

【図18】本発明の第6の実施形態に係る半導体記憶装置の製造方法の第1変形例を示す一工程の断面図である。

【図19】本発明の第6の実施形態に係る半導体記憶装置の製造方法の第2変形例を示す一工程の断面図である。

【図20】本発明の第7の実施形態に係る半導体記憶装置を示す断面図である。

【図21】(a)～(c)は本発明の第7の実施形態に係る半導体記憶装置の製造方法を示す工程順の断面図である。

【図22】(a)～(c)は本発明の第7の実施形態に係る半導体記憶装置の製造方法を示す工程順の断面図である。

【図23】(a)～(c)は本発明の第7の実施形態に係る半導体記憶装置の製造方法を示す工程順の断面図である。

40

【図24】本発明の第8の実施形態に係る半導体記憶装置を示す断面図である。

【図25】(a)～(c)は本発明の第8の実施形態に係る半導体記憶装置の製造方法を示す工程順の断面図である。

【図26】(a)～(d)は本発明の第8の実施形態に係る半導体記憶装置の製造方法を示す工程順の断面図である。

【図27】(a)～(c)は本発明の第8の実施形態に係る半導体記憶装置の製造方法を示す工程順の断面図である。

【図28】本発明の第9の実施形態に係る半導体記憶装置の駆動方法を示し、本発明の第5の実施形態に係る半導体記憶装置のメモリセルを動作させる場合の端子の構成を示す断

50

面模式図である。

【図29】本発明の第9の実施形態に係る半導体記憶装置の駆動方法を示し、本発明の第3の実施形態に係る半導体記憶装置のメモリセルを動作させる場合の端子の構成を示す断面模式図である。

【図30】本発明の第9の実施形態に係る半導体記憶装置の駆動方法を示し、本発明の第4の実施形態に係る半導体記憶装置のメモリセルを動作させる場合の端子の構成を示す断面模式図である。

【図31】本発明の第9の実施形態に係る半導体記憶装置の駆動方法において、半導体記憶装置のメモリセルを動作させる場合の端子の構成を示す平面模式図である。

【図32】従来の半導体記憶装置を示す断面図である。

10

【符号の説明】

【0201】

- |     |                     |    |

|-----|---------------------|----|

| 1   | P型ウェル又はP型半導体基板      |    |

| 2   | 素子分離絶縁膜             |    |

| 3   | 第1ゲート絶縁膜            |    |

| 4   | 電荷蓄積層               |    |

| 5   | 第2ゲート絶縁膜            |    |

| 6   | ソースドレイン拡散層          |    |

| 9   | N型拡散層               |    |

| 12  | 第1導電層               | 20 |

| 13  | 第2導電層(ワード線)         |    |

| 14  | N型半導体基板             |    |

| 15  | N型ウェル               |    |

| 16  | P型拡散層               |    |

| 17  | 深いN型ウェル             |    |

| 18  | N型拡散層               |    |

| 19A | 第1のシリサイド領域          |    |

| 19B | 第2のシリサイド領域          |    |

| 20  | レジスト                |    |

| 21  | 絶縁膜                 | 30 |

| 31  | 第3ゲート絶縁膜            |    |

| 32  | ゲート電極加工用絶縁膜         |    |

| 33  | ソースドレイン拡散層上絶縁膜(絶縁膜) |    |

| 34  | 第1のレジストパターン         |    |

| 35  | 第2のレジストパターン         |    |

| 36  | トンネル酸化膜(トンネル絶縁膜)    |    |

| 37  | 結合容量絶縁膜             |    |

| 40  | N型拡散層               |    |

| 41  | P型拡散層               |    |

| 42  | 第1のレジストパターン         | 40 |

| 43  | 第2のレジストパターン         |    |

| 50  | ゲート絶縁膜              |    |

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【 四 8 】

【図9】

【図 10】

### 【図 1 1】

### 【図12】

### 【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図30】

【図29】

【図31】

【図32】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 21/336 (2006.01)

(74)代理人 100115691

弁理士 藤田 篤史

(74)代理人 100117581

弁理士 二宮 克也

(74)代理人 100117710

弁理士 原田 智雄

(74)代理人 100121728

弁理士 井関 勝守

(74)代理人 100124671

弁理士 関 啓

(74)代理人 100131060

弁理士 杉浦 靖也

(72)発明者 守山 善也

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 原田 裕二

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 高橋 桂太

大阪府門真市大字門真1006番地 松下電器産業株式会社内

審査官 堀江 義隆

(56)参考文献 特開平11-233654 (JP, A)

特開平10-200077 (JP, A)

国際公開第03/071606 (WO, A1)

特開平10-173157 (JP, A)

特開2005-183769 (JP, A)

特開2002-164447 (JP, A)

(58)調査した分野(Int.Cl. , DB名)

H 01 L 21/8247

H 01 L 27/10

H 01 L 27/115

H 01 L 29/788

H 01 L 29/792