(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6061251号

(P6061251)

(45) 発行日 平成29年1月18日(2017.1.18)

(24) 登録日 平成28年12月22日(2016.12.22)

|              |              |

|--------------|--------------|

| (51) Int.Cl. | F 1          |

| HO 1 L 21/02 | (2006.01)    |

| HO 1 L 21/20 | (2006.01)    |

| B 23 K 20/00 | (2006.01)    |

| B 23 K 20/24 | (2006.01)    |

|              |              |

|              | HO 1 L 21/02 |

|              | HO 1 L 21/20 |

|              | B 23 K 20/00 |

|              | B 23 K 20/24 |

|              |              |

|              | B 23 K 20/00 |

|              | B 23 K 20/24 |

|              |              |

|              | B 23 K 20/00 |

|              | B 23 K 20/24 |

請求項の数 11 (全 14 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2013-142151 (P2013-142151) |

| (22) 出願日  | 平成25年7月5日(2013.7.5)          |

| (65) 公開番号 | 特開2015-15401 (P2015-15401A)  |

| (43) 公開日  | 平成27年1月22日(2015.1.22)        |

| 審査請求日     | 平成28年6月30日(2016.6.30)        |

|           |                                                           |

|-----------|-----------------------------------------------------------|

| (73) 特許権者 | 000003218<br>株式会社豊田自動織機<br>愛知県刈谷市豊田町2丁目1番地                |

| (73) 特許権者 | 313001309<br>株式会社サイコックス<br>東京都千代田区神田松永町23番 N C 島<br>商ビル2階 |

| (73) 特許権者 | 301021533<br>国立研究開発法人産業技術総合研究所<br>東京都千代田区霞が関1-3-1         |

| (74) 代理人  | 110000110<br>特許業務法人快友国際特許事務所                              |

| (72) 発明者  | 今岡 功<br>愛知県刈谷市豊田町2丁目1番地 株式会<br>社豊田自動織機内                   |

最終頁に続く

(54) 【発明の名称】半導体基板の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板の製造方法であって、

支持基板の表面の結晶構造に損傷を与えて第1の非晶質層を形成するとともに、半導体の単結晶層の表面の結晶構造に損傷を与えて第2の非晶質層を形成する非晶質層形成工程と、

前記第1の非晶質層と前記第2の非晶質層とを接触させる接触工程と、

前記第1の非晶質層と前記第2の非晶質層とが接触している状態の前記支持基板および前記単結晶層を熱処理する熱処理工程と、

を備え、

前記非晶質層形成工程は、前記支持基板の表面粗さおよび前記単結晶層の表面粗さが大きくなることに応じて前記第1の非晶質層および前記第2の非晶質層の厚さが厚くなるように、前記第1の非晶質層および前記第2の非晶質層を形成することを特徴とする半導体基板の製造方法。

## 【請求項 2】

前記支持基板の表面粗さおよび前記単結晶層の表面粗さに応じて、前記第1の非晶質層および前記第2の非晶質層の厚さを決定する非晶質層厚さ決定工程をさらに備え、

前記非晶質層形成工程は、前記厚さ決定工程で決定された厚さを有する前記第1の非晶質層および前記第2の非晶質層を形成することを特徴とする請求項1に記載の半導体基板の製造方法。

## 【請求項 3】

前記第1の非晶質層の厚さは、前記支持基板の表面の算術平均粗さの1倍～20倍の範囲内であり、

前記第2の非晶質層の厚さは、前記単結晶層の表面の算術平均粗さの1倍～20倍の範囲内であることを特徴とする請求項1または2に記載の半導体基板の製造方法。

## 【請求項 4】

前記第1の非晶質層の厚さは、前記支持基板の表面の粗さを示すPeak to Valley値の1倍～2倍の範囲内であり、

前記第2の非晶質層の厚さは、前記単結晶層の表面の粗さを示すPeak to Valley値の1倍～2倍の範囲内であることを特徴とする請求項1～3の何れか1項に記載の半導体基板の製造方法。

10

## 【請求項 5】

前記非晶質層形成工程は、真空中で原子レベルの粒子を照射することによって行われ、前記非晶質層形成工程が行われた真空中において、前記接触工程が引き続き行われることを特徴とする請求項1～4の何れか1項に記載の半導体基板の製造方法。

## 【請求項 6】

前記原子レベルの粒子の照射量および入射エネルギーは、前記支持基板の表面粗さおよび前記単結晶層の表面粗さが大きくなることに応じて大きくされることを特徴とする請求項5に記載の半導体基板の製造方法。

## 【請求項 7】

前記原子レベルの粒子は、アルゴンの中性原子であることを特徴とする請求項5または6に記載の半導体基板の製造方法。

20

## 【請求項 8】

前記熱処理工程の最高温度は950以上であることを特徴とする請求項1～7の何れか1項に記載の半導体基板の製造方法。

## 【請求項 9】

前記単結晶層は単結晶SiCであり、

前記支持基板は、多結晶SiCであることを特徴とする請求項1～8の何れか1項に記載の半導体基板の製造方法。

## 【請求項 10】

前記第1の非晶質層および前記第2の非晶質層は、SiとCを含有していることを特徴とする請求項9に記載の半導体基板の製造方法。

30

## 【請求項 11】

前記支持基板の表面から微少量の切りくずを機械的に除去することにより、前記支持基板の表面を平坦化する平坦化工程をさらに備え、

前記非晶質層形成工程は、前記平坦化工程によって平坦化された表面の結晶構造に損傷を与えて前記第1の非晶質層を形成することを特徴とする請求項1～6の何れか1項に記載の半導体基板の製造方法。

## 【発明の詳細な説明】

## 【技術分野】

40

## 【0001】

本明細書では、接合強度の高い接合面を備えている半導体基板の製造方法に関する技術を開示する。

## 【背景技術】

## 【0002】

次期パワーデバイスの基板材料の候補として炭化ケイ素（以下SiCと記載する）が挙げられるが、基板自身の製造コストが高く、実用化の障害となっている。これに対して、デバイス形成層部のみ品質の良い単結晶SiCを用いてそれを支持基板（デバイス製造工程に耐えうる強度・耐熱性・清浄度を持つ材料：例えばPoly-SiC）に何らかの方法で固定する事ができれば、低コスト（支持基板部）と高品質（SiC部）を兼ね備え

50

た基材を作る事が可能となる。上記構造を実現するために適用可能な既存技術として、基板接合がある。基板接合は、半導体集積回路作製技術やMEMS作製技術として使用され、主にシリコン基板同士またはシリコン基板と異種材料の基板を接合するために用いられている。この基板接合は、接着材・金属等の異物を介する「間接接合」と、これらを介さない「直接接合」に大別されるが、半導体デバイス材料用途の基板に対しては、接着材や金属等による汚染の影響を避けるために、「直接接合」を用いるほうが望ましい。直接接合の関連技術については、例えば以下のものが開示されている。特許文献1では、接合前のSiC基板表面にプラズマ活性化処理を施した後に基板表面同士を接触させて、その後に加熱処理を施す事により接合を形成するという、接合基板の製造法を開示している。この場合、接合前の基板表面は親水性を有しているため、接合形成後の接合界面には、導入された水に起因する酸化膜が形成される。一方、非特許文献1では、接合前のSi基板表面に希釈されたフッ化水素水溶液を用いた疎水化処理を施した後に基板表面同士を接触させて、その後に加熱処理を施す事により接合を形成するという、基板接合法を報告している。この場合、接合界面には水が存在しないため、接合界面における酸化膜形成を伴わずに接合基板を得る事ができる。10

#### 【先行技術文献】

#### 【特許文献】

#### 【0003】

【特許文献1】特開2009-117533号公報

【非特許文献1】Applied Physics Letters, Vol. 64, No. 5, 31 1994

20

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0004】

しかし、特許文献1に係る製造法を用いて接合基板を作製する場合、接合界面に形成された酸化膜の影響で、縦型パワー半導体デバイス用途においては、基板垂直方向の電気抵抗が増大するなどの問題を有する。またSiCのデバイス作製プロセスにおける加熱処理温度(>1200)に対して、界面構造が不安定であるなどの問題を有する。一方、非特許文献1に係る基板接合手法を用いて接合基板を作製する場合、接合させる基板表面の疎水化が必須であるが、SiCは化合物半導体であるため、単一元素で構成されているSiとは異なり、基板表面に露出する原子の種類により基板表面の電荷状態が異なる。そのため、非特許文献1で用いられている手法では、基板表面の広範囲において一様な疎水性を得ることが困難である。また、接合形成に中間層を介する間接接合とは異なり、直接接合では接合形成前の基板表面形状(粗さ)が有効接合面積に直接的な影響を及ぼす。そのため接合面の表面粗さを非常に小さくする必要があるなどの制限が存在する。しかし、SiC基板の表面平坦化に関しては、上述した基板表面の電荷状態の不均一性に加えて、基板内に含まれる結晶欠陥の影響で、Si基板と比較した場合に表面平坦性は低い。そのため有効接合面積が低下し、結果半導体プロセスに耐えうる接合強度を得ることが困難である。30

#### 【課題を解決するための手段】

#### 【0005】

本明細書では、半導体基板の製造方法を開示する。この半導体基板の製造方法は、支持基板の表面を改質して第1の非晶質層を形成するとともに、半導体の単結晶層の表面を改質して第2の非晶質層を形成する非晶質層形成工程を備える。また、第1の非晶質層と第2の非晶質層とを接触させる接触工程を備える。また、第1の非晶質層と第2の非晶質層とが接触している状態の支持基板および単結晶層を熱処理する熱処理工程を備える。40

#### 【0006】

上記方法では、非晶質層形成工程により、支持基板の表面に第1の非晶質層を形成するとともに、単結晶層の表面に第2の非晶質層を形成することができる。非晶質層は、原子が結晶構造のような規則性を持たない状態となっている層である。第1の非晶質層と第2の非晶質層とが接触している状態で熱処理工程を行うことにより、第1の非晶質層および50

第2の非晶質層を再結晶化させることができる。第1の非晶質層と第2の非晶質層とが一体となって再結晶化するため、支持基板と単結晶層とは共有結合によって強固に接合させることができる。これにより、接合界面における酸化膜の形成を伴わずに支持基板と単結晶層との接合界面の不連続性を消滅させることができる。

【0007】

また例えば、いわゆる直接接合などの方法は、原子間力等の基板表面間引力を用いるため、接合させる原子同士を数ナノメートル以内に接近させる必要があり、接合面の表面粗さを非常に小さくする必要がある。一方、上記方法では、接合面を非晶質層に改質している。非晶質層は、未結合手を持つ原子が存在するため、未結合手を有さない結晶層に比して原子の流動性が高い。よって、非晶質層を形成している原子が流動することによって、第1の非晶質層と第2の非晶質層との接触面に形成されている空間を埋めた上で、当該非晶質層を再結晶化させることができる。すなわち上記方法では、接合に表面間引力を必要としないため、直接接合法に要求される接合面の表面粗さよりも表面粗さが大きい場合においても、半導体プロセスなどに耐えうる接合強度を得ることが可能となる。

10

【発明の効果】

【0008】

本明細書に開示されている技術によれば、基板表面の平坦化が困難な基板に対しても、接合界面における酸化膜の形成を伴うことなく、且つ接合強度の高い接合面を備えている半導体基板の製造方法を提供することができる。

【図面の簡単な説明】

20

【0009】

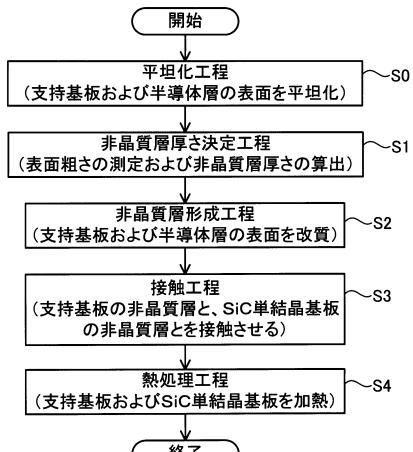

【図1】接合基板の製造方法を示すフロー図である。

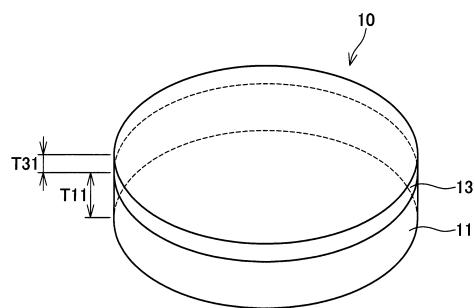

【図2】接合基板の斜視図である。

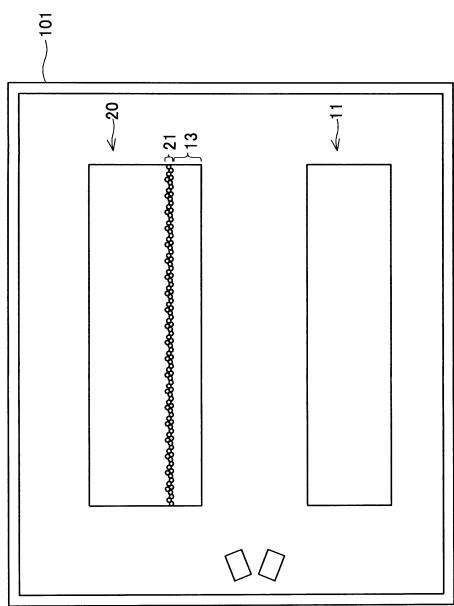

【図3】接合基板の製造工程の説明図である。

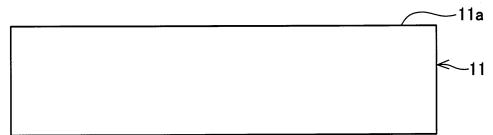

【図4】接合基板の製造工程の説明図である。

【図5】接合基板の製造工程の説明図である。

【図6】接合基板の製造工程の説明図である。

【図7】接合基板の製造工程の説明図である。

【図8】接合基板の製造工程の説明図である。

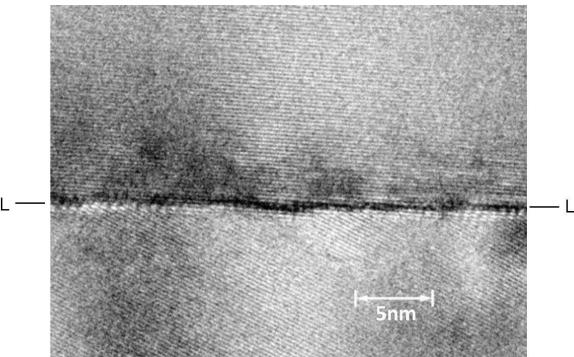

【図9】接合界面のTEM像である。

30

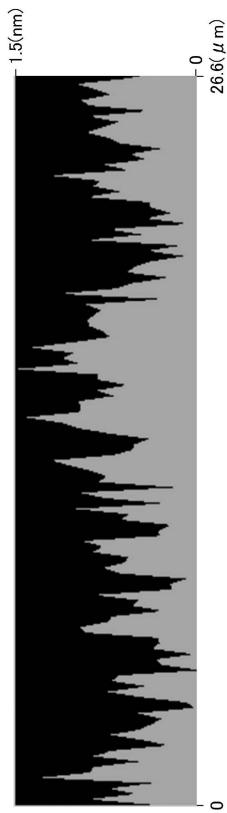

【図10】表面粗さの分析データ図である。

【発明を実施するための最良の形態】

【0010】

以下、本明細書で開示する実施例の技術的特徴の幾つかを記す。なお、以下に記す事項は、各々単独で技術的な有用性を有している。

【0011】

(特徴1) 上記の半導体基板の製造方法では、単結晶層は単結晶SiCであり、支持基板は、多結晶SiCであってもよい。多結晶SiCは単結晶SiCに比して安価であるため、単結晶SiCのみで形成された基板に比して製造コストが低減されたSiC基板を製造することができる。

40

【0012】

(特徴2) 第1の非晶質層および第2の非晶質層は、SiとCを含有したものであってもよい。これにより、例えばその組成比率がほぼ1:1である場合、第1の非晶質層および第2の非晶質層を再結晶化させる場合に、SiC結晶を形成させることができる。

【0013】

(特徴3) 上記の半導体基板の製造方法では、非晶質層形成工程は、真空中で原子レベルの粒子を照射することによって行われてもよい。非晶質層形成工程が行われた真空中において、接触工程が引き続き行われてもよい。真空中で原子レベルの粒子を照射することにより、支持基板の表面や半導体の単結晶層の表面に存在する酸化膜や吸着層を除去することができる。また、真空中において接触工程を行うことで、酸化膜や吸着層が除去された

50

清浄な面同士を接合させることができる。これにより、熱処理工程後において基材となる基板同士の共有結合の形成が可能となり、支持基板と単結晶層との接合界面の不連続性を消滅させることができる。

【0014】

(特徴4) 非晶質層の厚さが厚くなるほど、第1の非晶質層と第2の非晶質層との接觸面に形成されている空間を埋める能力を向上させることができる。一方、非晶質層の厚さが厚くなるほど、非晶質層の再結晶化に必要なサーマルバジェットが増大する。上記の半導体基板の製造方法では、支持基板の表面粗さおよび単結晶層の表面粗さに応じて、第1の非晶質層および第2の非晶質層の厚さを決定する非晶質層厚さ決定工程をさらに備えていてもよい。非晶質層非晶質層形成工程は、厚さ決定工程で決定された厚さを有する第1の非晶質層および第2の非晶質層を形成してもよい。これにより、接觸面に形成されている空間を埋めるために適切な厚さに、第1の非晶質層および第2の非晶質層の厚さを制御することが可能となる。よって、サーマルバジェットの増大を抑制することができる。

10

【0015】

(特徴5) 上記の半導体基板の製造方法では、第1の非晶質層の厚さは、支持基板の表面の算術平均粗さの1倍～20倍の範囲内であってもよい。第2の非晶質層の厚さは、単結晶層の表面の算術平均粗さの1倍～20倍の範囲内であってもよい。これにより、第1および第2の非晶質層を形成している原子の流動性を確保することができる。

【0016】

(特徴6) 上記の半導体基板の製造方法では、支持基板の表面から微少量の切りくずを機械的に除去することにより、支持基板の表面を平坦化する機械研磨のような平坦化工程をさらに備えていてもよい。非晶質層形成工程は、平坦化工程によって平坦化された表面を改質して第1の非晶質層を形成してもよい。支持基板の表面に対するCMP (Chemical Mechanical Polishing) などの研磨工程を省略することができるため、半導体基板の製造コストを低減させることができる。

20

【0017】

(特徴7) 上記の半導体基板は、多結晶SiCの第1層と、第1層上に配置されている単結晶SiCの第2層と、を備えており、第1層と第2層との界面に形成されている酸化膜厚が1原子層未満であってもよい。または、第1層と第2層との界面に存在する酸素原子密度が、SiC表面の原子密度である $1.2 \times 10^{15} \text{ cm}^{-2}$ 未満であってよい。

30

【実施例】

【0018】

<接合基板の構成>

図2に、本実施例に係る接合基板10の斜視図を示す。接合基板10は略円盤状に形成されている。接合基板10は、下側に配置された支持基板11と、支持基板11の上面に貼り合わされた半導体層13とを備えている。半導体層13は、例えば、化合物半導体(例: 6H-SiC、4H-SiC、GaN、AlN)の単結晶によって形成されていてもよい。また例えば、単元素半導体(例: Si、C)の単結晶によって形成されていてもよい。

【0019】

支持基板11には、各種の材料を用いることができる。支持基板11は、半導体層13に適用される各種の熱プロセスに対する耐性を有することが好ましい。また支持基板11は、半導体層13との熱膨張率の差が小さい材料であることが好ましい。例えば、半導体層13にSiCを用いる場合には、支持基板11には、単結晶SiC、多結晶SiC、単結晶Si、多結晶Si、サファイア、GaN、カーボンなどを用いることが可能である。多結晶SiCには、様々なポリタイプのSiC結晶が混在していても良い。様々なポリタイプが混在する多結晶SiCは、厳密な温度制御を行うことなく製造するため、支持基板11を製造するコストを低減させることができる。支持基板11の厚さT11は、後工程加工に耐えることができる機械的強度が得られるように定めればよい。厚さT11は、例えば、支持基板11の直径が100(mm)である場合には、100(

40

50

$\mu\text{m}$  ) 程度であってもよい。

【0020】

<接合基板の製造方法>

本実施例に係る接合基板10の製造方法を、図1のフローと、図3～図8の模式図を用いて説明する。図3～図8は、接合基板10を製造する各工程における、部分断面図である。なお、図3～図8では、見易さのために、ハッチングを省略している。本実施例では、例として、支持基板11が多結晶SiCであり、半導体層13が単結晶SiCである場合を説明する。また、半導体層13を形成するために、水素原子のアブレーションによる剥離技術(スマートカット(登録商標)とも呼ばれる)を用いる場合を説明する。

【0021】

まず、図3に示す支持基板11、および、SiC単結晶基板20が準備される。ステップS0において、平坦化工程が行われる。平坦化工程では、支持基板11の表面11aが平坦化される。支持基板11の表面11aは、研削、切削またはラッピングなどの機械研磨によって平坦化される。研削または切削では、微少量の切りくずを機械的に除去することにより、平坦化が行われる。研削または切削で平坦化された表面は、CMP法などの研磨法で平坦化された表面に比して、表面粗さが大きくなる。また、機械研磨で平坦化された表面は、表面粗さは十分小さくできるものの、加工変質層が数nm程度残留する。しかし、後述するように、本明細書に記載の方法では、接合面の表面粗さが大きくても接合することができるため、研削や切削後の表面を接合面に用いることが可能となる。また、加工変質層が残留していても、その領域は後述するように非晶質層を形成するため、機械研磨後の表面を接合面に用いることが可能となる。

【0022】

また、支持基板11は多結晶SiCであるが、多結晶SiCはCMPによる平坦化が困難である。これは、多結晶SiCでは様々な面方位が表面に表出しているためである。CMPを行う場合、エッティング速度が面方位に応じて変化するため結晶粒の影響を大きく受けてしまい、平坦度が低下してしまう。しかし本明細書に記載の方法では、CMPで接合面の表面粗さが大きくなても接合することができる。また、加工変質層が数nm程度残留していても接合することができるため、研磨速度の面方位依存性が小さいダイヤモンドの遊離砥粒などを用いた機械研磨を多結晶SiC基板の平坦化に用いることも出来る。

【0023】

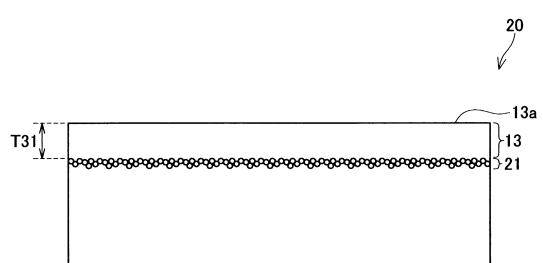

また平坦化工程では、SiC単結晶基板20の表面13aが平坦化される。表面13aは、研削や切削によって平坦化してもよいし、CMP法によって平坦化してもよい。SiC単結晶基板20は、異なる方位を有す結晶粒が基板面内に存在しないため、CMPによって平坦化することが可能である。そして、平坦化後の表面13aから水素イオンを注入する、イオン注入工程が行われる。これにより、図4の模式図に示すように、表面13aから所定深さに、水素イオン注入層21が形成される。図4では、打ち込まれた水素イオンを白抜きの丸印で擬似的に示している。水素原子のアブレーションによる剥離技術により剥離される半導体層13の厚さT31は、イオン注入する水素イオンのエネルギーにより制御できる。厚さT31は、0.5～1.0( $\mu\text{m}$ )の範囲であっても良い。なお、水素イオンの注入方法は、周知の方法でよいため、ここでは説明を省略する。

【0024】

ステップS1において、非晶質層厚さ決定工程が行われる。非晶質層厚さ決定工程は、支持基板の表面粗さおよび単結晶層の表面粗さに応じて、支持基板11の非晶質層11bの厚さT11と、SiC単結晶基板20の非晶質層13bの厚さT13を決定する工程である。

【0025】

具体的に説明する。まず、支持基板11の表面11aの表面粗さ、および、半導体層13の表面13aの表面粗さが測定される。表面粗さには、算術平均粗さRaや表面凹凸の高低差であるPV値(Peak to Valley)、最小二乗平均平方根粗さRMSなど各種の指標を用いても良い。本明細書内では算術平均粗さRaを用いている。また表面粗さの測定に

10

20

30

40

50

は、各種の方式を用いてもよい。例えば、触針方式、レーザセンサ方式、光干渉方式などを用いても良い。また、走査型プローブ顕微鏡（S P M）を表面粗さの測定に用いても良い。

#### 【 0 0 2 6 】

次に、測定された表面粗さに基づいて、厚さ T 1 1 および T 1 3 が決定される。本実施例では、厚さ T 1 1 は、表面 1 1 a の算術平均粗さ R a 1 1 の 1 倍～20 倍の範囲内に決定される。また、厚さ T 1 3 は、表面 1 3 a の算術平均粗さ R a 1 3 の 1 倍～20 倍の範囲内に決定される。例えば、本実施例では、R a = 1 nm の表面粗さに対して、厚さ約 2 nm の非晶質層を形成している。また、表面粗さに P V 値を用いる場合には、厚さ T 1 1 は、表面 1 1 a の P V 値の 1 倍～2 倍の範囲内に決定される。また、厚さ T 1 3 は、表面 1 3 a の P V 値の 1 倍～2 倍の範囲内に決定される。例えば、本実施例では、P V 値 = 1.5 nm の表面粗さに対して、厚さ約 2 nm の非晶質層を形成している。10

#### 【 0 0 2 7 】

ステップ S 2 において、非晶質層形成工程が行われる。非晶質層形成工程は、支持基板 1 1 の表面を改質して非晶質層 1 1 b を形成するとともに、半導体層 1 3 の表面を改質して非晶質層 1 3 b を形成する工程である。非晶質層とは、原子が結晶構造のような規則性を持たない状態となっている層のことをさす。非晶質層 1 1 b および非晶質層 1 3 b の厚さは、非晶質層厚さ決定工程（ステップ S 1）で決定された厚さとされる。

#### 【 0 0 2 8 】

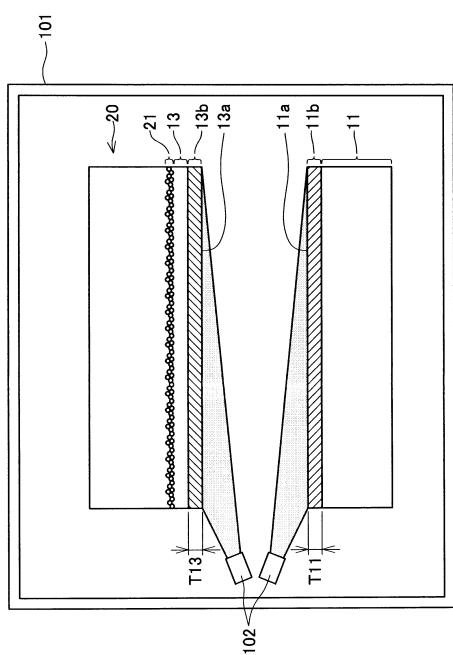

具体的に説明する。図 5 に示すように、SiC 単結晶基板 2 0 と支持基板 1 1 を、チャンバー 1 0 1 内にセットする。次に、SiC 単結晶基板 2 0 と支持基板 1 1 との相対位置の位置合わせを行う。位置合わせは、後述する接触工程で両基板が正しい位置関係で接触できるように行われる。次に、チャンバー 1 0 1 内を真空状態にする。チャンバー 1 0 1 内の真空中度は、例えば、 $1 \times 10^{-4} \sim 1 \times 10^{-6}$  (Pa) 程度であってもよい。20

#### 【 0 0 2 9 】

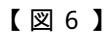

図 6 に示すように、支持基板 1 1 の表面 1 1 a および半導体層 1 3 の表面 1 3 a に F A B ガン（高速原子ビーム：Fast Atom Beam）1 0 2 を用いて、アルゴンの中性原子ビームを照射する。これにより、表面 1 1 a および 1 3 a の結晶構造を、表面から一定の深さで破壊することができる。その結果、基板表面に、Si と C を含んでいる非晶質層 1 1 b および 1 3 b を形成することができる。また、Si と C の含有比率が 1 : 1 となるように、非晶質層 1 1 b および 1 3 b を形成することができる。これにより、非晶質層 1 1 b および 1 3 b を再結晶化させる場合に、SiC 結晶を形成させることができるとなる。図 6 では、非晶質層 1 1 b および 1 3 b を、ハッチングで擬似的に示している。非晶質層 1 1 b の厚さ T 1 1 、および非晶質層 1 3 b の厚さ T 1 3 は、F A B ガン 1 0 2 から照射されるアルゴン原子のエネルギーにより制御できる。アルゴンの照射量 (atoms/cm<sup>2</sup>) は、形成する非晶質層の厚さとスペッタレートを用いて算出するとしてもよい。また入射エネルギーは、例えば 1.5 (keV) 程度であってもよい。30

#### 【 0 0 3 0 】

また、非晶質層形成工程では、表面 1 1 a および 1 3 a の酸化膜や吸着層を除去して結合手を表出させることができるために、表面 1 1 a および 1 3 a を活性化することができる。また非晶質層形成工程は真空中での処理であるため、表面 1 1 a および 1 3 a は、酸化等されず活性状態を保持することができる。40

#### 【 0 0 3 1 】

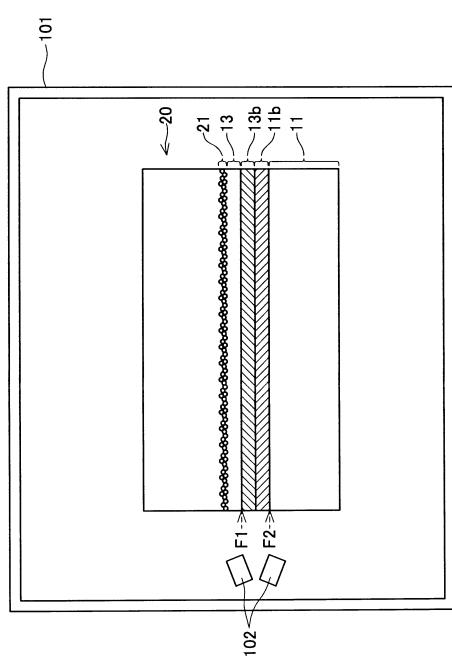

ステップ S 3 において、接触工程が行われる。接触工程では、図 7 に示すように、支持基板 1 1 の非晶質層 1 1 b と、SiC 単結晶基板 2 0 の非晶質層 1 3 b とを、チャンバー 1 0 1 内で、真空中で接触させる。また、接触後に支持基板 1 1 と SiC 単結晶基板 2 0 とが離反しないように、不図示のジグ等を用いて固定してもよい。

#### 【 0 0 3 2 】

ステップ S 4 において、熱処理工程が行われる。熱処理工程では、非晶質層 1 1 b と 1 3 b とが接触している状態で、支持基板 1 1 および SiC 単結晶基板 2 0 を熱処理する。50

熱処理工程は、チャンバー 101 内で減圧下で行われても良いし、チャンバー 101 以外の他の炉内で行われても良い。

【0033】

熱処理工程では、支持基板 11 および SiC 単結晶基板 20 が、所定温度（例えば 1000 度）に加熱される。これにより、非晶質層 11b および 13b に、流動性を持たせることができる。非晶質層 11b と 13b との接触面には、空間が形成される場合がある。形成される空間の体積は、非晶質層 11b や 13b の表面粗さが大きくなるほど大きくなる。そこで熱処理工程を行なうことにより、非晶質層 11b および 13b を形成している原子を流動させることができるために、非晶質層 11b と 13b との接触面に形成されている空間を埋めることができる。また熱処理工程によって、SiC 単結晶基板 20 を水素イオン注入層 21 で破断させることができる。従って、半導体層 13 の上方に位置していた SiC 単結晶基板 20 を取り除くことができる。

【0034】

また熱処理工程により、非晶質層 11b および 13b を、原子配列に規則性がない状態から、原子配列に規則性を有する状態へ再結晶化させることができる。非晶質層 13b の再結晶化は、非晶質層 13b と半導体層 13 との界面 F1（図 7 参照）から非晶質層 13b の内部（図 7 の下側）へ向かって、半導体層 13 の結晶構造（単結晶 SiC）に倣った原子配列となるよう行われる。また非晶質層 11b の再結晶化は、非晶質層 11b と支持基板 11 との界面 F2（図 7 参照）から非晶質層 11b の内部（図 7 の上側）へ向かって、支持基板 11 の結晶構造（多結晶 SiC）に倣った原子配列となるよう行われる。従って再結晶化が完了すると、図 8 に示すように、非晶質層 11b および 13b が消滅し、半導体層 13 と支持基板 11 とが直接に接合している接合基板 10 が形成される。非晶質層 11b と 13b とが一体となって再結晶化するため、半導体層 13 と支持基板 11 とを共有結合によって強固に接合させることができる。

【0035】

< TEM 像による分析（その 1）>

図 9 に、本明細書に記載されている接合方法で作成された接合基板 10 の、支持基板 11 と半導体層 13 との接合界面の TEM (Transmission Electron Microscope) 写真を示す。観察に用いられた接合基板 10 は、支持基板 11 が多結晶 SiC であり、半導体層 13 が単結晶の 4H-SiC である。非晶質層形成工程では、1.5 (keV) の入射エネルギーで、60 (sec) の間、アルゴン原子を照射した。熱処理工程の最高温度は 1100 である。

【0036】

図 9 の TEM 写真では、イオンミリングによって薄化した TEM 試料を観察している。図 9 において、L-L 線部分を境界線とした場合の下側の領域が支持基板 11（多結晶 SiC）であり、上側の領域が半導体層 13（単結晶 SiC）である。図 9 の L-L 線部分に示す接合界面の領域には、接合界面の領域の全般にわたって、原子の周期性が確認できる。よって、界面に非晶質層が存在していないことが分かる。また、余計な中間層が存在せず、多結晶 SiC と単結晶 SiC とが原子レベルで直接に接合していることが分かる。また、本接合基板に対して SIMS (Secondary Ion-microprobe Mass Spectrometer) による酸素濃度分析を行った結果、支持基板 11 と半導体層 13 との界面に存在する酸素原子密度が  $2.2 \times 10^{14} \text{ cm}^{-2}$  であった。これは、SiC 表面の原子密度である  $1.2 \times 10^{15} \text{ cm}^{-2}$  よりも低い値である。これから、本明細書に開示されている技術により形成された接合界面に存在する酸化膜厚が、1 原子層未満であることが分かる。なお、支持基板 11 と半導体層 13 との接合界面の一部に、非晶質層が存在している場合があることに留意されたい。これは、非晶質層 11b および 13b を形成している原子が流動することによって非晶質層 11b と 13b との接触面に形成されている空間を埋めるため、再結晶化させる必要のある非晶質層の厚さが一定ではないためである。また、支持基板 11 と半導体層 13 との接合界面の一部に、1 原子層以上の酸化膜が存在している場合があることに留意されたい。

## 【0037】

なお、従来知られている直接接合法や常温接合法では、多結晶SiCと単結晶SiCとが原子レベルで直接に接合しているとともに、接合界面の領域の全般にわたって原子の周期性が確認できるTEM像を得ることはできない。これは、大気圧中で接合する直接接合法では、酸化膜や吸着層が接合界面に存在するためである。また、常温接合法では、真空内のイオンガンによる表面活性化時に接合界面の原子配列が乱されてしまい、その後の処理で原子配列を整えることができないためである。換言すると、接合界面のTEM像により、貼り合わせ基板が本明細書に記載されている接合方法で作成されたか否かを確認することが可能である。

## 【0038】

10

## &lt;表面粗さおよび接合強度の分析&gt;

図10に、図9で分析を行った接合基板10を製造する際に行われた平坦化工程（ステップS0）における、表面粗さの分析データを示す。測定対象は、CMPによって平坦化された支持基板11の表面である。すなわち図10は、支持基板11表面の断面プロファイルである。測定機器は、日立ハイテクサイエンス社（登録商標）の原子間力顕微鏡（AFM）装置（型番SPA500 & SPI3800）である。横軸は測定範囲を示しており、約27μmである。図10に示した測定範囲における支持基板11のPV値は1.5nm、算術平均粗さはRa=1nmであった。この表面粗さは、従来の直接接合法を行うことができない程度に大きい値である。

## 【0039】

20

また、表面粗さ測定後の試料を用いて接合基板を作成し、引張り試験を行った。装置の上限である20(MPa)を加えても、接合面は剥離されなかった。これにより、接合面が、従来の直接接合法では接合することができない程度に大きな表面粗さを有している場合においても、本明細書に記載されている接合方法を用いることによって、半導体プロセスなどに耐えうる十分な接合強度で接合させることができることが分かる。

## 【0040】

## &lt;効果&gt;

支持基板と半導体の単結晶層とを、樹脂や合金などの中間材を介さずに直接に接合する、いわゆる直接接合技術では、表面間引力を用いて接合を行うため、接合面同士を数ナノメートル以内に接近させる必要があり、接合面の表面粗さを非常に小さくする必要がある（例えば、算術平均粗さRaで0.3(nm)程度が要求される場合がある）。また、接合面の表面粗さがある程度大きくなることを許容するために、接合面のSiC結晶に流動性を持たせる方法が考えられる。しかしSiC結晶は、2000を超えると昇華する（すなわち、固体から直接に気化する）性質を有するため、溶融して液化することができなく、流動性を持たせることが困難である。

30

## 【0041】

一方、本明細書に記載されている接合方法では、接合面を、SiとCを含んだ非晶質層11bおよび13bに改質している。非晶質層は、未結合手を持つ原子が存在するため、未結合手を有さない結晶層に比して、原子の流動性を高めることができる。すなわち、SiC結晶の昇華温度（約2500）に比して十分低い温度である、1000度以下程度の温度で、非晶質層11bおよび13bに流動性を持たせることができる。よって、昇華を防止しながら、接合面を形成する材料に流動性を持たせることができる。これにより、非晶質層11bおよび13bを形成している原子が流動することによって、非晶質層11bと13bとの接触面に形成されている空間を埋めた上で、当該非晶質層11bおよび13bを再結晶化させることができる。すなわち上記方法では、接合に表面間引力を必要としないため、直接接合法に要求される接合面の表面粗さよりも表面粗さが大きい場合においても、半導体プロセスなどに耐えうる接合強度で基板を接合することが可能となる。

40

## 【0042】

本明細書に記載されている接合方法では、直接接合法などに比して接合面の表面粗さが大きくても基板を接合することができる。よって平坦化工程（ステップS0）では、接合

50

面となる支持基板 11 の表面 11a を、研削または切削によって平坦化することができる。これにより、支持基板 11 の表面に対して、C M P ( Chemical Mechanical Polishing ) などの研磨工程を適用する必要性を無くすことができるため、半導体基板の製造コストを低減させることができる。

#### 【 0 0 4 3 】

非晶質層 11b の厚さ T 11 が厚くなるほど、非晶質層 11b および 13b の流動性を高くすることができるため、非晶質層 11b と 13b との接触面に形成されている空間を埋める能力を向上させることができる。一方、厚さ T 11 が厚くなるほど、非晶質層 11b および 13b の再結晶化に必要なサーマルバジエットが増大する。本明細書に記載されている接合方法では、非晶質層厚さ決定工程 (ステップ S 1 ) によって、支持基板 11 の表面粗さおよび半導体層 13 の表面粗さに応じて、厚さ T 11 および T 13 を決定することができる。これにより、表面 11a と 13a の接触面に形成されている空間を埋めるために適切な厚さに、厚さ T 11 および T 13 を制御することが可能となる。よって、サーマルバジエットの増大を抑制することができる。

10

#### 【 0 0 4 4 】

接触工程 (ステップ S 3 ) では、非晶質層形成工程 (ステップ S 2 ) で酸化膜や吸着層が除去された表面 11a と表面 13a とを、真空中において接触させるため、清浄な面同士を接合させることができる。これにより、図 9 の T E M 写真に示すように、余計な中間層が存在せず、多結晶 SiC と単結晶 SiC とが原子レベルで直接に接合している構造を形成することができる。従って、貼り合わせ基板 10 を用いて縦型デバイスを作成する場合に、支持基板 11 と半導体層 13 との界面を横切るように電流経路上が形成される場合においても、当該界面の存在によってデバイスの性能が低下 (例: オン抵抗の増加) してしまうことを防止することができる。本明細書に記載されている接合方法では、縦型デバイスの製造に適した接合基板 10 を製造することが可能となる。

20

#### 【 0 0 4 5 】

支持基板 11 と半導体層 13 とを、直接に接合する場合には、接合面において原子配列のずれが発生し、そのずれを緩和することができないため、応力が発生する。一方、本明細書に記載されている接合方法では、支持基板 11 と半導体層 13 とを、非晶質層 11b および 13b を介して接合する構成を有している。熱処理工程では、熱エネルギーによって、非晶質層 11b および 13b 内の Si 原子および C 原子が徐々に動いて再結晶化が起こる。これにより、非晶質層 13b と半導体層 13 との界面 F 1 (図 7 参照) での半導体層 13 の原子配列と、非晶質層 11b と支持基板 11 との界面 F 2 (図 7 参照) での支持基板 11 の原子配列と、の間にずれが発生している場合においても、界面 F 1 と界面 F 2 の間に介在する非晶質層 11b および 13b が、これらのずれを緩和するように再結晶化する。すなわち、非晶質層 11b および 13b を、熱処理工程によって消滅させることができる、応力緩和層として利用することができる。以上より、支持基板 11 と半導体層 13 との界面で発生する内部応力を緩和することができるため、支持基板 11 の上方に位置している半導体層 13 においても、内部応力が緩和されることになる。よって、熱処理工程によって半導体層 13 の内部応力を緩和するとともに、半導体層 13 内で欠陥の移動および再配列をさせることができるために、内部応力に起因して半導体層 13 に存在する各種欠陥の密度を低減させることができる。

30

#### 【 0 0 4 6 】

支持基板 11 と半導体層 13 とを、非晶質層 11b および 13b を形成せずに直接に接合した場合には、貼り合わせ後の基板に大きな応力が発生する場合がある。これは、支持基板 11 が多結晶 SiC であるため、様々な面方位が支持基板 11 の表面に表出しており、面方位に応じて熱膨張係数が僅かに異なることがあるためである。本明細書に記載されている接合方法では、支持基板 11 と半導体層 13 とを、非晶質層 11b および 13b を介して接合する構成を有している。接合後の熱処理において、面方位に応じた熱膨張係数差によって内部応力が発生する場合にも、この内部応力を緩和するように非晶質層 11b および 13b が徐々に流動しながら再結晶化する。よって、支持基板 11 と半導体層 13

40

50

との界面で発生する内部応力を緩和することができる。

【0047】

本明細書に記載されている接合方法では、支持基板11と半導体層13との間に、非晶質層11bおよび13bを介在させることができる。この非晶質層11bおよび13bによって、支持基板11の表面に表出している各種の欠陥が、半導体層13に影響してしまうことを防止できる。すなわち、熱処理工程において、半導体層13の原子の再配列が行われる場合に、支持基板11の表面に存在する各種の欠陥の影響を受けて、再配列後の半導体層13に欠陥が形成されてしまう事態を防止することができる。よって、半導体層13の欠陥密度を低減させることが可能となる。

【0048】

10

以上、本発明の実施例について詳細に説明したが、これらは例示に過ぎず、特許請求の範囲を限定するものではない。特許請求の範囲に記載の技術には、以上に例示した具体例を様々に変形、変更したものが含まれる。

【0049】

<変形例>

非晶質層形成工程（ステップS2）において、非晶質層を形成する方法は、アルゴンの中性原子ビーム照射に限られない。例えば、He、水素、Ar、Si、Cなどの、原子または分子またはイオンなどを注入する方法であってもよい。

【0050】

熱処理工程（ステップS4）において、処理時間に対する温度変化の態様は、様々であってよい。

20

【0051】

支持基板11に使用される材料は、多結晶SiCに限られない。半導体層13に適用される各種の熱プロセスに対する耐性を有する材料であれば、何れの材料であってもよい。例えば、セラミック材料の混合材料によって形成されている焼結体であってもよい。使用的セラミック材料は、各種の材料でよく、例えば、SiC、Si、AlN、Al<sub>2</sub>O<sub>3</sub>、GaN、Si<sub>3</sub>N<sub>4</sub>、SiO<sub>2</sub>、Ta<sub>2</sub>O<sub>5</sub>、などのうちの少なくとも1種類の材料であってもよい。

【0052】

本明細書または図面に説明した技術要素は、単独あるいは各種の組合せによって技術的有用性を発揮するものであり、出願時請求項記載の組合せに限定されるものではない。また、本明細書または図面に例示した技術は複数目的を同時に達成し得るものであり、そのうちの一つの目的を達成すること自体で技術的有用性を持つものである。

30

【符号の説明】

【0053】

10：接合基板、11：支持基板、11bおよび13b：非晶質層、13：半導体層、

20：SiC単結晶基板、21：水素イオン注入層

【 図 1 】

【図2】

【 义 5 】

【図3】

【 図 4 】

## 【 义 5 】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(72)発明者 小林 元樹

東京都千代田区外神田 3 - 12 - 8 住友不動産秋葉原ビル 12階14号室 株式会社サイコツ

クス内

(72)発明者 内田 英次

東京都千代田区外神田 3 - 12 - 8 住友不動産秋葉原ビル 12階14号室 株式会社サイコツ

クス内

(72)発明者 八木 邦明

東京都千代田区外神田 3 - 12 - 8 住友不動産秋葉原ビル 12階14号室 株式会社サイコツ

クス内

(72)発明者 河原 孝光

東京都千代田区外神田 3 - 12 - 8 住友不動産秋葉原ビル 12階14号室 株式会社サイコツ

クス内

(72)発明者 八田 直記

東京都千代田区外神田 3 - 12 - 8 住友不動産秋葉原ビル 12階14号室 株式会社サイコツ

クス内

(72)発明者 南 章行

東京都千代田区外神田 3 - 12 - 8 住友不動産秋葉原ビル 12階14号室 株式会社サイコツ

クス内

(72)発明者 坂田 豊和

東京都千代田区外神田 3 - 12 - 8 住友不動産秋葉原ビル 12階14号室 株式会社サイコツ

クス内

(72)発明者 牧野 友厚

東京都千代田区外神田 3 - 12 - 8 住友不動産秋葉原ビル 12階14号室 株式会社サイコツ

クス内

(72)発明者 高木 秀樹

茨城県つくば市東 1 - 1 - 1 独立行政法人産業技術総合研究所つくばセンター内

(72)発明者 倉島 優一

茨城県つくば市東 1 - 1 - 1 独立行政法人産業技術総合研究所つくばセンター内

審査官 高須 甲斐

(56)参考文献 特表2004-503942 (JP, A)

特開2000-091176 (JP, A)

特表2010-541230 (JP, A)

特開2005-252550 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/02

B23K 20/00

B23K 20/24

H01L 21/20