(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4908784号

(P4908784)

(45) 発行日 平成24年4月4日(2012.4.4)

(24) 登録日 平成24年1月20日(2012.1.20)

(51) Int.Cl.

**G09G 3/20 (2006.01)**

F 1

|      |      |         |

|------|------|---------|

| G09G | 3/20 | 6 3 3 B |

| G09G | 3/20 | 6 3 3 G |

| G09G | 3/20 | 6 3 3 H |

| G09G | 3/20 | 6 4 1 A |

| G09G | 3/20 | 6 4 1 C |

請求項の数 10 (全 26 頁) 最終頁に続く

(21) 出願番号 特願2005-175118 (P2005-175118)

(22) 出願日 平成17年6月15日 (2005.6.15)

(65) 公開番号 特開2006-47996 (P2006-47996A)

(43) 公開日 平成18年2月16日 (2006.2.16)

審査請求日 平成20年6月10日 (2008.6.10)

(31) 優先権主張番号 特願2004-193928 (P2004-193928)

(32) 優先日 平成16年6月30日 (2004.6.30)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100085006

弁理士 世良 和信

(74) 代理人 100100549

弁理士 川口 嘉之

(74) 代理人 100106622

弁理士 和久田 純一

(72) 発明者 磯野 青児

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社 内

審査官 鳥居 祐樹

最終頁に続く

(54) 【発明の名称】表示素子の駆動回路、画像表示装置、テレビジョン装置

## (57) 【特許請求の範囲】

## 【請求項 1】

表示素子が接続される配線に印加する変調信号を出力する変調回路と、

前記変調信号の波形の少なくとも一部分の波高値を決定する波高値データと、前記変調

信号の波形の少なくとも一部分のパルス幅を決定するパルス幅データと、を含むパラレル

データフォーマットの変調データが入力され、前記入力された変調データを、前記変調デ

タのビット数よりも少ない数の伝送経路で伝送可能にするために、前記伝送経路の数と

同じ個数のシリアルデータフォーマットのデータにシリアル化し、前記シリアル化したデ

タを前記伝送経路を介して前記変調回路に出力する出力回路とを有し、

前記伝送経路は複数あり、

前記出力回路は、

複数の伝送経路の内の所定の伝送経路には、シリアル化された前記パルス幅データを出

力せずにシリアル化された前記波高値データを出力し、前記所定の伝送経路以外の他の所

定の伝送経路には、シリアル化された前記波高値データを出力せずにシリアル化された前

記パルス幅データを出力することを特徴とする表示素子の駆動回路。

## 【請求項 2】

前記出力回路が、前記所定の伝送経路と前記他の所定の伝送経路の少なくともいずれか

において、前記波高値データを構成するデータビット及び前記パルス幅データを構成する

データビットのいずれも伝送しない時間に、当該伝送経路の信号レベルを規定するための

ダミーデータとして任意のデータビットを出力するように構成されており、

10

20

前記波高値データを構成するデータビット及び前記パルス幅データを構成するデータビットのいずれも伝送しない前記時間は、一つの変調信号を発生するための前記波高値データのビット数と、該一つの変調信号を発生するための前記パルス幅データのビット数とが互いに異なっており、且つ、前記波高値データのビット数と前記パルス幅データのビット数の少なくとも一方が前記シリアルデータフォーマットのデータの時系列方向のビット数で割り切れる値でないために、生じる時間である

請求項1記載の表示素子の駆動回路。

**【請求項3】**

前記出力回路が、前記所定の伝送経路において、前記波高値データを構成するデータビットを伝送しない時間に、当該伝送経路の信号レベルを規定するためのダミーデータとして任意のデータビットを出力するように構成されており、

10

前記波高値データを構成するデータビットを伝送しない前記時間は、一つの変調信号を発生するための前記波高値データのビット数と、該一つの変調信号を発生するための前記パルス幅データのビット数とが互いに異なっており、且つ、前記波高値データのビット数が前記シリアルデータフォーマットのデータの時系列方向のビット数で割り切れる値でないために、生じる時間であり、

前記任意のデータビットは、それぞれ値の異なる複数の前記波高値データを構成する各データビットの並びに対して同じ箇所に位置するように出力される

請求項1記載の表示素子の駆動回路。

**【請求項4】**

20

前記出力回路が、前記他の所定の伝送経路において、前記パルス幅データを構成するデータビットを伝送しない時間に、当該伝送経路の信号レベルを規定するためのダミーデータとして任意のデータビットを出力するように構成されており、

前記パルス幅データを構成するデータビットを伝送しない前記時間は、一つの変調信号を発生するための前記波高値データのビット数と、該一つの変調信号を発生するための前記パルス幅データのビット数とが互いに異なっており、且つ、前記パルス幅データのビット数が前記シリアルデータフォーマットのデータの時系列方向のビット数で割り切れる値でないために、生じる時間であり、

前記任意のデータビットは、それぞれ値の異なる複数の前記パルス幅データを構成する各データビットの並びに対して同じ箇所に位置するように出力される

30

請求項1記載の表示素子の駆動回路。

**【請求項5】**

表示素子が接続される配線に印加する変調信号を出力する変調回路と、

前記変調信号の波形の少なくとも一部分の波高値を決定する波高値データと、前記変調信号の波形の少なくとも一部分のパルス幅を決定するパルス幅データと、を含むパラレルデータフォーマットの変調データが入力され、前記入力された変調データを、前記変調データのビット数よりも少ない数の伝送経路で伝送可能にするために、前記伝送経路の数と同じ個数のシリアルデータフォーマットのデータにシリアル化し、前記シリアル化したデータを前記伝送経路を介して前記変調回路に出力する出力回路とを有し、

前記伝送経路が、前記波高値データを構成するデータビットの少なくとも一部および前記パルス幅データを構成するデータビットの少なくとも一部を共に伝送する伝送経路を少なくとも含んでおり、

40

前記変調回路は、

該伝送経路を経由して伝送されるデータビットを記憶する記憶回路と、

前記記憶回路から前記波高値データを構成するデータビットを読み出して、波高値データとして出力するとともに、前記記憶回路から前記パルス幅データを構成するデータビットを読み出して、パルス幅データとして出力する制御回路と、

を含むことを特徴とする表示素子の駆動回路。

**【請求項6】**

前記記憶回路は、入力されるデータビットを記憶する複数の記憶素子を有しており、

50

前記複数の記憶素子は直列に接続されており、各記憶素子は、新たなデータビットが入力されるのに同期して、記憶していたデータビットを直列に接続されている次の記憶素子に入力し、入力された新たなデータビットを記憶するように構成されており、

該直列に接続されている複数の記憶素子の一部の記憶素子から前記波高値データを構成するデータビットを出力し、他の一部の記憶素子から前記パルス幅データを構成するデータビットを出力する

請求項 5 記載の表示素子の駆動回路。

【請求項 7】

前記波高値データは前記変調信号の最大波高値の部分の波高値を決定するデータである

請求項 1 乃至 6 のいずれか 1 項に記載の表示素子の駆動回路。 10

【請求項 8】

前記パルス幅データは前記変調信号の立ち下がりのタイミングを決定するデータである

請求項 1 乃至 7 のいずれか 1 項に記載の表示素子の駆動回路。 11

【請求項 9】

請求項 1 乃至 8 のいずれか 1 項の駆動回路と、

該駆動回路から出力される変調信号に従って画像を表示する表示部と、

を含む画像表示装置。 12

【請求項 10】

請求項 9 に記載の画像表示装置と、

テレビ信号を受信して該画像表示装置に画像データを供給する受信回路と、

を含むテレビジョン装置。 20

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、表示素子の駆動回路に関し、特に、発光素子を階調データに対応する明るさで発光させるための駆動回路に適用して好適なものである。 21

【背景技術】

【0002】

従来技術としての特許文献 1においては、発光素子をパルス幅変調と振幅変調とを組み合わせた階段状駆動波形で駆動させるための駆動回路を簡略かつ低廉に構成するための駆動方法および駆動回路が記載されている。 30

【0003】

【特許文献 1】特開 2003 - 316312 号公報 ( 図 12 参照 )

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、上述した従来の駆動回路には次のような問題があった。すなわち、特許文献 1 に記載された発明においては、階調数の増加に伴って、伝送するデータ線数が増加してしまう。そのため、階調数が増加した場合であっても、データ線数の増加を抑制することができる技術の開発が熱望されていた。 40

【0005】

したがって、この発明の目的は、伝送経路や伝送線の数の低減化を図ることができる駆動回路を提供することにある。 41

【課題を解決するための手段】

【0006】

本願に係わる発明の一つは以下のように構成される駆動回路の発明である。

この発明は、表示素子が接続される配線に印加する変調信号を出力する変調回路と、前記変調信号の波形の少なくとも一部分の波高値を決定する波高値データと、前記変調信号 50

の波形の少なくとも一部分のパルス幅を決定するパルス幅データと、を含むパラレルデータフォーマットの変調データが入力され、前記入力された変調データを、前記変調データのビット数よりも少ない数の伝送経路で传送可能にするために、前記传送経路の数と同じ個数のシリアルデータフォーマットのデータにシリアル化し、前記シリアル化したデータを前記传送経路を介して前記変調回路に出力する出力回路とを有し、前記传送経路は複数あり、前記出力回路は、複数の传送経路の内の所定の传送経路には、シリアル化された前記パルス幅データを出力せずにシリアル化された前記波高値データを出力し、前記所定の传送経路以外の他の所定の传送経路には、シリアル化された前記波高値データを出力せずにシリアル化された前記パルス幅データを出力することを特徴とする表示素子の駆動回路である。

10

## 【0007】

このような構成によれば、传送経路の数の低減化を図ることができる。

## 【0008】

この発明において、

前記出力回路が、前記所定の传送経路と前記他の所定の传送経路の少なくともいずれかにおいて、前記波高値データを構成するデータビット及び前記パルス幅データを構成するデータビットのいずれも传送しない時間に、当該传送経路の信号レベルを規定するためのダミーデータとして任意のデータビットを出力するように構成されており、

前記波高値データを構成するデータビット及び前記パルス幅データを構成するデータビットのいずれも传送しない前記時間は、一つの変調信号を発生するための前記波高値データのビット数と、該一つの変調信号を発生するための前記パルス幅データのビット数とが互いに異なっており、且つ、前記波高値データのビット数と前記パルス幅データのビット数の少なくとも一方が前記シリアルデータフォーマットのデータの時系列方向のビット数で割り切れる値でないために、生じる時間である、構成を好適に採用できる。

20

## 【0009】

このような構成によれば、シリアル化を実行する際のデータ設定の自由度を高くすることができます。

## 【0010】

この発明において、

前記出力回路が、前記所定の传送経路において、前記波高値データを構成するデータビットを传送しない時間に、当該传送経路の信号レベルを規定するためのダミーデータとして任意のデータビットを出力するように構成されており、

前記波高値データを構成するデータビットを传送しない前記時間は、一つの変調信号を発生するための前記波高値データのビット数と、該一つの変調信号を発生するための前記パルス幅データのビット数とが互いに異なっており、且つ、前記波高値データのビット数が前記シリアルデータフォーマットのデータの時系列方向のビット数で割り切れる値でないために、生じる時間であり、

前記任意のデータビットは、それぞれ値の異なる複数の前記波高値データを構成する各データビットの並びに対して同じ箇所に位置するように出力される、構成を好適に採用できる。

30

## 【0011】

若しくは、

前記出力回路が、前記他の所定の传送経路において、前記パルス幅データを構成するデータビットを传送しない時間に、当該传送経路の信号レベルを規定するためのダミーデータとして任意のデータビットを出力するように構成されており、

前記パルス幅データを構成するデータビットを传送しない前記時間は、一つの変調信号を発生するための前記波高値データのビット数と、該一つの変調信号を発生するための前

40

50

記パルス幅データのビット数とが互いに異なっており、且つ、前記パルス幅データのビット数が前記シリアルデータフォーマットのデータの時系列方向のビット数で割り切れる値でないために、生じる時間であり、

前記任意のデータビットは、それぞれ値の異なる複数の前記パルス幅データを構成する各データビットの並びに対して同じ箇所に位置するように出力される、構成を好適に採用できる。

#### 【 0 0 1 2 】

これらの構成に依れば、任意のデータビットをデータビットの並びに挿入する場合であっても、変調回路における所望のデータの再生を容易に行うことができる。 10

#### 【 0 0 1 3 】

また、表示素子が接続される配線に印加する変調信号を出力する変調回路と、

前記変調信号の波形の少なくとも一部分の波高値を決定する波高値データと、前記変調信号の波形の少なくとも一部分のパルス幅を決定するパルス幅データと、を含むパラレルデータフォーマットの変調データが入力され、前記入力された変調データを、前記変調データのビット数よりも少ない数の伝送経路で伝送可能にするために、前記伝送経路の数と同じ個数のシリアルデータフォーマットのデータにシリアル化し、前記シリアル化したデータを前記伝送経路を介して前記変調回路に出力する出力回路とを有し、

前記伝送経路が、前記波高値データを構成するデータビットの少なくとも一部および前記パルス幅データを構成するデータビットの少なくとも一部を共に伝送する伝送経路を少なくとも含んでおり、 20

前記変調回路は、

該伝送経路を経由して伝送されるデータビットを記憶する記憶回路と、

前記記憶回路から前記波高値データを構成するデータビットを読み出して、波高値データとして出力するとともに、前記記憶回路から前記パルス幅データを構成するデータビットを読み出して、パルス幅データとして出力する制御回路と、

を有する構成を採用できる。

#### 【 0 0 1 4 】

なおこの発明において、波高値データおよびパルス幅データのシリアル化によりデータ非伝送時間が生じた場合に、前述の発明と同様に任意のデータビットを出力するように構成することもできる。 30

#### 【 0 0 1 5 】

このような構成によれば、異なるデータ属性のデータを混在化してシリアル伝送することができる。

#### 【 0 0 1 6 】

特に、この構成において、前記記憶回路は、入力されるデータビットを記憶する複数の記憶素子を有しており、

前記複数の記憶素子は直列に接続されており、

各記憶素子は、新たなデータビットが入力されるのに同期して、記憶していたデータビットを直列に接続されている次の記憶素子に入力し、入力された新たなデータビットを記憶するように構成されており、 40

該直列に接続されている複数の記憶素子の一部の記憶素子から前記波高値データを構成するデータビットを出力し、他の一部の記憶素子から前記パルス幅データを構成するデータビットを出力する構成を好適に採用できる。

#### 【 0 0 1 7 】

なお以上述べた各発明において、前記波高値データは前記変調信号の最大波高値の部分の波高値を決定するデータである構成や、前記パルス幅データは前記変調信号の立ち下がりのタイミングを決定するデータである構成を好適に採用できる。

#### 【 0 0 1 8 】

また本願は、画像表示装置の発明を含んでおり、この画像表示装置は前述の駆動回路と 50

、該駆動回路から出力される変調信号に従って画像を表示する表示部によって構成される。

#### 【0019】

また本願はテレビジョン装置の発明を含んでおり、このテレビジョン装置は、前述の画像表示装置と、テレビ信号を受信して該画像表示装置に画像データを供給する受信回路とによって構成される。

#### 【発明の効果】

#### 【0020】

本発明によれば、伝送経路や伝送線の数の低減化を図ることができる。

#### 【発明を実施するための最良の形態】

#### 【0021】

以下に図面を参照して、この発明の最良な実施の形態を例示的に詳しく説明する。ただし、この実施の形態に記載されている構成部品の寸法、材質、形状、その相対配置などは、特に特定的な記載がない限りは、この発明の範囲をそれらのみに限定する趣旨のものではない。なお、以下の実施形態の全図においては、同一または対応する部分には同一の符号を付す。

#### 【0022】

##### (テレビジョン装置の実施の形態)

まず、図12を用いて本発明が適用可能なテレビジョン装置について説明する。図12は、本発明に係るテレビジョン装置のブロック図である。テレビジョン装置は、セットトップボックス(STB)501と、画像表示装置502と、を備える。

#### 【0023】

セットトップボックス(STB)501は、受信回路503およびI/F部504を有する。受信回路503は、チューナーやデコーダ等からなり、衛星放送や地上波等のテレビ信号、ネットワークを介したデータ放送等を受信し、復号化した映像データをI/F部504に出力する。I/F部504は、映像データを画像表示装置502の表示フォーマットに変換して画像表示装置502に映像データを出力する。

#### 【0024】

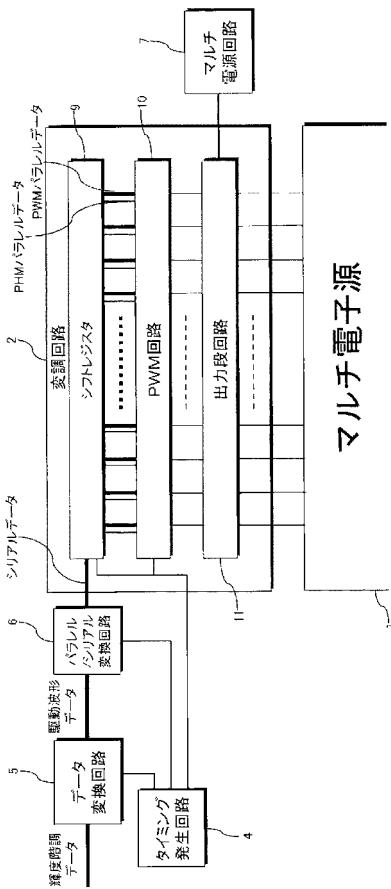

画像表示装置502は、表示パネル200、制御回路505、駆動回路506を有する。画像表示装置502に含まれる制御回路505は、入力した映像データに表示パネル200に適した補正処理等の画像処理を施すとともに、駆動回路506に映像データ及び各種制御信号を出力する。制御回路505は、一例として図1におけるタイミング発生回路4が挙げられる。駆動回路506は、入力された映像データに基づいて、表示パネル200に駆動信号を出力し、表示パネル200上にはテレビ映像が表示されることとなる。駆動回路506は、一例として図1における変調回路2や走査回路3が挙げられる。表示パネル200は、以下の実施の形態では図1に示すようにマルチ電子源1を例に挙げる。マルチ電子源1として、例えば、FED、PDP、LCDディスプレイ、LED、ELディスプレイ等の種々の表示パネルを用いることができる。

#### 【0025】

なお、受信回路503とI/F部504は、セットトップボックス(STB)501として画像表示装置502とは別の筐体に収められていてもよいし、また画像表示装置502と同一の筐体に収められていてもよい。

#### 【0026】

まず、この発明の第1の実施形態による表示装置の駆動回路について説明する。図1にこの第1の実施形態による駆動回路を示す。

#### 【0027】

変調信号の変調方法としては、変調信号の時間幅を変調するパルス幅変調や変調信号の振幅を変調する振幅変調を採用できる。単純なパルス幅変調であれば変調信号の振幅を一定としてパルス幅を階調データ(表示したい明るさを示すデータであって、例えば輝度データ)に応じて決定すればよい。その場合変調回路には階調データを直接入力すればよい

10

20

30

40

50

。また単純な振幅変調であれば変調信号のパルス幅を一定として振幅を階調データに応じて決定すればよい。その場合も変調回路には階調データを直接入力すればよい。

#### 【0028】

一方本願発明者は、単純なパルス幅変調や単純な振幅変調ではなく、変調信号のパルス幅制御と振幅制御との両方を階調データに基づいて設定する構成を検討している。この構成においては、変調回路が、ある変調信号のパルスの波形を規定するために、該変調信号の少なくとも一部の波高値（振幅）を決定するための回路である波高値設定回路と、該変調信号の少なくとも一部の波高値から他の波高値（変調信号の振幅の基準となる基準レベル（例えばグランドレベルなど）を含む）に遷移させるタイミングを決定するための回路であるタイミング設定回路を有する構成を好適に採用できる。この場合、表示したい明るさに1対1に対応した大きさの値を持つ階調データを直接変調回路に入力するよりも、波高値設定回路で波高値を設定するのに参照するデータである波高値データとタイミング設定回路でタイミングを設定するのに参照するデータであるタイミングデータとをそれぞれ発生させて（階調データのフォーマット変換を行って）、その波高値データとタイミングデータとを変調回路に入力する構成を好適に採用できる。10

#### 【0029】

ここで説明する実施形態においては、このように波高値データとタイミングデータとを変調回路に入力する場合の最も好適な形態を説明する。

#### 【0030】

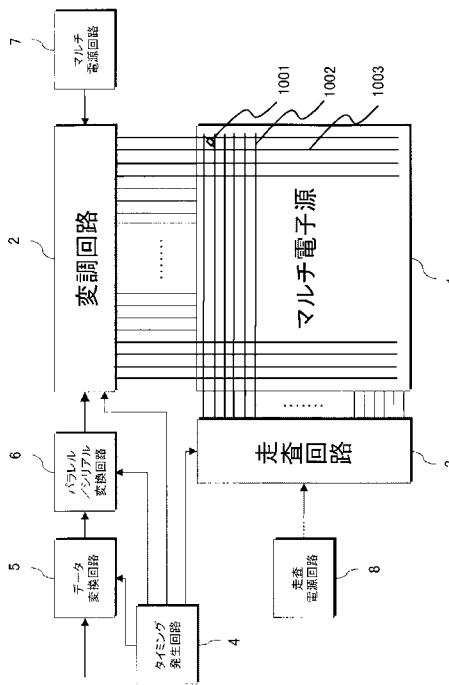

図1に示すように、マルチ電子源1を駆動する第1の実施形態による駆動回路においては、変調回路2、走査回路3、タイミング発生回路4、データ変換回路5、出力回路としてのパラレル／シリアル変換回路6、マルチ電源回路7および走査電源回路8を有して構成されている。この駆動回路は、画像表示装置における画像表示部の一部を構成する。20

#### 【0031】

マルチ電子源1は表示素子として表面伝導型放出素子1001を有している。ここでは表示素子として表面伝導型放出素子を用いているが、表示素子としてはスピント型の電子放出素子や、エレクトロルミネッセンス素子など種々の素子を用いることができる。なお、表示素子として表面伝導型放出素子などの電子放出素子を用いる場合は、電子放出素子が放出する電子が蛍光体に照射されることで光が生じる。この光によって画像が表示される。光の明るさは電子放出素子からの所定時間内（ここで示す形態においては、線順次走査の1選択期間内）における電子の照射量で制御することができる。電子放出素子からの電子の照射量は電子放出素子に印加される電圧の大きさ、時間幅によって制御できる。従って、走査信号の電位と変調信号の電位との電位差や走査信号印加期間内の変調信号の印加時間を制御することで所望の照射量を得ることができる。30

#### 【0032】

マルチ電子源1は複数の表示素子をマトリックス駆動できるように接続する複数の走査配線1002と複数の変調配線1003を有している。この走査配線1002に前記走査信号が印加され、変調配線1003に変調信号が印加される。

#### 【0033】

変調回路2は、マルチ電子源1の変調配線である列方向配線に接続されている。この変調回路2には、先に述べた波高値データであるPHM（Pulse Height Modulation）データとパルス幅データ（タイミングデータ）であるPWM（Pulse Width Modulation）データとがそれぞれ入力される。変調回路2には、出力回路としてのパラレル／シリアル変換回路6によりシリアル変換されたPHMデータとPWMデータとが入力される。なお波高値データであるPHMデータとタイミングデータであるPWMデータはそれ単独では要求される明るさと1対1に対応するデータではないが、双方を変調回路で参照することによって要求される明るさを実現するための変調信号を発生できるものである。従って、変調データとして変調回路に入力される波高値データであるPHMデータとタイミングデータであるPWMデータとは、要求される階調に対応する階調データを構成するデータと言える。変調回路2は入力された変調データに応じて変調信号を発生させる回路である。4050

変調回路 2 は、パラレル / シリアル変換回路 6 から入力された変調データに基づいて変調した変調信号を、複数の電子源にそれぞれ接続する列方向配線に与える、変調手段として機能する。

#### 【 0 0 3 4 】

走査回路 3 は、マルチ電子源 1 の行方向配線に接続されており、変調回路 2 の出力によって駆動されるべき表示素子が接続される走査配線に選択信号（走査信号）を供給する回路である。一般的には、一行ずつ順次行選択する線順次走査が行われるが、これに限定されるものではなく、飛び越し走査や複数行を選択したり面状に選択したりすることも可能である。すなわち、走査回路 3 は、マルチ電子源 1 に含まれる複数電子源のうち駆動対象となる複数の電子源が接続される行方向配線に対して所定時間に選択電位を与え、それ以外の時間に非選択電位を与えて、行選択をする選択手段として機能する。10

#### 【 0 0 3 5 】

タイミング発生回路 4 は、変調回路 2 、走査回路 3 、データ変換回路 5 およびパラレル / シリアル変換回路 6 の各回路のタイミング信号を発生する回路である。

#### 【 0 0 3 6 】

データ変換回路 5 は、外部からマルチ電子源 1 に要求する明るさを示す階調データ（輝度データ）を変調回路 2 に適した駆動波形データフォーマットに変換するデータ変換を行う回路である。

#### 【 0 0 3 7 】

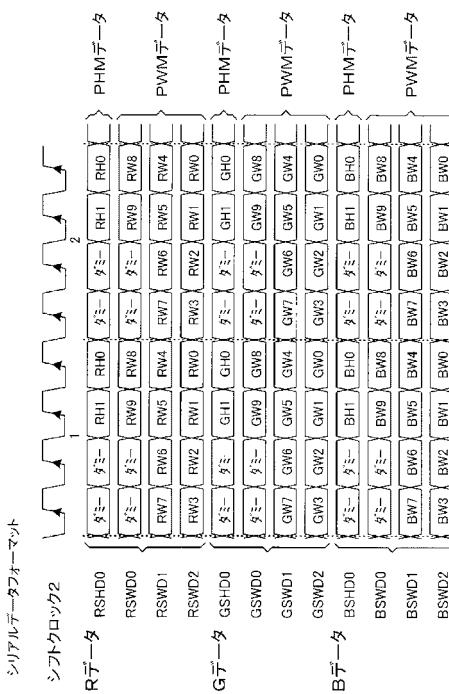

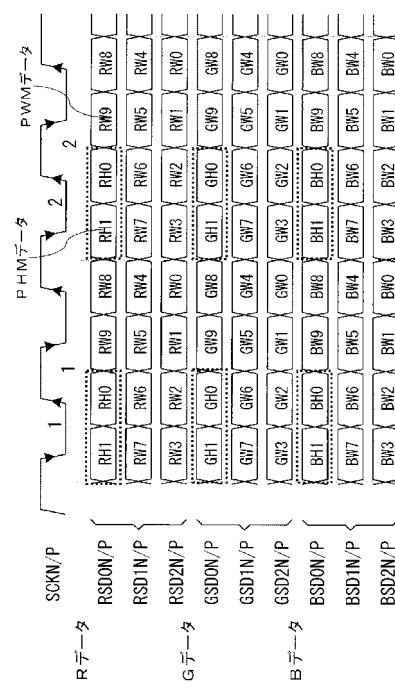

パラレル / シリアル変換回路 6 は、データ変換回路 5 から出力されたパラレルデータである階調データを P H M データおよび P W M データごとにそれぞれパラレルデータをシリアルデータに変換する回路である。このパラレル / シリアル変換回路 6 に入力されるデータフォーマットおよび、パラレル / シリアル変換回路 6 から出力されるデータフォーマットについて、図 2 および図 4 を用いて説明する。20

#### 【 0 0 3 8 】

図 2 に、パラレル / シリアル変換回路 6 に入力される駆動波形データのフォーマットを示す。これは、データ変換回路 5 が出力するデータのフォーマットである。図 2 に示すように、この駆動波形データは、タイミング発生回路 4 により発生されたタイミング信号の 1 つであるシフトクロック 1 に同期し、 R G B に対してそれぞれ個別に、 2 ビットの P H M データと 10 ビットの P W M データとがパラレルに構成されたデータフォーマットである。すなわち、パラレル / シリアル変換回路 6 に入力される状態においては、赤色の光を発生する蛍光体に対応する電子放出素子に印加する変調信号を発生させるための階調データは 12 ビットのパラレルデータ（ 2 ビットの波高値データと 10 ビットのタイミングデータ）である。他の色についても同様である。すなわち一つの変調信号パルスを形成するためのデータはこの段階では並列数が 12 、時系列方向のビット数が 1 のデータフォーマットを有する。ここでは、 P H M データを 2 ビット、 P W M データを 10 ビットとした構成の例について説明するが、必ずしもこのような構成に限定されるものではない。30

#### 【 0 0 3 9 】

また、図 3 に、パラレル / シリアル変換回路から出力される駆動波形データのフォーマットを示す。図 3 に示す駆動波形データは、タイミング発生回路 4 により発生されたタイミング信号の一つであるシフトクロック 2 に同期し、 P H M データと P W M データとを、それぞれ個別に、 4 ビットごとにデータをシリアル化したデータフォーマットである。なお、 4 ビットに対して不足したデータが存在した場合、すなわちデータ非伝送時間が生じた場合には、不足分を充填するように、疑似データとしてのダミーデータが出力される。後述するように変調回路においてダミーデータは無視できるように構成しているので、ダミーデータとしては任意のデータを使用できる。具体的には、伝送経路に出力する信号レベルを強制的に 0 レベル（ローレベル）もしくは 1 レベル（ハイレベル）に規定する構成を好適に採用できる。40

#### 【 0 0 4 0 】

このシリアル化により、図 2 に示す 12 ビットのパラレルデータの並列数 12 が、並列

数4に減少され、時系列方向のビット数は1から4に増えている。具体的には、2ビットのパラレルデータ（並列数が2、時系列方向のビット数が1）であったPHMデータが並列数が1、時系列方向のビット数が4のフォーマットに変換されている。また、10ビットのパラレルデータ（並列数が10、時系列方向のビット数が1）であったPWMデータが並列数が3、時系列方向のビット数が4のフォーマットに変換されている。

#### 【0041】

ここで、以下の条件を考える。すなわち、

- (1) PHMデータとPWMデータが混在しないようにするという条件、である。

#### 【0042】

10

この条件を満たす場合、PHMデータのビット数と、PWMデータのビット数によっては、前記使用可能な時間のうちPHMデータを構成するデータビットもしくはPWMデータを構成するデータビットを传送しない時間が発生する。これがPHMデータのビット数とPWMデータのビット数の不整合によって生じる時間である。

#### 【0043】

またここで示す実施形態では好適な実施の形態として以下の2つの条件を満たすように構成している。すなわち、

(2) 一つの伝送経路において、一つの変調信号を形成するためのPHMデータを传送する時間として使用可能な時間（ここでは4ビットの信号をシリアルに传送するための時間）と、他の一つの伝送経路において、前記一つの変調信号を形成するためのPWMデータを传送する時間として使用可能な時間（4ビットの信号をシリアルに传送するための時間）とを等しくするという条件、

20

(3) 各伝送経路の传送速度（単位時間あたりに传送可能なビット数）を同一にするという条件、

である。

#### 【0044】

この2つの条件を採用すると、条件(1)によって生じる、ビット数の不整合に依って生じる前記時間を解消しにくくなる。

#### 【0045】

30

この時間に伝送経路の信号レベルが不定になってしまふと誤動作が生じる恐れがある。そこで本実施形態では、該時間に任意のデータ（ダミーデータ）を出力するように構成することでこの問題を解消している。

#### 【0046】

具体的には、2ビットのPHMデータを4ビットのデータとして出力する構成を採用する。ここではPHMデータは4つの条件（ここでは変調信号が有するべき最大波高値がどの波高値になるかを指定する条件）を指定できればよいので、2ビット、すなわち、10進法では、0、1、2、3の値を有する。これを4ビットに変換する。4ビットのデータは10進法では0から15までの任意の値を指定できる。従って、もともとの4つの値0、1、2、3を0から15までの任意の値に変換して送信することができる。ただし、変調回路側で4ビットのデータから特定の2ビットのみを取り出すことで元のPHMデータを再現できるように構成するためには、もとの2ビットのデータ、すなわち、"00"、"01"、"10"、"11"の同じ箇所に、任意のデータビットを挿入するのが好ましい。具体的には、2ビットのデータの前、若しくは後、若しくは途中にデータビットを挿入する構成を採用できる。本実施形態のように複数のデータビットを挿入する場合は、それらの挿入箇所を組み合わせて用いることもできる。例えば、2ビットのデータの前に任意のデータビットとして"00"を挿入すると、上記4つの値は、"0000"、"0001"、"0010"、"0011"となる。この場合、このデータを受信する変調回路では、前半の2つのビットを無視すればよい。挿入されるデータビットは無視することができる。"00"である必要はなく、他の任意のデータビットを採用できる。また、例えば、2ビットのデータの途中に任意のデータビットとして"1"を挿入し、末尾に任意のデ

40

50

ータビットとして”0”を挿入する、という構成も採用できる。この場合、上記4つの値は、”0100”、“0110”、“1100”、“1110”となる。変調回路側では、先頭のビットと3桁目のビットから元の2ビットのPHMデータを再現できる。

#### 【0047】

もともとの4つの値、0、1、2、3(10進法)を、0から15までの任意の値として、7、8、9、10(10進法)に置換して送信することもできる。この場合は4ビットの信号が、”0111”、“1000”、“1001”、“1010”となり、特定の2つのビットを抽出するだけでは元のPHMデータを再現することができない。従って、本実施形態では、もとのデータのとりうる各値(伝送状態に応じた値。ここではハイレベル、ローレベルの2状態で伝送するので、2進法で表記した値)に対して、同じ位置に任意のビットを附加した値に変換して送信している。信号の伝送状態としては、2値伝送(ハイレベルとローレベルの2つの状態から伝送状態を選択する構成)を好適に採用できるが、他の伝送状態(例えば4つの伝送状態を選択できる構成)も採用できる。すなわち、データビットは0か1に限るものではない。

#### 【0048】

PWMデータも同様である。もともと10ビットのPWMデータを12ビット(一つの伝送経路でシリアルに4ビット伝送する。これを3つの伝送経路で行うので、全部で12ビットのデータとなる)に変換する変換方法としては種々の変換方法を採用可能である。変調回路側で、特定のビットを無視して元の10ビットのPWMデータを再現できるようにするために、本実施形態では、元のPWMデータの全ての値に対して同じ2箇所に任意のビットを附加して12ビット化するように構成している。

#### 【0049】

マルチ電源回路7は、複数の電源値を出力可能に構成された電源回路であり、変調回路2を制御するための回路である。マルチ電源回路7は、一般的に電圧源回路であるが、必ずしもこれに限定されるものではない。

#### 【0050】

走査電源回路8は、複数の電源値を出力する電源回路であり、走査回路3を制御する回路である。走査電源回路8は、一般的には、電圧源回路であるが、必ずしもこれに限定されるものではない。

#### 【0051】

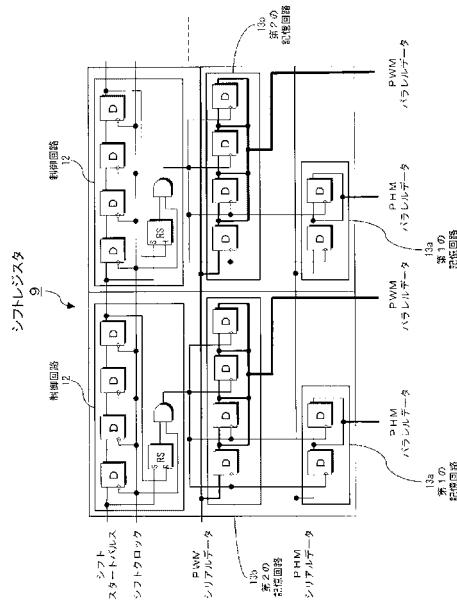

次に、変調回路2について説明する。図4に、変調回路2の内部構成を示す。図4に示すように、変調回路2は、シフトレジスタ9、PWM回路10および出力段回路11をして構成されている。

#### 【0052】

シフトレジスタ9には、パラレル/シリアル変換回路6によりシリアル変換されたPHMシリアルデータおよびPWMシリアルデータが入力される。また、シフトレジスタ9によりマルチ電子源1の列方向配線に応じた変調データである、PHMパラレルデータおよびPWMパラレルデータが転送される。

#### 【0053】

PWM回路10には、シフトレジスタ9からマルチ電子源1の列方向配線に応じた変調データであるPHMパラレルデータおよびPWMパラレルデータが入力される。そして、PWM回路10により、出力段回路11が出力する複数の信号レベル(信号の電位であり波高値に相当する)の出力タイミングを指定するための信号が、出力段回路11に対して出力される。

#### 【0054】

また、シフトレジスタ9およびPWM回路10の制御を行うためのタイミング信号が、タイミング発生回路4から入力される。出力段回路11は、マルチ電源回路7に接続され、後述する駆動波形を有した変調信号を出力する回路である。図5に、シフトレジスタ9の内部構成を示し、図6に、図4に示すPWM回路10として列方向配線1本当に備わる回路構成の一例を示し、図7に、図4に示す出力段回路11における列方向配線の1

10

20

30

40

50

本当たりに備わる回路の一例を示す。

**【0055】**

図5に示すように、シフトレジスタ9は、複数の制御回路12および複数の記憶回路13を有して構成される。この第1の実施形態においては、Dフリップフロップ回路、RSフリップフロップ回路およびアンドゲート回路を用いた構成を例に説明するが、制御回路12および記憶回路13は、これに限定されるものではない。

**【0056】**

図5に示すように、第1の記憶回路13aには、パラレル／シリアル変換回路6でシリアル変換されたPHMシリアルデータが入力される。そして、この第1の記憶回路13aにより、マルチ電子源1の列方向配線に応じた変調データであるPHMパラレルデータが転送される。10

**【0057】**

第2の記憶回路13bには、パラレル／シリアル変換回路6でシリアル変換されたPWMシリアルデータが入力される。なおここで、シリアルデータと称しているが、これはフォーマット変換前のデータに対して、少なくとも一部に対するシリアル化を行って並列数を減らしたデータであることをいうのであって、並列数が1に限るものではない。実際ここで示す形態ではこのPWMシリアルデータは並列数が3である。従って、第2の記憶回路13bもその並列数に合わせて3系統備えることになる。ただし図5では全てを図示することで不明瞭になることを避けるためそれら3系統を集合的に表記している。この第2の記憶回路13bにより、マルチ電子源1の列方向配線に応じた変調データであるPWMパラレルデータが転送される。20

**【0058】**

また、制御回路12には、タイミング発生回路4において発生されたタイミング信号の1つであるシフトスタートパルスとシフトクロックとが入力される。また、制御回路12により、マルチ電子源1の列方向配線に応じた変調データであるPHMシリアルデータおよびPWMデータを第1の記憶回路13aおよび第2の記憶回路13bに記録するための制御信号が発生される。

**【0059】**

この制御回路12が発生した記録制御信号に応じて、PHMシリアルデータが第1の記憶回路13aに記録されるとともに、PWMシリアルデータが第2の記憶回路13bに記録される。30

**【0060】**

第1の記憶回路13aおよび第2の記憶回路13bから出力されるデータは、パラレルに構成されており、マルチ電子源1の列方向配線に応じて、一括してPWM回路10に出力される。

**【0061】**

具体的には、4ビットの時系列方向のPWMシリアルデータが図5に示す第2の記憶回路13bの4つのフリップフロップで順次に転送される。該4ビットの時系列方向のPWMシリアルデータが4つのフリップフロップに記憶された状態において、出力タイミングがフリップフロップに対して指定されることで4ビットのパラレルデータが出力される。これを3系統夫々で並列に行うことによって、12ビットのPWMパラレルデータが出力される。ただし、2ビットはダミーデータなので、該ダミーデータは無視され、実際には10ビットのPWMパラレルデータが出力される。40

**【0062】**

また、4ビットの時系列方向のPHMシリアルデータが第1の記憶回路13aに入力される。ただし4ビットのうちの2ビットはダミーデータであるので、記憶回路13aはダミーデータを除く2ビットを記憶できるように2つのフリップフロップで構成されている。これによってPHMシリアルデータはパラレル化される。

**【0063】**

次に、図6を用いて、PWM回路10について説明する。なお、図6に示すPWM回路50

10は、あくまで一例であり、必ずしもこの回路構成に限定されるものではない。

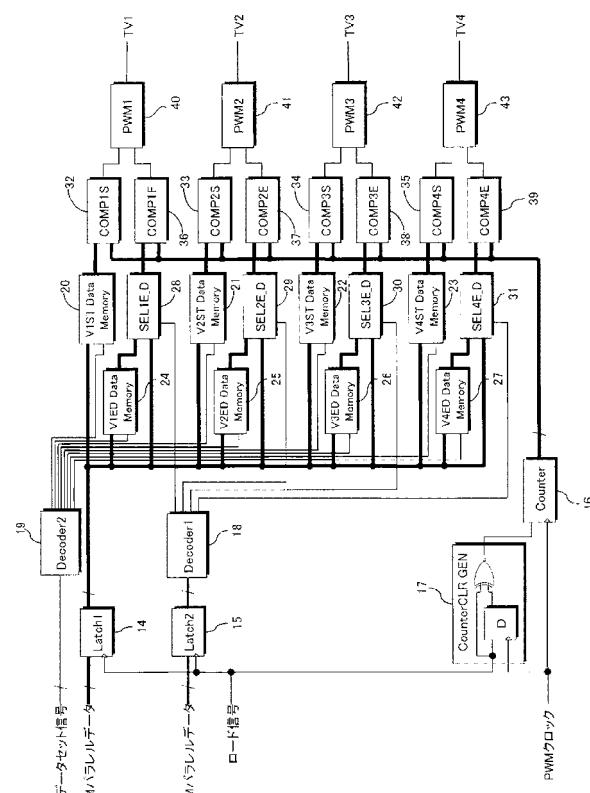

【 0 0 6 4 】

ここで示す実施形態のように、変調信号の振幅方向の制御と時間幅方向の制御との両方を行って変調信号を発生させる構成においては、種々の複雑な変調信号波形を発生させることができる。例えば、変調信号のパルス全体の時間幅の単位時間（クロック信号をカウントすることで時間幅を設定する構成においてはカウントの対象となるクロック信号の一周期がこれに相当する。）毎に個別に波高値制御すべく波高値データを各単位時間に対応させて発生させる構成も採用できる。しかしこのような複雑な構成をとる必要はない。具体的には、波高値データであるPHMデータとしては、一つの変調信号の波形のうちの少なくとも一点の波高値を要求される明るさに対応して規定できる情報を含んでいればよい。具体的には、少なくとも一点の波高値を規定する情報としては、変調信号における最大波高値を特定する情報を好適に採用できる。なお波高値の大小は電位の大小とは限らない。例えば走査信号の選択電位が変調信号のオン状態に対応する電位よりも高い電位である場合は、変調信号の波高値は、電位が低い方が大きいことになる。

〔 0 0 6 5 〕

またタイミングデータである PWMデータとしては、例えば、変調信号の波形の各波高値の部分夫々の遷移タイミング（ある波高値に制御されている状態から他の波高値に遷移するための制御を開始するタイミング）を規定する情報を全て含む構成にすることもできる。しかしこのような複雑な構成をとる必要はない。具体的には、タイミングデータである PWMデータとしては、変調信号の信号レベルを他のレベルに遷移させるタイミングを、要求される明るさに対応して少なくとも 1箇所規定できる情報を含んでいればよい。具体的には、ある変調信号において、その変調信号が使用する波高値のうちの最大の波高値からより小さい波高値に遷移させるタイミングを規定できるデータをタイミングデータとして用いる構成を好適に採用できる。なおデータに基づくタイミングの規定の方法は種々のものを採用できる。基準時点からの経過時間を計時する構成を採用し、タイミングデータがその計時時間を直接若しくは間接的に指定する構成を好適に採用できる。具体的には計時はクロックのカウントによって行う構成を好適に採用できる。この場合計時時間の指定はカウント数を直接若しくは間接的に指定することで行うことができる。

( 0 0 6 6 )

この第1の実施形態によるPWM回路10は、ラッチ回路として、PWMパラレルデータ用ラッチ回路14およびPHMパラレルデータ用ラッチ回路15を有している。また、このPWM回路10には、カウンタ関連の回路として、カウンタ回路16およびカウンタクリア信号発生回路17が設けられている。なお、この第1の実施形態においては、カウンタクリア信号発生回路17をDフリップフロップ回路とXOR回路とを用いて構成しているが、この回路構成は、あくまでも一例であり、必ずしもこの回路構成に限定されるものではない。

【 0 0 6 7 】

また、 PWM回路 10 は、デコード回路として、PHMデータデコード回路 18 および初期データセット信号デコード回路 19 が設けられ、記憶回路として、V1スタートデータ記憶回路 20 、V2スタートデータ記憶回路 21 、V3スタートデータ記憶回路 22 、V4スタートデータ記憶回路 23 、V1エンドデータ記憶回路 24 、V2エンドデータ記憶回路 25 、V3エンドデータ記憶回路 26 、および V4 エンドデータ記憶回路 27 が設けられている。

[ 0 0 6 8 ]

また、PWM回路10は、エンドデータ選択回路として、V1エンドデータ選択回路28、V2エンドデータ選択回路29、V3エンドデータ選択回路30、およびV4エンドデータ選択回路31を有し、データ比較回路として、V1スタートデータ比較器32、V2スタートデータ比較器33、V3スタートデータ比較器34、V4スタートデータ比較器35、V1エンドデータ比較器36、V2エンドデータ比較器37、V3エンドデータ比較器38およびV4エンドデータ比較器39を有している。

**【 0 0 6 9 】**

また、P W M回路1 0は、パルス幅発生回路として、V 1パルス幅発生回路4 0、V 2パルス幅発生回路4 1、V 3パルス幅発生回路4 2およびV 4パルス幅発生回路4 3を有している。

**【 0 0 7 0 】**

次に、以上のように構成されたこの第1の実施形態によるP W M回路1 0について説明する。

**【 0 0 7 1 】**

まず、P W Mパラレルデータ用ラッチ回路1 4は、シフトレジスタ9内の第2の記憶回路1 3 bに記録されたマルチ電子源1の列方向配線に応じた変調データであるP W Mパラレルデータを、タイミング発生回路4により発生されたタイミング信号の一つであるロード信号のタイミングに応じてラッチするための回路である。10

**【 0 0 7 2 】**

また、P H Mパラレルデータ用ラッチ回路1 5は、シフトレジスタ9内の第1の記憶回路1 3 aに記録されたマルチ電子源1の列方向配線に応じた変調データであるP H Mパラレルデータを、タイミング発生回路4により発生されたタイミング信号の一つであるロード信号のタイミングに応じてラッチするための回路である。

**【 0 0 7 3 】**

また、カウンタ回路1 6は、タイミング発生回路4により発生されたタイミング信号の一つであるP W Mクロックと、カウンタクリア信号発生回路1 7により発生されたカウンタクリア信号とに基づいて、内部タイミングを規定するカウントデータを、V 1スタートデータ比較器3 2、V 1スタートデータ比較器3 2、V 2スタートデータ比較器3 3、V 3スタートデータ比較器3 4、V 4スタートデータ比較器3 5、V 1エンドデータ比較器3 6、V 2エンドデータ比較器3 7、V 3エンドデータ比較器3 8およびV 4エンドデータ比較器3 9に出力するための回路である。20

**【 0 0 7 4 】**

また、カウンタクリア信号発生回路1 7は、タイミング発生回路4により発生されたタイミング信号の一つであるロード信号とP W Mクロックとから、内部タイミングを規定するカウンタのクリア信号を発生するための回路である。

**【 0 0 7 5 】**

P H Mデータデコード回路1 8は、P H Mパラレルデータ用ラッチ回路1 5によってラッチされたP H Mパラレルデータに応じて、V 1エンドデータ選択回路2 8、V 2エンドデータ選択回路2 9およびV 3エンドデータ選択回路3 0の選択信号を発生するデコード回路である。30

**【 0 0 7 6 】**

この第1の実施形態においては、2ビットのP H Mパラレルデータに応じて4つの選択信号が発生される。すなわち、P H Mデータ=“0 0”的場合には、V 1エンドデータ選択回路2 8の選択信号に“1”が入力され、そのほかの選択回路の選択信号は“0”となる。ここで、“0 0”は、バイナリ表示の数値を示す。また、P H Mデータ=“0 1”的場合は、V 2エンドデータ選択回路2 9の選択信号に“1”が入力され、他の選択回路の選択信号は、“0”となる。また、P H Mデータ=“1 0”的場合はV 3エンドデータ選択回路3 0の選択信号に“1”が入力され、他の選択回路の選択信号は“0”となる。P H Mデータ=“1 1”的場合はV 4エンドデータ選択回路3 1の選択信号に“1”が入力され、他の選択回路の選択信号は“0”となる。40

**【 0 0 7 7 】**

また、P W M回路1 0における初期データセット信号デコード回路1 9は、タイミング発生回路4において発生されたタイミング信号の一つである初期データセット信号に応じて、V 1スタートデータ記憶回路2 0、V 2スタートデータ記憶回路2 1、V 3スタートデータ記憶回路2 2、V 4スタートデータ記憶回路2 3、V 1エンドデータ記憶回路2 4、V 2エンドデータ記憶回路2 5、V 3エンドデータ記憶回路2 6およびV 4エンドデータ記憶回路2 7の選択信号に応じて、V 1エンドデータ選択回路2 8、V 2エンドデータ選択回路2 9およびV 3エンドデータ選択回路3 0の選択信号を発生するデコード回路である。50

タ記憶回路 27 に、 PWM パラレルデータ用ラッチ回路 14 によってラッチされた PWM データを記録するための書き込み信号を発生するデコード回路である。

#### 【 0078 】

この第 1 の実施形態においては、 3 ビットの初期データセット信号に応じて 8 本の選択信号が発生される。

#### 【 0079 】

すなわち、初期データセット信号 = "000" の場合、V1 スタートデータ記憶回路 20 の書き込み信号だけがオンになり、PWM パラレルデータ用ラッチ回路 14 によりラッチされた V1 への波高値遷移（波高値を大きくする方向の遷移）を開始する位置を指定するデータ（V1 スタートデータ：これは PWM データと同じ経路で予め与えら得るタイミング指定用データである）が、V1 スタートデータ記憶回路 20 に記録される。10

#### 【 0080 】

初期データセット信号 = "001" の場合、V2 スタートデータ記憶回路 21 の書き込み信号だけがオンになり、PWM パラレルデータ用ラッチ回路 14 によりラッチされた V2 への波高値遷移（波高値を大きくする方向の遷移）を開始する位置を指定するデータ（V2 スタートデータ：これは PWM データと同じ経路で予め与えられるタイミング指定用データである）が、V2 スタートデータ記憶回路 21 に記録される。

#### 【 0081 】

初期データセット信号 = "010" の場合、V3 スタートデータ記憶回路 22 の書き込み信号だけがオンになり、PWM パラレルデータ用ラッチ回路 14 によりラッチされた V3 への波高値遷移（波高値を大きくする方向の遷移）を開始する位置を指定するデータ（V3 スタートデータ：これは PWM データと同じ経路で予め与えられるタイミング指定用データである）が V3 スタートデータ記憶回路 22 に記録される。20

#### 【 0082 】

初期データセット信号 = "011" の場合、V4 スタートデータ記憶回路 23 の書き込み信号だけがオンになり、PWM パラレルデータ用ラッチ回路 14 によりラッチされた V4 への波高値遷移（波高値を大きくする方向の遷移）を開始する位置を指定するデータ（V4 スタートデータ：これは PWM データと同じ経路で予め与えられるタイミング指定用データである）が V4 スタートデータ記憶回路 23 に記録される。

#### 【 0083 】

初期データセット信号 = "100" の場合、V1 エンドデータ記憶回路 24 の書き込み信号だけがオンになり、PWM パラレルデータ用ラッチ回路 14 によりラッチされた V1 からより低い波高値への遷移を開始する位置を指定するデータ（V1 エンドデータ：これは PWM データと同じ経路で予め与えられるタイミング指定用データである）が V1 エンドデータ記憶回路 24 に記録される。30

#### 【 0084 】

初期データセット信号 = "101" の場合、V2 エンドデータ記憶回路 25 の書き込み信号だけがオンになり、PWM パラレルデータ用ラッチ回路 14 によりラッチされた V2 からより低い波高値への遷移を開始する位置を指定するデータ（V2 エンドデータ：これは PWM データと同じ経路で予め与えられるタイミング指定用データである）が V2 エンドデータ記憶回路 25 に記録される。40

#### 【 0085 】

初期データセット信号 = "110" の場合、V3 エンドデータ記憶回路 26 の書き込み信号だけがオンになり、PWM パラレルデータ用ラッチ回路 14 によりラッチされた V3 からより低い波高値への遷移を開始する位置を指定するデータ（V3 エンドデータ：これは PWM データと同じ経路で予め与えられるタイミング指定用データである）が V3 エンドデータ記憶回路 26 に記録される。

#### 【 0086 】

初期データセット信号 = "111" の場合、V4 エンドデータ記憶回路 27 の書き込み信号だけがオンになり、PWM パラレルデータ用ラッチ回路 14 によりラッチされた V4 から50

より低い波高値への遷移を開始する位置を指定するデータ（V4エンドデータ：これはPWMデータと同じ経路で予め与えられるタイミング指定用データである）がV4エンドデータ記憶回路27に記録される。

#### 【0087】

これらのスタート位置指定データ及びエンド位置指定データが記録されるデータ記憶回路20～27に、装置起動時を含む画像非表示期間中に、駆動波形を形成するための上述のパラメータ（V1スタートデータ、V2スタートデータ、V3スタートデータ、V4スタートデータ、V1エンドデータ、V2エンドデータ、V3エンドデータおよびV4エンドデータ）が順次転送される。これにより、データ記憶回路20～27に、パラメータ（V1スタートデータ、V2スタートデータ、V3スタートデータ、V4スタートデータ、V1エンドデータ、V2エンドデータ、V3エンドデータおよびV4エンドデータ）が記録される。10

#### 【0088】

また、PWM回路10におけるV1エンドデータ選択回路28は、PWMパラレルデータ用ラッチ回路14によりラッチされたPWMデータとV1エンドデータ記憶回路24に記録されたV1エンドデータとのいずれかを選択する選択回路である。この選択は、PHMデータデコード回路18から出力されるPHMデータに応じた選択信号により実行される。

#### 【0089】

また、V2エンドデータ選択回路29は、PHMデータデコード回路18から出力されるPHMデータに応じた選択信号により、PWMパラレルデータ用ラッチ回路14によりラッチされたPWMデータと、V2エンドデータ記憶回路25に記録されたV2エンドデータとのいずれかを選択する選択回路である。20

#### 【0090】

同様に、V3エンドデータ選択回路30は、PHMデータデコード回路18から出力されるPHMデータに応じた選択信号により、PWMパラレルデータ用ラッチ回路14によってラッチされたPWMデータとV3エンドデータ記憶回路26に記録されたV3エンドデータとのいずれかを選択する選択回路である。

#### 【0091】

また、同様に、V4エンドデータ選択回路31は、PHMデータデコード回路18から出力されるPHMデータに応じた選択信号により、PWMパラレルデータ用ラッチ回路14によりラッチされたPWMデータとV4エンドデータ記憶回路26に記録されたV4エンドデータとのいずれかを選択する選択回路である。30

#### 【0092】

V1からV4エンドデータ選択回路は、選択信号が“1”的場合に、PWMデータを選択し、選択信号が“0”的場合に、対応するエンドデータ記憶回路に記憶されたエンドデータを選択する。

#### 【0093】

また、V1スタートデータ比較器32は、V1スタートデータ記憶回路20に記録されたV1スタートデータと、内部タイミングを規定するカウンタ回路16のカウントデータとが一致したときに、V1スタートパルスを発生するための比較器である。V2スタートデータ比較器33は、V2スタートデータ記憶回路21に記録されたV2スタートデータと、カウンタ回路16のカウントデータとが一致したときに、V2スタートパルスを発生するための比較器である。V3スタートデータ比較器34は、V3スタートデータ記憶回路22に記録されたV3スタートデータと、カウンタ回路16のカウントデータとが一致したときに、V3スタートパルスを発生する比較器である。V4スタートデータ比較器35は、V4スタートデータ記憶回路23に記録されたV4スタートデータと、カウンタ回路16のカウントデータとが一致したときに、V4スタートパルスを発生する比較器である。40

#### 【0094】

10

20

30

40

50

また、V1エンドデータ比較器36は、V1エンドデータ選択回路28により選択されたV1エンドデータまたはPWMデータと、カウンタ回路16のカウントデータとが一致したときに、V1エンドパルスを発生する比較器である。V2エンドデータ比較器37は、V2エンドデータ選択回路29により選択されたV2エンドデータもしくはPWMデータと、カウンタ回路16のカウントデータとが一致したときに、V2エンドパルスを発生する比較器である。V3エンドデータ比較器38は、V3エンドデータ選択回路30により選択されたV3エンドデータまたはPWMデータと、カウンタ回路16のカウントデータとが一致したときに、V3エンドパルスを発生する比較器である。V4エンドデータ比較器39は、V4エンドデータ選択回路31により選択されたV4エンドデータまたはPWMデータと、カウンタ回路16のカウントデータとが一致したときに、V4エンドパルスを発生する比較器である。10

#### 【0095】

また、V1パルス幅発生回路40は、パルス幅波形TV1を出力するPWM回路である。パルス幅波形TV1は、V1スタートデータ比較器32において発生されたV1スタートパルスで立ち上がり、V1エンドデータ比較器36において発生されたV1エンドパルスで立ち下がる波形である。

#### 【0096】

また、V2パルス幅発生回路41は、パルス幅波形TV2を出力するPWM回路である。パルス幅波形TV2は、V2スタートデータ比較器33において発生されたV2スタートパルスで立ち上がり、V2エンドデータ比較器37において発生されたV2エンドパルスで立ち下がる波形である。20

#### 【0097】

また、V3パルス幅発生回路42は、パルス幅波形TV3を出力するPWM回路である。このパルス幅波形TV3は、V3スタートデータ比較器34において発生されたV3スタートパルスで立ち上がり、V3エンドデータ比較器38において発生されたV3エンドパルスで立ち下がる波形である。

#### 【0098】

また、V4パルス幅発生回路43は、パルス幅波形TV4を出力するPWM回路である。このパルス幅波形TV4は、V4スタートデータ比較器35において発生されたV4スタートパルスで立ち上がり、V4エンドデータ比較器39において発生されたV4エンドパルスで立ち下がるパルス幅波形である。30

#### 【0099】

なお、この第1の実施形態においては、PWM回路として、RSフリップフロップ回路における、セット入力にスタートパルスを入力し、リセット入力にエンドパルスを入力する回路を採用しているが、必ずしもこのような構成に限定されるものではない。

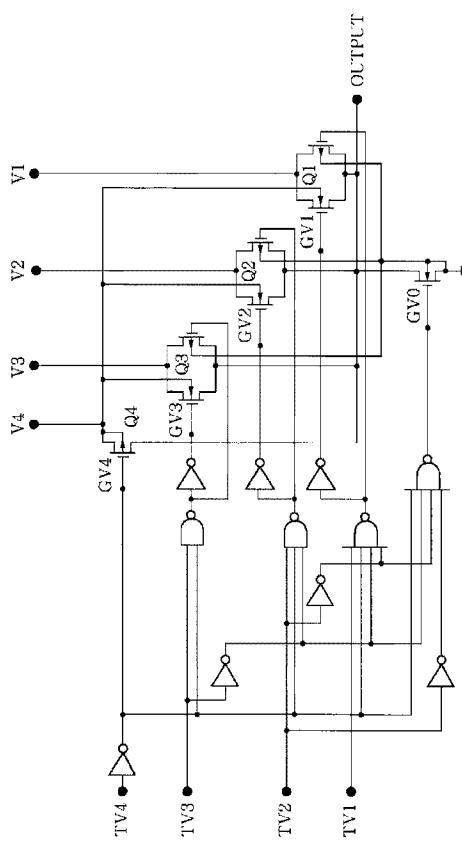

#### 【0100】

また、図7に示すように、電位V1～V4は、 $0 < V1 < V2 < V3 < V4$ であり、それぞれPWM出力波形TV1、TV2、TV3およびTV4に対応して出力される。また、トランジスタQ1、Q2、Q3およびQ4は、オンすることによりそれぞれ電位V1～V4を出力端子OUTPUTに出力可能に構成されている。なお、トランジスタQ1～Q4については、ペアトランジスタにより構成することも可能である。40

#### 【0101】

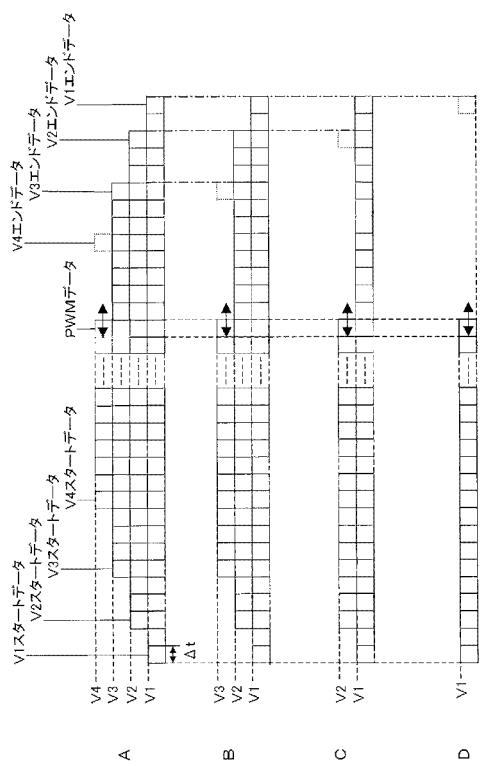

次に、以上のように構成された変調回路2の出力端子OUTPUTから出力される駆動波形について、図8を参照しつつ説明する。

#### 【0102】

図8Aに、PHMデータ＝”11”的場合において、電位V1～V4を用いた駆動波形を示す。図8Aに示すように、電位V1の立ち上がり位置については、V1スタートデータ記憶回路20に記憶されたV1スタートデータにより規定される。また、電位V2の立ち上がり位置は、V2スタートデータ記憶回路21に記憶されたV2スタートデータにより規定される。また、電位V3の立ち上がり位置は、V3スタートデータ記憶回路22に50

記憶されたV3スタートデータにより規定され、電位V4の立ち上がり位置がV4スタートデータ記憶回路23に記憶されたV4スタートデータにより規定される。

#### 【0103】

他方、電位V1の立ち下がり位置については、V1エンドデータ記憶回路24に記憶されたV1エンドデータにより規定され、電位V2の立ち下がり位置がV2エンドデータ記憶回路25に記憶されたV2エンドデータにより規定され、電位V3の立ち下がり位置はV3エンドデータ記憶回路26に記憶されたV3エンドデータにより規定され、電位V4の立ち下がり位置はPWMデータにより規定される。

#### 【0104】

図8Bに、PHMデータ="10"の場合において、電位V1~V3まで使用した駆動波形を示す。 10

#### 【0105】

図8Bに示すように、電位V1の立ち上がり位置はV1スタートデータ記憶回路20に記憶されたV1スタートデータにより規定され、電位V2の立ち上がり位置は、V2スタートデータ記憶回路21に記憶されたV2スタートデータにより規定され、電位V3の立ち上がり位置は、V3スタートデータ記憶回路22に記憶されたV3スタートデータにより規定される。

#### 【0106】

他方、電位V1の立ち下がり位置は、V1エンドデータ記憶回路24に記憶されたV1エンドデータにより規定され、電位V2の立ち下がり位置は、V2エンドデータ記憶回路25に記憶されたV2エンドデータにより規定され、電位V3の立ち下がり位置は、PWMデータにより規定される。 20

#### 【0107】

また、図8Cに、PHMデータ="01"の場合において、電位V1とV2を使用した駆動波形を示す。

#### 【0108】

図8Cに示すように、電位V1の立ち上がり位置は、V1スタートデータ記憶回路20に記憶されたV1スタートデータにより規定され、電位V2の立ち上がり位置は、V2スタートデータ記憶回路21に記憶されたV2スタートデータにより規定され、電位V1の立ち下がり位置は、V1エンドデータ記憶回路24に記憶されたV1エンドデータにより規定され、電位V2の立ち下がり位置は、PWMデータにより規定される。 30

#### 【0109】

図8Dに、PHMデータ="01"の場合において、電位V1を使用した駆動波形を示す。図8Dに示すように、電位V1の立ち上がり位置は、V1スタートデータ記憶回路20に記憶されたV1スタートデータにより規定され、電位V1の立ち下がり位置は、PWMデータにより規定される。

#### 【0110】

以上から明らかなように、本実施形態においては、各階調データに対応する変調信号は、それぞれの最大波高値に制御される部分のパルス幅が階調データを構成するタイミングデータ(PWMデータ)で決まる(変調される)ことになる。各変調信号のその他の部分(最大波高値に制御される部分以外の部分)の形状は、V1スタートデータ、V2スタートデータ、V3スタートデータ、V4スタートデータ、V3エンドデータ、V2エンドデータ、V1エンドデータによって階調データに依らずに決定することができる。ただし、変調信号のどの部分のパルス幅を階調データに対応づけて決定するかは、この構成に限るものではない。本実施形態では、2番目以降の波高値(前記V2、V3、V4に相当)を用いる変調信号においては、変調信号の立ち上がりの部分と立ち下がりの部分において、波高値が基準レベルから直接その変調信号における最大波高値まで立ち上がらないように途中の波高値を経由させている。これによって変調信号の印加によって生じるリンクギングが抑制できる。具体的には変調信号の立ち上がり部分と立ち下がり部分が階段形状になるように構成しており、これは、V1スタートデータ、V2スタートデータ、V3スタート 40

データ、V4スタートデータ、V3エンドデータ、V2エンドデータ、V1エンドデータを階段形状が得られるタイミングに設定することで実現している。

#### 【0111】

以上説明したように、この第1の実施形態による表示素子の駆動回路によれば、PWMデータとPHMデータとを、それぞれを構成するデータビットのビット数より少ない伝送経路（伝送線）により変調回路2に伝送するようにシリアル化していることにより、振幅変調とパルス幅変調とを併用した変調を行うための異なる属性を有する2種類のデータを、構成において伝送線数を大幅に増やすことなく伝送することが可能となる。

#### 【0112】

特にこの実施形態においては、パラレル／シリアル変換回路から変調回路に階調データを伝送する伝送経路のいずれにおいても、属性の異なるデータである波高値データとタイミングデータとを混在させないようにしている。そのため、パラレル／シリアル変換回路から変調回路に階調データを伝送した後で、波高値データとタイミングデータとを分離するための構成を設けなくてもよいというメリットがある。

#### 【0113】

##### （第2の実施形態）

次に、この発明の第2の実施形態について説明する。なお、この第2の実施形態による駆動回路の概略は、第1の実施形態におけると同様である。すなわち、図1に示すように、この第2の実施形態による駆動装置は、変調回路2、走査回路3、タイミング発生回路4、データ変換回路5、パラレル／シリアル変換回路6、マルチ電源回路7および走査電源回路8を有して構成され、マルチ電子源1を駆動する回路である。

#### 【0114】

また、走査回路3は、マルチ電子源1の行方向配線に接続され、変調回路2の出力をマルチ電子源1のいずれの行に信号を供給するかを選択するための回路である。そして、一般的には、一行ずつ順次行選択するようにした線順次走査が実行されるが、必ずしも線順次走査に限定されるものではなく、飛び越し走査や、複数行を同時に選択したり、面状に選択したりすることも可能である。すなわち、走査回路3は、マルチ電子源1に含まれる複数電子源のうちの駆動対象となる複数の電子源が接続される行方向配線に対して所定時間選択電位を供給し、その他の時間に非選択電位を供給することにより、行選択を行う選択手段である。なお、以下に説明する変調回路2およびこの変調回路2にシリアルデータの供給する周辺回路以外の回路構成については、第1の実施形態におけると同様であるので、その説明を省略する。

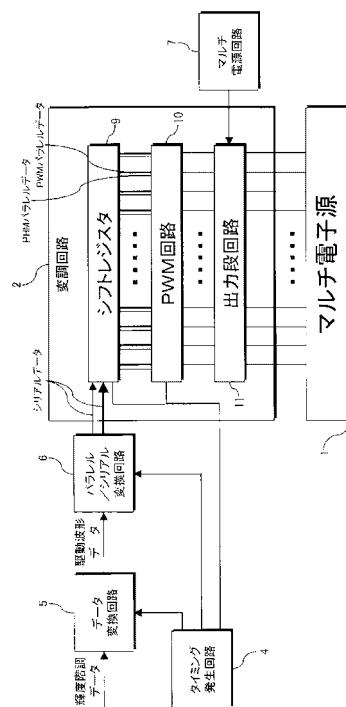

#### 【0115】

次に、この発明の第2の実施形態による変調回路2およびシリアルデータの供給について説明する。図9に、変調回路2の内部構成および、変調回路2にシリアルデータを供給する周辺回路を示す。図9に示すように、この第2の実施形態による変調回路2は、第1の実施形態におけると同様に、シフトレジスタ9、PWM回路10および出力段回路11を有して構成されている。なお、出力段回路11は、マルチ電源回路7に接続され、後述する駆動波形を有する変調信号を出力するための回路である。

#### 【0116】

データ変換回路5は、外部からマルチ電子源1の輝度階調制御する輝度階調データを変調回路2に適した駆動波形データフォーマットにデータ変換を行うための回路である。

#### 【0117】

パラレル／シリアル変換回路6は、データ変換回路5から供給された輝度階調データを、PHMデータおよびPWMデータのいずれのデータの属性に関わらず、一律のパラレルデータとして取り扱い、そのパラレルデータをシリアル差動データに変換する回路である。この第2の実施形態においては、差動データの場合を例にして説明するが、必ずしも差動データに限定されるものではなく、具体的に、例えば、シングルエンドデータや擬似差動データなどを利用することも可能である。

#### 【0118】

10

20

30

40

50

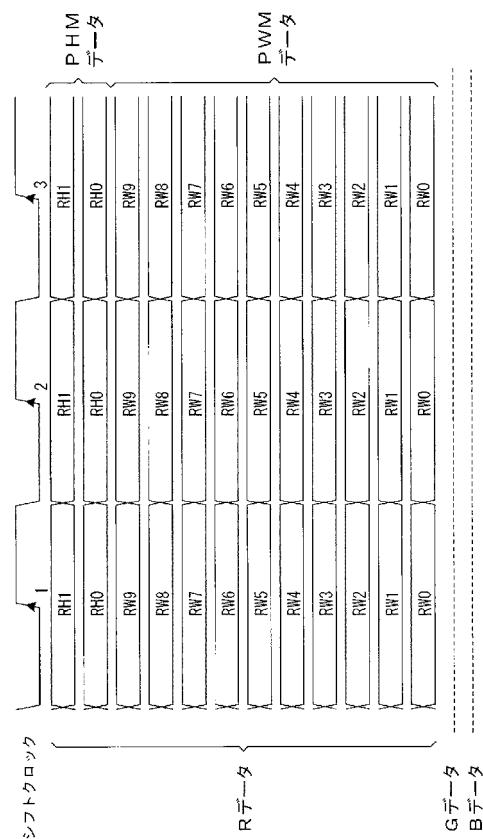

次に、図2および図10を用いて、パラレル／シリアル変換回路6に入力されるデータフォーマット、およびパラレル／シリアル変換回路6から出力されるデータフォーマットについて説明をする。なお、パラレル／シリアル変換回路に入力される駆動波形データのフォーマットは、第1の実施形態におけると同様であるので、説明を省略する。図10に、本実施形態のパラレル／シリアル変換回路から出力される駆動波形データのフォーマットを示す。

#### 【0119】

すなわち、図2に示すように、第2の実施形態による駆動波形データは、第1の実施形態におけると同様に、RGBでそれぞれ個別に、2ビットのPHMデータと10ビットのPWMデータとがパラレルに構成されたデータフォーマットである。そして、この駆動波形データは、タイミング発生回路4からデータ変換回路5に供給されるタイミング信号の1つであるシフトクロック1に同期されている。なお、この第2の実施形態においては、PHMデータを2ビット、PWMデータを10ビットとした場合を例に説明するが、必ずしも10ビットに限定されるものではなく、それ以外のビット数を採用することも可能である。

10

#### 【0120】

図10に示すように、この第2の実施形態によるシリアルデータは、タイミング発生回路4から発生されたタイミング信号の1つであるシフトクロック2に同期されて、PHMデータおよびPWMデータのいずれであるかというデータの属性とは無関係に、一律のデータとして4ビットごとにデータをシリアル化したデータフォーマットである。なお、この第2の実施形態においては、シフトクロックの立ち上がりと立ち下がりとの両エッジにおいて、トリガをかける構成を採用しているが、必ずしも、このような構成に限定されるものではない。さらに、この第2の実施形態においては、データビット数が4の倍数となる値（4で割り切れる値）としているが、データビット数が4で割り切れない場合、すなわち、データ非伝送時間が生じる場合には、4ビットに足りないデータに、疑似データとしてのダミーデータが充填されて出力される。

20

#### 【0121】

また、図9に示すように、変調回路2は、マルチ電子源1の列方向配線に接続されている。この変調回路2は、パラレル／シリアル変換回路6によってPHMデータとPWMデータとが一律にシリアル変換された変調データ（階調データ）に応じて、マルチ電子源1に変調信号を供給するための回路である。すなわち、この変調回路2は、パラレル／シリアル変換回路6から入力された変調データに基づいて、変調された変調信号を複数の電子源にそれぞれ接続する列方向配線に与える変調手段として機能する。

30

#### 【0122】

次に、この第2の実施形態による変調回路2に設けられるシフトレジスタ9について説明する。図11に、この第2の実施形態によるシフトレジスタ9の内部構成を示す。

#### 【0123】

図11に示すように、この第2の実施形態によるシフトレジスタ9には、パラレル／シリアル変換回路6によってシリアル変換されたPHMシリアルデータおよびPWMシリアルデータが入力される。また、シフトレジスタ9からは、マルチ電子源1の列方向配線に応じた変調データであるPHMパラレルデータおよびPWMパラレルデータが出力される。図10に示すように、一つの表示素子を1つの選択期間の間変調するための変調信号を発生するのに用いるデータは、パラレル／シリアル変換回路6に並列数12のパラレルデータとして入力され、並列数3、時系列方向のビット数4のフォーマットにシリアル変換される。すなわち図11に示すシフトレジスタ9には3系統（並列数3）の信号がシリアルデータとして入力されている。

40

#### 【0124】

シフトレジスタ9から出力された変調データとしてのPHMパラレルデータおよびPWMパラレルデータは、PWM回路10に供給される。このPWM回路10は、出力段回路11において、それぞれの出力電圧に応じた出力を発生させるための回路である。また、

50

タイミング発生回路 4 からは、シフトレジスタ 9 および PWM 回路 10 を制御するためのタイミング信号が供給される。

#### 【 0 1 2 5 】

また、図 11 に示すように、この第 2 の実施形態によるシフトレジスタ 9 は、複数の制御回路 52 および複数の記憶回路 53 を有して構成される。なお、この第 2 の実施形態においては、制御回路 52 および記憶回路 53 を、D フリップフロップ回路、RS フリップフロップ回路およびオアゲート回路を用いて構成する場合を例として説明するが、必ずしもこのような回路構成に限定されるものではない。

#### 【 0 1 2 6 】

記憶回路 53a、記憶回路 53b、記憶回路 53c、はそれぞれシリアル化された 3 系統のデータをパラレルデータに変換する回路を構成する。記憶回路 53b、記憶回路 53c には、PHM データと PWM データが混在しない 2 系統のシリアルデータがそれぞれ入力される。シリアルデータは記憶素子であるフリップフロップで転送され、所定のタイミングでパラレルデータとして出力される。記憶回路 53a には、パラレル / シリアル変換回路 6 で一律にシリアル変換された PHM データおよび PWM データを内包したシリアルデータの中で、特に PHM データと PWM データとがシリアルに混在されたデータが入力される。記憶回路 53a では記憶素子であるフリップフロップが 4 つ直列に接続されている。各フリップフロップは入力されるデータビットを記憶すると共に、次段のフリップフロップに記憶していたデータビットを入力する。この 4 つのフリップフロップによって 4 ビットのシリアルデータを保持する。そのうちの 2 ビットのデータを PHM データとして出力し、他の 2 ビットを PWM データとして出力する。記憶回路 53a が出力する 2 ビットの PWM データは、記憶回路 53b が出力する 4 ビットの PWM データ、及び記憶回路 53c が出力する 4 ビットの PWM データと共に 10 ビットの PWM パラレルデータを構成するデータとなる。これによってマルチ電子源 1 の列方向配線に応じた変調データである PHM パラレルデータと PWM パラレルデータとが PWM 回路 10 に出力される。

#### 【 0 1 2 7 】

また、制御回路 52 には、タイミング発生回路 4 により発生されたタイミング信号の一つである、シフトスタートパルスとシフトクロックとが供給される。この制御回路 52 は、マルチ電子源 1 の列方向配線に応じた変調データである PHM シリアルデータおよび PWM データを一律に記憶回路 53 に記録するための制御信号を発生する回路である。ここで、シフトパルスは、タイミング発生回路 4 において発生されたタイミング信号の 1 つである差動シフトクロックから形成されたクロックである。そして、このクロックの立ち上がりと立ち下がりとの両エッジのタイミングにおいてデータが転送される構成が採用されている。

#### 【 0 1 2 8 】

そして、制御回路 52 により発生された記録制御信号に応じて、シリアルデータが記憶回路 53 に記録される。記憶回路 53 から出力される出力データは、パラレルに構成されている。この出力データは、マルチ電子源 1 の列方向配線に応じて、一括して PWM 回路 10 に供給される。

#### 【 0 1 2 9 】

以上のようにして、この第 2 の実施形態による表示素子の駆動回路が構成されている。

#### 【 0 1 3 0 】

この第 2 の実施形態による画像表示装置の駆動回路によれば、第 1 の実施形態と同様の効果を得ることができるとともに、構成においても伝送線数を大幅に増やすことなく、振幅変調とパルス幅変調とを併用した 2 つの属性のデータを伝送することが可能となる。特にこの第 2 の実施形態においては、波高値データとタイミングデータとを分別して出力できる記憶回路を変調回路が有するように構成することで、波高値データとタイミングデータを混在させてシリアル化することが可能になっている。これによってダミーデータを不要にする、もしくは必要なダミーデータを減らすことができる。

#### 【 0 1 3 1 】

10

20

30

40

50

以上、この発明の実施形態について具体的に説明したが、この発明は、上述の実施形態に限定されるものではなく、この発明の技術的思想に基づく各種の変形が可能である。

### 【0132】

例えば、上述の実施形態において挙げた PWM回路、シフトレジスタ、出力段回路、PHMデータおよびPWMデータの構成はあくまでも例に過ぎず、必要に応じてこれと異なる構成を採用することも可能である。

### 【0133】

以上説明したように、この発明によれば、波高値およびパルス幅が変調された変調信号を決定する波高値データビットとパルス幅データビットとをシリアル化することにより、伝送経路や伝送線の数の低減化を図ることができるので、階調数が増加した場合であっても、伝送するためのデータ線数の増加を抑制することが可能となる。 10

### 【図面の簡単な説明】

#### 【0134】

【図1】この発明の第1の実施形態による駆動回路のブロック図である。

【図2】この発明の第1の実施形態による変調回路におけるパラレル／シリアル変換回路に入力される変調信号データのフォーマットを示す略線図である。

【図3】この発明の第1の実施形態による変調回路におけるパラレル／シリアル変換回路から出力されるシリアルデータのフォーマットを示す略線図である。

【図4】この発明の第1の実施形態による駆動回路における変調回路のブロック図である。 20

【図5】この発明の第1の実施形態による変調回路におけるシフトレジスタのブロック図である。

【図6】この発明の第1の実施形態による変調回路におけるPWM回路のブロック図である。

【図7】この発明の第1の実施形態による変調回路における出力段回路のブロック図である。

【図8】この発明の第1の実施形態による変調回路における出力段回路の出力駆動波形の一例を示す波形図である。

【図9】この発明の第2の実施形態による駆動回路における変調回路のブロック図である。 30

【図10】この発明の第2の実施形態による変調回路におけるパラレル／シリアル変換回路から出力されるシリアルデータのフォーマットを示す略線図である。

【図11】この発明の第2の実施形態による駆動回路の変調回路におけるシフトレジスタのブロック図である。

【図12】本発明に係るテレビジョン装置のブロック図である。

### 【符号の説明】

#### 【0135】

- 1 マルチ電子源

- 2 変調回路

- 3 走査回路

- 4 タイミング発生回路

- 5 データ変換回路

- 6 シリアル変換回路

- 7 マルチ電源回路

- 8 走査電源回路

- 9 シフトレジスタ

- 10 PWM回路

- 11 出力段回路

- 12, 52 制御回路

- 13, 53 記憶回路

10

20

30

40

50

|                               |                     |    |

|-------------------------------|---------------------|----|

| 1 4                           | P W M パラレルデータ用ラッチ回路 |    |

| 1 5                           | P H M パラレルデータ用ラッチ回路 |    |

| 1 6                           | カウンタ回路              |    |

| 1 7                           | カウンタクリア信号発生回路       |    |

| 1 8                           | データデコード回路           |    |

| 1 9                           | 初期データセット信号デコード回路    |    |

| 2 0                           | V 1 スタートデータ記憶回路     |    |

| 2 1                           | V 2 スタートデータ記憶回路     |    |

| 2 2                           | V 3 スタートデータ記憶回路     |    |

| 2 3                           | V 4 スタートデータ記憶回路     | 10 |

| 2 4                           | V 1 エンドデータ記憶回路      |    |

| 2 5                           | V 2 エンドデータ記憶回路      |    |

| 2 6                           | V 3 エンドデータ記憶回路      |    |

| 2 7                           | V 4 エンドデータ記憶回路      |    |

| 2 8                           | V 1 エンドデータ選択回路      |    |

| 2 9                           | V 2 エンドデータ選択回路      |    |

| 3 0                           | V 3 エンドデータ選択回路      |    |

| 3 1                           | V 4 エンドデータ選択回路      |    |

| 3 2                           | V 1 スタートデータ比較器      |    |

| 3 3                           | V 2 スタートデータ比較器      | 20 |

| 3 4                           | V 3 スタートデータ比較器      |    |

| 3 5                           | V 4 スタートデータ比較器      |    |

| 3 6                           | V 1 エンドデータ比較器       |    |

| 3 7                           | V 2 エンドデータ比較器       |    |

| 3 8                           | V 3 エンドデータ比較器       |    |

| 3 9                           | V 4 エンドデータ比較器       |    |

| 4 0                           | V 1 パルス幅発生回路        |    |

| 4 1                           | V 2 パルス幅発生回路        |    |

| 4 2                           | V 3 パルス幅発生回路        |    |

| 4 3                           | V 4 パルス幅発生回路        | 30 |

| O U T P U T 出力端子              |                     |    |

| Q 1 , Q 2 , Q 3 , Q 4         | トランジスタ              |    |

| T V 1 , T V 2 , T V 3 , T V 4 | パルス幅波形              |    |

| V 1 ~ V 4                     | 電位                  |    |

| 5 0 1                         | S T B               |    |

| 5 0 2                         | 画像表示装置              |    |

| 5 0 3                         | 受信回路                |    |

| 5 0 4                         | I / F 部             |    |

| 5 0 5                         | 制御回路                |    |

| 5 0 6                         | 駆動回路                | 40 |

| 2 0 0                         | 表示パネル               |    |

【 四 1 】

【図3】

【 四 2 】

【図4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

---

フロントページの続き

(51)Int.Cl. F I

G 0 9 G 3/20 6 4 1 K

(56)参考文献 特開2003-173159(JP,A)

特開平07-056543(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 0 9 G 3 / 0 0 - 3 / 0 8

G 0 9 G 3 / 1 2

G 0 9 G 3 / 1 6 - 3 / 2 6

G 0 9 G 3 / 3 0

G 0 9 G 3 / 3 4 - 3 / 3 8

G 0 9 G 5 / 0 0 - 5 / 4 0