(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5873275号

(P5873275)

(45) 発行日 平成28年3月1日(2016.3.1)

(24) 登録日 平成28年1月22日(2016.1.22)

|               |           |

|---------------|-----------|

| (51) Int.Cl.  | F 1       |

| HO 1 L 21/027 | (2006.01) |

| GO 3 F 7/20   | (2006.01) |

| HO 1 J 37/305 | (2006.01) |

|               |           |

| HO 1 L        | 21/30     |

| HO 1 L        | 21/30     |

| GO 3 F        | 7/20      |

| GO 3 F        | 7/20      |

| HO 1 J        | 37/305    |

|               | B         |

請求項の数 10 (全 15 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2011-198865 (P2011-198865) |

| (22) 出願日  | 平成23年9月12日 (2011.9.12)       |

| (65) 公開番号 | 特開2013-62326 (P2013-62326A)  |

| (43) 公開日  | 平成25年4月4日 (2013.4.4)         |

| 審査請求日     | 平成26年9月11日 (2014.9.11)       |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 100076428<br>弁理士 大塚 康徳                     |

| (74) 代理人  | 100112508<br>弁理士 高柳 司郎                     |

| (74) 代理人  | 100115071<br>弁理士 大塚 康弘                     |

| (74) 代理人  | 100116894<br>弁理士 木村 秀二                     |

| (74) 代理人  | 100130409<br>弁理士 下山 治                      |

| (74) 代理人  | 100134175<br>弁理士 永川 行光                     |

最終頁に続く

(54) 【発明の名称】描画装置及び物品の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

生成部で生成された描画データに基づいて荷電粒子線で基板に描画を行う描画装置であつて、

前記荷電粒子線に対するプランキングを行うプランキング部と、

前記プランキング部を制御するプランキング制御部と、を有し、

前記プランキング制御部は、

前記生成部で生成された描画データを記憶する第1記憶部、第2記憶部及び第3記憶部を含み、

前記第3記憶部に記憶された描画データに基づいて前記プランキング部を制御し、

前記生成部で生成された描画データを前記第1記憶部及び前記第2記憶部のうち選択された一方に記憶させる動作と、前記第1記憶部及び前記第2記憶部のうち他方に記憶された描画データを読み出して前記第3記憶部に記憶させる動作とが並行して行われるよう、前記第1記憶部、前記第2記憶部及び前記第3記憶部の動作を制御することを特徴とする描画装置。

## 【請求項 2】

前記プランキング制御部は、

前記生成部、前記第1記憶部、前記第2記憶部及び前記第3記憶部の間の接続状態を、前記第1記憶部と前記第3記憶部とが接続され、且つ、前記生成部と前記第2記憶部とが接続された第1状態と、前記第2記憶部と前記第3記憶部とが接続され、且つ、前記生成

10

20

部と前記第1記憶部とが接続された第2状態との間で切り替える切替部を含み、

前記第1状態では、前記生成部で生成された描画データを前記第2記憶部に記憶させる動作と、前記第1記憶部に記憶された描画データを読み出して前記第3記憶部に記憶させる動作とが並行して行われるように、前記第2状態では、前記生成部で生成された描画データを前記第1記憶部に記憶させる動作と、前記第2記憶部に記憶された描画データを読み出して前記第3記憶部に記憶させる動作とが並行して行われるように、前記第1記憶部、前記第2記憶部及び前記第3記憶部の動作を制御することを特徴とする請求項1に記載の描画装置。

【請求項3】

前記プランキング制御部は、

10

前記第1状態において、前記第2記憶部による記憶が完了し、且つ前記第3記憶部に記憶された描画データに基づく前記プランキング部の制御が完了した後に、前記切替部によって前記第1状態を前記第2状態に切り替え、

前記第2状態において、前記第1記憶部による記憶が完了し、且つ前記第3記憶部に記憶された描画データに基づく前記プランキング部の制御が完了した後に、前記切替部によって前記第2状態を前記第1状態に切り替えることを特徴とする請求項2に記載の描画装置。

【請求項4】

前記プランキング制御部は、

20

前記第1状態において、前記プランキング部の制御が完了した後に、前記切替部によって前記第1状態を前記第2状態に切り替え、

前記第2状態において、前記プランキング部の制御が完了した後に、前記切替部によって前記第2状態を前記第1状態に切り替えることを特徴とする請求項2に記載の描画装置。

【請求項5】

前記プランキング制御部は、

前記第1状態を前記第2状態に切り替えたときに、前記第1状態において前記第2記憶部による記憶が完了していない場合、前記第2記憶部に記憶されていない残りの描画データを前記第1記憶部に記憶させる動作と、前記第2記憶部に記憶された描画データを読み出して前記第3記憶部に記憶させる動作とが並行して行われるように、前記第1記憶部、前記第2記憶部及び前記第3記憶部の動作を制御し、

30

前記第2状態を前記第1状態に切り替えたときに、前記第2状態において前記第1記憶部による記憶が完了していない場合、前記第1記憶部に記憶されていない残りの描画データを前記第2記憶部に記憶させる動作と、前記第1記憶部に記憶された描画データを読み出して前記第3記憶部に記憶させる動作とが並行して行われるように、前記第1記憶部、前記第2記憶部及び前記第3記憶部の動作を制御することを特徴とする請求項4に記載の描画装置。

【請求項6】

前記プランキング制御部は、

40

前記第1状態において、前記第2記憶部による記憶が完了した後に、前記切替部によって前記第1状態を前記第2状態に切り替え、

前記第2状態において、前記第1記憶部による記憶が完了した後に、前記切替部によって前記第2状態を前記第1状態に切り替えることを特徴とする請求項2に記載の描画装置。

【請求項7】

前記第3記憶部は、前記第1記憶部の記憶容量及び前記第2記憶部の記憶容量のそれぞれより小さい記憶容量を有し、且つ前記第1記憶部の記憶速度及び前記第2記憶部の記憶速度のそれぞれより速い記憶速度を有することを特徴とする請求項1乃至6のうちいずれか1項に記載の描画装置。

【請求項8】

50

荷電粒子線で基板に描画を行う描画装置であって、

前記荷電粒子線に対するプランキングを行うプランキング部と、

第1乃至第3記憶部と切替部とを含み、描画データに基づいて前記プランキング部を制御するプランキング制御部と、を有し、

前記プランキング制御部は、

第1状態と第2状態との間で状態が切り替えられ、前記第1状態においては、前記描画データを前記第1記憶部に記憶させる動作と、前記第2記憶部に記憶された描画データを読み出して前記第3記憶部に記憶させる動作とが互いに並行して行われ、前記第2状態においては、前記描画データを前記第2記憶部に記憶させる動作と、前記第1記憶部に記憶された描画データを読み出して前記第3記憶部に記憶させる動作とが互いに並行して行われるように、前記第1乃至第3記憶部および前記切替部の動作を制御し、

前記第3記憶部に記憶された前記描画データに基づいて前記プランキング部を制御する、

ことを特徴とする描画装置。

【請求項9】

荷電粒子線で基板に描画を行う描画方法であって、

描画データの生成を生成部に行わせ、

第1記憶部および第2記憶部のうちの選択された1つに前記描画データを記憶させる動作と、前記第1記憶部および前記第2記憶部のうちの他の1つに記憶された前記描画データを読み出して第3記憶部に記憶させる動作とが並行して行われるように、前記荷電粒子線に対するプランキングを行うプランキング部を制御するプランキング制御部に、前記第1乃至第3記憶部の動作の制御を行わせ、

前記第3記憶部に記憶された前記描画データに基づいて前記荷電粒子線のプランキングを前記プランキング部に行わせる、

ことを特徴とする描画方法。

【請求項10】

請求項1乃至8のうちいずれか1項に記載の描画装置を用いて基板に描画を行うステップと、

前記ステップで描画を行われた前記基板を現像するステップと、

を有することを特徴とする物品の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、描画装置及び物品の製造方法に関する。

【背景技術】

【0002】

半導体デバイスなどの製造工程（リソグラフィ工程）で用いられる装置の1つとして、複数の荷電粒子線（電子線）によって基板にパターンを描画（転写）するマルチ荷電粒子方式の荷電粒子線描画装置が提案されている（特許文献1参照）。荷電粒子線描画装置は、複数の荷電粒子線のそれぞれの基板への照射及び非照射（プランキング）をプランキング偏向器で制御することで、基板にパターンを描画する。具体的には、プランキング偏向器を制御するプランキング制御部では、描画パターンデータ生成部から送信されるプランキング偏向器を構成する各偏向器のプランキング動作を制御するための描画データを、低速大容量の記憶部に記憶させる。そして、パターンの描画に必要な描画データを低速大容量の記憶部からメモリに送信し、プランキング偏向器のプランキング動作に同期させてメモリから描画データを読み出すことで、基板にパターンを描画する。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平07-273006号公報

10

20

30

40

50

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

荷電粒子線描画装置では、半導体デバイスの微細化に伴い、描画グリッド（1つの荷電粒子線の描画範囲）の狭ピッチ化が要求されている。また、半導体デバイスの生産性を向上させるために、同時に描画可能な荷電粒子線の数を増加させてパターンの描画面積を大きくする傾向にある。その結果、プランキング偏向器のプランキング動作を制御するための描画データのデータ容量が膨大になるため、記憶部又はメモリへの描画データの記憶（送信）が終了するまで装置が待ち状態となり、スループットが低下してしまう。このような問題は、マルチ荷電粒子方式の荷電粒子線描画装置だけではなく、シングル荷電粒子方式の荷電粒子線描画装置にも同様に発生する。

10

**【0005】**

本発明は、このような従来技術の課題に鑑みてなされ、描画装置におけるスループットの点で有利な技術を提供することを例示的目的とする。

**【課題を解決するための手段】****【0006】**

上記目的を達成するために、本発明の一側面としての描画装置は、生成部で生成された描画データに基づいて荷電粒子線で基板に描画を行う描画装置であって、前記荷電粒子線に対するプランキングを行うプランキング部と、前記プランキング部を制御するプランキング制御部と、を有し、前記プランキング制御部は、前記生成部で生成された描画データを記憶する第1記憶部、第2記憶部及び第3記憶部を含み、前記第3記憶部に記憶された描画データに基づいて前記プランキング部を制御し、前記生成部で生成された描画データを前記第1記憶部及び前記第2記憶部のうち選択された一方に記憶させる動作と、前記第1記憶部及び前記第2記憶部のうち他方に記憶された描画データを読み出して前記第3記憶部に記憶させる動作とが並行して行われるように、前記第1記憶部、前記第2記憶部及び前記第3記憶部の動作を制御することを特徴とする。

20

**【0007】**

本発明の更なる目的又はその他の側面は、以下、添付図面を参照して説明される好ましい実施形態によって明らかにされるであろう。

30

**【発明の効果】****【0008】**

本発明によれば、例えば、描画装置におけるスループットの点で有利な技術を提供することができる。

**【図面の簡単な説明】****【0009】**

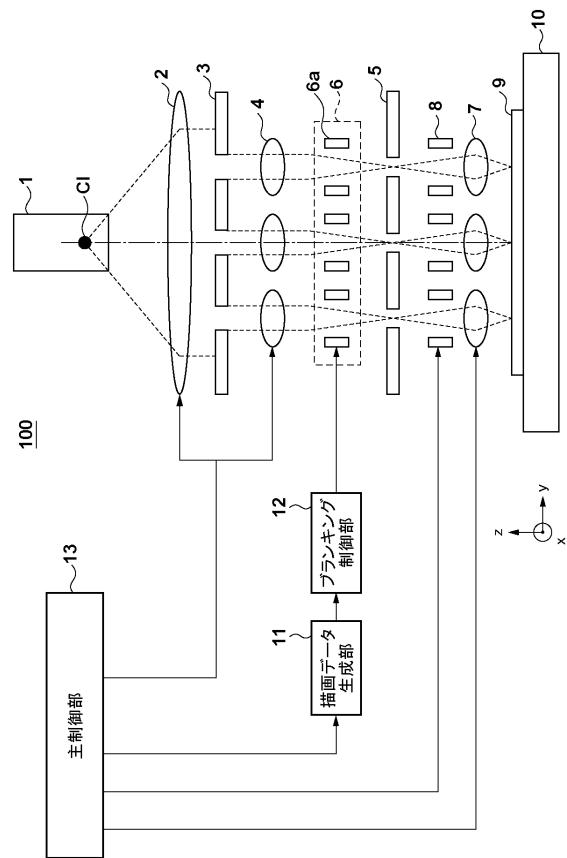

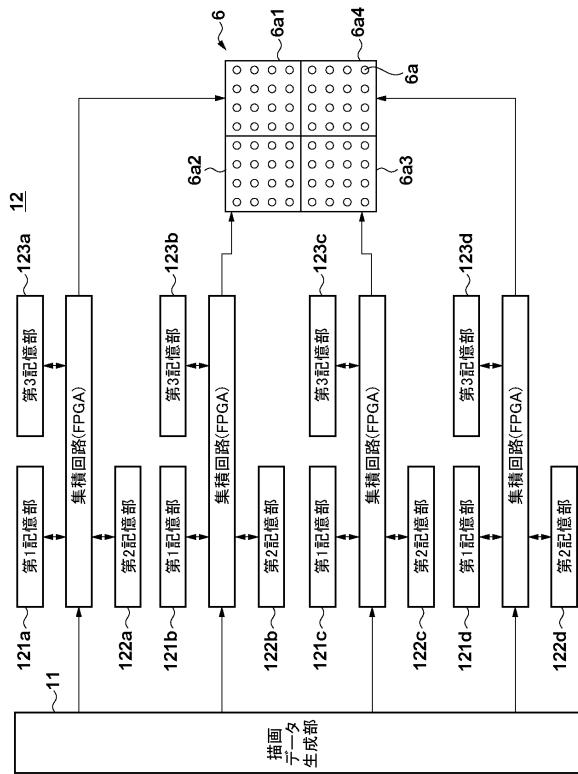

【図1】本発明の一側面としての描画装置の構成を示す図である。

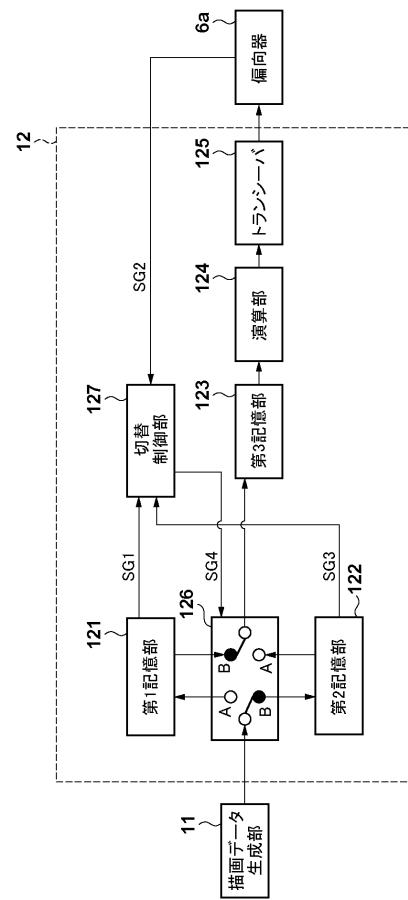

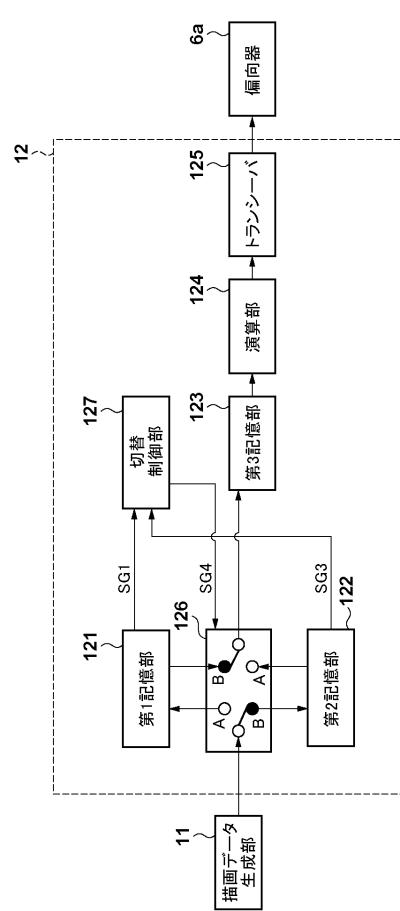

【図2】第1の実施形態におけるプランキング制御部の構成を示す図である。

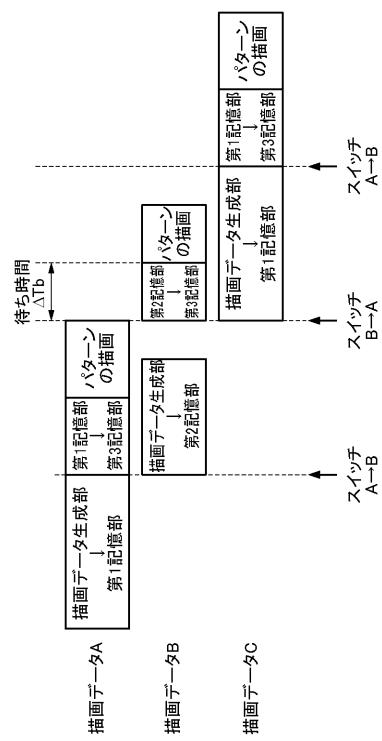

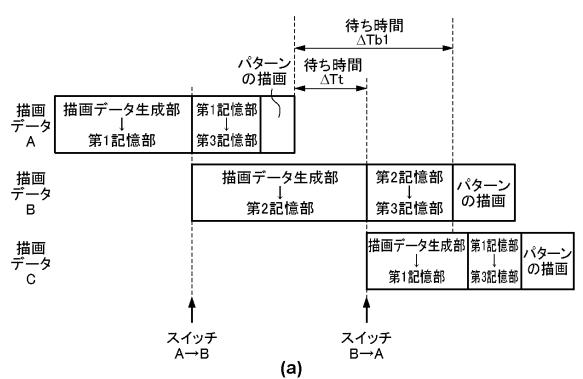

【図3】第1の実施形態におけるプランキング制御部による動作シーケンスを説明するための図である。

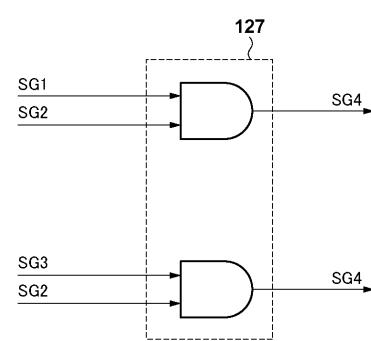

【図4】切替制御部による切替部におけるスイッチの切り替えのロジックの一例を模式的に示す図である。

40

【図5】複数の第1記憶部、第2記憶部及び第3記憶部を有するプランキング制御部の構成を示す図である。

【図6】第2の実施形態におけるプランキング制御部の構成を示す図である。

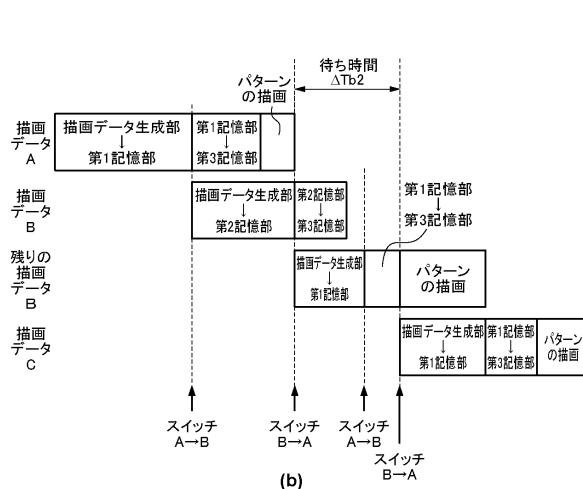

【図7】第2の実施形態におけるプランキング制御部による動作シーケンスを説明するための図である。

【図8】第3の実施形態におけるプランキング制御部の構成を示す図である。

【図9】第3の実施形態におけるプランキング制御部による動作シーケンスを説明するための図である。

【図10】従来技術におけるプランキング制御部を説明するための図である。

50

## 【発明を実施するための形態】

## 【0010】

以下、添付図面を参照して、本発明の好適な実施の形態について説明する。なお、各図において、同一の部材については同一の参照番号を付し、重複する説明は省略する。

## 【0011】

図1は、本発明の一側面としての描画装置100の構成を示す図である。描画装置100は、荷電粒子線（電子線）を用いて基板にパターンを描画する描画装置であって、本実施形態では、マルチ荷電粒子線方式の描画装置（複数の荷電粒子線で描画を行う描画装置）である。但し、描画装置100は、シングル荷電粒子線方式の描画装置（1つの荷電粒子線で描画を行う描画装置）であってもよい。

10

## 【0012】

描画装置100は、電子銃1と、コリメータレンズ2と、アパーチャアレイ3と、静電レンズ4と、プランキングアパーチャ5と、プランキング偏向部6とを有する。また、描画装置100は、静電レンズ7と、偏向部8と、基板9を保持して移動する基板ステージ10と、描画データ生成部11と、プランキング制御部12と、主制御部13とを有する。

## 【0013】

図1を参照するに、電子銃1は、クロスオーバ像CIを形成する。クロスオーバ像CIから発散した荷電粒子線（電子線）は、コリメータレンズ2を介して、略平行な荷電粒子線に変換され、アパーチャアレイ3に入射する。アパーチャアレイ3は、マトリクス状に配列された複数の円形形状の開口を有し、コリメータレンズ2を通過した荷電粒子線を複数の荷電粒子線に分割する。

20

## 【0014】

アパーチャアレイ3を通過した荷電粒子線は、円形形状の開口をそれぞれ有する複数の電極板（例えば、3つの電極板）で構成された静電レンズ4に入射する。静電レンズ4を通過した荷電粒子線が最初にクロスオーバ像を形成する位置には、マトリクス状に配列された複数の微小開口を有するプランキングアパーチャ5が配置されている。

## 【0015】

プランキング偏向部6は、荷電粒子線を偏向する偏向器6aを含む。プランキング偏向部6は、プランキング制御部12の制御下において、プランキングアパーチャ5と協同して、プランキング動作（基板9への荷電粒子線の照射及び非照射）を行う。

30

## 【0016】

プランキングアパーチャ5を通過した荷電粒子線は、静電レンズ7によって結像され、基板ステージ10に保持された基板9の上にクロスオーバ像CIに相当する像を形成する。この際、プランキングアパーチャ5を通過した荷電粒子線は、プランキングアパーチャ5と静電レンズ7との間に配置された偏向器を含む偏向部8によって偏向される（即ち、基板9の上に形成された像が偏向される）。

## 【0017】

描画データ生成部11は、基板9に描画すべきパターンに対応する描画データを生成する。なお、描画データは、後述するように、プランキング制御部12において、プランキング偏向部6における偏向器6aのそれぞれの駆動を制御する（偏向器6aの駆動をON又はOFFにする）ためのビットマップデータに変換される。

40

## 【0018】

プランキング制御部12は、描画データ生成部11で生成された描画データに基づいて、プランキング偏向部6を制御する。プランキング制御部12の構成や動作については、以下の各実施形態で詳細に説明する。

## 【0019】

主制御部13は、CPUやメモリなどを含み、描画装置100の全体（動作）を制御する。例えば、主制御部13は、基板9にパターンを描画する際に、基板9を保持する基板ステージ10をX軸方向に連続的に移動させる。そして、主制御部13は、プランキング

50

制御部 12 を介して、プランキングアーチャ 5 及びプランキング偏向部 6 によって荷電粒子線をプランキングしながら、基板 9 の上に形成された像を偏向部 8 で Y 軸方向に偏向する。これにより、基板 9 の上にパターンが描画される。

【 0020 】

ここで、プランキング制御部 12 を各実施形態で詳細に説明する前に、図 10 (a) 及び図 10 (b) を参照して、従来技術（例えば、特許文献 1）におけるプランキング制御部 1200 について説明する。図 10 (a) は、プランキング制御部 1200 の構成を示す図であり、図 10 (b) は、プランキング制御部 1200 による動作シーケンスを示す図である。描画データ生成部 1100 では、2 種類のパターンのそれぞれに対応する描画データ A 及び B が生成されるものとする。

10

【 0021 】

図 10 (a) に示すように、描画データ生成部 1100 で生成された描画データ A は、記憶部 1202 に送信され、記憶部 1202 に記憶される。記憶部 1202 は、低速大容量の記憶装置、例えば、ハードディスクドライブ (HDD) やソリッドステートドライブ (SSD) などの不揮発性の記憶装置で構成される。

【 0022 】

描画データ A に対応するパターンを基板に描画する際には、図 10 (b) に示すように、描画に必要な描画データを記憶部 1202 から読み出してメモリ 1204 に逐次記憶させながらパターンの描画を繰り返す。この際、メモリ 1204 に記憶（展開）された描画データ A は、演算部 1206 に送信されて各種の演算が施されて、プランキング偏向部における偏向器の駆動を ON 又は OFF にするためのビットマップデータに変換される。そして、かかるビットマップデータは、トランシーバ 1208 を介して、プランキング偏向部における偏向器 1300 に入力（送信）される。

20

【 0023 】

従来技術におけるプランキング制御部 1200 では、次に、描画データ B に対応するパターンを基板に描画する場合、描画データ生成部 1100 で生成された描画データ B を記憶部 1202 に送信して記憶させる必要がある。従って、図 10 (b) に示すように、描画データ B に対応するパターンの描画を開始するまでには、待ち時間 Tb が生じるため、描画装置のスループットの低下を招いてしまう。また、複数の描画データ（例えば、描画データ A 及び B）を予め記憶することができるよう、記憶部 1202 の記憶容量を増やすことも考えられる。但し、複数の描画データを予め記憶部 1202 に記憶させるためには膨大な時間（送信時間）が必要となることに加えて、記憶容量を増やすことによるコスト増大を招いてしまう。

30

【 0024 】

そこで、描画装置 100 では、プランキング制御部 12 を以下の各実施形態で説明するように構成することで、複数の描画データのそれぞれに対応するパターンを順次描画する場合であっても、スループットの低下を抑制している。

【 0025 】

< 第 1 の実施形態 >

図 2 は、第 1 の実施形態におけるプランキング制御部 12 の構成を示す図である。プランキング制御部 12 は、本実施形態では、描画データをそれぞれ記憶する第 1 記憶部 121、第 2 記憶部 122 及び第 3 記憶部 123 を含み、第 1 記憶部 121 及び第 2 記憶部 122 は、第 3 記憶部 123 の前段に並列に配置されている。

40

【 0026 】

第 3 記憶部 123 は、第 1 記憶部 121 及び第 2 記憶部 122 の記憶容量より小さい記憶容量を有し、且つ、第 1 記憶部 121 及び第 2 記憶部 122 の記憶速度より速い記憶速度を有する。具体的には、第 1 記憶部 121 及び第 2 記憶部 122 は、低速大容量の記憶装置、即ち、ハードディスクドライブ (HDD) やソリッドステートドライブ (SSD) などの不揮発性の記憶装置で構成される。このような記憶装置は、記憶速度（書き込み速度）は遅いが、電源を落としてもデータ（描画データ）が保持されるため、電源の再立ち上げ時

50

にデータを再送する（再記憶させる）ことが不要となる。一方、第3記憶部123は、プランキング偏向部6における偏向器6aを高速に駆動することを可能とするために、高速低容量の記憶装置、即ち、描画データを高速に読み出すことができる半導体メモリ（DDRメモリ）などで構成される。

【0027】

また、プランキング制御部12は、演算部124と、トランシーバ125とを含む。演算部124は、第3記憶部123に記憶された描画データに各種の演算を施して偏向器6aの駆動をON又はOFFにするためのビットマップデータに変換し、かかるビットマップデータを、トランシーバ125を介して、偏向器6aに入力する。このように、演算部124は、第3記憶部123に記憶された描画データに基づいて、偏向器6aを駆動して基板9への荷電粒子線の照射及び非照射を制御する制御部（第1制御部）として機能する。

10

【0028】

また、プランキング制御部12は、描画データ生成部11で生成された描画データの流れを切り替え可能な構成とするために、切替部126と、切替部126を制御する切替制御部（第2制御部）127とを含む。

【0029】

切替部126は、描画データ生成部11、第1記憶部121、第2記憶部122及び第3記憶部123との間の接続状態を切り替えるスイッチで構成される。切替部126は、図2に示すように、スイッチAを選択（設定）することで、第2記憶部122と第3記憶部123とが接続され、且つ、描画データ生成部11と第1記憶部121とが接続された状態A（第2状態）にする。また、切替部126は、スイッチBを選択（設定）することで、第1記憶部121と第3記憶部123とが接続され、且つ、描画データ生成部11と第2記憶部122とが接続された状態B（第1状態）にする。

20

【0030】

切替制御部127は、切替部126を制御して、第1記憶部121又は第2記憶部122における描画データの記憶に関する第1動作と、第3記憶部123における描画データの記憶に関する第2動作とが並行して行われるようにする。ここで、第1動作とは、描画データ生成部11から送信される描画データを第1記憶部121及び第2記憶部122のうち選択された一方に記憶させる動作である。また、第2動作とは、第1記憶部121及び第2記憶部121のうち他方に記憶された描画データを読み出して第3記憶部123に記憶させる動作である。従って、状態Aでは、描画データ生成部11からの描画データを第1記憶部121に記憶させる動作と、第2記憶部122に記憶された描画データを読み出して第3記憶部123に記憶させる動作とが並行して行われる。また、状態Bでは、描画データ生成部11からの描画データを第2記憶部122に記憶させる動作と、第1記憶部121に記憶された描画データを読み出して第3記憶部123に記憶させる動作とが並行して行われる。

30

【0031】

図3を参照して、本実施形態におけるプランキング制御部12による動作シーケンスを説明する。描画データ生成部11では、3種類のパターンのそれぞれに対応する描画データA、B及びCが生成されるものとする。まず、切替制御部127は、切替部126においてスイッチAを選択して（即ち、状態Aとして）、描画データ生成部11から送信される描画データAを第1記憶部121に記憶させる。切替制御部127は、描画データ生成部11から送信される描画データAの第1記憶部121への記憶が完了したことを示す信号SG1を受信すると、切替部126においてスイッチBを選択して、状態Aを状態Bに切り替える。そして、第1記憶部121に記憶された描画データAを読み出して第3記憶部123に記憶させる動作と、描画データ生成部11から送信される描画データBを第2記憶部122に記憶させる動作とを並行して行う。

40

【0032】

描画データAの第3記憶部123への記憶が完了したら、演算部124において倍率補

10

20

30

40

50

正や近接効果補正などの各種の演算（補正演算）が描画データAに施されてビットマップデータに変換される。かかるビットマップデータは、トランシーバ125を介して、偏向器6aに入力され、描画データAに対応するパターンの描画が行われる。描画データAに対応するパターンの描画が行われている間においても、描画データ生成部11から送信される描画データBを第2記憶部122に記憶させる動作は継続される。また、本実施形態では、偏向器6a（プランキング偏向部6）は、第1記憶部121から読み出されて第3記憶部123に記憶された描画データAに基づく偏向器6aの駆動が完了したことを示す信号SG2を切替制御部127に送信する。これにより、トランシーバ125と偏向器6aとの間において、描画データが誤りなく正しく送信されたこと（即ち、描画データAに対応するパターンの描画が正しく完了したこと）を保証することが可能となる。

10

#### 【0033】

切替制御部127は、信号SG2を受信し、且つ、描画データ生成部11から送信される描画データBの第2記憶部122への記憶が完了したことを示す信号SG3を受信すると、切替部126においてスイッチAを選択して、状態Bを状態Aに切り替える。そして、第2記憶部122に記憶された描画データBを読み出して第3記憶部123に記憶させる動作と、描画データ生成部11から送信される描画データCを第1記憶部121に記憶させる動作とを並行して行う。描画データBの第3記憶部123への記憶が完了したら、描画データBに対応するパターンの描画が行われる。描画データBに対応するパターンの描画が行われている間においても、描画データ生成部11から送信される描画データCを第1記憶部121に記憶させる動作は継続される。また、切替制御部127は、信号SG2を受信し、且つ、描画データ生成部11から送信される描画データCの第1記憶部122への記憶が完了したことを示す信号SG1を受信すると、切替部126においてスイッチBを選択して、状態Aを状態Bに切り替える。

20

#### 【0034】

図4は、切替制御部127による切替部126におけるスイッチの切り替えのロジックの一例を模式的に示す図である。スイッチAからスイッチBへの切り替えは、描画データ生成部11から送信される描画データの第1記憶部121への記憶が完了し、且つ、第2記憶部122に記憶された描画データの第3記憶部123への記憶が完了したことが条件となる。同様に、スイッチBからスイッチAへの切り替えは、描画データ生成部11から送信される描画データの第2記憶部122への記憶が完了し、且つ、第1記憶部121に記憶された描画データの第3記憶部123への記憶が完了したことが条件となる。

30

#### 【0035】

そこで、図4に示すように、切替制御部127は、状態Aにおいては、第1記憶部121から信号SG1を受信し、且つ、偏向器6aから信号SG2を受信したときに、スイッチAをスイッチBに切り替えるための信号SG4を生成して切替部126に入力する。同様に、切替制御部127は、状態Bにおいては、第2記憶部122から信号SG3を受信し、且つ、偏向器6aから信号SG2を受信したときに、スイッチBをスイッチCに切り替えるための信号SG4を生成して切替部126に入力する。なお、信号SG1は、描画データ生成部11から送信される描画データの第1記憶部121への記憶が完了したことを示す信号であり、信号SG3は、描画データ生成部11から送信される描画データの第2記憶部122への記憶が完了したことを示す信号である。また、信号SG2は、第3記憶部123に記憶された描画データに基づく偏向器6aの駆動が完了したことを示す信号である。

40

#### 【0036】

このように、本実施形態では、プランキング制御部12が低速大容量の記憶装置で構成される第1記憶部121及び第2記憶部122と、高速低容量の記憶装置で構成される第3記憶部123とを含んでいる。これにより、描画データ生成部11から送信される描画データを第1記憶部121及び第2記憶部122のうち、選択された一方に記憶させる動作と、他方に記憶された描画データを読み出して第3記憶部123に記憶させる動作とを並行して行うことができる。従って、本実施形態は、図3に示すように、従来技術（図1

50

0 参照) と比較して、描画パターン B に対応するパターンの描画を開始するまでの待ち時間  $T_b$  を大幅に短くすることが可能であり、待ち時間  $T_b$  に起因するスループットの低下を抑制することができる。

#### 【 0 0 3 7 】

また、第 3 記憶部 123 は、プランキング偏向部 6 における偏向器 6b を高速に駆動するため、高価な半導体メモリなどで構成する必要がある。但し、複数の描画データを記憶することができるよう、第 3 記憶部 123 の記憶容量を増やすことは、上述したように、コスト的に難しい。本実施形態では、高価な半導体メモリなどで構成された記憶部(第 3 記憶部)を増やすことなく、低価なハードディスクドライブなどで構成された 2 つの記憶部(第 1 記憶部及び第 2 記憶部)を有しているだけであるため、コスト面でも有利である。

10

#### 【 0 0 3 8 】

なお、図 2 では、図示を省略しているが、実際には、第 1 記憶部 121、第 2 記憶部 122 及び第 3 記憶部 123 のそれぞれには、その動作を制御する制御コントローラが配置される。また、描画データ生成部 11 からは、イーサネット(登録商標)などのネットワークを経由して描画データが送信されるため、ネットワークコントローラが配置される。また、このようなコントローラ、演算部 124、トランシーバ 125、切替部 126、切替制御部 127 などは、集積回路(FPGA)などで構成することも可能である。

#### 【 0 0 3 9 】

また、描画データ生成部 11 で生成される描画データは、数ナノメートル程度の細かいグリッドのデータであるため、一般的に、1 つのパターンに対応する描画データは、数テラバイトの膨大なデータとなる。かかる描画データを、ハードディスクなどで構成された 1 つの記憶部(第 1 記憶部又は第 2 記憶部)で記憶することは難しいため、図 5 に示すように、第 1 記憶部 121、第 2 記憶部 122 及び第 3 記憶部 123 を多段で構成してもよい。図 5 では、描画データを、プランキング偏向部 6 における偏向器群 6a1 乃至 6a4 のそれぞれに対応させて 4 つの分割描画データに分割している。そして、各分割描画データを記憶するために、プランキング制御部 12 は、4 つの第 1 記憶部 121a 乃至 121d と、4 つの第 2 記憶部 122a 乃至 122d と、4 つの第 3 記憶部 123a 乃至 123d とを含む。更に、プランキング制御部 12 は、演算部 124、トランシーバ 125、切替部 126、切替制御部 127 などをそれぞれ構成する 4 つの集積回路(FPGA)を含む。

20

#### 【 0 0 4 0 】

##### < 第 2 の実施形態 >

図 6 は、第 2 の実施形態におけるプランキング制御部 12 の構成を示す図である。本実施形態のプランキング制御部 12 は、第 1 の実施形態と比較して、第 1 記憶部 121 又は第 2 記憶部 122 から読み出された描画データの第 3 記憶部 123 への記憶が完了したことを示す信号 SG5 が切替制御部 127 に入力される点が異なる。

30

#### 【 0 0 4 1 】

図 7 を参照して、第 1 の実施形態と比較しながら、本実施形態におけるプランキング制御部 12 による動作シーケンスを説明する。図 7(a) は、第 1 の実施形態の動作シーケンスを示し、図 7(b) は、本実施形態の動作シーケンスを示している。本実施形態では、描画データ生成部 11 から送信される描画データを第 1 記憶部 121 又は第 2 記憶部 122 に記憶させる動作(かかる動作は、パターンを描画する動作と並行して行われている)が完了するまでの待ち時間  $T_t$  を排除する。これにより、パターンの描画を開始するまでの待ち時間  $T_b1$  を短くしてスループットの向上を実現することが可能となる。

40

#### 【 0 0 4 2 】

図 7(a) に示す第 1 の実施形態の動作シーケンスを参照するに、描画データ A に対応するパターンを描画する動作が完了した時点で、描画データ生成部 11 から送信される描画データ B を第 2 記憶部 122 に記憶させる動作が完了していない。このような場合、第 1 の実施形態では、図 7(a) に示すように、描画データ生成部 11 から送信される描画

50

データBの第2記憶部122への記憶が完了するまで待ってから、切替部126におけるスイッチBからスイッチAへの切り替えが行われる。従って、待ち時間Ttが生じてしまうため、描画装置100のスループットの低下を招くことになる。

#### 【0043】

一方、本実施形態では、図7(b)に示すように、描画データAに対応するパターンを描画する動作が完了した時点で、切替部126におけるスイッチBからスイッチAへの切り替えが行われる。この際、描画データ生成部11から送信される描画データBを第2記憶部122に記憶させる動作が完了していなければ、第2記憶部122に記憶されていない残りの描画データBは、第1記憶部121に記憶させる。そして、残りの描画データBを第1記憶部121に記憶させる動作と、第2記憶部122に記憶された描画データB(残りの描画データBを除く描画データB)を読み出して第3記憶部123に記憶させる動作とを並行して行う。かかる2つの動作が完了した時点で、スイッチAからスイッチBへの切り替えを行い、第1記憶部121に記憶された残りの描画データBを読み出して第3記憶部123に記憶させる(即ち、全ての描画データBを第3記憶部123に記憶させる)。描画データBの第3記憶部123への記憶が完了した時点で、スイッチBからスイッチAへの切り替えを行う。この際、スイッチBからスイッチAへの切り替えは、描画データBの第3記憶部123への記憶が完了したことを示す信号SG5を切替制御部127が受信することで行われる。そして、描画データBに対応するパターンを描画する動作と、描画データ生成部11から送信される描画データCを第1記憶部121に記憶させる動作とを並行して行う。

10

20

#### 【0044】

このように、本実施形態では、状態Aにおいて、第1記憶部121から読み出されて第3記憶部123に記憶された描画データに基づく偏向器6aの駆動が完了したことを示す信号SG2を切替制御部127が受信したときに、状態Aを状態Bに切り替える。また、状態Aを状態Bに切り替えたときに、切替制御部127が描画データ生成部11から送信される描画データの第2記憶部122への記憶が完了したことを示す信号SG3を受信していない場合には、以下のように、2つの動作を並行して行う。即ち、第2記憶部122に記憶されていない残りの描画データを第1記憶部121に記憶させる動作と、第2記憶部122に記憶された、残りの描画データを除く描画データを読み出して第3記憶部123に記憶させる動作とを並行して行う。

30

#### 【0045】

同様に、本実施形態では、状態Bにおいて、第2記憶部122から読み出されて第3記憶部123に記憶された描画データに基づく偏向器6aの駆動が完了したことを示す信号SG2を切替制御部127が受信したときに、状態Bを状態Aに切り替える。また、状態Bを状態Aに切り替えたときに、切替制御部127が描画データ生成部11から送信される描画データの第1記憶部121への記憶が完了したことを示す信号SG1を受信していない場合には、以下のように、2つの動作を並行して行う。即ち、第1記憶部121に記憶されていない残りの描画データを第2記憶部122に記憶させる動作と、第1記憶部121に記憶された、残りの描画データを除く描画データを読み出して第3記憶部123に記憶させる動作とを並行して行う。

40

#### 【0046】

これにより、本実施形態では、図7(b)に示すように、パターンの描画を開始するまでの待ち時間Tb2を第1の実施形態(Tb1)よりも短くすることが可能であり、描画装置100のスループットを更に向上させることができる。

#### 【0047】

##### <第3の実施形態>

図8は、第3の実施形態におけるプランキング制御部12の構成を示す図である。本実施形態のプランキング制御部12は、第1の実施形態と比較して、第3記憶部123に記憶された描画データに基づく偏向器6aの駆動が完了したことを示す信号SG2が切替制御部127に入力されない点が異なる。

50

**【 0 0 4 8 】**

図9を参照して、本実施形態におけるプランキング制御部12による動作シーケンスを説明する。本実施形態では、描画データ生成部11から送信される描画データBを第2記憶部122に記憶させる動作が完了したら、描画データAに対応するパターンを描画する動作の完了を待たず、切替部126におけるスイッチBからスイッチAへの切り替えが行われる。従って、描画データAに対応するパターンを描画する動作と、描画データ生成部11から送信される描画データCを第1記憶部121に記憶させる動作とが並行して行われることになる。但し、描画データAは、第1記憶部121から読み出されて第3記憶部123に記憶されているため、描画パターンCを第1記憶部121に記憶させることができある。

10

**【 0 0 4 9 】**

このように、本実施形態では、状態Aにおいて、描画データ生成部11から送信される描画データの第2記憶部122への記憶が完了したことを示す信号SG3を切替制御部127が受信したときに、状態Aを状態Bに切り替える。同様に、状態Bにおいて、描画データ生成部11から送信される描画データの第1記憶部121への記憶が完了したことを示す信号SG1を切替制御部127が受信したときに、状態Aを状態Bに切り替える。

**【 0 0 5 0 】**

これにより、本実施形態では、描画データCに対応するパターンの描画を開始するまでの待ち時間Tbを短くして描画装置100のスループットを向上させることができる。但し、本実施形態では、現在のパターンの描画に使用している描画データを記憶している記憶部（本実施形態では、描画データAを記憶している第1記憶部121）に新たな描画データ（本実施形態では、描画データC）を記憶させることになる。従って、現在のパターンの描画が正常に完了しない場合（例えば、トランシーバ125と偏向器6aとの間ににおいて、描画データが正しく送信されなかった場合など）には、描画データ生成部11から描画データを再送する必要がある。

20

**【 0 0 5 1 】**

本発明の実施形態にかかる物品の製造方法は、例えば、半導体デバイス等のマイクロデバイスや微細構造を有する素子等の物品を製造するのに好適である。本実施形態の物品の製造方法は、基板に塗布された感光剤に描画装置100を用いて潜像パターンを形成する工程（基板に描画を行う工程）と、かかる工程で潜像パターンが形成された基板を現像する工程とを含む。更に、かかる製造方法は、他の周知の工程（酸化、成膜、蒸着、ドーピング、平坦化、エッチング、レジスト剥離、ダイシング、ボンディング、パッケージング等）を含む。本実施形態の物品の製造方法は、従来の方法に比べて、物品の性能・品質・生産性・生産コストの少なくとも1つにおいて有利である。

30

**【 0 0 5 2 】**

以上、本発明の好ましい実施形態について説明したが、本発明はこれらの実施形態に限定されないことはいうまでもなく、その要旨の範囲内で種々の変形及び変更が可能である。

【 図 1 】

【 図 2 】

【 図 3 】

【図4】

【 図 5 】

【図6】

( 7 )

〔 四 8 〕

【図9】

【図10】

---

フロントページの続き

(72)発明者 大石 伸司

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 藤原 伸二

(56)参考文献 特開平01-111326 (JP, A)

特開2001-076989 (JP, A)

特開平07-273006 (JP, A)

特開昭62-263632 (JP, A)

特開平03-108712 (JP, A)

特開平11-134242 (JP, A)

特開昭54-128646 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/027

G03F 7/20

H01J 37/305

G06F 12/00 - 12/06

G06F 13/16 - 13/18