## (19) United States

## (12) Patent Application Publication (10) Pub. No.: US 2016/0359080 A1 Chae et al.

#### Dec. 8, 2016 (43) Pub. Date:

#### (54) SYSTEM, METHOD AND APPARATUS FOR CHEMICAL VAPOR DEPOSITION

- (71) Applicant: SolarCity Corporation, San Mateo, CA (US)

- Inventors: Yongkee Chae, San Ramon, CA (US); Jianming Fu, Palo Alto, CA (US)

- (73) Assignee: SolarCity Corporation, San Mateo, CA (US)

- Appl. No.: 14/985,263

- (22) Filed: Dec. 30, 2015

#### Related U.S. Application Data

(60) Provisional application No. 62/172,229, filed on Jun. 7, 2015.

### **Publication Classification**

(51) Int. Cl. H01L 31/18 (2006.01)C23C 16/455 (2006.01)

(52) U.S. Cl. CPC ....... H01L 31/1868 (2013.01); C23C 16/455 (2013.01)

#### (57)ABSTRACT

One embodiment of the present invention can provide a system for fabricating a photovoltaic structure. The system can include a combined chemical vapor deposition tool that can include a static deposition module and an inline deposition module. The static deposition module can be configured to deposit a first passivation layer on a first side of a crystalline Si base layer of the photovoltaic structure. The inline deposition module is configured to deposit a second passivation layer on the first passivation layer, and the inline deposition module is coupled to the static deposition module in a way that the photovoltaic structure can be transferred from the static deposition module to the inline deposition module without leaving a common vacuum space.

206

204

202

208

210

210

FIG. 2

<u>300</u>

FIG. 3

| BUFFER CARRIER A12 A14 A10          | 400<br>FIG. 4 | S BUFFER CVD CHAMBER BUFFER UNLOAD LOCK CARRIER 512 514 510 | 5 <u>00</u><br>FIG. 5 |

|-------------------------------------|---------------|-------------------------------------------------------------|-----------------------|

| CVD CHAMBER WITH STATIC CARRIER 406 | 400<br>FIG. 1 | CVD CHAMBER WITH MOVING S08 CARRIER 508                     | 500<br>FIG            |

| BUFFER W                            |               |                                                             |                       |

| LOAD LOCK<br>402                    |               | LOAD LOCK BUFFER 504                                        |                       |

| BUFFER UNLOAD LOCK<br>616 618                |

|----------------------------------------------|

| CVD CHAMBER WITH MOVING CARRIER 614          |

| BUFFER<br>612                                |

| CVD CHAMBER WITH MOVING CARRIER 610          |

| BUFFER<br>608                                |

| CVD CHAMBER<br>WITH STATIC<br>CARRIER<br>606 |

| BUFFER<br>604                                |

| LOAD LOCK BUFFER<br>602 604                  |

<u>009</u>

FIG. 8

# SYSTEM, METHOD AND APPARATUS FOR CHEMICAL VAPOR DEPOSITION

# CROSS-REFERENCE TO OTHER APPLICATIONS

[0001] This application claims the benefit of U.S. Provisional Application No. 62/172,229 (Attorney Docket No. P166-1PUS), entitled "Chemical Vapor Deposition Tool and Process," by inventors Yongkee Chae and Jianming Fu, filed Jun. 7, 2015.

#### FIELD OF THE INVENTION

[0002] This is generally related to semiconductor device fabrication. More specifically, this is related to a chemical vapor deposition tool and process with improved throughput.

#### **DEFINITIONS**

[0003] "Solar cell" or "cell" is a photovoltaic structure capable of converting light into electricity. A cell may have any size and any shape, and may be created from a variety of materials. For example, a solar cell may be a photovoltaic structure fabricated on a silicon wafer or one or more thin films on a substrate material (e.g., glass, plastic, or any other material capable of supporting the photovoltaic structure), or a combination thereof.

**[0004]** A "photovoltaic structure" can refer to a solar cell, a segment, or a solar cell strip. A photovoltaic structure is not limited to a device fabricated by a particular method. For example, a photovoltaic structure can be a crystalline silicon-based solar cell, a thin film solar cell, an amorphous silicon-based solar cell, a poly-crystalline silicon-based solar cell, or a strip thereof.

#### BACKGROUND

[0005] Large-scale production of high-efficiency solar cells plays an important role in ensuring the success of solar power over conventional energy sources that are based on fossil fuels. However, most of the current processes for manufacturing high-efficiency solar cells are not optimized for mass production. For example, many laboratory-made solar cells demonstrate superior performance, but the fabrication process for those solar cells cannot be applied in a mass production environment.

[0006] It has been shown that good passivation can be the key to ensuring high efficiency in solar cells. However, achieving good passivation under mass production conditions can be challenging. Conventional fabrication systems often have to sacrifice system throughput in order to meet the passivation requirement.

#### **SUMMARY**

[0007] One embodiment of the present invention can provide a system for fabricating a photovoltaic structure. The system can include a combined chemical vapor deposition tool that can include a static deposition module and an inline deposition module. The static deposition module can be configured to deposit a first passivation layer on a first side of a crystalline Si base layer of the photovoltaic structure. The inline deposition module is configured to deposit a second passivation layer on the first passivation layer, and the inline deposition module is coupled to the

static deposition module in a way that the photovoltaic structure can be transferred from the static deposition module to the inline deposition module without leaving a common vacuum space.

[0008] In a variation of this embodiment, the static deposition module can include multiple reaction chambers forming a cluster to allow parallel processing of multiple photovoltaic structures.

**[0009]** In a variation of this embodiment, the system can further include a second inline deposition module configured to deposit a heavily doped amorphous Si layer on the second passivation layer.

[0010] In a variation of this embodiment, the static deposition module comprises a static wafer carrier configured to remain stationary when the first passivation layer is deposited

[0011] In a further variation, the first passivation layer can include hydrogenated amorphous Si having low hydrogen content, and the static deposition module can be configured to use silane gas as a precursor.

[0012] In a variation of this embodiment, the inline deposition module can include comprises a wafer carrier configured to continuously move in a predetermine direction when the second passivation layer is deposited.

[0013] In a further variation, the second passivation layer can include hydrogenated amorphous Si having high hydrogen content, and the inline deposition module can be configured to use silane gas and hydrogen gas as precursors.

[0014] In a variation of this embodiment, the system can further include a buffer module positioned between the static deposition module and the inline deposition module.

[0015] In a variation of this embodiment, the system can further include a wet station configured to form a wet oxide layer on both surfaces of the Si base layer.

[0016] In a variation of this embodiment, the system can further include a physical vapor deposition module configured to deposit a transparent conductive oxide layer on the heavily doped amorphous Si layer.

[0017] In a further variation, the physical vapor deposition module can be further configured to deposit a metallic layer on the transparent conductive oxide layer, and the metallic layer can function as an adhesive layer between the transparent conductive oxide layer and a subsequently electroplated Cu grid.

[0018] In a variation of this embodiment, the static deposition module can be configured to start deposition after temperature and pressure conditions are stabilized, thereby facilitating formation of a high quality film layer.

[0019] In a variation of this embodiment, the inline deposition module can be configured to have a continuous flow of reaction gases, thereby facilitating high throughput of processed photovoltaic structures.

#### BRIEF DESCRIPTION OF THE FIGURES

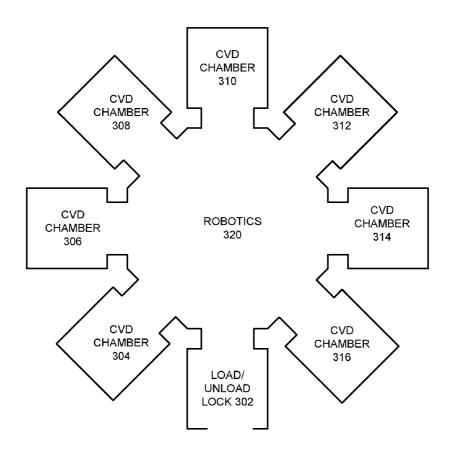

[0020] FIG. 1 shows an exemplary photovoltaic structure.

[0021] FIG. 2 shows an exemplary photovoltaic structure, according to an embodiment of the present invention.

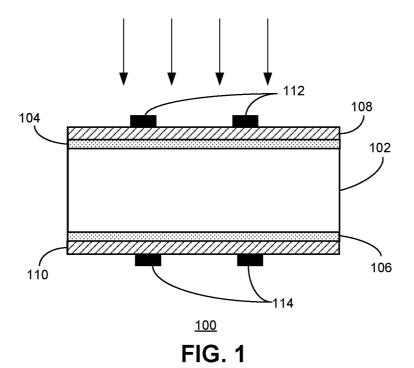

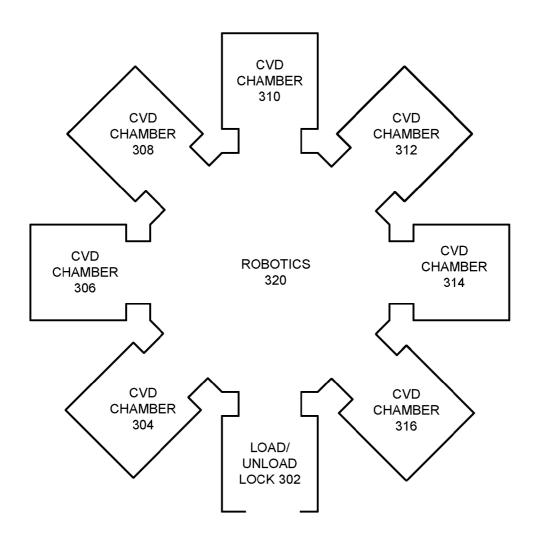

[0022] FIG. 3 shows a cluster CVD tool.

[0023] FIG. 4 shows a linear CVD tool.

[0024] FIG. 5 shows an inline-processing CVD tool.

[0025] FIG. 6 shows a combined CVD tool, according to one embodiment of the present invention.

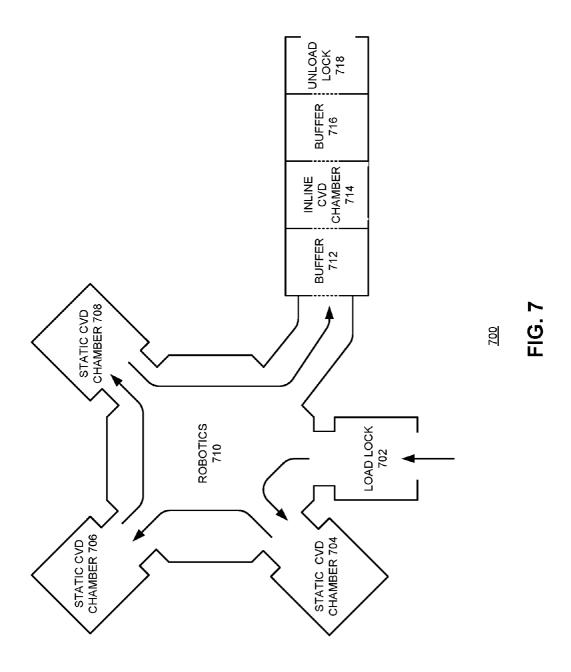

[0026] FIG. 7 shows a combined CVD tool, according to one embodiment of the present invention.

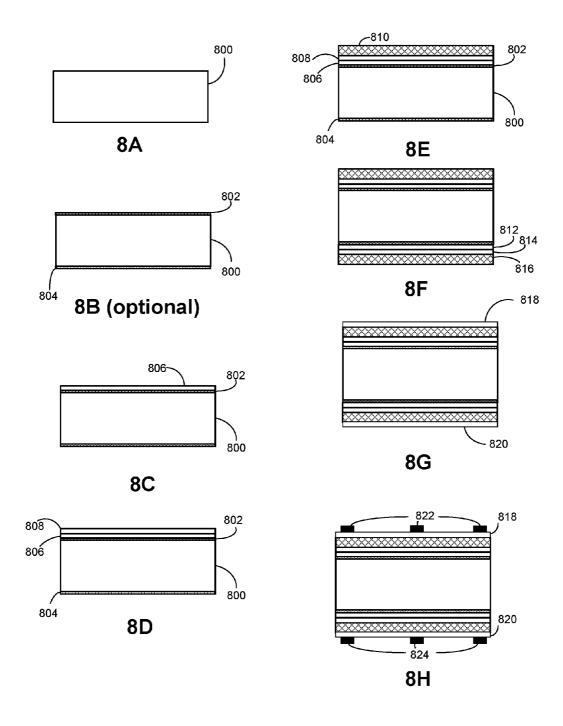

[0027] FIG. 8 shows an exemplary fabrication process of a photovoltaic structure, according to one embodiment of the present invention.

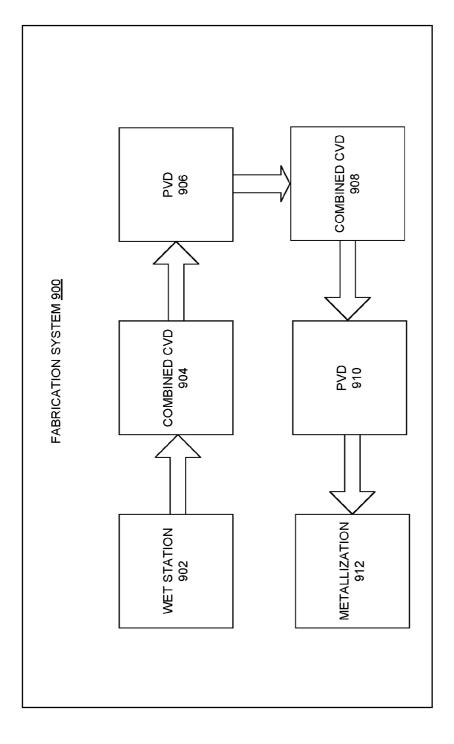

[0028] FIG. 9 shows an exemplary photovoltaic structure fabrication system, according to an embodiment of the present invention.

[0029] In the figures, like reference numerals refer to the same figure elements.

#### DETAILED DESCRIPTION

[0030] The following description is presented to enable any person skilled in the art to make and use the embodiments, and is provided in the context of a particular application and its requirements. Various modifications to the disclosed embodiments will be readily apparent to those skilled in the art, and the general principles defined herein may be applied to other embodiments and applications without departing from the spirit and scope of the present disclosure. Thus, the present invention is not limited to the embodiments shown, but is to be accorded the widest scope consistent with the principles and features disclosed herein.

#### Overview

[0031] Embodiments of the present invention can provide a system and method for fabricating high-efficiency photovoltaic structures with high throughput. To ensure good passivation at the surface of the crystalline Si substrate, a thin layer of intrinsic hydrogenated amorphous Si (a-Si:H) having a low hydrogen (H) concentration is deposited onto the Si substrate followed by the deposition of a thin layer of intrinsic a-Si:H having a high H concentration. The initial low-H a-Si:H layer can ensure a lower surface defect density, and the high H concentration of the subsequent a-Si layer can provide a layer with a wide bandgap, which can be the key to good surface passivation.

[0032] Chemical vapor deposition (CVD) tools can often be used to deposit the passivation layers as well as heavily doped emitter and/or surface field layers. Some embodiments of the present invention can provide a novel CVD tool that is capable of meeting both the passivation and throughput requirements. More specifically, the CVD tool can include at least a static chamber and an inline chamber. The initial a-Si passivation layer is deposited inside the static chamber to ensure a low-defect interface. The subsequent a-Si:H passivation layer is deposited inside the inline chamber to ensure high throughput. The Si substrates can be transported from the static chamber to the inline chamber without leaving a common vacuum space.

High-Efficiency Photovoltaic Structures and CVD Systems

[0033] FIG. 1 shows an exemplary photovoltaic structure. In FIG. 1, photovoltaic structure 100 can include substrate 102, passivation layers 104 and 106, surface-field layer 108, emitter layer 110, and electrode grids 112 and 114. In the example shown in FIG. 1, substrate 102 can include a lightly doped or substantially intrinsic crystalline Si (c-Si) layer; passivation layers 104 and 106 can include wide bandgap materials (e.g., a-Si:H or SiN $_x$ :H); surface-field layer 108 can include a heavily doped amorphous Si (a-Si) layer; and emitter layer 110 can include a heavily doped a-Si layer.

[0034] Also in FIG. 1, surface-field layer 108 can face the majority of incident light (as indicated by arrows), and hence can also be called the front surface-field (FSF) layer. Sub-

strate 102 can either be doped with n-type dopants (e.g., phosphorus) or p-type dopants (e.g., boron). The doping types of FSF layer 108 and emitter layer 110 can be determined by the doping type of substrate 102. For an n-type doped substrate, FSF layer 108 can be doped with n-type dopants to act as an electron collector; and emitter layer 110 can be doped with p-type dopants to act as a hole collector

[0035] As one can see from FIG. 1, photovoltaic structure 100 can include two junctions, a junction formed between FSF layer 108 and substrate 102 and a junction formed between emitter layer 110 and substrate 102. In order for photovoltaic structure 100 to have high efficiency, one must ensure that good passivation on both sides of substrate 102 can be achieved. Due to its wide bandgap and the ability to reduce the carrier recombination velocity, hydrogenated a-Si (a-Si:H) has been used for passivation purposes. The intrinsic a-Si:H typically can be deposited using a chemical vapor deposition (CVD) technique, such as a plasma-enhanced CVD (PECVD) technique.

[0036] A typical CVD process that deposits a-Si:H can use silane (SiH<sub>4</sub>) and H<sub>2</sub> as precursors. A high flow rate of H<sub>2</sub> can increase the atomic H concentration in the formed a-Si:H, resulting in a wider bandgap of the deposited a-Si:H. The wider bandgap is a desirable quality for passivation purposes. However, experiments have shown that introducing additional H<sub>2</sub> flow during the CVD of the a-Si:H can cause the a-Si:H—Si interface to have a high interface defect density (D<sub>it</sub>). This high D<sub>it</sub> can lead to increased carrier recombination at the Si surface, and hence can reduce the energy-conversion efficiency.

[0037] To simultaneously obtain an interface with a low  $D_{it}$  and to achieve the wide bandgap passivation, in some embodiments, the intrinsic a-Si:H passivation layer can include a bi-layer structure. FIG. 2 shows an exemplary photovoltaic structure, according to an embodiment of the present invention. In FIG. 2, photovoltaic structure 200 can include substrate 202, front passivation sub-layers 204 and 206, back passivation sub-layers 208 and 210, surface-field layer 212, emitter layer 214, and electrode grids 216 and 218.

[0038] Various layers of photovoltaic structures 200 can be similar to the corresponding layers of photovoltaic structure 100 shown in FIG. 1. For example, substrate 202 can be similar to substrate 102, surface field layer 212 can be similar to surface field layer 108, emitter layer 214 can be similar to emitter layer 110, and electrode grids 216 and 218 can be similar to electrode grids 112 and 114, respectively. [0039] Passivation sub-layers 204 and 208 are in contact with base layer 202. As discussed previously, H-rich a-Si:H can cause increased Dir. Hence, it can be desirable for passivation sub-layers 204 and 208 to be low in H content. In some embodiments, passivation sub-layers 204 and 208 can be formed using a CVD process that does not use H<sub>2</sub> as a precursor. In one embodiment, only silane can be used as the precursor gas during the CVD processes that form passivation sub-layers 204 and 208. In one embodiment, a combination of silane and one or more inert gases (e.g., Ar) may be used during the CVD processes that form passivation sub-layers 204 and 208. In some embodiments, the thickness of passivation sub-layers 204 and 208 can be between 10 and 50 angstroms.

[0040] On the other hand, passivation sub-layers 206 and 210 are not in direct contact with base layer 202; hence,

interface defects are less critical for these layers. Therefore, H-rich a-Si:H can be a better material choice for passivation sub-layers **206** and **210** due to its wider bandgap. In some embodiments, passivation sub-layers **206** and **210** can be formed using a CVD process that use both silane and  $\rm H_2$  as precursor gases. The ratio between the flow rates of silane and  $\rm H_2$  can be between 1 and 100, preferably between 1 and 30. This result in passivation sub-layers **206** and **210** to have higher H content than passivation sub-layers **204** and **208**. In some embodiments, one or more inert gases (e.g., Ar) can also be vented into the CVD chamber to assist the deposition (mostly for igniting the plasma during a PECVD process). In some embodiments, the thickness of passivation sub-layers **206** and **210** can be between 20 and 100 angstroms, preferably between 50 and 70 angstroms.

[0041] Other than the passivation layers, fabrications of other layers within photovoltaic structures 100 and 200 can also involve CVD processes. For example, surface field layers 108 and 212 and emitter layers 110 and 214 can also be formed using CVD processes. When a fabrication process involves multiple sequential CVD processes, a cluster CVD tool can be used to provide efficient fabrication. A cluster CVD tool can include one or more CVD chambers, which can be coupled with a robotics module operating in a common vacuum to handle wafer transport between these chambers. Within each chamber, a wafer can be held steady (for example, placed on a stable wafer carrier) and heated. When reaction gas encounters the heated surface of the wafer, solid material is deposited from the vapor by a chemical reaction occurring on or in the vicinity of the heated surface. By varying the deposition conditions (e.g., substrate material, substrate temperature, composition of the reaction gas mixture, gas flow rates, etc.), materials with different properties can be grown. Furthermore, plasma from an inert gas can be used to enhance the deposition process. Such plasma can be generated using a radio-frequency (RF) source with an injection of an inert gas flow.

[0042] When wafers undergo a CVD process in a cluster CVD tool, the wafers are static, i.e., not moving. Wafers are processed in batches in the multiple chambers. Such static processing generally results in better film quality, because the positioning and on-off timing of the reactive gases can be controlled and potentially optimized. For example, the placement of gas flows and plasma sources can be designed to improve film uniformity across all wafers held in a stationary wafer carrier. Furthermore, the plasma can be ignited after the wafers are stable in their positions, their temperature at the desired setting, and the gas flow rates/processing pressure stabilized to ensure optimal deposition conditions.

[0043] FIG. 3 shows a cluster CVD tool. In FIG. 3, cluster CVD tool 300 can include load/unload lock 302, robotics system 320, and CVD process chambers 304, 306, 308, 310, 312, 314, and 316. During operation, wafers are first loaded in load/unload lock 302, which can function as an airlock and facilitate vacuum pump-down before the wafers are transported into a CVD chamber. After the pressure in load/unload lock chamber 302 is pumped down, and optionally after the wafers have been heated to the desired temperature, robotics 320 can transport the wafers to one of the CVD chambers, such as CVD chamber 304, for film deposition. One or more of the CVD chambers can be used to deposit a number of layers. A buffer chamber can also be present between a respective CVD chamber and the center

robotics system to avoid potential cross-contamination between the deposited layers. A buffer chamber can include slit valves to separate the space on both sides of the valve, such that particles on one side are prevented from diffusing to the other side.

[0044] In a large-scale production scenario, each CVD chamber in cluster CVD tool 300 can accommodate multiple Si wafers, and cluster CVD tool 300 can be configured to have independent control in each chamber to allow for simultaneous deposition in all chambers. For example, it can be possible to configure first subset of the chambers of cluster CVD tool 300 for the deposition of intrinsic a-Si layers and a second subset of chambers for the deposition of doped a-Si layers. Si wafers can be loaded into the first subset of chambers for the deposition of the intrinsic a-Si layers (the passivation layers), and then be transported, within cluster CVD tool 300, to the second subset of chambers for the deposition of a doped a-Si layer (the surface field or emitter layer). This way, a relatively large batch (e.g., tens) of Si wafers can be simultaneously processed.

[0045] In addition to arranging the multiple CVD chambers in a cluster formation, it can also be possible to arrange the multiple CVD chambers in a linear formation. FIG. 4 shows a linear CVD tool. In FIG. 4, linear CVD tool 400 can include load lock 402, a number of static CVD chambers (CVD chambers with a static carrier, e.g., chambers 406 and 410), a number of buffer chambers (e.g., buffers 404, 408, and 412), and unload lock 414. The multiple CVD chambers can allow for deposition of multiple layers, and the buffer chambers can eliminate cross-contamination between deposited layers. Each CVD chamber may accommodate multiple wafers to allow for batch processing.

[0046] During operation, wafers are first placed in load lock 402 for vacuum pump-down and optional pre-heating. Subsequently, the wafers are moved into buffer chamber 404 by, for example, a robotic or conveyor system. Next, the wafers can be sequentially moved into the multiple CVD chambers (e.g., chambers 406 and 410) with the buffer chambers (e.g., buffer 408) in between for deposition of multiple layers. Each CVD chamber can be configured independently (e.g., temperature, pressure, precursors, RF powers, etc.) based on the desired material make-up and/or film quality of the corresponding layer. During deposition, the wafers are held steady and processed in a batch. Because the CVD environment is static (i.e., the wafers are not moving), linear CVD tool 400 can produce high-quality films. After the CVD processes, the wafers are then sent into buffer chamber 412, and unload lock 414 for vacuum release and cooling, before they are taken out of linear CVD tool

[0047] Although the cluster CVD tool and the linear CVD tool can allow for parallel processing of a batch of Si wafers, their capacities can be limited by the number of chambers and the size of each chamber. In addition, the entire system is static, meaning that wafers need to wait for the vacuum pumping down, the heating, the stabilization of gas pressure, the ignition of the plasma, etc. The limited chamber capacity and the required wait time can limit the overall throughput of the deposition system. In practice, large-scale manufacturing facilities of photovoltaic structures often rely on inline CVD tools for high-throughput fabrication. In an inline CVD tool, the wafers are placed on a carrier that can continuously move through a deposition chamber while

radicals are deposited onto the surface of the wafers. When multiple layers are needed, the wafer carrier can also transfer the wafers from one deposition chamber to the next.

[0048] FIG. 5 shows an inline-processing CVD tool. In FIG. 5, inline-processing CVD 500 tool can include load lock chamber 502, a number of inline CVD chambers (CVD chambers with a moving carrier, e.g., chambers 506 and 510), a number of buffer chambers (e.g., buffers 504, 508, and 512), and unload lock 514. This inline system is different from the static system shown in FIG. 4 in that the CVD chambers here are inline-processing chambers, meaning that the wafer carriers are moving (as indicated by the arrow in the chamber) during the CVD process. In the inline-processing chamber, the gases (e.g., precursor gases) flow continuously and the process pressure is constantly maintained. There is no need for the wafers to wait for stabilization of the gas flow rate and process pressure. Once the wafers enter an inline-processing CVD chamber, the RF power turns on to ignite the plasma, and the wafer carrier moves through the plasma-filled chamber while the film is deposited. Inline-processing CVD tool 500 can achieve higher throughput compared to the static tools, because the wafers processed in the inline tool do not need to stop in the CVD chamber. The tradeoff, however, is that the quality of the film produced by the inline CVD tool can be less than that produced by a static CVD tool due to the non-controllable plasma conditions. More specifically, inline CVD may not be able to deposit high-quality intrinsic a-Si film that can meet the passivation requirements of a high-efficiency photovoltaic structure.

[0049] To meet the passivation requirements while maintaining high fabrication throughput, some embodiments of the present invention can provide a CVD system that can combine both a static CVD chamber and an inline CVD chamber. This way, both high film quality (provided by the static CVD process) and high production throughput (provided by the inline CVD process) can be achieved. During fabrication of many types of semiconductor devices, such as photovoltaic structures, high film quality is usually only required at certain critical layers or interfaces between layers. For example, for heterojunction photovoltaic structures, it can be critical to maintain low  $D_{ii}$  at the junctions, meaning that the corresponding films (e.g., the passivation sub-layer that is in contact with the base layer) should have superior film quality in terms of uniformity and defect density. Other layers (e.g., the passivation sub-layer that is not in contact with the base layer and/or the surface field/ emitter layer) have less stringent quality requirements.

[0050] In some embodiments, a novel CVD system can include one or more static-processing CVD chambers combined with one or more inline-processing CVD chambers in a linear fashion. The layers with a higher film-quality requirement can be fabricated using the static-processing chamber(s), which can produce better quality films but can take longer time. The layers with a lower quality requirement can be fabricated using the inline-processing chamber (s), where the wafers continuously move through such chamber(s) to attain higher production throughput.

[0051] FIG. 6 shows a combined CVD tool, according to one embodiment of the present invention. In FIG. 6, combined CVD tool 600 can include load lock 402, buffer chamber 604, static CVD chamber (CVD chamber with a static carrier) 606, buffer chamber 608, inline CVD chamber (CVD chamber with a moving carrier) 610, buffer 612,

inline CVD chamber 614, buffer 616, and unload lock 618. During operation, the wafers can first enter load lock 602 for vacuum pump-down and optional pre-heating. This process can be a static process. The wafers can then be moved into static CVD chamber 606 via buffer chamber 604. Static CVD chamber 606 can be configured to accommodate a wafer carrier that can hold a large number (e.g., tens or hundreds) of wafers. To reduce contamination, the wafer carrier can be a graphite or carbon fiber composite (CFC) carrier coated with a low-porosity material, such as pyrolytic carbon or silicon carbide. The wafer carrier may also include a non-flat surface or a partially carved-out structure at the bottom of the wafer-holding pockets. In static CVD chamber 606, the wafers are held steady to undergo a CVD process that can grow a high-quality film with low D<sub>it</sub> (e.g, a passivation layer that interfaces with the Si base layer).

[0052] After this static CVD process, the wafers can be moved into buffer chamber 608. Note that at this point another batch of wafers can be moved into static CVD chamber 606 for processing, so that a pipelined operation can be achieved.

[0053] Next, the wafers can be placed onto a moving carrier (e.g., a wafer carrier on a conveyor) and moved from buffer chamber 608 into inline CVD chamber 610, which can already have the precursor influx turned on and the pressure inside the chamber maintained to a constant value. Once the wafers enter inline CVD chamber 610, RF power will be turned on to ignite the plasma. The wafers can continue their movement, without stopping, through inline CVD chamber 610 during this stage of the CVD process, which can deposit a film layer (e.g., a passivation layer that does not directly interface with the Si base layer) onto a large number of Si wafers in a short time period. The moving speed of the wafer carrier can be configured according to the desired layer thickness. After being processed inside inline CVD chamber 610, the wafers can continue their movement into the next inline CVD chamber 614 via buffer 612 for additional inline CVD processing. The continuous movement of the wafer carrier can bring the wafers to buffer 616 and eventually unload lock 618, before they are taken out of combined CVD tool 600. For high throughput, it can be desirable to have the wafer carrier moving at a steady speed, meaning that the settings (e.g., gas flow rate, RF power, etc.) of the multiple inline chambers should be adjusted based on a common moving speed. In certain scenarios (e.g., when there is a drastic difference in film thickness), the wafer carrier may move with different speeds in different inline chambers. However, this can introduce delay between processing, and thus may reduce fabrication throughput. Note that, in general, wafers can stay inside static CVD chamber 606 for the longest amount of time in order to obtain a high-quality film; hence, this can be the "bottleneck" for the entire tool and can determine the overall system throughput. [0054] Compared to conventional static CVD tools (e.g., a cluster CVD tool or a liner CVD too) and inline CVD tools, which only include either static-processing chambers or inline-processing chambers, but not both, this combined CVD tool can offer the best of both worlds. That is, static CVD processing is only used for layers that require high film quality, whereas inline CVD processing can be used for other layers. As a result, the overall system throughput can be significantly improved without sacrificing film quality for the critical layers. Furthermore, this combined CVD tool can

be used not only to deposit layers with different quality

requirements, but also to deposit a single layer with varying quality requirements by depositing different portions of the same layer in different chambers (i.e., the static-processing CVD chamber and the inline-processing CVD chamber). For example, photovoltaic structures often include one or more passivation layers, and a passivation layer usually is required to have a high-quality surface near the interface with the underlying material, such as a crystalline base layer. The present combined CVD tool can be used to deposit the high-quality portion of this passivation layer in its staticprocessing chamber, and then deposit the rest of the passivation layer in its inline-processing chamber. Compared with a system that deposits the entire passivation layer using a static CVD tool, this configuration can effectively shorten the amount of time required to deposit the passivation layer (because the length of time the wafer spends in the staticprocessing CVD chamber is shortened), and overall production throughput can be increased. Compared with a system that deposits the entire passivation layer using an inline CVD tool, this configuration can provide better passivation (because a low  $D_A$  can be achieved by the static-processing CVD chamber), and the efficiency of the produced photovoltaic structures can be enhanced.

[0055] Note that the system illustrated in FIG. 6 only shows one static-processing CVD chamber followed by two inline-processing CVD chambers. In general, any number of static-processing CVD chambers and inline-processing CVD chambers can be combined, in any order, into a single tool to meet the requirement of different layers based on a given device design. In addition, a number of static-processing CVD chambers may be configured in a cluster manner, and this cluster can be part of a larger, combined CVD tool that can include other inline-processing CVD chambers. During the entire CVD process, including depositions of the different passivation layers and any additional layers, the Si wafers remain in a common vacuum space that includes both the static-processing CVD chambers and the inline-processing CVD chambers. Because the vacuum remains unbroken in all processing chambers, wafers no longer need to wait for the pumping down of the processing chambers. This can provide higher throughput compared to a fabrication process that uses individual, segregated CVD systems for the depositions of the different layers

[0056] FIG. 7 shows a combined CVD tool, according to one embodiment of the present invention. In FIG. 7, combined CVD tool 700 includes a cluster portion and an inline portion. The cluster portion can include load lock 702, static CVD chambers 704, 706, and 708 configured in a cluster fashion, and robotics system 710. The cluster portion can be coupled (while maintaining the same vacuum seal) to the inline portion, which can include buffer chamber 712, inline CVD chamber 714, buffer chamber 716, and unload lock 718. The three static chambers 704, 706, and 708 can be used to fabricate multiple high-quality layers sequentially, or used in parallel to fabricate the same layer for three batches of wafers for improved throughput. In other words, if a single static CVD chamber creates a bottleneck for the entire CVD tool (as shown in FIG. 6) and slows down the overall throughput, multiple static CVD chambers can be used to alleviate the delay. These static CVD chambers can be connected in a cluster manner and operate in parallel on multiple wafer batches to match the throughput of the rest of the tool.

[0057] As illustrated in FIG. 7, static chambers 704, 706, and 708 can process three wafer batches at the same time, while the inline portion of the tool (namely inline CVD chamber 714) can process wafer batches at a higher speed. Optionally, the wafers can move continuously without stopping through the inline portion of the system (i.e., buffer 712, inline CVD chamber 714, buffer 716, and unload lock 718) for high-throughput production.

#### **Fabrication Process**

[0058] In one embodiment of the present invention, the aforementioned combined CVD system can be used to fabricate photovoltaic structures. The specific device structure described herein is only one use case for the present combined CVD system, and should not limit the application of this CVD system to only photovoltaic structure fabrication. In the example described herein, a photovoltaic structure can have a double tunneling junction structure, and can include a lightly doped (with n- or p-type dopants) crystalline silicon (c-Si) base layer. On both sides of the c-Si base layer there can be a thin dielectric (e.g., silicon oxide) layer functioning as a tunneling layer, and a first (high-quality) intrinsic a-Si layer and a second (regular quality) intrinsic a-Si layer combined to function as a passivation layer. The first (high-quality) intrinsic a-Si layer can be grown in a static-processing chamber and the second (regular quality) intrinsic a-Si layer can be grown in an inline-processing chamber. Note that the first and second a-intrinsic silicon layers may be grown using the same or different reactive gases, and may be viewed as a high-quality portion and regular-quality portion of a single layer, or viewed as two different layers. Adjacent to the passivation layers are more heavily doped n- and p-type layers as the emitter and surface field layers (which one functions as the emitter layer typically depends on the doping type of the base layer).

[0059] FIG. 8 shows an exemplary fabrication process of a photovoltaic structure using a CVD tool that includes both static and inline chambers, according to one embodiment of the present invention. The following process is described in conjunction with FIG. 6.

[0060] In operation 8A, substrate 800 can be prepared. In some embodiments, substrate 800 can include a solar grade Si (SG-Si) wafer, which can be epitaxially grown or prepared using a Czochralski (CZ) or Float Zone (FZ) method. The thickness of substrate 800 can be between 80 and 300 microns, preferably between 110 and 180 microns. The resistivity of the SG-Si wafer can range from 0.5 ohm-cm to 10 ohm-cm. Substrate 800 can be intrinsic or lightly doped with n- or p-type dopants. In some embodiments, substrate 800 can be doped with n-type dopants and can have a doping concentration ranging from  $1\times10^{10}$ /cm<sup>3</sup> to  $1\times10^{16}$ /cm<sup>3</sup>. In further embodiments, substrate 800 can have a graded doping profile. The preparation operation can include typical saw damage etching that removes approximately 10 µm of silicon and, optionally, surface texturing. The surface texture can have various patterns, including but not limited to: hexagonal-pyramid, inverted pyramid, cylinder, cone, ring, and other irregular shapes. In one embodiment, the surfacetexturing operation can result in a random pyramid textured surface. Afterwards, substrate 800 can go through extensive surface cleaning.

[0061] In optional operation 8B, a thin dielectric layer can be formed on both the front and back surfaces of Si substrate 800 to form front and back quantum tunneling barrier (QTB)

layers 802 and 804, respectively. The dielectric layers can include an oxide layer, e.g., silicon oxide  $(SiO_x)$ . Various oxidation techniques can be used to form the oxide layer, including, but not limited to: wet oxidation, dry oxidation at relatively high temperatures (around or below  $400^{\circ}$  C.) (also known as thermal oxidation), low-pressure radical oxidation, atomic layer deposition (ALD), plasma-enhanced chemical-vapor deposition (PECVD), etc. The oxide layers can also include native oxide. The thickness of dielectric layers 802 and 804 can be between 5 and 50 angstroms, preferably between 5 and 20 angstroms, and more preferably between 5 and 15 angstroms. This operation is optional, because the subsequently formed passivation layers can also function as a quantum tunneling barrier.

[0062] Next, the wafer (which has dielectric layers 802 and 804) can be placed in load lock 602 in combined CVD tool 600 illustrated in FIG. 6. After vacuum pump-down in load lock 602 to the desired setting, the wafer is then transported by a carrier to buffer chamber 604, where the wafer can pre-heated to a desired temperature. Then, in operation 8C, the wafer can be transported into staticprocessing CVD chamber 606 to form the first passivation layer 806. In some embodiments, silane (SiH<sub>4</sub>) gas (and optionally H<sub>2</sub> gas) can be used as a precursor, and first passivation layer 806 can include intrinsic a-Si:H. To ensure low D<sub>ir</sub> it can be desirable to have the a-Si:H in the first passivation layer 806 to have a relatively low H content. Therefore, it can be preferable not to inject H<sub>2</sub> gas into the reaction chamber during operation 8C. Note that in operation 8C the wafer can be held steady in a wafer carrier, and can remain stable during the entire CVD process. More specifically, the plasma can be turned on after the flow of the gas(es) and the chamber pressure stabilize. As a result, a high-quality, uniform intrinsic a-Si (or a-Si:H) film can be formed on dielectric layer 802. The thickness of the first passivation layer 806 can be between 10 and 50 angstroms, preferably between 20 and 40 angstroms, and more preferably between 25 and 35 angstroms, or approximately 30 angstroms.

[0063] After first passivation layer 806 is formed by the static CVD process, the wafer can be sent into inlineprocessing CVD chamber 610 via buffer chamber 608. At this stage (corresponding to operation 8D in FIG. 8), a second passivation layer 808 can be formed on first passivation layer 806. In some embodiments, a combination of silane and H<sub>2</sub> gases can be used as precursors, and second passivation layer 808 can include intrinsic a-Si:H. To ensure a wide bandgap of second passivation layer 808, it can be preferable to have a relatively high H<sub>2</sub> flow rate during the CVD process. In some embodiments, the ratio between the flow rates of silane and H2 can be between 1 and 100, preferably between 1 and 30. This can result in second passivation layer 808 to have higher H content than first passivation layer 806. Because second passivation layer 808 is not in contact with dielectric layer 802 or substrate layer 800, the quality requirement for this second passivation layer can be less stringent. Therefore, the deposition of second passivation layer 808 can occur in an inline-processing CVD chamber where the wafer continuously moves through inline CVD chamber 610 during the CVD process. The thickness of second passivation layer 808 can be between 20 and 100 angstroms, preferably between 40 and 80 angstroms, more preferably between 50 and 70 angstroms.

[0064] The wider bandgap of second passivation layer 808 can provide better matching to the subsequently grown heavily doped a-Si layers (described below), resulting in a higher open-circuit voltage (Voc) for the photovoltaic structure. Meanwhile, the presence of the high-quality first passivation layer 806 can ensure low defect density at the junction interface, which can be critical to good passivation. The combination of high-quality first passivation layer 806, grown in static-processing CVD chamber 606, and second passivation layer 808, grown in inline-processing CVD chamber 610 can achieve high production throughput while maintaining high-quality passivation and device performance.

[0065] In operation 8E, the wafer can be sent into inlineprocessing CVD chamber 614, for growing a heavily doped a-Si layer 810, which can be n- or p-type doped, and can function as a surface field layer or an emitter layer. In some embodiments, heavily doped a-Si layer 810 can be n-type doped, and during operation 8E, silane, H<sub>2</sub>, and phosphine (PH<sub>3</sub>) can be used as precursors for the CVD process. In alternative embodiments, heavily doped a-Si layer 810 can be p-type doped, and during operation 8E, silane, H2, and diborane (B<sub>2</sub>H<sub>6</sub>) can be used as precursors for the CVD process. The thickness of heavily doped a-Si layer 810 can be between 2 and 50 nm, preferably between 4 and 8 nm. The doping concentration of heavily doped a-Si layer 810 can range from  $1\times10^{15}$ /cm<sup>3</sup> to  $5\times10^{20}$ /cm<sup>3</sup>. In some embodiments, heavily doped a-Si layer 810 can have a graded doping profile. More specifically, the region adjacent to second passivation layer 808 can have a lower doping concentration, and the region away from second passivation layer 808 can have a higher doping concentration. Heavily doped a-Si layer 810 can be processed in an inline CVD chamber because the film quality is less critical for heavily doped layers.

[0066] The wafer can then be taken out of the CVD tool. Optionally, the wafer can go through a wet process (e.g., being submerged in a diluted HF solution) to remove dielectric layer 804, because this layer has been contaminated by the previous CVD processes. Optionally, another fresh dielectric layer can be re-deposited. Subsequently, the wafer can be placed in a separate, similar CVD tool for fabricating a similar structure on the opposite side of base layer 800. As shown in operation 8F in FIG. 8, first passivation layer 812, second passivation layer 814, and heavily doped a-Si layer **816** (which can be p- or n-type doped, and can function as an emitter layer or a surface field layer) are grown on the opposite side of base layer 800. These layers can be grown using a combined CVD tool similar to the one illustrated in FIG. 6. Specifically, first passivation layer 812 can be grown in a static-processing CVD chamber using a process similar to operation 8C, in which silane gas or a combination of silane and H<sub>2</sub> gases can be used as precursors. Second passivation layer 814 can be grown in an inline-processing CVD chamber using a process similar to operation 8D, in which silane gas or a combination of silane and H<sub>2</sub> gases can be used as precursors. Heavily doped a-Si layer 816 can be grown in an inline-processing CVD chamber using a process similar to operation 8E.

[0067] In operation 8G, transparent conductive oxide (TCO) layers 818 and 820 are formed on heavily doped a-Si layers 810 and 816, respectively. TCO layers 818 and 820 can be formed using a physical vapor deposition (PVD) process, such as sputtering or evaporation. Materials used to

form TCO layers **818** and **820** can include, but are not limited to: tungsten doped indium oxide (IWO), indium-tin-oxide (ITO), GalnO (GIO), GalnSnO (GITO), ZnInO (ZIO), ZnInSnO (ZITO), tin-oxide (SnO $_x$ ), aluminum doped zinc-oxide (ZnO:Al or AZO), gallium doped zinc-oxide (ZnO:Ga), and their combinations.

[0068] In operation 8H, metallic grids 822 and 824 can then be formed on TCO layers 818 and 820, respectively. In some embodiments, metallic grids 822 and 824 can include a Cu grid formed using various metallization techniques, including, but not limited to: electroless plating, electroplating, sputtering, and evaporation. In further embodiments, the Cu grid can include a Cu seed layer or a metallic adhesive layer that comprises Ti or Ta, and a electroplated bulk Cu layer. The seed layer and/or the metallic adhesive layer can be deposited onto the corresponding TCO layer using a physical vapor deposition (PVD) technique, such as sputtering and evaporation. The electroplated bulk Cu layer can be at least tens of microns thick (e.g., greater than 30 microns) to ensure low series resistivity.

[0069] In the exemplary process described above, the photovoltaic structure can also be fabricated using a combined CVD tool as the one illustrated in FIG. 7. For example, the high-quality first passivation layers (layers 802 and 812) can be fabricated in the cluster portion (static-processing CVD chambers 704-708) of combined CVD tool 700. Moreover, to improve production throughput, multiple batches of wafers can undergo this batch-processing CVD process in parallel, while the rest of the CVD tool operates in an inline fashion (e.g., having wafer carriers continuously moving through various inline chambers).

### Exemplary Fabrication System

[0070] FIG. 9 shows an exemplary photovoltaic structure fabrication system, according to an embodiment of the present invention. In FIG. 9, fabrication system 900 can include wet station 902, combined CVD tools 904 and 908, PVD tools 906 and 910, and metallization station 912.

[0071] During fabrication, lightly doped Si wafers can go through wet station 902 for surface treatment (including cleaning, texturing, and wet oxidation). Si wafers emerging from wet station 902 can have a thin oxide layer on both sides.

[0072] The Si wafers can then be sent to combined CVD tool 904, which can include a static CVD chamber and multiple inline CVD chambers. The Si wafers are first sent to the static chamber of combined CVD tool 904 to grow a high-quality passivation film, and then sent to inline chambers to sequentially grow another passivation film of regular quality and a heavily doped a-Si layer. The high-quality passivation film can include intrinsic a-Si:H with low H content, and the passivation film of regular quality can include a-Si:H with high H content. Accordingly, the static chamber may only use silane as precursor, whereas the inline chamber may use both saline and H2 as precursors. If the original Si wafers are n-type doped, diborane (B<sub>2</sub>H<sub>6</sub>) may also be introduced to the last inline chamber of combined CVD tool 904 as a p-type dopant. Si wafers emerging from combined CVD tool 904 can have p-side passivation layers and the p-type emitter.

[0073] PVD tool 906 can be used to deposit the p-side TCO layer and/or metallic layers. In some embodiments, the p-side TCO layer can include TCO materials with a rela-

tively high work function (e.g., between 5 and 6 eV). Si wafers emerging from PVD tool **906** can have the complete p-side layer stack.

[0074] Subsequently, the Si wafers can be sent to combined CVD tool 908 for growing the n-side passivation layers and the n-type doped surface field layer. Combined CVD tool 908 can be similar to combined CVD 904, and n-side passivation layers can be similar to p-side passivation layers. In some embodiments, phosphine (PH<sub>3</sub>) can be introduced to the last inline chamber of combined CVD tool 908 as an n-type dopant.

[0075] PVD tool 910 can be used for the deposition of the n-side TCO layer and/or metallic layers. Si wafers emerging from PVD tool 910 can have the complete p-side layer stack and n-side layer stack.

[0076] Metallization station 912 can be used for forming the metallic grids.

[0077] The foregoing descriptions of various embodiments have been presented only for purposes of illustration and description. They are not intended to be exhaustive or to limit the present invention to the forms disclosed. Accordingly, many modifications and variations will be apparent to practitioners skilled in the art. Additionally, the above disclosure is not intended to limit the present invention.

What is claimed is:

- 1. A system for fabricating a photovoltaic structure, comprising:

- a combined chemical vapor deposition tool that includes a static deposition module and an inline deposition module;

- wherein the static deposition module is configured to deposit a first passivation layer on a first side of a crystalline Si base layer of the photovoltaic structure;

- wherein the inline deposition module is configured to deposit a second passivation layer on the first passivation layer; and

- wherein the inline deposition module is coupled to the static deposition module in a way that the photovoltaic structure can be transferred from the static deposition module to the inline deposition module without leaving a common vacuum space.

- 2. The system of claim 1, wherein the static deposition module includes multiple reaction chambers forming a cluster to allow parallel processing of multiple photovoltaic structures.

- 3. The system of claim 1, further comprising a second inline deposition module configured to deposit a heavily doped amorphous Si layer on the second passivation layer.

- **4**. The system of claim **1**, wherein the static deposition module comprises a static wafer carrier configured to remain stationary when the first passivation layer is deposited.

- **5**. The system of claim **4**, wherein the first passivation layer comprises hydrogenated amorphous Si having low hydrogen content, and wherein the static deposition module is configured to use silane gas as a precursor.

- **6**. The system of claim **1**, wherein the inline deposition module comprises a wafer carrier configured to continuously move in a predetermine direction when the second passivation layer is deposited.

- 7. The system of claim 6, wherein the second passivation layer comprises hydrogenated amorphous Si having high hydrogen content, and wherein the inline deposition module is configured to use silane gas and hydrogen gas as precursors.

- **8**. The system of claim **1**, further comprising a buffer module positioned between the static deposition module and the inline deposition module.

- 9. The system of claim 1, further comprising a wet station configured to form a wet oxide layer on both surfaces of the Si base layer.

- 10. The system of claim 1, further comprising a physical vapor deposition module configured to deposit a transparent conductive oxide layer on the heavily doped amorphous Si layer.

- 11. The system of claim 10, wherein the physical vapor deposition module is further configured to deposit a metallic layer on the transparent conductive oxide layer, wherein the metallic layer functions as an adhesive layer between the transparent conductive oxide layer and a subsequently electroplated Cu grid.

- 12. The system of claim 1, wherein the static deposition module is configured to start deposition after temperature and pressure conditions are stabilized, thereby facilitating formation of a high quality film layer.

- 13. The system of claim 1, wherein the inline deposition module is configured to have a continuous flow of reaction gases, thereby facilitating high throughput of processed photovoltaic structures.

- 14. A chemical vapor deposition system, comprising:

- a static reaction chamber configured to perform a static chemical vapor deposition process; and

- an inline reaction chamber configured to perform an inline chemical vapor deposition process;

- wherein the static reaction chamber and the inline reaction chamber are coupled to each other in such a way that a wafer can be transferred between the static reaction chamber and inline reaction chamber without leaving a common vacuum space.

- 15. The chemical vapor deposition system of claim 14, further comprising a buffer chamber positioned between the static reaction chamber and the inline reaction chamber.

- 16. The chemical vapor deposition system of claim 14, wherein the static reaction chamber comprises a static wafer carrier that is configured to remain stationary during the static chemical vapor deposition process; and

- wherein the inline reaction chamber comprising a moving wafer carrier that is configured to move continuously through the inline reaction chamber during the inline chemical vapor deposition process.

- 17. The chemical vapor deposition system of claim 14, further comprising one or more additional static reaction chambers, wherein the additional static reaction chambers and the static reaction chamber forms a cluster to allow parallel processing of multiple wafers.

- 18. The chemical vapor deposition system of claim 14, further comprising one or more additional inline reaction chambers, wherein the additional inline reaction chambers and the inline reaction chamber share a common vacuum space.

- 19. The chemical vapor deposition system of claim 14, wherein the static reaction chamber is configured to start deposition after a temperature and a pressure inside the static reaction chamber are stabilized, thereby facilitating formation of a high quality film layer.

- 20. The chemical vapor deposition system of claim 14, wherein the inline reaction chamber is configured to have a continuous flow of reaction gases, thereby facilitating high throughput of processed wafers.

\* \* \* \* \*