(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6668337号

(P6668337)

(45) 発行日 令和2年3月18日(2020.3.18)

(24) 登録日 令和2年2月28日(2020.2.28)

(51) Int.Cl.

G 11 C 11/417 (2006.01)

G 11 C 5/14 (2006.01)

F 1

G 11 C 11/417 100

G 11 C 5/14

請求項の数 15 (全 17 頁)

(21) 出願番号 特願2017-515931 (P2017-515931)

(86) (22) 出願日 平成27年8月4日 (2015.8.4)

(65) 公表番号 特表2017-529644 (P2017-529644A)

(43) 公表日 平成29年10月5日 (2017.10.5)

(86) 國際出願番号 PCT/US2015/043602

(87) 國際公開番号 WO2016/048455

(87) 國際公開日 平成28年3月31日 (2016.3.31)

審査請求日 平成30年7月12日 (2018.7.12)

(31) 優先権主張番号 14/499,052

(32) 優先日 平成26年9月26日 (2014.9.26)

(33) 優先権主張国・地域又は機関

米国(US)

(73) 特許権者 507364838

クアルコム、インコーポレイテッド

アメリカ合衆国 カリフォルニア 921

21 サン デイエゴ モアハウス ドラ

イブ 5775

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100163522

弁理士 黒田 晋平

(72) 発明者 フランソワ・イブラヒム・アタラー

アメリカ合衆国・カリフォルニア・921

21-1714・サン・ディエゴ・モアハ

ウス・ドライブ・5775・クアルコム・

インコーポレイテッド

最終頁に続く

(54) 【発明の名称】レジスタファイル回路および最小動作供給電圧を改善するための方法

## (57) 【特許請求の範囲】

## 【請求項 1】

レジスタファイル回路であって、

仮想供給電圧および書き込みワード線に結合されたメモリセルと、

ゲート、ソース、およびドレインを有する第1のヘッダPFETであって、前記第1のヘッダ

PFETのソースがシステム供給電圧に結合され、前記第1のヘッダPFETのゲートが書き込み信

号を受信するためにドライバ回路の出力信号に結合され、前記第1のヘッダPFETのドレイ

ンが前記仮想供給電圧に結合される第1のヘッダPFETと、

ゲート、ソース、およびドレインを有する第1のヘッダNFETであって、前記第1のヘッダ

NFETのドレインが前記仮想供給電圧に結合され、前記第1のヘッダNFETのゲートが書き込み

信号を受信するために前記ドライバ回路の前記出力信号に結合され、前記第1のヘッダNFE

Tのソースがグランドに結合される第1のヘッダNFETと、

ゲート、ソース、およびドレインを有する第2のヘッダNFETであって、前記第2のヘッダ

NFETのドレインが前記システム供給電圧に結合され、前記第2のヘッダNFETのゲートが書

込み信号を受信するために前記ドライバ回路の前記出力信号に結合され、前記第2のヘッ

ダNFETのソースが前記仮想供給電圧に結合される第2のヘッダNFETとを備え、

前記第2のヘッダNFETは、前記仮想供給電圧を前記第1のヘッダNFETと前記第2のヘッダN

FETの比に応じた電圧にクランプする、レジスタファイル回路。

## 【請求項 2】

前記第1のヘッダNFETは、前記仮想供給電圧を前記グランドまで放電させる、または、

10

20

前記ドライバ回路は、可変出力パルス幅を有するパルス発生器を備える、請求項1に記載のレジスタファイル回路。

**【請求項3】**

前記ドライバ回路は、可変出力パルス幅を有するパルス発生器を備え、

前記ドライバ回路は、前記第1のヘッダNFETのゲート、前記第2のヘッダNFETのゲート、および前記第1のヘッダPFETのゲートに結合されるパルス書き込み信号を出力する、請求項1に記載のレジスタファイル回路。

**【請求項4】**

前記ドライバ回路は書き込みクロック信号を入力し、前記パルス書き込み信号は、書き込みワード線信号がアクティブになる前に出力される、請求項3に記載のレジスタファイル回路<sup>10</sup>。

**【請求項5】**

前記パルス書き込み信号は、前記メモリセルに対して書き込み動作を実行するのに十分な時間を前記メモリセルに与える書き込み完了時間が得られるように設定されたパルス幅を有する、請求項4に記載のレジスタファイル回路。

**【請求項6】**

前記メモリセルは、

ゲート、ソース、およびドレインを有する第1のPFETであって、前記第1のPFETのソースが前記仮想供給電圧に結合される第1のPFETと、

ゲート、ソース、およびドレインを有する第2のPFETであって、前記第2のPFETのソースが前記仮想供給電圧に結合される第2のPFETと、<sup>20</sup>

ゲート、ソース、およびドレインを有する第1のNFETであって、前記第1のNFETのドレインが前記第1のPFETのドレインに結合され、前記第1のNFETのゲートが前記第1のPFETのゲートに結合される第1のNFETと、

ゲート、ソース、およびドレインを有する第2のNFETであって、前記第2のNFETのドレインが前記第2のPFETのドレインに結合され、前記第2のNFETのゲートが前記第2のPFETのゲートに結合される第2のNFETと、

ゲート、ソース、およびドレインを有する第3のNFETであって、前記第3のNFETのゲートが前記書き込みワード線に結合され、前記第3のNFETのドレインが前記第2のPFETのゲートおよび前記第2のNFETのゲートに結合される第3のNFETと、<sup>30</sup>

ゲート、ソース、およびドレインを有する第4のNFETであって、前記第4のNFETのゲートが前記書き込みワード線に結合され、前記第4のNFETのドレインが前記第1のPFETのゲートおよび前記第1のNFETのゲートに結合される第4のNFETとを備える、請求項1に記載のレジスタファイル回路。

**【請求項7】**

前記第1のヘッダPFETは、前記第1のヘッダNFETおよび第2のヘッダNFETがオフのときはオンになり、前記第1のヘッダNFETおよび前記第2のヘッダNFETがオンのときはオフになるように構成される、請求項6に記載のレジスタファイル回路。

**【請求項8】**

第1の共通ノードおよび第2の共通ノードをさらに備え、前記第1の共通ノードが真ビット線を備え、前記第2の共通ノードが補ビット線を備える、請求項6に記載のレジスタファイル回路。<sup>40</sup>

**【請求項9】**

前記第1の共通ノードは、前記第1のNFETのドレインに接続するように動作可能に構成され、前記第2の共通ノードは、前記第2のNFETのドレインに接続するように構成される、請求項8に記載のレジスタファイル回路。

**【請求項10】**

前記第1の共通ノードおよび前記第2の共通ノードは、前記メモリセルに対する書き込み動作を実施するときに相補論理電圧に駆動される、請求項9に記載のレジスタファイル回路<sup>50</sup>。

**【請求項 1 1】**

前記ドライバ回路は、パルス書き込み信号を出力し、前記パルス書き込み信号が論理値ハイであるとき、前記第1のヘッダPFETがオフになり、前記第1のPFETおよび前記第2のPFETをオフにさせる、請求項10に記載のレジスタファイル回路。

**【請求項 1 2】**

前記第1のヘッダPFETは、前記第1のヘッダNFETおよび第2のヘッダNFETがオフのときはオンになり、前記第1のヘッダNFETおよび前記第2のヘッダNFETがオフのときはオフになるように構成される、請求項11に記載のレジスタファイル回路。

**【請求項 1 3】**

前記メモリセルは、モバイルフォン、モバイル通信デバイス、ペーディヤ、携帯情報端末、個人情報マネージャ、モバイルハンドヘルドコンピュータ、ラップトップコンピュータ、ワイヤレスデバイス、またはワイヤレスモデムのうちの1つに組み込まれる、請求項1に記載のレジスタファイル回路。 10

**【請求項 1 4】**

各々が、仮想供給電圧および書き込みワード線に結合された、複数のメモリセルと、各々が、ゲート、ソース、およびドレインを有する、複数のヘッダPFETであって、各ヘッダPFETのソースがシステム供給電圧に結合され、各ヘッダPFETのゲートが書き込み信号を受信するためにドライバ回路の出力信号に結合され、各ヘッダPFETのドレインが前記仮想供給電圧に結合される複数のヘッダPFETとをさらに備える、請求項1から13のいずれか一項に記載のレジスタファイル回路。 20

**【請求項 1 5】**

レジスタファイル回路内のメモリセルに書き込む方法であって、書き込みクロック信号を受信するステップと、パルス書き込み信号を生成するステップと、前記パルス書き込み信号を第1のヘッダPFETのゲートに印加して前記第1のヘッダPFETをオフにし、供給電圧からメモリセルまでの電流経路を遮断するステップと、

前記パルス書き込み信号を第1のヘッダNFETのゲートおよび第2のヘッダNFETのゲートに印加して前記第1のヘッダNFETおよび前記第2のヘッダNFETをオンにし、仮想供給電圧を前記第1のヘッダNFETと前記第2のヘッダNFETの比に応じた電圧にクランプするステップであって、前記第1のヘッダNFETが、前記仮想供給電圧に結合されたドレインを有し、前記第2のヘッダNFETが、前記供給電圧に結合されたドレインを有する、ステップと、 30

前記メモリセルに書き込みビット信号を印加して前記メモリセルに対する前記書き込み動作を有効化するステップとを含む、方法。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本開示は、概してレジスタファイル回路に関し、より詳細には、限定はしないが、メモリセル用のレジスタファイル回路に関する。

**【背景技術】****【0 0 0 2】**

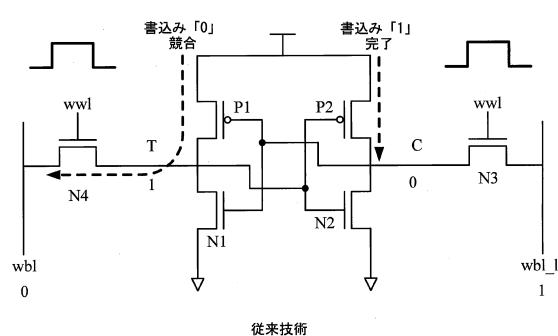

プロセッサがより複雑になるにつれて、プロセッサによって使用されるエネルギーが増大し、エネルギー使用率を最大にすることがより重要になる。プロセッサのエネルギー効率を最大にするために、プロセッサ設計では、性能要件の低いアプリケーションについては供給電圧(VDD)を低下させる(スケーリング)。たとえば、レジスタファイル回路には、書き込み動作を首尾よく実行するための最小動作VDD(VMIN)が必要である。レジスタファイルアレイはプロセッサ全体にわたって分散されているので、レジスタファイル回路とプロセッサ論理は同じVDDを共有する。このことに起因して、書き込み動作用のレジスタファイルVMINは、プロセッサVDDの全体的なスケーリングおよびエネルギーに関する潜在的な利点を限定する。図1に示すように、レジスタファイルVMINは、ノード「T」を接地させるのを試みるNFET転送デバイス(N4)とノード「T」をVDDに保持するのを試みるPFETプルアップ

40

50

デバイス(P1)との間の競合経路において生じる。他方のNFET転送デバイス(N3)が弱い「1」(VDD-Vt)(Vtはトランジスタしきい値電圧である)を補ノード「C」内に転送し、かつP1のゲートに送るので、P1デバイスは、部分的にオンのままであり、N4デバイスがノード「T」を接地させるのに抵抗する。この競合は、VDDが低下し、特にプロセスがNFETデバイスが低速になりPFETデバイスが高速になるようにスキューリングすると激しくなる。各構造は、すべてのプロセスコーナーにわたって動作する必要があるので、この競合はレジスタファイル回路のVMINを限定し、したがって、プロセッサエネルギー効率を限定する。従来のプロセッサのシミュレーションでは、レジスタファイルVMINによって、プロセッサのエネルギー節約における損失が26%を超える。

**【発明の概要】**

10

**【発明が解決しようとする課題】**

**【0003】**

したがって、本明細書で提供する改善された方法および装置を含む、従来の方法を改善する方法に対する長年にわたる産業界のニーズが存在する。

**【0004】**

本教示を特徴付ける発明性がある特徴は、さらなる特徴および利点とともに、詳細な説明および添付の図からより十分に理解される。図面の各々は例示および説明のみのために与えられ、本教示を限定しない。

**【課題を解決するための手段】**

**【0005】**

20

以下は、本明細書で開示する装置および方法に関する1つまたは複数の態様および/または例に関する簡略化された概要を提示する。したがって、以下の概要是、すべての企図される態様および/または例に関する広範囲にわたる概説と見なされるべきではなく、また、以下の概要是、すべての企図される態様および/もしくは例に関する主要もしくは重要な要素を識別するか、または任意の特定の態様および/もしくは例に関する範囲を定めると見なされるべきでもない。したがって、以下の概要是、以下に提示される詳細な説明に先立って、本明細書で開示する装置および方法に関する1つまたは複数の態様および/または例に関する特定の概念を簡略化された形で提示することが唯一の目的である。

**【0006】**

30

本開示のいくつかの例は、レジスタファイルピットセルなどのメモリセルの書き込み動作に必要な最小動作電圧を改善するためのシステム、装置、および方法を対象とする。

**【0007】**

本開示のいくつかの例では、このシステム、装置、および方法は、仮想供給電圧および書き込みワード線に結合されたメモリセルと、ゲート、ソース、およびドレインを有する第1のヘッダPFETであって、ヘッダPFETのソースがシステム供給電圧に結合され、ヘッダPFETのゲートがドライバに結合され、ヘッダPFETのドレインが仮想供給電圧に結合される第1のヘッダNFETと、第1のヘッダNFETのドレインが仮想供給電圧に結合され、第1のヘッダNFETのゲートがドライバに結合され、第1のヘッダNFETのソースがグランドに結合される第1のヘッダNFETと、ゲート、ソース、およびドレインを有する第2のヘッダNFETであって、第2のヘッダNFETのドレインがシステム供給電圧に結合され、第2のヘッダNFETのゲートがドライバに結合され、第2のヘッダNFETのソースが仮想供給電圧に結合される第2のヘッダNFETとを含む。

**【0008】**

40

本明細書で開示する装置および方法に関する他の特徴および利点は、添付の図面および詳細な説明に基づいて、当業者には明らかになるであろう。

**【0009】**

添付の図面は、本教示の例について説明するために提示され、限定するためのものではない。添付の図面は、本開示の例の説明を助けるために提示され、各例の限定ではなく、例示のみを目的として提供される。

50

## 【0010】

以下の詳細な説明を参照しながら、本開示を限定するためではなく単に例示するためには提示される添付の図面とともに検討すれば、本開示の態様およびその付随する利点の多くがよりよく理解されるようになるので、それらに関するより完全な諒解が容易に得られるであろう。

## 【図面の簡単な説明】

## 【0011】

【図1】従来のレジスタファイルビットセルを示す図である。

【図2A】本開示のいくつかの例による例示的なユーザ機器(UE)を示す図である。

【図2B】本開示のいくつかの例による例示的なプロセッサを示す図である。 10

【図3】本開示のいくつかの例による書き込みワード線(WWL)を有する例示的なメモリセルを示す図である。

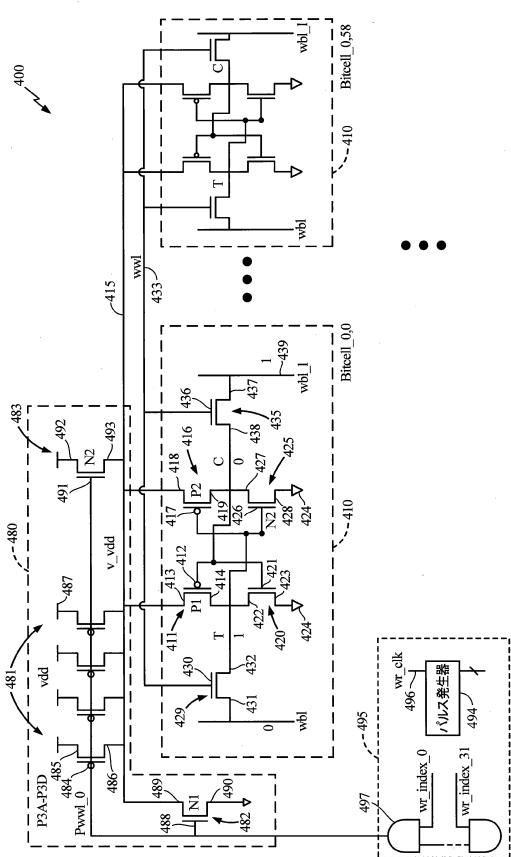

【図4】本開示のいくつかの例によるヘッダトランジスタを有する例示的なレジスタファイル回路を示す図である。

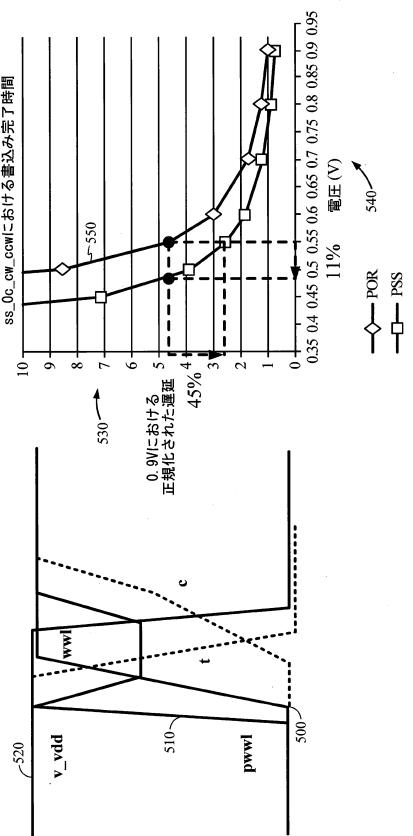

【図5】本開示のいくつかの例によるレジスタファイル回路に関する書き込みプロセスの例示的なタイミング図および完了時間グラフである。

## 【発明を実施するための形態】

## 【0012】

慣例に従って、図面に示される特徴は、一定の縮尺で描かれていない場合がある。したがって、示された特徴の寸法は、図を明快にするために、任意に拡大または縮小されている場合がある。慣例に従って、図面のうちのいくつかは、明快にするために簡略化されている。したがって、図面は、特定の装置または方法のすべての構成要素を示すとは限らない。さらに、同様の参照番号は、本明細書および図を通して同様の特徴を示す。 20

## 【0013】

レジスタファイルビットセルなどのメモリセルの書き込み動作に必要な最小動作電圧を改善するための方法、装置、およびシステムが提供される。本開示のいくつかの例では、メモリビットセルに書き込むためのVMINがより低く、したがって、全体的なプロセッサVMINを低下させるレジスタファイル回路について説明する。

## 【0014】

本開示のいくつかの例では、仮想vddを迅速に放電させるかまたはクランプするためのヘッダトランジスタ回路を追加することによってメモリセルにおける書き込み競合をなくすかまたは弱めることによって書き込みVMINを低下させる。仮想vddは、書き込み完了に悪影響を与えることなく書き込める程度に低い電圧にクランプされてもよい。ヘッダトランジスタ回路は、メモリセルのPFETと直列接続され、したがって、仮想VDDノードを形成する1つまたは複数のPFETヘッダを含んでもよい。書き込み中の行に関するPFETヘッダのゲートは、パルス書き込み信号によって制御されてもよく、このパルス書き込み信号は、書き込みクロックをアサートすることによって生成されてもよい。書き込みクロックがアクティブ化されると、PFETヘッダは、書き込み動作の間競合するメモリセルPFETへの電流経路を遮断する。本開示のいくつかの例では、PFETヘッダは、局的にビットセルごとに設けられてもよい。ヘッダトランジスタ回路は、v\_vddが、PFETヘッダがオフの場合は電圧をv\_vddに保持する大きいキャパシタンスを有するので、仮想VDDノードを放電させ書き込み動作の間の競合を抑制するためにv\_vddとグランドとの間に挿入されるNFETプルダウンを含んでもよい。ヘッダトランジスタ回路は、PFETヘッダと並列に配置され、仮想VDDノードをメモリセル内のプルアップPFETのしきい値電圧よりもわずかに低い電圧にクランプしてプルアップPFETがほぼオフになるようにし、仮想VDDノードがグランドまで放電するのを防止するクランプNFETを含んでもよい。 40

## 【0015】

本開示のいくつかの例では、ヘッダトランジスタ回路は、書き込みクロックがアクティブ化されるときに書き込みワード線に対するある範囲の可能なパルス幅および位置を生成するプログラム可能なパルス発生器を含んでもよい。パルス発生器は、構成ビットを使用して 50

パルス書き込み信号の幅および位置を調節し、プロセス変動全体にわたる最適なパルス幅の較正を有効化して部品またはプロセッサピン当たりのレジスタファイルVMINを最小限に抑えることができる。

#### 【0016】

本明細書の説明では、「書き込み」という用語は、当技術分野で知られる「記憶」動作と同義的に使用される。同様に、「読み取り」という用語は、「ロード」と同義的に使用される。さらに、本説明では、キャッシュライン全体に関する読み取り/書き込み動作よりも粒度が小さくなり得る「キャッシュブロック」に関する読み取り/書き込み動作について参照することがある。しかしながら、そのような参照は、説明のためのものにすぎず、本開示の範囲を限定するものと解釈されるべきでないことは理解されよう。たとえば、開示される技法は、適用可能な場合、キャッシュワード、キャッシュラインなどの任意の他の粒度の動作に容易に拡張することができる。さらに、データの書き込み/読み取り動作のみに関して説明する場合であっても、参照されるキャッシュブロックはデータまたは命令を含むことがあることも理解されよう。加えて、より低いレベルのメモリ階層に対する参照は、プロセッサまたは処理要素に関連付けられ得るローカルまたは第1のレベルの(L1)キャッシュ以外の補助記憶要素を含むことがある。たとえば、本明細書における、より低いレベルのメモリ階層に対する参照は、第2のレベルの(L2)キャッシュ、メインメモリ、および、L2キャッシュとメインメモリとの間に存在する場合がある1つまたは複数のレベルのメモリ構造を指すことがある。

#### 【0017】

本開示に関する具体例を示すために、以下の説明および関連する図面において様々な態様が開示される。代替的な例は、本開示を読んだときに当業者に明らかになり、本開示の範囲または趣旨を逸脱することなく構築され、実践されてもよい。加えて、本明細書で開示される態様および例の関連する詳細を不明瞭にしないように、よく知られている要素は詳細には説明されず、または省略される場合がある。

#### 【0018】

「例示的な」という単語は、本明細書では、「例、実例、または例証として働く」を意味するのに使用される。「例示的」として本明細書に記載されるいすれの詳細事項も、必ずしも他の例よりも好ましいか、または有利であると解釈されるべきでない。同様に、「例」という用語は、すべての例が説明する特徴、利点または動作モードを含むことを必要としない。本明細書において「一例では」、「例」、「1つの特徴では」、および/または「特徴」という用語を使用する場合、必ずしも同じ特徴および/または例を指すとは限らない。さらに、特定の特徴および/または構造は、1つもしくは複数の他の特徴および/または構造と組み合わせることができる。その上、本明細書で説明する装置の少なくとも一部分は、本明細書で説明する方法の少なくとも一部分を実行するように構成することができる。

#### 【0019】

本明細書で使用される用語は、特定の例を説明することのみを目的とし、本開示の例を限定することは意図されない。本明細書で使用される単数形「a」、「an」、および「the」は、文脈が別段に明確に示さない限り複数形を含むことを意図する。本明細書で使用するとき、「備える(comprises)」、「備えている(comprising)」、「含む.includes)」、および/または「含んでいる(including)」という用語は、述べられた特徴、整数、ステップ、動作、要素、および/または構成要素の存在を明示するが、1つまたは複数の他の特徴、整数、ステップ、動作、要素、構成要素、および/またはそれらのグループの存在または追加を排除するものではないことがさらに理解されよう。

#### 【0020】

「接続される」、「結合される」という用語、またはそれらのいかなる変形形態も、要素間の直接的または間接的な任意の接続または結合を意味し、仲介要素を介して互いに「接続」または「結合」される2つの要素間の仲介要素の存在を含むことができることに留意されたい。要素間の結合および/または接続は、物理的、論理的、またはそれらの組合

せであってもよい。本明細書で使用する要素は、たとえば、1つまたは複数のワイヤ、ケーブル、および/またはプリントされた電気接続部を使用することによって、ならびに電磁エネルギーを使用することによって互いに「接続」または「結合」できる。電磁エネルギーは、無線周波数領域、マイクロ波領域、および/または光学的(可視と不可視の両方の)領域の波長を有することができる。これらは、いくつかの非限定的かつ非網羅的な例である。

#### 【0021】

「信号」という用語は、データ信号、オーディオ信号、ビデオ信号、マルチメディア信号、アナログ信号、および/またはデジタル信号などの任意の信号を含むことができるこ<sup>10</sup>とを理解されたい。多種多様な技術および技法のうちのいずれかを使用して情報および信号を表すことができる。たとえば、本説明で説明するデータ、命令、処理ステップ、コマンド、情報、信号、ビット、および/もしくはシンボルは、電圧、電流、電磁波、磁場および/もしくは磁性粒子、光場および/もしくは光学粒子、またはそれらの任意の組合せによ<sup>10</sup>って表すことができる。

#### 【0022】

本明細書における「第1の」、「第2の」などの呼称を使用する要素へのあらゆる参照は、これらの要素の数量および/または順序を限定するものではない。むしろ、これらの呼称は、2つ以上の要素、および/または要素の例を区別する都合のよい方法として使用されている。したがって、第1および第2の要素への参照は、2つの要素のみを使用することができること、または第1の要素が第2の要素に必ず先行しなければならないことを意味しない。<sup>20</sup>また、別段に記載されていない限り、一組の要素は、1つまたは複数の要素を備えることができる。加えて、本説明または特許請求の範囲で使用される「A、B、またはCのうちの少なくとも1つ」という形態の用語は、「AもしくはBもしくはCまたはこれらの要素の任意の組合せ」と解釈できる。

#### 【0023】

さらに、多くの例について、たとえば、コンピューティングデバイスの要素によって実行されるべきアクションのシーケンスの観点から説明する。本明細書において説明される様々なアクションは、特定の回路(たとえば、特定用途向け集積回路(ASIC))によって実行することも、あるいは1つまたは複数のプロセッサによって実行されるプログラム命令によって実行することも、あるいはその両方の組合せによって実行することも可能であることが認識されよう。加えて、本明細書で説明するこれらの一連のアクションは、実行されると、関連するプロセッサに本明細書で説明する機能を実行させる、対応するコンピュータ命令のセットを記憶した任意の形態のコンピュータ可読記憶媒体の任意の形態において完全に具現化されるものと見なすことができる。したがって、本開示の様々な態様は、すべてが特許請求される主題の範囲内のものであると考えられるいくつかの異なる形態において具現化されてもよい。加えて、本明細書で説明する例ごとに、任意のそのような例の対応する形態は、本明細書では、たとえば、説明するアクションを実行する「ように構成された論理」として記載される場合がある。

#### 【0024】

本説明では、特定の特徴について説明するために特定の用語が使用される。「モバイルデバイス」という用語は、限定はしないが、モバイルフォン、モバイル通信デバイス、ページャ、携帯情報端末、個人情報マネージャ、モバイルハンドヘルドコンピュータ、ラップトップコンピュータ、ワイヤレスデバイス、ワイヤレスモデム、および/または通常個人によって持ち運ばれ、かつ/もしくは通信機能(たとえば、ワイヤレス、セルラー、赤外線、短距離無線など)を有する他のタイプの携帯型電子デバイスを表すことができる。さらに、「ユーザ機器」(UE)、「モバイル端末」、「モバイルデバイス」、および「ワイヤレスデバイス」という用語は、交換可能である場合がある。

#### 【0025】

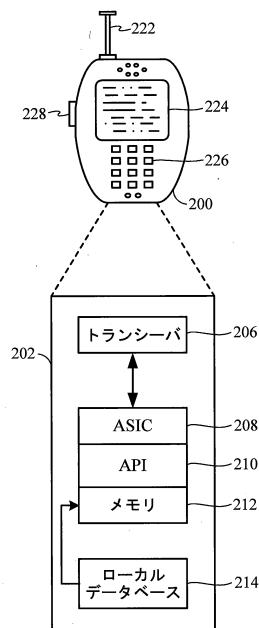

図2Aを参照すると、システム100は、セルラー電話機などのUE200(ここではワイヤレスデバイス)を含む。UE200は、プラットフォーム202を有し、プラットフォーム202は、無線

10

20

30

40

50

アクセスネットワーク(RAN)から送信され、最終的には、コアネットワーク、インターネット、および/または他のリモートサーバおよびネットワークから得られる場合があるソフトウェアアプリケーション、データ、および/またはコマンドを受信し実行することができる。プラットフォーム202はトランシーバ206を備えてよく、トランシーバ206は、特定用途向け集積回路(「ASIC」208)、または、他のプロセッサ、マイクロプロセッサ、論理回路、もしくは他のデータ処理デバイスに、動作可能に結合される。ASIC208または他のプロセッサは、ワイヤレスデバイスのメモリ212中の任意の常駐プログラムとインターフェースするアプリケーションプログラミングインターフェース(「API」)210レイヤを実行する。メモリ212は、読み取り専用メモリもしくはランダムアクセスメモリ(RAMおよびROM)、EEPROM、フラッシュカード、または、コンピュータプラットフォームにとって一般的な任意のメモリによって構成することができる。プラットフォーム202はまた、メモリ212中で積極的には使用されないアプリケーションを保持することのできるローカルデータベース214を含むことができる。ローカルデータベース214は、通常はフラッシュメモリセルだが、磁気媒体、EEPROM、光学媒体、テープ、ソフトまたはハードディスクなど、当技術分野で知られている任意の2次記憶デバイスとすることができます。内部プラットフォーム202の構成要素はまた、当技術分野で知られているように、構成要素の中でもとりわけ、アンテナ222、ディスプレイ224、プッシュツートークボタン228、およびキーボード226など、外部デバイスに動作可能に結合されてもよい。

#### 【0026】

したがって、本開示の一例は、本明細書において説明する機能を実施する能力を含むUEを含むことができる。当業者によって理解されるように、様々な論理要素は、本明細書において開示する機能を達成するために、個別の要素、プロセッサ上で実行されるソフトウェアモジュール、またはソフトウェアとハードウェアとの任意の組合せにおいて具現化することができる。たとえば、ASIC208、メモリ212、API210、およびローカルデータベース214をすべて協調的に用いて、本明細書で開示する様々な機能をロード、記憶および実行することができ、したがって、これらの機能を実行する論理を様々な要素に分散させてもよい。代替的に、機能は1つの個別の構成要素に組み込むことができる。したがって、図2AのUE200の特徴は、単に例示にすぎないものと見なされ、本開示は、示された特徴または構成に限定されない。

#### 【0027】

UE200とRANとの間のワイヤレス通信は、符号分割多元接続(CDMA)、W-CDMA、時分割多元接続(TDMA)、周波数分割多元接続(FDMA)、直交周波数分割多重(OFDM)、グローバルシステムフォーモバイルコミュニケーションズ(GSM(登録商標))、3GPPロングタームエボリューション(LTE)、または、ワイヤレス通信ネットワークもしくはデータ通信ネットワーク中で使用できる他のプロトコルなど、種々の技術に基づくことができる。したがって、本明細書において提供する例示は、本開示の例を限定することを意図するものではなく、本開示の例の態様の説明を助けるためのものにすぎない。

#### 【0028】

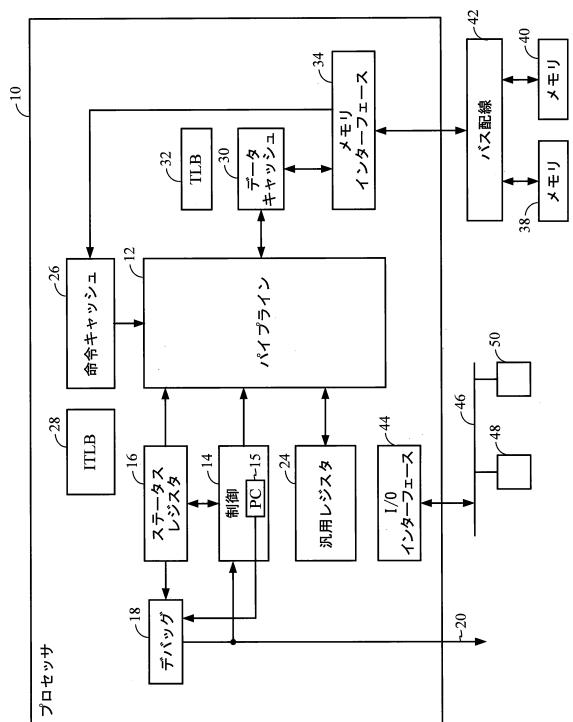

図2Bに、ビットセルへの改善された低電圧書き込み速度の特徴を組み込むように構成された、ASIC208などの例示的なプロセッサ10の機能ブロック図を示す。プロセッサ10は、制御論理14に従って、命令実行パイプライン12において命令を実行する。制御論理14は、プログラムカウンタ(PC)15を維持し、また、1つまたは複数のステータスレジスタ16中のビットをセットおよびクリアして、たとえば、現在の命令セット動作モード、算術演算の結果に関する情報、および論理比較(0、繰上り、等しい、等しくない)などを示す。いくつかの例では、パイプライン12は、複数の並列パイプラインを含むスーパースカラ設計であってもよい。パイプライン12はまた、実行ユニットと呼ばれることがある。汎用レジスタ(GPR)ファイル20は、パイプライン12によってアクセス可能な、メモリ階層の最上部を構成する汎用レジスタ24のリストを構成する。

#### 【0029】

プロセッサ10は、異なる命令セット動作モードにおける少なくとも2つの命令セットか

10

20

30

40

50

らの命令を実行するが、さらに、デバッグ回路18も備える。デバッグ回路18は、各命令の実行時に、少なくとも所定のターゲット命令セット動作モードを現在の命令セット動作モードと比較し、この2つの間の一一致を示す指示を提供するように動作する。デバッグ回路18については、以下においてより詳細に説明する。

#### 【0030】

パイプライン12は、命令側変換索引バッファ(ITLB)28によって管理されるメモリアドレス変換および許可を用いて、命令キャッシュ(Iキャッシュ)26から命令をフェッチする。主変換索引バッファ(TLB:Translation Lookaside Buffer)32によって管理されるメモリアドレス変換および許可を用いて、データキャッシュ(Dキャッシュ)30からデータがアクセスされる。様々な例において、ITLB28は、TLB32の一部のコピーを含んでよい。別法として、ITLB28とTLB32とは一体化されてもよい。同様に、プロセッサ10の様々な例で、Iキャッシュ26とDキャッシュ30とは、一体化または統合されてもよい。さらに、Iキャッシュ26およびDキャッシュ30がL1キャッシュとされてもよい。Iキャッシュ26および/またはDキャッシュ30中のミスは、メモリインターフェース34による、メイン(オフチップ)メモリ38、40へのアクセスを引き起こす。メモリインターフェース34は、1つまたは複数のメモリデバイス38、40への共有バスを実現するバス配線42へのマスタ入力であってもよく、メモリデバイス38、40は、本開示のいくつかの例による改善された低電圧書き込み速度を組み込むことができる。追加のマスタデバイス(図示せず)を、追加的にバス配線42に接続してもよい。

#### 【0031】

プロセッサ10は、入出力(I/O)インターフェース44を備えてよい。I/Oインターフェース44は、周辺バス上のマスタデバイスであってもよく、I/Oインターフェース44は、周辺バスを越えてバス46を介して様々な周辺デバイス48、50にアクセスしてもよい。プロセッサ10の多くの変形が可能であることが当業者には認識されよう。たとえば、プロセッサ10は、Iキャッシュ26とDキャッシュ30のいずれかまたは両方に関して第2のレベルの(L2)キャッシュを含んでもよい。加えて、プロセッサ10中に描かれた機能ブロックの1つまたは複数が、特定の例から省略されてもよい。JTAGコントローラ、命令プリデコーダ、分岐先アドレスキャッシュなど、プロセッサ10中に存在する場合がある他の機能ブロックは、本開示の説明と密接な関係はなく、明確にするためにこれらについては省略する。

#### 【0032】

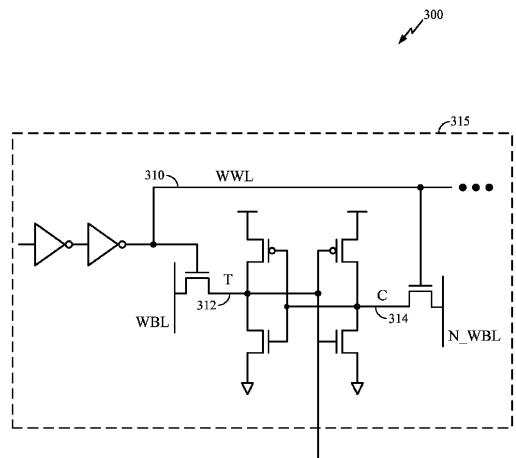

図3は、書き込みワードライン(WWL)ドライバ310を有するメモリセルまたはビットセルトランジスタ回路300を示す。6トランジスタ(6T)ビットセルは、読み出し安定性の問題を解消するために書き込みポート315を分離する6トランジスタ(6T)ビットセルに基づくシングルライトポートビットセルである。この方式は、6T部分の最適化を有効化して書き込み可能性を実現し、書き込みポート315における書き込み速度を高くる。1つの行上のビットセルは、同じWWLおよびRWLを共有し、同じ列上のビットセルは、読み取りビット線(RBL)、ワードビット線(WBL)、および補ワードビット線(N\_WBL)を共有する。真ノード312は、N型パスデバイス(NFET)およびP型パスデバイス(PFET)を介して選択的に直列に結合される共通の真ノードであり、補ノード314は、NFETおよびPFETを介して選択的に直列に結合される共通の補ノードである。共通の真ノードはTと表され、共通の補ノードはCと表される。

#### 【0033】

低電力CPUにおいて、電力を低下させる一般的な方法の1つは、供給電圧(VDD)を低下させることである。供給電圧は、供給レール(図示せず)に接続されてよい。供給電圧が低下するとき、性能の低下は、線形ではなく、供給が低減して最高V<sub>t</sub>デバイスのV<sub>t</sub>に近づくにつれて指数関数的になる。最高V<sub>t</sub>デバイスは通常、漏れ制御を目的としてメモリアレイに設けられる。

#### 【0034】

メモリビットセル中では、これらの動作特性が、データ保持と書き込み完了速度の両方について影響を与える。VDDがV<sub>t</sub>に近づくにつれて、電圧スケールダウンにより、NFETの漏れ電流がPFETの飽和電流に匹敵するようになることに起因して、スタティックランダムア

10

20

30

40

50

クセスメモリ(SRAM)に関するデータ保持の性能指数であるホールド信号雑音余裕(SNM)が低下する。一方、書き込み速度は、2つの動作、すなわち、転送NFETの1つによってTノードまたはCノードを迅速にグランドに迅速にプルする「0」書き込み相と、それに続く、プルアップPFETの1つによってCノードまたはTノードを迅速にVDDにプルする書き込み完了相に依存する。低電圧では、NFETが非常に弱いハイしか得られないときにPFETが入力をハイにプルアップする必要があるので、SNMの低下は、書き込み完了にも悪影響を及ぼす。NFET/PFETの比率は通常、2~3倍なので、PFETは非常に弱くなる傾向があり、この速度が、低電圧における最小書き込み時間(WWL310がセルに書き込むためにハイである必要のある最小時間)を決定することになる。この低下はプルアップPFETデバイスを弱めるが、最初の書き込み動作を助けるには不十分である。プルアップPFETが、TノードまたはCノードが「0」にプルされるのを妨げるために転送NFETデバイスと競合する競合経路がある。

10

#### 【0035】

低電圧における弱いPFETに対してデータ保持および書き込み速度を向上させるための最も直接的な方法は、より低い $V_t$ のデバイスのサイズを大きくするかまたはより低い $V_t$ のデバイスを使用することである。しかし、これは、すべての電圧でセルの書き込み可能性を低下させるので最適な解決法ではなく(PFETからの競合が増すことは、NFETがノードをフリップするのがより困難になることを意味する)、このことは漏れの増大につながる。

#### 【0036】

図4は、本開示のいくつかの例によるレジスタファイル回路を示す。図4に示すように、レジスタファイル回路400は、複数のメモリまたはピットセル410と、ヘッダ回路480と、ドライバ回路495とを含んでもよい。複数のメモリセル410が示されているが、単一のメモリセルが使用されてもよいことを理解されたい。さらに、メモリセル410は、読み取り回路(図示せず)を含んでもよい。

20

#### 【0037】

各メモリセル410は、ゲート412と、ソース413と、ドレイン414とを有する第1のPFET411を含んでもよい。第1のPFETのソース413は、仮想供給電圧( $v_{vdd}$ )415に結合されてもよい。各メモリセル410は、ゲート417と、ソース418と、ドレイン419とを有する第2のPFET416を含んでもよい。第2のPFETのソース418は、仮想供給電圧415に結合されてもよい。

#### 【0038】

各メモリセル410は、ゲート421と、ソース422と、ドレイン423とを有する第1のNFET420を含んでもよい。第1のNFETのソース422は第1のPFETのドレイン414に結合されてもよく、第1のNFETのゲート421は第1のPFETのゲート412に結合されてもよく、第1のNFETのドレイン423はグランド424に結合されてもよい。各メモリセル410は、ゲート426と、ソース427と、ドレイン428とを有する第2のNFET425を含んでもよい。第2のNFETのソース427は第2のPFETのドレイン419に結合されてもよく、第2のNFETのゲート426は第2のPFETのゲート417に結合されてもよく、第2のNFETのドレイン428はグランド424に結合されてもよい。図示されていないが、第2のNFETのゲートは読み取り回路に結合されてもよい。

30

#### 【0039】

各メモリセル410は、ゲート430と、ソース431と、ドレイン432とを有する第3のNFET429を含んでもよい。第3のNFETのゲート430は、書き込みワード線433に結合されてもよく、第3のNFETのドレイン432は、第2のPFETのゲート417および第2のNFETのゲート426に結合されてもよく、第3のNFETのソース431は書き込みビット線(wb1)434に結合されてもよい。各メモリセル410は、ゲート436と、ソース437と、ドレイン438とを有する第4のNFET435を含んでもよい。第4のNFETのゲート436は、書き込みワード線433に結合されてもよく、第4のNFETのドレイン438は、第1のPFETのゲート412および第1のNFETのゲート421に結合されてもよく、第4のNFETのソースは書き込みビット線補線(wb1\_1)439に結合されてもよい。

40

#### 【0040】

ヘッダ回路480は、複数のヘッダPFET481と、第1のヘッダNFET482と、第2のヘッダNFET483とを含んでもよい。複数のヘッダPFET481が示されているが、単一のヘッダPFET481が使用されてもよいことを理解されたい。さらに、複数のメモリセル410に関して単一のヘッ

50

ダ回路480が示されているが、メモリセル410ごとに別個のヘッダ回路が設けられてもよいことを理解されたい。メモリセル410ごとに別個のヘッダ回路480が設けられるとき、メモリセル410ごとのヘッダNFETデバイスの対の代わりにヘッダNFETデバイス482および483の単一の共通の対が使用されてもよい。

#### 【 0 0 4 1 】

各ヘッダPFET481は、ゲート484と、ソース485と、ドレイン486とを含んでもよい。ヘッダPFETのソース485は、メモリセルに結合されたプロセッサ用の電圧を供給するシステム供給電圧(vdd)487に結合されてもよく、ヘッダPFETのゲート484はドライバ回路495に結合されてもよく、ヘッダPFETのドレイン486は仮想供給電圧415に結合されてもよい。

#### 【 0 0 4 2 】

第1のヘッダNFET482は、ゲート488と、ソース489と、ドレイン490とを有してもよい。第1のヘッダNFETのソース489は仮想供給電圧415に結合されてもよく、第1のヘッダNFETのゲート488はドライバ回路495に結合されてもよく、第1のヘッダNFETのドレイン490はグランド424に結合されてもよい。

#### 【 0 0 4 3 】

第2のヘッダNFET483は、ゲート491と、ソース493と、ドレイン492とを有してもよい。第2のヘッダNFETのソース493はシステム供給電圧487に結合されてもよく、第2のヘッダNFETのゲート491はドライバ回路495に結合されてもよく、第2のヘッダNFETのドレイン492はグランド415に結合されてもよい。

#### 【 0 0 4 4 】

ドライバ回路495は、書き込みクロック信号(wr\_clk)496に結合されたパルス発生器494と、各ヘッダPFET481、第1のヘッダNFET482、および第2のヘッダNFET483のゲートに結合された書き込み信号出力497とを含んでもよい。

#### 【 0 0 4 5 】

次に、本開示のいくつかの例による図4に示すレジスタファイル回路400の例示的な動作について説明する。ヘッダPFET481は、仮想供給電圧415の電圧をメモリセルPFET411および416のしきい値電圧(Vt)よりも低い電圧に低下させるように構成される。このことは、ヘッダPFET481および第1のヘッダNFET482のゲートがドライバ回路495によって生成される書き込み信号出力に結合されているとき、第1のヘッダNFET482がオンである間、書き込み信号出力によりヘッダPFET481をオフにすることによって実現される。この構成は、メモリセル410への電流経路を遮断し、それによって第1のPFET411および第2のPFET416をオフにし、メモリセル410内の書き込み競合をなくす。仮想供給電圧415がグランドまたはゼロになるのを防止するために、第2のヘッダNFET483は仮想供給電圧415をvddからPFET411および416のVtを引いた値にクランプする。このことは、所望の抵抗分圧比電圧を発生させるようにNFET482および483のサイズを調整することによって実現されてもよい。

#### 【 0 0 4 6 】

ドライバ回路495の書き込み信号出力は、書き込みワード線433がアクティブである期間全体にわたって書き込み競合が完全になくなるのを防止するように設計された幅のパルス書き込み信号を生成するパルス発生器494を含んでもよい。パルスの幅は、第1のヘッダNFET482と第2のヘッダNFET483を同時にオンに維持することによって必要なエネルギーを低減させつつ書き込みプロセスを迅速に完了するように設定されかつそのようにタイミングが調整され(書き込みワード線信号に対する位置)てもよい。パルス書き込み信号の幅は、製造プロセスまたは作製プロセスの間に回路に生じるプロセス変動に対処するように最適化されてもよい。

#### 【 0 0 4 7 】

図5は、本開示のいくつかの例によるレジスタファイル回路に関する書き込みプロセスのタイミング図および完了時間グラフを示す。図5に示すように、書き込みワード線信号500は、アクティブ化され、ゼロからvddに立ち上がる。書き込みワード線信号500がアクティブ化される前に、パルス書き込み信号510がドライバ回路から出力され、パルス書き込み信号線上の電圧がゼロからvddに立ち上がる。パルス書き込み信号510がvddに達すると、仮想供給電

10

20

30

40

50

圧信号520が、vddよりも低下し、書き込みワード線信号500がvddに達する前に第1のヘッダN FETと第2のヘッダNFETの比に応じた電圧にクランプされる。パルス書き込み信号の幅は、パルス書き込み信号電圧が低下してゼロに戻る前に書き込みを完了するのに十分な時間が得られるように設定される。図5に示すように、y軸530は、0.9Vにおける正規化された遅延(書き込み支援機構を有しない従来のビットセルに対して正規化されている)を示し、x軸540は、ボルト単位のメモリセルのVminを示している。従来の6Tビットセルに関する書き込み完了時間のグラフ550では、Vminは0.55ボルトであり、一方、本開示のいくつかの例によるレジスタファイル回路に関する書き込み完了時間のグラフ560では、同じ遅延の間Vminは約0.48ボルトである。これによって、Vminが11%低下し、これは、書き込みが完了するまでの間エネルギーが21%節約されることに相当する。いくつかの例による書き込み支援によるレジスタファイル回路の所望のVminが0.55ボルトである場合、書き込み支援を使用しても、書き込み完了に関する遅延が45%短縮される。

#### 【0048】

本出願に記述されるか、例示されるか、または図示されるもののいずれも、任意の構成要素、ステップ、特徴、利益、利点、または均等物が特許請求の範囲に記載されているかどうかにかかわらず、それらの構成要素、ステップ、特徴、利益、利点、または均等物を公衆に献呈することを意図していない。

#### 【0049】

様々な異なる技術および技法のいずれかを使用して、情報および信号が表されてもよいことを当業者は理解されよう。たとえば、上記の説明全体にわたって参照される場合があるデータ、命令、コマンド、情報、信号、ビット、シンボル、およびチップは、電圧、電流、電磁波、磁場もしくは磁性粒子、光場もしくは光学粒子、またはそれらの任意の組合せによって表される場合がある。

#### 【0050】

さらに、本明細書で開示される例に関連して記載される、様々な例示の論理ブロック、モジュール、回路、およびアルゴリズムステップは、電子ハードウェア、コンピュータソフトウェアまたは両方の組合せとして実装できることが、当業者には諒解されよう。ハードウェアおよびソフトウェアのこの互換性を明確に示すために、種々の例示的な構成要素、ブロック、モジュール、回路、およびステップについて、上記では概してそれらの機能に関して説明した。そのような機能がハードウェアとして実現されるのか、それともソフトウェアとして実現されるのかは、特定の適用例および全体的なシステムに課された設計制約によって決まる。当業者は、上述の機能を特定の適用例ごとに様々な方法で実現できるが、そのような実装上の決定は、本開示の範囲からの逸脱を引き起こすものと解釈されるべきではない。

#### 【0051】

本明細書で開示した例に関連して説明した方法、シーケンス、および/またはアルゴリズムは、ハードウェア、プロセッサによって実行されるソフトウェアモジュール、またはその2つの組合せにおいて直接具現化されてもよい。ソフトウェアモジュールは、RAMメモリ、フラッシュメモリ、ROMメモリ、EPROMメモリ、EEPROMメモリ、レジスタ、ハードディスク、リムーバブルディスク、CD-ROM、または当技術分野において知られている任意の他の形態の記憶媒体内に存在してもよい。例示的な記憶媒体は、プロセッサが記憶媒体から情報を読み取ること、および記憶媒体に情報を書き込むことができるようにプロセッサに結合される。代替として、記憶媒体は、プロセッサに一体化されていてもよい。

#### 【0052】

本明細書で開示する態様に関して説明する様々な例示的な論理ブロック、モジュール、および回路は、汎用プロセッサ、デジタル信号プロセッサ(DSP)、特定用途向け集積回路(ASIC)、フィールドプログラマブルゲートアレイ(FPGA)もしくは他のプログラマブル論理デバイス、個別ゲートもしくはトランジスタ論理、個別ハードウェア構成要素、または本明細書で説明する機能を実行するように設計されたそれらの任意の組合せを用いて実装または実行されてもよい。汎用プロセッサはマイクロプロセッサであってもよいが、代替と

10

20

30

40

50

して、プロセッサは、任意の従来のプロセッサ、コントローラ、マイクロコントローラまたはステートマシンであってもよい。プロセッサは、コンピューティングデバイスの組合せ(たとえば、DSPとマイクロプロセッサの組合せ、複数のマイクロプロセッサ、DSPコアと連結した1つもしくは複数のマイクロプロセッサ、または任意の他のそのような構成)として実装されてもよい。

#### 【0053】

デバイスについていくつかの態様について説明してきたが、これらの態様が対応する方法の説明も構成し、したがって、デバイスのブロックまたは構成要素が対応する方法ステップまたは方法ステップの特徴としても理解されるべきであることは言うまでもない。それと同様に、方法ステップに関するまたは方法ステップとして説明した態様は、対応するブロックまたは対応するデバイスの詳細もしくは特徴の説明も構成する。方法ステップのいくつかまたはすべては、たとえば、マイクロプロセッサ、プログラマブルコンピュータ、または電子回路などのハードウェア装置によって(またはハードウェア装置を使用して)実行することができる。いくつかの例では、最も重要な方法ステップのうちのいくつかまたは複数は、そのような装置によって実行することができる。

10

#### 【0054】

上述の例は、本開示の原理の例示を構成しているにすぎない。本明細書で説明した構成および詳細の変更および改変が他の当業者に明らかになることは言うまでもない。したがって、本開示は、本説明に基づいて提示された具体的な詳細と、本明細書の例の説明とによってではなく、添付の特許請求の範囲の保護範囲によってのみ限定されるものとする。

20

#### 【0055】

上記の発明を実施するための形態では、各例において様々な特徴が互いにグループ化されることがわかる。この開示様式は、特許請求された例が、それぞれの請求項に明示的に述べられたものよりも多い特徴を必要とするものとして理解されるべきでない。むしろ、実際には、発明性がある内容は、開示された個々の例のすべての特徴よりも少ない場合がある。したがって、以下の特許請求の範囲は、これによって本説明に組み込まれたものと見なされるべきであり、各請求項は単独で別個の例として存在することができる。各請求項は単独で別個の例として存在することができるが、従属請求項は、特許請求の範囲内で1つまたは複数の請求項との具体的な組合せを参照することができる一方で、他の例は、前記従属請求項と任意の他の従属請求項の主題との組合せ、または任意の特徴と他の従属請求項および独立請求項との組合せを包含するか、または含むことが可能であることに留意されたい。そのような組合せは、具体的な組合せが意図されていないことが明示的に表されない限り、本明細書で提案される。さらに、請求項の特徴は、前記請求項が独立請求項に直接従属していないとも、任意の他の独立請求項に含まれることが可能であることも意図される。

30

#### 【0056】

本説明または特許請求の範囲に開示された方法は、本方法のそれぞれのステップまたは動作を実行するための手段を含むデバイスによって実行することが可能であることにさらに留意されたい。

#### 【0057】

40

さらに、いくつかの例では、個々のステップ/アクションは、複数のサブステップに再分割されるか、または複数のサブステップを含むことができる。そのようなサブステップは、個々のステップの開示に含まれ、個々のステップの開示の一部分となることが可能である。

#### 【0058】

上記の開示は本開示の例を示すが、添付の特許請求の範囲によって定義される本開示の範囲から逸脱することなく、本明細書で様々な変形および変更を施すことが可能であることに留意されたい。本明細書に記載の本開示の例による方法クレームの機能、ステップ、および/またはアクションは、任意の特定の順序で実行される必要はない。さらに、本開示の要素は、単数形において説明または特許請求がなされる場合があるが、単数形に限定

50

することが明示的に述べられていない限り、複数形が企図される。

【符号の説明】

【0059】

|                   |    |

|-------------------|----|

| 10 プロセッサ          |    |

| 12 命令実行パイプライン     |    |

| 14 制御論理           |    |

| 16 ステータスレジスタ      |    |

| 18 デバッグ回路         |    |

| 24 汎用レジスタ         |    |

| 26 命令キャッシュ        | 10 |

| 30 データキャッシュ       |    |

| 34 メモリインターフェース    |    |

| 38 メモリデバイス        |    |

| 40 メモリデバイス        |    |

| 42 バス配線           |    |

| 100 システム          |    |

| 202 ブラットフォーム      |    |

| 208 ASIC          |    |

| 300 ビットセルトランジスタ回路 |    |

| 400 レジスタファイル回路    | 20 |

| 410 メモリセル         |    |

| 411 第1のPFET       |    |

| 412 第1のPFETのゲート   |    |

| 413 第1のPFETのソース   |    |

| 414 第1のPFETのドレイン  |    |

| 415 仮想供給電圧        |    |

| 416 第2のPFET       |    |

| 417 第2のPFETのゲート   |    |

| 418 第2のPFETのソース   |    |

| 419 第2のPFETのドレイン  | 30 |

| 420 第1のNFET       |    |

| 421 第1のNFETのゲート   |    |

| 422 第1のNFETのソース   |    |

| 423 第1のNFETのドレイン  |    |

| 424 グランド          |    |

| 425 第2のNFET       |    |

| 426 第2のNFETのゲート   |    |

| 427 第2のNFETのソース   |    |

| 428 第2のNFETのドレイン  |    |

| 429 第3のNFET       | 40 |

| 430 第3のNFETのゲート   |    |

| 431 第3のNFETのソース   |    |

| 432 第3のNFETのドレイン  |    |

| 433 書込みワード線       |    |

| 435 第4のNFET       |    |

| 436 第4のNFETのゲート   |    |

| 437 第4のNFETのソース   |    |

| 438 第4のNFETのドレイン  |    |

| 480 ヘッダ回路         |    |

| 481 ヘッダPFET       | 50 |

|     |                 |    |

|-----|-----------------|----|

| 482 | ヘッダNFET         |    |

| 483 | 第2のヘッダNFET      |    |

| 484 | ヘッダPFETのゲート     |    |

| 485 | ヘッダPFETのソース     |    |

| 486 | ヘッダPFETのドレイン    |    |

| 487 | システム供給電圧        |    |

| 488 | 第1のヘッダNFETのゲート  | 10 |

| 489 | 第1のヘッダNFETのソース  |    |

| 490 | 第1のヘッダNFETのドレイン |    |

| 491 | 第2のヘッダNFETのゲート  |    |

| 492 | 第2のヘッダNFETのドレイン |    |

| 493 | 第2のヘッダNFETのソース  |    |

| 494 | パルス発生器          |    |

| 495 | ドライバ回路          |    |

| 497 | 書き込み信号出力        |    |

| 500 | 書き込みワード線信号      |    |

| 510 | パルス書き込み信号       |    |

| 520 | 仮想供給電圧信号        |    |

| 530 | y軸              |    |

| 540 | x軸              | 20 |

【図1】

【図2A】

【 図 2 B 】

【 四 3 】

FIG. 3

【 四 4 】

【 义 5 】

---

フロントページの続き

(72)発明者 ジフン・ジョン

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775・クアルコム・インコーポレイテッド

(72)発明者 キース・アラン・ボウマン

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775・クアルコム・インコーポレイテッド

(72)発明者 アメイ・スドィール・クルカルニ

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775・クアルコム・インコーポレイテッド

(72)発明者 ジェイソン・フィリップ・マルツロフ

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775・クアルコム・インコーポレイテッド

(72)発明者 ジョシュア・ランス・パケット

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775・クアルコム・インコーポレイテッド

審査官 堀田 和義

(56)参考文献 国際公開第2013/147848 (WO, A1)

特開2007-149325 (JP, A)

特開2009-134779 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 11 / 417

G 11 C 5 / 14