(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5732708号

(P5732708)

(45) 発行日 平成27年6月10日(2015.6.10)

(24) 登録日 平成27年4月24日(2015.4.24)

(51) Int.Cl.

G06F 3/06 (2006.01)

G06F 3/08 (2006.01)

F 1

G06F 3/06

G06F 3/083/06

3/08301 F

C

請求項の数 20 (全 24 頁)

(21) 出願番号 特願2012-524720 (P2012-524720)

(86) (22) 出願日 平成22年7月23日 (2010.7.23)

(65) 公表番号 特表2013-502001 (P2013-502001A)

(43) 公表日 平成25年1月17日 (2013.1.17)

(86) 國際出願番号 PCT/US2010/043095

(87) 國際公開番号 WO2011/019494

(87) 國際公開日 平成23年2月17日 (2011.2.17)

審査請求日 平成25年7月22日 (2013.7.22)

(31) 優先権主張番号 61/233,118

(32) 優先日 平成21年8月11日 (2009.8.11)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 61/256,502

(32) 優先日 平成21年10月30日 (2009.10.30)

(33) 優先権主張国 米国(US)

(73) 特許権者 502188642

マーベル ワールド トレード リミテッド

バルバドス国 ビービー14027, セントマイケル、ブリトンズ ヒル、ガンサイ

トロード、エル ホライズン

(74) 代理人 110000877

龍華国際特許業務法人

(72) 発明者 フアン、チェン クオ

アメリカ合衆国、95054 カリフォルニア州、サンタ クララ、マーベル レーン 5488 マーベル セミコンダクター インコーポレイテッド内

最終頁に続く

(54) 【発明の名称】不揮発性メモリからのデータ読み出し用コントローラ

## (57) 【特許請求の範囲】

## 【請求項 1】

データブロックを識別し、識別された前記データブロックの複数の部分を、コマンドを発行するホストへ送信する第1シーケンスを識別する前記コマンドに対応して、前記データブロックを保持し、前記データブロックの前記複数の部分が、対応する複数の不揮発性メモリユニットに格納されるバッファと、

前記コマンドに応答して、前記データブロックの前記複数の部分を、前記対応する複数の不揮発性メモリユニットから前記第1シーケンスとは異なる第2シーケンスで取得するデータ取得部と、

前記データ取得部と協働するように結合され、前記第2シーケンスに従って、前記データ取得部から、前記データブロックの前記複数の部分を受信し、前記第2シーケンスに従って、前記データ取得部から、前記データブロックの前記複数の部分を受信する際に、前記データブロックの前記複数の部分にエラーが無いかを判断するべく前記データブロックの前記複数の部分のそれぞれをチェックし、前記第2シーケンスに従って、チェックされた前記データブロックの前記複数の部分を前記バッファに送信する、エラーチェック及び補正ユニットと、

前記エラーチェック及び補正ユニットと協働するように結合され、前記第1シーケンスを受信し、前記第2シーケンス内で取得される前記データブロックの前記複数の部分を追跡し、前記エラーチェック及び補正ユニットが前記データブロックに含まれる全ての前記複数の部分を前記バッファに送信したことを示す指示を提供するシーケンサと

を備え、

前記第2シーケンスは、取得した非連続な前記データブロックの前記複数の部分に関連し、

前記エラー・チェック及び補正ユニットは、前記データブロックの一部分にエラーが無いことを示す信号を前記シーケンサに送信し、

前記シーケンサは、前記データブロックのそれぞれの部分について、前記エラーチェック及び補正ユニットが前記データブロックの前記一部分の識別子及び前記一部分にエラーが無いことを示す信号を送信するかを判断することによって、前記第2シーケンスで取得された前記データブロックを追跡し、

前記バッファは、前記第2シーケンスに従って、チェックされた前記データブロックの前記複数の部分を受信し、前記第1シーケンスに基づいて識別されたバッファ空間内にチェックされた前記データブロックの前記複数の部分のそれぞれを格納し、前記エラーチェック及び補正ユニットが前記データブロックに含まれる全ての前記複数の部分を前記バッファに送信したことを示す指示に応答して、前記第1シーケンスに従って、前記データブロックを前記ホストへ送信するデバイス。

### 【請求項 2】

前記バッファは、複数のコマンドのそれぞれに対応する複数のデータブロックを保持し、

前記データ取得部は、異なる前記複数のデータブロックの異なる複数の部分を並行して取得する請求項1に記載のデバイス。

### 【請求項3】

前記データ取得部は、第1コマンドに対応するデータブロックの複数の部分を、第2コマンドに対応するデータブロックの複数の部分と交互に配置する請求項2に記載のデバイス。

#### 【請求項4】

それぞれの不揮発性メモリユニットは複数のセクタを有し、

前記データブロックの前記複数の部分は、前記複数の不揮発性メモリユニットの前記複数のセクタにわたって格納され、

前記データ取得部は、前記複数のセクタから前記データブロックの前記複数の部分を前記第2シーケンスで取得する請求項1から3のいずれか一項に記載のデバイス。

### 【請求項 5】

対応する複数の不揮発性メモリユニットに複数の部分が格納されるデータブロックを識別し、識別された前記データブロックの前記複数の部分を、コマンドを発行するホストへ送信する第1シーケンスを識別する、前記データブロックに対する前記コマンドを受信する段階と、

処理回路によって、前記データブロックの前記複数の部分を、前記対応する複数の不揮発性メモリユニットから前記第1シーケンスとは異なる第2シーケンスで取得する段階と

前記データブロックの前記複数の部分が前記第2シーケンスで受信された際に、前記データブロックの部分にエラーが無いかを判断するために、前記データブロックの前記複数の部分のそれぞれをチェックする段階と

前記データブロックの部分にエラーが無いことを示す信号を送信する段階と、

前記第1シーケンスに基づいて識別されたバッファのバッファ空間内に、チェックされ

た前記データブロックの前記複数の部分のそれぞれを格納する段階と

格納された前記データが、前記データブロックの全ての前記複数の部分を含むか判断する段階であって、前記データブロックのそれぞれの部分について、前記データブロックの前記部分の識別子及び前記部分にエラーが無いことを示す信号が送信されたかを判断することによって、前記第2シーケンスで取得された前記データブロックを追跡する段階を有する段階と。

前記判断することに応答して、前記第1シーケンスに従って、前記データプロックを前記

記ホストに送信させるよう前記バッファに指示する段階と

を備え、

前記第2シーケンスは、取得した非連續な前記データブロックの前記複数の部分に関連する、

方法。

【請求項6】

前記第2シーケンスで取得された前記データブロックの前記複数の部分を追跡する段階をさらに備える請求項5に記載の方法。

【請求項7】

付加的なデータブロックを送信するための付加的なコマンドを受信する段階と、

10

前記コマンドに対応する前記データブロック及び前記付加的なコマンドに対応する前記付加的なデータブロックを並行して取得する段階と

をさらに備える請求項5または6に記載の方法。

【請求項8】

前記データブロックの複数の部分を、前記付加的なデータブロックの複数の部分と交互に配置する段階をさらに備え、

交互に配置された前記複数の部分は前記バッファに格納される

請求項7に記載の方法。

【請求項9】

それぞれの不揮発性メモリユニットは複数のセクタを有し、

20

前記データブロックの前記複数の部分は、前記複数の不揮発性メモリユニットの前記複数のセクタにわたって格納され、

前記データブロックの前記複数の部分を取得する段階は、前記複数のセクタから前記データブロックの前記複数の部分を前記第2シーケンスで取得する段階を有する請求項5から8のいずれか一項に記載の方法。

【請求項10】

複数のデータブロックの複数の部分を格納する複数の不揮発性メモリユニットと、

前記複数の不揮発性メモリユニットの1つ以上に格納される、前記複数のデータブロックの2つ以上のデータブロックを受信するための複数のコマンドを送信するホストと、

前記複数の不揮発性メモリユニットと前記ホストとの間でデータを送信するコントローラと、

30

前記コントローラと協働するように結合されたエラーチェック及び補正ユニットと

を備え、

前記コントローラは、

それぞれが前記2つ以上のデータブロックのデータブロック及び前記ホストへ送信する前記データブロックの複数の部分の第1シーケンスを識別する複数のコマンドを前記ホストから受信し、

前記2つ以上のデータブロックを並行して取得し、

それぞれのデータブロックの前記複数の部分は、対応するコマンドによって識別される

前記第1シーケンスとは異なる第2シーケンスで取得され、

40

前記第2シーケンスは、取得した非連續な前記対応するデータブロックの前記複数の部分に関連し、

前記エラーチェック及び補正ユニットは、

対応する前記第2シーケンスに従って、前記コントローラから、それぞれのデータブロックの前記複数の部分を受信し、

前記それぞれのデータブロックの前記複数の部分が、対応する前記第2シーケンスに従って、前記コントローラから受信された際に、前記部分にエラーが無いかを判断するため

に、前記それぞれのデータブロックの前記複数の部分のそれぞれをチェックし、

前記データブロックの前記部分にエラーが無いことを示す信号を前記コントローラに送

信し、

50

対応する前記第1シーケンスに基づいて識別されたバッファ空間内に、チェックされた前記それぞれのデータブロックの前記複数の部分を格納し、

前記コントローラは、

前記データブロックのそれぞれの部分について、前記データブロックの前記部分の識別子及び前記部分にエラーが無いことを示す信号が送信されたかを判断することによって、前記第2シーケンスで取得された前記データブロックを追跡し、

前記複数のコマンドの各々に対し、格納された対応するデータブロックの前記複数の部分が前記ブロックの全ての前記データを含むか判断し、

前記複数のコマンドの各々に対し、前記判断することに応答して、格納された前記対応するデータブロックの複数の部分を、対応する前記第1シーケンスに基づいて前記ホストへ送信する、

システム。

#### 【請求項11】

前記コントローラはさらに、第1コマンドを受信することに応答して取得される第1データブロックの複数の部分を、第2コマンドに応答して取得される第2データブロックの複数の部分と交互に配置し、

交互に配置された前記複数の部分は不揮発性メモリユニットに格納される

請求項10に記載のシステム。

#### 【請求項12】

それぞれの不揮発性メモリユニットは複数のセクタを有し、

前記データブロックの前記複数の部分は、前記複数の不揮発性メモリユニットの前記複数のセクタにわたって格納され、

前記コントローラは、前記複数のセクタから前記データブロックの前記複数の部分を前記第2シーケンスで取得する請求項10または11に記載のシステム。

#### 【請求項13】

前記第2シーケンスにおいて、前記データ取得部は、セクタごとに、セクタに関連する何れのチャネルもスキップすることなく、前記複数の不揮発性メモリユニットのそれぞれから前記データブロックの複数の部分を取得する請求項4に記載のデバイス。

#### 【請求項14】

前記複数のセクタは、第1セクタ及び第2セクタを含み、

前記第2シーケンスにおいて、前記データ取得部は、前記データブロックの前記複数の部分の第1部分または前記データブロックの前記複数の部分の第2部分の取得において、何れのチャネルもスキップすることなく、前記第2セクタから前記第2部分を取得する前に、前記第1セクタから前記第1部分を取得する請求項4に記載のデバイス。

#### 【請求項15】

前記第2シーケンスで前記データブロックの前記複数の部分を取得する段階は、セクタごとに、セクタに関連する何れのチャネルもスキップすることなく、前記複数の不揮発性メモリユニットのそれぞれから、前記データブロックの前記複数の部分を取得する段階を有する、請求項9に記載の方法。

#### 【請求項16】

前記複数のセクタは、第1セクタ及び第2セクタを含み、

前記データブロックの前記複数の部分を取得する段階は、前記第2シーケンスにおいて、前記データブロックの前記複数の部分の第1部分または前記データブロックの前記複数の部分の第2部分の取得において、何れのチャネルもスキップすることなく、前記第2セクタから前記第2部分を取得する前に、前記第1セクタから前記第1部分を取得する段階を含む、請求項9に記載の方法。

#### 【請求項17】

前記第2シーケンスにおいて、前記コントローラは、セクタごとに、セクタに関連する何れのチャネルもスキップすることなく、前記複数の不揮発性メモリユニットのそれぞれから前記データブロックの前記複数の部分を取得する、請求項12に記載のシステム。

10

20

30

40

50

## 【請求項 18】

前記複数のセクタは、第1セクタ及び第2セクタを含み、

前記第2シーケンスにおいて、前記コントローラは、前記データブロックの前記複数の部分の第1部分または前記データブロックの前記複数の部分の第2部分の取得において、何れのチャネルもスキップすることなく、前記第2セクタから前記第2部分を取得する前に、前記第1セクタから前記第1部分を取得する、請求項12に記載のシステム。

## 【請求項 19】

前記コントローラは、

格納された第1データブロックの複数の部分が、前記第1データブロック内の全てのデータよりも少ないデータを含み、かつ、格納された第2データブロックの複数の部分が、前記第2データブロック内の全てのデータを含むかを判断し、

前記格納された前記第1データブロックの複数の部分が、前記第1データブロックの全てのデータを含むまで、格納された前記第2データブロックの前記複数の部分の前記ホストへの送信を遅らせる、請求項10に記載のシステム。

## 【請求項 20】

前記複数のコマンドは、前記2つ以上のデータブロックのうちの第1データブロックを識別する第1コマンドと、前記2つ以上のデータブロックの第2データブロックを識別する第2コマンドとを含み、

前記コントローラは、

前記第2コマンドを受信する前に、前記第1コマンドを受信し、

格納された前記第1データブロックの前記複数の部分が、前記第1データブロックの全てのデータよりも少ないデータを含み、かつ、格納された前記第2データブロックの前記複数の部分が、前記第2データブロックの全てのデータを含むかを判断し、

格納された前記第1データブロックの前記複数の部分を前記ホストに送信する前に、格納された前記第2データブロックの前記複数の部分を前記ホストに送信する、請求項10に記載のシステム。

## 【発明の詳細な説明】

## 【背景技術】

## 【0001】

【関連出願】 本出願は、米国特許法第119(e)条の下で、2009年8月11日に出願された「An Efficient Random Read Strategy and Implementation for Solid-State Devices」と題する米国特許出願第61/233,118号、及び、2009年10月30日に出願された「A Method for Maximizing the Read Performance of A Set of Large Unbalanced Commands」と題する米国特許出願第61/256,502号からの優先権を主張する。上述の出願の開示内容全体を参照により本明細書に組み込む。

## 【0002】

本開示は固体ドライブ(SSD)に関するシステム及び技術を記載する。

## 【0003】

SSDは、データを格納するための固体メモリを用いたデータストレージデバイスである。不揮発性メモリ、例えばNANDをベースとするフラッシュメモリが、SSDと共にストレージデバイスとして使用されることが多い。不揮発性メモリデバイスと協働するよう結合されたSSDは、不揮発性メモリデバイスにデータを書き込み、不揮発性メモリデバイスからデータを取得するように構成されるコントローラを含む。SSDを介したデータスループットを増大させるために、複数の不揮発性メモリデバイスがSSDコントローラに結合されることが多い。データブロックは、不揮発性メモリユニットのセクタに格納される。SSDコントローラは、SSDコントローラ中のチャネルを介し、各チャネルと協働するよう結合された不揮発性メモリユニットのセクタをスキャンすることによって、データブロックの複数の部分を取得することができる。いくつかの状況においては、データブロックの全ての又は複数の部分が、1つのチャネルと協働するよう結合された不揮発性メモリユニットのセクタ中に集められる。

10

20

30

40

50

**【発明の概要】****【0004】**

本明細書は、不揮発性メモリからデータを読み出すためのコントローラに関する技術を記載する。記載されるシステム及び技術の革新的な面は、コマンドに対応するデータブロックを保持するように構成されたバッファを含むデバイスとして実施することができる。コマンドは、データブロックを識別し、識別されたデータブロックが送信されるべき第1シーケンスを識別する。データブロックの複数の部分は、それぞれの不揮発性メモリユニットに格納される。デバイスは、コマンドに応じてそれぞれの不揮発性メモリユニットからデータブロックの複数の部分を取得するように構成されたデータ取得部を含む。データ取得部は、第1シーケンスとは異なる第2シーケンスで複数の部分を取得し、取得したデータブロックの複数の部分をバッファに送信するように構成される。第2シーケンスで取得されたデータブロックが追跡される。データブロックに含まれる全ての部分をデータ取得部が取得したという指示に応じて、バッファがデータブロックを送信する。10

**【0005】**

こうした側面、及びその他の側面は、以下の特徴の1つ以上を含むことができる。データ取得部は、第1コマンドに対応するデータブロックの複数の部分を、第2コマンドに対応するデータブロックの複数の部分と交互に配置できるように構成される。不揮発性メモリユニットのそれぞれは、複数のセクタを有することができる。データブロックの複数の部分が、不揮発性メモリユニットの複数のセクタにわたって格納される。データ取得部は、複数のセクタからデータブロックの複数の部分を第2シーケンスで取得するように構成される。デバイスは、第1シーケンスを受信し、第2シーケンスで取得されたデータブロックを追跡し、データブロックに含まれる全ての部分をデータ取得部が取得したことを示す指示を提供するように構成されたシーケンサをさらに備えることができる。デバイスは、データ取得部と協働するように結合され、データ取得部によって取得されたデータブロックの1つ以上の部分をチェックするように構成されたエラーチェック及び補正ユニットをさらに備えることができる。データ取得部は、データブロックの複数の部分を第2シーケンスでエラーチェック及び補正ユニットへ送信する。エラーチェック及び補正ユニットは、シーケンサと協働するように結合され、データブロックの一部分にエラーが無いことを示す信号をシーケンサに送信するよう構成される。シーケンサは、データブロックの各部分に対し、エラーチェック及び補正ユニットがデータブロックの当該一部分の識別子及び当該一部分にエラーが無いことを示す信号を送信するか判断することによって、第2シーケンスで取得されたデータブロックを追跡することができる。20

**【0006】**

記載されるシステム及び技術の別の革新的な側面は、データブロックに対するコマンドの受信を含む方法として実行される。コマンドは、データブロックを識別し、識別されたデータブロックが送信されるべき第1シーケンスを識別する。データブロックの複数の部分は、それぞれの不揮発性メモリユニットに格納される。この方法は、処理回路によって、それぞれの不揮発性メモリユニットからデータブロックの複数の部分を第1シーケンスとは異なる第2シーケンスで取得することを含む。取得されたデータブロックはバッファに格納される。この方法は、取得されたデータが第2シーケンスに従ったデータブロックの全ての部分を含むか判断し、判断したことに応じてデータブロックを送信させるようバッファに指示することを含む。30

**【0007】**

こうした側面、及びその他の側面は、以下の特徴の1つ以上を含むことができる。第2シーケンスで取得されたデータブロックの複数の部分が追跡される。付加的なデータブロックを送信するための付加的なコマンドが受信される。コマンドに対応するデータブロック、及び付加的なコマンドに対応する付加的なデータブロックが、並行して取得される。データブロックの複数の部分が、付加的なデータブロックの複数の部分と交互に配置される。交互配置された複数の部分がバッファに格納される。取得されたデータブロックの複数の部分は、バッファに送信される。それぞれの不揮発性メモリユニットは、複数のセクタにわたって格納される。40

タを有することができる。データブロックの複数の部分は、不揮発性メモリユニットの複数のセクタにわたって格納される。データブロックの複数の部分を取得することは、複数のセクタからデータブロックの複数の部分を第2シーケンスで取得することを含んでよい。取得されたデータブロックにエラーが無いか判断するために、データブロックの1つ以上の部分がチェックされる。データブロックの一部分にエラーが無いことを示す信号が送信される。追跡することは、データブロックの各部分に対し、ブロックの当該一部分の識別子及び当該一部分にエラーが無いことを示す信号が送信されると判断することによって、第2シーケンスで取得されたデータブロックを追跡することを含んでよい。

## 【0008】

10

記載されるシステム及び技術は、電子回路、コンピュータハードウェア、ファームウェア、ソフトウェア、又はそれらの組み合わせにおいて、本明細書に開示される構造的な手段、及び構造的なその等価物として実施することができる。これは、少なくとも1つのコンピュータ読み取り可能な媒体を含んでよく、1つ以上のデータ処理装置（例えば、プログラマブルプロセッサを含む信号処理デバイス）に対し、記載されるオペレーションを実行させるように動作するプログラムを実現させる。従って、プログラムの実施は、開示される方法、システム、又は装置から実現され、装置の実施は、開示されるシステム、コンピュータ読み取り可能な媒体、又は方法から実現される。同様に、方法の実施は、開示されるシステム、コンピュータ読み取り可能な媒体、又は装置から実現され、システムの実施は、開示される方法、コンピュータ読み取り可能な媒体、又は装置から実現される。

## 【0009】

20

例えば、以下に開示される実施例は、これらに限定されるものではないが、特定用途向データ処理装置（例えばワイヤレスアクセスポイント、リモート環境モニタ、ルータ、スイッチ、コンピュータシステム部品、媒体アクセスユニット）、移動型データ処理装置（例えばワイヤレスクライアント、携帯電話、携帯情報端末（PDA）、モバイルコンピュータ、デジタルカメラ）、一般用途向データ処理装置（例えば、ミニコンピュータ、サーバ、メインフレーム、スーパーコンピュータ）、またはこれらの組み合わせを含む、様々なシステム及び装置として実施されてよい。

## 【0010】

30

従って、記載されるシステム及び技術の他の側面によれば、システムは、データブロックの複数の部分を格納するように構成された複数の不揮発性メモリユニット、1つ以上の不揮発性メモリユニットに格納される1つ以上のデータブロックを受信するためのコマンドを送信するように構成されたホスト、複数の不揮発性メモリユニットとホストとの間でデータを送信するように構成されたコントローラを備える。コントローラは、ホストから複数のコマンドを受信し、複数の不揮発性メモリユニットに格納される複数のデータブロックを並行して取得し、それぞれのコマンドに対して、取得されたデータブロックの複数の部分がブロック内の全てのデータを含むか判断し、判断することに応じて取得されたデータブロックを送信するように構成される。それぞれのコマンドは、データブロック、及びデータブロックがホストへ送信されるべき第1シーケンスを識別する。1つ以上のデータブロックの複数の部分は、対応するコマンドによって識別される第1シーケンスとは異なる第2シーケンスで取得される。

## 【0011】

40

以下の利点の1つ以上を実現するために、本明細書に記載される主題の特定の実施例が実行されてよい。ここに記載する技術は、コントローラがデータブロックを取得するチャネルにおける処理能力の浪費を低減することができる。さらにこの技術は、不揮発性メモリユニットからデータブロックが取得される効率を増大することができる。加えて、複数のデータブロックを要求するコマンドが並行して提供される。特に、例えば、大きなデータブロックが全チャネルよりも少ないチャネルに均等に分配されている場合、又は1つのチャネルに集中している場合、当該大きなデータブロックに対するコマンドに加えて、複数のコマンドを並行して実行することができる。このようにすることにより、複数のバス

50

における単一の大きなコマンドを提供すると同時に、付加的なコマンドも提供することができる。これにより、与えられた大きなコマンドグループに対する処理時間を最小限にすることができる。さらに、SSDコントローラのスループットを増大することができる。

【0012】

1つ以上の実施例の詳細を、添付する図面及び以下の記載において説明する。その他の特徴、目的、及び利点は、この記載、図面、及び特許請求の範囲から明らかになるであろう。

【図面の簡単な説明】

【0013】

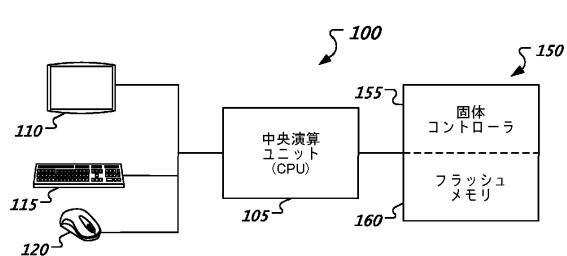

【図1】固体メモリサブシステムを含むコンピュータシステムの例を示す。

10

【0014】

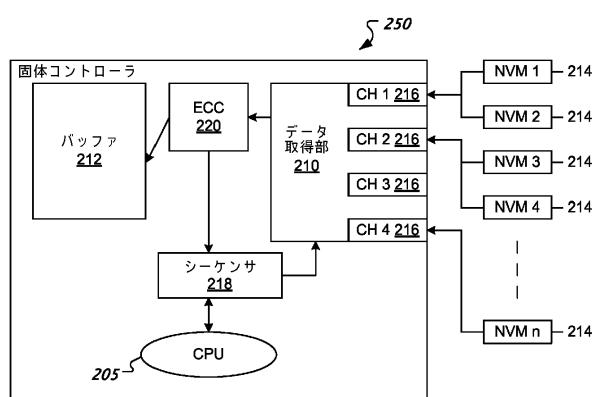

【図2】固体コントローラの例を示す。

【0015】

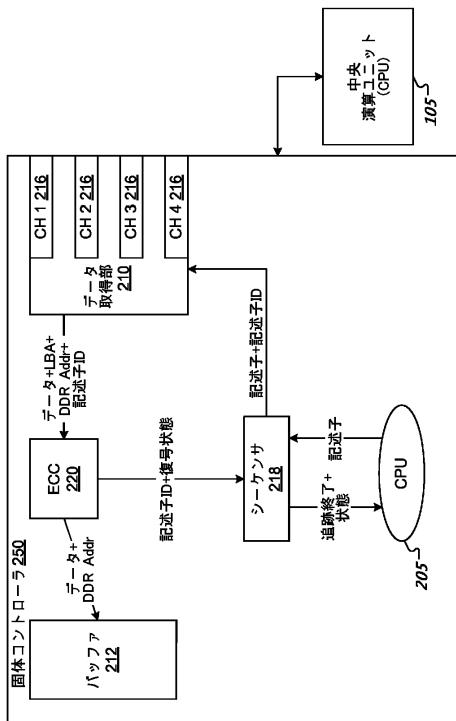

【図3】2つのデータブロックを取得する間のデータフローの例を示す。

【0016】

【図4】固体コントローラによって実行されるデータ送信方法の例を示す。

【0017】

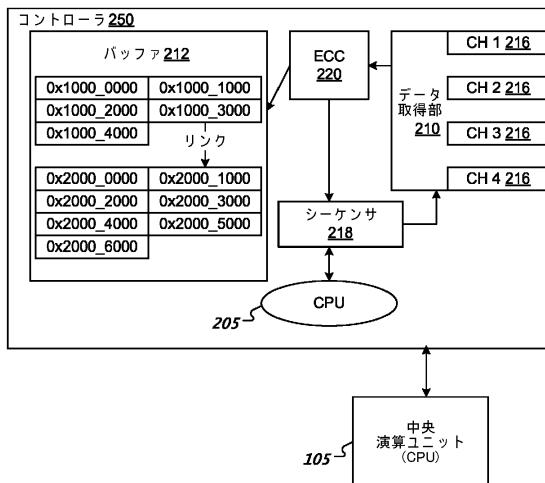

【図5】データブロックを識別するコマンドに割り当てられた領域を含む固体コントローラ中のバッファの例を示す。

【0018】

20

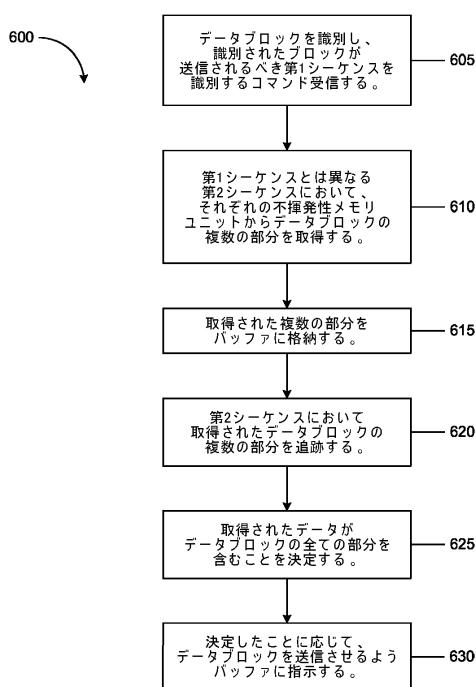

【図6】ホストからのコマンドに応答して不揮発性メモリユニットからデータを取得するプロセスの例を示す。

【0019】

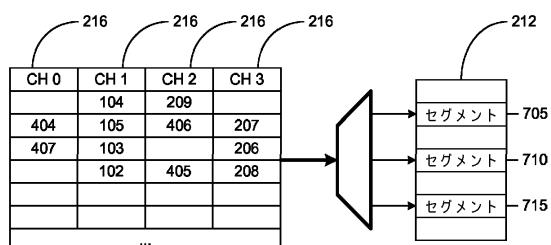

【図7】チャネルからバッファへのデータフローの例を示す。

【発明を実施するための形態】

【0020】

図1は、固体メモリサブシステム150を備えるコンピュータシステム100の例を示す。システム100は、中央演算ユニット(CPU)105、ディスプレイ装置110(例えばCRT(陰極線管)又はLCD(液晶ディスプレイ)モニタ)、及び、キーボード115並びにポインティングデバイス120(図1ではマウスとして示されているが、他のポインティングデバイスであってもよい)等の入力デバイスを備える。システム100は、1つ以上の追加プロセッサ、及び1つ以上の追加入出力デバイス、例えばマイクロフォン、スピーカ、プリンタ等を有してもよい。

30

【0021】

固体メモリサブシステム150は、固体コントローラ155、及び、例えばNANDフラッシュメモリのようなフラッシュメモリ160を有する。フラッシュメモリ160は、1つ以上の単層セル(SLC)デバイス、及び/又は多層セル(MLC)デバイスを有してよい。固体メモリサブシステム150は、オペレーティングシステム及びアプリケーションソフトウェアを固体メモリサブシステム150がシステム100にロードさせるように設計された制御ロジックを有することができる。

40

【0022】

固体メモリサブシステム150は、マルチチャネルコンフィグレーションにおいて固体コントローラ155によって動作するように構成される。そのようなコンフィグレーションにおいて、コントローラ155は、例えばCPU105であるホストからコマンドを受信することに応じて、高いデータスループットを提供する並列なマルチチャネルを介して、CPU105とフラッシュメモリ160との間でデータを送信する。例えば、フラッシュメモリ160は、それぞれが約1.6Gbpsのレートでデータ転送することができる(図2及び3を参照して記載される)複数のNANDフラッシュメモリユニットに協働するように結合された、4つのチャネルを有することができる。このような構成において固体コントローラ155が達成することのできるスループットは、フラッシュメモリ160

50

が4つのNANDフラッシュメモリユニットから連続してデータを送信する場合にコントローラ155が達成することのできるスループットに比べて4倍大きい。ここに記載される技術を使用すると、コントローラ155が結合された複数のNANDフラッシュメモリユニットから、固体コントローラ155がデータを取得する効率を増大させることができる。

#### 【0023】

認識されるように、システム100はデスクトップパーソナルコンピュータを表しており、ハードディスクドライブ、ネットワークインターフェイス、マザーボード等のような図示されていない、その他多くのデバイス及びサブシステムを備えることができる。しかしながらこれは、ここに開示された主題を実行することのできる、より大きなシステムの単なる1つの例にすぎない。そのような、より大きなデバイス及びシステムの他の例としては、単なる他のドライブのようだが、ラップトップ、ノートブック、ディスクレスサブノートブック、及び、PCI Express Card、ラップトップのPCIe Mini-Slot、又はデスクトップのPCIeスロットに適合するウルトラスリムドライブ等が含まれる。またその他の例として、不揮発性メモリデバイスを使用するスマートフォン、ネットブック、メディアプレイヤー等が含まれる。

#### 【0024】

しかしながら、これら特定の例とはかわりなく、ここに記載される主題は、多くの異なるタイプのコンピュータシステムと両立することが可能である。さらに、フラッシュメモリ160は、いかなる外部電源も必要とせずに自身のデータを保持することのできる、多くの異なるタイプの固体ストレージデバイスを含むことができる。そのようなデバイスとしては、BIOSチップ、コンパクトフラッシュ（登録商標）、スマートメディア、メモリスティック、PCMCIAタイプIおよびタイプIIメモリカード、及びビデオゲーム制御装置用メモリカード等のフラッシュメモリデバイスが含まれる。そのようなデバイスとして、相変化メモリデバイスが含まれてもよい。

#### 【0025】

図2は固体コントローラ250の例を示す。コントローラ250は、例えばコンピュータシステムのCPU105であり、ホストと協働するように結合されるべく構成される。コントローラは、データブロックに対するコマンドをホストから受信し、当該コマンドによって識別されるデータブロックをホストに送信する。例えば、CPU105は、データブロックを識別するコマンドをコントローラ250に送信し、これに応じてコントローラ250は、ここに記載される技術を用いて、複数の不揮発性メモリユニットからデータブロックを取得する。

#### 【0026】

コントローラ250は、例えばNFLASHであり、データブロックを取得するように構成されたデータ取得部210を有する。データは、複数の不揮発性メモリユニット（NVM）214、例えば、NVM1、NVM2、NVM3、NVM4、...NVMnに格納される。例えば、各データブロックは複数の部分に分割され、対応するNVMのセクタに各部分が格納される。単一のデータブロックの全ての部分が同一のNVMに格納される必要は無い。むしろ、複数のNVMにわたって複数の部分が分布されてよい。

#### 【0027】

データ取得部210は、複数のNVM214と協働するように結合された複数のチャネル216を含む。例えば図2に示されるように、データ取得部210は4つのチャネル216を有する。データ取得部210は、例えば5つ又は6つといった、より多くのチャネル、あるいは、例えば2つ又は3つといった、より少ないチャネルを有してよい。チャネル216は、1つ以上のNVM214と協働するように結合される。例えば、チャネル1（216）はNVM1及び2（214）と結合され、チャネル2（216）はNVM3及び4（214）と結合される。チャネル3（216）は、1つ以上のNVM214（不図示）と結合され、チャネル4（216）はNVMn（214）と結合される。それぞれのNVM214は、データブロックの一部分を物理的に格納することのできる複数のセクタ

10

20

30

40

50

を有することができる。データ取得部 210 は、データブロックの一部分が格納されている NVM 214 のセクタから、当該一部分を取得するように構成される。

#### 【0028】

コントローラ 250 は、取得されたデータブロックの複数の部分を格納するように構成されたバッファ 212 をさらに備える。例えば、データ取得部 210 は、チャネル 216 を介して複数の NVM からデータブロックの複数の部分を取得し、取得された複数の部分をバッファ 212 に送信する。バッファ 212 は、複数の部分の一時的な格納ユニットとして機能する。

#### 【0029】

コントローラ 250 は、複数の NVM 214 から取得されたデータブロックの複数の部分を追跡するように構成されたシーケンサ 218 をさらに備える。特に、シーケンサ 218 は、データ取得部 210 によって取得されてバッファ 212 へ送信された複数の部分を追跡するように構成される。シーケンサ 218 は、複数の NVM 214 からデータブロックの全ての部分が取得されるまでこれを行う。続いて、シーケンサ 218 は、ブロックの全ての部分が取得されたことを示す指示、例えば信号を、バッファ 212 へと送信する。シーケンサ 218 から指示を受信したことに応じて、バッファ 212 は、取得されたデータブロックの複数の部分をホストへと送信する。

10

#### 【0030】

いくつかの実施例においては、コントローラ 250 は、データ取得部 210 と協働するように結合されるエラーチェック及び補正ユニット 220 を含む。エラーチェック及び補正ユニット 220 は、データ取得部 210 によって取得されたデータブロックの各部分をチェックし、取得された部分にエラーが無いかを判断する。エラーチェック及び補正ユニット 220 はシーケンサ 218 にも結合され、取得された部分にエラーが無いことを示す信号を送信する。

20

#### 【0031】

データブロックの各部分は、ホストによる利用順序に従ってどのようにデータが格納されるかを定義する、論理ブロックアドレス (LBA) が割り当てられる。いくつかの実施例においては、連続した複数の部分が、連続した複数の NVM に格納されてよい。あるいは、連続した複数の部分が同じ複数の NVM に格納されてよい。またあるいは、複数の部分が複数の NVM にわたって分布されてもよい。さらに、各 NVM は複数のセクタを含み、各セクタは、データブロックの一部分を物理的に格納するように構成される。従って、データブロックの複数の部分は、複数の NVM に含まれる複数のセクタにわたって分布されてよい。

30

#### 【0032】

複数の NVM にわたって格納される 2 つのデータブロックを並行して取得する方法を、以下の表 2 を参照して記載する。2 つのデータブロックを並行して取得することは、複数のデータブロックの複数の部分が、複数の NVM の複数のセクタにわたって各バスにおいて取得されることを意味する。言い換えると、データ取得部 210 は、第 1 ブロックの全ての部分を取得することを待たずに、第 2 ブロックの複数の部分を取得する。それどころか、データ取得部 210 は、複数の NVM の複数のセクタから、両方のデータブロックの複数の部分を取得する。以下の表 2 においては、データブロックの複数の部分が、「ブロック番号\_部分番号」という慣例に従って表記されている。ブロック番号はコマンドに対応し、部分番号はデータブロックの一部分に対する識別子に対応する。いくつかの実施例においては、部分番号は、以下に記載する記述子によって表される。

40

## 【表2】

| 表2 - 2つのデータブロックを取得する |             |             |             |

|----------------------|-------------|-------------|-------------|

| チャネル0 (216)          | チャネル1 (216) | チャネル2 (216) | チャネル3 (216) |

| 1_0                  | 2_1         | 1_2         | 1_3         |

| 1_1                  | 2_5         | 2_2         | 2_3         |

| 1_4                  |             | 2_6         |             |

| 2_0                  |             |             |             |

| 2_4                  |             |             |             |

## 【0033】

表2を参照して記載される例においては、ブロック1は5つの部分（1\_0から1\_4）で構成され、ブロック2は7つの部分（2\_0から2\_6）で構成される。ブロック1及びブロック2を取得する1つの方法は、まずブロック1の全てのブロック部分を取得し、次いで、ブロック2の全てのブロック部分を取得する方法である。つまり、ブロック部分取得シーケンスは、チャネル0からの1\_0、（チャネル1、2、3をスキップ）、1\_1、（チャネル1をスキップ）、1\_2、1\_3、1\_4、（チャネル1、2、3をスキップ）、2\_0、2\_1、2\_2、2\_3、2\_4、2\_5、及び2\_6となる。ブロック2の任意のブロック部分を取得する前にブロック1の全てのブロック部分を取得する場合は、チャネルをスキップすることが含まれるので、チャネルの全処理能力が使用されず、取得の間に遅延が生じる。

## 【0034】

あるいは、処理能力を最大限に活用して遅延を減少させるために、データ取得部210は、チャネル0経由で第1セクタからブロック部分1\_0を取得し、次いでチャネル1経由で第1セクタからブロック部分2\_1を取得し、次いでチャネル2経由で第1セクタからブロック部分1\_2を取得し、次いでチャネル3経由で第1セクタからブロック部分1\_3を取得する。データ取得部210は、全4チャネル経由で全てのデータブロックが取得されるまで、第2セクタ、第3セクタ等に対してこれらのステップを繰り返す。言い換えると、データ取得部210は、チャネルをスキップする代わりに、1つのチャネルの1つのセクタに見出される任意のブロック部分を取得する。部分が格納されていないセクタからは部分は取得されない。

## 【0035】

取得のためのこのパターンは、各データブロックの複数の部分を識別する記述子（表3を参照して以下に記載される）に基づいて決定される。コントローラ250は、ホストから受信される記述子に基づいて、取得されるべきデータブロックの複数の部分を識別する。例えば、コマンド中において、ブロック部分1\_0及び2\_1を識別する記述子をホストが供給したので、データ取得部210は、ホストがこれらのブロック部分を要求したと判断し、これらを取得する。データ取得部210は、ブロック部分1\_0に続く部分、つまりブロック部分1\_1を取得するために、ブロック部分2\_1又はその他のブロック部分をスキップする必要が無い。その代わりに、データ取得部210がそうしたブロック部分を識別するに連れて、ホストによって特定される全てのブロック部分を、データ取得部210が取得することができる。

## 【0036】

図3は、2つのデータブロック取得の間のデータフローの例を示す。図3の例においては、2つのデータブロック取得の間のデータフローは、次のシーケンスとなっている。つまり、1\_0、1\_2、1\_3、2\_1、1\_1、2\_5、2\_2、2\_3、1\_4、2\_6、2\_0、及び2\_4である。図3に示されるデータフローは、チャネル0-3(216)経由で複数のNVM214からデータの複数の部分を取得することができる、多くの可能なシーケンスの1つである。例えば、別のデータフローは、2\_0、2\_1、2\_2、2\_3、2\_4、2\_5、2\_6、1\_3、1\_0、1\_2、1\_1、及び1\_4というシーケンスである。特に、データ取得部210が、データブロックの他の複数の部分を除外してデータブロックの連続した複数の部分を取得する必要が無いので、データフローは、データの同一のブロック部分の非連続的な複数の部分、例えば1\_0に続く1\_2を含む。さらに、第2データブロックの複数の部分を取得する前に第1データブロックの全ての部分をデータ取得部210が取得する必要が無いので、データフローは、例えば、1\_3、次いで2\_1、次いで1\_1のように、ブロック2の複数の部分と交互に配置されたブロック1の複数の部分を含む。

10

#### 【0037】

データ取得部210は、複数のデータブロックの複数の部分を、複数のNVM214の複数のセクタに複数の部分が格納されるシーケンスで取得することができる。この点においては、1つのデータブロックの複数の部分が取得されるシーケンスは、1つのデータブロックの連続した複数の部分のシーケンスとは異なる。さらに、データ取得部210は、ブロック1の複数の部分とブロック2の複数の部分とを交互に配置することができるので、これにより、チャネル216を介して両方のデータブロックを並行して取得することができる。図3に関連して示されるデータフローと、1つのブロックの連続した複数の部分が取得されるデータフローとの比較を以下の表に示す。

20

【表 A】

| データフロー(図3) | データフロー(連続した複数の部分の取得) |

|------------|----------------------|

| 1_0        | 1_0                  |

| 1_2        |                      |

| 1_3        |                      |

| 2_1        |                      |

| 1_1        |                      |

| 2_5        |                      |

| 2_2        |                      |

| 2_3        |                      |

| 1_4        |                      |

| 2_6        |                      |

| 2_0        | 2_0                  |

| 2_4        |                      |

## 【0038】

前述のように、データ取得部210は、例えばCPU105であるホストからコマンドを受信したことに応じて、複数のNVM214からデータブロックを取得する。データブロックを要求することに加え、CPU105は、データブロックがCPU105へ送信されるべきシーケンスを特定する。例えば、CPU105は、連続した複数の部分のシーケンス、つまり1\_0、1\_1、1\_2、1\_3、及び1\_4において、(表2を参照して記載される)ブロック1が送信されるべきであることを特定する。複数のNVMの複数のセクタに複数の部分が格納されているシーケンスで複数のデータブロックを取得することにより、CPU105へ複数の部分が送信されるべきシーケンスとは異なるシーケンスで、データ取得部210がデータブロックの複数の部分を取得することができる。コントローラ250は、図4に関連して記載される様式で、データ取得部210によって取得された複数の部分を送信する。

## 【0039】

図4は、固体コントローラ250によって実行されるデータ送信方法の例を示す。シーケンサ218は、例えばCPU105であるホストから、データブロックに対するコマンドを受信する。いくつかの実施例においては、コマンドは、データブロック、特にデータブロックの複数の部分を識別する複数の記述子を含む。CPU205は、データブロックの複数の部分を識別する記述子を、コントローラ250によってCPU205へ複数の部分が送信されるべき順序を表す論理順序で、シーケンサ218へと送信する。図4に示されるコントローラ250は、CPU205と協働するように結合される。CPU205は、それぞれがデータブロックを受信するためのコマンドを送信可能な複数のホストと協働するように結合されることが理解されるであろう。記述子は以下のように表される。

10

20

30

40

50

【表 B】

|                     |              |                                             |

|---------------------|--------------|---------------------------------------------|

| 論理ブロック<br>アドレス(LBA) | バッファ<br>アドレス | 物理ブロック<br>アドレス(PBA)-<br>(CH,CE,MP,NVMアドレス等) |

|---------------------|--------------|---------------------------------------------|

10

【0040】

データブロックの対応する複数の部分（アロケーションユニット（AU）としても知られている）がデータ取得部210によって取得され、バッファ212に送信されるまで、シーケンサ218が記述子を格納する。いくつかの実施例においては、データ取得部210は、取得されたデータブロックの一部分を、エラーチェック及び補正ユニット220へと送信する。そのような実施例においては、複数の部分がエラーチェック及び補正ユニット220によって処理されてバッファ212に送られるまで、シーケンサ218が記述子を格納することができる。

【0041】

シーケンサ218は、それぞれの記述子に記述子IDを付与し、以下に表される新たな記述子を生成する。対応する複数の部分が複数のNVM214から取得されてバッファ212又はエラーチェック及び補正ユニット220に送信されるまで、データ取得部210が当該新たな記述子を格納する。

20

【表 C】

|     |              |                         |    |

|-----|--------------|-------------------------|----|

| LBA | バッファ<br>アドレス | PBA-(CH,CE,MP,NVMアドレス等) | ID |

|-----|--------------|-------------------------|----|

30

【0042】

データ取得部210は、前述のシーケンス（取得シーケンス）において複数のNVMから取得された複数の部分を、バッファ212又はエラーチェック及び補正ユニット220へと送信する。取得シーケンスは、論理シーケンスとは異なっていてよい。データ取得部210は、取得されたそれぞれの部分と共に、対応する記述子をエラーチェック及び補正ユニット220へと送信する。例えば、データ取得部210からエラーチェック及び補正ユニット220へと送信された記述子の内容は、以下のように表される。

【表 D】

40

|     |          |    |

|-----|----------|----|

| LBA | バッファアドレス | ID |

|-----|----------|----|

【0043】

データ取得部210からユニット220が複数の部分を受信するにつれて、エラーチェック及び補正ユニット220が複数の部分を1つずつ処理することができる。エラーチェック及び補正ユニット220は、記述子の「バッファアドレス」フィールドを使用して、バッファ212の正しい位置にそれぞれの部分を送ることができる。エラーチェック及び補正ユニット220は、記述子の「ID」フィールドをさらに使用して、対応する部分に

50

に対するエラーチェックが完了したことを示す信号をシーケンサ218に送信することができる。

【0044】

シーケンサ218は、エラーチェック及び補正ユニット220によって送信された「ID」フィールド中の識別子を受け取ることができる。いくつかの実施例においては、シーケンサ218は、記述子識別子の長いリストを格納できるように構成される。このようにして、シーケンサは、データ取得部210が取得シーケンスで取得したデータブロックの複数の部分を追跡する。CPU205から受信した論理シーケンス中に特定されたデータブロックの全ての部分をエラーチェック及び補正ユニット220がバッファ212へ送信したとシーケンサ218が判断した場合、シーケンサ218は、データブロックをCPU205へ送信するための指示をバッファ212へと送信する。このようにして、コントローラ250はデータ送信方法を実行する。特に、コントローラ250は、データブロックの複数の部分の論理シーケンスを特定するコマンドをホストから受信し、論理シーケンスとは異なっていてよい取得シーケンスでデータブロックを取得し、論理シーケンスでデータブロックをホストへ送信できるように構成される。10

【0045】

例えばCPU205であるホストによって生成され、論理順序でシーケンサ218へと送信される記述子の例が(以下の)表3に示される。

【表3】

| 表3 - 2つのデータブロックに対して生成された記述子 |       |          |             |                 |

|-----------------------------|-------|----------|-------------|-----------------|

| ホストコマンド番号                   | 記述子番号 | 記述子フィールド |             |                 |

|                             |       | LBA      | バッファアドレス    | CH#<br>(PBAの一部) |

| 1                           | 0     | 110      | 0x1000_0000 | 0               |

|                             | 1     | 111      | 0x1000_1000 | 0               |

|                             | 2     | 112      | 0x1000_2000 | 2               |

|                             | 3     | 113      | 0x1000_3000 | 3               |

|                             | 4     | 114      | 0x1000_4000 | 0               |

| 2                           | 0     | 210      | 0x2000_0000 | 0               |

|                             | 1     | 211      | 0x2000_1000 | 1               |

|                             | 2     | 212      | 0x2000_2000 | 2               |

|                             | 3     | 213      | 0x2000_3000 | 3               |

|                             | 4     | 214      | 0x2000_4000 | 0               |

|                             | 5     | 215      | 0x2000_5000 | 1               |

|                             | 6     | 216      | 0x2000_6000 | 2               |

## 【0046】

表2は、ブロック1又はブロック2のどちらかのデータブロックにおけるそれぞれの部分が占めるチャネル216を示す。上述のように、ブロック1及びブロック2がホストへ送信されるべき論理順序とは異なっていてよい取得順序で、ブロック1及びブロック2の複数の部分が並行に取得される。さらに、取得された複数の部分は、論理シーケンスとは異なるシーケンスでバッファ212へと送信される。例えば、取得された複数の部分は、複数の部分が取得されたシーケンスでバッファ212へと送信されてよい。

## 【0047】

いくつかの状況においてコントローラ250は、ブロック1及びブロック2をそれぞれ要求する、2つのホストコマンド - コマンド1及びコマンド2 - を受信する。コマンド1及びコマンド2のそれぞれは、ブロック1及びブロック2に対して対応する論理シーケンスもそれぞれ特定する。バッファ212は、ブロック1の全ての部分よりも前に、ブロック2の全ての部分を受信することができる。そのような場合においては、ホストコマンドが受信された順序で取得されたブロックをホストへ送信するように、コントローラ250が構成されてよい。言い換えると、ホストコマンド2よりも前にホストコマンド1が受信された場合、コントローラ250は、まずブロック1の複数の部分を送信し、次いでブロ

10

20

30

40

50

ック 2 の複数の部分を送信することができる。そのために、データの全ての部分が取得されてバッファ 212 に格納されても、コントローラ 250 がデータブロックの送信を遅らせることができる。

【 0048 】

あるいは、コントローラ 250 は、取得されたブロックがホストへ送信される順序を変更するように構成されてよい。例えば、ホストコマンド 2 よりも前にホストコマンド 1 が受信され、かつ、ブロック 1 の全ての部分を取得する前にブロック 2 の全ての部分をコントローラ 250 が取得した場合、コントローラ 250 は、まずブロック 2 の複数の部分をホストに送信し、次いでブロック 1 の複数の部分を送信することができる。これにより、取得されたブロックがホストに送信される順序を変更することができる。さらに、コントローラ 250 がブロック 1 の全ての部分は取得していないが、ブロック 2 の全ての部分を取得した場合、ブロック 1 の全ての部分が取得されるまで、ブロック 2 の複数の部分の送信をコントローラ 250 が遅らせることができる。

10

【 0049 】

図 5 は、複数のデータブロックを識別するコマンドに割り当てられた領域を含む、固体コントローラ 250 中のバッファ 212 の例を示す。いくつかの実施例においては、データブロックのそれぞれに対し、バッファ 212 は、データブロックの複数の部分に対するバッファアドレスを、対応するリスト中に格納する。データブロックのバッファアドレスを格納するリストがリンクされる。リスト中の各項目は、データブロックの一部分を格納するためのバッファ空間である。各項目は、対応するバッファアドレスでさらにラベルされる。データ取得部 210 によって取得され、エラーチェック及び補正ユニット 220 によってチェックされたブロック\_部分をバッファ 212 が受信するにつれて、バッファ 212 は、ブロック\_部分のアドレスに基づいて識別される対応するバッファ空間中にそれぞれのブロック\_部分を格納することによって、リンクされるリストを追加する。

20

【 0050 】

図 6 は、ホストからのコマンドに応じて、不揮発性メモリユニットからデータを取得するプロセス 600 の例を示す。605において、データブロックを識別するコマンドが受信される。コマンドは、識別されたブロックに含まれるデータブロックの複数の部分が送信されるべき第 1 シーケンスも識別する。610において、それぞれの不揮発性メモリユニットから、データブロックの複数の部分が第 1 シーケンスとは異なる第 2 シーケンスで取得される。615において、取得された複数の部分がバッファに格納される。620において、第 2 シーケンスで取得されたデータブロックの複数の部分が追跡される。625において、取得されたデータが、データブロックの全ての部分を含むかが判断される。630において、バッファは、判断したことに応じてデータブロックを送信するように指示される。

30

【 0051 】

プロセス 600 は、ハードウェア、ファームウェア、又は、それらの組み合わせを含む処理回路を用いて実行することができる。いくつかの実施例においては、同一のホスト又は異なるホストから、付加的なデータブロックを識別する付加的なコマンドを受信することができる。これに応じて、対応するデータブロック及び付加的なデータブロックの複数の部分が取得される。さらに、取得された複数の部分は交互に配置され、バッファに送信される。特に、付加的なデータブロックの複数の部分がデータブロックの複数の部分と一緒に送信されるように、取得された複数の部分が交互に配置されてよい。

40

【 0052 】

いくつかの実施例を上記のように詳細に記載したが、様々な変更が可能である。いくつかの実施例においては、大きなデータブロックが複数のチャネルにわたって均等に分配されておらず、むしろ単一のチャネルに集中している場合に、複数のコマンドをコントローラ 250 が並行して実行することにより、与えられた大きなデータブロックのグループに対する実行時間を最小限にすることができる。表 4 は、3 つの大きなデータブロック、つまり部分 102 - 105 を含むブロック 1、部分 207 - 209 を含むブロック 2、及び

50

、部分 404 - 407 を含むブロック 4 にアクセスするためであり、それぞれが不揮発性メモリユニットの対応するセクタと協働するように結合された 4 つのチャネルを示す。

【表 4】

| 表4 - 3つの大きなデータブロックにアクセスするための4つのチャネル216 |      |      |      |

|----------------------------------------|------|------|------|

| CH 0                                   | CH 1 | CH 2 | CH 3 |

|                                        | 104  | 209  |      |

| 404                                    | 105  | 406  | 207  |

| 407                                    | 103  |      | 206  |

|                                        | 102  | 405  | 208  |

|                                        |      |      |      |

|                                        |      |      |      |

| ...                                    |      |      |      |

10

20

【0053】

ブロック 1 を識別したコマンドと並行して、ブロック 2 及びブロック 4 を識別したコマンドを提供することにより、チャネル 216 において得られる処理能力が十分に利用され、データブロックのグループに対する読み出し性能を最大限にすることができる。データ取得部 210 は 4 つのバス / オペレーションでブロックを読み出すが、その期間において 3 つのコマンドが提供される。

【0054】

そのようにするために、データブロックの一部分が、適切な位置、例えばバッファ 212 のセクタに送られる。通常は、1 つのオペレーションにおいて読み出された複数の部分は、データブロックの複数の部分を格納するために用意されたバッファ 212 の物理領域である、バッファ中の同一の論理セグメントへ送られる。論理セグメントは、連続的な、あるいは、物理的に分散したアドレス空間であってよく、コントローラ 250 によってリンク及び管理される。

【0055】

図 7 は、チャネル 216 からバッファ 212 へのデータフローの例を示す。データ取得部 210 が実行するデータ取得オペレーションは、バッファ 212 中に、複数の行き先セグメント 705、710、715 を有することができる。行き先セグメントのそれぞれは、提供されるべきコマンドに対応し、コマンドはデータブロックを識別する。CPU 205 は、行き先位置を制御することができる。例えば、CPU 205 はバッファ分散リストによって行き先セグメントを制御することができる。それぞれのバスが実行されるにつれて、正しい行き先セグメント、及び、それぞれのセグメント内においてさらに適当なオフセットへとデータブロックの一部分を分配するためのバッファ分散リストを、CPU 205 は構築することができる。

【0056】

本明細書に記載される機能的なオペレーションを含め、開示される主題は、電子回路、コンピュータハードウェア、ファームウェア、ソフトウェア、又はそれらの組み合わせ等、本明細書に開示される構造的な手段、及び構造的なその等価物として実施することができる。

30

40

50

きる。これは、記載されるオペレーションを1つ以上のデータ処理装置に実行させるべく動作可能なプログラム（メモリデバイス、ストレージデバイス、機械読み取り可能なストレージ基板、あるいは、その他の物理的機械読み取り可能な媒体、又はそれらの1つ以上の組み合わせであり、コンピュータ読み取り可能な媒体中の符号化されたプログラム等）を含む。

【0057】

本開示には多くの詳細な点が含まれているが、これらは、特許請求の範囲に対する限定とみなされるべきではなく、むしろ、特定の実施例に対して具体的な特徴を記載するものとみなされるべきである。個々の実施例の関係において本明細書に記載されるいくつかの特徴は、1つの実施例において組み合わせて実行されてもよい。反対に、1つの実施例に関連して記載される様々な特徴が、複数の実施例において別々に実行されてよく、あるいは、任意の適切なサブコンビネーションにおいて実行されてもよい。さらに、上記の特徴は、特定の組み合わせにおいて作用するように記載され、元々そのように請求されてもいるかもしれないが、いくつかの場合においては、請求される組み合わせから1つ以上の特徴が削除されてよく、また、請求される組み合わせが、サブコンビネーション又はサブコンビネーションの変形に向けられたものでもよい。

10

【0058】

同様に、オペレーションは特定の順序で図面に記述されているが、これは、示されている特定の順序で、又は連続した順序でそのようなオペレーションが実行される必要があると理解されるべきではない。あるいは、望ましい結果を達成するために、示される全てのオペレーションが実行される必要があると理解されるべきではない。さらに、上述の実施例における様々なシステム構成要件を分離することは、全ての実施例においてそのような分離が必要であると理解されるべきではない。

20

【0059】

その他の実施例は、以下の特許請求の範囲の範囲内に入るものである。

[項目1]

データブロックを識別し、識別された前記データブロックを送信する第1シーケンスを識別するコマンドに対応して、前記データブロックを保持し、前記データブロックの複数の部分が、対応する複数の不揮発性メモリユニットに格納されるバッファと、

前記コマンドに応答して、前記データブロックの前記複数の部分を、前記対応する複数の不揮発性メモリユニットから前記第1シーケンスとは異なる第2シーケンスで取得し、取得された前記データブロックの前記複数の部分を前記バッファへ送信するデータ取得部と

30

を備え、

前記第2シーケンスで取得された前記データブロックが追跡され、

前記バッファは、前記データ取得部が前記データブロックに含まれる前記複数の部分を取得したことを示す指示に応答して、前記データブロックを送信するデバイス。

[項目2]

前記バッファは、複数のコマンドにそれぞれ対応する複数のデータブロックを保持し、前記データ取得部は、異なる前記複数のデータブロックの異なる複数の部分を並行して取得する項目1に記載のデバイス。

40

[項目3]

前記データ取得部は、第1コマンドに対応するデータブロックの複数の部分を、第2コマンドに対応するデータブロックの複数の部分と交互に配置する項目2に記載のデバイス。

[項目4]

それぞれの不揮発性メモリユニットは複数のセクタを有し、

前記データブロックの前記複数の部分は、前記複数の不揮発性メモリユニットの前記複数のセクタにわたって格納され、

前記データ取得部は、前記複数のセクタから前記データブロックの前記複数の部分を前記第2シーケンスで取得する項目1に記載のデバイス。

50

## [ 項目 5 ]

前記第1シーケンスを受信し、前記第2シーケンスで取得される前記データブロックを追跡し、前記データブロックに含まれる全ての前記複数の部分を前記データ取得部が取得したことを示す指示を提供するシーケンサと、

前記データ取得部と協働するように結合され、前記データ取得部によって取得されたデータブロックの1つ以上の部分をチェックするエラーチェック及び補正ユニットとをさらに備え、

前記データ取得部は、前記データブロックの前記複数の部分を前記第2シーケンスで前記エラーチェック及び補正ユニットへ送信する項目1に記載のデバイス。

## [ 項目 6 ]

10

前記エラーチェック及び補正ユニットは、前記シーケンサと協働するように結合され、前記データブロックの一部分にエラーが無いことを示す信号を前記シーケンサへ送信し、

前記シーケンサは、前記データブロックのそれぞれの部分に対して前記エラーチェック及び補正ユニットが前記データブロックの前記一部分の識別子及び前記一部分にエラーが無いことを示す信号を送信するか判断することによって、前記第2シーケンスで取得された前記データブロックを追跡する項目5に記載のデバイス。

## [ 項目 7 ]

20

対応する複数の不揮発性メモリユニットに複数の部分が格納されるデータブロックを識別し、識別された前記データブロックを送信する第1シーケンスを識別する、前記データブロックに対するコマンドを受信する段階と、

処理回路によって、前記データブロックの前記複数の部分を、前記対応する複数の不揮発性メモリユニットから前記第1シーケンスとは異なる第2シーケンスで取得し、取得された前記データブロックはバッファに格納される段階と、

取得された前記データが、前記第2シーケンスに従って前記データブロックの前記複数の部分を含むか判断する段階と、

前記判断することに応答して、前記データブロックを送信させるよう前記バッファに指示する段階と

を備える方法。

## [ 項目 8 ]

30

前記第2シーケンスで取得された前記データブロックの前記複数の部分を追跡する段階をさらに備える項目7に記載の方法。

## [ 項目 9 ]

付加的なデータブロックを送信するための付加的なコマンドを受信する段階と、

前記コマンドに対応する前記データブロック及び前記付加的なコマンドに対応する前記付加的なデータブロックを並行して取得する段階と

をさらに備える項目7に記載の方法。

## [ 項目 10 ]

前記データブロックの複数の部分を、前記付加的なデータブロックの複数の部分と交互に配置する段階をさらに備え、

交互に配置された前記複数の部分は前記バッファに格納される

項目9に記載の方法。

40

## [ 項目 11 ]

取得された前記データブロックの前記複数の部分を前記バッファへ送信する段階をさらに備える項目7に記載の方法。

## [ 項目 12 ]

それぞれの不揮発性メモリユニットは複数のセクタを有し、

前記データブロックの前記複数の部分は、前記複数の不揮発性メモリユニットの前記複数のセクタにわたって格納され、

前記データブロックの前記複数の部分を取得する段階は、前記複数のセクタから前記データブロックの前記複数の部分を前記第2シーケンスで取得する段階を有する項目7に記

50

載の方法。

[ 項目 1 3 ]

前記取得されたデータブロックにエラーが無いかを判断するために、データブロックの1つ以上の部分をチェックする段階をさらに備える項目 7 に記載の方法。

[ 項目 1 4 ]

前記データブロックの一部分にエラーが無いことを示す信号を送信する段階をさらに備え、

前記追跡する段階は、前記データブロックのそれぞれの部分に対して前記データブロックの前記一部分の識別子及び前記一部分にエラーが無いことを示す信号が送信されるか判断することによって、前記第 2 シーケンスで取得された前記データブロックを追跡する段階を有する

10

項目 1 3 に記載の方法。

[ 項目 1 5 ]

複数のデータブロックの複数の部分を格納する複数の不揮発性メモリユニットと、

前記複数の不揮発性メモリユニットの1つ以上に格納される1つ以上のデータブロックを受信するための複数のコマンドを送信するホストと、

前記複数の不揮発性メモリユニットと前記ホストとの間でデータを送信するコントローラと

を備え、

前記コントローラは、

20

それぞれがデータブロック及び前記ホストへ送信する前記データブロックの第 1 シーケンスを識別する複数のコマンドを前記ホストから受信し、

前記複数の不揮発性メモリユニットに格納される複数のデータブロックを並行して取得し、

それぞれのコマンドに対し、取得されたデータブロックの前記複数の部分が前記データブロックの前記データを含むか判断し、

前記判断することに応答して、取得された前記データブロックを送信し、

1つ以上のデータブロックの複数の部分は、対応する前記コマンドによって識別される前記第 1 シーケンスとは異なる第 2 シーケンスで取得されるシステム。

[ 項目 1 6 ]

30

前記コントローラはさらに、第 1 コマンドを受信することに応答して取得される第 1 データブロックの複数の部分を、第 2 コマンドに応答して取得される第 2 データブロックの複数の部分と交互に配置し、

交互に配置された前記複数の部分はバッファに格納される

項目 1 5 に記載のシステム。

[ 項目 1 7 ]

それぞれの不揮発性メモリユニットは複数のセクタを有し、

前記データブロックの前記複数の部分は、前記複数の不揮発性メモリユニットの前記複数のセクタにわたって格納され、

前記コントローラは、前記複数のセクタから前記データブロックの前記複数の部分を前記第 2 シーケンスで取得する項目 1 5 に記載のシステム。

40

[ 項目 1 8 ]

前記コントローラと協働するように結合され、データブロックの1つ以上の部分をチェックして取得された前記データブロックにエラーが無いか判断するエラーチェック及び補正ユニットをさらに備える項目 1 5 に記載のシステム。

[ 項目 1 9 ]

前記エラーチェック及び補正ユニットは、前記データブロックの一部分にエラーが無いことを示す信号を前記バッファへ送信する項目 1 8 に記載のシステム。

[ 項目 2 0 ]

前記コントローラはさらに、前記データブロックのそれぞれの部分に対して前記データ

50

プロックの前記一部分の識別子及び前記一部分にエラーが無いことを示す信号が送信されるか判断することによって、前記第2シーケンスで取得された前記データプロックを追跡する項目19に記載のシステム。

【図1】

【図3】

FIG. 3

【図2】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(72)発明者 オウ、シュウ - ハン フレッド

アメリカ合衆国、95054 カリフォルニア州、サンタ クララ、マーベル レーン 5488

マーベル セミコンダクター インコーポレイテッド内

(72)発明者 ニューイエン、ラウ

アメリカ合衆国、95054 カリフォルニア州、サンタ クララ、マーベル レーン 5488

マーベル セミコンダクター インコーポレイテッド内

(72)発明者 ネオス、ペリー

アメリカ合衆国、95054 カリフォルニア州、サンタ クララ、マーベル レーン 5488

マーベル セミコンダクター インコーポレイテッド内

審査官 坂東 博司

(56)参考文献 特開平07-334413 (JP, A)

特開平08-106365 (JP, A)

特開2005-115600 (JP, A)

特開2007-156582 (JP, A)

特表2005-525652 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G06F 3/06

G06F 3/08