(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4895867号

(P4895867)

(45) 発行日 平成24年3月14日(2012.3.14)

(24) 登録日 平成24年1月6日(2012.1.6)

(51) Int.Cl.

G05F 1/56 (2006.01)

G11C 16/06 (2006.01)

F 1

G05F 1/56 310F

G11C 17/00 632A

請求項の数 5 (全 23 頁)

(21) 出願番号 特願2007-55934 (P2007-55934)

(22) 出願日 平成19年3月6日 (2007.3.6)

(65) 公開番号 特開2008-217577 (P2008-217577A)

(43) 公開日 平成20年9月18日 (2008.9.18)

審査請求日 平成22年1月27日 (2010.1.27)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100083703

弁理士 仲村 義平

(74) 代理人 100096781

弁理士 堀井 豊

(74) 代理人 100109162

弁理士 酒井 将行

(74) 代理人 100111246

弁理士 荒川 伸夫

最終頁に続く

(54) 【発明の名称】 内部電圧発生回路

## (57) 【特許請求の範囲】

## 【請求項 1】

ポンプ動作により電圧出力線に昇圧電圧を生成するポンプ回路、

前記ポンプ回路の電圧出力線に結合され、前記ポンプ回路の電圧出力線と出力ノードとの間に電流を流す第1の電流源、

動作モードに応じて電圧レベルが設定される基準電圧を発生する基準電圧発生回路、

動作時、前記基準電圧発生回路からの基準電圧と前記出力ノードの電圧とを比較し、該比較結果に応じた信号を生成する比較回路、

前記比較回路の出力信号に従って前記出力ノードと参照電位ノードとの間に電流を流すドライブ素子、

前記ポンプ回路の電圧出力線と前記比較回路との間に結合され、前記比較回路の動作電流を流す第2の電流源、

前記第1の電流源と前記出力ノードとの間に接続され、前記第1の電流源と前記出力ノードとの間に電圧差を生じさせて前記第1の電流源に印加される電圧を緩和する第1の耐圧緩和回路、

前記第2の電流源と前記比較回路との間に接続され、前記第2の電流源と前記比較回路との間に電圧差を生じさせて前記比較回路の構成要素に印加される電圧を緩和する第2の耐圧緩和回路、および

前記出力ノードと前記ドライブ素子との間に接続され、前記ドライブ素子に印加される電圧を緩和する第3の耐圧緩和回路を備える、内部電圧発生回路。

10

20

### 【請求項 2】

前記比較回路は、前記基準電圧を受ける第1の比較入力ノードと、前記出力ノードに結合される第2の比較入力ノードとを有し、

前記内部電圧発生回路は、さらに、

短絡指示信号に従って、前記ポンプ回路の電圧出力線と前記出力ノードとを電気的に短絡する第1の短絡素子と、

前記前記短絡指示信号に従って前記第1の短絡素子と相補的に導通し、導通時、前記出力ノードと前記第2の比較入力ノードとを電気的に結合する第2の短絡素子と、

前記出力ノードと前記第2の比較入力ノードとの間に接続され、前記出力ノードと前記第2の比較入力ノードとの間に電圧差を生じさせる耐圧緩和素子とを備える、請求項1記載の内部電圧発生回路。10

### 【請求項 3】

前記第1の電流源は、駆動電流量が変更可能な可変電流源であり、

前記内部電圧発生回路は、さらに、動作モードに従って前記可変電流源の供給電流量を設定するセレクタを備える、請求項1または2に記載の内部電圧発生回路。

### 【請求項 4】

前記第1の耐圧緩和回路は、前記第1の電流源と前記出力ノードとの間に接続され、ゲートに第1の耐圧制御信号を受ける第1導電型の第1のトランジスタを備え、

前記第2の耐圧緩和回路は、前記第2の電流源と前記比較回路の電源ノードとの間に接続され、ゲートに前記第1の耐圧制御信号を受ける第1導電型の第2のトランジスタを備え。20

前記第3の耐圧緩和回路は、前記出力ノードと前記ドライブ素子との間に接続され、ゲートに第2の耐圧制御信号を受ける第2導電型の第3のトランジスタを備える、請求項1から3のいずれかに記載の内部電圧発生回路。

### 【請求項 5】

前記第1の耐圧緩和回路は、さらに、前記第1のトランジスタと前記第1の電流源の間の接続ノードの電圧をクランプする第1のクランプ素子を備え、

前記第2の耐圧緩和回路は、さらに、前記第2のトランジスタと前記第2の電流源の間の接続ノードの電圧をクランプする第2のクランプ素子を備え、

前記第3の耐圧緩和回路は、さらに、前記第3のトランジスタと前記ドライブ素子の間の接続ノードの電圧をクランプする第3のクランプ素子を備える、請求項4記載の内部電圧発生回路。30

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

この発明は、内部電圧発生回路に関し、特に、ポンプ動作により昇圧電圧を発生するポンプ回路からの電圧に従って所望の電圧レベルの内部電圧を生成する回路の構成に関する。より特定的には、この発明は、小面積かつ低消費電力で所望の電圧レベルの内部電圧を生成する内部電圧発生回路の構成に関する。

#### 【背景技術】

#### 【0002】

半導体装置においては、電源電圧および接地電圧と異なる電圧レベルの電圧が用いられることが多い。このような電圧は、装置外部から供給する場合、半導体装置の端子数が増大し、または外部信号線の充放電電流により消費電流が増大するという問題が生じる。したがって、半導体装置内部で、必要な電圧レベルの電圧を生成する。このような内部電圧を発生する回路としては、容量素子のチャージポンプ動作を利用するポンプ回路が広く用いられる。40

#### 【0003】

不揮発性半導体記憶装置において、このポンプ回路を用いて必要な内部電圧を生成する構成が、特許文献1（特開2006-185530号公報）に示されている。この特許文50

献1においては、チャージポンプ回路の段数を動作モードに応じて変更する。また、動作モードに応じてチャージポンプ回路のポンプ段を並列接続することにより、電流駆動力を大きくする。この特許文献1は、複数のマクロに共通に1つの電源回路を設け、動作モードに応じて、この電源回路に含まれるチャージポンプ回路の段数および電流駆動力を調整することを図る。電源回路をメモリブロック(マクロ)ごとに設けた場合、電源回路の数が増大し、応じて占有面積が増大するという問題を解消することを図る。

#### 【0004】

また液晶駆動回路によりデータ線およびソース線を駆動する場合の電圧を、チャージポンプ回路により生成する構成が、特許文献2(特開2006-201807号公報)に示される。この特許文献2に示される構成においては、内部電圧それぞれに対応して昇圧回路を設け、高速応答および低消費電流が要求される電圧を、それぞれ異なるチャージポンプ回路で生成する。安定性が要求される電圧は、外部からの電圧を利用する。

10

#### 【0005】

この特許文献2は、従来技術として、チャージポンプ回路の出力電圧を抵抗で分圧して、オペアンプでインピーダンス変換を行なって高電圧VHおよび低電圧VLを生成する場合、データ線駆動時に無効電流が抵抗分圧回路において流れ、インピーダンス変換用のオペアンプにおいて無駄な電流が消費される問題を、解消することを図る。

#### 【0006】

また、電源電圧から必要な電圧レベルの内部電圧を生成する内部電圧生成回路が、特許文献3(特開2004-133954号公報)に示されている。この特許文献3においては、電源線から出力ノードへ定電流源を介して電流を供給する。この出力ノードの電圧と基準電圧とを比較し、その比較結果に従って出力ノードから電流を引抜く。出力ノードの電圧レベルを、基準電圧が決定する電圧レベルに維持する。

20

#### 【0007】

また、定電流を利用して高電圧を発生する回路のトランジスタの耐圧特性を保証する構成が、特許文献4(特開2005-222301号公報)に示されている。この特許文献4においては、負荷と接地ノードの間に高耐圧MOSトランジスタおよび低耐圧MOSトランジスタを直列に接続する。高耐圧MOSトランジスタを負荷側に接続する。これらのMOSトランジスタは、デプレシヨントランジスタであり、それぞれのゲートが接地ノードに接続される。高耐圧MOSトランジスタのしきい値電圧の絶対値は、低耐圧MOSトランジスタのしきい値電圧の絶対値よりも大きくされる。負荷に対しては電源ノードから動作電源電圧および電流が供給される。MOSトランジスタにより定電流を負荷から引抜く。低耐圧MOSトランジスタのドレイン-ソース電圧に対して、高耐圧MOSトランジスタおよび低耐圧MOSトランジスタのドレイン電流が、相反的に変化する。この定電流回路の動作点は、これらのMOSトランジスタを流れる電流が一致する点である。この場合、低耐圧MOSトランジスタのドレイン-ソース間耐圧としては、高耐圧MOSトランジスタのしきい値電圧の絶対値以上の値が要求されるだけである。

30

#### 【0008】

この特許文献4は、高耐圧MOSトランジスタのしきい値電圧により、低耐圧MOSトランジスタに印加される電圧の上限値を制限して、低耐圧MOSトランジスタの耐圧を保証する。また、低耐圧MOSトランジスタを利用して、電流値を設定することにより、安定性を改善することを図る。また、負荷側ノードを電源ノードとして利用することにより、この定電流回路の動作電源電圧範囲を、低耐圧MOSトランジスタのしきい値電圧の絶対値まで拡張して、電源電圧の変動時においても安定に定電流を生成することを図る。

40

【特許文献1】特開2006-185530号公報

【特許文献2】特開2006-201807号公報

【特許文献3】特開2004-133954号公報

【特許文献4】特開2005-222301号公報

#### 【発明の開示】

【発明が解決しようとする課題】

50

## 【0009】

特許文献1においては、複数のメモリブロックに共通に電源回路を設け、動作モードに応じて、電源回路に含まれるチャージポンプの段数を変更する。チャージポンプ回路の段数を多くすることにより、昇圧電圧の電圧レベルを高くし、書込および消去に必要な電圧を生成する。この書込および消去は、メモリブロック単位で実行する。一方、データ読出時においては、チャージポンプ段数を低減しつゝ並列に接続することにより、複数のメモリブロックに対して、読出電圧を安定に供給することを図る。この電流駆動力調整時においては、消去および書込時には中速のポンプクロック信号を供給し、読出時には、高速のクロック信号を供給する。スタンバイ時には、低速のクロック信号を供給して、スタンバイ時の消費電流を低減する。しかしながら、この特許文献1においては、チャージポンプ回路の出力電圧そのものを書込、消去および読出に利用する構成が示されているだけであり、このチャージポンプ回路の出力電圧から、さらに、所望の電圧レベルの内部電圧を生成する構成については何ら考慮していない。また、高電圧発生時のトランジスタの耐圧については、何ら考慮していない。

10

## 【0010】

特許文献2は、液晶ドライバであり、内部で必要とされるデータ線駆動電圧を、それぞれ専用のチャージポンプ回路を用いて生成している。これにより、抵抗分圧回路を利用する場合の消費電力を低減することを図る。しかしながら、この特許文献2においては、内部電圧それぞれに、専用のチャージポンプ回路を設けているだけであり、共通のチャージポンプ回路の出力電圧から複数の電圧レベルの内部電圧を生成する構成については考慮していない。また、チャージポンプ動作停止時において残留電荷を高速で放電するための回路構成が特許文献2においては示されているものの、この高電圧発生時における、内部電圧生成部の耐圧については何ら考察されていない。

20

## 【0011】

この特許文献2は、抵抗分圧回路により高電圧を複数の電圧レベルに分圧して、必要とされる内部電圧を選択する構成の場合、回路面積および消費電流が大きくなるという問題を解決することを図る。しかしながら、必要とされる内部電圧レベルに対応してポンプ回路を設ける場合、回路占有面積が増大するという問題が、依然解消されない。

## 【0012】

特許文献3は、電源線から定電流を供給し、内部電圧と基準電圧との差に応じて出力ノードから電流を引抜いて内部電圧を生成する。この内部電圧は、電源電圧よりも低い電圧レベルである。特許文献3は、電源電圧よりも高い電圧を生成する回路構成については何ら考慮していない。

30

## 【0013】

特許文献4は、耐圧特性を劣化させることなく、定電流回路の動作電圧範囲を拡張することを図る。この特許文献4は、定電流を引抜くデプレッション型トランジスタの耐圧を保証するために、高耐圧トランジスタを低耐圧トランジスタに直列に接続している。生成される内部電圧（定電流回路の動作電源電圧）は、電源電圧よりも低い電圧である。特許文献4は、電源電圧よりも高い電圧を安定に生成することについては、考慮していない。また、定電流を生成しているものの、単に負荷を流れる電流を一定とする定電流源を示しているだけであり、この定電流をどのように利用するかについては、具体的に示していない。「負荷」は、トランジスタ、ダイオード、信号線およびこれらの組合せによる各種回路を示すとされているだけである。

40

## 【0014】

それゆえ、この発明の目的は、チャージポンプ回路の出力電圧レベルに依存することなく、安定に低消費電流かつ低占有面積で、内部電圧を生成することのできる内部電圧発生回路を提供することである。

## 【課題を解決するための手段】

## 【0015】

この発明に係る内部電圧発生回路は、要約すれば、チャージポンプ回路の出力と内部電

50

圧出力ノードとの間に電流源を設け、内部電圧出力ノードとポンプ回路の出力ノードとの間に電流を流すとともに、この内部電圧出力ノードの電圧レベルと基準電圧との比較結果に基づいて、出力ノードと参照ノードの間に接続されるドライブ素子のコンダクタンスを調整する。基準電圧は、動作モードに応じて、その電圧レベルが設定される。電流源、ドライブ素子、および比較回路に対して、印加電圧を緩和する耐圧緩和回路を設ける。

【0016】

すなわち、この発明の一実施の形態に従えば、内部電圧発生回路は、ポンプ動作により昇圧電圧を生成するポンプ回路と、ポンプ回路の出力と内部電圧出力ノードとの間に結合され、内部電圧出力ノードとポンプ回路出力との間に電流を流す電流源と、内部電圧出力ノードの電圧と基準電圧とを比較する比較回路と、この比較回路の出力信号に従って内部電圧出力ノードと参照電圧ノードとの間に電流を流すドライブ素子と、比較回路、ドライブ素子および電流源に対して印加電圧を緩和する耐圧緩和回路とを備える。

10

【0017】

電流源は、好ましくは、選択信号に従って駆動電流量が設定され、内部電圧出力ノードに電流を供給する。基準電圧発生回路は、動作モードに応じて電圧レベルが調整される基準電圧を発生する。比較回路は、このポンプ回路の出力から動作電流を供給され、動作時に、基準電圧発生回路からの基準電圧と内部電圧出力ノードの電圧とを比較し、その比較結果に応じた信号を生成する。

【発明の効果】

【0018】

20

電流源およびドライブ素子により、チャージポンプ回路の出力から内部電圧を生成している。したがって、チャージポンプ回路の出力電圧を分圧するための高抵抗素子が不要となり、占有面積を低減することができる。

【0019】

また、耐圧緩和回路を設けることにより、不揮発性メモリに適用される場合、不揮発性メモリ特有の高電圧生成時においてもトランジスタ素子の耐圧が保証され、安定に所定の電圧レベルの高電圧を生成することができる。

【0020】

また、このような電流源として、駆動電流量を動作状況に応じて変更することのできる電流源を利用することにより、以下の効果が得られる。すなわち、出力負荷および動作モードに応じて駆動電流量を調整することができる。これにより、必要以上に電流が消費されるのを防止することができ、消費電力を低減することができる。

30

【0021】

また、ドライブ素子が、基準電圧との内部電圧との比較に基づいてそのコンダクタンスが調整される。これにより、正確に内部電圧を、基準電圧が規定する電圧レベルに設定することができる。また、基準電圧の電圧レベルを動作モードに応じて変更することにより、1つのポンプ回路の出力から複数レベルの内部電圧を生成することができる。内部電圧のレベルに応じて、個々に、チャージポンプ回路を設ける必要がなく、内部電圧発生回路のレイアウト面積を低減することができる。

【0022】

40

また、内部電圧線の充放電により内部電圧の電圧レベルを設定することができる。このため、抵抗分圧回路のように高抵抗を介して内部電圧線を充放電する必要がなく、高速で所定の電圧レベルの内部電圧を生成することができる。

【発明を実施するための最良の形態】

【0023】

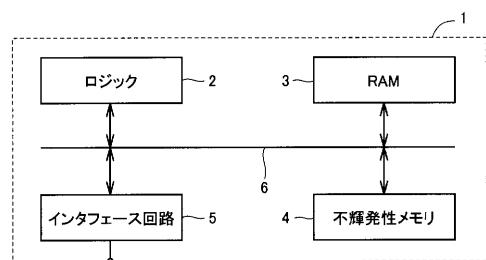

【実施の形態1】

図1は、この発明が適用される不揮発性半導体記憶装置を含む半導体集積回路装置の全体の構成の一例を、概略的に示す図である。図1において、半導体集積回路装置1は、動作制御および演算処理を実行するロジック2と、RAM(ランダム・アクセス・メモリ)3と、不揮発性メモリ4とを含む。RAM3は、ロジック2の演算処理するデータを格納

50

する作業領域として用いられ、また、外部との間でのデータ転送時のバッファ領域として用いられる。

【0024】

不揮発性メモリ4は、データの書換が可能であり、アプリケーションプログラム、ブートプログラム、および大量のダウンロードデータなどを格納する。

【0025】

ロジック2、RAM3および不揮発性メモリ4は、内部データバス6を介して相互接続される。内部データバス6は、インターフェイス回路5を介して外部と結合される。したがって、ロジック2は、内部データバス6およびインターフェイス回路5を介して外部との間でデータの転送を行ない、また、RAM3または不揮発性メモリ4は、DMA(ダイレクト・メモリ・アクセス)モードで、インターフェイス回路5を介して外部との間でデータ転送を行なう。

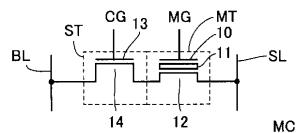

【0026】

図2は、図1に示す不揮発性メモリ4に含まれるメモリセルMCの構成の一例を、概略的に示す図である。図2において、メモリセルMCは、データを記憶するメモリセルトランジスタMTと、メモリセルMCを選択するための選択トランジスタSTとを含む。メモリセルトランジスタMTは、導通時にチャネルが形成されるチャネル形成領域12と、このチャネル形成領域12上に形成される電荷蓄積膜11と、電荷蓄積膜11への電荷の注入/引抜きを制御するメモリセルゲート10とを含む。電荷蓄積膜11は、ONO膜(酸化膜-窒化膜-酸化膜)の積層構造を有し、この窒化膜中に、記憶データに応じて電荷を蓄積する。選択トランジスタSTは、チャネル形成領域14と、チャネル形成領域14上に図示しないゲート絶縁膜を介して形成されるコントロールゲート13とを含む。メモリセルトランジスタMTおよび選択トランジスタSTが、各々、一例として、Nチャネルトランジスタで構成される。

【0027】

メモリセルMCにおいて、メモリセルトランジスタMTと選択トランジスタSTがソース線SLとビット線BLの間に直列に接続される。メモリセルトランジスタMTがソース線SLに結合され、選択トランジスタSTが、ビット線に結合される。選択トランジスタSTのコントロールゲート13が、コントロールゲート線CGに結合され、メモリセルトランジスタMTのメモリセルゲート10が、メモリゲート線MGに結合される。

【0028】

メモリセルMCへのデータ書込時においては、選択トランジスタSTを、弱いオン状態に設定する(コントロールゲート線CGへ、選択トランジスタSTのしきい値電圧より少し高い電圧を印加する)。メモリゲート線MGにたとえば11Vの電圧を印加し、ソース線SLに、たとえば5Vの電圧を印加する。ビット線BLは、たとえば0.8V程度に設定される。この場合、ソース線SLからビット線BLに電流が流れる。選択トランジスタSTのチャネル形成領域14は、高抵抗状態であり、このメモリセルトランジスタMTにおいて、ソース側で高電界によりホットエレクトロンが生成される。このホットエレクトロンが、メモリセルゲート10の高電圧により電荷蓄積膜11方向に引かれて、電荷蓄積膜11内の窒化膜に注入されてトラップされる。この状態では、メモリセルトランジスタMTは、しきい値電圧が高い状態である。

【0029】

データの消去時においては、逆に、メモリセルゲート10に負のたとえば-7V程度の電圧を印加し、ソース線SLに5V程度の電圧に印加する。選択トランジスタSTは、書込時と同様、弱いオン状態に設定される。ビット線は同様、0.8V程度である。ソース線SLからビット線BLへ電流が流れる場合、メモリセルトランジスタMTのドレイン側(ソース線SLに接続される導通ノード(不純物領域))において高電界が発生し、ホットホールが生成される。このホットホールが、バンド間トンネリングにより、電荷蓄積膜11に注入される。これにより、電荷蓄積膜11に蓄積されるエレクトロンとホールとの中和が生じ、消去が行なわれる。消去状態においては、メモリセルトランジスタMTは、

10

20

30

40

50

しきい値電圧が低い状態である。

【0030】

データ読出時においては、メモリゲート線MGが、たとえば読出電圧レベルに設定される。読出電圧は、メモリセルトランジスタMTの消去状態と書込状態のしきい値電圧の間の電圧レベルである。コントロールゲート線CGはHレベルに駆動し、選択トランジスタSTを、強いオン状態に設定する。メモリセルトランジスタMTは、電荷蓄積膜11の蓄積される電子量が多い書込状態のときには、しきい値電圧が高い状態であり、一方、電荷蓄積膜11に蓄積される電子量が少ない消去状態のときには、そのしきい値電圧は低い状態である。読出電圧が、書込状態と消去状態のしきい値電圧の間の電圧レベルに設定されるため、メモリセルトランジスタMTの記憶データ（しきい値電圧）に応じてビット線BLからソース線SLに電流が流れる。この電流量をセンスアンプ等により検出してデータの読出を行なう。10

【0031】

上述のように、メモリセルMCにおいては、書込および消去および読出において種々のレベルの電圧が必要とされる。また、データの書込／消去が確実に行なわれたかを内部で検証するために、またベリファイ電圧が生成される。これらの各種の電圧を、内部で生成する。なお、上述の電圧レベルは、単なる一例であり、これらの各種電圧の電圧レベルは、上述の電圧レベルに限定されない。以下の説明においても、同様である。

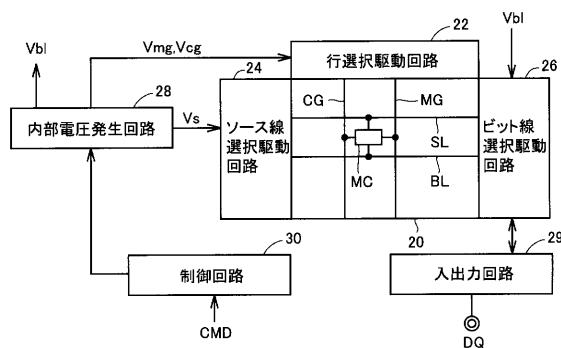

【0032】

図3は、図1に示す不揮発性メモリ4の全体構成を概略的に示す図である。図3において、不揮発性メモリ4は、メモリセルMCが行列状に配列されるメモリセルアレイ20を含む。メモリセルアレイ20においては、メモリセルMCの各行に対応してコントロールゲート線CGおよびメモリゲート線MGが配設される。メモリセルの各列に対応してビット線BLが配列される。図3においては、ソース線SLが、ビット線BLに平行にメモリセル列各々に対応して配置されるように示す。しかしながら、ソース線SLは、メモリセル行に対応して、行方向に延在するように配置されてもよい。20

【0033】

不揮発性メモリ4は、さらに、アドレス信号（図示せず）に従って選択行のコントロールゲート線CGおよびメモリゲート線MGを選択状態へ駆動する行選択駆動回路22と、ソース線SLを、データの書込／消去時に所定電圧レベルに駆動するソース線選択駆動回路24と、ビット線BLを選択し、選択ビット線へ動作モードに応じた電圧を伝達するビット線選択駆動回路26を含む。30

【0034】

行選択駆動回路22は、内部電圧発生回路28からの電圧VmgおよびVcgに従ってメモリゲート線MGおよびコントロールゲート線CGの電圧レベルを設定する。これらのメモリゲート線MGおよびコントロールゲート線CGの選択状態時の電圧レベルおよび非選択時の電圧レベルは、それぞれ動作モードに応じて設定される。例えば、書込時、メモリゲート線MGの選択電圧は11V、非選択電圧は3.5Vである。コントロールゲート線CGの選択電圧は1V、非選択電圧は0Vである。

【0035】

ソース線選択駆動回路24は、書込および消去が、ブロック単位で行なわれるとき、各ブロックごとに、ソース線を選択し、選択ソース線の電圧レベルを内部電圧発生回路28からの電圧Vsに従って設定する。データ読出時においては、ソース線選択駆動回路24は、ソース線SLを接地電圧レベルに維持する。例えば、書込時、選択ソース線電圧は、5V、非選択ソース線電圧は1.5Vまたは0Vである。40

【0036】

ビット線選択駆動回路26は、図示しないアドレス信号に従って、選択列に対応するビット線BLを選択し、消去時には選択ブロックのビット線に消去電圧も伝達する（ブロック単位での消去が行なわれるとき）。データ書込時においては、このビット線選択駆動回路26は、非選択列のビット線に対しては、書込阻止電圧を伝達して、選択行／非選択列50

のメモリセルへの電流が流れるのを防止する。また選択列のビット線に対しては、書込電圧を伝達して、選択メモリセルにおいて電流を流す。書込阻止電圧は、例えば、1.5Vであり、書込電圧は、例えば、0.8Vである。データ読出時、ビット線選択駆動回路26は、選択列のビット線に読出電圧を伝達するとともに、選択列を、入出力回路29に結合する。ビット線読出電圧は、ビット線およびメモリセルを介して電流を流し、このビット線電流を図示しないセンスアンプにより検知するために印加される。

#### 【0037】

入出力回路29は、外部のロジックまたはインターフェース回路(図1参照)との間で、データDQの書込/読出を行なう。この不揮発性メモリ4においては、内部動作を制御するための制御回路30が設けられる。この制御回路30は、たとえばシーケンスコントローラで構成され、外部からの動作モードを指示するコマンドCMDに従って各動作モードを実行するための内部制御信号を生成する。内部電圧発生回路28は、この制御回路30からの内部制御信号に従って、内部電圧Vmg、Vcg、VsおよびVblを、それぞれ動作モードに応じた電圧レベルに設定する。

10

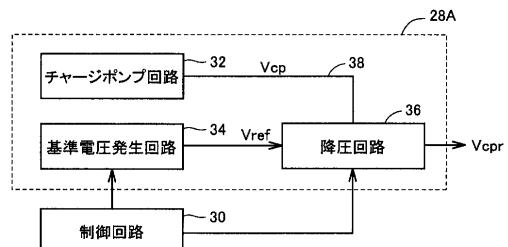

#### 【0038】

図4は、図3に示す内部電圧発生回路28の1種類の内部電圧を発生する部分28Aの構成を概略的に示す図である。内部電圧発生回路28Aが、各内部電圧Vmg、Vcg、VsおよびVblそれぞれに対応して設けられる。図4において、内部電圧発生回路28Aは、ポンプ動作に従って高電圧Vcpを生成するチャージポンプ回路32と、動作モードに応じて電圧レベルが設定される基準電圧Vrefを生成する基準電圧発生回路34と、この動作モードに応じて、チャージポンプ回路32からの出力電圧線38上に伝達される電圧Vcpを降圧して内部電圧Vcprを生成する降圧回路36とを含む。

20

#### 【0039】

チャージポンプ回路32は、容量素子のチャージポンプ動作を利用して、たとえば11Vから12Vのポンプ高電圧Vcpを生成する。このチャージポンプ回路32は、内部に、ポンプ高電圧Vcpの電圧レベルをモニタする電圧レベル検出回路を含む。このレベル検出回路の出力信号に従って内部でポンプ動作を制御して、ポンプ高電圧Vcpの電圧レベルを、所定の電圧レベルに維持する。

#### 【0040】

降圧回路36は、チャージポンプ回路32からのポンプ高電圧Vcpを降圧して、内部電圧Vcprを生成する。この降圧回路36の構成は後に詳細に説明するが、基準電圧発生回路34からの基準電圧Vrefと内部電圧Vcprの電圧レベルを比較し、その比較結果に従って、出力ノード50から電流を引抜き、内部電圧Vcprを、基準電圧Vrefの電圧レベルに維持する。

30

#### 【0041】

この基準電圧発生回路34が生成する基準電圧Vrefの電圧レベルの設定および降圧回路36の動作制御は、制御回路30により行なわれる。

#### 【0042】

図5は、図4に示す降圧回路36の構成をより具体的に示す図である。図5において、降圧回路36は、チャージポンプ回路32の出力電圧線38から電流を流す定電流源40と、定電流源40から動作電流を供給され、基準電圧Vrefと出力電圧Vcprとを比較する差動增幅回路(比較回路)44と、出力電圧線38から電流を供給する定電流源42と、差動增幅回路44の出力信号に従って出力ノード50から接地ノード(参照電圧ノード)に電流を引抜くドライブトランジスタ46とを含む。

40

#### 【0043】

定電流源40および42は、各々、アンプ活性化信号AMPENの活性化時(Hレベルのとき:ポンプ高電圧Vcpレベル)、図4に示すチャージポンプ回路32から出力電圧線38に伝達された電圧Vcpを電流に変換する。定電流源40および42は、各々、たとえば、電流源MOSトランジスタ(Pチャネル絶縁ゲート型電界効果トランジスタ)と、アンプ活性化信号AMPENの非活性化時(Lレベルのとき)導通し、電流源MOSト

50

ランジスタのゲートを出力電圧線 3 8 に電気的に結合する P チャネルM O S トランジスタと、アンプ活性化信号 A M P E N の活性化時導通し、定電圧レベルの電流制御電圧を電流源M O S トランジスタのゲートに伝達するトランスマッシュゲートとで構成される。電流制御電圧が接地電圧レベルである場合には、アンプ活性化信号 A M P E N の反転信号により、電流源M O S トランジスタのオン / オフを制御する。定電流源 4 0 は、活性化時、例えば 8  $\mu$  A の電流を流す。定電流源 4 2 は、活性化時、例えば 4 0  $\mu$  A の電流を流す。

#### 【 0 0 4 4 】

差動增幅回路 4 4 は、動作電源ノード 4 1 にソースノードが結合される P チャネルM O S トランジスタ P Q 1 および P Q 2 と、ソースノードが接地ノード ( V S S ノード ) に接続される N チャネルM O S トランジスタ N Q 1 および N Q 2 を含む。M O S トランジスタ P Q 1 は、そのゲートに基準電圧 V r e f を受け、M O S トランジスタ N Q 1 に電流を供給する。M O S トランジスタ P Q 2 は、出力ノード 5 0 上の電圧 V c p r をゲートに受け、M O S トランジスタ N Q 2 に電流を供給する。M O S トランジスタ N Q 1 および N Q 2 は、カレントミラー回路を構成する。M O S トランジスタ N Q 2 が、ゲートおよびドレンが相互接続され、このカレントミラー回路のマスターとして機能する。

#### 【 0 0 4 5 】

差動增幅回路 4 4 は、動作時、基準電圧 V r e f と出力電圧 V c p r とをM O S トランジスタ P Q 1 および P Q 2 により比較する。基準電圧 V r e f が出力電圧 V c p r よりも高い場合には、M O S トランジスタ P Q 1 よりもM O S トランジスタ P Q 2 を介して流れれる電流量が多くなる。M O S トランジスタ N Q 1 には、M O S トランジスタ N Q 2 を介して流れれる電流量と同じ大きさの電流が流れる ( ミラー比が 1 )。したがって、M O S トランジスタ N Q 1 の放電する電流量は、M O S トランジスタ P Q 1 が供給する電流量よりも大きくなり、内部ノード 4 9 の電圧レベルは低下する。逆に、基準電圧 V r e f が出力電圧 V c p r よりも低い場合には、M O S トランジスタ P Q 1 が供給する電流量が、M O S トランジスタ P Q 2 が供給する電流量よりも大きくなる。したがって、この場合には、M O S トランジスタ N Q 1 は、M O S トランジスタ P Q 1 からの電流をすべて放電することができず、内部ノード 4 9 の電圧レベルが上昇する。

#### 【 0 0 4 6 】

この差動增幅回路 4 4 の内部ノード 4 9 の信号電圧が比較結果指示信号として、ドライブトランジスタ 4 6 のゲートへ与えられる。従って、基準電圧 V r e f が出力電圧 V c p r よりも高い場合には、ドライブトランジスタ 4 6 のコンダクタンスが小さくなりまたはオフ状態となり、出力ノード 5 0 からの引抜き電流量が低下し、出力ノード 5 0 の電圧レベルが定電流源 4 2 からの電流により上昇する。一方、基準電圧 V r e f よりも出力電圧 V c p r が高い場合には、ドライブトランジスタ 4 6 のコンダクタンスが大きくなり、出力ノード 5 0 からの引抜き電流量が増加し、出力ノード 5 0 の電圧レベルを低下させる。従って、差動增幅回路 4 4 およびドライブトランジスタ 4 6 によるフィードバックループ制御により、出力ノード 5 0 の電圧レベルは、基準電圧 V r e f に等しい電圧レベルとなる。

#### 【 0 0 4 7 】

降圧回路 3 6 は、さらに、定電流源 4 0 と差動增幅回路 4 4 の動作電源ノード 4 1 の間に接続される耐圧緩和回路 ( 第 2 の耐圧緩和回路 ) 5 2 と、定電流源 4 2 と出力ノード 5 0 の間に設けられる耐圧緩和回路 ( 第 1 の耐圧緩和回路 ) 5 3 とを含む。耐圧緩和回路 5 2 は、定電流源 4 0 と差動增幅回路 4 6 の動作電源ノード 4 1 の間に接続されかつそのゲートに耐圧制御信号 V s c p r を受ける P チャネルM O S トランジスタ P Q 3 を含む。耐圧制御信号 V s c p r は動作モードまたは用途に応じて 0 V または 3 . 5 V に設定される。

#### 【 0 0 4 8 】

M O S トランジスタ P Q 3 のゲートに耐圧制御信号 V s c p r を供給することにより、チャージポンプ回路 3 2 からのポンプ高電圧 V c p により、定電流源 4 0 に高電圧が印加されるのを防止する。すなわち、降圧回路 3 6 は、適用用途に応じて供給されるポンプ高

10

20

30

40

50

電圧の電圧レベルが異なる。例えば、この降圧回路36が、MONOSメモリのメモリゲート線電圧を生成する場合、このメモリゲート線電圧 $V_{mg}$ は、最大11Vと成る。この最大電圧から降圧回路36により動作モードに応じた電圧レベルの電圧を生成する。このときに耐圧緩和MOSトランジスタPQ3がなければ、定電流源40に $11V - 0V = 11V$ の電圧が印加される可能性がある。このような高電圧の生成時には、耐圧緩和制御信号 $V_{scpr}$ を例えば3.5Vに設定すると、定電流源40とMOSトランジスタPQ3の間の接続ノードは、 $3.5V + MOSトランジスタPQ3のしきい値電圧の絶対値V_{thp}$ 以上にしかならない。従って、定電流源40に印加される電圧は、 $11V - (3.5V + V_{thp})$ に緩和される。

## 【0049】

10

耐圧緩和回路53は、定電流源42と出力ノード50の間に接続されかつそのゲートに耐圧制御信号 $V_{scpr}$ を受けるPチャネルMOSトランジスタPQ4を含む。MOSトランジスタPQ4は、また、定電流源42からの電流を出力ノード50へ供給する。

## 【0050】

ポンプ高電圧 $V_{cp}$ が高電圧のとき、耐圧制御信号 $V_{scpr}$ により、定電流源42と出力ノード50との間に電圧降下を生じさせ、定電流源42のトランジスタのソースドレイン間に高電圧が印加されるのを抑制し定電流源42のトランジスタの耐圧特性を保証する。また、この耐圧緩和回路53により、出力ノード50の電圧をポンプ高電圧 $V_{cp}$ よりも確実に低くして、差動增幅回路44のMOSトランジスタPQ2のゲート-ソース間に高電圧が印加されるのを抑制する。

20

## 【0051】

降圧回路36は、さらに、出力ノード50とドライブトランジスタ46の間に接続される耐圧緩和回路（第3の耐圧緩和回路）54と、差動增幅回路44の入出力応答の位相補償を行うミラー補償回路55と、アンプ活性化信号AMPENをインバータ59を介してゲートに受けて選択的に導通するNチャネルMOSトランジスタ60を含む。

## 【0052】

耐圧緩和回路54は、出力ノード50とドライブトランジスタ46の間に接続されかつそのゲートに耐圧制御信号 $V_{crd}$ を受けるNチャネルMOSトランジスタNQ3を含む。耐圧緩和制御信号 $V_{crd}$ は、ポンプ高電圧 $V_{cp}$ が例えば11Vの高電圧のときに例えば5.5Vの電圧レベルに設定される。この状態においては、MOSトランジスタNQ3は、ゲート電圧 $V_{crd}$ からそのしきい値電圧を減算した大きさの電圧を伝達する。これにより、ドライブトランジスタ46のソース-ドレイン間に高電圧が印加されるのを抑制することができる。

30

## 【0053】

インバータ59は、ハイ側電源電圧として、耐圧緩和制御電圧 $V_{crd}$ を受ける。アンプ活性化信号AMPENは、定電流源40および42を降圧回路36の非活性化時、非導通状態とするため、Hレベルがポンプ高電圧レベルである。インバータ59によりレベル変換を行なって、MOSトランジスタ60のゲート-ソース間に高電圧が印加されるのを回避する。

## 【0054】

40

降圧回路36の非活性状態の時、アンプ活性化信号AMPENは、Lレベルであり、MOSトランジスタ60は、オン状態となる。この状態においては、差動增幅回路44の内部ノード49が接地電圧VSSレベルに設定され、ドライブトランジスタ46がオフ状態となる。定電流源40および42は、非導通状態であり、電流供給は行わない。従って、出力ノード50からの内部電圧の生成動作は停止される。このとき、差動增幅回路44において内部ノード49が接地電圧レベルであり、差動增幅回路44内においてフローティング状態となるノードが存在するのは、回避される（電源ノード41も接地電圧レベルへ駆動される）。

## 【0055】

また、出力ノード50については、出力ノード50には負荷回路の容量が付随しており

50

、フローティング状態となつても、この負荷回路の容量により安定に電圧が保持される。

【0056】

アンプ活性化信号AMPENのHレベルのとき、MOSトランジスタ60がオフ状態となつて、前述のように基準電圧Vrefと出力ノード50の電圧との比較結果に応じてドライブトランジスタ46のコンダクタンスの調整が行われる。

【0057】

ミラー補償回路55は、出力ノード50と内部ノード49との間に直列に接続される容量素子Cおよび抵抗素子Rを含む。このミラー補償回路55は、差動增幅回路44の入出力において負帰還を掛けて、差動增幅回路44が発振するのを防止する。すなわち、差動增幅回路44の動作時、出力ノード50の電圧Vcprが変動すると、その電圧変動がミラー補償回路55のミラー容量Cを介して内部ノード49、すなわち、ドライブトランジスタ46のゲート電圧を変化させる。応じて、ドライブトランジスタ46は、出力ノード50の電圧変動を抑制する方向にそのコンダクタンスが調整され、出力ノード50の電圧を安定化する。抵抗素子Rは、ミラー補償回路55において、応答の感度を調整し、瞬間的なノイズ性の電圧変動に対する感度を小さくして、過剰に出力ノード50の電圧変動に対して応答して、出力ノード50にリップルが生じるのを抑制する。

【0058】

差動增幅回路44が高速動作し、入出力応答において位相反転が生じることがなく、出力ノード50の電圧変動にほぼ追随することができる場合には、このミラー補償回路55は、特に設ける必要がない。

【0059】

次に、耐圧緩和回路の配置位置について説明する。

(1) 定電流源40および42各自と出力電圧線38との間に配置することを考える。定電流源40および42は、各自、PMOSトランジスタを電流源トランジスタとして利用する。この場合、電流源トランジスタのゲート電圧は固定することが可能であるものの、ソース電圧が耐圧緩和回路の挿入により変動する(耐圧緩和MOSトランジスタのチャネル抵抗のばらつきによる)。また、耐圧緩和制御信号Vscprの電圧レベルが動作モードに応じて変動するため、動作モードに応じて電流源トランジスタのゲート-ソース間電圧が変化し、駆動電流量が変化する。このため、差動增幅回路44の駆動電流量を一定として安定に動作させるのが困難となる、また、出力ノード50の供給電流も変動し、出力ノード50からの内部電圧の安定化に要する時間が変動し、高速かつ安定な動作を保証することができなくなる。従って、定電流源40および42とポンプ出力電圧線38との間に耐圧緩和回路を配置するのは好ましくない。

【0060】

(2) 差動增幅回路44の内部ノードに耐圧緩和回路を配置した場合、差動增幅回路44の内部ノードにおいて電圧降下が生じる。この場合、差動增幅回路44の差動段MOSトランジスタPQ1およびPQ2を安定に動作させるためには、これらのMOSトランジスタPQ1およびPQ2のソース-ドレイン間電圧差を大きくすることができない。従って、出力ノード50の電圧が例えば1Vの低電圧のとき、大きな電流変化をこれらのMOSトランジスタPQ1およびPQ2において生じさせることができず、安定に差動増幅動作により内部電圧を生成することができなくなる。また、MOSトランジスタPQ1およびPQ2のゲート-ソース間電圧が低電圧生成時に大きくなり、耐圧を保証することができなくなる。従って、この差動增幅回路の内部ノードに耐圧緩和回路を配置するのは、好ましくない。

【0061】

(3) MOSトランジスタNQ1、NQ2およびドライブトランジスタ46との間に耐圧緩和回路を配置する。この場合、差動增幅回路44においてMOSトランジスタNQ1およびNQ2を飽和領域で動作させるために、差動增幅回路44の内部ノード(49)の電圧レベルを高くする必要がある。従って、上記(2)において考察した場合と同様、出力電圧Vcprとして低電圧を安定に生成することができなくなる。

10

20

30

40

50

## 【0062】

ドライブトランジスタ46においても、ゲート-ソース間電圧差が小さくなり、応答速度が低下する。特に、出力ノード50の電圧 $V_{cpr}$ が低電圧のとき、ドライブトランジスタ46は、オン状態のときのゲート電圧は、高電圧が出力ノードから出力される場合に比べて高くなる。従って、この場合、出力ノード50から電流を引抜くことができず、低電圧出力時の動作を保証することができない。

## 【0063】

従って、図5に示すように、耐圧緩和回路を定電流源40と差動增幅回路44の間、定電流源42と出力ノード50の間、および出力ノード50とドライブトランジスタ46の間に配置することにより、低電圧出力および降圧回路の安定性に対する支障を生じさせることなく、出力電圧の広い電圧範囲にわたって降圧回路のトランジスタの耐圧を保証することができる。

10

## 【0064】

以上のように、この発明の実施の形態1に従えば、降圧回路36においては、チャージポンプ回路32の出力電圧線38から動作電源電圧および電流を受け、基準電圧 $V_{ref}$ との比較に基づいて出力電圧 $V_{cpr}$ を生成している。したがって、抵抗分圧回路を利用して、必要な内部電圧を生成する構成に比べて、高抵抗素子が不要となり、回路占有面積が低減される。また、必要な電圧レベルの出力電圧 $V_{cpr}$ を、動作モードに応じて生成するだけである。従って、常時、抵抗分圧回路を介して電流を流す必要がなく、消費電流を低減することができる。

20

## 【0065】

また、耐圧緩和回路を比較回路の動作電源ノードおよび出力ノードにそれぞれ設けており、低電圧の出力を安定に行なうことができ、また、降圧回路のトランジスタの耐圧を保証することができる。

## 【0066】

## [実施の形態2]

図6は、この発明の実施の形態2に従う降圧回路の全体の構成を示す図である。この図6に示す降圧回路は以下の点で、図5に示す降圧回路とその構成が異なる。

## 【0067】

すなわち、耐圧緩和回路52において、PチャネルMOSトランジスタPQ3のゲートとソースとの間にPチャネルMOSトランジスタPQ5が接続される。このMOSトランジスタPQ5は、ゲートおよびソースが定電流源40に結合され、ドレインがMOSトランジスタPQ3のゲートに接続される。

30

## 【0068】

耐圧緩和回路53において、MOSトランジスタPQ4のゲートと定電流源42の間にPチャネルMOSトランジスタPQ6が接続される。このMOSトランジスタPQ6は、ゲートおよびソースが定電流源42に接続され、ドレインがMOSトランジスタPQ4のゲートに接続される。

## 【0069】

耐圧緩和回路54において、MOSトランジスタNQ3のゲートとドライブトランジスタ46との間にNチャネルMOSトランジスタNQ4が接続される。このMOSトランジスタNQ4は、バックゲート(基板領域)およびソースがMOSトランジスタNQ3のゲートに接続され、そのゲートおよびドレインが、ドライブトランジスタ46とMOSトランジスタNQ3との間の接続ノードに接続される。

40

## 【0070】

この降圧回路36において、さらに、出力ノード50と差動增幅回路44のトランジスタPQ2のゲートの間に耐圧緩和回路62が設けられ、また、ポンプ電圧出力線38と耐圧緩和回路53の間に、PチャネルMOSトランジスタで構成される短絡トランジスタ64が接続される。

## 【0071】

50

短絡トランジスタ 6 4 は、ゲートに補の短絡指示信号 S R T N を受けて、選択的に導通し、導通時、定電流源 4 2 を短絡する。耐圧緩和回路 6 2 は、並列に接続される N チャネル M O S トランジスタ N Q 5 および P チャネル M O S トランジスタ P Q 7 を含む。M O S トランジスタ N Q 5 はゲートに耐圧緩和制御信号 V c r d を受け、M O S トランジスタ P Q 7 は、ゲートに短絡指示信号 S R T を受ける。

【 0 0 7 2 】

この図 6 に示す降圧回路の他の構成は、図 5 に示す降圧回路の構成と同じであり、対応する部分には同一参照符号を付し、その詳細説明は省略する。

【 0 0 7 3 】

耐圧緩和回路 5 2 - 5 4 においてダイオード接続された M O S トランジスタ P Q 5 、 P Q 6 および N Q 4 が、設けられているのは以下の理由による。 10

【 0 0 7 4 】

定電流源 4 0 および 4 2 は、アンプ活性化信号 A M P E N に従って選択的に活性化される。これらの定電流源 4 0 および 4 2 は、通常、ゲートに電流制御電圧（定電圧）を受けて一定の電流を流す。定電流源トランジスタのゲート電圧とポンプ出力電圧線 3 6 の電圧が等しくなると（例えば降圧回路の非活性化時）、定電流源トランジスタがオフ状態となる。このとき、耐圧緩和回路 5 2 および 5 3 の M O S トランジスタ P Q 3 および P Q 4 のソースノードがフローティング状態となる可能性がある。この場合、フローティングノードの電圧がリーク電流により低下した場合、定電流源 4 0 および 4 2 において、定電流源トランジスタのソース - ドレイン間に高電圧が印加され、定電流源トランジスタの耐圧が保証することができなくなる。 20

【 0 0 7 5 】

M O S トランジスタ P Q 5 は、ダイオードモードで動作し、M O S トランジスタ P Q 3 のソース電圧を耐圧緩和制御電圧 V s c p r からそのしきい値電圧の絶対値 V t h p 低い電圧レベルにクランプする。高電圧生成時、耐圧緩和制御電圧 V s c p r を、3 . 5 V に設定することにより、M O S トランジスタ P Q 3 のソースノードの電圧の下限値を、V s c p r - V t h p に設定することができ、定電流源 4 0 のトランジスタの耐圧を保証することができる。これは耐圧緩和回路 5 3 においても、同様であり、M O S トランジスタ P Q 6 により、M O S トランジスタ P Q 4 のソース電圧の下限値を V s c p r - V t h p の電圧レベルにクランプする。 30

【 0 0 7 6 】

耐圧緩和回路 5 4 においては、ドライブトランジスタ 4 6 がオフ状態のとき、ドライブトランジスタ 4 6 のドレインノードがフローティング状態となる。このフローティングノードの電圧が、出力ノード 5 0 からのリーク電流により上昇し、ドライブトランジスタ 4 6 のドレイン - ソース間に高電圧が印加される可能性がある。M O S トランジスタ N Q 4 は、ダイオードモードで動作し、ドライブトランジスタ 4 6 のフローティング状態のドレインノードを電圧 V c r d + V t h n の電圧レベルにクランプする。ここで、V t h n は、M O S トランジスタ N Q 4 のしきい値電圧を示す。

【 0 0 7 7 】

短絡指示信号 S R T および S R T N は、出力ノード 5 0 の電圧 V c p r として、ポンプ高電圧 V c p を降圧することなく出力する場合に利用される。この場合、短絡指示信号 S R T が H レベル（ポンプ高電圧 V c p レベル）に設定され、補の短絡指示信号 S R T N が L レベルに設定される。また、出力電圧 V c p r の電圧レベルのフィードバック制御は、この場合、不要であり、アンプ活性化信号 A M P E N が非活性状態（L レベル）に設定される。 40

【 0 0 7 8 】

この状態においては、耐圧緩和回路 6 2 において、M O S トランジスタ P Q 7 がオフ状態となる。M O S トランジスタ N Q 5 は、ゲートに耐圧制御電圧 V c r d を受けており、出力ノード 5 0 から M O S トランジスタ P Q 2 のゲートに対して電圧 V c p r - v t h n を伝達する。これにより、M O S トランジスタ P Q 2 のゲート - ソース / ドレイン間に高 50

電圧が印加されるのを防止する。差動増幅回路 4 4 においては、非活性状態であり、定電流源 4 0 からの電流は供給されず、内部ノードは接地電圧レベルに維持され、また、MOSトランジスタ 6 0 により、内部ノードのフローティング状態は回避される。

【0079】

また、短絡トランジスタ 6 4 が導通し、定電流源 4 2 を短絡して、出力ノード 5 0 ポンプ出力電圧線 3 8 からの電圧を出力ノードに伝達する。このとき、耐圧制御電圧  $V_{cpr}$  が、接地電圧レベルに設定されれば、耐圧緩和回路 5 3 において、MOSトランジスタ  $P_{Q4}$  により、定電流源 4 2 のトランジスタのソース - ドレイン間電圧は 0 V であり、耐圧は保証される。

【0080】

耐圧緩和回路 5 4 においては、耐圧緩和制御電圧  $V_{crd}$  を、5.5 V に設定することにより、出力電圧  $V_{cpr}$  が 11 V であっても、MOSトランジスタ  $N_{Q3}$  がドライブトランジスタ 4 6 のドレイン電圧を電圧  $V_{crd} - V_{thn}$  の電圧レベルに設定する。従って、ドライブトランジスタ 4 6 が、オフ状態であっても、そのドレイン - ソース間電圧を充分に緩和することができる。

【0081】

ポンプ高電圧  $V_{cp}$  を降圧する場合には、短絡指示信号  $S_{RT}$  を L レベルに設定し、補の短絡指示信号  $S_{RTN}$  をポンプ高電圧レベルの H レベルに設定する。アンプ活性化信号  $AMPEN$  の活性化に従って、実施の形態 1 と同様に降圧動作が行われる。

【0082】

なお、図 5 に示す降圧回路においても、図 6 に示すクランプ用のトランジスタ  $P_{Q5}$ 、 $P_{Q6}$  および  $N_{Q4}$  が各耐圧緩和回路 5 2 - 5 4 に設けても良い。

【0083】

以上のように、この発明の実施の形態 2 に従えば、耐圧緩和回路においてフローティング防止のクランプトランジスタを設けている。従って、電流源のトランジスタおよび電圧引抜き用のドライブトランジスタの耐圧を確実に維持することができる。また、短絡トランジスタを用いて出力ノードとポンプ出力電圧線 3 8 とを短絡可能としている。従って、出力ノードの電圧の電圧範囲を拡張することができる。

【0084】

【実施の形態 3】

図 7 は、この発明の実施の形態 3 に従う降圧回路 3 6 の構成を示す図である。この図 7 に示す降圧回路 3 6 は、以下の点で、図 5 に示す降圧回路 3 6 とその構成が異なる。すなわち、図 7 に示す降圧回路においては、定電流源 4 2 に代えて、可変電流源 6 5 が用いられる。この可変電流源 6 5 の駆動電流を調整するためにセレクタ 6 6 が設けられる。

【0085】

この図 7 に示す降圧回路 3 6 の他の構成は図 5 に示す降圧回路 3 6 の構成と同じであり、対応する部分には同一参照符号を付して、その詳細説明は省略する。なお、図 7 においては、耐圧緩和回路 5 2、5 3 および 5 4 においてクランプトランジスタ  $P_{Q5}$ 、 $P_{Q6}$  および  $N_{Q4}$  を示しているものの、これらのクランプトランジスタ  $P_{Q5}$ 、 $P_{Q6}$  および  $N_{Q4}$  は、実施の形態 1 と同様に設けられなくても良い。

【0086】

セレクタ 6 6 が、一例として 4 ビット選択信号  $S_{EL} < 3 : 0 >$  に従って可変電流源 6 5 の供給電流量を調整する。この 4 ビット選択信号  $S_{EL} < 3 : 0 >$  は、動作モードに応じて、それらの論理値が設定される。たとえばシステム立上げ時、電源投入検出信号に従って、この可変電流源 6 5 の駆動電流量を大きくして、出力ノード 5 0 の電圧  $V_{cpr}$  を所定の電圧レベルに高速で設定する。

【0087】

また、各動作モードの開始時においても、これらの可変電流源 6 5 の駆動電流量を調整することにより、高速で出力電圧  $V_{cpr}$  の電圧レベルを上昇または低下させる。出力電圧  $V_{cpr}$  の電圧レベルが安定化すると、4 ビット選択信号  $S_{EL} < 3 : 0 >$  に従って可

10

20

30

40

50

変電流源 6 5 の駆動電流量を小さくすることにより、消費電流を低減する。

【 0 0 8 8 】

可変電流源 6 5 は、スタンバイ時および実際にデータの書込／消去／読出が行なわれる動作サイクルに応じて、その駆動電流量がセレクタ 6 4 により、調整されてもよい。

【 0 0 8 9 】

この選択信号 S E L < 3 : 0 > は、図 4 に示す制御回路 3 0 から各動作モードに応じて生成される。

【 0 0 9 0 】

図 8 は、図 7 に示す可変電流源 6 5 およびセレクタ 6 6 の構成の一例を示す図である。図 8 において、可変電流源 6 5 は、ポンプ出力電圧線 3 8 と内部出力ノード 6 9 との間に並列に結合される P チャネルM O S トランジスタ P T 0 - P T 3 を含む。内部出力ノード 6 9 が、図 7 に示す耐圧緩和回路 5 3 に結合される。

10

【 0 0 9 1 】

セレクタ 6 6 は、M O S トランジスタそれぞれに対応して設けられる N A N D ゲート N G 0 - N G 3 を含む。N A N D ゲート N G 0 - N G 3 は、それぞれ、選択信号 S E L < 0 > - S E L < 3 > とアンプ活性化信号 A M P E N とを受け、それぞれの出力信号を対応のM O S トランジスタ P T 0 - P T 3 のゲートへ与える。

【 0 0 9 2 】

N A N D ゲート N G 0 - N G 3 は、ハイ側電源電圧としてポンプ高電圧 V c p を受け、ロー側電源電圧として定電圧 V c を受ける。この定電圧により、M O S トランジスタ P T 0 1 - P T 3 各々の駆動電流が設定される。これらのM O S トランジスタ P T 0 - P T 3 は、サイズ(チャネル長とチャネル幅の比)が同一であっても良く、また、1、2、4、および8のように、そのサイズが異なっていても良い。図 4 に示す制御回路 3 0 により、動作モードに応じて選択信号 S E L < 3 : 0 > の各ビットの論理値を設定する。

20

【 0 0 9 3 】

アンプ活性化信号 A M P E N が H レベルの時には、N A N D ゲート N G 0 - N G 3 がインバータとして動作し、4 ビット選択信号 S E L < 3 : 0 > に従ってM O S トランジスタ P T 0 - P T 3 を選択的に導通状態に設定する。

【 0 0 9 4 】

アンプ活性化信号 A M P E N が L レベルの時には、N A N D ゲート N G 0 - N G 3 の出力信号はポンプ高電圧レベルの H レベルであり、M O S トランジスタ P T 0 - P T 3 がオフ状態となる。

30

【 0 0 9 5 】

以上のように、この発明の実施の形態 3 に従えば、出力ノードへ供給電流量を変更可能としている。従って、動作モードに応じて、高速で出力電圧を変化させて安定化させることができる。また、出力電圧の安定化後に可変電流源からの供給電流を低減することにより消費電流を低減することができる。また、実施の形態 1 と同様の効果を得ることができる。

【 0 0 9 6 】

[ 実施の形態 4 ]

40

図 9 は、この発明の実施の形態 4 に従う内部降圧回路 3 6 の構成を示す図である。この図 9 に示す内部降圧回路の構成は、以下の点で図 6 に示す内部降圧回路とその構成が異なる。すなわち、定電流源 4 2 に代えて可変電流源 6 5 およびセレクタ 6 6 が用いられる。この図 9 に示す降圧回路の他の構成は、図 6 に示す降圧回路の構成と同じであり、対応する部分には同一参照符号を付して、その詳細説明は省略する。

【 0 0 9 7 】

なお、この図 9 に示す構成においても、耐圧緩和回路 5 2 - 5 4 においてクランプ用のトランジスタ P Q 5、P Q 6 および N Q 4 は、省略されても良い。

【 0 0 9 8 】

この図 9 に示す降圧回路 3 6 の構成においては、出力ノード 5 0 から電圧としてポンプ

50

高電圧  $V_{c,p}$  を出力する場合、可変電流源 65 の供給電流を増大させることにより、高速で出力電圧  $V_{c,r}$  をポンプ高電圧レベルに駆動することができる。また、実施の形態 3 と同様、動作モードに応じてセレクタ 66 の出力信号を調整することにより、高速で安定に所定の電圧レベルの内部電圧を低消費電流で生成することができる。

#### 【0099】

なお、図 9 に示す可変電流源 65 およびセレクタ 66 の構成としては、図 8 に示す構成を利用することができます。

#### 【0100】

##### [実施の形態 5]

図 10 は、図 3 および 4 に示す制御回路 30 の構成の一例を、概略的に示す図である。

10

図 10 において、制御回路 30 は、電源電圧  $V_{CC}$  を動作電源電圧として受け、外部からのコマンド CMD に従って動作モードを検出するモード検出回路 70 と、モード検出回路 70 からのモード指示信号に従って耐圧緩和制御信号  $V_{scpr}$  および  $V_{crd}$  を生成する緩和信号発生回路 72 と、モード検出回路 70 からのモード検出信号に従って 4 ビット選択信号  $SEL < 3 : 0 >$  を生成する駆動電流調整回路 74 とを含む。

#### 【0101】

緩和信号発生回路 72 は、内部に、電源電圧  $V_{CC}$  と異なる電圧レベル (3.5V および 5.5V) を生成する回路を含み、動作モードまたはポンプ高電圧の電圧レベルに応じて、これらの緩和緩和制御信号  $V_{scpr}$  および  $V_{crd}$  の電圧レベルを調整する。ポンプ高電圧が、降圧回路のトランジスタの耐圧を超える例えば 11V の電圧レベルのとき、これらの耐圧緩和制御信号  $V_{scpr}$  および  $V_{crd}$  が、それぞれ、3.5V および 5.5V に設定される。ポンプ高電圧が、降圧回路のトランジスタの耐圧 (例えば 9V) を超えない電圧レベルのとき、耐圧緩和制御信号  $V_{scpr}$  が 0V に設定される。この場合、耐圧緩和制御信号  $V_{crd}$  の電圧レベルは、常時 5.5V の電圧レベルに維持されてもよい。これにより、内部で生成される電圧に対して同一構成の降圧回路を利用して内部電圧を生成することができる (ポンプ回路の生成する電圧レベルを内部で利用される用途に応じて設定する)。

20

#### 【0102】

駆動電流調整回路 74 は、図 7 に示す可変電流源 65 が用いられるときに設けられ、動作モードに応じて、4 ビット選択信号  $SEL < 3 : 0 >$  の各ビット値を設定する。電源投入時または動作モード変更時に、内部電圧 (出力ノード 50 の電圧  $V_{cpr}$ ) の電圧を高速で上昇させる場合には、選択信号  $SEL < 3 : 0 >$  により可変電流源 65 の供給電流量を増大させる。動作モード変更時に、出力電圧  $V_{crd}$  の電圧レベルを低下させる場合には、この選択信号  $SEL < 3 : 0 >$  に従って可変電流源 65 の供給電流量を低下させる。この駆動電流調整回路 74 は、内部電圧が安定化すると可変電流源 65 の供給電流量をデフォルト値に設定して、動作時に必要とされる電流を供給して、消費電流を低減する。

30

#### 【0103】

このデフォルト値に設定する場合、動作モード変更時に一定時間経過後に選択信号  $SEL < 3 : 0 >$  のビット値をデフォルト値に設定しても良い。また、これに代えて、基準電圧  $V_{ref}$  との比較に基づいて、出力電圧が所望の電圧レベル (基準電圧の電圧レベル) に到達したときに、選択信号  $SEL < 3 : 0 >$  がデフォルト値に設定されても良い。基準電圧と出力電圧との比較を行う回路の出力信号の論理レベルの変化を検出することにより、出力電圧が基準電圧が規定する電圧レベルに到達したかを検出することができる。例えば、比較回路の出力信号の立上りおよび立下りを検出する回路を利用することにより、出力電圧  $V_{cpr}$  が基準電圧が所定値に到達したかを検出することができる。この場合、比較回路として降圧回路内部の差動増幅回路 44 を利用してもよい。

40

#### 【0104】

この制御回路 30 は、さらに、モード検出回路 70 の出力信号に従ってアンプ活性化信号  $AMPEN$  および短絡指示信号  $SRT$ 、 $SRTN$  を生成する降圧制御回路 75 を含む。この降圧制御回路 75 は、可変電流源が設けられている場合、動作モード検出信号に従つ

50

て、出力電圧  $V_{cpr}$  の電圧レベルを高速で上昇させる場合、アンプ活性化信号  $AMPEN$  を、出力電圧  $V_{cpr}$  が安定化するまで非活性状態に維持する。動作モード変更時において、出力電圧  $V_{cpr}$  を低下させる場合、アンプ活性化信号  $AMPEN$  をモード検出に従って出力電圧レベルに拘わらず活性化する。

#### 【0105】

実施の形態1および2のように可変電流源が設けられていない場合、降圧制御回路75は、モード検出に従ってアンプ活性化信号  $AMPEN$  を活性化する。モード変更時、基準電圧と出力電圧との比較結果に従って、出力ノードの電圧レベルを調整する。

#### 【0106】

降圧制御回路75は、さらに、実施の形態2および4のように短絡トランジスタが設けられている場合、モード検出信号に従って選択的に短絡指示信号  $SRT$  および  $SRTN$  を活性化する。すなわち、降圧制御回路75は、降圧回路の出力電圧  $V_{cpr}$  が、ポンプ高電圧  $V_{cp}$  の電圧レベルに等しいか否かに従って、その出力制御信号の電圧レベルを設定する。例えば、出力電圧  $V_{cpr}$  としてたとえば11Vのポンプ高電圧  $V_{cp}$  が利用されるとき（書込モード時）、アンプ活性化信号  $ANPEN$  はLレベル、短絡指示信号  $SRTEN$  がLレベル、短絡指示信号  $SRT$  をHレベルに設定する。これにより、差動増幅回路44の比較動作を停止させ、短絡トランジスタ（64）を導通状態として、出力ノード50に、ポンプ高電圧  $V_{cp}$  を伝達することができる。

#### 【0107】

この図10に示す制御回路30を利用することにより、ポンプ高電圧の電圧レベルに拘わらず降圧回路のトランジスタの耐圧緩和を行なうことができ、回路動作の安定性を保証することができる。また、可変電流源が設けられている場合、可変電流源の電流量を調整することにより、高速で出力電圧を所定の電圧レベルに駆動することができ、内部動作開始タイミングを早くすることができる。また、出力電圧が、動作モードに応じて所定の電圧レベルに上昇した後に可変電流源の供給電流を低減することにより、消費電流を低減することができる。

#### 【0108】

図11は、図4に示す基準電圧発生回路34の構成の一例を示す図である。図11において、基準電圧発生回路34は、電源電圧  $V_{CC}$  を供給する電源ノードに並列に結合されるPチャネルMOSトランジスタ  $PTR0 - PTRk$  と、これらのMOSトランジスタ  $PTR0 - PTRk$  からの供給電流を受けるNチャネルMOSトランジスタ  $NTR1$  と、MOSトランジスタ  $NTR1$  とカレントミラー回路を構成するNチャネルMOSトランジスタ  $NTR2$  を含む。

#### 【0109】

MOSトランジスタ  $PTR0 - PTRk$  は、それぞれのゲートに、活性制御信号  $ZEN0 - ZENk$  を受ける。活性制御信号  $ZEN0 - ZENk$  は、動作モードに応じて図4に示す制御回路（30）の制御の元にそれぞれの電圧レベル（論理レベル）が設定される。

#### 【0110】

MOSトランジスタ  $NTR1$  は、そのゲートおよびドレインが相互接続されて、MOSトランジスタ  $PTR0 - PTRk$  からの供給電流を電圧に変換する。MOSトランジスタ  $NTR2$  は、このMOSトランジスタ  $NTR1$  を流れる電流のミラー電流を流す。ミラーレートが1であれば、MOSトランジスタ  $NTR1$  および  $NTR2$  に同じ大きさの電流が流れれる。

#### 【0111】

基準電圧発生回路34は、さらに、電源電圧  $V_{CC}$  よりも高い高電圧  $V_p$  を生成するポンプ回路76と、ポンプ回路76の出力ノードとMOSトランジスタ  $NTR2$  の間に接続されるPチャネルMOSトランジスタ  $PTRm$  と、ポンプ回路76の出力ノードと基準電圧出力ノード78の間に接続されるPチャネルMOSトランジスタ  $PTRn$  と、基準電圧出力ノード78と接地ノードの間に接続される抵抗素子  $R_Z$  を含む。

#### 【0112】

10

20

30

40

50

MOSトランジスタPTRmはゲートおよびドレインが相互接続される。したがって、MOSトランジスタPTRmおよびPTRnによりカレントミラー段が構成され、このMOSトランジスタPTRmを介して流れる電流のミラー電流が、MOSトランジスタPTRnを介して流れる。ミラー比が1であれば、MOSトランジスタPTRmおよびPTRnに同じ大きさの電流Iが流れる。

【0113】

図11に示す基準電圧発生回路34の構成において、活性制御信号ZENO-ZENkを動作モードに応じてそれぞれの電圧レベルを設定する。これにより、MOSトランジスタNTR1へ供給される電流を設定することができ、応じて、MOSトランジスタNTR2およびPTRmを介して流れるミラー電流量を調整することができる。したがって、基準電圧出力ノード78からの基準電圧Vrefの電圧レベルは、抵抗素子RZの抵抗値RZとMOSトランジスタPTRnを介して供給される電流Iの積I·RZにより設定される。したがって、抵抗素子RZを1つ用いても、この電流Iの電流値を調整することにより、基準電圧Vrefの電圧レベルを、例えば、1Vから6.3Vの範囲で調整することが可能となる。

【0114】

MOSトランジスタPTR0-PTRkは、それぞれのサイズ(チャネル幅とチャネル長の比)が同じであってもよく、また、1倍、2倍、4倍、…のようにそのサイズ比が異なり、電流駆動量が異なる構成であってもよい。MOSトランジスタPTR0-PTRkの供給する電流のステップ値に応じて、基準電圧Vrefの電圧レベルを変更することができる。

【0115】

基準電圧発生回路34においては、基準電圧Vrefは、単に図5以降に示す降圧回路内の差動增幅回路44のMOSトランジスタPQ1のゲート電圧を設定することが、要求されるだけである。MOSトランジスタPQ1のゲート容量は小さく、また、MOSトランジスタPQ1のゲートの入力インピーダンスは、ハイインピーダンスである。従って、基準電圧発生回路34の駆動電流量は十分小さくすることができ、消費電流は十分に抑制される。また、抵抗素子RZを1つ用いるだけあり、そのレイアウト面積は十分小さくすることができる。

【0116】

ポンプ回路76は、一例として、基準電圧発生回路34に対して専用に設けられる。基準電圧のVrefの駆動電流量小さいため、ポンプ回路76のポンプ電流駆動力は、十分小さくすることができる。また、基準電圧Vrefの最大電圧(例えば6.3V)を生成することができればよく、ポンプ回路76のレイアウト面積も十分小さくすることができる(素子サイズおよび容量素子のサイズは小さくすることができる)。このポンプ回路76として、図4に示すチャージポンプ回路32が用いられても良い。

【0117】

基準電圧発生回路34において、MOSトランジスタPTRnを介して流れる電流Iが小さくても、抵抗素子RZの抵抗値が十分大きければ、電流Iの小さな変化により、基準電圧Vrefの電圧変化を大きくすることができる。また、抵抗素子RZの抵抗値を充分大きくすることにより、このポンプ回路76の消費電流は、充分に小さくすることができる。

【0118】

また、出力電圧Vcprがポンプ高電圧Vcp電圧レベルのときには、基準電圧発生回路34において、活性制御信号ZENO-ZENkを、すべてHレベルに設定するとともにポンプ回路76のポンプ動作を停止させる。これにより、基準電圧発生動作を停止させることができ、消費電流を低減することができる。

【0119】

また、スタンバイ状態時などにおいて、活性制御信号ZENO-ZENkをすべてHレベルに設定するとともにポンプ回路76のポンプ動作を停止させてもよい。

10

20

30

40

50

## 【0120】

図12は、図3に示す内部電圧発生回路28の構成を概略的に示す図である。図8において、内部電圧発生回路80(28)は、内部で利用される電圧に対応して、コントロールゲート電圧発生回路82と、メモリセルゲート電圧発生回路84と、ピット線電圧発生回路86と、ソース線電圧発生回路88とを含む。

## 【0121】

コントロールゲート電圧発生回路82は、コントロールゲート線に伝達されるコントロールゲート電圧 $V_{cg}$ を生成する。コントロールゲート線は、メモリセルの選択トランジスタのコントロールゲートが接続される。書込および消去モード時には、選択時に例えば1Vに設定され、読出モード時には、電源電圧レベルまたはそれよりも高い3.5Vに設定される。

10

## 【0122】

メモリセルゲート電圧発生回路84は、メモリゲート線 $V_{mg}$ に伝達されるメモリゲート電圧 $V_{mg}$ を伝達する。メモリゲート線には、メモリセルトランジスタのゲートが接続される。書込時において選択電圧として11V、非選択電圧として3.5Vが利用される。読出時には、選択電圧として消去状態および書込状態のしきい値電圧の中間の電圧レベルの電圧が生成される。非選択電圧は、消去状態のしきい値電圧以下の電圧である。消去状態のしきい値電圧が負の値、すなわちメモリセルが過消去状態に設定される構成の場合には、読出時にはメモリゲート電圧 $V_{mg}$ は、選択/非選択に拘わらず接地電圧レベルに維持されても良い。消去時のメモリゲート電圧 $V_{mg}$ の選択電圧レベルは負電圧であり、これは別に設けられる負の高電圧を生成するチャージポンプ回路を利用して生成される。

20

## 【0123】

ピット線電圧発生回路86は、ピット線に伝達されるピット線電圧 $V_{b1}$ を生成する。このピット線電圧 $V_{mg}$ は、書込時および消去時において、非選択列のピット線電圧は、1.5Vでありおよび選択列のピット線電圧は、0.8Vである。また、読出時においてはピット線には読出電流を伝達するためのピット線読出電圧が伝達される。このピット線読出電圧は、読出時のコントロールゲート電圧よりも低い電圧レベルである。

## 【0124】

ソース線電圧発生回路88は、ソース線に伝達されるソース線電圧 $V_s$ を伝達する。ソース線電圧 $V_s$ は、書込および消去時において、選択ブロックにおいては5V、非選択ブロックにおいては、1.5Vまたは接地電圧レベルである。書込および消去単位のブロックの構成に応じて、非選択時のソース線電圧 $V_s$ の電圧レベルが設定される。読出時には、ソース線電圧 $V_s$ は接地電圧レベルに維持される。なお、選択電圧および非選択電圧を対応の信号線に伝達する場合、そのドライバ(たとえばピット線ドライバ)のハイ側電源ノードおよびロー側電源ノードにそれぞれ選択電圧および非選択電圧またはその逆を伝達する。

30

## 【0125】

図12に示すように、各内部電圧ごとに、選択電圧レベルおよび非選択電圧レベルを設定することにより、各回路ごとに、動作モードに応じて必要とされる電圧を生成することができる。

40

## 【0126】

また、これらの電圧発生回路82、84、86および88は、その内部構成は、先の実施の形態1から4に示す構成と同じであり、それぞれ同一構成を有する。実施の形態1から4に示す降圧回路および図11に一例として示す基準電圧発生回路を1つのモジュールを、動作特性が保証されたライブラリとして登録する。各電圧発生回路82、84、86および88をこの登録モジュールを利用して構成する。これにより、動作特性が保証された小占有面積の内部電圧生成回路を容易に生成することができる。また、不揮発性メモリの内部構成の拡張時に、メモリブロック数が増大する場合にも、これらの内部電圧発生回路(内部降圧回路)を各メモリブロックに対して配置することにより、メモリ拡張に対応して内部電圧発生回路を拡張する場合にも、容易に対応することができる。

50

## 【0127】

なお、上述の説明においては、ポンプ高電圧を生成するチャージポンプ回路もそれぞれ内部電圧に応じて設けられるように示す。しかしながら、ポンプ高電圧を生成するチャージポンプ回路が複数の内部電圧に対して共通に設けられ、各内部電圧に対応して降圧回路が配置される構成が用いられても良い。共通のチャージポンプ回路からのポンプ高電圧にしたがって、それぞれ基準電圧に従って降圧回路により、各内部電圧を生成する。

## 【0128】

また、上述の実施の形態においては、電源電圧VCCよりも高いポンプ高電圧Vcpを生成している。しかしながら、この内部電圧発生回路は、負の高電圧を生成する回路であってもよい。実施の形態1から4に示す降圧回路において、トランジスタの極性を反対とし、また電源ノードの電圧極性を反対にすることにより、負の高電圧を生成する内部電圧発生回路の降圧回路の構成は容易に実現される。10

## 【0129】

さらに、不揮発性メモリとしては、MONOS型メモリを示している。しかしながら、この発明に従う内部電圧発生回路の構成は、フローティングゲートの蓄積電荷量に応じてデータを記憶する不揮発性メモリに対しても適用することができる。

## 【産業上の利用可能性】

## 【0130】

この発明は、一般に、内部で複数種類の内部電圧を利用する半導体回路装置に対して適用することにより、低消費電流かつ低占有面積の内部電圧発生回路を実現することができる。特に、書込／消去等において高電圧を必要とする不揮発性メモリに、この発明に従う内部電圧発生回路を適用することにより、耐圧を保証しつつ低消費電流かつ低占有面積の内部電圧発生回路を実現することができる。また、この発明に従う不揮発性メモリを搭載するシステム・オン・チップ(SOC)などの用途に適用することにより、システムの消費電流およびレイアウト面積を低減することができる。20

## 【0131】

なお、これまでの説明においては、内部電圧発生回路28(80)は、不揮発性メモリ内に設けられるように示している。しかしながら、SOCなどのように、1つの半導体チップ上に、複数のメモリおよびロジックが集積化される場合、この内部電圧発生回路(28, 80)は、不揮発性メモリ4のブロック(マクロ)の外部に配置されてもよい。この場合、内部電圧発生回路を1つのマクロとしてチップ上に配置する。30

## 【図面の簡単な説明】

## 【0132】

【図1】この発明が適用される半導体集積回路の全体の構成を概略的に示す図である。

【図2】図1に示す不揮発性メモリに含まれるメモリセルの電気的等価回路の一例を概略的に示す図である。

【図3】図1に示す不揮発性メモリの全体の構成を概略的に示す図である。

【図4】図3に示す内部電圧発生回路の構成を概略的に示す図である。

【図5】この発明の実施の形態1に従う降圧回路の構成を示す図である。

【図6】この発明の実施の形態2に従う降圧回路の構成を示す図である。40

【図7】この発明の実施の形態3に従う降圧回路の構成を概略的に示す図である。

【図8】図7に示す可変電流源およびセレクタの構成の一例を示す図である。

【図9】この発明の実施の形態4に従う降圧回路の構成を示す図である。

【図10】図3に示す制御回路の構成を概略的に示す図である。

【図11】図4に示す基準電圧発生回路の構成の一例を示す図である。

【図12】図3に示す内部電圧発生回路の全体の構成を概略的に示す図である。

## 【符号の説明】

## 【0133】

1 半導体集積回路装置、4 不揮発性メモリ、MC メモリセル、ST 選択トランジスタ、MT メモリセルトランジスタ、20 メモリセルアレイ、22 行選択駆動回50

路、 2 4 ソース線選択駆動回路、 2 6 ビット線選択駆動回路、 2 8 , 2 8 A 内部電圧発生回路、 3 0 制御回路、 3 2 チャージポンプ回路、 3 4 基準電圧発生回路、 3 6 降圧回路、 4 0 , 4 2 定電流源、 4 4 差動増幅回路、 4 6 ドライブトランジスタ、 5 2 , 5 3 , 5 4 耐圧緩和回路、 P Q 1 - P Q 6 P チャネルMOSトランジスタ、 N Q 1 - N Q 4 N チャネルMOSトランジスタ、 5 9 インバータ、 6 0 N チャネルMOSトランジスタ、 6 4 短絡用MOSトランジスタ、 6 5 可変電流源、 6 6 セレクタ、 7 0 モード検出回路、 7 2 緩和信号発生回路、 7 4 駆動電流調整回路、 7 5 降圧制御回路、 7 6 ポンプ回路、 8 0 内部電圧発生回路、 8 2 コントロールゲート電圧発生回路、 8 4 メモリセルゲート電圧発生回路、 8 6 ビット線電圧発生回路、 8 8 ソース線電圧発生回路。

10

( 1 )

【 四 2 】

〔 义 3 〕

【 4 】

〔 四 5 〕

【図6】

:PQ5, PQ6, NQ4は

設けられなくてもよい

【図7】

:PQ5, PQ6, NQ4は

設けられなくてもよい

【図8】

【図9】

:PQ5, PQ6, NQ4は

設けられなくてもよい

【図10】

【図11】

【図12】

---

フロントページの続き

(74)代理人 100124523

弁理士 佐々木 真人

(74)代理人 100098316

弁理士 野田 久登

(72)発明者 小川 大也

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72)発明者 西山 崇之

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72)発明者 丸山 由紀子

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

審査官 櫻田 正紀

(56)参考文献 特開平02-194412 (JP, A)

特開2001-052489 (JP, A)

特開2000-090675 (JP, A)

特開平07-240472 (JP, A)

特表2003-528489 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 05 F 1/445, 1/56, 1/613, 1/618

G 11 C 16/06