(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6509323号

(P6509323)

(45) 発行日 令和1年5月8日(2019.5.8)

(24) 登録日 平成31年4月12日(2019.4.12)

(51) Int.Cl.

F 1

H01L 21/82 (2006.01)

H01L 21/82

21/82

W

H01L 21/822 (2006.01)

H01L 27/04

27/04

D

H01L 27/04 (2006.01)

H01L 27/04

27/04

H

請求項の数 10 (全 18 頁)

(21) 出願番号 特願2017-503100 (P2017-503100)

(86) (22) 出願日 平成27年7月21日 (2015.7.21)

(65) 公表番号 特表2017-521871 (P2017-521871A)

(43) 公表日 平成29年8月3日 (2017.8.3)

(86) 國際出願番号 PCT/US2015/041371

(87) 國際公開番号 WO2016/014559

(87) 國際公開日 平成28年1月28日 (2016.1.28)

審査請求日 平成30年7月2日 (2018.7.2)

(31) 優先権主張番号 14/340,381

(32) 優先日 平成26年7月24日 (2014.7.24)

(33) 優先権主張国 米国(US)

(73) 特許権者 507364838

クアルコム、インコーポレイテッド

アメリカ合衆国 カリフォルニア 921

21 サンディエゴ モアハウス ドラ

イブ 5775

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100163522

弁理士 黒田 晋平

(72) 発明者 チュン一チェン・リュウ

アメリカ合衆国・カリフォルニア・921

21-1714・サン・ディエゴ・モアハ

ウス・ドライブ・5775

最終頁に続く

(54) 【発明の名称】金属ラインおよびビアのマトリクスの挿入によるエレクトロマイグレーション、突入電流効果、IR電圧降下、およびジッタの軽減

## (57) 【特許請求の範囲】

## 【請求項1】

集積回路を製造する方法であって、

前記集積回路の経路選択を実行して複数の金属層にわたって複数の導電性経路を生成するステップと、

ある電流および電流密度を有する、前記複数の導電性経路のうちの第1の導電性経路を特定するステップであって、前記第1の導電性経路が、前記集積回路の第1のポイントから前記集積回路の第2のポイントに延び、第1の金属層内に少なくとも第1の金属ラインを含む、特定するステップと、経路選択および特定の前記ステップを実行した後、前記第1のポイントから前記第2のポイントに延びる補助導電性経路を形成するステップであって、第1のビア、第2の金属ラインおよび第2のビアを形成するステップを含み、前記第1のビアが前記第2の金属ラインに電気的に結合され、前記第2の金属ラインが次に前記第2のビアに電気的に結合され、前記第2の金属ラインが前記第1の金属層とは異なる第2の金属層内に配置され、前記第1および前記第2のビアが前記第1の金属層と前記第2の金属層との間に配置される、ステップとを含み、前記補助導電性経路が、前記第1の導電性経路を通って流れる前記電流の一部を転流することによって前記第1の導電性経路の前記電流および前記電流密度を低減するように、前記第1および前記第2のビアが前記第1の金属ラインを前記第2の金属ラインに電気的に結合する、方法。

10

20

**【請求項 2】**

前記補助導電性経路の経路長が、前記第1の導電性経路の経路長とは異なる、請求項1に記載の方法。

**【請求項 3】**

前記補助導電性経路の前記経路長が、前記第1の導電性経路の前記経路長より長い、請求項2に記載の方法。

**【請求項 4】**

経路選択および特定の前記ステップを実行した後、第3の金属ライン、第4の金属ラインおよび第5の金属ラインを形成するステップを含む第2の補助導電性経路を形成するステップであって、前記第3の金属ラインが前記第4の金属ラインに電気的に結合され、前記第4の金属ラインが次に前記第5の金属ラインに電気的に結合され、前記第3、前記第4および前記第5の金属ラインがすべて、前記第2の金属層内に配置される、ステップをさらに含み、

前記第2の補助導電性経路が、前記第1の導電性経路を通って流れる前記電流の追加の部分を転流することによって前記第1の導電性経路の前記電流および前記電流密度をさらに低減するように、前記第3および前記第5の金属ラインが、前記第4の金属ラインを前記第2の金属ラインに電気的に結合する、請求項1に記載の方法。

**【請求項 5】**

前記第1の導電性経路、前記補助導電性経路、および前記第2の補助導電性経路の各々に対する経路長が、互いに異なる、請求項4に記載の方法。

**【請求項 6】**

経路選択および特定の前記ステップを実行した後、第3のビア、第3の金属ラインおよび第4のビアを形成するステップを含む第2の補助導電性経路を形成するステップであって、前記第3のビアが前記第3の金属ラインに電気的に結合され、前記第3の金属ラインが次に前記第4のビアに電気的に結合され、前記第3の金属ラインが前記第1および前記第2の金属層とは異なる第3の金属層内に配置され、前記第3および前記第4のビアが前記第2の金属層と前記第3の金属層との間に配置される、ステップをさらに含み、

前記第2の補助導電性経路が、前記第1の導電性経路を通って流れる前記電流の追加の部分を転流することによって前記第1の導電性経路の前記電流および前記電流密度をさらに低減するように、前記第3および前記第4のビアが前記第3の金属ラインを前記第2の金属ラインに電気的に結合する、請求項1に記載の方法。

**【請求項 7】**

前記第1の導電性経路、前記補助導電性経路、および前記第2の補助導電性経路の各々に対する経路長が、互いに異なる、請求項6に記載の方法。

**【請求項 8】**

前記補助導電性経路を形成するステップが、前記第2の金属層内の第3および第4の金属ラインと、前記第3の金属ラインを通して前記第1のビアに電気的に結合された前記第2の金属ラインの第1の端部と、前記第4の金属ラインを通して前記第2のビアに電気的に結合された前記第2の金属ラインの第2の端部とをさらに含む、請求項1に記載の方法。

**【請求項 9】**

前記第2の金属ラインの端部が、前記第2の金属ラインがビアに結合された接合点を越えて延びる金属延長片を含み、前記延長片が、原子を収集するように、および/またはエレクトロマイグレーションによるボイドを形成するように適合される、請求項1に記載の方法。

**【請求項 10】**

前記補助導電性経路が、前記集積回路の設置および経路選択が実行された後、前記第1および前記第2のビアと前記第2の金属ラインとを前記集積回路のレイアウト設計に挿入することによって形成される、請求項1に記載の方法。

**【発明の詳細な説明】****【技術分野】**

10

20

30

40

50

**【0001】**

関連出願の相互参照

本出願は、内容全体が参照により本明細書に組み込まれる、2014年7月24日に米国特許商標庁に出願した、米国非仮特許出願第14/340,381号の優先権および利益を主張するものである。

**【0002】**

様々な特徴は、一般に、集積回路(IC)に関し、より詳細には、エレクトロマイグレーション、IR電圧降下を含む突入電流効果、およびジッタを低減および/または軽減するための金属ラインおよびビアのマトリクスの挿入を特徴とするICおよびそのICを製造する方法に関する。

10

**【背景技術】****【0003】**

エレクトロマイグレーションは、伝導する電子と拡散する金属原子との間の運動量移動に起因する、導体中のイオンの運動によって生じる素材についての移動である。IC内のワイヤラインまたは相互接続などの導体は、導体を通る電流密度が比較的高いときに特にエレクトロマイグレーションの影響を受けやすい。エレクトロマイグレーションは、IC内の導電性経路に沿ってボイド(すなわち、開回路)および/またはショートをもたらすことがあるので、ICの信頼性を低下させ、そのことが、最終的にICを機能不全にならしめることがある。ICの大きさは、サイズを継続的に縮小しているので、エレクトロマイグレーションの影響および重大性が増している。

20

**【0004】**

突入電流は、オンに切り替えられるとき、またはさもなければ、何らかの方法で起動されたときに、電気デバイスまたは電気回路によって引き込まれる最大の瞬時入力電流である。電力を動的に節約するために、クロックゲーティングが、現代のIC上で広く使用されている。しかしながら、その結果、クロックゲーティングがオフに切り替えられるときに大電流が回路に流入すると、突入電流問題が生じ、そのことで、著しいIR電圧降下が引き起こされることがある。もたらされたIR電圧降下は、オフであるべきトランジスタをオンに切り替えるなど、トランジスタにおける動作状態の変化を引き起こすことがある。その上、突入電流問題は、ICの電源スイッチ付近に特有のものであり、そのことでしばしば、突入電流問題はロケーションに固有の問題になる。しかしながら、そのようなロケーションにおけるチップ面積は、IC設計によって極めて限定することができ、したがって、突入電流問題に対して提案される解決策によって占有されるチップ面積の大きさは、可能な限り小さくなるはずである。

30

**【0005】**

ジッタは、周期信号の固定された周期性からの周波数偏移である。ジッタの原因には、電源雑音、データ経路雑音、回路上の位相ひずみ(たとえば、位相ロックループによって生じる)、などが含まれる。ジッタは、多くの異なる用途に関連するICにとって重大な問題となり得る。

**【0006】**

極めて一般的には、従来技術のICは、エレクトロマイグレーション、突入電流によって生じるIR電圧降下、およびジッタの上記の望ましくない影響を軽減するために、減結合キヤパシタ(たとえば、「de-cap」)を利用する。詳細には、de-capは、上記の問題のうちの1つまたは複数が予期される回路内の戦略的ポイントに挿入される。しかしながら、de-capは、明確な欠点を有する。第1に、de-capは、大きいチップ面積を消費し、そのことで、ICのいくつかのロケーション(たとえば、電源スイッチ付近)において、de-capの使用は極めて非実用的なまたは困難なものになる。第2に、いくつかのde-capは1つまたは複数のトランジスタを含むがあるので、それらのde-capは、かなりの電力を消費する。第3に、de-capは、回路の予期される動作周波数に基づいて選択される周波数由来のインピーダンスを有する。厄介なことに、回路の動作周波数に対する変化(たとえば、ICが低電力状態に入るとき)は、de-capの性能に悪影響を及ぼすことがあり、回路は、性能を再最適化

40

50

するために再調整されなければならないことがある。

【発明の概要】

【発明が解決しようとする課題】

【0007】

より少ない電力を消費し、より小さいチップ面積を消費し、ICの動作周波数の変化に対してロバストである、エレクトロマイグレーション、突入電流ベースのIR電圧降下、およびジッタに関連する問題を軽減する、方法およびデバイスが必要とされている。

【課題を解決するための手段】

【0008】

1つの特徴は、集積回路を製造する方法を提供する。方法は、集積回路の経路選択を実行して複数の金属層にわたって複数の導電性経路を生成するステップと、電流および電流密度を有する複数の導電性経路のうちの第1の導電性経路を特定するステップであって、第1の導電性経路が第1の金属層内に少なくとも第1の金属ラインを含む、特定するステップと、経路選択および特定のステップを実行した後、第1のビア、第2の金属ラインおよび第2のビアを形成するステップを含む補助導電性経路を形成するステップとを含む。第1のビアは第2の金属ラインに電気的に結合し、次に第2の金属ラインは第2のビアに電気的に結合される。第2の金属ラインは、第1の金属層とは異なる第2の金属層内に配置され、第1および第2のビアは、第1の金属層と第2の金属層との間に配置される。第1および第2のビアは、第1の金属ラインを第2の金属ラインに電気的に結合し、それによって、補助導電性経路は、第1の導電性経路を通じて流れる電流の一部を転流することによって第1の導電性経路の電流および電流密度を低減する。一態様によれば、補助導電性経路の経路長は、第1の導電性経路の経路長とは異なる。別の態様によれば、補助導電性経路の経路長は、第1の導電性経路の経路長より長い。

10

【0009】

一態様によれば、方法は、経路選択および特定のステップを実行した後、第3の金属ライン、第4の金属ラインおよび第5の金属ラインを含む第2の補助導電性経路を形成するステップをさらに含み、第3の金属ラインは第4の金属ラインに電気的に結合され、第4の金属ラインは次に第5の金属ラインに電気的に結合され、第3、第4および第5の金属ラインはすべて、第2の金属層内に配置され、第3および第5の金属ラインは、第4の金属ラインを第2の金属ラインに電気的に結合し、それによって、第2の補助導電性経路は、第1の導電性経路を通じて流れる電流の追加の部分を転流することによって第1の導電性経路の電流および電流密度をさらに低減する。別の態様によれば、第1の導電性経路、補助導電性経路および第2の補助導電性経路の各々に対する経路長は、互いに異なる。

20

【0010】

一態様によれば、方法は、経路選択および特定のステップを実行した後、第3のビア、第3の金属ラインおよび第4のビアを形成するステップを含む第2の補助導電性経路を形成するステップをさらに含み、第3のビアは第3の金属ラインに電気的に結合され、第3の金属ラインは次に第4のビアに電気的に結合され、第3の金属ラインは第1および第2の金属層とは異なる第3の金属層内に配置され、第3および第4のビアは第2の金属層と第3の金属層との間に配置され、第3および第4のビアは第3の金属ラインを第2の金属ラインに電気的に結合し、それによって、第2の補助導電性経路は、第1の導電性経路を通じて流れる電流の追加の部分を転流することによって第1の導電性経路の電流および電流密度をさらに低減する。別の態様によれば、補助導電性経路を形成するステップは、第2の金属層内の第3および第4の金属ラインと、第3の金属ラインを通して第1のビアに電気的に結合された第2の金属ラインの第1の端部と、第4の金属ラインを通して第2のビアに電気的に結合された第2の金属ラインの第2の端部とをさらに含む。

30

【0011】

一態様によれば、第2の金属ラインの端部は、第2の金属ラインがビアに結合された接合点を越えて延びる金属延長片を含み、延長片は、原子を収集するように、および/またはエレクトロマイグレーションによるボイドを形成するように適合される。別の態様によれ

40

50

ば、補助導電性経路は、集積回路の設置および経路選択が実行された後、第1および第2のビアと第2の金属ラインとを集積回路のレイアウト設計に挿入することによって形成される。

#### 【0012】

別の特徴は、第1の金属層内に少なくとも第1の金属ラインを含む第1の導電性経路と、第1のビア、第2の金属ラインおよび第2のビアを含む少なくとも1つの補助導電性経路とを備える集積回路を提供する。第1のビアは第2の金属ラインに電気的に結合され、第2の金属ラインは次に第2のビアに電気的に結合され、第2の金属ラインは第1の金属層とは異なる第2の金属層内に配置される。第1および第2のビアは、第1の金属層と第2の金属層との間に配置され、第1および第2のビアは、第1の金属ラインを第2の金属ラインに電気的に結合し、それによって、補助導電性経路は、第1の導電性経路を通って流れる電流の一部を転流することによって第1の導電性経路の電流および電流密度を低減する。10

#### 【0013】

一態様によれば、集積回路は、第3の金属ライン、第4の金属ラインおよび第5の金属ラインを含む第2の補助導電性経路をさらに備え、第3の金属ラインは第4の金属ラインに電気的に結合され、第4の金属ラインは次に第5の金属ラインに電気的に結合される。第3、第4および第5の金属ラインはすべて、第2の金属層内に配置され、第3および第5の金属ラインは、第4の金属ラインを第2の金属ラインに電気的に結合し、それによって、第2の補助導電性経路は、第1の導電性経路を通って流れる電流の追加の部分を転流することによって第1の導電性経路の電流および電流密度をさらに低減する。20

#### 【0014】

一態様によれば、集積回路は、第3のビア、第3の金属ラインおよび第4のビアを含む第2の補助導電性経路をさらに備え、第3のビアは第3の金属ラインに電気的に結合され、第3の金属ラインは次に第4のビアに電気的に結合され、第3の金属ラインは第1および第2の金属層とは異なる第3の金属層内に配置され、第3および第4のビアは第2の金属層と第3の金属層との間に配置され、第3および第4のビアは第3の金属ラインを第2の金属ラインに電気的に結合し、それによって、第2の補助導電性経路は、第1の導電性経路を通って流れる電流の追加の部分を転流することによって第1の導電性経路の電流および電流密度をさらに低減する。

#### 【0015】

別の特徴は、集積回路の経路選択を実行して複数の金属層にわたって複数の導電性経路を生成するステップと、電流および電流密度を有する複数の導電性経路のうちの第1の導電性経路を特定するステップであって、第1の導電性経路が第1の金属層内の少なくとも第1の金属ラインを含む、実行するステップと、経路選択および特定のステップを実行した後、第1のビア、第2の金属ラインおよび第2のビアを形成するステップを含む補助導電性経路を形成するステップとを含むプロセスによって準備される集積回路であって、第1のビアは第2の金属ラインに電気的に結合され、第2の金属ラインは次に第2のビアに電気的に結合され、第2の金属ラインは、第1の金属層とは異なる第2の金属層内に配置され、第1および第2のビアは第1の金属層と第2の金属層との間に配置され、第1および第2のビアは第1の金属ラインを第2の金属ラインに電気的に結合し、それによって、補助導電性経路は、第1の導電性経路を通って流れる電流の一部を転流することによって第1の導電性経路の電流および電流密度を低減する、集積回路を提供する。3040

#### 【図面の簡単な説明】

#### 【0016】

【図1】金属ラインおよびビアのマトリクスの挿入を特徴とする例示的な集積回路(IC)の斜視図である。

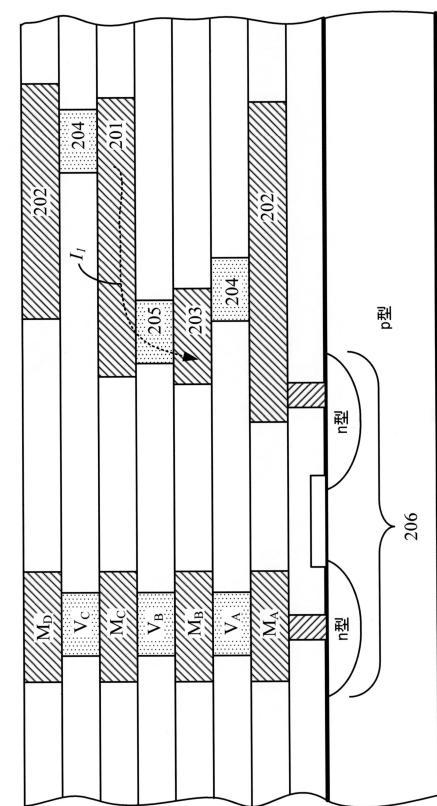

【図2】線2-2に沿った、ICの概略的な横断面図である。

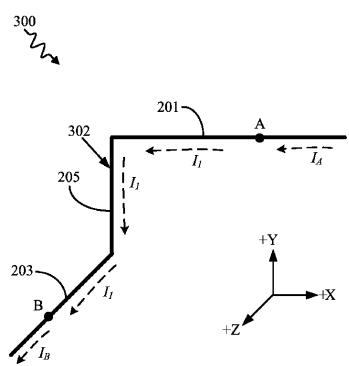

【図3】IC内の第1の導電性経路の概念的な斜視図である。

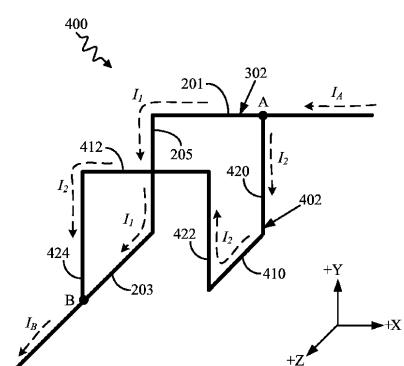

【図4】金属ライン-ビアのマトリクスの挿入を特徴とするIC内の第2の導電性経路の概念的な斜視図である。50

【図5】多段バッファ経路を示す図である。

【図6】金属ライン-ビアのマトリクスの挿入後の多段バッファ経路を示す図である。

【図7】図5および図6に示すバッファ経路のステージA、BおよびCに対する相対的IR電圧

下降対時間を示す図である。

【図8】金属ライン-ビアのマトリクスの挿入を特徴とするIC内の第3の導電性経路の概念的な斜視図である。

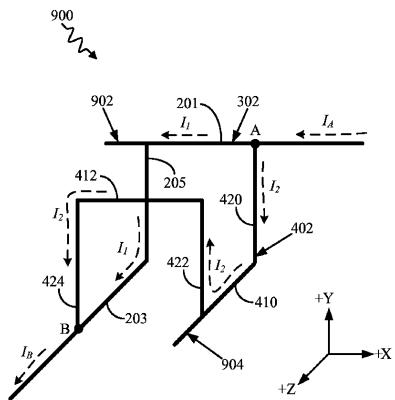

【図9】金属ライン-ビアのマトリクスの挿入を特徴とするIC内の第4の導電性経路の概念的な斜視図である。

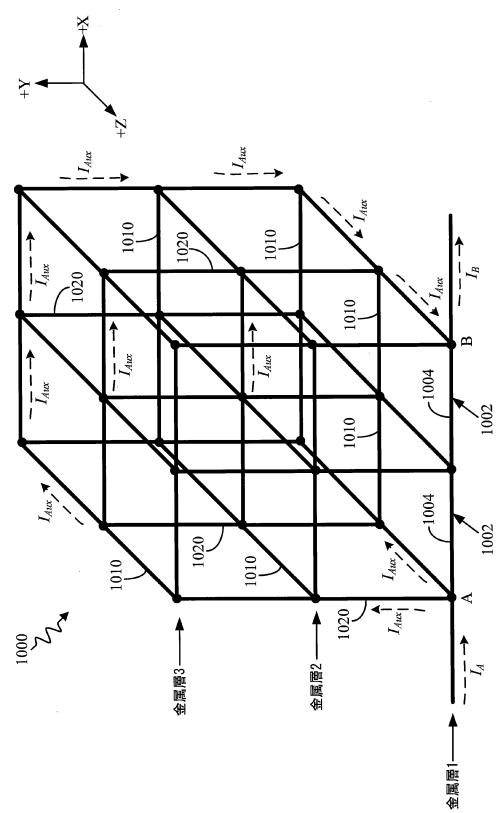

【図10】金属ライン-ビアのマトリクスの挿入を特徴とするIC内の第5の導電性経路の概念的な斜視図である。 10

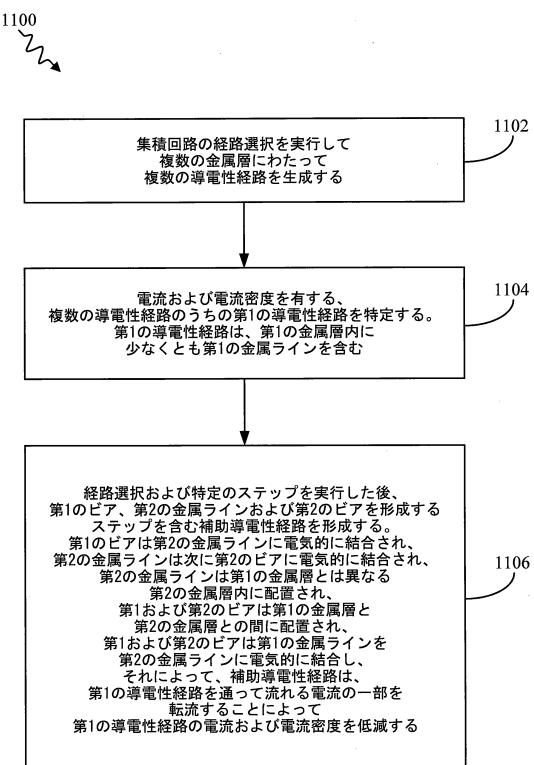

【図11】集積回路を製造する方法のフローチャートである。

【発明を実施するための形態】

【0017】

以下の説明では、本開示の様々な態様の完全な理解を提供するために、具体的な詳細が与えられる。しかしながら、これらの態様が、これらの具体的な詳細なしに実施されてもよいことが、当業者には理解されよう。たとえば、回路は、不必要的詳細で態様を不明瞭にすることを避けるために、ブロック図で示される場合がある。他の事例では、よく知られている回路、構造、および技法は、本開示の態様を不明瞭にしないために、詳細には示されない場合がある。

【0018】 20

「例示的」という単語は、本明細書では、「例、事例、または例示として機能する」ことを意味するために使用される。「例示的」として本明細書で説明した任意の実装形態または態様は、必ずしも本開示の他の態様よりも好ましいまたは有利であると解釈されるべきではない。同様に、「態様」という用語は、本開示のすべての態様が、説明された特徴、利点、または動作モードを含むことを必要としない。本明細書において使用されているように、「電気的に結合された」という用語は、2つの対象間に生じる電流の流れを許容する、2つの対象間の直接的または間接的結合を指す。たとえば、物体Aが物体Bに物理的に接触し、物体Bが物体Cに接触する場合、物体AおよびCは、互いに直接物理的に接触していないとも、物体Bが、物体Aから物体Cへの、および/または物体Cから物体Aへの電流の流れが発生することを可能にする導体であれば、互いに電気的に結合されるとさらに見なされ得る。 30

【0019】

概説

集積回路のレイアウトに対して、設置および経路選択プロセス(place and route process)が実行および/または完了された後の金属ライン-ビアのマトリクスの挿入を特徴とする、集積回路およびそのような回路を製造する方法を、本明細書で開示する。金属ライン-ビアマトリクスは、エレクトロマイグレーション、IR電圧降下、および/またはジッタの影響を被るものと決定された第1の導電性経路を通る電流および電流密度を低下させるために、特定のポイントにおいて集積回路のレイアウト内に挿入される1つまたは複数の追加の金属ラインおよび1つまたは複数の追加のビアから成る。詳細には、金属ライン-ビアマトリクスは、さもなければ第1の導電性経路を通って流れることになる電流の一部を転流して搬送するために、1つまたは複数の補助導電性経路を提供する。このことで、第1の導電性経路に沿ったエレクトロマイグレーション問題とIR電圧降下とが軽減される。このことで、同じく、経路に沿ったジッタによる問題を緩和することが支援され得る。 40

【0020】

金属ラインおよびビアのマトリクスの挿入を特徴とする例示的なIC

図1は、本開示の一態様による、金属ラインおよびビアのマトリクスの挿入を特徴とする例示的な集積回路(IC)100の斜視図を示す。IC100は、限定はしないが、プロセッサ、プロセッサ内の処理回路、メモリ回路などを含む、任意のタイプのICとすることができます。IC100は、限定はしないが、モバイルフォン、コンピュータ、タブレット、時計、メガネ 50

などの電子通信デバイスを含む任意の電子デバイス内で見出されることがある。図示の例では、IC100は、「フリップチップ」ICである。しかしながら、本明細書で説明する方法およびデバイスは、ワイヤボンドICを含む任意の他のタイプのICに、同等に適用される。

#### 【0021】

図2は、線2-2(図1参照)に沿ったIC100の概略的な横断面図を示す。IC100は、導電性ピア( $V_A$ 、 $V_B$ 、 $V_C$ 、など)を通って共に電気的に結合されてよい金属ライン/金属トレース201、202、203を有する複数の金属層(たとえば、 $M_A$ 、 $M_B$ 、 $M_C$ 、 $M_D$ 、など)を含む。金属ライン201、202、203およびピア204、205のネットワークは、たとえば、導電性経路を設けることによって、トランジスタ206または他の回路要素を、他のデバイス、電力ネットワーク、接地ネットワークなど、IC100の他の部分に電気的に結合してもよい。これらの金属ライン201、202、203および/またはピア204、205のうちの1つまたは複数は、エレクトロマイグレーション、突入電流によって生じるIR電圧降下、および/またはジッタの影響を受けやすい場合があり、したがって、これらの問題のある影響を低減するための方法およびデバイスが、そのようなIC100に適用され得る。たとえば、金属ライン201、203およびピア205を通じて流れる電流 $I_1$ は、比較的高い電流密度を有し、エレクトロマイグレーション、IR電圧降下、および/またはジッタの問題を生じることがある。以下でより詳細に説明するように、IC100は、電流密度および電流 $I_1$ を低減するための金属ラインおよびピア挿入を含み、それによってエレクトロマイグレーション、IR電圧降下、およびジッタが緩和される。図示の例では、4つの金属層が示されている。しかしながら、実際には、本明細書で説明する方法およびデバイスは、任意の複数の金属およびピアの層を有するICに適用される。

#### 【0022】

図3は、非制限的な一例による、IC100内の導電性経路300の概念的な斜視図を示す。導電性経路300は、ポイントAからポイントBに延び、金属ライン201、203およびピア205を含む第1の導電性経路302を含む。第1の導電性経路302は、図3に示す破線の方向を示す矢印に従って流れる電流 $I_1$ を搬送する。したがって、電流 $I_1$ は、(1)正のX軸から開始して負のX軸に向かう方向に第1の金属ライン201に沿って流れ、(2)次いで、ピア205を下方に(すなわち、正のY軸から負のY軸に)流れ、(3)次いで、負のZ軸から正のZ軸の方向に第2の金属ライン203を通じて流れる。ポイントAに入る電流 $I_A$ の大きさは、ポイントBを出る電流 $I_B$ の大きさに等しい。図示の第1の導電性経路302は、電流 $I_A$ が流入し、電流 $I_B$ が流出するために利用可能な唯一の経路であるので、電流 $I_1$ の大きさは、電流 $I_A$ および $I_B$ の大きさに等しい。したがって、 $|I_1|=|I_A|=|I_B|$ である。

#### 【0023】

図示の例では、第1の金属ライン201は、第2の金属ライン203(たとえば、金属層 $M_B$ 内)より高い金属層(たとえば、金属層 $M_C$ )内にあってよく、ピア205はピア層 $V_B$ 内にあってよい。しかしながら、これは、単なる例である。第1の金属ライン201は、第2の金属ライン203とは異なる任意の金属層内にあってよく、1つまたは複数のピア205は、2つのライン201、203を共に電気的に結合してもよい。同様に、電流 $I_1$ 、 $I_A$ および $I_B$ の方向は、反転されてもよい。

#### 【0024】

図3に示す導電性経路300、302は、IC100(または、導電性経路300、302を含むIC100の少なくとも一部)の設置および経路選択が実行/完了された後に生成される。設置および経路の設計ステージが実行された後、第1の導電性経路302は、その経路を通じて流れる大電流に起因する高電流密度および突入電流によって引き起こされるIR電圧降下によるエレクトロマイグレーションの影響を受けやすいものと、(たとえば、シミュレーション/試験によって)決定されることがある。同様にまたは代替として、導電性経路302は、ジッタ問題の影響を受けやすいことがある。以下で説明するように、1つまたは複数の追加の、金属ラインから成る導電性経路およびピアをICのレイアウト設計に挿入することで、第1の導電性経路302の電流密度および電流が低減され、その結果、エレクトロマイグレーション、IR電圧降下、および/またはジッタの問題が緩和され得る。

10

20

30

40

50

## 【0025】

図4は、非限定的な一例による、金属ライン-ビアのマトリクスの挿入を特徴とするIC10 0内の導電性経路400の概念的な斜視図を示す。導電性経路400はポイントAからポイントBに延び、図3に関して上記で説明した第1の導電性経路302(たとえば、「主導電性経路」と呼ばれることがある)を含み、同じく、追加の金属ライン410、412およびビア420、422、424の挿入によって形成された補助導電性経路402(たとえば、「第二の導電性経路」と呼ばれることがある)を含む。(金属ライン410、412およびビア420、422、424など、挿入された金属ラインおよびビアは、本明細書では「金属ライン-ビアマトリクス」と呼ばれることがある。)第1の挿入された金属ライン410は、第2の挿入された金属ライン412とは異なる(たとえば、金属ライン412より低い)金属層内にあってよい。第1の挿入された金属ライン410は第2の金属ライン203と、および第2の挿入された金属ライン412は第1の導電性経路302の第1の金属ライン201と、それぞれ同じ金属層内にあってよい。挿入されたビア420、422、424は、第1の導電性経路302のビア205と同じビア層内にあってよい。補助導電性経路402を備える金属ライン-ビアマトリクスは、IC100(または、第1の導電性経路302を含むIC100の何らかの部分)の設置および経路選択ステージが実行された後、IC100のレイアウト設計に挿入される。10

## 【0026】

図3に関して上記で説明した導電性経路300と同様に、ポイントAに入る図4の電流 $I_A$ の大きさは、ポイントBを出る電流 $I_B$ の大きさに等しい。しかしながら、図3とは違って、図4に示す電流 $I_A$ の一部は、電流 $I_1$ として第1の導電性経路302に沿って流れ、電流 $I_A$ の別の部分は、破線の方向を示す矢印に沿って電流 $I_2$ として補助導電性経路402に沿って流れ。したがって、例に示すように、電流 $I_2$ は、(1)正のY軸から負のY軸の方向に第1の挿入されたビア420を通って下方に流れ、(2)負のZ軸から正のZ軸の方向に第1の挿入された金属ライン410を通って流れ、(3)負のY軸から正のY軸の方向に第2の挿入されたビア422を通って上方に流れ、(4)正のX軸から負のX軸の方向に第2の挿入された金属ライン412を通って流れ、(5)正のY軸から負のY軸の方向に第3の挿入されたビア424を下方に戻って流れ、そこで、電流 $I_2$ は、第1の導電性経路302の電流 $I_1$ と再結合して、ポイントBから流出する電流 $I_B$ を形成する。したがって、 $|I_1 + I_2| = |I_A| = |I_B|$ である。20

## 【0027】

実際には、補助導電性経路402は、さもなければ通常に第1の導電性経路302を通って流れることになる電流の一部を転流する。この電流を補助導電性経路402を通して転流する(たとえば、電流 $I_2$ を生成する)ことによって、第1の導電性経路302の電流密度(たとえば、電流 $I_1$ )は低減され、その結果、第1の導電性経路302に沿った任意の既存のエレクトロマイグレーション問題もまた低減され得る。同様に、第1の導電性経路302を通って流れる電流の量(たとえば、それは突入電流であることがある)も低減され、低減されたIR電圧降下がもたらされる。同じく、金属ライン-ビアマトリクスの挿入によって、第1の導電性経路302に沿ったジッタの低減が支援され得る。30

## 【0028】

その上、第1の導電性経路302を通って流れる電流の量の低減に加えて、金属ライン-ビアマトリクスは、突入電流によって引き起こされるIR電圧降下を低減するという付加的特徴/特性を提供する。金属ライン-ビアマトリクスの補助導電性経路402は、第1の導電性経路302とは異なる長さを有し、その結果、補助導電性経路402の電流 $I_2$ がポイントAからポイントBまで流れるのにかかる時間の量は、電流 $I_1$ がポイントAからポイントBまで流れるのにかかる時間の量とは異なる。図4に示す非限定的な例では、第2の導電性経路402は、第1の導電性経路302より長く、したがって、第2の導電性経路402の電流 $I_2$ がポイントAからポイントBまで流れるのにかかる時間期間は、電流 $I_1$ がポイントAからポイントBまで流れるのにかかる時間期間より長い。補助導電性経路402と第1の導電性経路302との待ち時間は異なるので、全体的導電性経路400(それは経路302、402を含む)を通って流れる突入電流は、より長い時間間にわたって分散される。このことは、突然流入する電流の影響を著しく低減する(たとえば、IR電圧降下を低減する)。補助導電性経路402の最適長さ(ま4050

たは、複数の補助経路の場合は各補助経路の最適長さ(たとえば、図8および図10参照))は、導電性経路400と関係付けられた抵抗-キャパシタ遅延(すなわち、RC遅延)と、導電性経路400を有する回路のクロック周波数(たとえば、IC100のクロック周波数)とによって決定されてよい。

#### 【0029】

図5～図7は共に、突入電流によって引き起こされる最大IR電圧降下を低減するために、補助導電性経路402および第1の導電性経路302の異なる待ち時間(すなわち、信号経路遅延)が、突入電流をより長い時間間にわたって分散するのをどのように支援するかを示す。

#### 【0030】

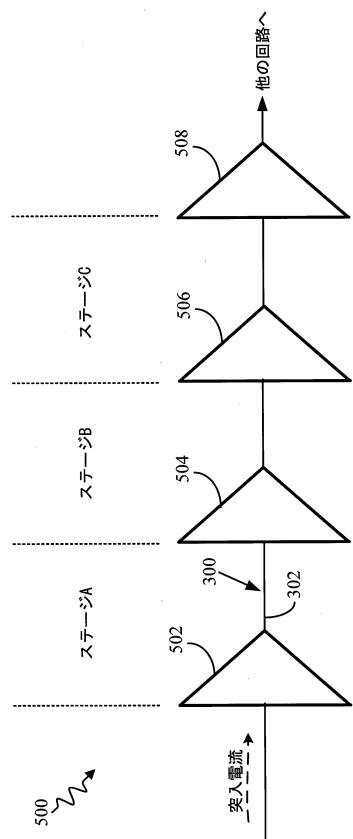

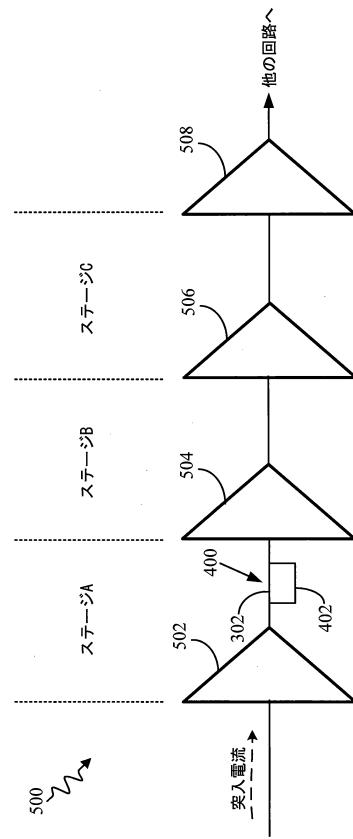

図5は、本開示の一態様による、多段バッファ経路500を示す。バッファ経路500は、第1のバッファ502、第2のバッファ504、第3のバッファ506、および第4のバッファ508を含む。追加のバッファ(図示せず)が、第4のバッファ508に後続してもよい。第1のバッファ502と第2のバッファ504との間のバッファ経路500の部分は、ステージAと見なされてよく、第2のバッファ504と第3のバッファ506との間の部分はステージB、第3のバッファ506と第4のバッファ508との間の部分はステージCと見なされてよい。図5の破線の矢印で示される突入電流は、バッファ経路500を通って流れる。図5では、第1のバッファ502を第2のバッファ504に結合する導電性経路は、図3の導電性経路300であり、導電性経路300は第1の導電性経路302を含む。

#### 【0031】

図6は、金属ライン-ピアのマトリクスの挿入後の多段バッファ経路500を示しており、ここで、第1のバッファ502を第2のバッファ504に結合する導電性経路は、今回は、第1の導電性経路302のみならず補助導電性経路402をも含む図4の導電性経路400である。上記で説明したように、補助導電性経路402は、第1の導電性経路302とは異なる(たとえば、より長い)経路遅延を有する。

#### 【0032】

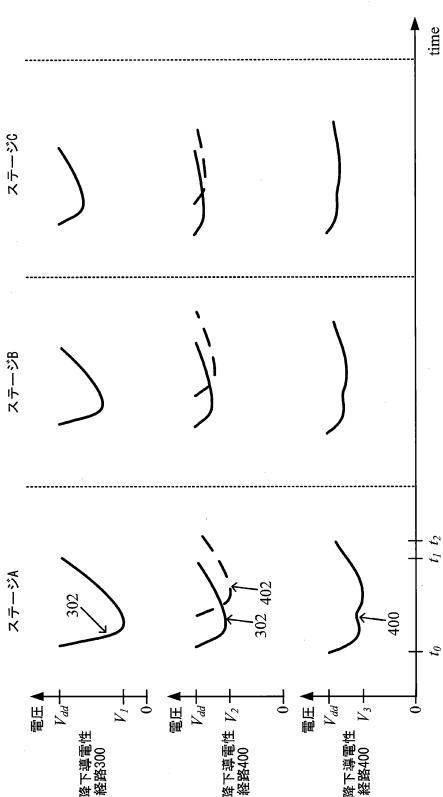

図7は、第1のバッファ502と第2のバッファ504との間に設置された特定の導電性経路(たとえば、図3の導電性経路300または図4の導電性経路400のいずれか)による、図5および図6に示すバッファ経路500のステージA、BおよびCに対する相対的IR電圧降下対時間を示す。図7の上部三分の一は、第1の導電性経路302のみを含む図3の導電性経路300が、第1のバッファ502と第2のバッファ504とを互いに電気的に結合するときの、バッファ経路500の突入電流によって引き起こされるIR電圧降下を示す。第1の導電性経路302において観測された最大IR電圧降下は、ステージAにおける電圧を相対的に低い電圧 $V_1$ まで低下させる。このことは、いくつかの問題の中でも特に、たとえば低電圧レベルがいくつかのトランジスタを、それらがオフであるべきときにオンに、またはそれらがオンであるべきときにオフに切り替わらせる場合に、回路不良を引き起こすことがある。

#### 【0033】

図7の中部三分の一は、第1の導電性経路302と補助導電性経路402の両方を含む図4の導電性経路400が、第1のバッファ502と第2のバッファ504とを互いに電気的に結合するときの、バッファ経路500の突入電流によって引き起こされるIR電圧降下を示す。第1の導電性経路302および補助導電性経路402において観測された最大IR電圧降下は、これらの経路302、402の各々のステージAにおける電圧レベルがほぼ電圧 $V_2$ (ここで $V_2$ は $V_1$ より大きい)まで低下し、それらの経路の異なる経路遅延のために互いに対しても時間シフトすることを引き起こす。したがって、図7の中部三分の一は、各導電性経路302、402の個別のIR電圧降下の寄与を示す。

#### 【0034】

図7の下部三分の一は、再び図4の導電性経路400が、第1のバッファ502と第2のバッファ504とを互いに電気的に結合するときの、バッファ経路500の突入電流によって引き起こされるIR電圧降下を示す。ここに示す曲線は、導電性経路400の電圧レベルを電圧 $V_3$ まで低下させる、ステージAの合成の最大IR電圧降下を表す。 $V_3$ は $V_1$ より大きいので、金属ライ

10

20

30

40

50

ン-ビアマトリクスを挿入することで、第1の導電性経路302の突入電流によって引き起こされる最大のIR電圧降下が、 $V_3-V_1$ の量だけ低減される。補助導電性経路402に関連するより長い信号経路は、突入電流全体が、より長い時間期間にわたって導電性経路400を通って流れることをもたらして、IR電圧降下を、 $t_0 \sim t_1$ ではなく $t_0 \sim t_2$ に時間的に長引かせる。バッファ経路500の後のステージ(たとえば、ステージBおよびC)は、バッファ504、506の効果によって突入電流によって引き起こされるIR電圧降下があまり顕著でない(すなわち、あまり大きくない)ことを除いて、ステージAと非常に類似した形状の曲線を示す。

#### 【 0 0 3 5 】

上述のように、補助導電性経路402の図4に示す例は、例にすぎない。一般に、任意のサイズおよび形状の1つまたは複数の補助導電性経路を備える金属ライン-ビアマトリクスは、IC500の設置および経路選択が実行され、エレクトロマイグレーション、IR電圧降下、および/またはジッタを生じやすい、問題のある導電性経路が特定された後で挿入されてもよい。一般に、挿入された金属ライン-ビアマトリクスは、第1の金属層内に少なくとも第1の金属ラインを含む第1の導電性経路と、第2の金属層内の第2の金属ライン、第1の金属層と第2の金属層との間の第1のビア、および第1の金属層と第2の金属層との間の第2のビアを含む少なくとも1つの補助導電性経路とを備えてよい。第1および第2のビアは、第1の金属ラインを第2の金属ラインに電気的に結合し、それによって、補助導電性経路は、第1の導電性経路を通って流れる電流の一部を共有/転流することによって、第1の導電性経路の電流および電流密度を低減する。下記は、第1の導電性経路のエレクトロマイグレーション、IR電圧降下、および/またはジッタを低減するために補助導電性経路を提供する異なる態様による、金属ライン-ビアマトリクスのいくつかの追加の非限定的な例である。

#### 【 0 0 3 6 】

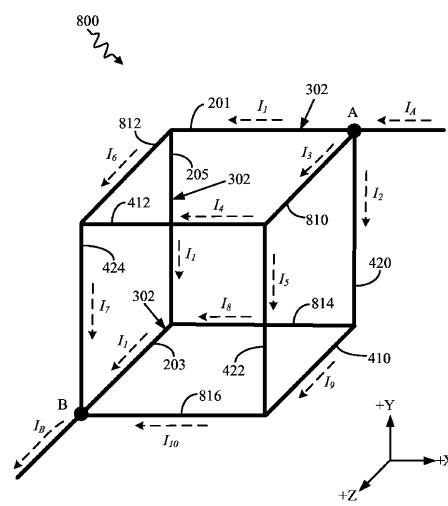

図8は、非限定的な別の例による、金属ライン-ビアのマトリクスの挿入を特徴とするIC100内の導電性経路800の概念的な斜視図を示す。図4に示す導電性経路400と同様に、図8の導電性経路800は、ポイントAからポイントBに延び、第1の導電性経路302を含む。導電性経路800はまた、金属ライン410、412、810、812、814、816およびビア420、422、424を含む金属ライン-ビアマトリクスの挿入によって形成された追加の補助導電性経路を含む。いくつかの挿入された金属ライン410、814、816は、他の挿入された金属ライン412、810、812とは異なる(たとえば、より低い)金属層内にあってよい。いくつかの挿入された金属ライン410、814、816は、第1の導電性経路302の第2の金属ライン203と同じ金属層内にあってよく、他の挿入された金属ライン412、810、812は、第1の導電性経路302の第1の金属ライン201と同じ金属層内にあってよい。挿入されたビア420、422、424は、第1の導電性経路302のビア205と同じビア層内にあってよい。図8に示す金属ライン-ビアマトリクスは、IC100(または、第1の導電性経路302を含むIC100の何らかの部分)の設置および経路選択のステージが実行された後に挿入される。

#### 【 0 0 3 7 】

図3に関して上記で説明した導電性経路300と同様に、ポイントAに入る図8の電流 $I_A$ の大きさは、ポイントBを出る電流 $I_B$ の大きさに等しい。しかしながら、図3とは違って、図8に示す電流 $I_A$ の一部のみが、電流 $I_1$ として第1の導電性経路302に沿って流れる。電流 $I_A$ の他のかなりの部分は、電流 $I_2$ 、 $I_3$ 、 $I_4$ 、 $I_5$ 、 $I_6$ 、 $I_7$ 、 $I_8$ 、 $I_9$ および $I_{10}$ で表される、金属ライン-ビアマトリクスの追加の補助導電性経路に沿って流れる。補助導電性経路の電流 $I_2$ 、 $I_3$ 、 $I_4$ 、 $I_5$ 、 $I_6$ 、 $I_7$ 、 $I_8$ 、 $I_9$ および $I_{10}$ は、全体的に、破線の方向を示す矢印で示すように、ポイントAからポイントBの方向に流れる。

#### 【 0 0 3 8 】

実際には、挿入された金属ライン-ビアマトリクスは、さもなければ通常に第1の導電性経路302を通って流れることになる電流の一部を転流する。金属ライン-ビアマトリクスを通るこの電流(たとえば、電流 $I_2$ 、 $I_3$ 、 $I_4$ 、 $I_5$ 、 $I_6$ 、 $I_7$ 、 $I_8$ 、 $I_9$ および $I_{10}$ )を転流することによって、第1の導電性経路302の電流密度および電流が低減され、その結果、第1の導電性経路302に沿った任意の既存のエレクトロマイグレーション、突入電流によって引き

10

20

30

40

50

起こされるIR電圧降下、および/またはジッタの問題もまた、低減され得る。

#### 【0039】

図9は、非限定的な別の例による、金属ライン-ビアのマトリクスの挿入を特徴とするIC100内の導電性経路900の概念的な斜視図を示す。図9に示す導電性経路900は、第1の導電性経路302の第1の金属ライン201が金属延長片902を含み、金属ライン-ビアマトリクスの第1の挿入された金属ライン410が金属延長片904を含むことを除いて、図4に示す導電性経路400と極めて類似している。すなわち、第1の金属ライン201は、第1の延長片902を形成するために延長され、第2の挿入された金属ライン410は、より長くなるように形成され、それによって金属ライン410は第2の延長片904を含む。延長片902、904は、金属ライン201がビア205と結合する接合点、および金属ライン410がビア422と結合する接合点を越えて延びる。延長片902、904は、エレクトロマイグレーションによって増大する原子および/または正孔の影響を和らげる原子および/または正孔(すなわち、ボイド)収集プール(collision pool)として働く。延長片902、904は、それらが延び出して、エレクトロマイグレーションによって増大する原子がショートを生じる可能性があるほどIC100の他の導電性経路に接近しすぎることないように、注意深く形成される。同様に、延長片902、904の端部906、908は、いずれのものとも電気的に結合しない(すなわち、端部906、908はどこにも通じていない)ので、エレクトロマイグレーションによって引き起こされるボイドによって延長片902、904に沿った開回路ができた場合でも、延長片902、904は、導電性経路900の故障を生じることはない。図9に示す金属ライン201、410において形成された延長片902、904は、例にすぎない。延長片は、IC100の導電性経路(たとえば、第1の導電性経路および/または補助導電性経路)の任意の金属ラインおよび/またはビアに沿って形成されてよい。10 20

#### 【0040】

挿入された金属ライン-ビアマトリクスは、(設計基準検査(DRC)違反がないものと仮定して)任意のサイズおよび形状であり得る。したがって、図10は、非限定的な別の例による、金属ライン-ビアのマトリクスの挿入を特徴とするIC100内の導電性経路1000の概念的な斜視図を示す。第1の金属ライン1004だけを含んでいた第1の導電性経路1002は、エレクトロマイグレーション、突入電流によって引き起こされるIR電圧降下、および/またはジッタを生じやすかった元の導電性経路である。その結果、図示の残りの金属ライン1010およびビア1020(明確さのため、図10にすべてがラベル付けされているわけではない)は、補助導電性経路( $I_{Aux}$ とラベル付けされている、明確さのため、すべてがラベル付けされているわけではない)を生成して第1の導電性経路1002を通る電流密度および電流を低減するために、IC100の設置および経路選択の後で挿入される。30

#### 【0041】

図8の金属ライン-ビアマトリクスは、「 $2 \times 2$ 」マトリクスと見なされてよい一方、図10に示す金属ライン-ビアマトリクスは、3つの異なる金属層(たとえば、 $M_A$ 、 $M_B$ 、 $M_C$ 、など)内に挿入された金属ラインと、それらの金属層の間のビアとを含むので、「 $3 \times 3$ 」マトリクスと見なされてよい。他の非限定的な金属ライン-ビアマトリクスのサイズには、 $4 \times 4$ 、 $2 \times 4$ 、 $4 \times 2$ 、 $2 \times 3$ 、 $3 \times 2$ 、 $1 \times 2$ 、 $2 \times 1$ 、などが含まれる。

#### 【0042】

図11は、本開示の一態様による、集積回路を製造する方法のフローチャート1100を示す。最初に、集積回路の経路選択が、複数の金属層にわたって複数の導電性経路を生成するために実行される1102。次に、電流および電流密度を有する、複数の導電性経路のうちの第1の導電性経路が特定され、ここで、第1の導電性経路は、第1の金属層内に少なくとも第1の金属ラインを含む1104。次いで、経路選択および特定のステップを実行した後、第2のビアに電気的に結合された第2の金属ラインに電気的に結合された第1のビアを含む補助導電性経路が形成される。第2の金属ラインが、第1の金属層とは異なる第2の金属層内に配置される。第1および第2のビアが、第1の金属層と第2の金属層との間に配置される。その上、第1および第2のビアは、第1の金属ラインを第2の金属ラインに電気的に結合し、それによって、補助導電性経路は、第1の導電性経路を通って流れる電流の一部を転流する40 50

ことによって第1の導電性経路の電流および電流密度を低減する1106。

【0043】

減結合キャパシタと比較すると、上記で説明したように、エレクトロマイグレーション、IR電圧降下、およびジッタに対処するために金属ライン-ビアのマトリクスの挿入を利用することで、著しく少ない電力が消費される。その上、金属ライン-ビアマトリクスは、従来のde-capと比較して、非常に小さい空間を占める。

【0044】

図1、図2、図3、図4、図5、図6、図7、図8、図9、図10および図11に示された構成要素、ステップ、特徴および/または機能のうちの1つまたは複数は、単一の構成要素、ステップ、特徴または機能に再構成され、かつ/もしくは組み合わされ、または、いくつかの構成要素、ステップ、または機能で具現化することができる。本発明から逸脱することなく、さらなる要素、構成要素、ステップ、および/または機能が付加されてもよい。また、本明細書で説明したアルゴリズムは、効率的にソフトウェアに実装されてもよく、かつ/またはハードウェアに組み込まれてもよい。

10

【0045】

また、本開示の態様は、フローチャート、流れ図、構造図またはロック図として示されるプロセスとして説明され得ることに留意されたい。フローチャートは動作を逐次プロセスとして説明する場合があるが、動作の多くは並行してまたは同時に実行され得る。加えて、動作の順序は並べ替えられてもよい。プロセスは、その動作が完了したとき、終了する。プロセスは、方法、関数、プロシージャ、サブルーチン、サブプログラムなどに対応する場合がある。プロセスが関数に相当する場合、その終了は、その関数が呼び出し関数またはメイン関数に戻ることに相当する。

20

【0046】

その上、記憶媒体は、読み取り専用メモリ(ROM)、ランダムアクセスメモリ(RAM)、磁気ディスク記憶媒体、光学記憶媒体、フラッシュメモリデバイスおよび/もしくは他の機械可読媒体、およびプロセッサ可読媒体、ならびに/または情報を記憶するためのコンピュータ可読媒体を含む、データを記憶するための1つもしくは複数のデバイスを表し得る。「機械可読媒体」、「コンピュータ可読媒体」、および/または「プロセッサ可読媒体」という用語は、限定はしないが、ポータブルもしくは固定ストレージデバイス、光ストレージデバイス、ならびに、命令および/またはデータを記憶または格納することが可能な様々な他の媒体のような非一時的媒体を含み得る。したがって、本明細書で説明される様々な方法は、「機械可読媒体」、「コンピュータ可読媒体」および/または「プロセッサ可読媒体」に記憶され、1つもしくは複数のプロセッサ、機械および/またはデバイスによって実行され得る命令および/またはデータによって、完全にまたは部分的に実装され得る。

30

【0047】

さらに、本開示の態様は、ハードウェア、ソフトウェア、ファームウェア、ミドルウェア、マイクロコード、またはそれらの任意の組合せによって実装され得る。ソフトウェア、ファームウェア、ミドルウェアまたはマイクロコードで実装されるとき、必要なタスクを実行するプログラムコードまたはコードセグメントは、記憶媒体または他のストレージのような機械可読媒体に記憶され得る。プロセッサは、必要なタスクを実行する場合がある。コードセグメントは、プロシージャ、関数、サブプログラム、プログラム、ルーチン、サブルーチン、モジュール、ソフトウェアパッケージ、クラス、または命令、データ構造もしくはプログラムステートメントの任意の組合せを表す場合がある。コードセグメントは、情報、データ、引数、パラメータ、またはメモリ内容を渡すことおよび/または受け取ることによって、別のコードセグメントまたはハードウェア回路に結合され得る。情報、引数、パラメータ、データなどは、メモリ共有、メッセージパッシング、トーカンパッシング、ネットワーク送信などを含む、任意の適切な手段を介して渡されてもよく、転送されてもよく、または送信され得る。

40

【0048】

50

本明細書で開示する例に関して説明する様々な例示的な論理ブロック、モジュール、回路、要素、および/または構成要素は、汎用プロセッサ、デジタル信号プロセッサ(DSP)、特定用途向け集積回路(ASIC)、フィールドプログラマブルゲートアレイ(FPGA)もしくは他のプログラマブル論理構成要素、個別ゲートもしくはトランジスタ論理、個別ハードウェア構成要素、または本明細書で説明する機能を実施するように設計されたそれらの任意の組合せで実装または実行されてもよい。汎用プロセッサはマイクロプロセッサであり得るが、代替として、プロセッサは、任意の従来型プロセッサ、コントローラ、マイクロコントローラ、またはステートマシンであり得る。プロセッサはまた、コンピューティング構成要素の組合せ、たとえば、DSPとマイクロプロセッサとの組合せ、いくつかのマイクロプロセッサ、DSPコアと連係した1つもしくは複数のマイクロプロセッサ、または他の任意のそのような構成として実装され得る。

#### 【0049】

本明細書で開示する例に関して説明する方法またはアルゴリズムは、直接ハードウェアにおいて、プロセッサによって実行可能なソフトウェアモジュールにおいて、または両方の組合せにおいて、処理ユニット、プログラミング命令、または他の指示の形態で実施されてもよく、かつ、単一のデバイスに含まれてもよく、または複数のデバイスにわたって分散され得る。ソフトウェアモジュールは、RAMメモリ、フラッシュメモリ、ROMメモリ、EPROMメモリ、EEPROMメモリ、レジスタ、ハードディスク、リムーバブルディスク、CD-ROM、または当技術分野において知られている任意の他の形態の記憶媒体に常駐し得る。プロセッサが記憶媒体から情報を読み取り、記憶媒体に情報を書き込むことができるよう記憶媒体はプロセッサに結合され得る。代替案では、記憶媒体は、プロセッサに一体化され得る。

#### 【0050】

当業者は、本明細書で開示される態様に関連して説明された様々な例示的な論理ブロック、モジュール、回路、およびアルゴリズムステップが、電子ハードウェア、コンピュータソフトウェア、またはその両方の組合せとして実施され得ることを、さらに了解する。ハードウェアおよびソフトウェアのこの互換性を明確に示すために、様々な例示的なコンポーネント、ブロック、モジュール、回路、およびステップが、上では全般的にそれらの機能性に関して説明された。そのような機能性が、ハードウェアまたはソフトウェアのいずれとして実施されるのかは、特定の応用例およびシステム全体に課せられる設計制約に依存する。

#### 【0051】

本明細書で説明される本発明の様々な特徴は、本発明から逸脱することなく、異なるシステム内で実施され得る。本開示のこれまでの態様は例にすぎず、本発明を限定するものと解釈されるべきではないことに留意されたい。本開示の態様の説明は、例示であることを意図しており、特許請求の範囲を限定することは意図していない。したがって、本教示は、他のタイプの装置に容易に適用されることが可能であり、多くの代替形態、変更形態、および変形形態が当業者には明らかであろう。

#### 【符号の説明】

#### 【0052】

- 100 集積回路(IC)

- 201 金属ライン/金属トレース

- 202 金属ライン/金属トレース

- 203 金属ライン/金属トレース

- 204 ピア

- 205 ピア

- 206 トランジスタ

- 300 導電性経路

- 302 第1の導電性経路

- 400 導電性経路

10

20

30

40

50

|      |               |    |

|------|---------------|----|

| 402  | 補助導電性経路       |    |

| 410  | 第1の挿入された金属ライン |    |

| 412  | 第2の挿入された金属ライン |    |

| 420  | ピア            |    |

| 422  | ピア            |    |

| 424  | ピア            |    |

| 500  | 多段バッファ経路      |    |

| 502  | 第1のバッファ       |    |

| 504  | 第2のバッファ       |    |

| 506  | 第3のバッファ       | 10 |

| 508  | 第4のバッファ       |    |

| 800  | 導電性経路         |    |

| 810  | 挿入された金属ライン    |    |

| 812  | 挿入された金属ライン    |    |

| 814  | 挿入された金属ライン    |    |

| 816  | 挿入された金属ライン    |    |

| 900  | 導電性経路         |    |

| 902  | 金属延長片         |    |

| 904  | 金属延長片         |    |

| 906  | 端部            | 20 |

| 908  | 端部            |    |

| 1000 | 導電性経路         |    |

| 1002 | 第1の導電性経路      |    |

| 1004 | 第1の金属ライン      |    |

| 1010 | 金属ライン         |    |

| 1020 | ピア            |    |

【 図 1 】

*FIG. 1*

【 四 2 】

【 図 3 】

*FIG. 3*

【図4】

FIG. 4

【 図 5 】

【 図 6 】

【図7】

【 図 8 】

**FIG. 8**

【図9】

FIG. 9

【図10】

【図11】

---

フロントページの続き

(72)発明者 ジュ・イ・ル

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775

(72)発明者 シエンチョン・シェ

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775

審査官 市川 武宣

(56)参考文献 特表2008-541308(JP,A)

特開平11-186433(JP,A)

特開2006-228987(JP,A)

特開2002-009159(JP,A)

特開平02-165652(JP,A)

特開2003-031662(JP,A)

特開2011-091178(JP,A)

特開2007-214397(JP,A)

特開平11-243146(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/82

H01L 21/822

H01L 27/04