(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6705436号

(P6705436)

(45) 発行日 令和2年6月3日(2020.6.3)

(24) 登録日 令和2年5月18日(2020.5.18)

(51) Int.Cl.

F 1

**HO4N 5/3745 (2011.01)**

**HO4N 5/353 (2011.01)**

**HO4N 5/369 (2011.01)**

**HO1L 27/146 (2006.01)**

HO 4 N 5/3745 5 O O

HO 4 N 5/353

HO 4 N 5/369

HO 1 L 27/146 A

HO 1 L 27/146 D

請求項の数 15 (全 16 頁)

(21) 出願番号

特願2017-213249 (P2017-213249)

(22) 出願日

平成29年11月2日 (2017.11.2)

(62) 分割の表示

特願2013-197318 (P2013-197318)

の分割

原出願日 平成25年9月24日 (2013.9.24)

(65) 公開番号

特開2018-50319 (P2018-50319A)

(43) 公開日

平成30年3月29日 (2018.3.29)

審査請求日 平成29年12月1日 (2017.12.1)

(73) 特許権者 000004112

株式会社ニコン

東京都港区港南二丁目15番3号

(74) 代理人 110000877

龍華国際特許業務法人

(72) 発明者 綱井 史郎

東京都千代田区有楽町一丁目12番1号

株式会社ニコン内

審査官 松永 隆志

最終頁に続く

(54) 【発明の名称】撮像素子および撮像装置

(57) 【特許請求の範囲】

## 【請求項1】

光を光電変換して電荷を生成する光電変換部と、

前記光電変換部で生成された電荷量が閾値以上となると第1信号を出力する検出部と、

前記光電変換部で生成された電荷量が前記閾値以上となつた回数を計数する計数部と、

前記光電変換部に入射する光の強度が小さくなると周期が短くなり、光の強度が大きくなると周期が長くなる第2信号が、入力される入力部と、

前記第1信号と前記第2信号とに基づいて、前記光電変換部で生成された電荷の蓄積をリセットするリセット部と、

を備える撮像素子。

## 【請求項2】

請求項1に記載の撮像素子において、

前記リセット部は、前記入力部に前記第2信号が入力されている間に、前記検出部から前記第1信号が出力されると、前記光電変換部で生成された電荷の蓄積をリセットする撮像素子。

## 【請求項3】

請求項1または2に記載の撮像素子において、

前記入力部は、前記第1信号と前記第2信号とが入力され、

前記入力部は、前記第2信号が入力されている間に、前記第1信号が入力されると、前記光電変換部で生成された電荷の蓄積をリセットするよう前記リセット部に信号を出力す

る撮像素子。

**【請求項 4】**

請求項 1 から 3 のいずれか一項に記載の撮像素子において、複数の前記光電変換部毎に前記閾値を制御する制御部と、を備える撮像素子。

**【請求項 5】**

請求項 4 に記載の撮像素子において、

前記制御部は、前記光電変換部に入射する光の強度に基づいて前記閾値を制御する撮像素子。

**【請求項 6】**

請求項 4 または 5 に記載の撮像素子において、

前記制御部は、複数の前記光電変換部に入射する光の強度に基づいて、複数の前記光電変換部毎に前記閾値を制御する撮像素子。

**【請求項 7】**

請求項 4 から 6 のいずれか一項に記載の撮像素子において、

複数の前記制御部を備え、

複数の前記制御部はそれぞれ複数の前記光電変換部毎に 1 つ設けられ、複数の前記光電変換部毎に前記閾値を制御する撮像素子。

**【請求項 8】**

請求項 1 から 7 のいずれか一項に記載の撮像素子において、

前記検出部は、前記光電変換部で生成された電荷に基づく信号に基づいて、前記光電変換部で生成された電荷量が閾値以上となることを検出する撮像素子。

**【請求項 9】**

請求項 1 から 8 のいずれか一項に記載の撮像素子において、

前記計数部は、所定の期間内に、前記光電変換部で生成された電荷量が閾値以上になった回数を計数する撮像素子。

**【請求項 10】**

請求項 1 から 9 のいずれか一項に記載の撮像素子において、

前記計数部は、前記第 1 信号に基づいて、前記光電変換部で生成された電荷量が閾値以上になった回数を計数する撮像素子。

30

**【請求項 11】**

請求項 1 から 10 のいずれか一項に記載の撮像素子において、

前記計数部は、前記リセット部によりリセットされた回数を計数する撮像素子。

**【請求項 12】**

請求項 1 から 11 のいずれか一項に記載の撮像素子において、

前記光電変換部で生成された電荷に基づく信号が出力される出力部と、

前記第 1 信号を遅延させた信号を出力する遅延部を備え、

前記検出部は、前記遅延部から信号が出力されたタイミングにおいて前記出力部から出力される信号と、前記光電変換部で生成された電荷に基づく信号との差分が入力される撮像素子。

40

**【請求項 13】**

請求項 1 から 12 のいずれか一項に記載の撮像素子において、

複数の前記光電変換部が設けられる撮像チップと、

前記撮像チップに積層され、前記計数部が設けられる信号処理チップと、を備える撮像素子。

**【請求項 14】**

請求項 1 3 に記載の撮像素子において、

前記検出部は、前記撮像チップに設けられる撮像素子。

**【請求項 15】**

請求項 1 から 14 のいずれか一項に記載の撮像素子を備える撮像装置。

50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、撮像素子および撮像装置に関する。

**【背景技術】****【0002】**

複数の画素を有する撮像素子において、A/Dコンバータを画素毎に配置する構成が知られている（例えば、特許文献1図2参照）。

特許文献1 特許第4928674号公報

**【発明の概要】**

10

**【発明が解決しようとする課題】****【0003】**

上述した撮像素子は、異なる露光時間のフレーム毎に画像を取得する。そして、各フレームの画像を組み合わせることで、A/Dコンバータのダイナミックレンジを広くしている。このため、A/Dコンバータの分解能を高くするには、フレーム数を多くしなければならない。しかし、フレーム毎に画像データを記憶しなければならぬので、高分解能化は困難である。

**【課題を解決するための手段】****【0004】**

20

本発明の第1の態様においては、入射光に応じて電荷を発生させる複数の光電変換部と、光電変換部毎に設けられた個別処理部とを備え、それぞれの個別処理部は、対応する光電変換部が発生した電荷の蓄積量が、予め定められた規定閾値を超えたことを検出する検出部と、蓄積量が規定閾値を超えた場合に、蓄積量をリセットするリセット部と、予め定められた規定期間内に、蓄積量が規定閾値を超えた回数を計数する計数部とを有する撮像素子を提供する。

**【0005】**

本発明の第2の態様においては、第1の態様の撮像素子を備える撮像装置を提供する。

**【0006】**

なお、上記の発明の概要は、本発明の必要な特徴の全てを列挙したものではない。また、これらの特徴群のサブコンビネーションもまた、発明となりうる。

30

**【図面の簡単な説明】****【0007】**

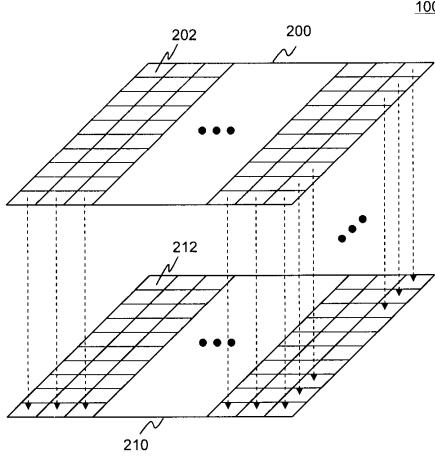

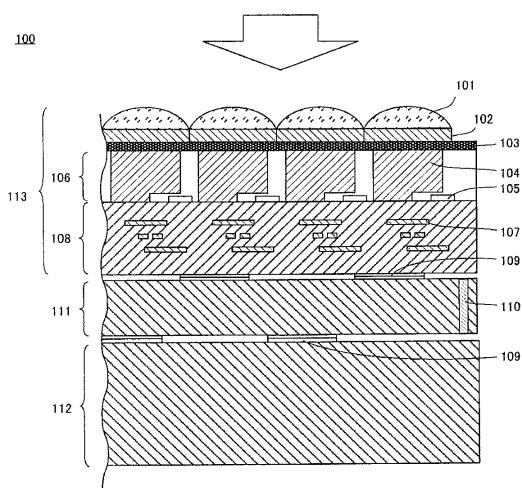

【図1】本発明の実施形態に係る撮像素子100の概要を示す図である。

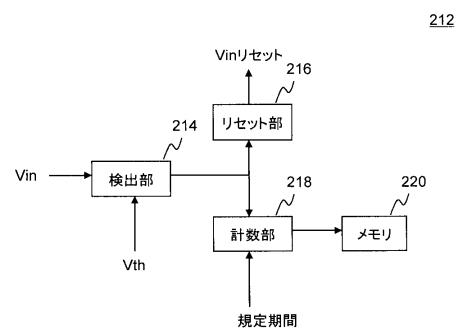

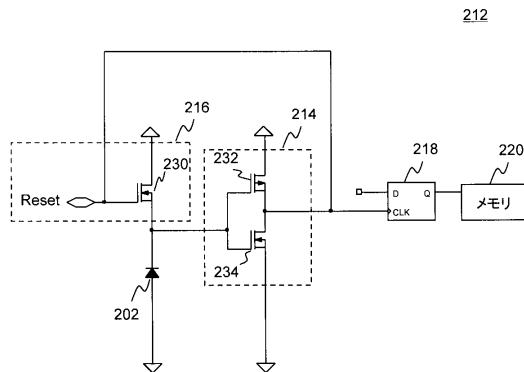

【図2】個別処理部212の構成例を示すブロック図である。

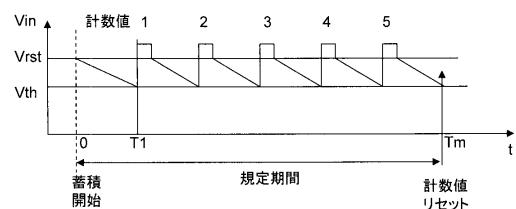

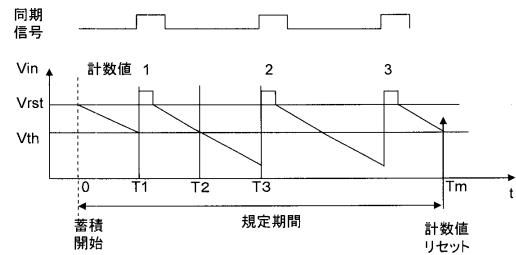

【図3】図2に示した個別処理部212の動作例を示す図である。

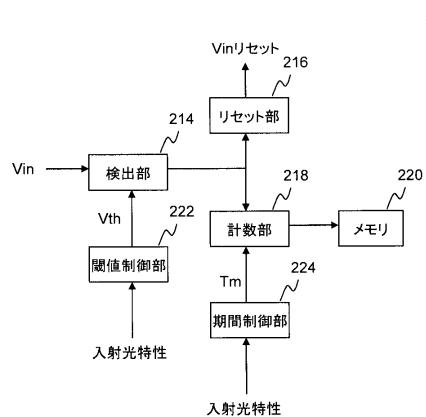

【図4】個別処理部212の他の構成例を示すブロック図である。

【図5】撮像素子100の断面の一例を示す図である。

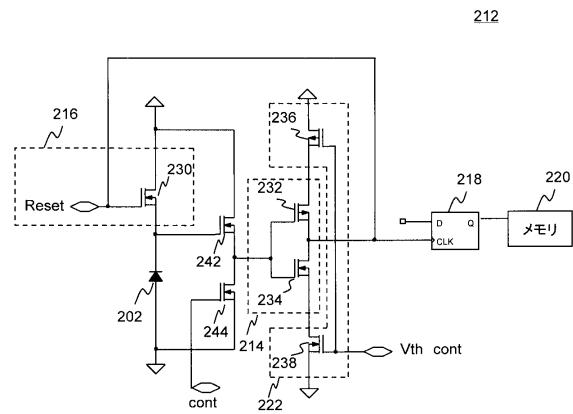

【図6】個別処理部212の回路構成例を示す図である。

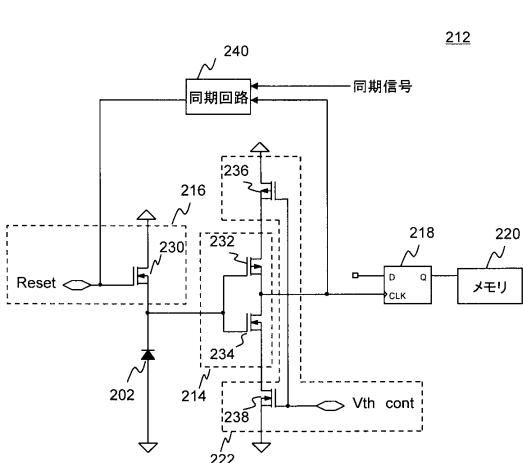

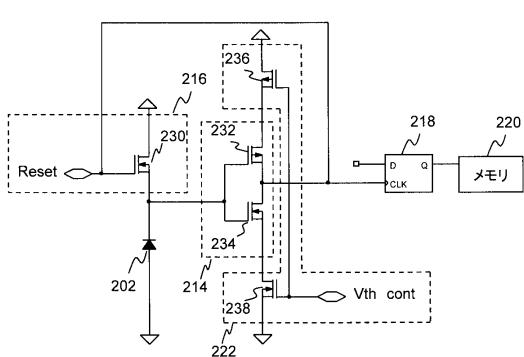

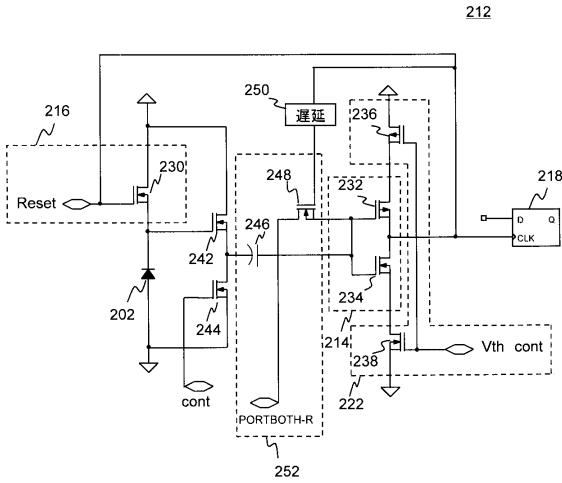

【図7】個別処理部212の他の回路構成例を示す図である。

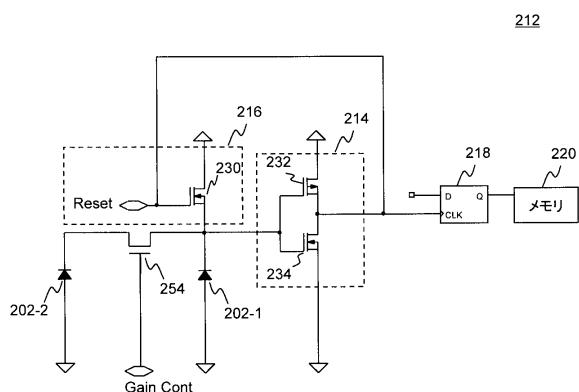

【図8】個別処理部212の他の回路構成例を示す図である。

40

【図9】図8に示した個別処理部212の動作例を示す図である。

【図10】個別処理部212の他の回路構成例を示す図である。

【図11】個別処理部212の他の回路構成例を示す図である。

【図12】個別処理部212の他の回路構成例を示す図である。

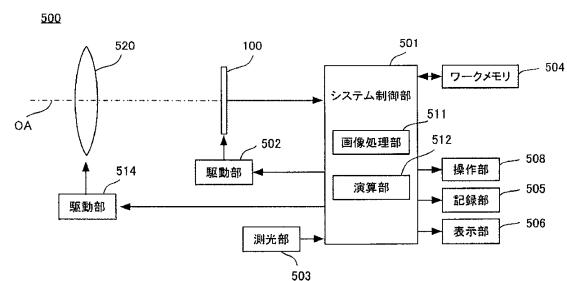

【図13】本発明の実施形態に係る撮像装置500の構成例を示すブロック図である。

**【発明を実施するための形態】****【0008】**

以下、発明の実施の形態を通じて本発明を説明するが、以下の実施形態は特許請求の範囲にかかる発明を限定するものではない。また、実施形態の中で説明されている特徴の組み合わせの全てが発明の解決手段に必須であるとは限らない。

50

## 【0009】

図1は、本発明の実施形態に係る撮像素子100の概要を示す図である。撮像素子100は、被写体からの入射光に応じた画像データを生成する。撮像素子100は、受光部200および信号処理部210を備える。

## 【0010】

受光部200は、複数の光電変換部202を有する。本例の複数の光電変換部202は、行列方向に沿って配列される。それぞれの光電変換部202は、被写体からの入射光に応じて電荷を発生させる。光電変換部202は、フォトダイオード等の光電変換素子を有する。

## 【0011】

信号処理部210は、それぞれの光電変換部202が発生した電荷量に応じた画素信号を生成する。信号処理部210は、複数の個別処理部212を有する。個別処理部212は、光電変換部202毎に設けられる。

## 【0012】

それぞれの個別処理部212は、対応する光電変換部202が発生した電荷量に応じたデジタルの画素信号を生成する。複数の個別処理部212は、複数の光電変換部202が発生したアナログの電荷量を並行して読み出してよい。これにより、グローバルシャッタを実現できる。なお、入射光を電荷に変換する変換領域の面積を広げるべく、個別処理部212の少なくとも一部の構成要素は、光電変換部202とは異なる層に配置されることが好ましい。

## 【0013】

図2は、個別処理部212の構成例を示すブロック図である。本例の個別処理部212は、検出部214、リセット部216、計数部218およびメモリ220を有する。光電変換部202が入射光を受光すると、入射光に応じて電荷が発生する。光電変換部202が発生した電荷は、光電変換部202等に蓄積される。

## 【0014】

検出部214は、対応する光電変換部202における電荷の蓄積量が、予め定められた規定閾値を超えたことを検出する。本例の検出部214には、対応する光電変換部202における電荷の蓄積量を示す蓄積電圧 $V_{in}$ と、当該規定閾値に応じた閾値電圧 $V_{th}$ が入力される。本例の検出部214は、蓄積電圧 $V_{in}$ が閾値電圧 $V_{th}$ より小さくなった場合に、電荷の蓄積量が規定閾値を超えたと判定して検出信号を出力する。

## 【0015】

リセット部216は、対応する光電変換部202における電荷の蓄積量が、当該規定閾値を超えた場合に、対応する光電変換部202における電荷の蓄積量をリセットする。本例のリセット部216は、検出部214から検出信号が入力された場合に、対応する光電変換部202における電荷の蓄積量をリセットする。例えばリセット部216は、対応する光電変換部202が発生した電荷を蓄積している領域を、基準電位に接続することで電荷の蓄積量をリセットする。リセット後においても、光電変換部202が発生する電荷により、電荷の蓄積量は再度増大する。つまり、電荷の蓄積量は、増大およびリセットが繰り返される。

## 【0016】

計数部218は、予め定められた規定期間内に、対応する光電変換部202における電荷の蓄積量が規定閾値を超えた回数を計数する。本例の計数部218は、検出部214から検出信号が入力された回数を計数する。計数部218は、規定期間が終了した時点における計数値に関する情報を、対応する光電変換部202の画素信号としてメモリ220に記憶させる。メモリ220は、複数の個別処理部212に対して一つ設けられてもよい。

## 【0017】

図3は、図2に示した個別処理部212の動作例を示す図である。図3において横軸は時間を示し、縦軸は蓄積電圧 $V_{in}$ の強度を示す。本例において蓄積電圧 $V_{in}$ は、蓄積された電荷量が増加するに従い減少する。

10

20

30

40

50

**【0018】**

対応する光電変換部202に光が入射すると、電荷の蓄積が開始する( $t = 0$ )。光電変換部202が入射光を受光している間、蓄積電圧 $V_{in}$ は、入射光の強度に応じた傾きで減少する。蓄積電圧 $V_{in}$ が閾値電圧 $V_{th}$ 以下になると( $t = T_1$ )、検出部214が検出信号を出力する。

**【0019】**

リセット部216は、当該検出信号に応じて、対応する光電変換部202における電荷の蓄積量をリセットする。これにより、蓄積電圧 $V_{in}$ は、所定の初期電圧にもどる。また、計数部218は、当該検出信号に応じて計数値をインクリメントする。

**【0020】**

リセット部216によるリセット後、所定の時間が経過すると、蓄積電圧 $V_{in}$ は所定のリセット電圧 $V_{rst}$ になる。そして、光電変換部202における入射光の強度に応じて、蓄積電圧 $V_{in}$ が再度減少する。そして、蓄積電圧 $V_{in}$ が閾値電圧 $V_{th}$ 以下になると検出部214が検出信号を出力する。このような動作を、電荷の蓄積開始から、予め定められた規定期間が経過するまで( $t = 0 \sim T_m$ )繰り返す。予め定められた規定期間が経過した時点( $t = T_m$ )で、計数部218は計数値をメモリ220に格納する。また、計数部218は計数値をリセットして、次の画素信号の生成に備える。

**【0021】**

このような動作により、個別処理部212は、対応する光電変換部202が規定期間内に発生した電荷量に応じた画素信号(本例では計数値)を生成することができる。また、個別処理部212を、検出部214、リセット部216および計数部218の簡単な構成で実現できるので、個別処理部212を光電変換部202毎に設けることが容易となる。

**【0022】**

また、閾値電圧 $V_{th}$ を変化させることで、撮像素子100の感度を制御することができる。例えば、閾値電圧 $V_{th}$ とリセット電圧 $V_{rst}$ との差を小さくすると、強度の小さい入射光に対して精度よく画素信号を生成できる。また、閾値電圧 $V_{th}$ とリセット電圧 $V_{rst}$ との差を大きくすると、計数部218におけるオーバーフローを防ぎ、強度の大きい入射光に対して精度よく画素信号を生成できる。

**【0023】**

また、規定期間を変化させることによっても、撮像素子100の感度を制御することができる。規定期間を長くすれば低強度の入射光に対する精度が向上し、規定期間を短くすれば強強度の入射光に対する精度が向上する。このように、本例の撮像素子100は感度の制御が容易であり、入射光の強度を高分解能に再現する画素信号を容易に生成できる。

**【0024】**

また、輝度変化の激しいフリッカー等のある被写体であっても、輝度変化を平均化した画像データを取得することができる。また、光電変換部202等で生じたノイズも平均化することができる。

**【0025】**

また、計数部218は、規定期間内において計数値が所定の値となった時点で、当該計数値をメモリ220に格納し、且つ、計数値をリセットして初期値から計数を再開してよい。メモリ220は、規定期間内において計数部218から受け取った計数値の総和を記憶してよい。これにより、計数部218の計数値がオーバーフローすることを避けることができる。このため、計数部218の規模を小さくすることができる。

**【0026】**

また、規定期間内における入射光量は、閾値電圧 $V_{th}$ とリセット電圧 $V_{rst}$ との差分に、計数値を乗算した値に対応する。メモリ220は、当該乗算値を記憶してよく、計数値および当該電圧の差分を対応付けて記憶してもよい。また、規定期間内における入射光量を規定期間の長さで除算することで、単位時間当たりの入射光量に変換できる。メモリ220は、規定期間の長さを更に記憶してよく、単位時間当たりの入射光量を記憶してもよい。また、リセット電圧 $V_{rst}$ が既知であれば、当該電圧の差分に代えて、閾値電

10

20

30

40

50

圧  $V_{th}$  を記憶してもよい。

**【0027】**

図4は、個別処理部212の他の構成例を示すブロック図である。本例の個別処理部212は、図2に示した個別処理部212の構成に加え、閾値制御部222および期間制御部224を更に備える。

**【0028】**

閾値制御部222は、入射光の特性に応じて、対応する検出部214における規定閾値(本例では閾値電圧  $V_{th}$ )を制御する。入射光の特性とは、例えば入射光の強度である。入射光の強度は、対応する光電変換部202に対する入射光の強度であってよく、複数の光電変換部202に対する入射光の強度の平均であってもよい。閾値制御部222は、

10 対応する蓄積電圧  $V_{in}$  の変化の傾きに基づいて、対応する光電変換部202に対する入射光の強度を算出してよい。

**【0029】**

閾値制御部222は、入射光の強度が小さいほど、閾値電圧  $V_{th}$  とリセット電圧  $V_{rst}$ との差分を小さくしてよい。つまり、閾値制御部222は、入射光の強度が大きいほど、閾値電圧  $V_{th}$  とリセット電圧  $V_{rst}$ との差分を大きくしてよい。このような制御により、入射光の特性に応じて、撮像素子100の感度を制御することができる。また、光電変換部202および個別処理部212を含む画素毎に感度を制御することができる。このため、受光面において入射光の強度の差が大きい場合であっても、それぞれの画素の感度を適切に制御することができる。

20

**【0030】**

また、閾値制御部222は、複数の光電変換部202を複数のブロックに分割して、ブロック毎に独立して閾値電圧  $V_{th}$  を制御してよい。この場合、閾値制御部222は、ブロック内の光電変換部202に対する入射光の強度の平均値を用いて、当該ブロック内の閾値電圧  $V_{th}$  を制御する。

**【0031】**

この場合、閾値制御部222は、各ブロックに一つ設けられてよい。また、各ブロックの範囲は可変であってもよい。例えば、閾値制御部222は、被写体画像のエッジに沿って、複数の光電変換部202を複数のブロックに分割する。画像のエッジとは、隣接する画素における画素信号の強度の差(コントラスト)が予め定められた値以上の領域を指す。

30

**【0032】**

期間制御部224は、入射光の特性に応じて、それぞれの計数部218における規定期間を制御する。ただし、規定期間は、全ての個別処理部212において同一であることが好ましい。つまり、期間制御部224は、全ての光電変換部202における入射光の強度の平均値に基づいて、信号処理部210全体における規定期間を制御することが好ましい。

**【0033】**

期間制御部224は、入射光の強度が小さいほど、規定期間を長くしてよい。つまり、期間制御部224は、入射光の強度が大きいほど、規定期間を短くしてよい。このような制御により、入射光の特性に応じて、撮像素子100の感度を制御することができる。

40

**【0034】**

図5は、撮像素子100の断面の一例を示す図である。本例では、裏面照射型の撮像素子100を示すが、撮像素子100は裏面照射型に限定されない。本例の撮像素子100は、入射光に対応した信号を出力する撮像チップ113と、撮像チップ113からの信号を処理する信号処理チップ111と、信号処理チップ111が処理した画像データを記憶するメモリチップ112とを備える。これら撮像チップ113、信号処理チップ111およびメモリチップ112は積層されており、Cu等の導電性を有するバンプ109により互いに電気的に接続される。

**【0035】**

10

20

30

40

50

なお、撮像チップ113には、複数の光電変換部202が設けられる。信号処理チップ111には、信号処理部210の少なくとも一部の構成が設けられる。例えば信号処理チップ111には、それぞれの個別処理部212における計数部218が設けられる。メモリ220は、メモリチップ112に設けられてよく、信号処理チップ111に設けられてもよい。

#### 【0036】

なお、図示するように、入射光は主に白抜き矢印で示す方向へ入射する。本実施形態においては、撮像チップ113において、入射光が入射する側の面を裏面と称する。撮像チップ113の一例は、裏面照射型のMOSイメージセンサである。撮像チップ113は、受光部200に対応する。PD(フォトダイオード)層106は、配線層108の裏面側に配されている。PD層106は、二次元的に配され、入射光に応じた電荷を蓄積する複数のPD部104、および、PD部104に対応して設けられたトランジスタ105を有する。PD部104は、光電変換部202の一例である。10

#### 【0037】

PD層106における入射光の入射側にはパッシベーション膜103を介してカラーフィルタ102が設けられる。カラーフィルタ102は、互いに異なる波長領域を透過する複数の種類を有しており、PD部104のそれぞれに対応して特定の配列を有している。カラーフィルタ102の配列については後述する。カラーフィルタ102、PD部104および複数のトランジスタ105の組が一つの画素に含まれる。複数のトランジスタ105のオンオフを制御することで、各画素の受光開始タイミング(リセットタイミング)等を制御する。20

#### 【0038】

カラーフィルタ102における入射光の入射側には、それぞれの画素に対応して、マイクロレンズ101が設けられる。マイクロレンズ101は、対応するPD部104へ向けて入射光を集光する。

#### 【0039】

配線層108は、PD層106からの信号を信号処理チップ111に伝送する配線107を有する。配線107は多層であってもよく、また、受動素子および能動素子が設けられてもよい。

#### 【0040】

配線層108の表面には複数のバンプ109が配される。当該複数のバンプ109が信号処理チップ111の対向する面に設けられた複数のバンプ109と位置合わせされて、撮像チップ113と信号処理チップ111とが加圧等されることにより、位置合わせされたバンプ109同士が接合されて、電気的に接続される。30

#### 【0041】

同様に、信号処理チップ111およびメモリチップ112の互いに対向する面には、複数のバンプ109が配される。これらのバンプ109が互いに位置合わせされて、信号処理チップ111とメモリチップ112とが加圧等されることにより、位置合わせされたバンプ109同士が接合されて、電気的に接続される。

#### 【0042】

なお、バンプ109間の接合には、固相拡散によるCuバンプ接合に限らず、はんだ溶融によるマイクロバンプ結合を採用してもよい。また、バンプ109は、一つの単位ブロックに対して一つ程度設ければよい。したがって、バンプ109の大きさは、PD部104のピッチよりも大きくてもよい。また、画素が配列された撮像領域以外の周辺領域において、撮像領域に対応するバンプ109よりも大きなバンプを併せて設けてよい。40

#### 【0043】

信号処理チップ111は、表裏面にそれぞれ設けられた回路を互いに接続するTSV(シリコン貫通電極)110を有する。TSV110は、周辺領域に設けられることが好ましい。また、TSV110は、撮像チップ113の周辺領域、メモリチップ112にも設けられてよい。

**【0044】**

図6は、個別処理部212の回路構成例を示す図である。なお、光電変換部202をあわせて示している。本例の個別処理部212は、検出部214、リセット部216、計数部218およびメモリ220を有する。

**【0045】**

本例の検出部214は、CMOSインバータを有する。CMOSインバータは、PMOSトランジスタ232およびNMOSトランジスタ234を有する。CMOSインバータの入力端子は、光電変換部202の出力端子に接続される。光電変換部202が発生した電荷は、光電変換部202と検出部214との間における寄生容量等に蓄積される。CMOSインバータには、当該蓄積された電荷に応じた蓄積電圧 $V_{in}$ が入力される。

10

**【0046】**

CMOSインバータの出力は、蓄積電圧 $V_{in}$ がCMOSインバータの閾値電圧より小さくなつた場合（すなわち、電荷の蓄積量が規定閾値を超えた場合）に、第1論理値（本例ではL論理）から第2論理値（本例ではH論理）に遷移する。検出部214の出力がL論理からH論理に遷移したエッジが、上述した検出信号として機能する。また、CMOSインバータの閾値電圧が、上述した閾値電圧 $V_{th}$ に相当する。

**【0047】**

リセット部216は、リセットトランジスタ230を有する。リセットトランジスタ230は、ソースおよびドレインが、光電変換部202の出力端子と、所定の高圧側基準電位との間に設けられる。また、リセットトランジスタ230のゲートは、CMOSインバータの出力端子に接続される。リセットトランジスタ230は、CMOSインバータの出力がL論理からH論理に遷移した場合に、光電変換部202と検出部214との間の配線を高圧側基準電位に接続する。これにより、蓄積されていた電荷がリセットされ、検出部214の出力はL論理に遷移する。

20

**【0048】**

計数部218は、規定期間内に、検出部214の出力がL論理からH論理に遷移した回数をカウントする。計数部218は、規定期間が終了した時点の計数值をメモリ220に格納する。このような構成により、小さい回路規模で、個別処理部212を実現できる。

**【0049】**

なお、本例のように、光電変換部202の出力が、検出部214のCMOSインバータの入力端子に直接接続される場合、検出部214は撮像チップ113に設けられることが好ましい。直接接続されると、例えば、光電変換部202の出力と、CMOSインバータの入力端子との間にトランジスタまたはバッファ等の電荷の移動を遮断する素子がない状態を指す。これにより、光電変換部202と検出部214との間の寄生容量が大きくなりすぎるのを防ぐことができる。このため、撮像素子100の感度が低下することを防ぐことができる。

30

**【0050】**

図7は、個別処理部212の他の回路構成例を示す図である。本例の個別処理部212は、図6に示した個別処理部212の構成に加え、閾値制御部222を更に備える。閾値制御部222は、CMOSインバータの各MOSトランジスタに対して設けられる閾値制御トランジスタ236および閾値制御トランジスタ238を有する。

40

**【0051】**

閾値制御トランジスタ236、238は、それぞれ対応するPMOSトランジスタ232、NMOSトランジスタ234のソースに接続され、CMOSインバータの閾値を制御する。閾値制御トランジスタ236は、ソースおよびドレインが、高圧側基準電位とPMOSトランジスタ232のソースとの間に接続されるPMOSトランジスタである。また、閾値制御トランジスタ238は、ソースおよびドレインが、低圧側基準電位とNMOSトランジスタ234のソースとの間に接続されるNMOSトランジスタである。

**【0052】**

閾値制御トランジスタ236および閾値制御トランジスタ238のゲートには、閾値制

50

御信号  $V_{th\_cont}$  が入力される。このような構成により、検出部 214 における CMOS トランジスタの閾値電圧を、閾値制御信号  $V_{th\_cont}$  により制御することができる。上述したように、閾値制御部 222 は、入射光の特性値に応じて閾値制御信号  $V_{th\_cont}$  を生成してよい。

#### 【0053】

なお、本例の検出部 214 は、撮像チップ 113 に設けられることが好ましい。閾値制御トランジスタ 236 および閾値制御トランジスタ 238 は、撮像チップ 113 に設けられてよく、信号処理チップ 111 に設けられてもよい。

#### 【0054】

図 8 は、個別処理部 212 の他の回路構成例を示す図である。本例の個別処理部 212 は、図 6 または図 7 に示したいずれかの個別処理部 212 の構成に加え、同期回路 240 を更に有する。図 8 では、図 7 に示した個別処理部 212 の構成に、同期回路 240 を追加した構成を示す。10

#### 【0055】

同期回路 240 は、検出部 214 の出力端子と、リセットトランジスタ 230 のゲートとの間に設けられる。同期回路 240 は、検出部 214 が出力する検出信号と、同期信号とを受け取る。同期信号は、同期回路 240 に対して予め定められた周期で入力される。

#### 【0056】

同期回路 240 は、同期信号を受け取っている間に、CMOS インバータが H 論理を出力したことを条件として、リセット部 216 に電荷の蓄積量をリセットさせる。これにより、規定期間内に蓄積量がリセットされる回数の上限は、規定期間内における同期信号の回数に制限される。このため、計数部 218 における計数値のオーバーフローを防ぐことができる。規定期間内において、同期回路 240 に同期信号が入力される回数は、計数部 218 における計数値の上限値と同一であってよい。なお、同期回路 240 は、信号処理チップ 111 に設けられてよい。20

#### 【0057】

図 9 は、図 8 に示した個別処理部 212 の動作例を示す図である。本例における個別処理部 212 の動作は、検出部 214 が H 論理を出力し、且つ、H 論理の同期信号が同期回路 240 に入力されている場合に限り、リセット部 216 が電荷蓄積量をリセットする点を除き、図 3 に示した動作と同一である。30

#### 【0058】

$t = T_1$ において、図 3 と同様に、検出部 214 の出力が L 論理から H 論理に遷移する。このとき、図 9 の例では、H 論理の同期信号が同期回路 240 に入力されているので、蓄積電圧  $V_{in}$  はリセットされる。また、 $t = T_2$ においても、検出部 214 の出力が L 論理から H 論理に遷移するが、図 9 の例では、H 論理の同期信号が同期回路 240 に入力されていないので、 $t = T_2$  のタイミングでは蓄積電圧  $V_{in}$  はリセットされない。このため、検出部 214 の出力は H 論理に維持される。

#### 【0059】

$t = T_3$  のタイミングで、H 論理の同期信号が入力される。このとき、検出部 214 の出力は H 論理なので、リセット部 216 は、蓄積電圧  $V_{in}$  をリセットする。このような動作により、計数部 218 における計数タイミングを、同期信号の周期で制御することができる。40

#### 【0060】

撮像素子 100 は、同期信号の周期を、入射光の強度等の特性値に応じて制御してよい。例えば、入射光の強度がより小さい場合には、同期信号の周期をより小さく（つまり、規定期間内における同期信号の個数を多く）する。入射光の強度がより大きい場合には、同期信号の周期をより大きくする。このような制御によっても、撮像素子 100 の感度を制御することができる。同期信号の周期は、個別処理部 212 毎に独立に制御されてよい。また、同期信号の周期は、画素のブロック毎に制御されてもよい。

#### 【0061】

10

20

30

40

50

図10は、個別処理部212の他の回路構成例を示す図である。本例の個別処理部212は、図6から図9において説明したいずれかの個別処理部212の構成に加え、ソースフォロワ回路242およびトランジスタ244を更に有する。図10においては、図7に示した個別処理部212の構成に、ソースフォロワ回路242およびトランジスタ244を追加した例を示す。

#### 【0062】

ソースフォロワ回路242は、光電変換部202の出力端子と、検出部214のCMOSインバータの入力端子との間に配置される。本例のソースフォロワ回路242は、光電変換部202の出力端子がゲートに接続されるN MOSトランジスタを有する。光電変換部202が発生した電荷は、光電変換部202およびソースフォロワ回路242の間の寄生容量に蓄積される。ソースフォロワ回路242は、蓄積された電荷量に応じた蓄積電圧を、CMOSインバータに入力する。10

#### 【0063】

また、トランジスタ244は、低圧側基準電位と、検出部214のCMOSインバータの入力端子との間に配置される。トランジスタ244は、制御信号contに応じて、CMOSインバータの入力端子を低圧側基準電位に接続するか否かを切り替える。

#### 【0064】

本例では、検出部214のCMOSインバータは、信号処理チップ111に設けられる。ソースフォロワ回路242は、撮像チップ113に設けられる。トランジスタ244は、信号処理チップ111に設けられてよい。これにより、撮像チップ113に設けるトランジスタの数を低減でき、光電変換部202の面積を大きくすることができる。20

#### 【0065】

図11は、個別処理部212の他の回路構成例を示す図である。本例の個別処理部212は、図6から図10において説明したいずれかの個別処理部212の構成に加え、遅延部250およびクランプ部252を更に有する。図11においては、図10に示した個別処理部212の構成に、遅延部250およびクランプ部252を追加した例を示す。

#### 【0066】

遅延部250は、検出部214のCMOSインバータからリセット部216に入力される検出信号を分岐して受け取り、当該検出信号を遅延させたクランプ信号を生成する。遅延部250における遅延量は、リセット部216が蓄積電圧V<sub>in</sub>をリセットしてから、蓄積電圧V<sub>in</sub>が所定のリセット電圧V<sub>rst</sub>より小さくなるまでの期間に対応する。当該遅延量は、リセット部216が蓄積電圧V<sub>in</sub>をリセットしてから、蓄積電圧V<sub>in</sub>がフィードスルー電圧となるまでの期間に対応してよい。30

#### 【0067】

クランプ部252は、ソースフォロワ回路242が出力する信号の電圧（蓄積電圧V<sub>in</sub>）を、クランプ信号のタイミングでクランプする。つまり、クランプ部252は、リセット部216が蓄積電圧V<sub>in</sub>をリセットした後に、所定のリセット電圧V<sub>rst</sub>より小さくなった蓄積電圧V<sub>in</sub>をクランプしたクランプ電圧を保持する。

#### 【0068】

クランプ部252は、クランプ信号のタイミングより後における蓄積電圧V<sub>in</sub>とクランプ電圧との差分を、検出部214におけるCMOSインバータに入力する。このような動作により、CMOSインバータには、クランプ電圧を基準とした蓄積電圧V<sub>in</sub>が入力されるので、ソースフォロワ回路242におけるオフセットおよびノイズ等の影響を低減することができる。40

#### 【0069】

本例のクランプ部252は、クランプコンデンサ246およびクランプトランジスタ248を有する。クランプコンデンサ246は、ソースフォロワ回路242の出力端子およびCMOSインバータの入力端子の間に設けられる。クランプトランジスタ248は、クランプ信号がゲートに入力された場合に、CMOSインバータの入力端子側のクランプコンデンサ246の電極を、所定電位PORTBOTH-Rに接続する。これにより、クラ50

ンプコンデンサ 246 は、クランプ信号のタイミングにおける蓄積電圧  $V_{in}$  の電圧をクランプする。

【0070】

このような構成により、規定期間内で繰り返される蓄積電圧  $V_{in}$  の波形のそれぞれにおいて、ノイズ等の影響を低減することができる。なお、本例における遅延部 250 およびクランプ部 252 は、信号処理チップ 111 に設けられてよい。ただし、クランプコンデンサ 246 は、撮像チップ 113 に設けられてもよい。

【0071】

図 12 は、個別処理部 212 の他の回路構成例を示す図である。本例の個別処理部 212 は、図 6 から図 11 において説明したいずれかの個別処理部 212 の構成に加え、容量切替部 254 を更に有する。図 12 においては、図 6 に示した個別処理部 212 の構成に、容量切替部 254 を追加した例を示す。

【0072】

容量切替部 254 は、個別処理部 212 に対応する光電変換部 202-1 の出力端子に接続される電荷検出容量の大きさを切り替える。本例において電荷検出容量は、光電変換部 202-1 の出力端子に接続される寄生容量である。

【0073】

本例の容量切替部 254 は、ゲイン制御信号 Gain Cont に応じて、光電変換部 202-1 の出力端子と、他の光電変換部 202-2 の出力端子とを接続するか否かを切り替えるスイッチである。なお、光電変換部 202-1 および光電変換部 202-2 のそれぞれに対して個別処理部 212 が設けられるが、図 12 においては、光電変換部 202-2 に対応する個別処理部 212 を省略している。ただし、容量切替部 254 は、光電変換部 202-1 および光電変換部 202-2 に対して共通に設けられる。

【0074】

容量切替部 254 がオン状態になると、光電変換部 202-1 の出力端子には、光電変換部 202-2 に対する寄生容量も接続される。このため、容量切替部 254 がオン状態になると、容量切替部 254 がオフ状態のときに比べて、光電変換部 202-1 の出力端子に接続される寄生容量の大きさは 2 倍となる。

【0075】

このように、容量切替部 254 により、光電変換部 202-1 に対する寄生容量の大きさを切り替えることができ、当該画素における入射光量に対する画素信号のゲイン（すなわち感度）を切り替えることができる。なお、容量切替部 254 は、光電変換部 202-1 に接続する他の光電変換部 202 の個数を可変に制御してもよい。これにより、より多様なゲインを実現することができる。

【0076】

図 13 は、本発明の実施形態に係る撮像装置 500 の構成例を示すブロック図である。撮像装置 500 は、撮影光学系としての撮影レンズ 520 を備え、撮影レンズ 520 は、光軸 OA に沿って入射する被写体光束を撮像素子 100 へ導く。撮影レンズ 520 は、撮像装置 500 に対して着脱できる交換式レンズであっても構わない。撮像装置 500 は、撮像素子 100、システム制御部 501、駆動部 502、測光部 503、ワークメモリ 504、記録部 505、表示部 506 および駆動部 514 を主に備える。

【0077】

撮影レンズ 520 は、複数の光学レンズ群から構成され、シーンからの被写体光束をその焦点面近傍に結像させる。なお、図 13 では瞳近傍に配置された仮想的な 1 枚のレンズで当該撮影レンズ 520 を代表して表している。

【0078】

駆動部 514 は撮影レンズ 520 を駆動する。より具体的には駆動部 514 は撮影レンズ 520 の光学レンズ群を移動させて合焦位置を変更する。また、撮影レンズ 520 内の虹彩絞りを駆動して撮像素子 100 へ入射する被写体光束の光量を制御する。

【0079】

10

20

30

40

50

駆動部 502 は、システム制御部 501 からの指示に従って撮像素子 100 のタイミング制御、領域制御等の電荷蓄積制御を実行する制御回路である。駆動部 502 は、撮像素子 100 の受光部 200 および信号処理部 210 を、図 1 から図 12 に関連して説明したように動作させる。また、操作部 508 はリリーズボタン等により撮像者からの指示を受け付ける。

#### 【0080】

撮像素子 100 は、図 1 から図 12 に関連して説明した撮像素子 100 と同一である。撮像素子 100 は、画素信号をシステム制御部 501 の画像処理部 511 へ引き渡す。画像処理部 511 は、ワークメモリ 504 をワークスペースとして種々の画像処理を施した画像データを生成する。例えば、JPEG ファイル形式の画像データを生成する場合は、ベイダー配列で得られた信号からカラー映像信号を生成した後に圧縮処理を実行する。生成された画像データは、記録部 505 に記録されるとともに、表示信号に変換されて予め設定された時間の間、表示部 506 に表示される。10

#### 【0081】

測光部 503 は、画像データを生成する一連の撮影シーケンスに先立ち、シーンの輝度分布を検出する。測光部 503 は、例えば 100 万画素程度の AE センサを含む。システム制御部 501 の演算部 512 は、測光部 503 の出力を受けてシーンの領域ごとの輝度を算出する。

#### 【0082】

演算部 512 は、算出した輝度分布に従ってシャッタ速度、絞り値、ISO 感度を決定する。測光部 503 は撮像素子 100 で兼用してもよい。なお、演算部 512 は、撮像装置 500 を動作させるための各種演算も実行する。駆動部 502 は、一部または全部が撮像素子 100 に搭載されてよい。システム制御部 501 の一部が撮像素子 100 に搭載されてもよい。20

#### 【0083】

以上、本発明を実施の形態を用いて説明したが、本発明の技術的範囲は上記実施の形態に記載の範囲には限定されない。上記実施の形態に、多様な変更または改良を加えることが可能であることが当業者に明らかである。その様な変更または改良を加えた形態も本発明の技術的範囲に含まれ得ることが、特許請求の範囲の記載から明らかである。

#### 【0084】

特許請求の範囲、明細書、および図面中において示した装置、システム、プログラム、および方法における動作、手順、ステップ、および段階等の各処理の実行順序は、特段「より前に」、「先立って」等と明示しておらず、また、前の処理の出力を後の処理で用いるのでない限り、任意の順序で実現しうることに留意すべきである。特許請求の範囲、明細書、および図面中の動作フローに関して、便宜上「まず、」、「次に、」等を用いて説明したとしても、この順で実施することが必須であることを意味するものではない。30

#### 【符号の説明】

#### 【0085】

100 撮像素子、101 マイクロレンズ、102 カラーフィルタ、103 パッジベーション膜、104 PD 部、105 トランジスタ、106 PD 層、107 配線、108 配線層、109 バンプ、110 TSV、111 信号処理チップ、112 メモリチップ、113 撮像チップ、200 受光部、202 光電変換部、210

信号処理部、212 個別処理部、214 検出部、216 リセット部、218 計数部、220 メモリ、222 閾値制御部、224 期間制御部、230 リセットトランジスタ、232 PMOS トランジスタ、234 NMOS トランジスタ、236

閾値制御トランジスタ、238 閾値制御トランジスタ、240 同期回路、242 ソースフォロワ回路、244 トランジスタ、246 クランプコンデンサ、248 クランプトランジスタ、250 遅延部、252 クランプ部、254 容量切替部、500

撮像装置、501 システム制御部、502 駆動部、503 測光部、504 ワークメモリ、505 記録部、506 表示部、508 操作部、511 画像処理部、5

40

50

## 12 演算部、514 駆動部、520 撮影レンズ

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図8】

【図7】

【図 9】

【図 10】

【図 11】

【図 12】

【図 13】

---

フロントページの続き

(56)参考文献 特開2001-054022(JP,A)

特開平07-067043(JP,A)

特開2008-125074(JP,A)

特開2011-071958(JP,A)

特開2009-239442(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/225-5/378

H04N 9/00-9/11

H01L 27/146