(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6265120号

(P6265120)

(45) 発行日 平成30年1月24日(2018.1.24)

(24) 登録日 平成30年1月5日(2018.1.5)

(51) Int.Cl.

F 1

**HO4N 5/3745 (2011.01)**

**HO4N 5/378 (2011.01)**

**HO4N 5/369 (2011.01)**

**HO1L 27/146 (2006.01)**

HO 4 N 5/3745 500

HO 4 N 5/378

HO 4 N 5/369

HO 1 L 27/146 A

請求項の数 11 (全 16 頁)

(21) 出願番号 特願2014-519841 (P2014-519841)

(86) (22) 出願日 平成25年6月5日 (2013.6.5)

(86) 国際出願番号 PCT/JP2013/003533

(87) 国際公開番号 WO2013/183291

(87) 国際公開日 平成25年12月12日 (2013.12.12)

審査請求日 平成28年5月31日 (2016.5.31)

(31) 優先権主張番号 特願2012-131232 (P2012-131232)

(32) 優先日 平成24年6月8日 (2012.6.8)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000004112

株式会社ニコン

東京都港区港南二丁目15番3号

(74) 代理人 110000877

龍華国際特許業務法人

(72) 発明者 村田 寛信

東京都千代田区有楽町一丁目12番1号

株式会社ニコン内

審査官 松永 隆志

最終頁に続く

(54) 【発明の名称】撮像素子および撮像装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の画素を含む第1撮像領域と、前記第1撮像領域に対して第1の方向に配置された複数の画素を含む第2撮像領域と、前記第1撮像領域に対して前記第1の方向と交差する第2の方向に配置された複数の画素を含む第3撮像領域とを有する画素部と、前記複数の画素からの信号の読み出しを制御する制御信号を前記撮像領域毎に供給可能な制御部と、

前記複数の信号処理回路を有し、前記撮像領域毎に供給された前記制御信号により読み出された前記撮像領域の複数の画素からの信号を、前記複数の信号処理回路の異なる信号処理回路で信号処理する、前記画素部に積層された信号処理部と

を備え、

前記第1撮像領域の第1画素からの信号と前記第2撮像領域の第2画素からの信号とは第1信号処理回路で信号処理され、

前記第1撮像領域の第3画素からの信号と前記第2撮像領域の第4画素からの信号とは第2信号処理回路で信号処理される

撮像素子。

## 【請求項 2】

前記画素部の下に前記信号処理部が積層され、

前記第1撮像領域に対応した前記画素部の下の位置に、前記第1信号処理回路が配置され、

10

20

前記第2撮像領域に対応した前記画素部の下の位置に、前記第2信号処理回路が配置される

請求項1に記載の撮像素子。

【請求項3】

前記複数の信号処理回路は、入力された信号をデジタル信号に変換するA/Dコンバータである

請求項1に記載の撮像素子。

【請求項4】

前記画素部と前記信号処理部とは複数のバンプにより接続され、

前記撮像領域毎に前記複数のバンプが配置されている

請求項1から3のいずれか一項に記載の撮像素子。

【請求項5】

前記複数のバンプは、前記第1の方向と前記第2の方向とにおいて等間隔に配置されている

請求項4に記載の撮像素子。

【請求項6】

複数の画素を含む第1撮像領域と、前記第1撮像領域に対して第1の方向に配置された複数の画素を含む第2撮像領域と、前記第1撮像領域に対して前記第1の方向と交差する第2の方向に配置された複数の画素を含む第3撮像領域と、前記複数の画素からの信号の読み出しを制御する制御信号を前記撮像領域毎に供給可能な制御部と、を有する撮像チップと、

一つ又は複数の画素列毎または一つ又は複数の画素行毎に設けられ、画素から出力される画素信号を信号処理する複数の素子を有し、前記撮像領域毎に供給された前記制御信号により読み出された前記撮像領域の複数の画素からの信号を、前記信号処理する複数の素子の異なる素子で信号処理し、前記撮像チップに積層された信号処理チップとを備え、

前記第1撮像領域の第1画素からの信号と前記第2撮像領域の第2画素からの信号とは第1の信号処理する素子で信号処理され、

前記第1撮像領域の第3画素からの信号と前記第2撮像領域の第4画素からの信号とは第2の信号処理する素子で信号処理される撮像素子。

【請求項7】

前記撮像チップの下に前記信号処理する素子が積層され、

前記第1撮像領域に対応した前記撮像チップの下の位置に、前記第1の信号処理する素子が配置され、

前記第2撮像領域に対応した前記撮像チップの下の位置に、前記第2の信号処理する素子が配置される

請求項6に記載の撮像素子。

【請求項8】

前記信号処理する素子は、前記画素から出力される画素信号をデジタル信号に変換するA/Dコンバータである

請求項6に記載の撮像素子。

【請求項9】

前記撮像チップと前記信号処理する素子とは複数のバンプにより接続され、

前記撮像領域毎に前記複数のバンプが配置されている

請求項6から8のいずれか一項に記載の撮像素子。

【請求項10】

前記複数のバンプは、前記第1の方向と前記第2の方向とにおいて等間隔に配置されている

請求項9に記載の撮像素子。

【請求項11】

10

20

30

40

50

請求項 1 から 10 のいずれか一項に記載の撮像素子を備える電子機器。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、撮像素子および撮像装置に関する。

【背景技術】

【0002】

従来、列並列型 A / D コンバータ（単に A D C と称する）を備えたイメージセンサが知られている。また、信号処理チップを積層したイメージセンサにおいては、ブロック並列型 A D C が提案されている（例えば、非特許文献 1 参照）。 10

[非特許文献 1] "A Very Low Area ADC for 3-D Stacked CMOS Image Processing System" K. Kiyoyama 他, IEEE 3DIC 2012.

【発明の概要】

【発明が解決しようとする課題】

【0003】

列並列型 A D C は、画素列毎に A D C を設け、選択した行の各画素の画素信号を、各 A D C で並列に読み出す。しかし、従来の列並列型 A D C は、有効画素領域と同一面（例えば有効画素領域の列方向における上下）に形成されるので、撮像素子の面積が増大してしまう。また、複数行を並列・高速処理する場合には、有効画素領域内に配線を引き回さなければならない。また、複数行を並列・高速処理する場合には A D C が大型化して、撮像素子の面積が更に増大してしまう。 20

【0004】

一方、ブロック並列型 A D C は、有効画素のブロック毎（例えば 10 画素 × 10 画素のブロック毎）に A D C を設ける。しかし、ブロック内の各画素を一つの A D C で読み出すには、複雑な制御線を用いる、または、撮像チップ側に制御用トランジスタを配置する等の工夫が必要になる。また、ブロック毎の A D C はそれぞれ独立に動作する。このため、A D C による発熱も独立に生じてしまい、信号処理チップが局所的に発熱する場合がある。信号処理チップにおける局所的な発熱は、積層された撮像チップに伝達して、撮像チップの動作に影響を与えることが考えられる。 30

【課題を解決するための手段】

【0005】

本発明の第 1 の態様においては、複数の画素が行列状に配置された撮像チップと、一つ又は複数の画素列毎または一つ又は複数の画素行毎に設けられ、画素から出力される画素信号を信号処理する素子を有し、撮像チップに積層された信号処理チップとを備える撮像素子が提供される。

【0006】

本発明の第 2 の態様においては、上記撮像素子を用いた撮像装置が提供される。

【0007】

なお、上記の発明の概要は、本発明の必要な特徴の全てを列挙したものではない。また、これらの特徴群のサブコンビネーションもまた、発明となりうる。 40

【図面の簡単な説明】

【0008】

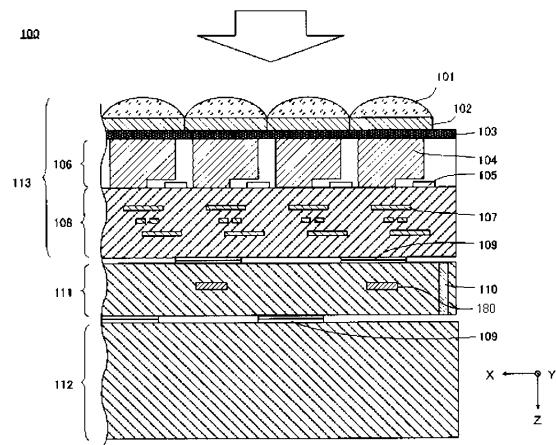

【図 1】本実施形態に係る撮像素子 100 の断面図である。

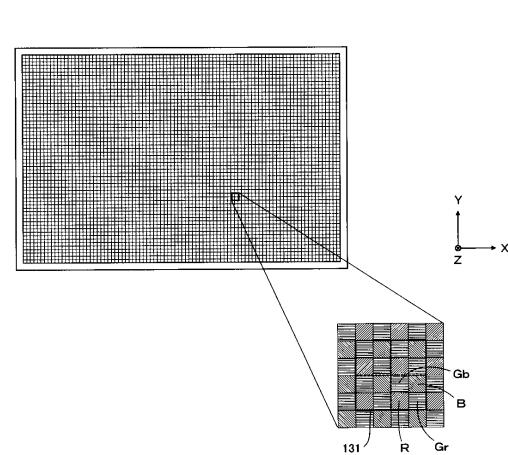

【図 2】撮像チップ 113 の画素配列と単位グループ 131 を説明する図である。

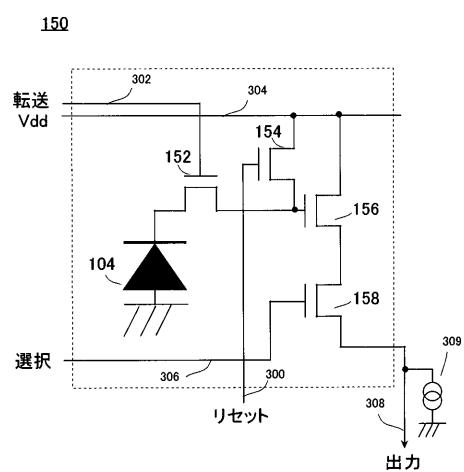

【図 3】画素 150 の等価回路図を示す。

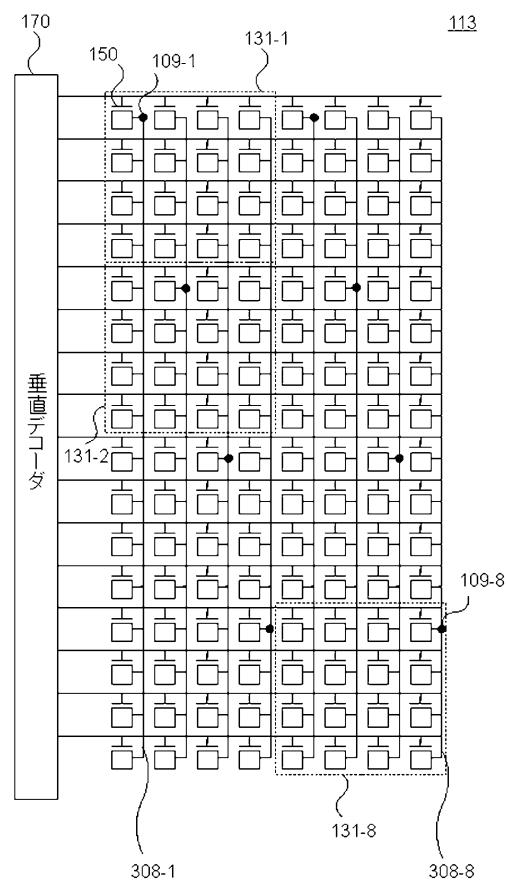

【図 4】撮像チップ 113 における複数の画素 150 およびバンプ 109 の配置例を示す図である。

【図 5】信号処理チップ 111 の A D C 配置面に配置される複数の A D C 180 を示す図である。

【図 6】撮像チップ 113 における複数の画素 150 およびバンプ 109 の他の配置例を 50

示す図である。

【図7】撮像チップ113における複数の画素150およびTSV120の配置例を示す図である。

【図8】信号処理チップ111のADC配置面に配置される複数のADC180およびTSV120を示す図である。

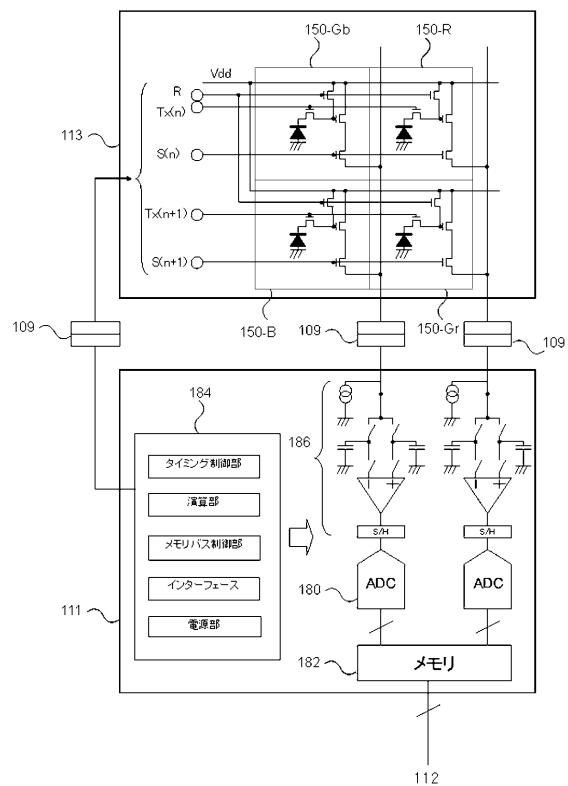

【図9】アナログCDS回路186を有する信号処理チップ111の概要を、撮像チップ113と合わせて示す図である。

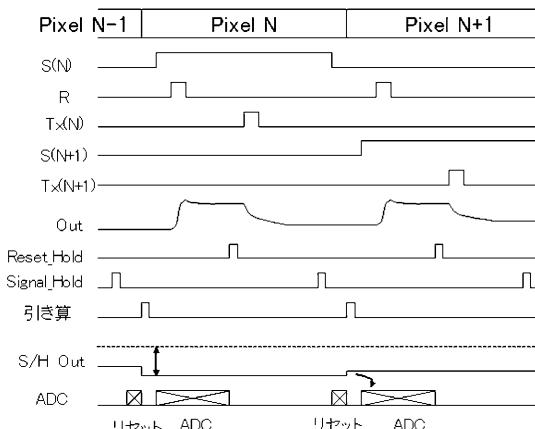

【図10】アナログCDS回路186を有する信号処理チップ111の動作例を示すタイミングチャートである。

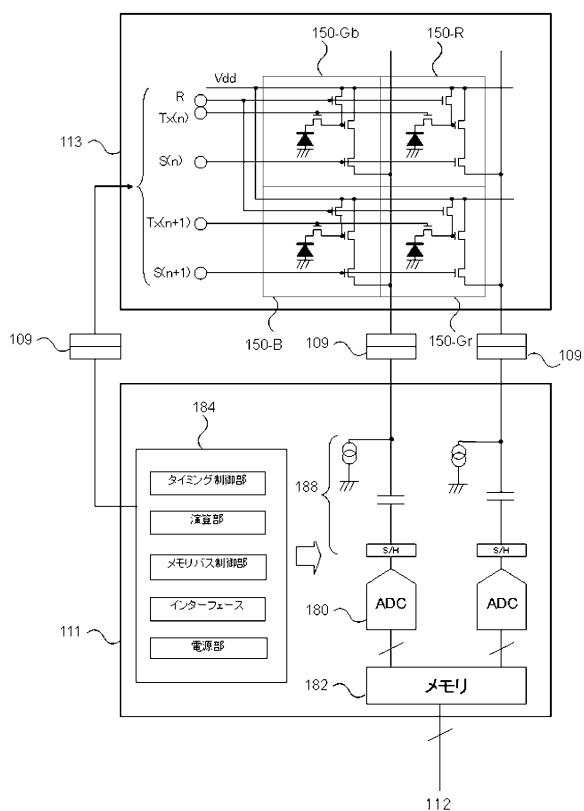

【図11】DDDS回路188を有する信号処理チップ111の概要を、撮像チップ113と合わせて示す図である。 10

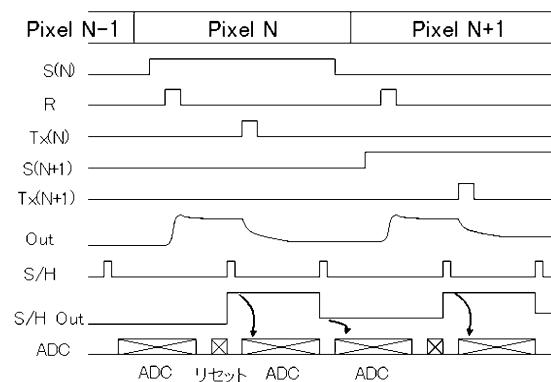

【図12】DDDS回路188を有する信号処理チップ111の動作例を示すタイミングチャートである。

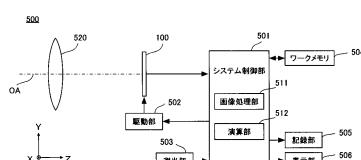

【図13】本実施形態に係る撮像装置500の構成を示すブロック図である。

【発明を実施するための形態】

【0009】

以下、発明の実施の形態を通じて本発明を説明するが、以下の実施形態は請求の範囲にかかる発明を限定するものではない。また、実施形態の中で説明されている特徴の組み合わせの全てが発明の解決手段に必須であるとは限らない。

【0010】 20

図1は、本実施形態に係る撮像素子100の断面図である。本例では、いわゆる裏面照射型の撮像素子100を示すが、撮像素子100は裏面照射型に限定されず、表面照射型であってもよい。撮像素子100は、撮像チップ113に積層された積層チップを備える構造であればよい。

【0011】

本例の撮像素子100は、入射光に対応した画素信号を出力する撮像チップと113と、画素信号を処理する信号処理チップ111と、画素信号を記憶するメモリチップ112とを備える。これら撮像チップ113、信号処理チップ111およびメモリチップ112は積層されており、Cu等の導電性を有する複数のバンプ109により互いに電気的に接続される。本例では、信号処理チップ111およびメモリチップ112が、上述した積層チップに相当する。 30

【0012】

なお、図示するように、入射光は主に白抜き矢印で示すZ軸プラス方向へ向かって入射する。本実施形態においては、撮像チップ113において、入射光が入射する側の面を裏面と称する。また、座標軸に示すように、Z軸に直交する紙面右方向をX軸プラス方向、Z軸およびX軸に直交する紙面手前方向をY軸プラス方向とする。以降のいくつかの図においては、図1の座標軸を基準として、それぞれの図の向きがわかるように座標軸を表示する。

【0013】

撮像チップ113の一例は、裏面照射型のMOSイメージセンサである。PD層106は、配線層108の裏面側に配されている。PD層106は、光に応じた電荷を生成する複数の光電変換部を有する。撮像チップ113は、当該電荷に応じた画素信号を出力する。本例のPD層106は、二次元的に配された複数のPD(フォトダイオード)104、および、PD104に対応して設けられたトランジスタ105を有する。PD104は、光電変換部の一例である。 40

【0014】

PD層106における入射光の入射側にはパッシベーション膜103を介してカラーフィルタ102が設けられる。カラーフィルタ102は、互いに異なる波長領域を透過する複数の種類を有しており、PD104のそれぞれに対応して特定の配列を有している。カラーフィルタ102の配列については後述する。カラーフィルタ102、PD104およ 50

びトランジスタ 105 の組が一つの画素を形成する。

【0015】

カラーフィルタ 102 における入射光の入射側には、それぞれの画素に対応して、マイクロレンズ 101 が設けられる。マイクロレンズ 101 は、対応する P D 104 へ向けて入射光を集光する。

【0016】

配線層 108 は、P D 層 106 からの画素信号を信号処理チップ 111 に伝送する配線 107 を有する。配線 107 は多層であってもよく、また、受動素子および能動素子が設けられてもよい。

【0017】

配線層 108 の表面には複数のバンプ 109 が配される。当該複数のバンプ 109 が信号処理チップ 111 の対向する面に設けられた複数のバンプ 109 と位置合わせされて、撮像チップ 113 と信号処理チップ 111 とが加圧等されることにより、位置合わせされたバンプ 109 同士が接合されて、電気的に接続される。

【0018】

同様に、信号処理チップ 111 およびメモリチップ 112 の互いに対向する面には、複数のバンプ 109 が配される。これらのバンプ 109 が互いに位置合わせされて、信号処理チップ 111 とメモリチップ 112 とが加圧等されることにより、位置合わせされたバンプ 109 同士が接合されて、電気的に接続される。

【0019】

なお、バンプ 109 間の接合には、固相拡散による Cu バンプ接合に限らず、はんだ溶融によるマイクロバンプ結合を採用してもよい。また、バンプ 109 は、例えば後述する一つの出力配線に対して一つ設けてよく、複数設けてもよい。バンプ 109 の大きさは、P D 104 のピッチよりも大きくてもよい。また、画素が配列された画素領域以外の周辺領域において、画素領域に対応するバンプ 109 よりも大きなバンプを併せて設けてよい。

【0020】

信号処理チップ 111 は、撮像チップ 113 が output するアナログの画素信号を受け取る。信号処理チップ 111 は、受け取った画素信号に対して所定の信号処理を行い、メモリチップ 112 に出力する。メモリチップ 112 は、信号処理チップ 111 から受け取る信号を保存する。

【0021】

信号処理チップ 111 は、画素から出力される画素信号を信号処理する複数の素子を有する。本例の信号処理チップ 111 は、当該複数の素子の一例として複数の A D C 180 を有する。当該複数の素子は、演算回路等のように、A D C 180 とは異なる素子であってもよい。それぞれの A D C 180 は、撮像チップ 113 が output するアナログの画素信号を、デジタル信号に変換する。信号処理チップ 111 は、当該デジタル信号に対して、補正等の所定の演算を行ってよい。

【0022】

複数の A D C 180 の少なくとも一部は、複数の画素が設けられた面と平行な A D C 配置面において、二次元に配置される。例えば、撮像チップ 113 において複数の画素が行方向および列方向に沿って二次元に配置されており、信号処理チップ 111 において複数の A D C 180 が行方向および列方向に沿って二次元に配置される。複数の A D C 180 は、信号処理チップ 111 において等間隔に配置されることが好ましい。

【0023】

また、A D C 配置面に配置された複数の A D C 180 のうちの少なくとも二以上の A D C 180 は並列制御され、並列動作する。並列動作とは、複数の A D C 180 におけるアナログ - デジタル変換処理が、略同時に行われることを指す。これにより、当該二以上の A D C 180 が略同時に発熱することとなり、複数の A D C 180 が独立に動く場合に比べて、温度分布のばらつきを低減することができる。なお、A D C 配置面に配置された複

10

20

30

40

50

数のADC180の全てが略同時に動作することが好ましい。これにより、ADC180の発熱による温度分布を均等にすることができる。また、複数のADC180は、信号処理チップ111のADC配置面において、不均一に配置されてもよい。例えば複数のADC180は、信号処理チップ111のADC配置面の中央よりも、端部のほうが密度が高くなるように配置されてもよい。

#### 【0024】

また、複数のADC180は、信号処理チップ111において、Z軸方向における位置が異なる複数のADC配置面に配置されてもよい。つまり、信号処理チップ111は多層チップであり、複数のADC180は、異なる層に設けられてよい。この場合においても、複数のADC180が配置された位置を、単一のADC配置面に投影した場合に、それぞれのADC180が等間隔に配置されることが好ましい。

10

#### 【0025】

また、信号処理チップ111は、表裏面にそれぞれ設けられた回路を互いに接続するTSV（シリコン貫通電極）110を有する。TSV110は、周辺領域に設けられることが好ましい。また、TSV110は、撮像チップ113の周辺領域、メモリチップ112にも設けられてよい。

#### 【0026】

図2は、撮像チップ113の画素配列と単位グループ131を説明する図である。特に、撮像チップ113を裏面側から観察した様子を示す。画素領域には画素が行方向および列方向に沿ってマトリックス状に配列されている。本例では、x軸方向を行方向とし、y軸方向を列方向とする。本実施形態においては、隣接する4画素×4画素の16画素が一つのグループを形成する。図の格子線は、隣接する画素がグループ化されて単位グループ131を形成する概念を示す。なお、単位グループ131は後述するADC180の位置を説明するための概念的なものであり、撮像チップ113は、単位グループ131毎に独立して動作しなくてよい。

20

#### 【0027】

画素領域の部分拡大図に示すように、単位グループ131は、緑色画素Gb、Gr、青色画素Bおよび赤色画素Rの4画素から成るいわゆるベイヤー配列を、上下左右に4つ内包する。緑色画素Gb、Grは、カラーフィルタ102として緑色フィルタを有し、入射光のうち緑色波長帯の光を受光する。同様に、青色画素Bは、カラーフィルタ102として青色フィルタを有し、青色波長帯の光を受光し、赤色画素Rは、カラーフィルタ102として赤色フィルタを有し、赤色波長帯の光を受光する。

30

#### 【0028】

図3は、画素150の等価回路図を示す。上記複数の画素150の各々は、上記PD104、転送トランジスタ152、リセットトランジスタ154、増幅トランジスタ156および選択トランジスタ158を有する。これらのトランジスタの少なくとも一部は図1のトランジスタ105に対応する。さらに、画素150には、リセットトランジスタ154のオン信号が供給されるリセット配線300、転送トランジスタ152のオン信号が供給される転送配線302、電源Vddから電力の供給を受ける電源配線304、選択トランジスタ158のオン信号が供給される選択配線306、および、画素信号を出力する出力配線308が配される。以下、各トランジスタをnチャンネル型FETを例として説明するが、トランジスタの種類はこれに限られない。

40

#### 【0029】

転送トランジスタ152のソース、ゲート、ドレインはそれぞれ、PD104の一端、転送配線302、増幅トランジスタ156のゲートに接続される。また、リセットトランジスタ154のドレインは電源配線304に接続され、ソースは増幅トランジスタ156のゲートに接続される。増幅トランジスタ156のドレインは電源配線304に接続され、ソースは選択トランジスタ158のドレインに接続される。選択トランジスタ158のゲートは選択配線306に接続され、ソースは出力配線308に接続されている。負荷電流源309は、出力配線308に電流を供給する。すなわち、選択トランジスタ158に

50

対する出力配線 308 は、ソースフォロアにより形成される。なお、負荷電流源 309 は、撮像チップ 113 側に設けてもよいし、信号処理チップ 111 側に設けてもよい。

#### 【0030】

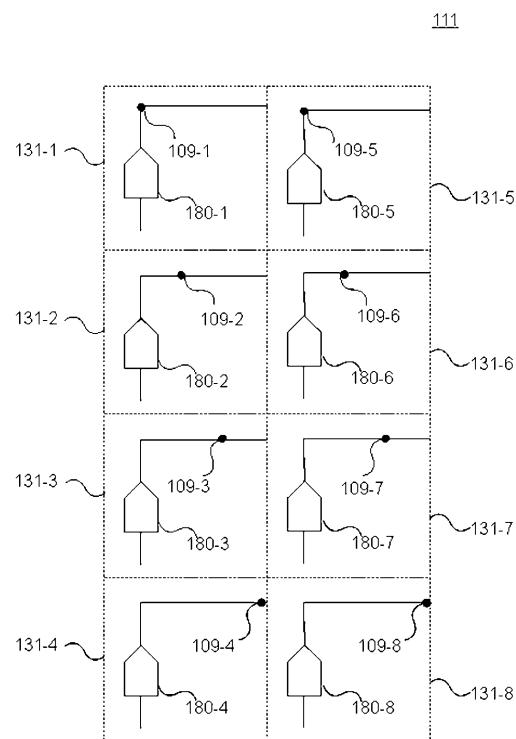

図 4 は、撮像チップ 113 における複数の画素 150 およびバンプ 109 の配置例を示す図である。なお画素 150 は、図 3 に示した画素 150 と同一であるが、図 4 においては簡略化して示す。図 4 に示すように、複数の画素 150 は、行方向および列方向に沿って行列状に配置される。なお、行方向および列方向は、平面内の異なる 2 つの方向を指し、必ずしも直交しなくともよい。なお本例では、複数の画素 150 を、4 画素 × 4 画素の単位グループ 131 に概念的に分けて説明する。本例の複数の画素 150 は、単位グループ 131 - 1 から 131 - 8 の 8 つの単位グループに分けられる。なお、単位グループ 131 - 3 から 131 - 7 を示す点線は省略している。 10

#### 【0031】

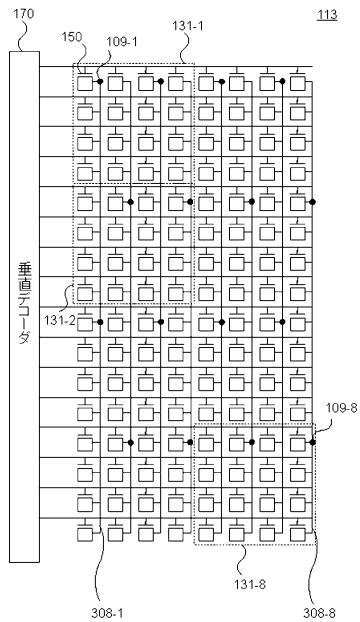

それぞれの列に沿って設けられた画素 150 は、共通の出力配線 308 に接続される。また、撮像チップ 113 は、複数の画素 150 からの画素信号を行毎に読み出す垂直デコーダ 170 を有する。それぞれの行に沿って設けられた画素 150 は、共通の制御配線に接続され、垂直デコーダ 170 からの制御信号に応じて画素信号が読み出される。選択された行における各画素 150 から読み出された画素信号は、それぞれ対応する出力配線 308 およびバンプ 109 を介して並列に伝送され、信号処理チップ 111 に設けられた対応する ADC 180 にそれぞれ入力される。垂直デコーダ 170 は、二以上の ADC 180 を並列動作させる制御部の一例である。 20

#### 【0032】

図 5 は、信号処理チップ 111 の ADC 配置面に配置される複数の ADC 180 を示す図である。なお図 5 には、図 4 に示した複数の単位グループ 131 を投影した領域を示す。それぞれの ADC 180 は、いずれか一つまたは複数の画素列毎に設けられる。即ち、それぞれの ADC 180 は、いずれか一つまたは複数の出力配線 308 毎に設けられる。それぞれの ADC 180 は、対応する出力配線 308 を介して、対応する列の複数の画素 150 に接続される。本例における複数の ADC 180 は、画素領域の複数の出力配線 308 と一対一に対応して設けられる。それぞれの ADC 180 は、対応する出力配線 308 に接続された画素 150 のうち、垂直デコーダ 170 により選択された行の画素 150 の画素信号を受け取り、デジタル信号に変換する。なお、それぞれの ADC 180 が複数の出力配線 308 に接続される場合、それぞれの出力配線 308 からの画素信号をバッファして、対応する ADC 180 に順番に入力する素子を、信号処理チップ 111 に更に設けてよい。 30

#### 【0033】

また、それぞれの ADC 180 は、信号処理チップ 111 の ADC 配置面において二次元に配置される。ここで二次元に配置とは、少なくとも 2 つの方向に沿って ADC 180 が配置されることを指し、当該 2 つの方向は直交していないともよい。本例の複数の ADC 180 は、直交する行方向および列方向に一定間隔に配置される。また、複数の ADC 180 は、それぞれの単位グループ 131 に所定の個数ずつ設けられてよい。本例の複数の ADC 180 は、それぞれの単位グループ 131 に一つずつ設けられる。 40

#### 【0034】

なお、それぞれの ADC 180 の列方向における長さは、複数の画素 150 が設けられた画素領域の列の長さより短い。また、それぞれの ADC 180 は、ADC 配置面における形状が略正方形であってよい。このような形状を有することで、ADC 180 の配置の自由度を向上させることができ、図 5 に示すように、ADC 配置面に ADC 180 を均等に配置することが容易となる。

#### 【0035】

本例の撮像素子 100 によれば、それぞれの ADC 180 が、列毎の出力配線 308 に接続されるので、垂直デコーダ 170 が任意の行を選択する毎に、それぞれの ADC 180 は略同時に動作する。そして、それぞれの ADC 180 が、信号処理チップ 111 の A 50

D C 配置面に均等に配置されるので、それぞれの A D C 1 8 0 が発熱しても、A D C 配置面における温度分布を均等化にすることができる。このため、A D C 1 8 0 の発熱による、複数の P D 1 0 4 の暗電流のバラツキ等を低減することができる。なお、係る効果は、撮像チップ 1 1 3 における画素 1 5 0 の数が多くなるほど、より顕著になる。また、撮像素子 1 0 0 は、A D C 配置面における全ての A D C 1 8 0 が同時に動作するものに限定されない。A D C 配置面における二以上の A D C 1 8 0 が同時に動作すれば、温度分布のばらつきを低減することができる。例えば、垂直デコーダ 1 7 0 が任意の行を選択した場合に、当該行における全ての画素 1 5 0 からの画素信号を同時に読み出すのではなく、それぞれが二以上の画素 1 5 0 からなるグループ単位で、当該行における画素 1 5 0 からの画素信号を読み出してもよい。この場合、グループ内の二以上の画素 1 5 0 からの画素信号は同時に読み出され、対応する二以上の A D C 1 8 0 が同時に動作する。

#### 【 0 0 3 6 】

なお、単位グループ 1 3 1 が  $n$  画素  $\times$   $n$  画素を有している場合、複数の画素 1 5 0 は、列方向に  $n$  個の単位グループ 1 3 1 に分けられることが好ましい。すなわち、複数の画素 1 5 0 は、単位グループ 1 3 1 内の列数と同数の単位グループ 1 3 1 を、列方向に有することが好ましい。列方向に並んだ単位グループ 1 3 1 に設けられる各 A D C 1 8 0 は、これらの単位グループ 1 3 1 に対応するいずれかの出力配線 3 0 8 に接続される。

#### 【 0 0 3 7 】

また、信号処理チップ 1 1 1 は、一部の単位グループ 1 3 1 の画素信号だけを読み出すこともできる。例えば単位グループ 1 3 1 - 1 に含まれる画素 1 5 0 の画素信号だけを読み出す場合、まず、単位グループ 1 3 1 - 1 における第 1 行目の画素 1 5 0 ( 本例では 4 個の画素 1 5 0 ) の画素信号を読み出す。この場合、対応する 4 個の A D C 1 8 0 - 1 、 1 8 0 - 2 、 1 8 0 - 3 、 1 8 0 - 4 が、それぞれの画素 1 5 0 の画素信号をデジタル信号に同時に変換する。

#### 【 0 0 3 8 】

次に、単位グループ 1 3 1 - 1 における第 2 行目の画素 1 5 0 の画素信号を読み出す。このときも、対応する 4 個の A D C 1 8 0 - 1 から 1 8 0 - 4 が、それぞれの画素 1 5 0 の画素信号をデジタル信号に同時に変換する。同様に、4 個の A D C 1 8 0 - 1 から 1 8 0 - 4 を同時に用いて、単位グループ 1 3 1 - 1 における第 3 行目および第 4 行目の画素 1 5 0 を順次読み出す。単位グループ 1 3 1 - 1 における最終行の画素 1 5 0 を読み出した後、読み出し対象行を第 1 行目に戻し、処理を繰り返す。

#### 【 0 0 3 9 】

本例によれば、異なる場所に配置された複数の A D C 1 8 0 を用いるので、局所的な単位グループ 1 3 1 に含まれる画素 1 5 0 の画素信号だけを読み出す場合であっても、A D C 1 8 0 の発熱による温度上昇を面内で均一にすることができる。

#### 【 0 0 4 0 】

また、それぞれの A D C 1 8 0 は、バンプ 1 0 9 を介して、対応する出力配線 3 0 8 に接続される。本例の撮像素子 1 0 0 は、それぞれの A D C 1 8 0 に対して一つずつバンプ 1 0 9 を有する。それぞれのバンプ 1 0 9 は、それぞれの A D C 1 8 0 と同一の単位グループ 1 3 1 の領域に形成される。それぞれのバンプ 1 0 9 は、A D C 1 8 0 と接続すべき出力配線 3 0 8 の直下に設けられてよい。例えばバンプ 1 0 9 は、出力配線 3 0 8 毎に設けられ、且つ、行方向に隣接する出力配線 3 0 8 每に、列方向におけるバンプ 1 0 9 の位置が所定の間隔ずつずれて配置される。当該所定の間隔は、単位グループ 1 3 1 の列方向の長さと等しくてよい。また、バンプ 1 0 9 の配置パターンは、 $n$  行毎に繰り返してよい(ただし、 $n$  は単位グループ 1 3 1 に含まれる行方向の画素 1 5 0 の数)。

#### 【 0 0 4 1 】

なお、それぞれの A D C 1 8 0 は、それぞれの単位グループ 1 3 1 の領域において同一の相対位置に設けられてよい。この場合、A D C 1 8 0 と、バンプ 1 0 9 との相対位置は、単位グループ 1 3 1 每に異なってよい。信号処理チップ 1 1 1 は、対応する A D C 1 8 0 およびバンプ 1 0 9 を接続する配線を有する。

10

20

30

40

50

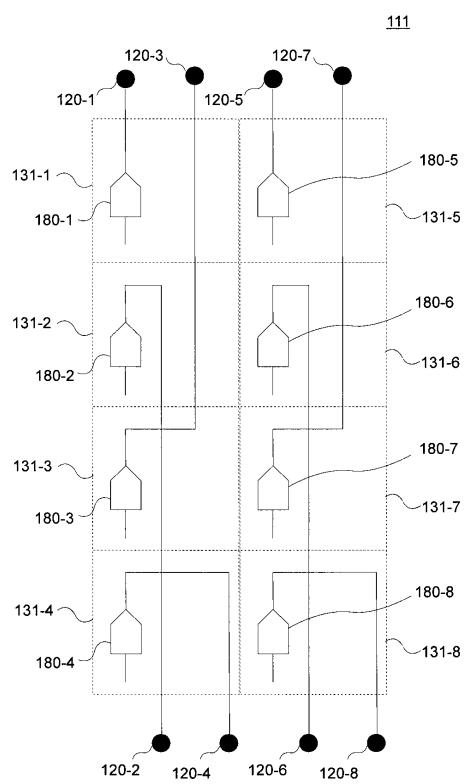

## 【0042】

図6は、撮像チップ113における複数の画素150およびバンプ109の他の配置例を示す図である。図4に示した例では、一つの出力配線308に対して一つのバンプ109を設けたが、本例では、一つの出力配線308に対して複数のバンプ109を設ける。この場合、一つの出力配線308に対する複数のバンプ109は、異なる単位グループ131の領域に設けられてよい。一つの出力配線308に接続される複数のバンプ109は、共通のADC180に接続される。つまり、一つの出力配線308に対して複数のバンプ109を設けている場合においても、同一の出力配線308に接続されたバンプ109は、同一のADC180に接続される。この場合、信号処理チップ111は、同一の出力配線308に接続された複数のバンプ109を、同一のADC180に接続する配線を有する。当該配線は、複数の単位グループ131の領域に渡って形成される。また、出力配線308に対して設けた複数のバンプ109のうちの一部は、出力配線308およびADC180に接続されないダミーバンプであってもよい。

10

## 【0043】

本例の複数のバンプ109も、行方向および列方向において等間隔に配置されることが好み。また、図6に示すように、各列における複数のバンプ109は、行方向に隣接する出力配線308毎に、列方向における位置が所定の間隔ずつずれて配置されてもよい。以上のように、各出力配線308に対して複数のバンプ109を設けることで、撮像チップ113および信号処理チップ111の間の支持点数を増やすことができ、チップの反りを防止することができる。

20

## 【0044】

なお、撮像素子100における画素信号の読み出しの制御方法は、いわゆる列並列型センサと同一にすることができる。このため、複雑な制御線等を用いずに、信号処理チップ111に設けたADC180で、画素信号を読み出すことができる。また、撮像素子100は、垂直デコーダ170がいずれの行を読み出した場合でも、複数のADC180を同時に動作させることができる。また、信号処理チップ111は、画素信号に対して相關二重サンプリングを行い雑音を除去するアナログCDS回路またはDDS回路（デジタルCDS回路）を有してよい。

## 【0045】

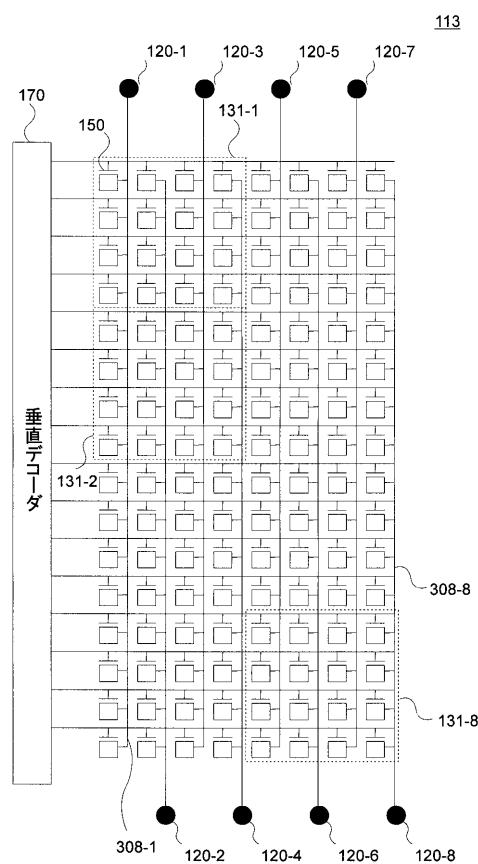

図7は、撮像チップ113における複数の画素150およびTSV120の配置例を示す図である。本例では、バンプ109に代えてTSV120により、撮像チップ113および信号処理チップ111を電気的に接続する。TSV120は、撮像チップ113および信号処理チップ111を貫通して形成され、撮像チップ113および信号処理チップ111を電気的に接続する。出力配線308および垂直デコーダ170は、図4に示した例と同一である。

30

## 【0046】

それぞれの行に沿って設けられた画素150は、共通の制御配線に接続され、垂直デコーダ170からの制御信号に応じて画素信号が読み出される。選択された行における各画素150から読み出された画素信号は、それぞれ対応する出力配線308およびTSV120を介して並列に伝送され、信号処理チップ111に設けられた対応するADC180にそれぞれ入力される。

40

## 【0047】

なお、TSV120は、画素が配列された画素領域以外の周辺領域に設けられる。本例では、TSV120は、列毎に、画素領域の上側および下側に交互に設けられるが、TSV120の配列は本例に限定されない。全てのTSV120を画素領域の上側および下側の一方に設けてよく、また、2列毎に画素領域の上側および下側に交互に設けてよい。

## 【0048】

図8は、信号処理チップ111のADC配置面に配置される複数のADC180およびTSV120を示す図である。図7および図8において同一の符号で示したTSV120は電気的に接続されている。例えばそれぞれのTSV120は、撮像チップ113から信

50

号処理チップ111まで連続して形成される。

【0049】

ADC180の配置は、図5に示した例と同一である。それぞれのADC180は、TSV120を介して、対応する出力配線308に接続される。本例の撮像素子100は、それぞれのADC180に対して一つずつTSV120を有する。TSV120の配置は、図7に示した撮像チップ113と同一である。なお、図8において配線が交差して形成されているが、多層配線構造により、これらの配線間を電気的に絶縁している。図7および図8に示したように、バンプ109に代えてTSV120を用いても、複数のADC180を並列動作させて、温度上昇を均一化することができる。

【0050】

図9は、アナログCDS回路186を有する信号処理チップ111の概要を、撮像チップ113と合わせて示す図である。なお図9においては、撮像チップ113における画素として2画素×2画素のみを示し、他の画素を省略する。また、信号処理チップ111においても同様に、2つのADC180のみを示し、他のADC180を省略している。

【0051】

信号処理チップ111は、それぞれのADC180に対してアナログCDS回路186を有する。アナログCDS回路186の動作は後述する。また、信号処理チップ111は、制御回路184を有する。制御回路184は、タイミング制御部、演算部、メモリバス制御部、インターフェース、および、電源部等を含む。制御回路184は、バンプ109を介して撮像チップ113の各画素150の読み出しタイミングを制御する。バンプ109に代えて、TSVを用いてもよい。また、制御回路184は、アナログCDS回路186、ADC180およびメモリ182の動作を制御する。制御回路184は、撮像素子100の外部と信号を送受信し、また、信号処理チップ111の各回路に電源電力および動作クロックを供給する。また、制御回路184は、画素信号およびデジタル信号に対する所定の演算を行う。

【0052】

図10は、アナログCDS回路186を有する信号処理チップ111の動作例を示すタイミングチャートである。制御回路184は、画素150-Nに対する選択信号S(N)をHレベルにすると共に、画素150-NにリセットパルスRを供給する。これにより、画素150-Nの出力Outは、リセットレベルとなる。制御回路184は、アナログCDS回路186のスイッチを制御する信号Reset\_Holdを出力して、アナログCDS回路186のコンデンサを、当該リセットレベルで充電する。

【0053】

次に、制御回路184は、画素150-Nに対して転送パルスTx(N)を供給する。これにより、画素150-Nは画素信号を出力する。そして、制御回路184は、アナログCDS回路186のスイッチを制御する信号Signal\_Holdを出力して、アナログCDS回路186の他方のコンデンサを、当該画素信号のレベルで充電する。次に制御回路184は、アナログCDS回路186のスイッチを制御して、2つのコンデンサの電圧の差分を、引き算回路に出力させる。アナログCDS回路186のサンプルホールド回路は、引き算回路が出力する差分電圧の電圧値を保持して、ADC180に入力する。ADC180は、当該差分電圧をデジタル値に変換する。このような動作を、各画素150に対して行う。なお、当該動作は、従来の列並列型センサと同一である。即ち、撮像素子100は、従来の列並列型センサにおける信号読み出しの制御をそのまま用いつつ、信号処理チップ111に配置された複数のADC180が同時に動作するので、チップ内における局所的な発熱を防ぐことができる。

【0054】

図11は、DDS回路188を有する信号処理チップ111の概要を、撮像チップ113と合わせて示す図である。本例の信号処理チップ111は、図9に示した信号処理チップ111に対して、アナログCDS回路186に代えてDDS回路188を有する。

【0055】

10

20

30

40

50

図12は、DDS回路188を有する信号処理チップ111の動作例を示すタイミングチャートである。制御回路184は、画素150-Nに対する選択信号S(N)をHレベルにすると共に、画素150-NにリセットパルスRを供給する。これにより、画素150-Nの出力Outは、リセットレベルとなる。制御回路184は、DDS回路188のサンプルホールド回路に、当該リセットレベルを保持させるパルスS/Hを出力する。サンプルホールド回路は、当該リセットレベルをADC180に入力する。ADC180は、当該リセットレベルをデジタル値に変換する。

#### 【0056】

次に、制御回路184は、画素150-Nに対して転送パルスTx(N)を供給する。これにより、画素150-Nは画素信号を出力する。そして、制御回路184は、DDS回路188のサンプルホールド回路に、当該画素信号のレベルを保持させるパルスS/Hを出力する。サンプルホールド回路は、当該画素信号のレベルをADC180に入力する。ADC180は、当該画素信号のレベルをデジタル値に変換する。制御回路184は、ADC180が出力するリセットレベルのデジタル値と、画素信号のレベルのデジタル値の差分を算出する。このような動作を、各画素150に対して行う。なお、当該動作は、従来の列並列型センサと同一である。即ち、撮像素子100は、従来の列並列型センサにおける信号読み出しの制御をそのまま用いつつ、信号処理チップ111に配置された複数のADC180が同時に動作するので、チップ内における局所的な発熱を防ぐことができる。

#### 【0057】

図13は、本実施形態に係る撮像装置500の構成を示すブロック図である。撮像装置500は、撮影光学系としての撮影レンズ520を備え、撮影レンズ520は、光軸OAに沿って入射する被写体光束を撮像素子100へ導く。撮影レンズ520は、撮像装置500に対して着脱できる交換式レンズであっても構わない。撮像装置500は、撮像素子100、システム制御部501、駆動部502、測光部503、ワークメモリ504、記録部505、および表示部506を主に備える。

#### 【0058】

撮影レンズ520は、複数の光学レンズ群から構成され、シーンからの被写体光束をその焦点面近傍に結像させる。なお、図13では瞳近傍に配置された仮想的な1枚のレンズで代表して表している。駆動部502は、システム制御部501からの指示に従って撮像素子100のタイミング制御、領域制御等の電荷蓄積制御を実行する制御回路である。この意味において駆動部502は、撮像素子100に対して電荷蓄積を実行させて画素信号を出力させる撮像素子制御部の機能を担うと言える。駆動部502は、撮像素子100と組み合わされて撮像ユニットを形成する。駆動部502を形成する制御回路は、チップ化されて、撮像素子100に積層されてもよい。

#### 【0059】

撮像素子100は、画素信号をシステム制御部501の画像処理部511へ引き渡す。撮像素子100は、図1から図12において説明した撮像素子100と同一である。画像処理部511は、ワークメモリ504をワークスペースとして種々の画像処理を施し、画像データを生成する。例えば、JPEGファイル形式の画像データを生成する場合は、ホワイトバランス処理、ガンマ処理等を施した後に圧縮処理を実行する。生成された画像データは、記録部505に記録されるとともに、表示信号に変換されて予め設定された時間の間、表示部506に表示される。

#### 【0060】

測光部503は、画像データを生成する一連の撮影シーケンスに先立ち、シーンの輝度分布を検出する。測光部503は、例えば100万画素程度のAEセンサを含む。システム制御部501の演算部512は、測光部503の出力を受けてシーンの領域ごとの輝度を算出する。演算部512は、算出した輝度分布に従ってシャッタ速度、絞り値、ISO感度を決定する。なお、上記AEセンサに用いられる画素を撮像素子100内に設けてもよく、この場合には当該撮像素子100とは別個の測光部503を設けなくてもよい。本

10

20

30

40

50

例の撮像装置 500 によれば、A D C 180 による局所的な発熱を低減した撮像素子 100 を用いるので、暗電流等のバラツキを低減した画像データを取得することができる。

#### 【0061】

以上、本発明を実施の形態を用いて説明したが、本発明の技術的範囲は上記実施の形態に記載の範囲には限定されない。上記実施の形態に、多様な変更または改良を加えることが可能であることが当業者に明らかである。その様な変更または改良を加えた形態も本発明の技術的範囲に含まれ得ることが、請求の範囲の記載から明らかである。

#### 【0062】

請求の範囲、明細書、および図面中において示した装置、システム、プログラム、および方法における動作、手順、ステップ、および段階等の各処理の実行順序は、特段「より前に」、「先立って」等と明示しておらず、また、前の処理の出力を後の処理で用いるのでない限り、任意の順序で実現しうることに留意すべきである。請求の範囲、明細書、および図面中の動作フローに関して、便宜上「まず、」、「次に、」等を用いて説明したとしても、この順で実施することが必須であることを意味するものではない。

#### 【符号の説明】

#### 【0063】

100 撮像素子、101 マイクロレンズ、102 カラーフィルタ、103 パッセーション膜、104 P D、105 トランジスタ、106 P D層、107 配線、108 配線層、109 バンプ、110 T S V、111 信号処理チップ、112 メモリチップ、113 撮像チップ、120 T S V、131 単位グループ、150 画素、152 転送トランジスタ、154 リセットトランジスタ、156 増幅トランジスタ、158 選択トランジスタ、170 垂直デコーダ、180 A D C、182 メモリ、184 制御回路、186 アナログC D S回路、188 D D S回路、300 リセット配線、302 転送配線、304 電源配線、306 選択配線、308 出力配線、309 負荷電流源、500 撮像装置、520 撮影レンズ、501 システム制御部、502 駆動部、503 測光部、504 ワークメモリ、505 記録部、506 表示部、511 画像処理部、512 演算部

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

---

フロントページの続き

(56)参考文献 特開2012-104684(JP,A)

特開2012-054876(JP,A)

特開2011-151375(JP,A)

特開2011-010184(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/3745

H01L 27/146

H04N 5/369

H04N 5/378