# WORLD INTELLECTUAL PROPERTY ORGANIZATION

#### INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(51) International Patent Classification 6:

G09G 3/28

(11) International Publication Number:

WO 97/20302

(43) International Publication Date:

5 June 1997 (05.06.97)

(21) International Application Number:

PCT/US96/18375

**A1**

(22) International Filing Date:

15 November 1996 (15.11.96)

(30) Priority Data:

08/563,947

29 November 1995 (29.11.95) US

(71) Applicant: PLASMACO INC. [US/US]; 180 South Street, Highland, NY 12528 (US).

(72) Inventor: MARCOTTE, Robert, G.; 34 Laura Drive, New Paltz, NY 12561 (US).

(74) Agent: KOFFSKY, David, N.; Ohlandt, Greeley, Ruggiero & Perle, Suite 903, One Landmark Square, Stamford, CT 06901 (US).

(81) Designated States: AL, AM, AT, AU, AZ, BB, BG, BR, BY, CA, CH, CN, CZ, DE, DK, EE, ES, FI, GB, GE, HU, IL, IS, JP, KE, KG, KP, KR, KZ, LK, LR, LS, LT, LU, LV, MD, MG, MK, MN, MW, MX, NO, NZ, PL, PT, RO, RU, SD, SE, SG, SI, SK, TJ, TM, TR, TT, UA, UG, UZ, VN, ARIPO patent (KE, LS, MW, SD, SZ, UG), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, CH, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, ML, MR, NE, SN, TD, TG).

#### Published

With international search report.

Before the expiration of the time limit for amending the claims and to be republished in the event of the receipt of amendments.

(54) Title: DISPLAY PANEL SUSTAIN CIRCUIT ENABLING PRECISE CONTROL OF ENERGY RECOVERY

#### (57) Abstract

An energy efficient driver circuit for driving a display panel having panel electrodes and panel capacitance includes an inductor means coupled to the panel electrodes; a driving voltage source; a voltage supply for providing a supply voltage of a magnitude which is greater than the driving voltage; a first switch device for selectively coupling the driving voltage to the inductor in response to a rising input signal transition, the input signal transition commencing a first state wherein a first current flow occurs through the inductor to charge the panel capacitance, the inductor causing the panel electrodes to rise to a voltage in excess of the driving voltage, at which point the first current flow reaches zero; and a second switch device for selectively coupling the voltage supply to the inductor and panel electrodes. A switch control is responsive to current flow in the inductor and is operative during the first state to initially maintain the second switch device in an open condition, and thereafter, in response to signals derived from the inductor, to cause a closure of the second switch device at a time which enables said second switch device to be fully conductive when the first current flow reaches zero, whereby the supply voltage source during a succeeding second state supplies current to both the panel electrodes and flyback current to said inductor. A like circuit is similarly operational on a falling input signal transition.

### FOR THE PURPOSES OF INFORMATION ONLY

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

| AM | Armenia                  | GB | United Kingdom               | MW | Malawi                   |

|----|--------------------------|----|------------------------------|----|--------------------------|

| AT | Austria                  | GE | Georgia                      | MX | Mexico                   |

| ΑU | Australia                | GN | Guinea                       | NE | Niger                    |

| BB | Barbados                 | GR | Greece                       | NL | Netherlands              |

| BE | Belgium                  | HU | Hungary                      | NO | Norway                   |

| BF | Burkina Faso             | IE | Ireland                      | NZ | New Zealand              |

| BG | Bulgaria                 | IT | Italy                        | PL | Poland                   |

| ВJ | Benin                    | JP | Japan                        | PT | Portugal                 |

| BR | Brazil                   | KE | Kenya                        | RO | Romania                  |

| BY | Belarus                  | KG | Kyrgystan                    | RU | Russian Federation       |

| CA | Canada                   | KP | Democratic People's Republic | SD | Sudan                    |

| CF | Central African Republic |    | of Korea                     | SE | Sweden                   |

| CG | Congo                    | KR | Republic of Korea            | SG | Singapore                |

| CH | Switzerland              | KZ | Kazakhstan                   | SI | Slovenia                 |

| CI | Côte d'Ivoire            | LI | Liechtenstein                | SK | Slovakia                 |

| CM | Cameroon                 | LK | Sri Lanka                    | SN | Senegal                  |

| CN | China                    | LR | Liberia                      | SZ | Swaziland                |

| CS | Czechoslovakia           | LT | Lithuania                    | TD | Chad                     |

| CZ | Czech Republic           | LU | Luxembourg                   | TG | Togo                     |

| DE | Germany                  | LV | Latvia                       | ŤJ | Tajikistan               |

| DK | Denmark                  | MC | Monaco                       | TT | Trinidad and Tobago      |

| EE | Estonia                  | MD | Republic of Moldova          | UA | Ukraine                  |

| ES | Spain                    | MG | Madagascar                   | UG | Uganda                   |

| FI | Finland                  | ML | Mali                         | US | United States of America |

| FR | France                   | MN | Mongolia                     | UZ | Uzbekistan               |

| GA | Gabon                    | MR | Mauritania                   | VN | Viet Nam                 |

1

# DISPLAY PANEL SUSTAIN CIRCUIT ENABLING PRECISE CONTROL OF ENERGY RECOVERY

#### FIELD OF THE INVENTION

This invention is related to sustain signal driver circuits for a capacitive display panel and, more particularly, to a sustain signal driver circuit which enables precisely controllable energy recovery and prevents inductively created flyback currents from adversely affecting pixel sites in the panel.

#### BACKGROUND OF THE INVENTION

15

20

25

30

35

10

5

Plasma display panels, or gas discharge panels, are well known in the art and, in general, comprise a structure including a pair of substrates respectively supporting column and row electrodes, each coated with a dielectric layer disposed in parallel spaced relation to define a gap therebetween in which an ionized gas is sealed. substrates are arranged such that the electrodes are disposed in orthogonal relation to one another, thereby defining points of intersection which, in turn, define discharge pixel sites at which selective discharges may be established to provide a desired storage or display function. It is also known to operate such panels with AC voltages and particularly to provide a write voltage which exceeds the firing voltage at a given discharge site, as defined by selected column and row electrodes, thereby to produce a discharge at a selected cell. The discharge at a selected cell can be continuously "sustained" by applying an alternating sustain voltage (which, by itself, , insufficient to initiate a discharge). This technique relies upon wall charges generated on the dielectric layers of the substrates which, in conjunction with the sustain voltage, operate to maintain continuing discharges.

Details of the structure and operation of gas

discharge panels or plasma displays are set forth in U.S. Pat. No. 3,559,190 issued Jan. 26, 1971 to Donald L. Bitzer, et al. and in U.S. Patent 4,772,884 to Weber et al. issued Sept. 20, 1988.

5

Energy recovery sustainers have been developed for plasma display panels to enable recovery of energy used to charge and discharge the panel's capacitance. As AC plasma display panels have grown in size and operating voltage, the need to precisely control the turn-on of sustain signal drivers has become critical. Turning on sustain signal drivers too early results in lower efficiency and larger electromagnetic (EMI) emissions. Late turn-on results in premature gas discharges within the panel which adversely affects operating margins.

15

20

10

Because a sustain pulse's rise time is controlled by a resonant circuit comprising the sustainer's inductor and the display panel's capacitance, the rise time can vary considerably, based upon the number of ON and OFF pixel sites (i.e., the data content stored in the panel can cause a wide variation in the panel's capacitance). which employ fixed timing circuits, drivers variability minimized by adding ballast must be capacitance, which increases power dissipation, or by adding complex capacitance compensation circuits.

The variable capacitance problem can only be solved by

use of a variable timing circuit which is capable of

driver must begin to turn on as the inductor current

30

25

turning on sustain driver circuits as the inductor concludes its resonant cycle. Prior art circuits have waited to turn on the sustain driver until the inductor's current goes to zero and reverses direction. This creates a "flyback" transition on the energy recovery side of the inductor which is used to trigger the turn-on of output 35 With today's voltages and gas mixtures, the flyback occurs too late to be fully useful.

5

10

15

20

25

30

35

diminishes and well before a flyback current occurs.

Use of flyback current to control sustain output drivers has an unwanted side effect of drawing current out of the panel, while the output driver is turning on. This creates ringing currents throughout the system. The voltage flyback occurs on the recovery side of the inductor at the completion of the resonant cycle. The inductor voltage is opposite to that of the original applied forcing voltage. Flyback current flows to charge or discharge the capacitance on the recovery side of the inductor to match the panel voltage. In doing so, charge is transferred that is opposite to the desired transition, resulting in an increase in non-recoverable energy consumed by the circuit and a noisy transition as the output driver turns on.

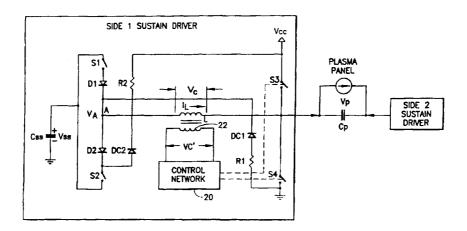

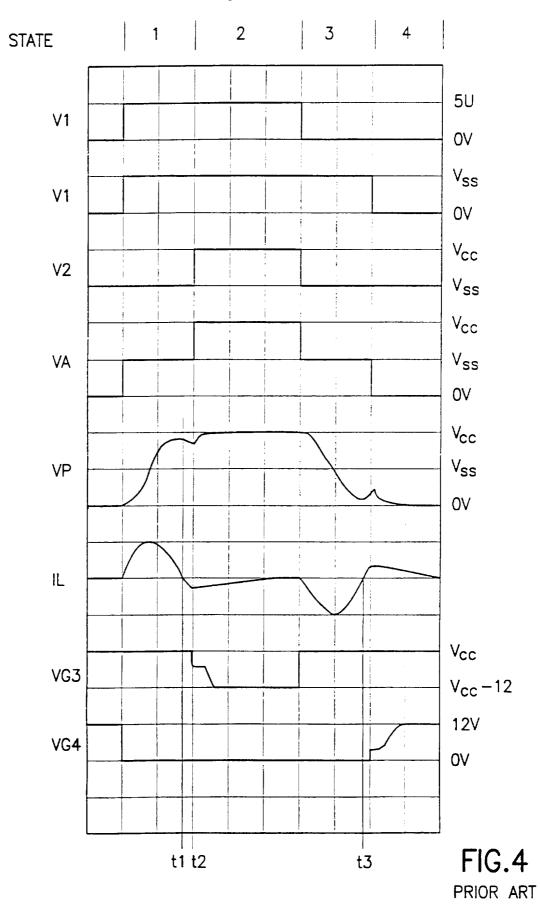

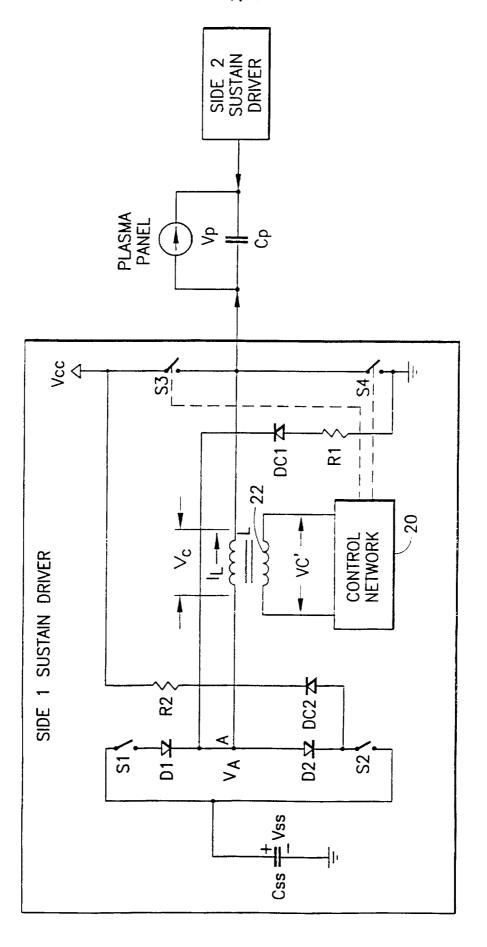

Weber et al., in US Patents 4,866,349 and 5,081,400, disclose a power efficient sustain driver for an AC plasma panel. While, the disclosure of the Weber et al. patent is incorporated herein by reference, because the invention disclosed herein is a direct improvement of the Weber et al. design, details of that design will be hereafter described. The Weber et al. sustain driver circuit employs inductors in the charging and discharging of panel capacitances so as to recover a large percentage of energy theretofore lost in driving panel capacitances. Figs. 1-4 hereof are directly taken from the Weber et al. patent.

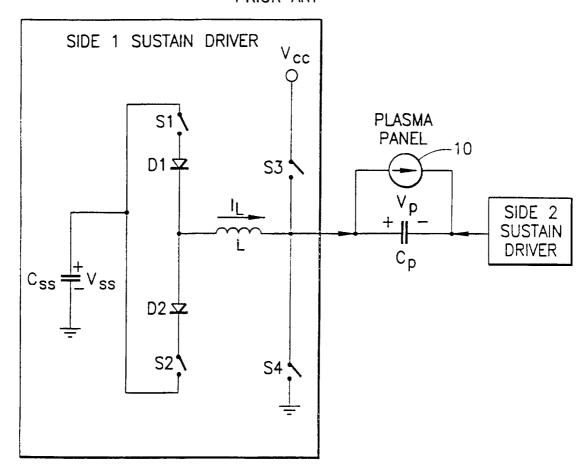

Fig. 1 shows an idealized schematic of the Weber et al. sustain driver and Fig. 2 shows the output voltage and inductor current waveforms expected for the circuit of Fig 1, as four switches S1, S2, S3, S4 are opened and closed through four successive switching states. It is to be understood that each idealized circuit shown hereafter is driven by a logic level control signal which has both a leading rising edge and a lagging falling edge. The means for connecting the source of the control signals to the driver circuit are only shown on the detailed circuit

views.

It is assumed, prior to State 1, that recovery voltage Vss is at Vcc/2 (where Vcc is the sustain driver's power supply voltage), Vp is at zero, S1 and S3 are open, and S2 and S4 are closed. Capacitance Css must be much greater than Cp to minimize variation of Vss during States 1 and 3. The reason that Vss is at Vcc/2 will be explained, below, after the switching operation is explained.

10

15

5

State 1: At the leading, rising edge of an input sustain pulse, S1 closes, S2 opens, and S4 opens (S3 is open). With S1 closed, inductor L and Cp (which is the panel capacitance as seen from the sustain driver circuit) form a series resonant circuit, and a "forcing" voltage of Vss=Vcc/2 is applied thereto. Vp rises to Vcc (through action of inductor L), at which point  $I_L$  has fallen to zero, and diode D1 becomes reverse biased.

20

State 2: S3 is closed to clamp Vp at Vcc and to provide a current path for any "ON" pixels in the panel. When a pixel is in the ON state, its periodic discharges provide a substantial short circuit across the ionized gas, with the current required to maintain the discharge supplied from Vcc. The discharge/conduction state of a pixel is represented by icon 10 in Fig. 1.

30

25

State 3: (occurs upon the falling lagging edge of the input sustain pulse); S2 closes, S1 opens, and S3 opens. With S2 closed, inductor L and capacitance Cp again form a series resonant circuit, with the voltage across inductor L equal to Vss=Vcc/2. However the polarity of the voltage is reverse to that in State 1, causing a negative flow of current  $I_L$ . Vp then falls to ground as the stored energy in inductor L is dissipated, at which point  $I_L$  has reached zero. D2 becomes reverse biased.

35

State 4: S4 is closed to clamp Vp at ground while an

identical driver on the opposite side of the plasma panel drives the opposite side to Vcc and a discharge current then flows in S4 if any pixels are "ON".

It was assumed above that Vss remains stable at Vcc/2 during charging and discharging of Cp. The reasons for this are as follows. If Vss were less than Vcc/2, then on the rise of Vp, when S1 is closed, the forcing voltage would be less than Vcc/2. Subsequently, on the fall of Vp, when S2 is closed, the forcing voltage would be greater than Vcc/2. Therefore, on average, current would flow into Css. Conversely, if Vss were greater than Vcc/2, then on average, current would flow out of Css. Thus, the stable voltage at which the net current into Css is zero, is Vcc/2. In fact, on power up, as Vcc rises, if the driver is continuously switched through the four states explained above, then Vss will rise with Vcc to Vcc/2.

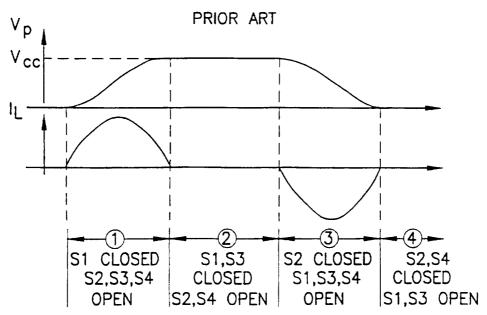

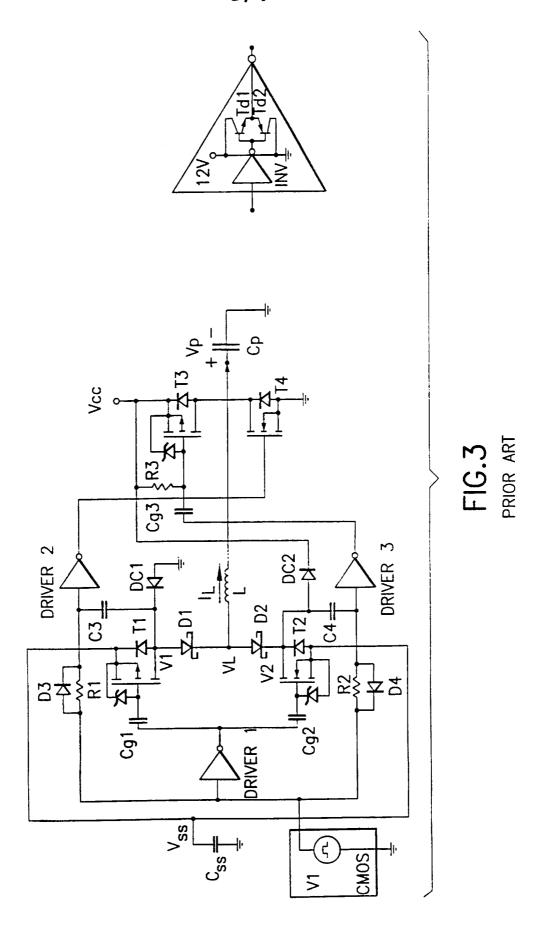

The circuit implementation of the idealized circuit of Fig. 1 is shown in Fig. 3 and the associated timing diagram is shown in Fig. 4. Transistors T1-T4 replace switches S1-S4, respectively. Driver 1 is used to control transistors T1 and T2 in a complementary fashion so that when T1 is on, T2 is off and vice-versa. Driver 2 uses the time constant of R1-C3 or the voltage rise at V1 to turn on transistor T4. Similarly, Driver 3 uses the time constant of R2-C4 or the voltage rise of V2 to turn on transistor T3. Diodes D3 and D4 are used to turn off transistors T3 and T4 quickly.

State 1: To start, T4 and T2 turn off, and T3 is off, waiting to be turned on by the R2-C4 time constant or the rise of V2 (all via diode DC2). An input sustain pulse transition from source 12 turns T1 on and Vss is applied to nodes V1, A, and V2. Inductor L and panel capacitance Cp form a series resonant circuit, which has a forcing voltage of Vss=Vcc/2. As a result of the stored energy in inductor L, Vp rises past Vss to Vcc, at which point  $I_{\rm L}$  goes to

PCT/US96/18375

zero.

WO 97/20302

Since Vp typically rises to 80% of Vcc, inductor L thereafter sees a forcing voltage (from the panel side) of Vp minus Vss. Negative current  $I_L$  now flows out of the panel, back through the inductor L, reverse biases D1 and charges the capacitance of T2. This is the current flyback previously mentioned and starts at time t1 in Figure 4. The flyback current causes voltage flyback at A and V2 to rise sharply. As V2 rises, C4 couples this rise to trigger Driver 3 to turn on T3.

The panel voltage Vp drops as energy is taken out of the panel by the flyback current and put back into inductor L between times t1 and t2. This flyback energy is dissipated in T3, L, D2, and DC2.

State 2: T3 is turned on to clamp Vp at Vcc and to provide a current path for any discharging "ON" pixel. Since energy was put into inductor L, negative current  $I_L$  continues to flow from T3, and through inductor L, diode D2, and diode DC2, until the energy is dissipated. All of the aforesaid components are low loss components so the current decay is slow.

25

30

35

5

10

15

20

State 3: T1 and T3 turn off, T4 remains off, and T2 turns on. Vp is approximately Vcc, as the panel capacitance Cp is fully charged. With T2 on, inductor L and panel capacitance Cp again form a series resonant circuit, having a forcing voltage across inductor L of Vss=Vcc/2. Vp then falls to ground, at which point  $I_L$  is zero. Similar to the end of State 1, the forcing voltage due to the stored energy in inductor L is of reverse polarity, and D2 becomes reverse biased and discharges the capacitance of T1, pulling node V1 to ground, sharply. The flyback current  $I_L$  occurs at time t3 and is coupled through C3 to Driver 2 which turns on T4.

State 4: T4 clamps Vp at ground while an identical driver on the opposite side of the panel drives the opposite side to Vcc and a discharge current then flows in T4 if any pixels are "ON".

5

The above design has a number of deficiencies:

10

1) At time t1, where Vp peaks before T3 turns on, gas discharge activity can begin. Since Vp is less than Vcc, any discharges will be weaker than desired, resulting in dim areas or flickering pixel sites. The discharge has an added affect of further pulling Vp down before T3 can turn on, thus reducing efficiency.

15

20

2) As operating voltages and panel capacitance increase, it becomes necessary to use large area mosfets due to the high currents required. The larger mosfets and higher voltages produce much greater flyback energy levels which must be dissipated during State 2. This is the leading cause for the output voltage drop between times t1 and t2. Since all components are designed for low losses, the inductor current flowing during State 2 continues to flow into State 3 and disturbs the sustainer's falling transition.

25

3) Stray inductance in the panel and interconnect wiring add considerable noise to the system during the turn-on of T3 and T4. Since the flyback action draws current from the panel and T3 sources current to pull up the output, the result is a large, fast current change in the panel which affects the entire ground system of the display, creating radiated Electromagnetic Interference (EMI).

35

30

4) Because R1 and R2 will turn on the output transistors, regardless of the resonant cycle, the circuit is capable of dissipating considerable power during fault conditions.

8

#### SUMMARY OF THE INVENTION

5

10

15

20

25

30

35

The invention described herein builds upon the Weber et al. design by adding a secondary winding to the inductor to enable a control network to enable early turn on of either the high side driver or the low side driver. The produces a voltage proportional instantaneous voltage across inductor L. As the current flows through inductor L into panel capacitance Cp, the voltage across inductor L diminishes to zero when the panel voltage equals the recovery voltage (one half the sustain voltage). The energy stored in inductor L keeps current flowing to further charge the panel capacitance Cp. As the panel voltage rises above the recovery voltage, polarity of the inductor voltage reverses and increases with the panel voltage. This polarity change and voltage rise is followed by the secondary winding and is used to turn on the respective output driver. The output driver's turn-on is dampened by a gate resistor. This allows the mosfet's capacitance to restrict the current flow through the mosfet, allowing inductor L to transfer it's remaining energy into the panel.

Since the polarity change must occur before the output driver can turn on, the amount of energy transferred by the inductor is always maximized even under varying capacitive loads. EMI effects are reduced because the output driver is allowed to turn on slowly and is fully on when the flyback occurs. This eliminates the ringing currents present on the earlier design.

#### BRIEF DESCRIPTION OF THE DRAWINGS

- Fig 1. is an idealized circuit diagram of a prior art sustain driver for an AC plasma panel.

- Fig 2. is a waveform diagram illustrating the operation of the circuit of Fig. 1.

9

Fig. 3 is a detailed circuit diagram of the idealized prior art sustain driver of Fig. 1

Fig 4 is a waveform diagram illustrating the operation of the circuit of Fig 3.

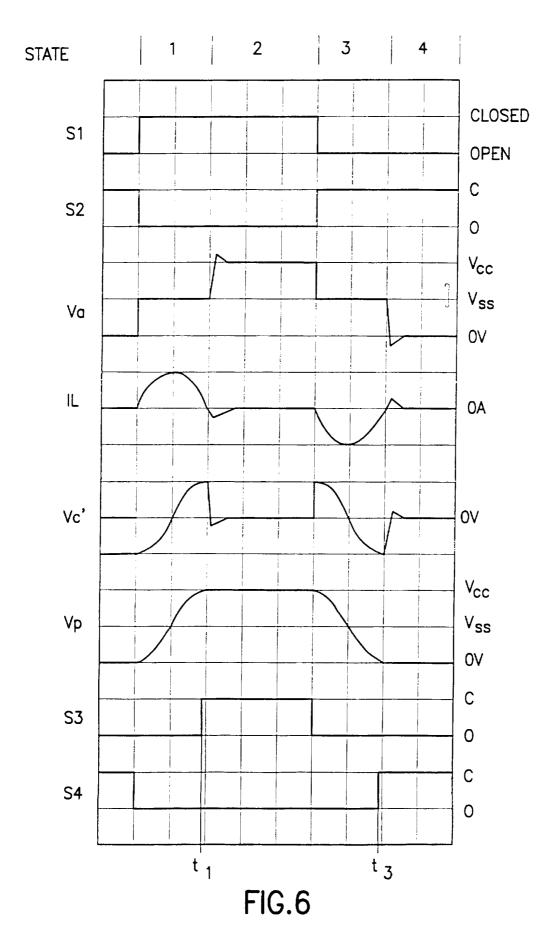

- Fig 5. is an idealized circuit diagram of a sustain driver for an AC plasma panel incorporating the invention.

- Fig 6. is a waveform diagram illustrating the operation of the circuit of Fig. 5.

5

15

20

25

30

35

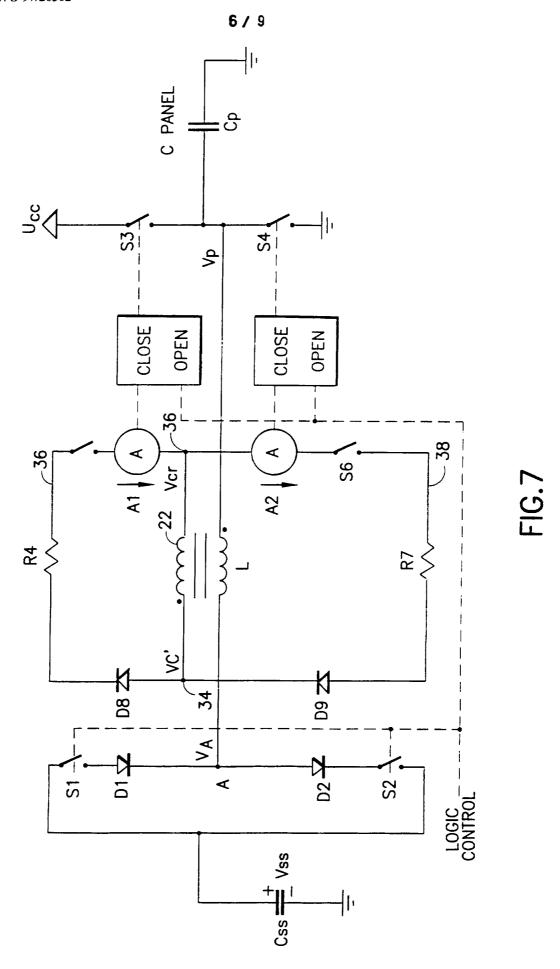

- Fig 7. is an idealized circuit diagram illustrating further details of the sustain driver of Fig. 5.

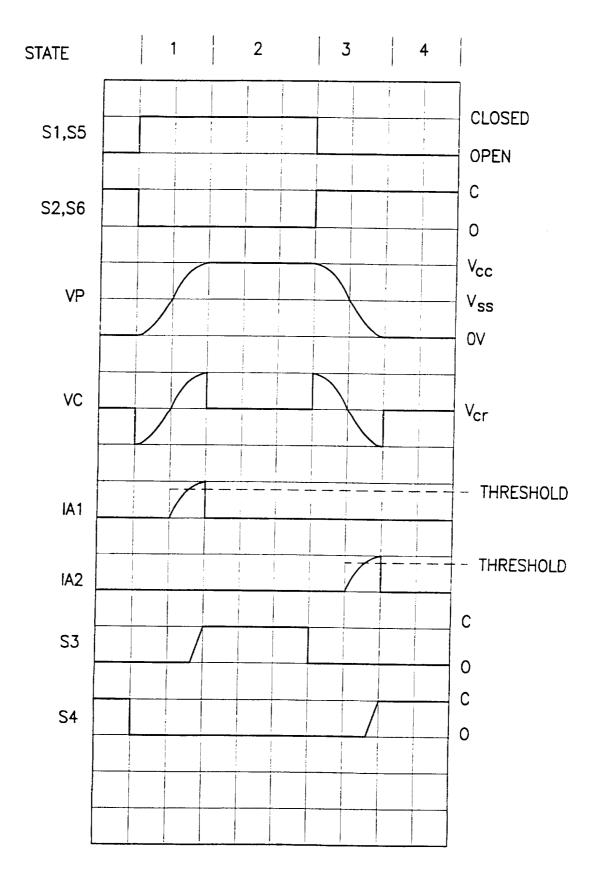

- Fig 8. is a waveform diagram illustrating the operation of the circuit of Fig. 7.

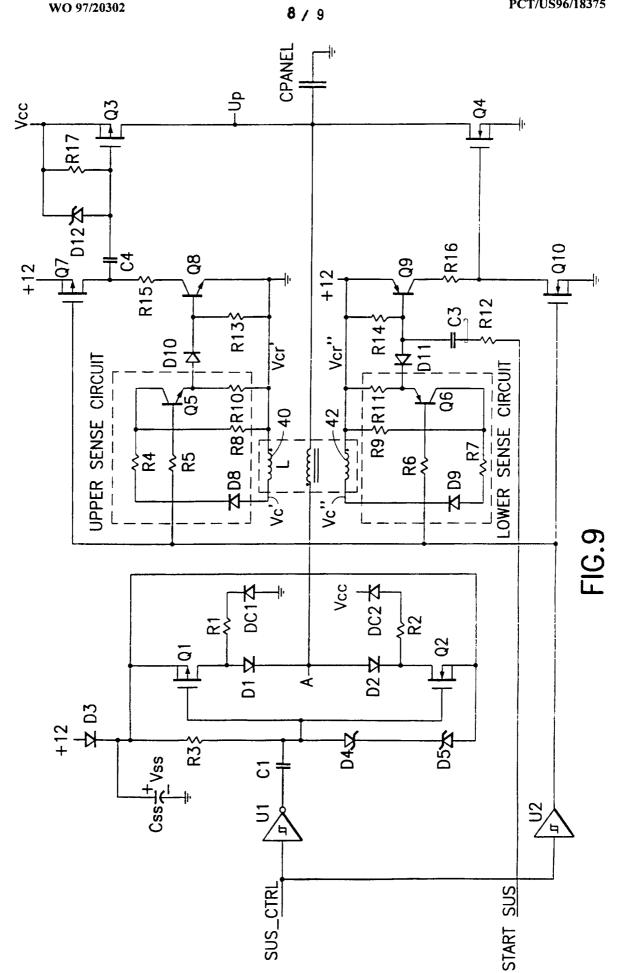

- Fig. 9 is a detailed circuit diagram of a sustain driver incorporating the invention.

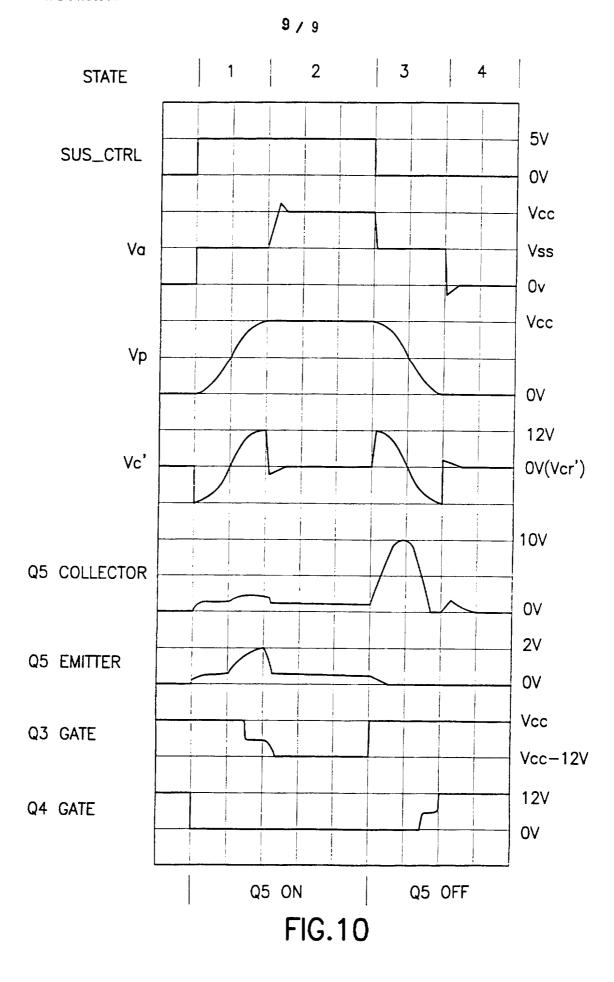

- Fig 10 is a waveform diagram illustrating the operation of the circuit of Fig 9.

#### DETAILED DESCRIPTION OF THE INVENTION

Fig. 5 illustrates the changes made by the invention hereof to the prior art sustain driver of Fig 1. A control network 20 has been added and is coupled to inductor L via a secondary winding 22. Control network 20 controls the conductivity states of switches S3 and S4 and operates in accordance with the waveforms shown in Fig. 6. Control network 20 uses the voltage across inductor L (and secondary winding 22) to slowly close the output switch S3 after the output has risen past the halfway point. On the fall, switch S4 is slowly closed after the output descends past the halfway point. Diode DC2 and resistor R2 dampen one polarity of flyback current and diode DC1 and resistor

R1 dampen the opposite polarity flyback current. The conductivity states of S1 and S2 are controlled by circuitry (not shown) that is responsive to input rise and fall of the logic control signal.

5

The operation of the four switching states of the circuit of Fig. 5 and timing diagrams of Fig. 6 are explained in detail below, where it is assumed that prior to State 1, the recovery voltage, Vss, is at Vcc/2 (where Vcc is the sustain power supply voltage), Vp is at zero, S1 and S3 are open, and S2 and S4 are closed.

10

15

20

25

State 1: Switches S2 and S4 are opened, and switch S1 is closed, thus applying Vss to node A. Vc is the voltage across inductor L, i.e., Vc=Vp-VA. Since the current through inductor L is proportional to the time integral of the voltage across it, current  $I_{\text{L}}$  increases for the first half of State 1 and then decreases as panel voltage Vp rises above recovery voltage Vss, during the second half of State 1. Control network 20 senses Vc' across secondary winding 22, which is proportional to Vc, and allows switch S3 to be turned on only after Vp has crossed Vss, the half-way point and then only during the rise of Vp. In the ideal case, S3 is closed at the positive peak of Vc, time tl and the instant the inductor L current  $\mathbf{I}_{\mathtt{L}}$  equals zero. Briefly stated, S3 is to be closed and ready for full conduction when  ${\bf I}_{\rm L}$  falls to zero at the end of State 1. This action enables the following flyback current through Inductor L to be drawn from the Vcc supply, through S3, and not from the panel.

30

35

State 2: S1 and S3 remain closed, allowing S3 to be the source of both the current to sustain discharges in the panel and the flyback current which flows through inductor L. The flyback current brings voltage  $V_{\rm A}$  at node A up to Vcc. The energy induced into inductor L by the flyback current is dissipated by conduction through diodes D2, DC2 and resistor R2. The value of resistor R2 is chosen to

5

10

15

20

25

30

35

dissipate the flyback energy before State 3.

State 3: S1 and S3 are opened, S4 remains open, and S2 is closed, bringing voltage  $V_{\rm A}$  at node A down to Vss. Vp is now greater than  $V_{\rm A}$ , causing negative current  $I_{\rm L}$  to flow proportional to the time integral of the voltage Vc across the inductor. Once the falling voltage Vp crosses the half-way point, Vc reverses polarity and control network 22 turns on switch S4 at the negative peak of Vc at time t3 in a manner similar to that described above for State 1.

State 4: S4 is closed while the sustainer on the opposite side of the panel rises, discharges, and falls since S4 is part of the return path for the opposite sustainer. When the voltage flyback occurs, the flyback current is drawn from S4 rather than from the panel, and returns the voltage Vc back to zero.

Figure 7 shows a simplified model of control network 20 and includes a loop that includes a pair of current meters A1 and A2 positioned between a pair of switches S5 and S6. Secondary coil 22 is connected between a pair of nodes 34 and 36. Diode D8 and resistor R4 connect node 34 to switch S5 and diode D9 and resistor R7 connect switch S6 to node 34. Figure 8 details the timing of control network 20.

Using the same switching state analysis, the operation of the control network of Fig. 7 will be considered with the aid of timing diagram of Fig. 8. Prior to State 1, secondary winding 22 has 0V across it, S6 is closed and S5 is open. Current meter A2 measures the current through switch S6 and causes switch S4 to be closed when a threshold is crossed. S4 remains closed until the deassertion of the logic control signal.

State 1: Switch S5 is closed and S2, S4, and S6 are opened. When S1 is closed by an input sustain pulse

transition, Vss is applied to node A, and Vc' goes negative relative to Vcr. This negative voltage reverse biases D8, closing off upper current loop 36 and since S6 is open, no current flows through lower loop 38. As current flows through the primary winding of inductor L into the panel, the panel voltage Vp rises with respect to  $V_A$ . result, Vc' rises in accord with the panel voltage Vp (divided by the turns ratio of inductor L). through State 1, panel voltage Vp rises above  $V_A$ , causing Vc' to rise above Vcr. D8 is now forward biased. controls the amount of current allowed to flow through upper loop 36. As Vc' rises with panel voltage Vp, the current through R4 rises and the threshold of current meter Al is crossed, causing the closing of S3. The value of R4 is chosen to precisely determine the turn-on of S3 any time after the midpoint of the sustainer rise. S3 will remain closed until the de-assertion of the logic control signal in state 3.

5

10

15

20

25

30

35

State 2: Once the voltage flyback occurs, Vc' returns to Vcr, and the control network circuit sits idle.

State 3: S1, S3, and S5 open, S6 and S2 close, pulling  $V_A$  back down to Vss. The panel voltage Vp is greater than  $V_A$ , making Vc' go positive again, reverse biasing D9. Since S5 is open, no current can flow through upper loop 36. As the panel voltage Vp drops, Vc' drops and crosses Vcr at the midpoint of the fall. D9 is now forward biased. As Vp continues to fall, Vc' becomes increasingly negative, increasing the current through R7, until the threshold of current meter A2 is reached. This causes closure of S4 and the transition is complete. S4 will remain closed until the next assertion of the logic control signal.

State 4: Again the return voltage flyback brings  ${\rm V}_{\rm A}$  back to zero and Vc' returns to Vcr.

A preferred circuit implementation of the invention is shown in Figure 9 and its waveforms are illustrated in Figure 10. The implementation of Fig. 9 uses two control windings 40 and 42 added to inductor L, rather than the one secondary winding approach described for Figs. 5 and 7, above. Since Q3 is a P-channel mosfet, its gate needs to be pulled low to turn it on, so NPN transistors Q5 and Q8 are used, with Vcr' connected to ground. Q4 is an N-channel mosfet, thereby requiring positive gate drive, so a PNP implementation is used, for Q6 and Q9 with Vcr' connected to +12V. Both windings 40 and 42 have the same number of turns and polarity. Vc' simply has a 12V level shift.

5

10

15

20

25

30

35

Operation of the circuit of Fig 9 begins with SUS\_CTRL de-asserted, Q2, Q6, Q7, and Q4 on. STARTSUS is a startup signal used to turn Q9 on which then turns Q4 on, in turn. For the sustain circuit of Fig. 9 to start up correctly, Q4 must be on prior to SUS\_CTRL being asserted. It is common practice to pulse STARTSUS periodically at a time when Vp is low.

State 1 begins with the activation of SUS\_CTRL. Buffer U1 drives the common gate of recovery mosfets Q1 and Q2, turning Q2 off and Q1 on. Buffer U2 produces a 12V drive signal from SUS\_CTRL to turn Q10 and Q5 on, and Q6 and Q7 off.

Once again, Q1 turning on applies Vss to node A. The polarities of secondary windings produce negative voltages Vc' and Vc'' relative to their respective references, reverse biasing D8 and forward biasing D9. Q6 is off, so the low side driver Q9 is not turned on. The amplitude at each secondary winding is equal to Vss divided by the turns ratio; typically selected for 12V peak.

As current through inductor L builds to its peak, the voltage across inductor L diminishes to zero when the

WO 97/20302 14

panel's voltage Vp equals recovery voltage Vss. Since the secondary windings accurately reflect the voltage across inductor L, Vc' returns to zero and Vc'' returns to +12 volts.

PCT/US96/18375

5

10

At the zero crossing of Vc', inductor L reaches its peak energy level, and continues to source current until its energy is depleted. As the panel continues to charge, secondary windings 40 and 42 become increasingly positive, reverse biasing D9 and forward biasing D8. As voltage Vc' increases, so does the current through transistor Q5. The voltage at Q5's emitter quickly rises high enough to forward bias D10 and turn on Q8, the high side driver. Q8 saturates, providing ample drive to turn on the high side FET Q3. Damping resistor R15 prevents Q3 from turning on too quickly.

20

15

As the sustainer circuit's output continues to rise, the drain-to-gate capacitance of FET Q3 sources additional current for R15 to sink, keeping Q3 in the linear region. While FET Q3 is in the linear region, it only sources a small percentage of the energy needed to complete the sustainer's rise and therefore does not dissipate excessive power.

25

Turn-on of the high side driver can be set very precisely by adjusting the value of R4 in the collector circuit of Q5. Q8 will turn on when the voltage across R10 exceeds two diode drops. Varying R4 changes the secondary winding voltage required to raise the voltage at R10 sufficiently to turn on the driver.

35

30

At the start of State 2, high side FET Q3 is fully on and any residual energy in inductor L is returned to Vcc through Q3. When the energy of inductor L reaches zero, current  $I_{I}$  has stopped flowing. However, panel voltage Vpnow exceeds the recovery voltage Vss and negative current  $I_{\text{L}}$  flows back towards recovery FETs Q1 and Q2, causing  $V_{\text{m}}$

15

to rise sharply to the sustain voltage. This voltage flyback charges the capacitance of T2 which requires current to flow through L. This puts undesirable energy into inductor L, however these currents flow directly from Vcc through Q3 and not from the panel. The addition of R5 dissipates this energy quickly so that the only currents flowing in the system are the sustainer discharge currents.

After all the flyback currents have subsided, there is zero voltage across inductor L. Hence the secondary winding voltage Vc' also returns to zero and Q8 shuts off. Q3 remains on by means of charge on the gate of Q3 until Q7 turns on or Q3 is eventually turned off by the resistor-capacitor combination R17 and C4.

15

20

25

30

35

10

5

State 3 begins the fall of the sustainer output, with the fall of SUS\_CTRL. Q7 turns on, shutting off the high side FET Q3. Q10 shuts off to allow Q4 to be turned on by Q9 when driven by the lower sense circuit. Q5 shuts off to disable the upper sense circuit and Q6 turns on to enable the lower sense circuit. Buffer U1 drives Q1 off and Q2 on, pulling  $V_{\rm A}$  back down to the recovery voltage Vss. Lower secondary winding 42 behaves identically to the upper secondary winding 40, however its connection to 12 volts centers its waveform about +12V to drive PNP transistors Q6 and O9.

The drop of voltage  $V_A$  applies voltage  $(V_A$  -  $V_P)$  across inductor L, which reverse biases D9. Negative current  $I_L$  through inductor L builds as the output falls.

When the output voltage crosses the recovery voltage Vss, Vc'' will drop below +12V and forward biases D9. Again the secondary voltage is across R7, establishing the current through R11. When the voltage across R11 exceeds two diode drops, Q9 turns on and begins to turn on Q4 through damping resistor R16. Again this turn-on is slow, allowing inductor L to remove most of the charge from the

5

10

15

20

25

30

35

WO 97/20302 16

panel's capacitance therefore not dissipating excessive power.

PCT/US96/18375

State 4 occurs when the low side FET Q4 is fully on and any residual inductor current is drawn from ground to complete the sustainer's fall. Another voltage flyback occurs, this time returning  $\boldsymbol{V}_{\!\boldsymbol{A}}$  to ground, and the flyback energy is dissipated in R2.

It should be noted that resistors R8 and R9, are used to bleed off any charge on the collectors of Q5 and Q6. The charge develops when the diodes D8 and D9 are forward biased while the transistors are off. If this charge is not removed prior to turning on Q5 or Q6, a false signal can be sent to Q8 or Q9.

The exclusive use of induced voltages in the secondary windings to control the turn on of output drivers Q3 and Q4 has a number of advantages over flyback designs. First and foremost is the ability to precisely control the high side driver's turn-on. Operating margin studies have shown that the sustain voltage operating window can be widened over designs having the flyback based circuits. Sustainers have been successfully built and operated for high frequency addressing circuits as well as high voltage sustainer circuits.

A common fear with "early" turn on circuits is the danger of turning on both output transistors at the same time during a failure condition. Since the output drivers cannot be turned on before the output voltage exceeds the recovery voltage, under most fault conditions, sustainer will lay idle, unable to start up.

Efficiency can be greatly reduced if the output driver is allowed to begin to turn on before the inductor current peaks. Since the secondary winding switches polarity at the same time the inductor's current peaks, it is difficult

WO 97/20302

for the output driver to impede the inductor's operation. Even with minimal signal delays of 50 to 100 nS, the output is typically up to 75% of its final level when the output driver turns on.

17

PCT/US96/18375

5

In variable capacitance applications, states 1, and 3 will expand in time with the increasing capacitance. Since the sense circuit activates the output driver based on the inductor voltage, the output will turn on at the same voltage regardless of the rise time. In varying voltage applications, the circuit should be tuned for optimum turn-on at the minimum operating voltage. As the voltage is increased, the turn-on will occur earlier in the rise, as the sense winding voltage is proportional to the sustain voltage. This is an added benefit, since gas discharges become faster and stronger as the voltage is increased.

15

10

Radiated noise has been diminished considerably by removing the flyback currents from the panel and system grounds.

It should be understood that the foregoing description

20

25

30

only illustrative of the invention. alternatives and modifications can be devised by those skilled in the art without departing from the invention. For instance, this invention is applicable to DC plasma panels, electroluminescent displays, LCD displays, or any application driving capacitive loads. Accordingly, invention is intended to embrace all such alternatives, modifications and variances which fall within the scope of the appended claims.

18

#### CLAIMS

#### I Claim:

1. An energy efficient driver circuit for driving a display panel having panel electrodes and panel capacitance, said driver circuit comprising:

inductor means having a first terminal and a second terminal, said second terminal coupled to said panel electrodes;

driving voltage source means for providing a driving voltage;

voltage supply means for providing a supply voltage of a magnitude which is greater than said driving voltage;

first switch means for selectively coupling said driving voltage source means to said first terminal in response to an input signal transition, said input signal transition commencing a first state wherein, during said coupling, a first current flow occurs through said inductor means to charge said panel capacitance, said inductor means causing said panel electrodes to achieve a voltage in excess of said driving voltage, at which point said first current flow reaches zero;

second switch means for selectively coupling said voltage supply means to said second terminal and said panel electrodes; and

switch control means coupled to said inductor means and responsive to current flow therein, said switch control means operative during at least a portion of said first state to maintain said second switch means

in an open condition, and thereafter in response to a signal derived from said inductor means, to cause a closure of said second switch means at a time which enables said second switch means to be fully conductive at about the time said first current flow reaches zero, whereby said voltage supply means, during a succeeding second state, supplies current to both said panel electrodes and flyback current to said inductor means.

2. The energy efficient driver circuit as recited in claim 1, further comprising:

third switch means for selectively coupling said driving voltage source means to said first terminal in response to a reverse input signal transition, said reverse input signal transition commencing a third state wherein, during said coupling, a second current flow occurs through said inductor to discharge said panel capacitance, said inductor causing said panel electrodes to reach a voltage below said driving voltage, at which point said second current flow reaches zero;

fourth switch means for selectively coupling said second terminal and said panel electrodes to a source of common potential;

said switch control means operative during said third state to initially maintain said fourth switch means in an open condition, and thereafter in response to signals derived from said inductor means, to cause a closure of said fourth switch means at a time which enables said fourth switch means to be fully conductive when said second current flow reaches zero, whereby said source of common potential forms a sink for flyback current from said inductor means and

provides a discharge path for said panel capacitance.

- 3. The energy efficient driver circuit as recited in claim 1, wherein said driving voltage is about one half of said supply voltage.

- 4. The energy efficient driver circuit as recited in claim 1, wherein said switch control means is inductively coupled to said inductor means.

- 5. The energy efficient driver circuit as recited in claim 1, wherein said switch control means includes an upper sense circuit which, during said first state, causes closure of said second switch means only after said panel electrodes manifest a voltage that exceeds said driving voltage and before said first current reaches zero.

- 6. The energy efficient driver circuit as recited in claim 1, further comprising:

- a flyback return circuit including resistive dissipation means coupled between said first terminal of said inductor means and said voltage supply means for providing a dissipation pathway for said flyback current.

- 7. The energy efficient driver circuit as recited in claim 2, wherein said driving voltage is about one half of said supply voltage.

- 8. The energy efficient driver circuit as recited in claim 2, wherein said switch control means is inductively coupled to said inductor means.

- 9. The energy efficient driver circuit as recited in claim 2, wherein said switch control means includes a lower sense circuit which, during said third state, causes closure of said fourth switch means only after said panel electrodes manifest a voltage that is less than said driving voltage and before said second current reaches zero.

- 10. The energy efficient driver circuit as recited in claim 2, further comprising:

- a flyback return circuit including resistive dissipation means coupled between said first terminal of said inductor means and said source of common voltage for providing a dissipation pathway for said flyback current.

1/9

FIG. 1 PRIOR ART

FIG.2

FIG. 5

5/9

FIG.8

## INTERNATIONAL SEARCH REPORT

Intr tonal Application No PCT/US 96/18375

| A. CLASS<br>IPC 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IFICATION OF SUBJECT MATTER G09G3/28                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| According t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | to International Patent Classification (IPC) or to both national class                                                                                                  | sification and IDC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | S SEARCHED                                                                                                                                                              | aneadon and II C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ocumentation searched (classification system followed by classification G09G                                                                                            | ation symbols)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                       |

| Documenta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | tion searched other than minimum documentation to the extent tha                                                                                                        | such documents are included in the fields searc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | hed                   |

| Electronic d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | lata base consulted during the international search (name of data b                                                                                                     | ase and, where practical, search terms used)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |

| C. DOCUM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | IENTS CONSIDERED TO BE RELEVANT                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                       |

| Category *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Citation of document, with indication, where appropriate, of the                                                                                                        | relevant passages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Relevant to claim No. |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | US 5 081 400 A (LARRY F. WEBER) 1992 cited in the application see column 8, line 24 - column 1 36; figures 5-14                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1-3,6,7               |

| Furt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | her documents are listed in the continuation of box C.                                                                                                                  | Patent family members are listed in an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | inex.                 |

| 'A' document defining the general state of the art which is not considered to be of particular relevance  'E' earlier document but published on or after the international filing date  'L' document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)  'O' document referring to an oral disclosure, use, exhibition or other means  'P' document published prior to the international filing date but later than the priority date claimed  Date of the actual completion of the international search |                                                                                                                                                                         | 'T' later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention  'X' document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone  'Y' document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.  '&' document member of the same patent family  Date of mailing of the international search report |                       |

| 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | April 1997                                                                                                                                                              | 2 9. 04. 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                       |

| Name and n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | nailing address of the ISA  European Patent Office, P.B. 5818 Patentlaan 2  NL - 2280 HV Rijswijk  Tel. (+ 31-70) 340-2040, Tx. 31 651 epo nl,  Fax: (+ 31-70) 340-3016 | Authorized officer  Van Roost, L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                       |

1

# INTERNATIONAL SEARCH REPORT

Intr Nonal Application No

PCT/US 96/18375

| Patent document cited in search report | Publication<br>date | Patent family member(s)                                                                                  | Publication<br>date                                                                          |

|----------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| US 5081400 A                           | 14-01-92            | US 4866349 A CA 1306815 A DE 3788766 D DE 3788766 T EP 0261584 A EP 0548051 A JP 7109542 B JP 63101897 A | 12-09-89<br>25-08-92<br>24-02-94<br>19-05-94<br>30-03-88<br>23-06-93<br>22-11-95<br>06-05-88 |

Form PCT/ISA/210 (patent family annex) (July 1992)