**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

|                                                                  |                                                                                                              |

|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| (51) Int. Cl.<br><i>G09G 3/36</i> (2006.01)                      | (45) 공고일자<br>2006년09월27일                                                                                     |

|                                                                  | (11) 등록번호<br>10-0627995                                                                                      |

|                                                                  | (24) 등록일자<br>2006년09월19일                                                                                     |

| (21) 출원번호<br>10-2000-7002376                                     | (65) 공개번호<br>10-2001-0023722                                                                                 |

| (22) 출원일자<br>2000년03월06일                                         | (43) 공개일자<br>2001년03월26일                                                                                     |

| 번역문 제출일자<br>2000년03월06일                                          |                                                                                                              |

| (86) 국제출원번호<br>PCT/IB1999/001181                                 | (87) 국제공개번호<br>WO 2000/02184                                                                                 |

| 국제출원일자<br>1999년06월24일                                            | 국제공개일자<br>2000년01월13일                                                                                        |

| (81) 지정국<br>국내특허 : 일본, 대한민국,                                     |                                                                                                              |

|                                                                  | EP 유럽특허 : 오스트리아, 벨기에, 스위스, 리히텐슈타인, 독일, 덴마크, 스페인, 프랑스, 영국, 그리스, 아일랜드, 이탈리아, 룩셈부르크, 모나코, 네덜란드, 포르투칼, 스웨덴, 핀란드, |

| (30) 우선권주장<br>98202259.2                                         | 1998년07월06일<br>유럽특허청(EPO)(EP)                                                                                |

| (73) 특허권자<br>코닌클리케 필립스 일렉트로닉스 엔.브이.<br>네델란드왕국, 아인드호펜, 그로네보드스베그 1 |                                                                                                              |

| (72) 발명자<br>미진스베르겐프레데릭체.케.<br>네덜란드, 아아아인드호펜5656, 홀스틀란6           |                                                                                                              |

|                                                                  | 비질스마십케<br>네덜란드, 아아아인드호펜5656, 홀스틀란6                                                                           |

| (74) 대리인<br>이병호<br>정상구<br>신현문<br>이범래                             |                                                                                                              |

심사관 : 정병락

---

**(54) 상이한 비디오 표준들로부터의 비디오 신호들을 표시하도록 적용된 매트릭스 디스플레이 장치**

---

**요약**

매트릭스 디스플레이 장치는 다수의 디스플레이 라인들(R)로 배치된 화소들(18)을 갖는 매트릭스 디스플레이(10)를 포함한다. 구동 회로(3)는 필드(Fp)에서 디스플레이 라인들(R)의 수보다 적은 수의 비디오 라인들을 포함하는 비디오 신호(V)에 의존하여 화상 신호들(Ds)을 화소들(18)에 공급한다. 라인 기간(Tl)은 비디오 라인들 중 한 라인의 지속기간으로 규정된다. 모든 디스플레이 라인들(R) 상에 규칙적으로 비디오 정보를 표시하기 위해, 다수의 라인 기간들(Tl) 후에, 한 디스플레이 라인(R)보다 많은 라인에 비디오 정보를 기록하도록 한 디스플레이 라인(R)보다 많은 라인이 한 라인 기간(Tl) 내에서 선택된다. 따라서, 타이밍 회로(21)는 연속적이며 중첩하지 않는 선택 기간들(Tn;Tr)을 결정하도록 비디오 타이밍 정보(S)를 수신하고, 각각의 선택된 기간(Tn;Tr)은 완전하게 라인 기간(Tl) 내에서 발생한다. 라인 기간들(Tl) 중 적어도 한

기간에서 적어도 두 선택 기간들(Tr)이 발생한다. 선택 회로(20)는 디스플레이 라인들(R)을 연속적으로 선택하고, 각각의 디스플레이 라인(R)은 선택 기간들(Tn:Tr) 중 관련 기간 동안 선택된다. 본 발명에 따른 타이밍 회로(21)는 모두가 실질적으로 동일한 지속기간을 갖는 선택 기간들(Tr)을 얻도록 적용된다. 따라서, 단지 하나의 디스플레이 라인(R)이 선택되는 라인 기간들(Tl) 동안 선택 기간들(Tr)은 한 디스플레이 라인(R)보다 많은 라인이 표시되는 라인 기간들(Tl) 동안의 선택 기간들(Tr)과 동일한 지속시간을 갖는다.

## 대표도

도 1

## 색인어

매트릭스 디스플레이, 화소, 선택 기간

## 명세서

### 기술분야

본 발명은 청구항 1항의 전제부에서 규정된 바와 같은 매트릭스 디스플레이 장치에 관한 것이다. 그러한 매트릭스 디스플레이 장치는 특히 매트릭스 디스플레이 장치의 매트릭스 디스플레이의 디스플레이 라인들의 수보다 적은 비디오 라인들의 수로 비디오 신호를 표시하는데 유용하다.

### 배경기술

EP-A-0565167은 PAL 매트릭스 디스플레이 상에 NTSC 비디오 신호를 표시하는 해결책을 기술한다. 이러한 종래 기술에서는, 행(raw) 구동기 회로가 임의의 NTSC 비디오 신호의 라인들을 반복하도록 동일한 화상 정보로 여러 행들의 화소들을 구동한다. 이러한 방법에 있어서, 화상은 이용가능성 표시 영역을 채우도록 효과적으로 수직 방향으로 확장된다. 하지만, 이러한 기술은 인지 가능한 표시 아티팩트들을 유도하게 될 수 있다. 반복되는 라인들 및 반복되지 않는 라인들에 대하여 화소 전압들의 차가 발생할 수 있다.

### 발명의 상세한 설명

본 발명의 목적은 특히 보다 적은 아티팩트를 갖는 매트릭스 디스플레이의 디스플레이 라인들의 수보다 적은 주사 라인들의 수로 비디오 신호를 확장하는 해결책을 제공하는 것이다.

이러한 목적을 위하여, 본 발명의 제 1 특징은 청구항 1항에 규정된 바와 같은 매트릭스 디스플레이 장치를 제공하는 것이다. 바람직한 실시예들은 종속항들에 규정된다.

본 발명에 따른 매트릭스 디스플레이 장치는 소정 수의 디스플레이 라인들로 배열된 화소들을 갖는 매트릭스 디스플레이를 포함한다. 구동 회로는 화상 신호들을 화소들에 공급하고, 타이밍 회로는 선택 기간들을 발생하며, 선택 회로는 디스플레이 라인들을 선택한다.

구동 회로는 매트릭스 디스플레이의 디스플레이 라인들의 수보다 적은 수의 비디오 라인들을 포함하는 비디오 신호를 수신하고, 비디오 라인들 중 관련 라인에 따른 화상 데이터 신호들을 디스플레이 라인들 중 선택된 라인의 화소들에 공급한다. 타이밍 회로는 연속하는 중첩하지 않는 선택 기간들을 공급하도록 비디오 타이밍 정보를 수신한다. 각각의 선택 기간은 비디오 라인들 중 한 라인의 지속기간을 갖는 라인 기간 내에서 완전하게 발생한다. 이러한 것은 선택 기간들이 비디오 라인들의 반복 기간에 고정된다는 것을 의미한다. 비디오 타이밍 정보는 비디오 신호의 라인 및 필드 동기화 펠스들을 포함할 수도 있다. 선택 회로는 연속하는 선택 기간들 동안 디스플레이 라인들을 연속적으로 선택하도록 연속적인 선택 펠스들을 발생한다.

비디오 라인들의 수가 매트릭스 디스플레이의 디스플레이 라인들의 수보다 적어짐에 따라, 매트릭스 디스플레이 장치는 엑스트라 비디오 라인들을 발생해야 한다. 엑스트라 비디오 라인들은 명료함을 위해 반복하는 라인 기간들이라고 칭하는

임의의 라인 기간들 동안 발생된다. 이를 반복하는 라인 기간들 동안, 적어도 두 선택 기간들은 모두가 비디오 정보를 수신하는 적어도 두 대응하는 디스플레이 라인들을 연속적으로 선택하기 위해 존재한다. 정규 라인 기간들이라고 칭하는 다른 라인 기간들에서, 한 라인 기간의 비디오 정보가 대응하는 디스플레이 라인 상에 표시된다.

종래 기술에서는, 정규 라인 기간 동안 선택 기간이 라인 기간과 실질적으로 동일하며, 반면 두 선택 기간들이 발생하는 반복 라인 기간들에 있어서 선택 기간들은 라인 기간의 절반과 실질적으로 동일하다. 이 상이한 선택 시간들은 스트라이핑(striping) 아티팩트들을 야기한다. 본 발명은 반복 라인 기간들 동안 발생하게 되는 선택 기간들과 동일하게 되도록 정규 라인 기간들 동안 선택 기간들을 선택함으로써 이들 스트라이핑 아티팩트들을 넓은 범위까지 줄이게 된다.

예컨대, 청구범위 2에 청구된 본 발명의 실시예에 규정된 바와 같이, 임의의 수의 연속하는 정규 비디오 라인 기간들 이후, 반복 라인 기간 동안, 두 연속하는 선택 기간들이 두 연속하는 디스플레이 라인들 상에 비디오 데이터 신호들을 표시하도록 발생된다. 두 선택 기간들은 비디오 신호의 한 라인 기간 지속기간 내에 맞춰진다. 결과적으로, 모든 디스플레이 라인들은 라인 기간의 반보다 적은 선택 기간 동안 선택된다. 4:3의 확장 계수가 요구되는 실제의 경우에 있어서, 타이밍 회로는 모든 두 연속하는 정규 라인 기간들 이후에 반복 라인 기간을 발생한다. 이러한 방법에 있어서, 반복 라인 기간들은 디스플레이 라인들에 걸쳐서 고르게 분포되며, 단 한 라인의 엑스트라 비디오 정보만이 반복 라인 기간 동안 발생된다.

청구항 3항에 청구된 본 발명의 실시예에 있어서, 엑스트라 비디오 정보는 라인 기간의 비디오 정보를 반복함으로써 간단한 방법으로 얻어진다. 이러한 방법에 있어서, 동일한 비디오 정보는 두 연속하는 디스플레이 라인들 상에서 표시된다.

청구항 4항에 청구된 본 발명의 실시예에 있어서, 엑스트라 비디오 정보는 한 라인 기간보다 많은 비디오 정보에 의존하게 된다. 예컨대, 엑스트라 비디오 정보는 두 인접하는 라인 기간들의 비디오 정보로부터 보간될 수 있다.

EP-A-0565167에 따라, 동일하지 않은 선택 시간에 의해 야기된 종래 기술의 아티팩트들은 인가된 비디오 신호의 필드 기간 및 패널의 행들의 수의 함수인 레이트로 차례로 화소들의 행들을 주사하는 방식으로 행 구동기 회로를 제어함으로써 최소화된다. 이러한 방법에 있어서, 모든 행들(디스플레이 라인들)은 동일한 어드레스 기간(선택 기간)를 갖는 비디오 신호의 한 필드 기간 내에서 어드레스 된다. 행 구동기 회로는 비동기 방식으로 동작되어, 행 구동기 회로의 타이밍은 비디오 라인들의 타이밍과 직접 연결되지 않는다는 것을 주목해야 한다. 결과적으로, 선택 기간들은 라인 기간들 중 한 기간 내에서 완전하게 발생되지 않는다. 이러한 것은 복잡한 구동 회로를 낳게 한다. 더욱이, 비디오 신호의 비동기 디스플레이 역시 아티팩트들을 발생시킬 수 있다. 따라서, EP-A-0565167은 종래 기술의 문제점을 기술하고는 있지만, 본 발명에 의해 제공된 해결책과 비교할 때 모두가 동일한 지속시간을 갖는 선택 기간들을 얻음에 있어서 전체적으로 상이한 해결책을 기술하고 있다.

EP-A-0794524는 종횡비 변환을 갖는 매트릭스 디스플레이를 기술한다. 매트릭스 디스플레이에는 16:9의 종횡비 및 240 디스플레이 라인들을 갖는 액정 디스플레이(LCD)가 된다. 프레임 당 180 주사 라인들을 갖는 EDTV2(Extended Definition Television 2)비디오 신호가 그러한 디스플레이 상에 표시된다면, 비디오 신호의 주사 라인들(라인 기간들)의 수가 디스플레이의 선택 라인들(디스플레이 라인들)의 수보다 적게 되므로, 디스플레이의 상단 및 하단 부분은 비디오 신호를 수신하지 않을 것이다. 비디오 신호의 모든 3 주사 라인들마다 한 번씩 비디오 신호의 주사 라인을 2 선택 라인들에 한번에 기록하는 구동 회로가 제공된다. 이러한 방식에 서는, LCD의 선택 라인들의 수보다 적은 주사 라인들의 수를 갖는 비디오 신호가 디스플레이의 상단 및 하단 부분의 영상까지도 표시하도록 수직방향으로 확장된다. 이러한 종래 기술과 본 발명 간의 주요한 차이는 본 발명에 의하면 선택 기간들이 중첩하지 않는다는 것이다. 이러한 종래 기술의 해결책은 선택 라인들의 동시 선택이 아티팩트들을 야기하는 매트릭스 디스플레이들에서 또는 선택 회로가 한번에 하나 이상의 선택 라인을 선택할 수 없는 경우 구현될 수 없다.

종래 기술의 상이한 선택 기간들에 기인한 스트라이핑 아티팩트들이 본 발명에서 효과적으로 감소되기는 하지만, 반복 라인 기간에서의 제 1 비디오 라인이 다른 비디오 라인들보다 어둡게 나타난다는 점에서 여전히 일부 성가신 스트라이핑이 가시적으로 남아있게 될 수 있다.

청구항 5항에 규정된 본 발명의 실시예는 이렇게 남아있는 스트라이핑이 다른 디스플레이 라인들간의 극성이 부호를 변경하는 동안, 반복 라인 기간에서의 비디오 라인들의 극성이 동일하다는 사실에 의해 야기된다는 인식에 기초한다. 동일한 극성을 갖는 비디오 라인보다 앞서 있는 비디오 라인들은 더 어둡게 나타난다. 디스플레이 라인들간의 전송 차는 더 어두운 행들의 전송이 증가되거나 또는 더 밝은 행들의 전송이 감소되는 방식으로 구동 신호들을 적용함으로써 보상된다.

청구항 6항에 규정된 바와 같은 본 발명의 실시예에서는, TFT LCD에서, 디스플레이 라인들간의 전송 차가 더 어두운 행들의 전송이 증가되거나 또는 더 밝은 행들의 전송이 감소되는 방식으로 공통 신호를 적용함으로써 보상된다. 공통 신호는 화소들을 상호접속하는 공통 전극에 공급된다.

청구항 7항에 규정된 바와 같은 본 발명의 실시예에서는, TFT LCD에서, 모든 디스플레이 라인들의 전송이 더 어두운 행들의 경우 포지티브 필드들의 킥백(kickback)량을 증가시키고 또한 더 어두운 행들의 경우 네가티브 필드들의 킥백량을 감소시킴으로써 동일하게 되며 또는 더 밝은 행들의 경우 다른 방법으로 동일하게 된다. 킥백량은 TFT의 게이트 선택 신호 상에 구형파 신호를 중복시킴으로써 영향을 받게 할 수 있다. 킥백 효과는 TFT의 게이트-소스 커패시턴스를 통한 게이트 선택 신호로부터 화소들로의 용량성 누화에 기인한다.

본 발명의 상기 및 기타 특징들은 이후 기술되는 실시예들을 참조하여 보다 명확하게 될 것이다.

### 도면의 간단한 설명

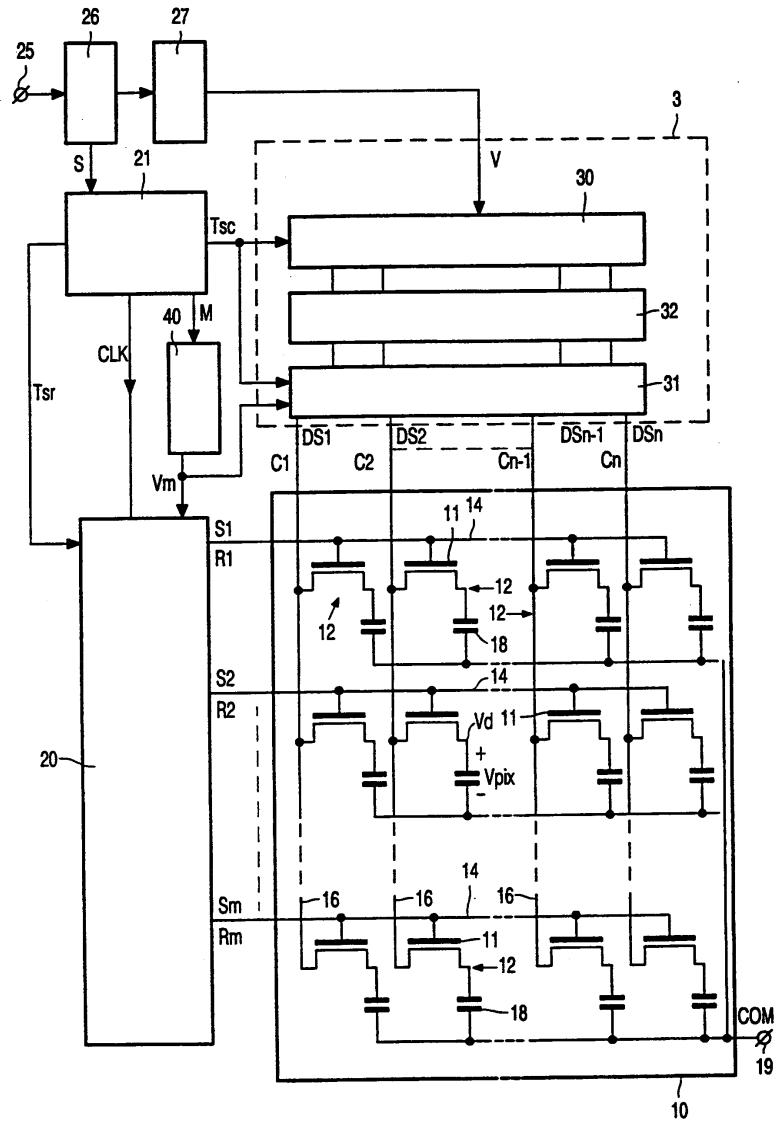

도 1은 본 발명에 따른 매트릭스 디스플레이 장치의 실시예에 대한 개략 회로도.

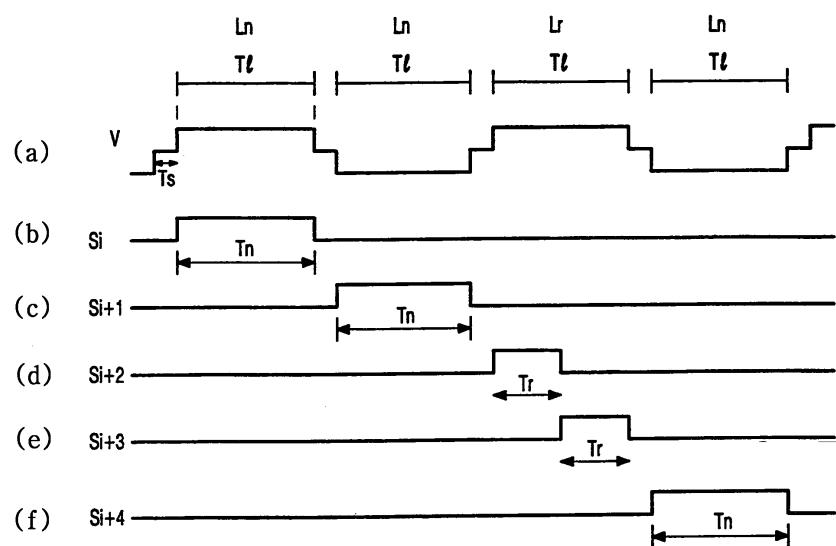

도 2는 종래 기술에 따른 비디오 라인들 및 선택 펠스들의 타이밍을 설명하는 타이밍도.

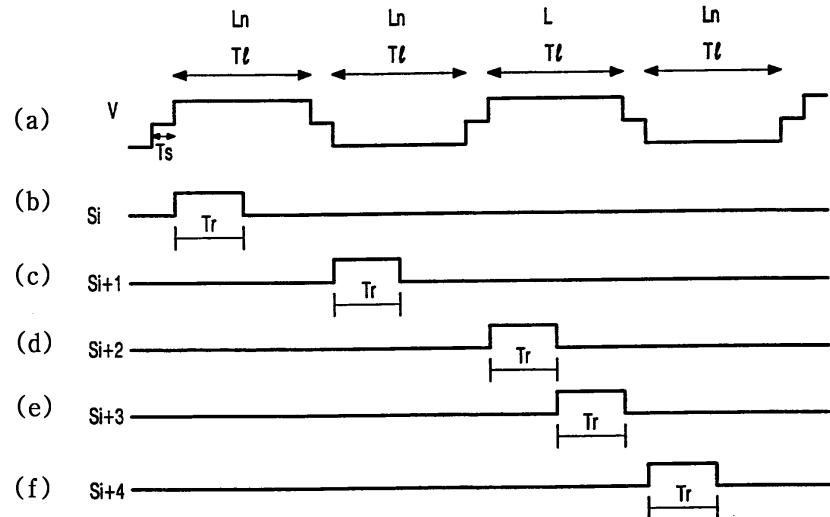

도 3은 본 발명의 실시예에 따른 비디오 라인들 및 선택 펠스들의 타이밍을 설명하는 타이밍도.

도 4는 본 발명의 실시예에 따른 포지티브 및 네가티브 필드의 연속적인 디스플레이 라인들의 극성을 도시하는 도면.

도 5는 킥백 효과를 설명하는 과정을 도시하는 도면.

### 실시예

도 1은 본 발명에 따른 매트릭스 디스플레이 장치의 실시예에 대한 개략 회로도를 도시한다. 본 발명은 일정 형태의 매트릭스 디스플레이에 제한되지는 않지만, 명료히 하기 위해 본 발명을 활성 TFT 액정 디스플레이(LCD)를 갖는 매트릭스 디스플레이 장치와 관련하여 이하에 설명한다.

비디오 화상들을 표시하도록 의도된 활성 LCD 장치들은 이 기술에 있어서 널리 알려져 있다. 예컨대, 라인 반전을 갖는 그러한 LCD 장치를 구동하는 또 다른 정보에 대해서는 본 명세서에 참고로 포함된 GB-A-2134300를 참조하면 된다.

LCD 장치는 각각의 행  $R_i$ 에  $n$  개의 수평적으로 배열된 화소들을 갖는  $m$  개의 행들  $R_1-R_m$ 으로 구성된 행 및 열 어레이를 갖는 활성 매트릭스 어드레스 LCD 패널(active-matrix-addressed LCD panel; 10)을 포함한다. 화소들(18)은 행 및 열 도체들(14 및 16)의 각 교점에 각각 인접하여 위치된 액정(LC) 소자들이다. 각각의 화소(18)는 본 예에서 박막 트랜지스터(TFT)의 형태로 스위칭 장치(11)와 결합된다. 동일한 행  $R_i$ 의 화소들(18)과 결합되는 모든 TFT들(11)의 게이트 단자들은 선택 펠스들  $Si(S_1-S_m)$ 이 공급되는 공통 행 도체(14)에 접속된다. 마찬가지로, 동일한 열  $C_i(C_1-C_n)$ 의 화소들(18)과 결합된 TFT들의 소스 단자는 화상 데이터 신호들  $Dsi(Ds_1-Ds_n)$ 이 공급되는 공통 열 도체(16)에 접속된다. LC 소자들(18) 중 아직 접속되지 않은 단자들은 공통 신호  $COM$ 이 공급되는 공통 전극(19)에 접속된다. 매트릭스 디스플레이 패널(10)은 행 및 열 도체들(14 및 16)의 세트들에 각각 접속된 행 구동기 회로(20) 및 열 구동기 회로(3)에 의해 구동된다. 매트릭스 패널 디스플레이(10)의 도시된 방향은 행들  $R_i$  및 열들  $C_i$ 가 뒤바뀌는 방식으로 다를 수 있으므로, 행 및 열 구동기들(20,3) 각각에 대해서는 선택 및 구동 회로의 더욱 일반적인 용어가 종종 사용되며, 행 및 열 도체들(14,16)을 각각 선택 및 데이터 도체들로 불린다. 이들 양 구동기(20 및 3)는 종래의 형태이므로, 상세히 설명하지 않는다. 간단하게, 행 구동기 회로(20)는 디지털 시프트 레지스터(도시되지 않음)를 포함하며, 상기 레지스터의 동작은 입력(25)에 공급된 비디오 신호로부터 유도된 동기화 신호들  $S$ 가 동기화 분리기(26)로부터 공급되는 타이밍 회로(21)로부터의 정규 클럭킹 펠스  $CLK$  및 제어 신호  $Tsr$ 에 의해 제어되며, 타이밍 회로(21)에 의해 동작가능하게 되어 행 도체들(14)을 선택 신호들로 연속적으로 주사한다.

선택 신호들간의 간격에 있어서, 행 도체들에는 실질적으로 일정한 기준 전위가 공급된다. 비디오 데이터 신호들  $Ds$ 는 시프트 레지스터 회로(30) 및 샘플 홀드 회로(31)를 포함하는 열 구동기 회로(3)로부터 열 도체들(16)에 공급된다.

열 구동기 회로(3)에는 입력(25)에 공급된 비디오 신호로부터 유도되며 비디오 처리 회로(27)로부터의 비디오 정보 신호 V가 공급된다.

입력 비디오 신호의 타이밍 정보로부터 동기화 분리기(26)에서 얻어진 동기화 신호들 S는 제어 회로(21)에 의해 사용되어 열 구동기 회로(3)를 제어하기 위한 타이밍 신호들 Tsc를 발생한다. 열 구동기 회로(3)는 패널(10)의 어드레싱에 적합한 비디오 정보 신호의 직렬-병렬 변환을 수행한다. 패널(10)은 TFT들의 각 행 Ri를 차례로 턴-온 하도록 행 도체(14)를 선택 신호로 순차적으로 주사하고 데이터 신호들 DSi를 열 도체들에 공급함으로써 한번에 한 행을 구동하게 된다. 모든 선택된 행 Ri에 대하여, 열 구동기 회로(3)의 시프트 레지스터(30)는 행 Ri이 선택되는 시간 동안 직렬 비디오 데이터를 샘플 훌드 회로(31)에 기억되는 병렬 데이터로 변환한다. 한번에 한 행을 어드레싱하는 것을 이용하여, 어드레스된 행 Ri의 모든 TFT들(11)을 선택 신호 Si의 지속기간으로 결정된 기간 동안 스위치 온함으로써, 그 기간 동안 열 도체들(16) 상에 존재하는 비디오 정보 신호들 DSi가 화소들(18)로 전송된다. 선택 신호 Si의 종료시 행의 TFT들(11)은 턴 오프되고, 그에 따라 화소들(18)을 도체들(16)로부터 분리한다.

LC 물질의 전기 화학적 열화를 방지하기 위하여, 그것이 달성되는 수단을 간략히 하기 위해 도 1에 도시하지 않았지만, 화소들(18)에 공급되는 구동 신호들의 극성은 공지된 방식에 따라 기간적으로 반전된다. 이러한 극성 반전은 디스플레이 패널의 모든 완전한 필드 이후(필드 반전) 및 선택적으로 모든 행 어드레스 기간 이후(라인 반전) 발생할 수 있다.

매트릭스 디스플레이 장치는 시프트 레지스터 회로(30)와 훌드 회로(31) 사이에 배치될 수 있는 신호 처리 회로(32)를 포함할 수 있다. 신호 처리 회로(32)의 동작은 도 3 및 도 4와 관련하여 설명된다.

매트릭스 디스플레이 장치는 또한 변조 전압 Vm을 행 구동기 회로(20) 및/또는 훌드 회로(31)에 공급하도록 타이밍 회로(21)로부터 타이밍 정보 M을 수신하는 전압 변조기(40)를 포함한다. 전압 변조기(40)의 동작은 도 4와 관련하여 설명된다. 전압 변조기(40)는 또한 공통 전극(19)에 결합될 수 있다.

TFT의 드레인 상의 전압은 Vd로 표시되며, 화소(18) 양단의 전압은 Vpix로 표시된다.

도 2는 종래 기술에 따른 선택 필스들 및 비디오 라인들의 타이밍도를 나타낸다. 도 2의 a는 시프트 레지스터 회로(30)에 공급된 비디오 신호 V의 라인 기간들 T1 및 라인 동기화 기간들 Ts를 도시한다. 비디오 신호 V는 임의의 열 Ci에 공급된 데이터 신호 DS를 나타내며, 라인간 극성 반전이 표시된다. 도 2의 b-f는 연속하는 행들(디스플레이 라인들) Ri-Ri+4에 공급되는 선택 필스들 Si-Si+4를 도시한다. 행들 Ri, Ri+1 및 Ri+4에 대한 선택 필스들 Si, Si+1, Si+4은 지속기간 Tn을 갖는다. 선택 필스들 Si+2 및 Si+3은 지속기간 Tn의 절반인 지속기간 Tr을 갖는다. 정규 라인 기간들 Ln 동안, 훌드 회로(31)는 병렬로 데이터 신호들 DS1-Dsn을 선택된 디스플레이 라인 Ri의 화소들(18)에 공급한다. 데이터 신호들 DS1-Dsn은 대응하는 비디오 라인 기간 Ln 동안 디스플레이될 비디오 정보를 나타낸다. 동일한 방법으로, 라인 기간 Lr 동안 훌드 회로(31)는 대응하는 비디오 라인 Lr의 비디오 정보를 나타내는 데이터 신호들 DSi를 공급한다. 이러한 반복 라인 기간 Lr 동안 두 연속하는 행들 Ri+2 및 Ri+3은 연속하는 선택 필스들 Si+2 및 Si+3으로 선택되며, 비디오 정보는 양쪽의 연속하는 행들 Ri+2 및 Ri+3 상에 표시된다.

도 3은 본 발명에 따른 실시예의 선택 필스들 및 비디오 라인들의 타이밍을 설명하는 타이밍도이다. 도 3의 a는 비디오 신호 V의 라인 기간들 T1 및 수평 동기화 기간들 Ts를 도시한다. 라인 기간 T1 동안, 비디오 신호 V의 라인은 선택된 디스플레이 라인의 화소들에 대한 병렬 데이터 신호들로서 공급된다. 도 3에 있어서, 간략히 하기 위해 비디오 신호의 활성 라인 기간 T1은 이러한 활성 라인 기간 T1 동안 비디오 신호와 관련된 데이터 신호들 DS가 발생하는 동안의 기간과 일치한다. 실제로, 이들 기간들은 서로에 대하여 지연될 수 있다. 선택 필스들 Si는 데이터 신호들 DS가 공급되는 기간들과 정렬되어야 한다는 것은 명백하다. 또한, 라인 기간들 T1은 활성 비디오 라인 기간 및 라인 동기화 기간 Th를 포함하는 지속기간을 갖는 것이 가능하다.

도 3의 b-f는 연속적인 행들(디스플레이 라인들) Ri-Ri+4에 공급된 선택 필스들 Si-Si+4를 도시한다. 동일한 표시들(indices)은 도 2에서와 동일한 신호들을 나타낸다. 타이밍 회로(21)는 각각의 라인 기간 T1 동안 동일한 선택 기간들 Tr을 공급하도록 적용된다. 예컨대, 타이밍 회로(21)는 수평 동기화 필스가 검출될 때 개시하며, 선택 기간 Tn, Tr의 지속기간을 결정하도록 임의의 값으로부터 또 다른 값으로 카운트하는 카운터를 포함한다. 이러한 다른 값은 각각의 라인 기간 T1 동안 모두가 실질적으로 동일한 지속기간을 갖는 하나 이상의 선택 기간들 Tr을 얻도록 적용될 수 있다.

구동 회로(3)가 적용되지 않을 경우, 동일한 비디오 정보가 동일한 라인 기간 T1 내에서 연속적으로 선택되는 두 행들 Ri+2 및 Ri+3에 기록된다.

더욱 정교한 실행이 반복 라인 기간  $L_r$  내에서 발생하는 두 행들 중 한 행 상에 표시될 비디오 정보를 보간함으로써 도달될 수 있다. 이러한 경우에 있어서, 시프트 레지스터(30) 다음에는 보간 회로를 포함하는 비디오 처리 유닛(32)이 온다. 비디오 처리 유닛(32)은 많은 공지된 방법들 중 하나로 구성될 수 있다. 예컨대, 보간된 비디오 라인은 비디오 신호  $V$ 의 두 연속하는 라인들로부터 발생된다. 보간된 비디오 라인의 샘플들은 두 연속하는 라인들의 대응하는 샘플들의 평균값을 가질 수 있다. 예로서, 두 연속하는 라인들의 제 1 라인은 반복 라인 기간  $L_r$  동안 제 1 행  $R_{i+2}$  상에 표시되고, 보간된 비디오 라인은 반복 라인 기간  $L_r$  동안 제 2 행  $R_{i+3}$  상에 표시되며, 두 연속하는 라인들의 제 2 라인은 반복 라인 기간  $L_r$ 에 이어지는 정규 라인 기간  $L_n$  동안 표시된다. 비디오 처리 회로(32)는 또한 시프트 레지스터(30)의 정면에 또는 홀딩 회로(31)와 열 도체들(16)의 세트 사이에 배치될 수도 있다.

도 4는 본 발명의 실시예에 따른 포지티브 및 네가티브 필드의 연속하는 디스플레이 라인들  $R_i$ 의 극성을 도시한다. 좌측 열은 9개의 연속하는 디스플레이 라인들  $R_i$ 를 나타내는 행 번호들  $R_i$ 를 도시한다. 중간 열은 비디오 신호  $V$ 의 포지티브 필드 기간  $F_{p,n}$  동안 연속하는 디스플레이 라인들  $R_i$ 에 공급된 비디오 데이터  $D_s$ 의 극성을 도시한다. 우측 열은 비디오 신호  $V$ 의 네가티브 필드 기간  $F_{p,n+1}$  동안 연속하는 디스플레이 라인들  $R_i$ 에 공급된 비디오 데이터  $D_s$ 의 극성을 도시한다. 연속하는 필드들  $F_p$ 는 반대 극성을 갖는다. 용어 포지티브 및 네가티브 필드 기간  $F_p$ 는 각 필드 기간  $F_p$ 의 제 1 디스플레이 라인  $R_i$ 에 대해 비디오 데이터  $D_s$ 의 극성이 각각 포지티브 또는 네가티브인 것으로 규정된다. 이러한 방법에 있어서, 임의의 디스플레이 라인  $R_i$ 와 관련된 화소들(18) 양단의 전압이 LC 소자들(18)의 AC 구동을 얻도록 매 필드마다 반전된다. 본 발명에 따라 반복 라인들 없이(단지 하나의 디스플레이 라인  $R_i$ 가 매 라인 기간  $T_1$  동안 선택됨), 동일한 필드  $F_p$  동안 데이터 신호들  $D_s$ 의 극성이 매 라인  $R_i$ 마다 변경된다. 라인들이 본 발명에 따라 반복될 때(임의의 라인 기간들  $T_1$ 에 있어서, 한 디스플레이 라인  $R_i$ 보다 많은 라인들이 선택됨), 반복된 라인들의 데이터 신호들  $D_s$ 의 극성은 동일할 수 있다. 이러한 것은 특히 동일한 데이터 신호들  $D_s$ 가 두 개의 연속하는 디스플레이 라인들  $R_{i+2}, R_{i+3}$ 에 기록되는 적절한 실시예의 경우가 된다. 도 4는 매 세 번째 비디오 라인이 한번 반복되는 경우 데이터 신호들  $D_s$ 의 극성을 도시한다. 연속하는 반복되지 않는 비디오 라인들의 수 및 반복되는 비디오 라인들의 수는 요구되는 또는 원하는 확장률(expansion factor)에 의존함을 유의해야 한다. 도 4에 도시된 바와 같이, 반복되는 비디오 라인들의 극성 및 연속하는 반복된 비디오 라인들은 동일하다.

본 발명의 실시예는, 모든 디스플레이 라인들  $R_i$ 의 선택 기간  $T_r$ 이 본 발명에 따라 동일하게 이루어지기는 하지만 발생할 수 있는 잔류 스트라이핑 아티팩트들이 연속하는 행들  $R_i$ 의 화소들(18) 사이의 용량성 결합(capacitive coupling)에 의해 야기된다는 인식에 기초한다. 포지티브 필드  $F_{p,n}$ 에 있어서, 행  $R_i$ 에 기록된 데이터 신호들  $D_s$ 는 포지티브 극성을 가지며, 다음의 행  $R_{i+1}$ 에 기록된 데이터 신호들  $D_s$ 는 네가티브 극성을 갖는다. 행  $R_{i+1}$ 에서의 화소들의 네가티브 전압 스윙은 행  $R_i$ 의 화소들(18)에 용량적으로 결합되며, 결과적으로 행  $R_i$ 의 화소들(18) 양단에 더 적은 포지티브 전압들을 발생시킨다. 이들 화소들(18)의 전송은 증가한다. 행  $R_{i+1}$ 이 네가티브 극성으로 기록되고 다음의 행  $R_{i+2}$ 가 포지티브 극성으로 기록되는 것에 대하여 비교 가능한 효과가 발생한다. 행  $R_{i+2}$ 에서의 화소들의 포지티브 전압 스윙은 행  $R_{i+1}$ 의 화소들(18)에 용량적으로 결합되고, 결과적으로 행  $R_{i+1}$ 의 화소들 양단에 더 적은 네가티브 전압들을 야기하고, 따라서 이들 화소들(18)의 전송은 용량성 결합을 통하여 증가되지 않는다. 이것에 의해 행  $R_{i+2}$ 의 화소들(18)이 행들  $R_i, R_{i+1}$  및  $R_{i+3}$ 의 화소들 보다 어둡게 나타난다. 일반적으로, 동일한 극성을 갖는 디스플레이 라인  $R_i$ 가 이어지는 모든 디스플레이 라인들  $R_i$ 는 반대 극성을 갖는 디스플레이 라인  $R_i$ 가 이어지는 다른 디스플레이 라인들  $R_i$ 보다 어둡게 나타난다. 이러한 인식에 기초하여, 몇몇 해결책들은 이용되는 매트릭스 디스플레이 종류에 의존하는 잔류 스트라이핑을 최소화하는 것이 가능하다. 모든 해결책들은 임의의 디스플레이 라인  $R_i$ 와 관련된 화소들(18) 양단의 전압이 모든 행들  $R_i$ 의 전송이 동일하게 되는 방식으로 제어된다는 것을 공통적으로 갖는다. 더 어둡게 나타나는 행  $R_i$ 의 화소들(18) 양단의 전압을 감소하거나 또는 더 밝게 나타나는 행들  $R_i$ 의 화소들(18) 양단의 전압을 증가하는 것이 가능하다.

선택된 디스플레이 라인  $R_i$ 에 의존하여 신호 처리 회로(32)로 디지털 데이터 신호들  $D_{si}$ 의 값들을 적용함으로써 전송 차들에 대해 정정하는 것이 가능하다.

대안적으로, 2극의 비선형 스위칭 소자들을 갖는 LCD들에 있어서, 화소들 양단의 전압은 선택 펄스들  $S_i$  또는 데이터 신호들  $D_s$ 의 전압 레벨들 중 하나를 변경함으로써 변조될 수 있다. 또한 두 전압 레벨들을 동시에 제어하는 것이 가능하다. 전압 레벨들은 선택 회로(20) 및 구동 회로(30)의 한 쪽 또는 양쪽의 공급 전압들을 변조하도록 변조 전압  $V_m$ 을 발생하는 전압 변조기(40)에 의해 제어될 수 있다.

TFT LCD에 있어서, 모든 화소들(18)의 접합점에 공급된 데이터 신호  $D_s$  또는 공통 신호  $Com$ 을 변조하는 것이 가능하다. 예컨대, 동일한 라인 기간  $T_1$  내에서 연속적으로 선택된 연속하는 행들  $R_i$ 에 속하는 화소들(18) 양단에서 상이한 전압들을 얻기 위해 공통 신호  $Com$  상에 선형 기간 톱니파(line-frequent sawtooth)를 도입하는 것이 가능하다. 또한, 선택 펄스들

Si를 통하여 정정을 적용하는 것이 가능하다. 이러한 정정은 TFT들(11)의 게이트-드레인 커패시턴스를 통한 TFT들(11)의 게이트 신호의 킥백에 기초한다. 킥백 효과는 도 5와 관련하여 더 설명된다. 킥백 효과에 기초한 정정에 대한 설명은 도 5의 설명 후에 기술된다.

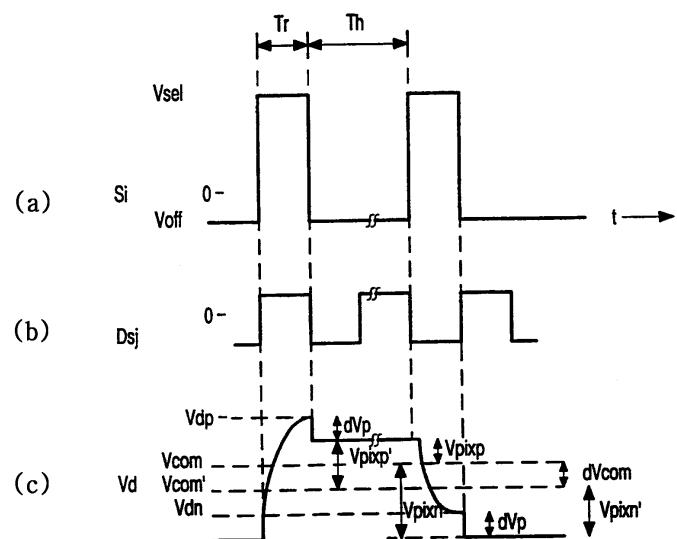

도 5는 킥백 효과를 설명하는 과정들을 도시한다. 도 5의 a는 임의의 디스플레이 라인  $R_i$ 에 대한 게이트 선택 펄스들  $Si$ 를 도시한다. 도 5의 b는 화소들(18) 중 하나와 관련된 TFT들(11) 중 하나에 공급된 비디오 데이터 신호  $D_{sj}$ 를 도시한다. 도 5의 c는 이러한 TFT(11)의 드레인 상의 전압  $V_d$  및 관련 화소(18) 양단의 전압  $V_{pix}$ 를 도시한다. 선택 펄스  $Si$ 는 선택 기간  $Tr$  동안 고전압 레벨  $V_{sel}$ 을 가지며, 그 동안 선택된 행  $R_i$ 의 화소들(18)은 비디오 데이터 신호  $D_{sj}$ 를 화소들(18)에 공급하도록 공통 커넥터들(16)과 공통 전극(19) 사이에 접속된다. 홀딩 기간  $Th$  동안, 선택 펄스  $Si$ 는 저전압 값  $V_{off}$ 를 가지며, 화소들(18)은 선택 기간  $Tr$  동안 공급된 화소들(18) 양단의 전압을 유지하도록 공통 전극들(16)로부터 분리된다. 홀딩 기간  $Th$  동안, 다른 행들  $R_i$ 가 하나씩 선택된다. 도시된 두 선택 펄스들이 두 연속하는 필드들과 관련된다. 제 1 선택 펄스 동안, 비디오 데이터 신호  $D_{sj}$ 는 포지티브 극성을 가지며, 제 2 선택 펄스 동안 비디오 데이터 신호  $D_{sj}$ 는 네가티브 극성을 갖는다.

제 1 선택 펄스 동안, 드레인 전압  $V_d$ 는 포지티브 값  $V_{dp}$ 로 상승한다. 제 1 선택 펄스의 하강 에지는 게이트-드레인 커패시턴스에 기인하여 드레인 전압  $V_d$ 의 전압 강하  $dV_p$ 를 야기한다. 결과적으로, 화소(18) 양단의 전압  $V_{pix}$ 는 너무 작은 량의  $dV_p$ 가 되는  $V_{pixp}$  값을 가지며, 결과적으로 이러한 화소(18)의 전송은 홀딩 기간 동안 너무 높게 된다.

제 2 선택 펄스 동안, 드레인 전압  $V_d$ 는 네가티브 값  $V_{dn}$ 으로 감소한다. 다시, 게이트-드레인 커패시턴스에 기인하여, 제 2 선택 펄스의 하강 에지는 드레인 전압  $V_d$ 의 전압 강하  $dV_p$ 를 야기한다. 결과적으로, 화소(18) 양단의 전압  $V_{pix}$ 는 홀딩 기간 동안 너무 큰 량의  $dV_p$ 인  $V_{pixn}$  값을 갖는다. 결과적으로, 이러한 화소(18)의 전송은 너무 낮게 된다. 도시된 바와 같이, 화소(18) 양단의 전압  $V_{pix}$ 는 킥백 효과가 발생하지 않았다면  $V_{dp}$  및  $V_{dn}$  사이의 중간에서 선택될 수 있는 공통 전압  $V_{com}$ 과 드레인 전압  $V_d$  사이의 차가 된다. 킥백 효과는 정정된 공통 전압  $V_{com}'$ 을 얻도록 량  $dV_p$  만큼 공통 전압  $V_{com}$ 을 낮춤으로써 보상될 수 있다. 이제,  $V_{pixp}'$  및  $V_{pixn}'$ 으로 지정된 의도된 화소 전압들이 발생한다.

킥백 효과는 행  $R_i$ 와 관련된 화소들(18) 양단의 전압을 변조하는데 유용하게 이용될 수 있다. 두 연속하는 행들  $R_i$ 에 공급된 데이터 신호들  $D_s$ 의 극성이 포지티브(예컨대, 포지티브 필드  $F_{p,n}$ 에서의 행들  $R_{i+2}$  및  $R_{i+3}$ , 도 4 참조)인 상황에서, 두 연속하는 행들  $R_i$ 의 제 1 행( $R_{i+2}$ )의 선택 펄스들  $Si$ 의 진폭이, 화소들(18) 양단의 전압들이 감소하고 이러한 제 1 행( $R_{i+2}$ )의 전송이 증가하는 방식으로, 킥백 효과를 증가시키도록 증가되어야 한다. 두 연속하는 행들  $R_i$ 에 공급된 데이터 신호들의 극성이 네가티브(예컨대, 포지티브 필드  $F_{p,n}$ 에서의 행들  $R_{i+6}$  및  $R_{i+7}$ )인 상황에서, 두 연속하는 행들  $R_i$ 의 제 1 행( $R_{i+6}$ )의 선택 펄스의 진폭이, 화소들(18) 양단의 전압들이 감소하고 이러한 제 1 행( $R_{i+6}$ )의 전송이 증가하는 방식으로, 킥백 효과를 감소시키도록 감소되어야 한다.

디스플레이 라인  $R_i$ 와 관련된 화소들(18) 양단의 전압은 전압 변조기(40)로 변조된다. 타이밍 회로(21)는 선택 펄스들  $Si$ 가 더 높거나 또는 더 낮은 레벨을 가질 필요가 있는 선택 기간들  $Tr$ 을 나타내도록 전압 변조기(40)에 타이밍 정보  $M$ 을 공급한다. 예컨대, 전압 변조기(40)는 선택 펄스들  $Si$ 의 레벨을 정정하도록 행 구동기 회로(20)의 공급 전압을 변조할 수 있다. 대안적으로, 행 구동기 회로(20)에 의해 공급된 선택 펄스들  $Si$ 의 레벨이 기준 레벨에 의해 결정된다면, 전압 변조기는 이러한 기준 레벨 상에 구형과 신호를 중첩시킬 수 있으므로, 선택 펄스들  $Si$ 의 레벨은 정정 선택 기간들  $Tr$  동안 증가 및 감소된다.

잔류 스트라이핑 아티팩트들의 가시도는 온도 의존적인 것으로 나타났다. 따라서, 스트라이핑 아티팩트들의 보다 양호한 삭제가 요구될 경우, 정정은 온도 의존적이 되어야 한다. 정정이 킥백 효과에 기초한다면, 선택 펄스의 레벨은 온도 의존적이 될 수 있다. 이것은 변조된 공급 전압을 발생하거나 또는 기준 레벨을 발생하는 회로의 온도-의존 요소를 사용함으로써 가능하게 된다. 또한 온도를 측정하여 그에 따라 변조된 공급 전압 또는 기준 레벨을 정정하는 것이 가능하다.

상술한 실시 예들은 본 발명을 제한하려는 것이 아니라 단지 설명을 위한 것이며, 당업자들은 첨부된 특허청구범위를 벗어나지 않는 범위내에서 많은 대안적인 실시예를 설계할 수 있을 것이다.

### 산업상 이용 가능성

대부분의 실시 예들은 TFT LCD와 관련하여 기술되었지만, 본 발명은 또한 예컨대 수동 LCD 및 플라즈마 디스플레이와 같은 다른 매트릭스 디스플레이들에도 적합하다. 본 실시 예들은 LC 물질 양단의 전압이 감소할 때 증가하는 전송을 갖는 LCD 물질을 기술하고 있지만, 또한 그 양단의 전압이 증가할 때 증가하는 전송을 갖는 LC 물질을 사용하는 것도 가능하다. 이러한 LC 물질을 처리하는데 요구되는 신호 레벨들과 관련한 적용성은 용이하게 구현될 수 있다.

청구범위에 있어서, 팔호내의 참조 부호들도 본 청구범위를 제한하려는 것이 아니다. 단어 "포함하는"이라는 용어는 청구항에 기술된 것 이외의 다른 요소들 또는 단계들의 존재를 배제하지 않는다. 본 발명은 여러개의 개별 요소들을 포함하는 하드웨어 및 적절히 프로그램된 컴퓨터에 의해 구현될 수 있다. 여러개의 수단들을 열거하는 장치 청구항에서, 이들 수단들 중 몇몇은 하드웨어 중 하나 및 동일 품목으로 구현될 수 있다.

### (57) 청구의 범위

#### 청구항 1.

매트릭스 디스플레이 장치로서,

다수의 디스플레이 라인들(R)을 갖는 매트릭스 디스플레이(10)로서, 한 필드(Fp)에 상기 디스플레이 라인들(R)의 수보다 적은 수의 비디오 라인들을 포함하는 비디오 신호(V)를 표시하는, 상기 매트릭스 디스플레이(10);

연속적이며 중첩하지 않는 선택 기간들(Tn;Tr)을 결정하도록 비디오 타이밍 정보(S)를 수신하는 타이밍 회로(21)로서, 각각의 선택 기간(Tn;Tr)은 상기 비디오 라인들 중 하나의 지속기간을 갖는 라인 기간(Tl)내에서 완전하게 발생하고, 상기 라인 기간들 중 적어도 하나의 기간 동안 단일 선택 기간(Tr)은 발생하고, 적어도 두 선택 기간들(Tr)은 상기 라인 기간들(Tl) 중 적어도 하나에서 발생하는, 상기 타이밍 회로(21); 및

상기 디스플레이 라인들(R)을 연속적으로 선택하는 선택 회로(20)로서, 각각의 디스플레이 라인(R)은 상기 선택 기간들(Tn;Tr) 중 관련 기간 동안 선택되는, 상기 선택 회로(20)를 포함하는, 매트릭스 디스플레이 장치에 있어서;

상기 타이밍 회로(21)는 모두가 실질적으로 동일한 지속기간을 갖는 선택 기간들(Tr)을 얻도록 적응되는, 매트릭스 디스플레이 장치.

#### 청구항 2.

제 1 항에 있어서:

상기 타이밍 회로(21)는;

임의의 수의 연속하는 비디오 라인들에 대하여 하나의 비디오 라인을 하나의 대응하는 디스플레이 라인(R) 상에 표시하도록 한 라인 기간(Tl) 동안 하나의 선택 기간(Tr)을 발생하며,

임의의 수의 연속하는 비디오 라인들 이후에, 제 1 및 제 2 비디오 라인을 두 연속하는 디스플레이 라인들(R) 상에 각각 표시하도록 한 라인 기간(Tl) 동안 두 선택 기간들(Tr)을 발생하는, 매트릭스 디스플레이 장치.

#### 청구항 3.

제 2 항에 있어서,

화상 신호들(Ds)을 상기 매트릭스 디스플레이(10)의 화소들(18)에 공급하는 구동 회로(3)로서, 동일한 비디오 라인을 나타내는 화상 신호들(Ds)을 상기 적어도 두 연속하는 디스플레이 라인들(R)에 공급하는 상기 구동 회로(3)를 더 포함하는, 매트릭스 디스플레이 장치.

#### 청구항 4.

제 2 항에 있어서,

화상 신호들(Ds)을 매트릭스 디스플레이(10)의 화소들(18)에 공급하는 구동 회로(3)로서, 상기 적어도 두 연속하는 비디오 라인들에 종속하는 데이터 신호들(Ds)을 상기 적어도 두 연속하는 디스플레이 라인들(R)에 공급하는 상기 구동 회로(3)를 더 포함하는, 매트릭스 디스플레이 장치.

## 청구항 5.

제 1 항에 있어서,

상기 구동 회로(3) 또는 상기 선택 회로(20)에 적어도 하나의 변조 전압(Vm)을 공급하기 위해 타이밍 정보(M)를 수신하도록 상기 타이밍 회로(21)에 결합된 전압 변조기(40)를 더 포함하며, 상기 구동 회로(3) 또는 상기 선택 회로(20)는 상기 적어도 두 디스플레이 라인들(R) 중 제 1 라인의 각 화소들(18) 양단에서 구동 전압들을 얻도록 상기 디스플레이 라인들(R)에 상기 데이터 신호들(Ds) 또는 상기 선택 신호들(S)을 공급하도록 적용되며, 상기 구동전압들은 상기 변조 전압(Vm)에 응답하여 다른 디스플레이 라인들(R)에 공급된 구동 전압들과는 상이한, 매트릭스 디스플레이 장치.

## 청구항 6.

제 1 항에 있어서,

스위칭 입력들을 갖는 스위칭 소자들(11)로서, 공통 전극(19)에 접속된 화소들(18)에 상기 데이터 신호들(Ds)을 스위치 가능하게 결합하기 위해 상기 화소들(18) 중 대응하는 화소와 각각 직렬로 배열되는 상기 스위칭 소자들(11), 및

상기 적어도 두 디스플레이 라인들(R) 중 제 1 라인의 각 화소들(18) 양단에서 구동 전압들을 얻도록 상기 공통 전극(19)에 적어도 하나의 변조 전압(Vm)을 공급하기 위해 타이밍 정보(M)를 수신하도록 상기 타이밍 회로(21)에 결합된 전압 변조기(40)를 더 포함하고 상기 구동 전압들은 상기 변조 전압(Vm)에 응답하여 다른 디스플레이 라인(R)에 공급된 구동 전압들과는 상이한, 매트릭스 디스플레이 장치.

## 청구항 7.

제 1 항에 있어서,

상기 매트릭스 디스플레이(10)는 스위칭 입력들을 갖는 스위칭 소자들(11)을 더 포함하되, 상기 스위칭 소자들(11) 각각은 상기 화소들(18)에 데이터 신호들(Ds)을 스위치 가능하게 결합하기 위해 상기 화소들(18) 중 대응하는 화소와 각각 직렬로 배열되며, 상기 선택 회로(20)는 상기 적어도 두 디스플레이 라인들(R) 중 제 1 라인 동안 일정 레벨을 갖는 전압 파형을 발생하도록 적용되고, 상기 일정 레벨은 다른 디스플레이 라인들(R)에 공급된 레벨과는 상이하며, 상기 전압 파형은 디스플레이 라인들(R) 중 선택된 라인과 관련된 상기 스위칭 소자들(11)의 상기 스위칭 입력들에 공급되는, 매트릭스 디스플레이 장치.

도면

도면1

도면2

도면3

도면4

|           | $F_{p,n}$ | $F_{p,n+1}$ |

|-----------|-----------|-------------|

| $R_i$     | +         | -           |

| $R_{i+1}$ | -         | +           |

| $R_{i+2}$ | +         | -           |

| $R_{i+3}$ | +         | -           |

| $R_{i+4}$ | -         | +           |

| $R_{i+5}$ | +         | -           |

| $R_{i+6}$ | -         | +           |

| $R_{i+7}$ | -         | +           |

| $R_{i+8}$ | +         | -           |

도면5