(12)发明专利

(10)授权公告号 CN 109075148 B

(45)授权公告日 2019.08.16

(21)申请号 201780026378.0

(73)专利权人 株式会社POWDEC

(22)申请日 2017.09.25

地址 日本栃木县

(65)同一申请的已公布的文献号

专利权人 株式会社桑田

申请公布号 CN 109075148 A

(72)发明人 河合弘治 八木修一 越后谷祥子

(43)申请公布日 2018.12.21

(74)专利代理机构 中原信达知识产权代理有限公司 11219

(30)优先权数据

代理人 高培培 戚传江

2016-186741 2016.09.26 JP

(51)Int.Cl.

2017-018254 2017.02.03 JP

H01L 23/48(2006.01)

(85)PCT国际申请进入国家阶段日

H01L 23/12(2006.01)

2018.10.26

H01L 23/28(2006.01)

(86)PCT国际申请的申请数据

H01L 23/29(2006.01)

PCT/JP2017/034411 2017.09.25

H01L 23/31(2006.01)

(87)PCT国际申请的公布数据

H01L 25/07(2006.01)

W02018/056426 JA 2018.03.29

H01L 25/18(2006.01)

审查员 商纪楠

权利要求书10页 说明书17页 附图27页

(54)发明名称

半导体封装体、安装有半导体封装体的模块及电气设备

(57)摘要

一种半导体封装体，具备：半导体芯片(C)，在绝缘基板(10)的第一主面上设置有构成三端子半导体元件的半导体层(20)，在半导体层(20)上以三角形配置有源极(30)、漏极(40)及栅极；电极焊盘(60、70)等，分别与源极(30)、漏极(40)及栅极电连接，被拉出到半导体层(20)的外部；及电绝缘性的树脂(90)，对半导体层(20)、源极(30)、漏极(40)、栅极及绝缘基板(10)的侧面进行密封。

1.一种半导体封装体,设置于金属基板的一个主面和双面印刷配线基板的一个主面之间来使用,其特征在于,

所述半导体封装体具备:

半导体芯片,具有长方形的平面形状,在厚度为 $120\mu\text{m}$ 以下的蓝宝石基板的第1主面上设置有构成三端子半导体元件的半导体层,在所述半导体层上以三角形配置有第1电极、第2电极及第3电极;

第1电极焊盘、第2电极焊盘及第3电极焊盘,分别与所述第1电极、所述第2电极及所述第3电极接触而电连接,被拉出到所述半导体层的外部;及

电绝缘性的树脂,对所述第1电极、所述第2电极、所述第3电极、所述半导体层及所述蓝宝石基板的侧面进行密封,

当设所述半导体芯片的四个边在逆时针方向上依次为S<sub>1</sub>、S<sub>2</sub>、S<sub>3</sub>、S<sub>4</sub>时,所述第1电极具有具备与边S<sub>1</sub>平行的长边和与边S<sub>2</sub>平行的短边的细长的长方形形状,并且所述第1电极靠近边S<sub>1</sub>和S<sub>2</sub>地设置,所述第1电极的长边的长度比边S<sub>1</sub>的长度短,所述第2电极具有具备与边S<sub>3</sub>平行的长边和与边S<sub>2</sub>平行的短边的细长的长方形形状,并且所述第2电极靠近边S<sub>2</sub>和S<sub>3</sub>地设置,所述第2电极的长边的长度比边S<sub>3</sub>的长度短,所述第3电极具有具备与边S<sub>4</sub>平行的长边和与边S<sub>1</sub>平行的短边的长方形形状,并且所述第3电极在所述第1电极与边S<sub>4</sub>之间的区域中靠近边S<sub>1</sub>和S<sub>4</sub>地设置,

所述第1电极焊盘从所述第1电极经由所述树脂上而向与边S<sub>1</sub>垂直的方向且与所述半导体层和所述蓝宝石基板平行的方向突出,该突出的所述第1电极焊盘的前端与边S<sub>1</sub>平行,所述第2电极焊盘从所述第2电极经由所述树脂上而向与边S<sub>3</sub>垂直的方向且与所述半导体层和所述蓝宝石基板平行的方向突出,该突出的所述第2电极焊盘的前端与边S<sub>3</sub>平行,所述第3电极焊盘从所述第3电极经由所述树脂上而向与边S<sub>4</sub>垂直的方向且与所述半导体层和所述蓝宝石基板平行的方向突出,该突出的所述第3电极焊盘的前端与边S<sub>4</sub>平行,

所述半导体封装体以使所述蓝宝石基板的第2主面与所述金属基板的所述一个主面接触的方式安装在所述金属基板的所述一个主面上,所述第1电极焊盘、所述第2电极焊盘及所述第3电极焊盘的从所述树脂突出的部分的与所述蓝宝石基板相反的一侧的面与所述双面印刷配线基板的所述一个主面上的规定的配线的规定的部位连接而构成规定的电路。

2.一种半导体封装体,设置于金属基板的一个主面和双面印刷配线基板的一个主面之间来使用,其特征在于,

所述半导体封装体具备:

半导体芯片,具有长方形的平面形状,在厚度为 $120\mu\text{m}$ 以下的蓝宝石基板的第1主面上设置有构成三端子半导体元件的半导体层,在所述半导体层上以三角形配置有第1电极、第2电极及第3电极;

第1电极焊盘、第2电极焊盘及第3电极焊盘,分别与所述第1电极、所述第2电极及所述第3电极接触而电连接,被拉出到所述半导体层的上方;及

电绝缘性的树脂,对所述第1电极、所述第2电极、所述第3电极、所述半导体层及所述蓝宝石基板的侧面进行密封,

当设所述半导体芯片的四个边在逆时针方向上依次为S<sub>1</sub>、S<sub>2</sub>、S<sub>3</sub>、S<sub>4</sub>时,所述第1电极具有具备与边S<sub>1</sub>平行的长边和与边S<sub>2</sub>平行的短边的细长的长方形形状,并且所述第1电极靠近边

S<sub>1</sub>和S<sub>2</sub>地设置,所述第1电极的长边的长度比边S<sub>1</sub>的长度短,所述第2电极具有具备与边S<sub>3</sub>平行的长边和与边S<sub>2</sub>平行的短边的细长的长方形形状,并且所述第2电极靠近边S<sub>2</sub>和S<sub>3</sub>地设置,所述第2电极的长边的长度比边S<sub>3</sub>的长度短,所述第3电极具有具备与边S<sub>4</sub>平行的长边和与边S<sub>1</sub>平行的短边的长方形形状,并且所述第3电极在所述第1电极与边S<sub>4</sub>之间的区域中靠近边S<sub>1</sub>和S<sub>4</sub>地设置,

所述第1电极焊盘在被从所述第1电极相对于所述半导体层向垂直上方拉出之后,以跨过边S<sub>1</sub>的方式在所述半导体层的上方与所述半导体层平行地延伸,所述第1电极焊盘的外侧的前端与边S<sub>1</sub>平行,所述第2电极焊盘在被从所述第2电极相对于所述半导体层向垂直上方拉出之后,以跨过边S<sub>3</sub>的方式在所述半导体层的上方与所述半导体层平行地延伸,所述第2电极焊盘的外侧的前端与边S<sub>3</sub>平行,所述第3电极焊盘在被从所述第3电极相对于所述半导体层向垂直上方拉出之后,以跨过边S<sub>4</sub>的方式在所述半导体层的上方与所述半导体层平行地延伸,所述第3电极焊盘的外侧的前端与边S<sub>4</sub>平行,

所述树脂的轮廓比所述半导体芯片大所述半导体芯片的侧面的所述树脂的厚度的量,但与所述半导体芯片的外形基本相似,

所述第1电极焊盘的所述前端、所述第2电极焊盘的所述前端及所述第3电极焊盘的所述前端与所述树脂的轮廓一致,

所述半导体封装体以使所述蓝宝石基板的第2主面与所述金属基板的所述一个主面接触的方式安装在所述金属基板的所述一个主面上,所述第1电极焊盘、所述第2电极焊盘及所述第3电极焊盘的与所述蓝宝石基板相反的一侧的面与所述双面印刷配线基板的所述一个主面上的规定的配线的规定的部位连接而构成规定的电路。

3. 根据权利要求1或2所述的半导体封装体,其中,

所述半导体层为GaN系半导体层,所述三端子半导体元件为GaN系场效应晶体管。

4. 根据权利要求3所述的半导体封装体,其中,

所述GaN系场效应晶体管为极化超结GaN系场效应晶体管。

5. 根据权利要求3或4所述的半导体封装体,其中,

所述第1电极为源极,所述第2电极为漏极,所述第3电极为栅极。

6. 一种安装有半导体封装体的模块,具备:

金属基板;

一个或多个所述半导体封装体,安装在所述金属基板的一个主面上;及

双面印刷配线基板,在一个主面上具有规定的配线,所述规定的配线以构成规定的电路的方式设置在所述一个或多个半导体封装体上,

所述半导体封装体具备:

半导体芯片,具有长方形的平面形状,在厚度为120μm以下的蓝宝石基板的第1主面上设置有构成三端子半导体元件的半导体层,在所述半导体层上以三角形配置有第1电极、第2电极及第3电极;

第1电极焊盘、第2电极焊盘及第3电极焊盘,分别与所述第1电极、所述第2电极及所述第3电极接触而电连接,被拉出到所述半导体层的外部;及

电绝缘性的树脂,对所述第1电极、所述第2电极、所述第3电极、所述半导体层及所述蓝宝石基板的侧面进行密封,

当设所述半导体芯片的四个边在逆时针方向上依次为S<sub>1</sub>、S<sub>2</sub>、S<sub>3</sub>、S<sub>4</sub>时，所述第1电极具有具备与边S<sub>1</sub>平行的长边和与边S<sub>2</sub>平行的短边的细长的长方形形状，并且所述第1电极靠近边S<sub>1</sub>和S<sub>2</sub>地设置，所述第1电极的长边的长度比边S<sub>1</sub>的长度短，所述第2电极具有具备与边S<sub>3</sub>平行的长边和与边S<sub>2</sub>平行的短边的细长的长方形形状，并且所述第2电极靠近边S<sub>2</sub>和S<sub>3</sub>地设置，所述第2电极的长边的长度比边S<sub>3</sub>的长度短，所述第3电极具有具备与边S<sub>4</sub>平行的长边和与边S<sub>1</sub>平行的短边的长方形形状，并且所述第3电极在所述第1电极与边S<sub>4</sub>之间的区域中靠近边S<sub>1</sub>和S<sub>4</sub>地设置，

所述第1电极焊盘从所述第1电极经由所述树脂上而向与边S<sub>1</sub>垂直的方向且与所述半导体层和所述蓝宝石基板平行的方向突出，该突出的所述第1电极焊盘的前端与边S<sub>1</sub>平行，所述第2电极焊盘从所述第2电极经由所述树脂上而向与边S<sub>3</sub>垂直的方向且与所述半导体层和所述蓝宝石基板平行的方向突出，该突出的所述第2电极焊盘的前端与边S<sub>3</sub>平行，所述第3电极焊盘从所述第3电极经由所述树脂上而向与边S<sub>4</sub>垂直的方向且与所述半导体层和所述蓝宝石基板平行的方向突出，该突出的所述第3电极焊盘的前端与边S<sub>4</sub>平行，

所述半导体封装体以使所述蓝宝石基板的第2主面与所述金属基板的所述一个主面接触的方式安装在所述金属基板的所述一个主面上，所述第1电极焊盘、所述第2电极焊盘及所述第3电极焊盘的从所述树脂突出的部分的与所述蓝宝石基板相反的一侧的面与所述双面印刷配线基板的所述一个主面上的所述规定的配线的规定的部位连接而构成所述规定的电路。

7. 一种安装有半导体封装体的模块，具备：

金属基板；

一个或多个所述半导体封装体，安装在所述金属基板的一个主面上；及

双面印刷配线基板，在一个主面上具有规定的配线，所述规定的配线以构成规定的电路的方式设置在所述一个或多个半导体封装体上，

所述半导体封装体具备：

半导体芯片，具有长方形的平面形状，在厚度为120μm以下的蓝宝石基板的第1主面上设置有构成三端子半导体元件的半导体层，在所述半导体层上以三角形配置有第1电极、第2电极及第3电极；

第1电极焊盘、第2电极焊盘及第3电极焊盘，分别与所述第1电极、所述第2电极及所述第3电极接触而电连接，被拉出到所述半导体层的上方；及

电绝缘性的树脂，对所述第1电极、所述第2电极、所述第3电极、所述半导体层及所述蓝宝石基板的侧面进行密封，

当设所述半导体芯片的四个边在逆时针方向上依次为S<sub>1</sub>、S<sub>2</sub>、S<sub>3</sub>、S<sub>4</sub>时，所述第1电极具有具备与边S<sub>1</sub>平行的长边和与边S<sub>2</sub>平行的短边的细长的长方形形状，并且所述第1电极靠近边S<sub>1</sub>和S<sub>2</sub>地设置，所述第1电极的长边的长度比边S<sub>1</sub>的长度短，所述第2电极具有具备与边S<sub>3</sub>平行的长边和与边S<sub>2</sub>平行的短边的细长的长方形形状，并且所述第2电极靠近边S<sub>2</sub>和S<sub>3</sub>地设置，所述第2电极的长边的长度比边S<sub>3</sub>的长度短，所述第3电极具有具备与边S<sub>4</sub>平行的长边和与边S<sub>1</sub>平行的短边的长方形形状，并且所述第3电极在所述第1电极与边S<sub>4</sub>之间的区域中靠近边S<sub>1</sub>和S<sub>4</sub>地设置，

所述第1电极焊盘在被从所述第1电极相对于所述半导体层向垂直上方拉出之后，以跨

过边S<sub>1</sub>的方式在所述半导体层的上方与所述半导体层平行地延伸,所述第1电极焊盘的外侧的前端与边S<sub>1</sub>平行,所述第2电极焊盘在被从所述第2电极相对于所述半导体层向垂直上方拉出之后,以跨过边S<sub>3</sub>的方式在所述半导体层的上方与所述半导体层平行地延伸,所述第2电极焊盘的外侧的前端与边S<sub>3</sub>平行,所述第3电极焊盘在被从所述第3电极相对于所述半导体层向垂直上方拉出之后,以跨过边S<sub>4</sub>的方式在所述半导体层的上方与所述半导体层平行地延伸,所述第3电极焊盘的外侧的前端与边S<sub>4</sub>平行,

所述树脂的轮廓比所述半导体芯片大所述半导体芯片的侧面的所述树脂的厚度的量,但与所述半导体芯片的外形基本相似,

所述第1电极焊盘的所述前端、所述第2电极焊盘的所述前端及所述第3电极焊盘的所述前端与所述树脂的轮廓一致,

所述半导体封装体以使所述蓝宝石基板的第2主面与所述金属基板的所述一个主面接触的方式安装在所述金属基板的所述一个主面上,所述第1电极焊盘、所述第2电极焊盘及所述第3电极焊盘的与所述蓝宝石基板相反的一侧的面与所述双面印刷配线基板的所述一个主面上的所述规定的配线的规定的部位连接而构成所述规定的电路。

8.一种电气设备,具备一个或多个模块,

至少一个所述模块是如下的模块,即,具备:

金属基板;

一个或多个半导体封装体,安装在所述金属基板的一个主面上;及

双面印刷配线基板,在一个主面上具有规定的配线,所述规定的配线以构成规定的电路的方式设置在所述一个或多个半导体封装体上,

所述半导体封装体具备:

半导体芯片,具有长方形的平面形状,在厚度为120μm以下的蓝宝石基板的第1主面上设置有构成三端子半导体元件的半导体层,在所述半导体层上以三角形配置有第1电极、第2电极及第3电极;

第1电极焊盘、第2电极焊盘及第3电极焊盘,分别与所述第1电极、所述第2电极及所述第3电极接触而电连接,被拉出到所述半导体层的外部;及

电绝缘性的树脂,对所述第1电极、所述第2电极、所述第3电极、所述半导体层及所述蓝宝石基板的侧面进行密封,

当设所述半导体芯片的四个边在逆时针方向上依次为S<sub>1</sub>、S<sub>2</sub>、S<sub>3</sub>、S<sub>4</sub>时,所述第1电极具有具备与边S<sub>1</sub>平行的长边和与边S<sub>2</sub>平行的短边的细长的长方形形状,并且所述第1电极靠近边S<sub>1</sub>和S<sub>2</sub>地设置,所述第1电极的长边的长度比边S<sub>1</sub>的长度短,所述第2电极具有具备与边S<sub>3</sub>平行的长边和与边S<sub>2</sub>平行的短边的细长的长方形形状,并且所述第2电极靠近边S<sub>2</sub>和S<sub>3</sub>地设置,所述第2电极的长边的长度比边S<sub>3</sub>的长度短,所述第3电极具有具备与边S<sub>4</sub>平行的长边和与边S<sub>1</sub>平行的短边的长方形形状,并且所述第3电极在所述第1电极与边S<sub>4</sub>之间的区域中靠近边S<sub>1</sub>和S<sub>4</sub>地设置,

所述第1电极焊盘从所述第1电极经由所述树脂上而向与边S<sub>1</sub>垂直的方向且与所述半导体层和所述蓝宝石基板平行的方向突出,该突出的所述第1电极焊盘的前端与边S<sub>1</sub>平行,所述第2电极焊盘从所述第2电极经由所述树脂上而向与边S<sub>3</sub>垂直的方向且与所述半导体层和所述蓝宝石基板平行的方向突出,该突出的所述第2电极焊盘的前端与边S<sub>3</sub>平行,所述第

3电极焊盘从所述第3电极经由所述树脂上而向与边S<sub>4</sub>垂直的方向且与所述半导体层和所述蓝宝石基板平行的方向突出,该突出的所述第3电极焊盘的前端与边S<sub>4</sub>平行,

所述半导体封裝体以使所述蓝宝石基板的第2主面与所述金属基板的所述一个主面接触的方式安装在所述金属基板的所述一个主面上,所述第1电极焊盘、所述第2电极焊盘及所述第3电极焊盘的从所述树脂突出的部分的与所述蓝宝石基板相反的一侧的面与所述双面印刷配线基板的所述一个主面上的所述规定的配线的规定的部位连接而构成所述规定的电路。

9.一种电气设备,具备一个或多个模块,

至少一个所述模块是如下的模块,即,具备:

金属基板;

一个或多个半导体封裝体,安装在所述金属基板的一个主面上;及

双面印刷配线基板,在一个主面上具有规定的配线,所述规定的配线以构成规定的电路的方式设置在所述一个或多个半导体封裝体上,

所述半导体封裝体具备:

半导体芯片,具有长方形的平面形状,在厚度为120μm以下的蓝宝石基板的第1主面上设置有构成三端子半导体元件的半导体层,在所述半导体层上以三角形配置有第1电极、第2电极及第3电极;

第1电极焊盘、第2电极焊盘及第3电极焊盘,分别与所述第1电极、所述第2电极及所述第3电极接触而电连接,被拉出到所述半导体层的上方;及

电绝缘性的树脂,对所述第1电极、所述第2电极、所述第3电极、所述半导体层及所述蓝宝石基板的侧面进行密封,

当设所述半导体芯片的四个边在逆时针方向上依次为S<sub>1</sub>、S<sub>2</sub>、S<sub>3</sub>、S<sub>4</sub>时,所述第1电极具有具备与边S<sub>1</sub>平行的长边和与边S<sub>2</sub>平行的短边的细长的长方形形状,并且所述第1电极靠近边S<sub>1</sub>和S<sub>2</sub>地设置,所述第1电极的长边的长度比边S<sub>1</sub>的长度短,所述第2电极具有具备与边S<sub>3</sub>平行的长边和与边S<sub>2</sub>平行的短边的细长的长方形形状,并且所述第2电极靠近边S<sub>2</sub>和S<sub>3</sub>地设置,所述第2电极的长边的长度比边S<sub>3</sub>的长度短,所述第3电极具有具备与边S<sub>4</sub>平行的长边和与边S<sub>1</sub>平行的短边的长方形形状,并且所述第3电极在所述第1电极与边S<sub>4</sub>之间的区域中靠近边S<sub>1</sub>和S<sub>4</sub>地设置,

所述第1电极焊盘在被从所述第1电极相对于所述半导体层向垂直上方拉出之后,以跨过边S<sub>1</sub>的方式在所述半导体层的上方与所述半导体层平行地延伸,所述第1电极焊盘的外侧的前端与边S<sub>1</sub>平行,所述第2电极焊盘在被从所述第2电极相对于所述半导体层向垂直上方拉出之后,以跨过边S<sub>3</sub>的方式在所述半导体层的上方与所述半导体层平行地延伸,所述第2电极焊盘的外侧的前端与边S<sub>3</sub>平行,所述第3电极焊盘在被从所述第3电极相对于所述半导体层向垂直上方拉出之后,以跨过边S<sub>4</sub>的方式在所述半导体层的上方与所述半导体层平行地延伸,所述第3电极焊盘的外侧的前端与边S<sub>4</sub>平行,

所述树脂的轮廓比所述半导体芯片大所述半导体芯片的侧面的所述树脂的厚度的量,但与所述半导体芯片的外形基本相似,

所述第1电极焊盘的所述前端、所述第2电极焊盘的所述前端及所述第3电极焊盘的所述前端与所述树脂的轮廓一致,

所述半导体封装体以使所述蓝宝石基板的第2主面与所述金属基板的所述一个主面接触的方式安装在所述金属基板的所述一个主面上,所述第1电极焊盘、所述第2电极焊盘及所述第3电极焊盘的与所述蓝宝石基板相反的一侧的面与所述双面印刷配线基板的所述一个主面上的所述规定的配线的规定的部位连接而构成所述规定的电路。

10.一种半导体封装体,设置于金属基板的一个主面和双面印刷配线基板的一个主面之间来使用,其特征在于,

所述半导体封装体具备:

半导体芯片,具有长方形的平面形状,在厚度为 $120\mu\text{m}$ 以下的蓝宝石基板的第1主面上设置有构成二极管的半导体层,在所述半导体层上以三角形配置有第1电极、第2电极及第3电极;

第1电极焊盘和第2电极焊盘,分别与所述第1电极和所述第2电极接触而电连接,被拉出到所述半导体层的外部;及

电绝缘性的树脂,对所述第1电极、所述第2电极、所述第3电极、所述半导体层及所述蓝宝石基板的侧面进行密封,

当设所述半导体芯片的四个边在逆时针方向上依次为S<sub>1</sub>、S<sub>2</sub>、S<sub>3</sub>、S<sub>4</sub>时,所述第1电极具有具备与边S<sub>1</sub>平行的长边和与边S<sub>2</sub>平行的短边的细长的长方形形状,并且所述第1电极靠近边S<sub>1</sub>和S<sub>2</sub>地设置,所述第1电极的长边的长度比边S<sub>1</sub>的长度短,所述第2电极具有具备与边S<sub>3</sub>平行的长边和与边S<sub>2</sub>平行的短边的细长的长方形形状,并且所述第2电极靠近边S<sub>2</sub>和S<sub>3</sub>地设置,所述第2电极的长边的长度比边S<sub>3</sub>的长度短,所述第3电极具有具备与边S<sub>4</sub>平行的长边和与边S<sub>1</sub>平行的短边的长方形形状,并且所述第3电极在所述第1电极与边S<sub>4</sub>之间的区域中靠近边S<sub>1</sub>和S<sub>4</sub>地设置,

所述第1电极焊盘从所述第1电极经由所述树脂上而向与边S<sub>1</sub>垂直的方向且与所述半导体层和所述蓝宝石基板平行的方向突出,该突出的所述第1电极焊盘的前端与边S<sub>1</sub>平行,所述第2电极焊盘从所述第2电极经由所述树脂上而向与边S<sub>3</sub>垂直的方向且与所述半导体层和所述蓝宝石基板平行的方向突出,该突出的所述第2电极焊盘的前端与边S<sub>3</sub>平行,

所述第1电极和所述第2电极构成正极和负极,所述第1电极焊盘和所述第2电极焊盘构成正极焊盘和负极焊盘,

所述半导体封装体以使所述蓝宝石基板的第2主面与所述金属基板的所述一个主面接触的方式安装在所述金属基板的所述一个主面上,所述第1电极焊盘和所述第2电极焊盘的从所述树脂突出的部分的与所述蓝宝石基板相反的一侧的面与所述双面印刷配线基板的所述一个主面上的所述规定的配线的规定的部位连接而构成规定的电路。

11.一种半导体封装体,设置于金属基板的一个主面和双面印刷配线基板的一个主面之间来使用,其特征在于,

所述半导体封装体具备:

半导体芯片,具有长方形的平面形状,在厚度为 $120\mu\text{m}$ 以下的蓝宝石基板的第1主面上设置有构成二极管的半导体层,在所述半导体层上以三角形配置有第1电极、第2电极及第3电极;

第1电极焊盘和第2电极焊盘,分别与所述第1电极和所述第2电极接触而电连接,被拉出到所述半导体层的上方;及

电绝缘性的树脂,对所述第1电极、所述第2电极、所述第3电极、所述半导体层及所述蓝宝石基板的侧面进行密封,

当设所述半导体芯片的四个边在逆时针方向上依次为S<sub>1</sub>、S<sub>2</sub>、S<sub>3</sub>、S<sub>4</sub>时,所述第1电极具有具备与边S<sub>1</sub>平行的长边和与边S<sub>2</sub>平行的短边的细长的长方形形状,并且所述第1电极靠近边S<sub>1</sub>和S<sub>2</sub>地设置,所述第1电极的长边的长度比边S<sub>1</sub>的长度短,所述第2电极具有具备与边S<sub>3</sub>平行的长边和与边S<sub>2</sub>平行的短边的细长的长方形形状,并且所述第2电极靠近边S<sub>2</sub>和S<sub>3</sub>地设置,所述第2电极的长边的长度比边S<sub>3</sub>的长度短,所述第3电极具有具备与边S<sub>4</sub>平行的长边和与边S<sub>1</sub>平行的短边的长方形形状,并且所述第3电极在所述第1电极与边S<sub>4</sub>之间的区域中靠近边S<sub>1</sub>和S<sub>4</sub>地设置,

所述第1电极焊盘在被从所述第1电极相对于所述半导体层向垂直上方拉出之后,以跨过边S<sub>1</sub>的方式在所述半导体层的上方与所述半导体层平行地延伸,所述第1电极焊盘的外侧的前端与边S<sub>1</sub>平行,所述第2电极焊盘在被从所述第2电极相对于所述半导体层向垂直上方拉出之后,以跨过边S<sub>3</sub>的方式在所述半导体层的上方与所述半导体层平行地延伸,所述第2电极焊盘的外侧的前端与边S<sub>3</sub>平行,

所述树脂的轮廓比所述半导体芯片大所述半导体芯片的侧面的所述树脂的厚度的量,但与所述半导体芯片的外形基本相似,

所述第1电极焊盘的所述前端和所述第2电极焊盘的所述前端与所述树脂的轮廓一致,

所述第1电极和所述第2电极构成正极和负极,所述第1电极焊盘和所述第2电极焊盘构成正极焊盘和负极焊盘,

所述半导体封装体以使所述蓝宝石基板的第2主面与所述金属基板的所述一个主面接触的方式安装在所述金属基板的所述一个主面上,所述第1电极焊盘和所述第2电极焊盘的与所述蓝宝石基板相反的一侧的面与所述双面印刷配线基板的所述一个主面上的规定的配线的规定的部位连接而构成规定的电路。

12.一种安装有半导体封装体的模块,具备:

金属基板;

一个或多个所述半导体封装体,安装在所述金属基板的一个主面上;及

双面印刷配线基板,在一个主面上具有规定的配线,所述规定的配线以构成规定的电路的方式设置在所述一个或多个半导体封装体上,

所述半导体封装体具备:

半导体芯片,具有长方形的平面形状,在厚度为120μm以下的蓝宝石基板的第1主面上设置有构成二极管的半导体层,在所述半导体层上以三角形配置有第1电极、第2电极及第3电极;

第1电极焊盘和第2电极焊盘,分别与所述第1电极和所述第2电极接触而电连接,被拉出到所述半导体层的外部;及

电绝缘性的树脂,对所述第1电极、所述第2电极、所述第3电极、所述半导体层及所述蓝宝石基板的侧面进行密封,

当设所述半导体芯片的四个边在逆时针方向上依次为S<sub>1</sub>、S<sub>2</sub>、S<sub>3</sub>、S<sub>4</sub>时,所述第1电极具有具备与边S<sub>1</sub>平行的长边和与边S<sub>2</sub>平行的短边的细长的长方形形状,并且所述第1电极靠近边S<sub>1</sub>和S<sub>2</sub>地设置,所述第1电极的长边的长度比边S<sub>1</sub>的长度短,所述第2电极具有具备与边S<sub>3</sub>平

行的长边和与边S<sub>2</sub>平行的短边的细长的长方形形状，并且所述第2电极靠近边S<sub>2</sub>和S<sub>3</sub>地设置，所述第2电极的长边的长度比边S<sub>3</sub>的长度短，所述第3电极具有具备与边S<sub>4</sub>平行的长边和与边S<sub>1</sub>平行的短边的长方形形状，并且所述第3电极在所述第1电极与边S<sub>4</sub>之间的区域中靠近边S<sub>1</sub>和S<sub>4</sub>地设置，

所述第1电极焊盘从所述第1电极经由所述树脂上而向与边S<sub>1</sub>垂直的方向且与所述半导体层和所述蓝宝石基板平行的方向突出，该突出的所述第1电极焊盘的前端与边S<sub>1</sub>平行，所述第2电极焊盘从所述第2电极经由所述树脂上而向与边S<sub>3</sub>垂直的方向且与所述半导体层和所述蓝宝石基板平行的方向突出，该突出的所述第2电极焊盘的前端与边S<sub>3</sub>平行，

所述第1电极和所述第2电极构成正极和负极，所述第1电极焊盘和所述第2电极焊盘构成正极焊盘和负极焊盘，

所述半导体封装体以使所述蓝宝石基板的第2主面与所述金属基板的所述一个主面接触的方式安装在所述金属基板的所述一个主面上，所述第1电极焊盘和所述第2电极焊盘的从所述树脂突出的部分的与所述蓝宝石基板相反的一侧的面与所述双面印刷配线基板的所述一个主面上的所述规定的配线的规定的部位连接而构成所述规定的电路。

13.一种安装有半导体封装体的模块，具备：

金属基板；

一个或多个所述半导体封装体，安装在所述金属基板的一个主面上；及

双面印刷配线基板，在一个主面上具有规定的配线，所述规定的配线以构成规定的电路的方式设置在所述一个或多个半导体封装体上，

所述半导体封装体具备：

半导体芯片，具有长方形的平面形状，在厚度为120μm以下的蓝宝石基板的第1主面上设置有构成二极管的半导体层，在所述半导体层上以三角形配置有第1电极、第2电极及第3电极；

第1电极焊盘和第2电极焊盘，分别与所述第1电极和所述第2电极接触而电连接，被拉出到所述半导体层的上方；及

电绝缘性的树脂，对所述第1电极、所述第2电极、所述第3电极、所述半导体层及所述蓝宝石基板的侧面进行密封，

当设所述半导体芯片的四个边在逆时针方向上依次为S<sub>1</sub>、S<sub>2</sub>、S<sub>3</sub>、S<sub>4</sub>时，所述第1电极具有具备与边S<sub>1</sub>平行的长边和与边S<sub>2</sub>平行的短边的细长的长方形形状，并且所述第1电极靠近边S<sub>1</sub>和S<sub>2</sub>地设置，所述第1电极的长边的长度比边S<sub>1</sub>的长度短，所述第2电极具有具备与边S<sub>3</sub>平行的长边和与边S<sub>2</sub>平行的短边的细长的长方形形状，并且所述第2电极靠近边S<sub>2</sub>和S<sub>3</sub>地设置，所述第2电极的长边的长度比边S<sub>3</sub>的长度短，所述第3电极具有具备与边S<sub>4</sub>平行的长边和与边S<sub>1</sub>平行的短边的长方形形状，并且所述第3电极在所述第1电极与边S<sub>4</sub>之间的区域中靠近边S<sub>1</sub>和S<sub>4</sub>地设置，

所述第1电极焊盘在被从所述第1电极相对于所述半导体层向垂直上方拉出之后，以跨过边S<sub>1</sub>的方式在所述半导体层的上方与所述半导体层平行地延伸，所述第1电极焊盘的外侧的前端与边S<sub>1</sub>平行，所述第2电极焊盘在被从所述第2电极相对于所述半导体层向垂直上方拉出之后，以跨过边S<sub>3</sub>的方式在所述半导体层的上方与所述半导体层平行地延伸，所述第2电极焊盘的外侧的前端与边S<sub>3</sub>平行，

所述树脂的轮廓比所述半导体芯片大所述半导体芯片的侧面的所述树脂的厚度的量，但与所述半导体芯片的外形基本相似，

所述第1电极焊盘的所述前端和所述第2电极焊盘的所述前端与所述树脂的轮廓一致，

所述第1电极和所述第2电极构成正极和负极，所述第1电极焊盘和所述第2电极焊盘构成正极焊盘和负极焊盘，

所述半导体封装体以使所述蓝宝石基板的第2主面与所述金属基板的所述一个主面接触的方式安装在所述金属基板的所述一个主面上，所述第1电极焊盘和所述第2电极焊盘的与所述蓝宝石基板相反的一侧的面与所述双面印刷配线基板的所述一个主面上的所述规定的配线的规定的部位连接而构成所述规定的电路。

14. 一种电气设备，具备一个或多个模块，

至少一个所述模块是如下的模块，即，具备：

金属基板；

一个或多个半导体封装体，安装在所述金属基板的一个主面上；及

双面印刷配线基板，在一个主面上具有规定的配线，所述规定的配线以构成规定的电路的方式设置在所述一个或多个半导体封装体上，

所述半导体封装体具备：

半导体芯片，具有长方形的平面形状，在厚度为 $120\mu\text{m}$ 以下的蓝宝石基板的第1主面上设置有构成二极管的半导体层，在所述半导体层上以三角形配置有第1电极、第2电极及第3电极；

第1电极焊盘和第2电极焊盘，分别与所述第1电极和所述第2电极接触而电连接，被拉出到所述半导体层的外部；及

电绝缘性的树脂，对所述第1电极、所述第2电极、所述第3电极、所述半导体层及所述蓝宝石基板的侧面进行密封，

当设所述半导体芯片的四个边在逆时针方向上依次为 $S_1$ 、 $S_2$ 、 $S_3$ 、 $S_4$ 时，所述第1电极具有具备与边 $S_1$ 平行的长边和与边 $S_2$ 平行的短边的细长的长方形形状，并且所述第1电极靠近边 $S_1$ 和 $S_2$ 地设置，所述第1电极的长边的长度比边 $S_1$ 的长度短，所述第2电极具有具备与边 $S_3$ 平行的长边和与边 $S_2$ 平行的短边的细长的长方形形状，并且所述第2电极靠近边 $S_2$ 和 $S_3$ 地设置，所述第2电极的长边的长度比边 $S_3$ 的长度短，所述第3电极具有具备与边 $S_4$ 平行的长边和与边 $S_1$ 平行的短边的长方形形状，并且所述第3电极在所述第1电极与边 $S_4$ 之间的区域中靠近边 $S_1$ 和 $S_4$ 地设置，

所述第1电极焊盘从所述第1电极经由所述树脂上而向与边 $S_1$ 垂直的方向且与所述半导体层和所述蓝宝石基板平行的方向突出，该突出的所述第1电极焊盘的前端与边 $S_1$ 平行，所述第2电极焊盘从所述第2电极经由所述树脂上而向与边 $S_3$ 垂直的方向且与所述半导体层和所述蓝宝石基板平行的方向突出，该突出的所述第2电极焊盘的前端与边 $S_3$ 平行，

所述第1电极和所述第2电极构成正极和负极，所述第1电极焊盘和所述第2电极焊盘构成正极焊盘和负极焊盘，

所述半导体封装体以使所述蓝宝石基板的第2主面与所述金属基板的所述一个主面接触的方式安装在所述金属基板的所述一个主面上，所述第1电极焊盘和所述第2电极焊盘的从所述树脂突出的部分的与所述蓝宝石基板相反的一侧的面与所述双面印刷配线基板的

所述一个主面上的所述规定的配线的规定的部位连接而构成所述规定的电路。

15. 一种电气设备,具备一个或多个模块,

至少一个所述模块是如下的模块,即,具备:

金属基板;

一个或多个半导体封装体,安装在所述金属基板的一个主面上;及

双面印刷配线基板,在一个主面上具有规定的配线,所述规定的配线以构成规定的电路的方式设置在所述一个或多个半导体封装体上,

所述半导体封装体具备:

半导体芯片,具有长方形的平面形状,在厚度为 $120\mu\text{m}$ 以下的蓝宝石基板的第1主面上设置有构成二极管的半导体层,在所述半导体层上以三角形配置有第1电极、第2电极及第3电极;

第1电极焊盘和第2电极焊盘,分别与所述第1电极和所述第2电极接触而电连接,被拉出到所述半导体层的上方;及

电绝缘性的树脂,对所述第1电极、所述第2电极、所述第3电极、所述半导体层及所述蓝宝石基板的侧面进行密封,

当设所述半导体芯片的四个边在逆时针方向上依次为S<sub>1</sub>、S<sub>2</sub>、S<sub>3</sub>、S<sub>4</sub>时,所述第1电极具有具备与边S<sub>1</sub>平行的长边和与边S<sub>2</sub>平行的短边的细长的长方形形状,并且所述第1电极靠近边S<sub>1</sub>和S<sub>2</sub>地设置,所述第1电极的长边的长度比边S<sub>1</sub>的长度短,所述第2电极具有具备与边S<sub>3</sub>平行的长边和与边S<sub>2</sub>平行的短边的细长的长方形形状,并且所述第2电极靠近边S<sub>2</sub>和S<sub>3</sub>地设置,所述第2电极的长边的长度比边S<sub>3</sub>的长度短,所述第3电极具有具备与边S<sub>4</sub>平行的长边和与边S<sub>1</sub>平行的短边的长方形形状,并且所述第3电极在所述第1电极与边S<sub>4</sub>之间的区域中靠近边S<sub>1</sub>和S<sub>4</sub>地设置,

所述第1电极焊盘在被从所述第1电极相对于所述半导体层向垂直上方拉出之后,以跨过边S<sub>1</sub>的方式在所述半导体层的上方与所述半导体层平行地延伸,所述第1电极焊盘的外侧的前端与边S<sub>1</sub>平行,所述第2电极焊盘在被从所述第2电极相对于所述半导体层向垂直上方拉出之后,以跨过边S<sub>3</sub>的方式在所述半导体层的上方与所述半导体层平行地延伸,所述第2电极焊盘的外侧的前端与边S<sub>3</sub>平行,

所述树脂的轮廓比所述半导体芯片大所述半导体芯片的侧面的所述树脂的厚度的量,但与所述半导体芯片的外形基本相似,

所述第1电极焊盘的所述前端和所述第2电极焊盘的所述前端与所述树脂的轮廓一致,

所述第1电极和所述第2电极构成正极和负极,所述第1电极焊盘和所述第2电极焊盘构成正极焊盘和负极焊盘,

所述半导体封装体以使所述蓝宝石基板的第2主面与所述金属基板的所述一个主面接触的方式安装在所述金属基板的所述一个主面上,所述第1电极焊盘和所述第2电极焊盘的与所述蓝宝石基板相反的一侧的面与所述双面印刷配线基板的所述一个主面上的所述规定的配线的规定的部位连接而构成所述规定的电路。

## 半导体封装体、安装有半导体封装体的模块及电气设备

### 技术领域

[0001] 本发明涉及半导体封装体、模块及电气设备，特别是，涉及使用了氮化镓(GaN)系半导体的三端子或两端子半导体元件，例如对GaN系场效应晶体管(FET)或GaN系二极管进行了封装而成的半导体封装体、包含该半导体封装体的模块及包含该模块的电气设备。

### 背景技术

[0002] 对于以往的高压电力系统的电子元件，主流的是硅(Si)-MOS晶体管、绝缘栅双极型晶体管(IGBT)及碳化硅(SiC)-MOS晶体管。这些电子元件具有将漏极设置在下表面且将源极和栅极设置在上表面的纵型结构。在这种纵型元件中，由于电极形成在上表面和下表面，因此要拉出电极，或者电路布线成为立体布线。另外，还公知有对多个上述的纵型元件的芯片进行整合封装化的方法。而且，在上述的纵型元件的裸芯片的安装中，一般使用在铜(Cu)基底基板上依次堆叠了氮化硅(SiN)层和Cu层的DBC(direct bonding Copper，覆铜陶瓷)基板。此时，在纵型元件的结构上，需要进行基于引线键合、导电条、端子等的立体布线。

[0003] 另一方面，由本发明人提出了利用了极化超结(Polarization Super Junction; PSJ)的、具有横型结构的功率GaN系场效应晶体管(FET)(参照专利文献1、2)。在该功率极化超结GaN系FET中，与上述的纵型元件不同，在构成FET的半导体层的同一面上设置有源极、漏极及由p电极构成的栅极。

[0004] 现有技术文献

[0005] 专利文献

[0006] 专利文献1：日本专利第5669119号说明书

[0007] 专利文献2：日本专利第5828435号说明书

### 发明内容

[0008] 发明所要解决的课题

[0009] 对于上述以往的纵型元件的封装及集成化的技术，实际情况是在低成本化、高频化、省体积化、低热阻化等中，正在达到技术饱和点。

[0010] 因此，本发明所要解决的课题在于，提供如下的半导体封装体、使用了该半导体封装体的高性能的模块及使用了该模块的高性能的电气设备：不使用具有纵型结构的电子元件而使用作为具有横型结构的电子元件的功率极化超结GaN系FET甚至GaN系二极管，更一般地说，使用在形成于绝缘基板上的半导体层的同一面上形成有所有的电极的三端子或两端子半导体元件，使该半导体元件以面朝上来容易地安装到基板上，且与以往相比能够实现大幅的低成本化、高频化、省体积化、低热阻化等。

[0011] 用于解决课题的手段

[0012] 为了解决所述课题，本发明提供一种半导体封装体，具有：

[0013] 半导体芯片，在绝缘基板的第1主面上设置有构成三端子半导体元件的半导体层，在所述半导体层上以三角形配置有第1电极、第2电极及第3电极；

[0014] 第1电极焊盘、第2电极焊盘及第3电极焊盘，分别与所述第1电极、所述第2电极及所述第3电极电连接，被拉出到所述半导体层的外部或上方；及

[0015] 电绝缘性的树脂，对所述半导体层、所述第1电极、所述第2电极、所述第3电极及所述绝缘基板的侧面进行密封。

[0016] 在典型的一例中，第1电极焊盘、第2电极焊盘及第3电极焊盘在分别从第1电极、第2电极及第3电极与半导体层和绝缘基板平行地在树脂上延伸之后垂直地弯曲而沿着该树脂的侧面与半导体层和绝缘基板的侧面平行地延伸，以与绝缘基板的第2主面相同的高度终止。或者，在其他的例子中，第1电极焊盘、第2电极焊盘及第3电极焊盘分别从第1电极、第2电极及第3电极经由树脂上而向与半导体层和绝缘基板平行的方向突出。另外，半导体层在典型的情况下具有长方形状的平面形状，第1电极焊盘、第2电极焊盘及第3电极焊盘在典型的情况下以与该半导体层的包含彼此不同的四个角部中的彼此不同的一个或两个角部的规定的区域重叠的方式延伸。在典型的情况下，所述规定的区域具有在一个顶点包含一个或两个角部的长方形的平面形状。而且，在另一例子中，第1电极焊盘、第2电极焊盘及第3电极焊盘分别在被从第1电极、第2电极及第3电极相对于半导体层向垂直上方拉出之后，在半导体层的上方与半导体层平行地延伸。此时，在典型的情况下，半导体层具有长方形状的平面形状，第1电极焊盘、第2电极焊盘及第3电极焊盘以跨越半导体层的四个边中的彼此不同的一个边的方式延伸。

[0017] 密封用的树脂根据需要从第1电极焊盘、第2电极焊盘及第3电极焊盘之间的区域在这些第1电极焊盘、第2电极焊盘及第3电极焊盘上延伸。由此，能够充分确保树脂的厚度，能够实现半导体封装体的强度的提高。或者，该树脂也可以从绝缘基板的侧面在该绝缘基板的第2主面上以留下该第2主面的中央部的区域的方式延伸到该中央部的区域。由此，同样能够充分确保树脂的厚度，能够实现半导体封装体的强度的提高。此时，根据需要，在该绝缘基板的第2主面的中央部的区域(也可以换言之形成于在绝缘基板的第2主面上延伸的树脂的开口)设置导热层。

[0018] 在典型的情况下，虽然半导体层为GaN系半导体层，三端子半导体元件为GaN系场效应晶体管、尤其是极化超结GaN系场效应晶体管(参照专利文献1、2)，但是并不限于此。此时，第1电极、第2电极及第3电极为源极、漏极及栅极。

[0019] 关于绝缘基板，优选的是蓝宝石基板，且在典型的情况下为C面蓝宝石基板，但是并不限于此。对于该绝缘基板，优选的是使用薄的基板，以使得充分进行通过该绝缘基板的散热。例如，在该绝缘基板为蓝宝石基板时，其厚度优选选为150μm以下，一般例如选为50μm以上，更优选的是选为50μm以上120μm以下。

[0020] 另外，本发明提供一种模块，具备：

[0021] 金属基板；

[0022] 一个或多个半导体封装体，安装在所述金属基板的一个主面上；及

[0023] 配线，以构成规定的电路的方式设置在所述一个或多个半导体封装体上，

[0024] 所述半导体封装体具备：

[0025] 半导体芯片，在绝缘基板的第1主面上设置有构成三端子半导体元件的半导体层，在所述半导体层上以三角形配置有第1电极、第2电极及第3电极；

[0026] 第1电极焊盘、第2电极焊盘及第3电极焊盘，分别与所述第1电极、所述第2电极及

所述第3电极电连接,被拉出到所述半导体层的外部或上方;及

[0027] 电绝缘性的树脂,对所述半导体层、所述第1电极、所述第2电极、所述第3电极及所述绝缘基板的侧面进行密封,

[0028] 所述半导体封装体以使所述绝缘基板与所述金属基板接触的方式安装在所述金属基板的所述主面上,所述第1电极焊盘、所述第2电极焊盘及所述第3电极焊盘与所述规定的配线的规定的部位连接而构成所述规定的电路。

[0029] 此处,作为金属基板,最好使用散热性的基板,例如Cu基板、铝(Al)基板等。另外,虽然不特别限定以在半导体封装体上构成规定的电路的方式设置的配线的形成方法,但是例如使用一层或二层以上的引线框架。此时,在典型的情况下,设置有引线框架以与安装在金属基板上的半导体封装体的第1电极焊盘、第2电极焊盘及第3电极电连接。或者,也可以代替引线框架,使用双层柔性聚酰亚胺基板、或使用了环氧树脂基板的双面印刷配线基板(PCB)等。此时,能够通过形成在该双层柔性聚酰亚胺基板或环氧树脂基板的两面的Cu层的图案化来形成配线。

[0030] 另外,本发明提供一种电气设备,具备一个或多个模块,

[0031] 至少一个所述模块是如下的模块,即,具备:

[0032] 金属基板;

[0033] 一个或多个半导体封装体,安装在所述金属基板的一个主面上;及

[0034] 配线,以构成规定的电路的方式设置在所述一个或多个半导体封装体上,

[0035] 所述半导体封装体,具备:

[0036] 半导体芯片,在绝缘基板的第1主面上设置有构成三端子半导体元件的半导体层,在所述半导体层上以三角形配置有第1电极、第2电极及第3电极;

[0037] 第1电极焊盘、第2电极焊盘及第3电极焊盘,分别与所述第1电极、所述第2电极及所述第3电极电连接,被拉出到所述半导体层的外部或上方;及

[0038] 电绝缘性的树脂,对所述半导体层、所述第1电极、所述第2电极、所述第3电极及所述绝缘基板的侧面进行密封,

[0039] 所述半导体封装体以使所述绝缘基板与所述金属基板接触的方式安装在所述金属基板的所述主面上,所述第1电极焊盘、所述第2电极焊盘及所述第3电极焊盘与所述规定的配线的规定的部位连接而构成所述规定的电路。

[0040] 此处,电气设备大致包含所有的使用电器的设备,与用途、功能、大小等无关,例如,存在电子设备、移动体、动力装置、建设机械、工作机械等。电子设备为机器人、计算机、游戏设备、车载设备、家电产品(空调等)、工业产品、便携电话、移动设备、IT设备(服务器等)、在太阳能发电系统中使用的功率调节器、送电系统等。移动体为,铁路车辆、汽车(电动车等)、摩托车、飞机、火箭、航天器等。

[0041] 在所述模块和电气设备的各发明中,只要不与其性质相悖,则与所述半导体封装体的发明优选的说明成立。

[0042] 另外,本发明提供一种半导体封装体,具备:

[0043] 半导体芯片,在绝缘基板的第1主面上设置有构成两端子半导体元件的半导体层,在所述半导体层上彼此相对地配置有第1电极和第2电极;

[0044] 第1电极焊盘和第2电极焊盘,分别与所述第1电极和所述第2电极电连接,被拉出

到所述半导体层的外部或上方；及

[0045] 电绝缘性的树脂，对所述半导体层、所述第1电极、所述第2电极及所述绝缘基板的侧面进行密封。

[0046] 另外，本发明提供一种模块，具备：

[0047] 金属基板；

[0048] 一个或多个半导体封装体，安装在所述金属基板的一个主面上；及

[0049] 配线，以构成规定的电路的方式设置在所述一个或多个半导体封装体上，

[0050] 所述半导体封装体具备：

[0051] 半导体芯片，在绝缘基板的第1主面上设置有构成两端子半导体元件的半导体层，在所述半导体层上彼此相对地配置有第1电极和第2电极；

[0052] 第1电极焊盘和第2电极焊盘，分别与所述第1电极和所述第2电极电连接，被拉出到所述半导体层的外部或上方；及

[0053] 电绝缘性的树脂，对所述半导体层、所述第1电极、所述第2电极及所述绝缘基板的侧面进行密封，

[0054] 所述半导体封装体以使所述绝缘基板与所述金属基板接触的方式安装到所述金属基板的所述主面上，所述第1电极焊盘和所述第2电极焊盘与所述规定的配线的规定的部位连接而构成所述规定的电路。

[0055] 另外，本发明提供一种电气设备，具备一个或多个模块，

[0056] 至少一个所述模块是如下的模块，即，具备：

[0057] 金属基板；

[0058] 一个或多个半导体封装体，安装在所述金属基板的一个主面上；及

[0059] 配线，以构成规定的电路的方式设置在所述一个或多个半导体封装体上，

[0060] 所述半导体封装体具备：

[0061] 半导体芯片，在绝缘基板的第1主面上设置有构成两端子半导体元件的半导体层，在所述半导体层上彼此相对地配置有第1电极和第2电极；

[0062] 第1电极焊盘和第2电极焊盘，分别与所述第1电极和所述第2电极电连接，被拉出到所述半导体层的外部或上方；及

[0063] 电绝缘性的树脂，对所述半导体层、所述第1电极、所述第2电极及所述绝缘基板的侧面进行密封，

[0064] 所述半导体封装体以使所述绝缘基板与所述金属基板接触的方式安装到所述金属基板的所述主面上，所述第1电极焊盘和所述第2电极焊盘与所述规定的配线的规定的部位连接而构成所述规定的电路。

[0065] 在上述的两端子半导体元件的半导体封装体、模块及电气设备的各发明中，只要不与其性质相悖，则与所述半导体封装体、模块及电气设备的各发明有关的说明成立。

[0066] 发明效果

[0067] 根据本发明，使用如下的半导体封装体，即该半导体封装体具备：半导体芯片，在绝缘基板的第1主面上设置有构成三端子或两端子半导体元件的半导体层，第1电极、第2电极及第3电极以三角形配置在该半导体层上，或者，第1电极和第2电极彼此相对配置；及第1电极焊盘、第2电极焊盘及第3电极焊盘或者第1电极焊盘和第2电极焊盘，分别与第1电极、

第2电极及第3电极或者与第1电极和第2电极电连接，拉出到半导体层的外部或上方，并且使该半导体封装体的半导体芯片的绝缘基板侧朝向金属基板，拉出到半导体层的外部或上方的第1电极焊盘、第2电极焊盘及第3电极焊盘或者第1电极焊盘和第2电极焊盘与形成在半导体封装体上的配线连接，从而能够容易将三端子或两端子半导体元件以面朝上安装到金属基板上，与以往相比能够实现大幅的低成本化、高频化、省体积化、低热阻化等。而且，第1电极、第2电极及第3电极配置为三角形，因此第1电极焊盘、第2电极焊盘及第3电极焊盘也能够配置为三角形，因此能够将半导体封装体上的配线形成为彼此不交叉。由此，能够容易实现安装有半导体封装体的高性能的模块。并且，通过使用该模块能够便宜地实现高性能的电气设备。

### 附图说明

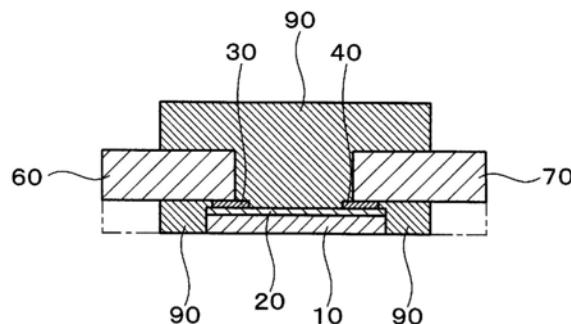

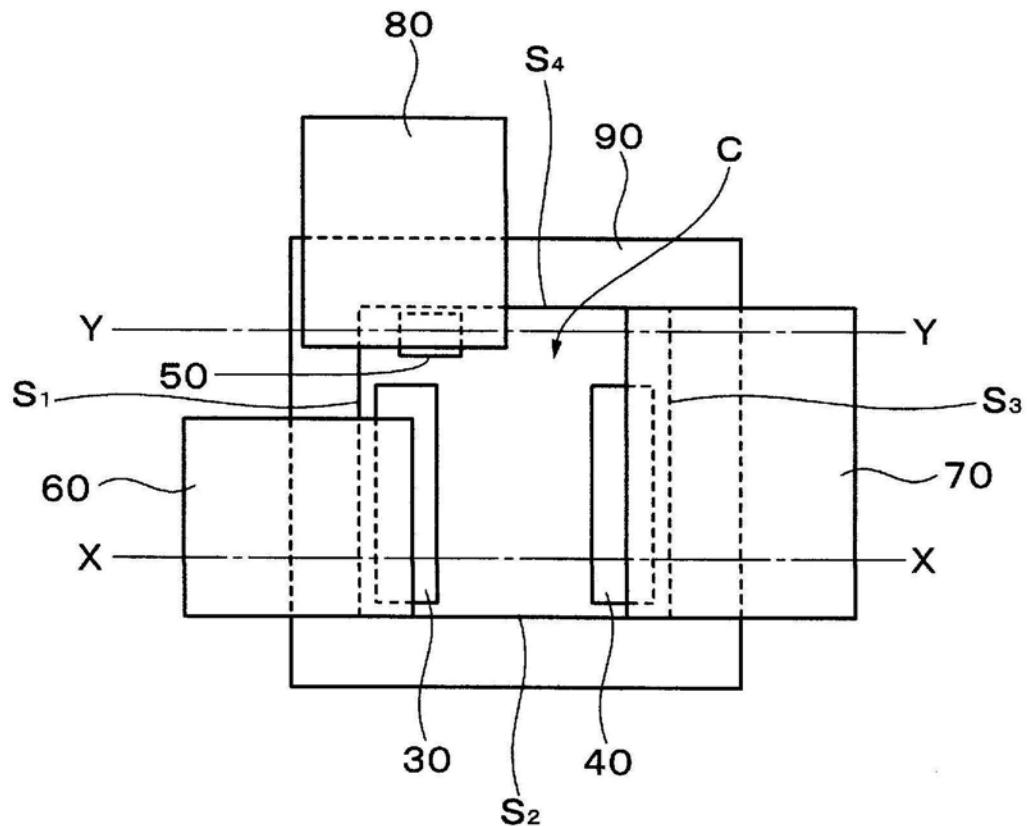

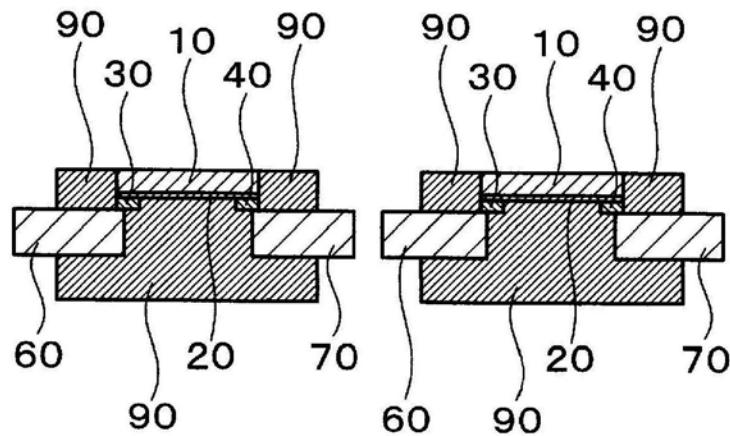

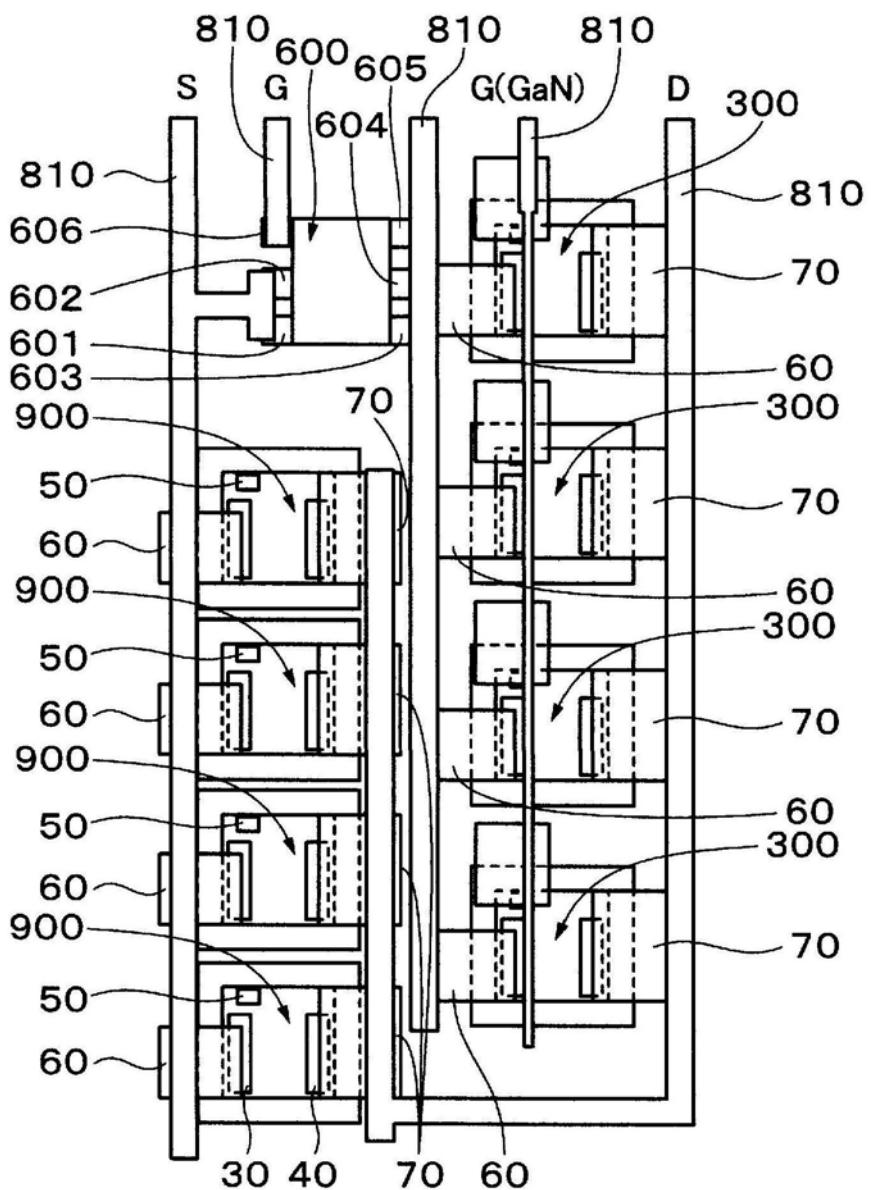

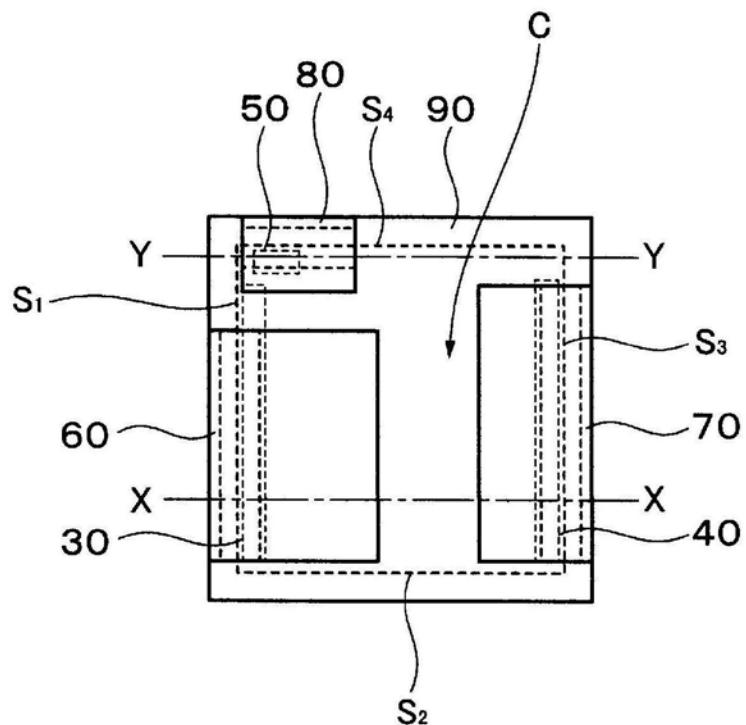

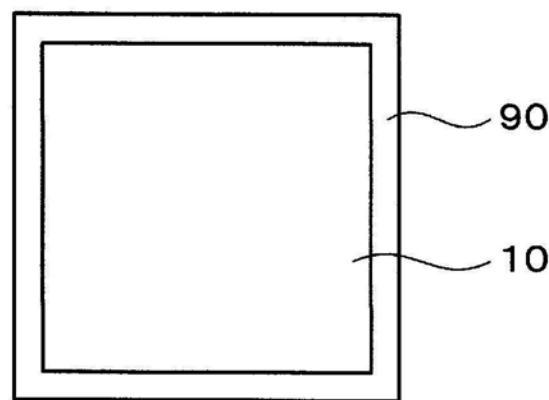

- [0068] 图1是示出本发明的第1实施方式的半导体封装体的俯视图。

- [0069] 图2是示出本发明的第1实施方式的半导体封装体的仰视图。

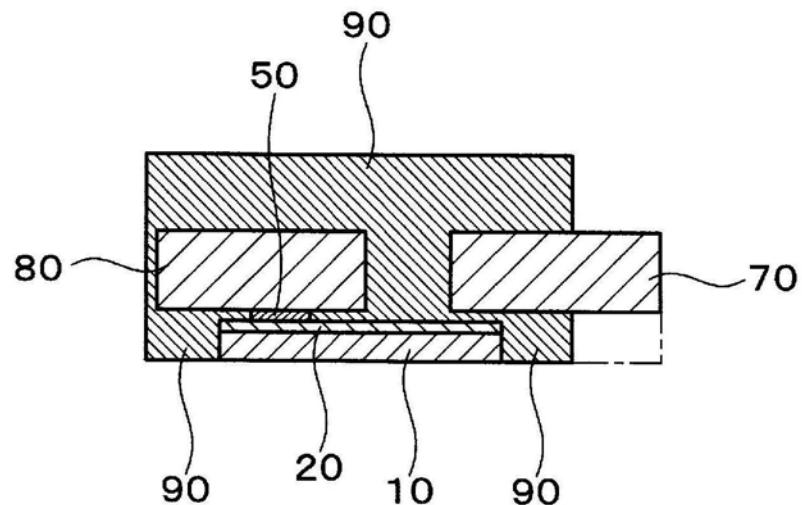

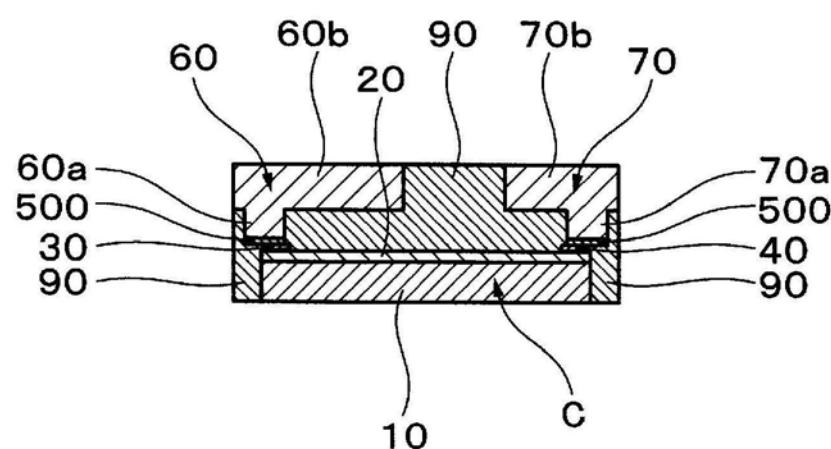

- [0070] 图3是沿着图1的X-X线的剖视图。

- [0071] 图4是沿着图1的Y-Y线的剖视图。

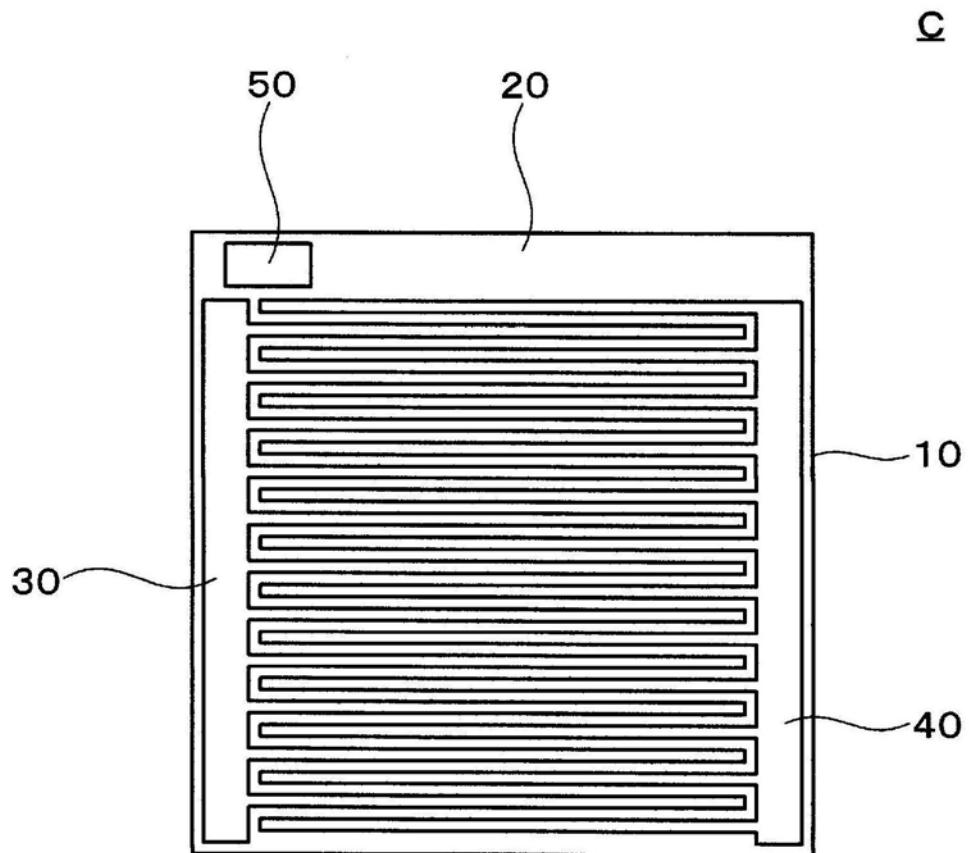

- [0072] 图5是示出本发明的第1实施方式的半导体封装体中的半导体芯片C的具体例的俯视图。

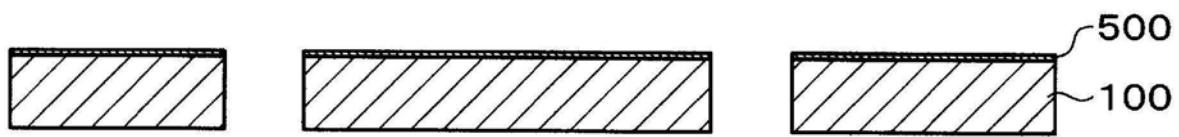

- [0073] 图6A是用于说明本发明的第1实施方式的半导体封装体的制造方法的剖视图。

- [0074] 图6B是用于说明本发明的第1实施方式的半导体封装体的制造方法的剖视图。

- [0075] 图6C是用于说明本发明的第1实施方式的半导体封装体的制造方法的剖视图。

- [0076] 图6D是用于说明本发明的第1实施方式的半导体封装体的制造方法的剖视图。

- [0077] 图6E是用于说明本发明的第1实施方式的半导体封装体的制造方法的剖视图。

- [0078] 图7是用于说明本发明的第1实施方式的半导体封装体的制造方法的俯视图。

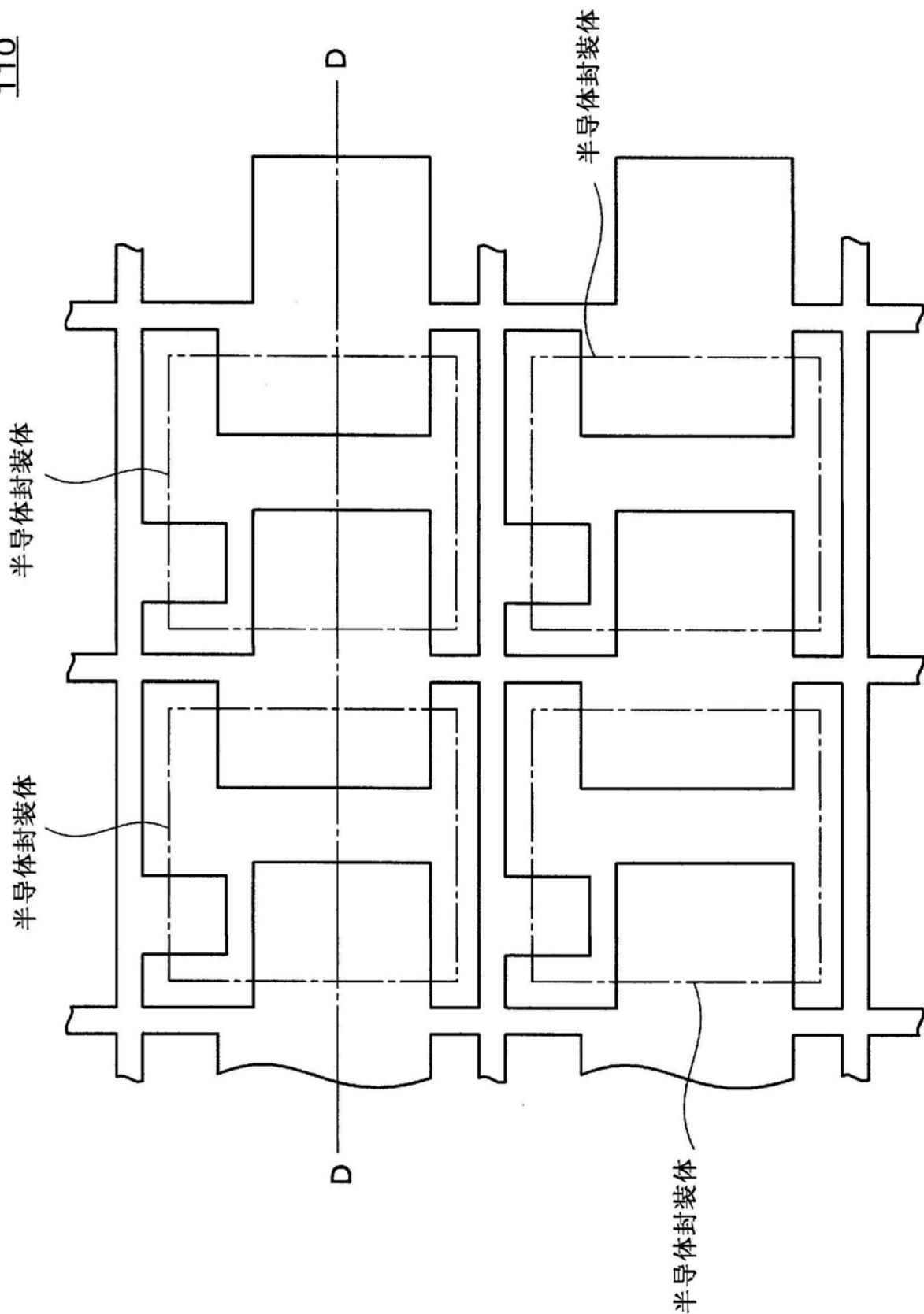

- [0079] 图8是用于说明本发明的第1实施方式的半导体封装体的制造方法的俯视图。

- [0080] 图9是用于说明本发明的第1实施方式的半导体封装体的制造方法的俯视图。

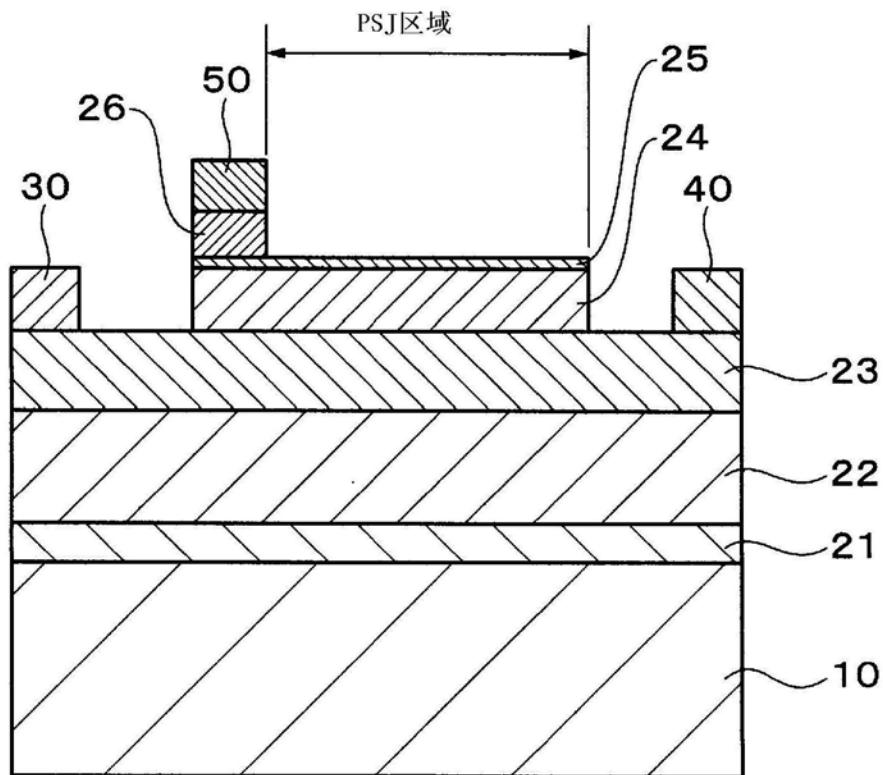

- [0081] 图10是示出本发明的第1实施方式的被半导体封装体密封的、构成极化超结GaN系FET的半导体芯片的一例的剖视图。

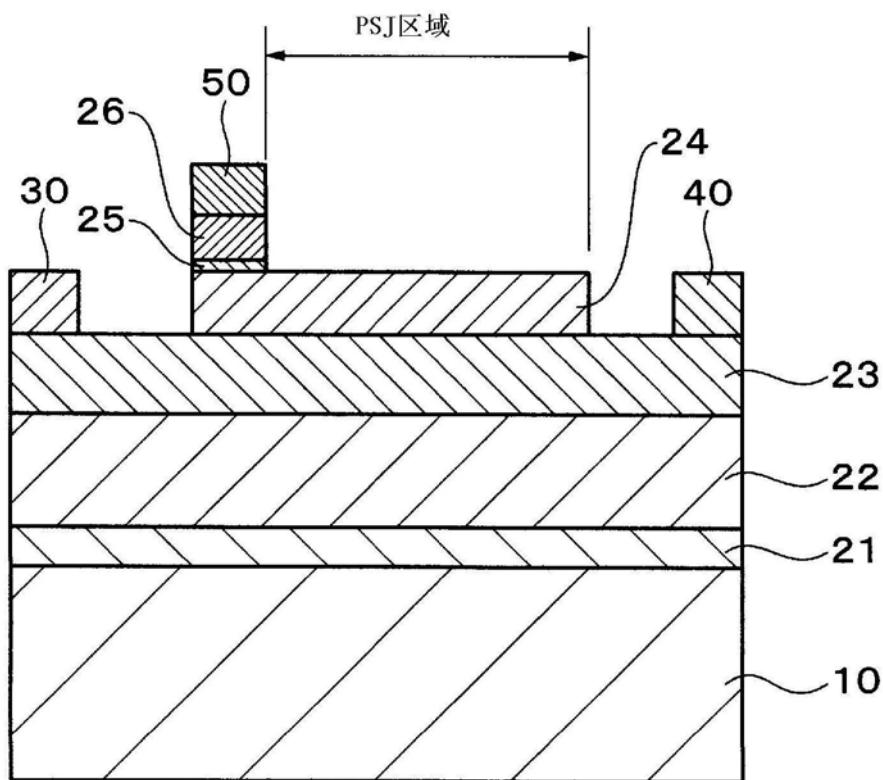

- [0082] 图11是示出本发明的第1实施方式的被半导体封装体密封的、构成极化超结GaN系FET的半导体芯片的另一例的剖视图。

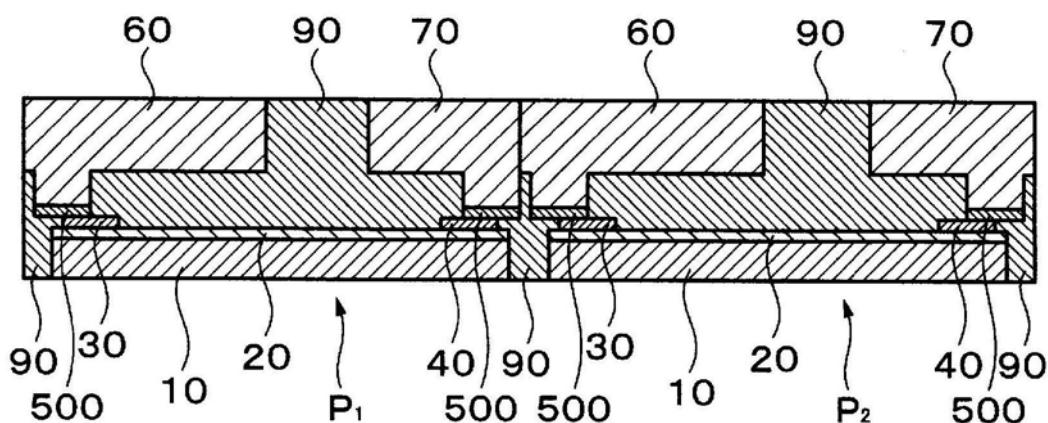

- [0083] 图12是用于说明安装本发明的第1实施方式的半导体封装体的方法的剖视图。

- [0084] 图13A是示出安装了本发明的第1实施方式的半导体封装体的模块的电路图。

- [0085] 图13B是示出安装了本发明的第1实施方式的半导体封装体的模块的俯视图。

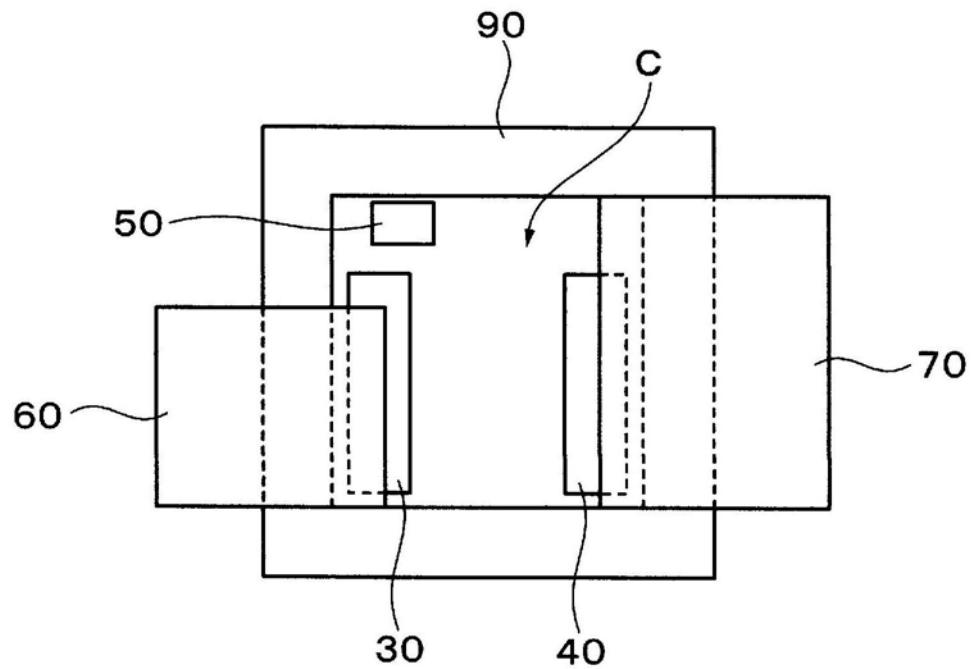

- [0086] 图14是示出在安装了本发明的第1实施方式的半导体封装体的模块中使用的反接保护用二极管的俯视图。

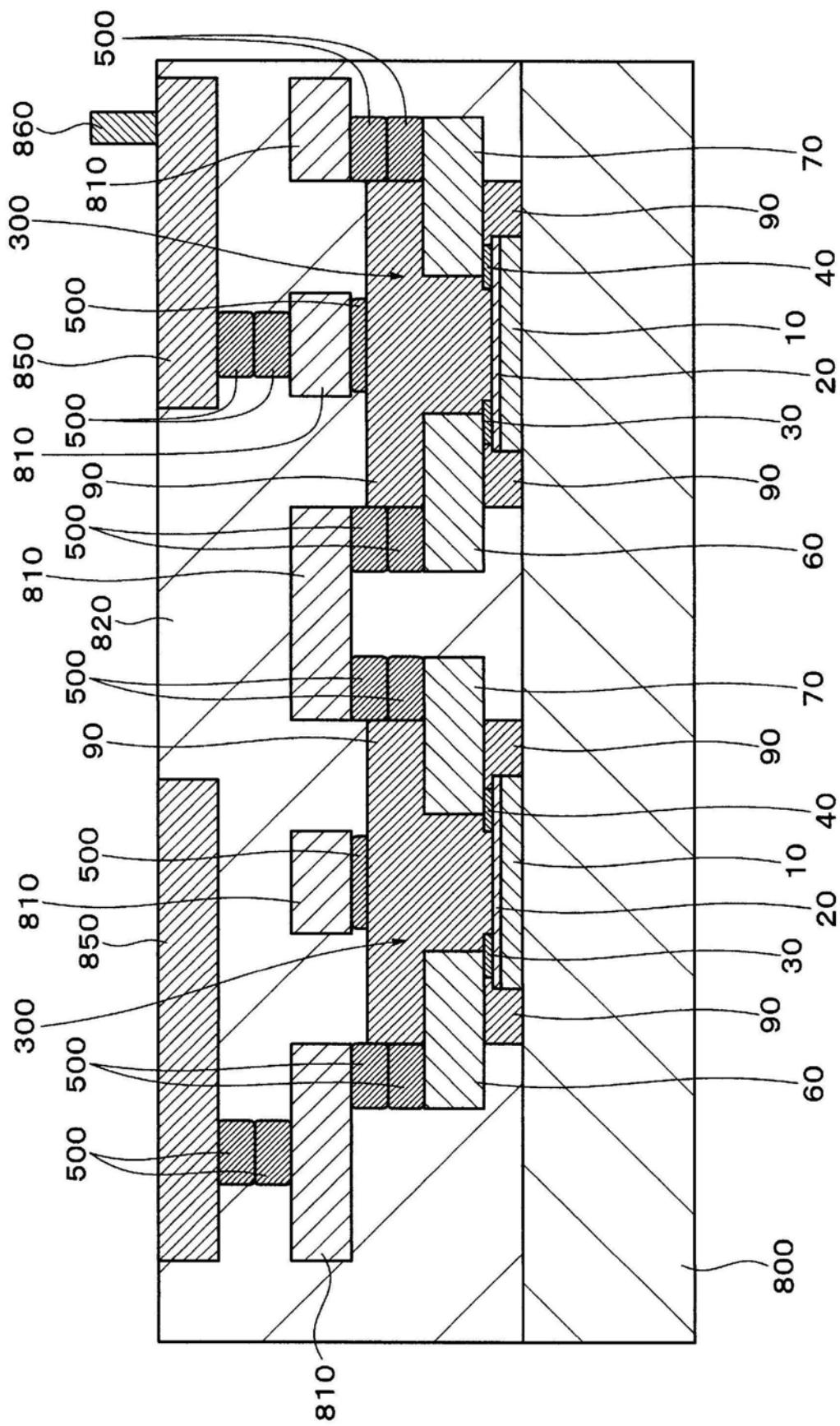

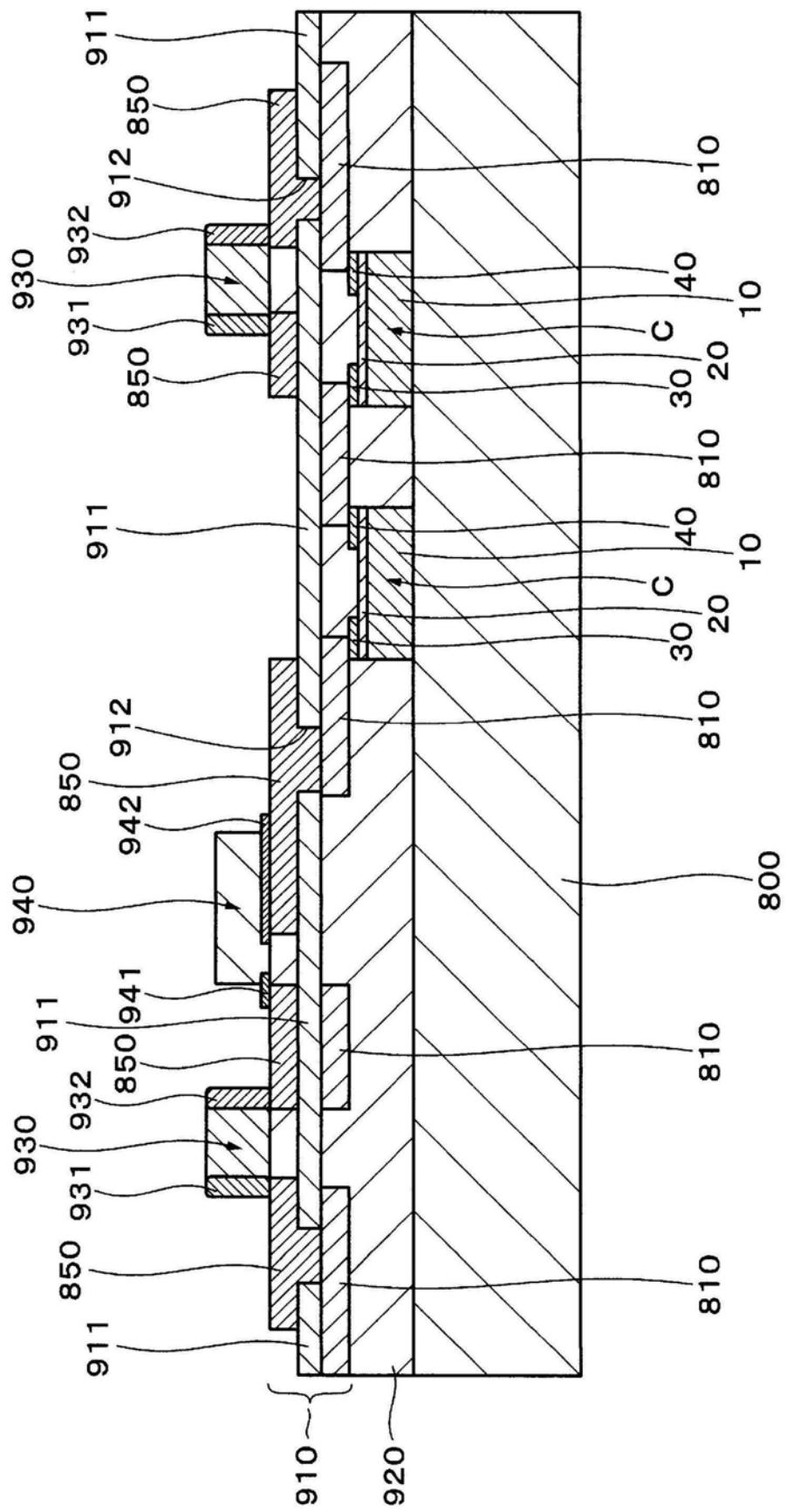

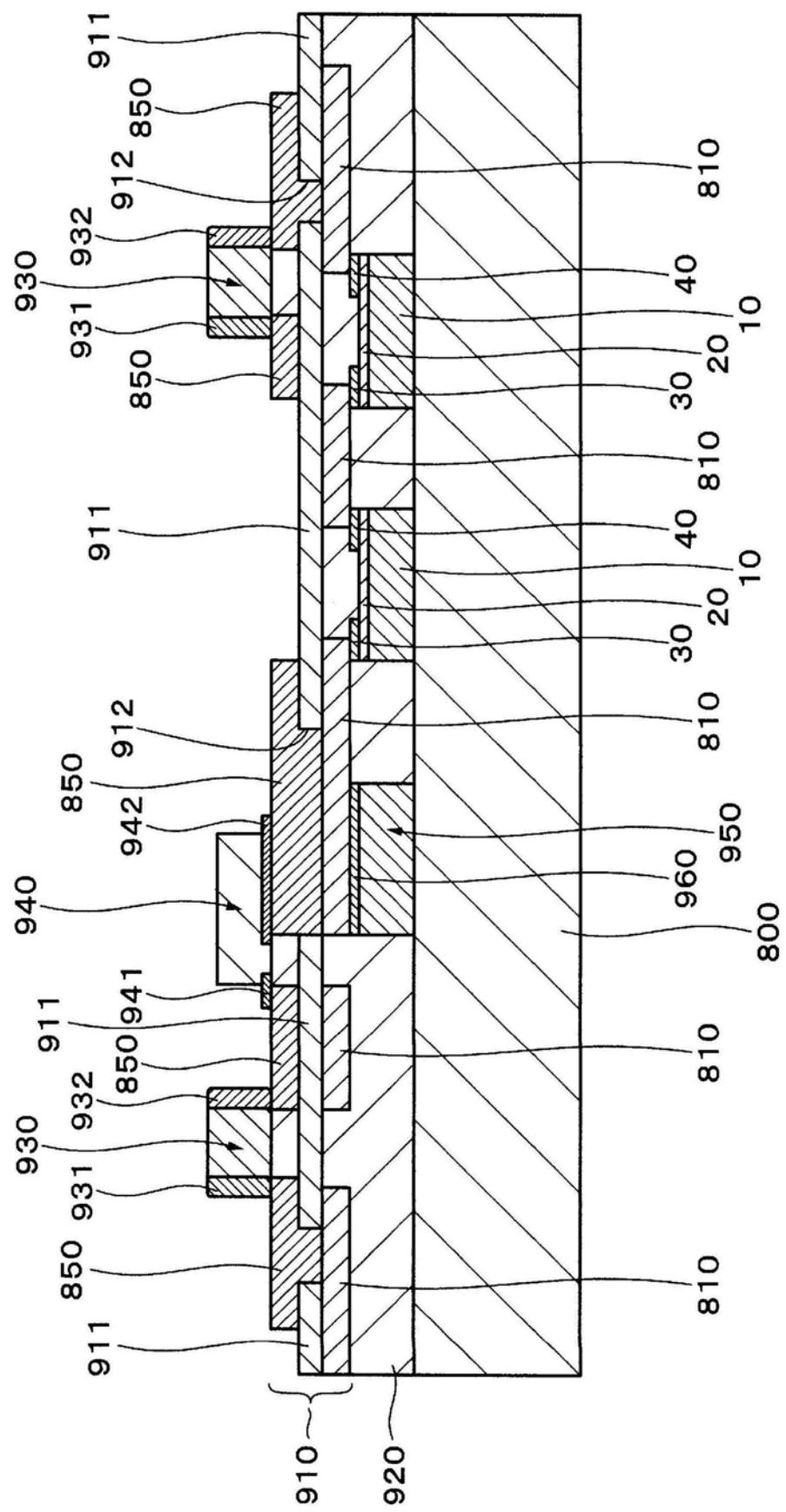

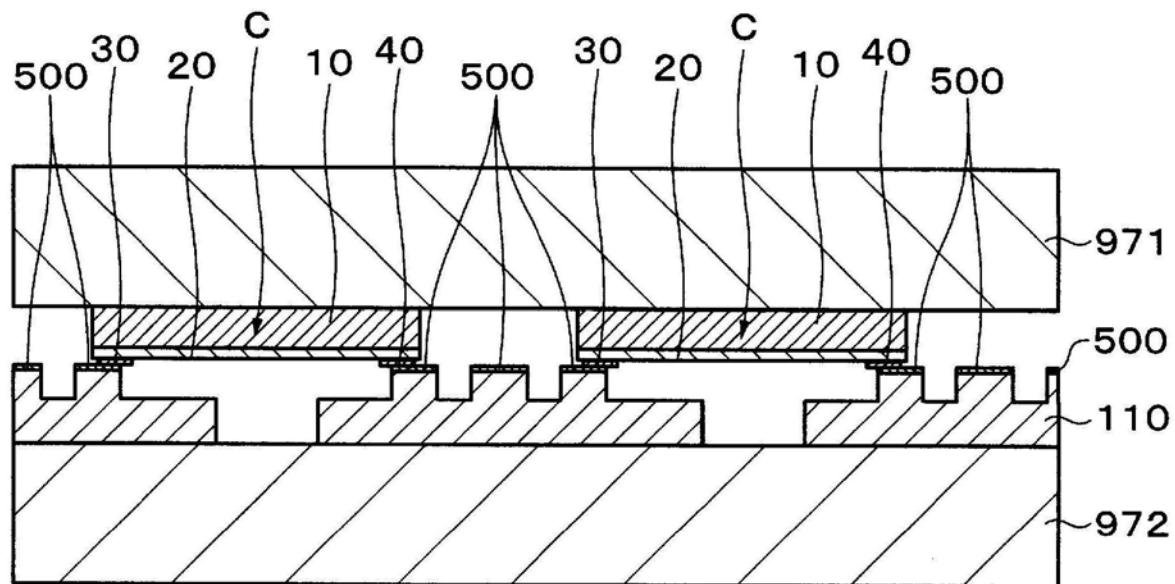

- [0087] 图15是用于说明在本发明的第2实施方式中安装第1实施方式的半导体封装体的方法的剖视图。

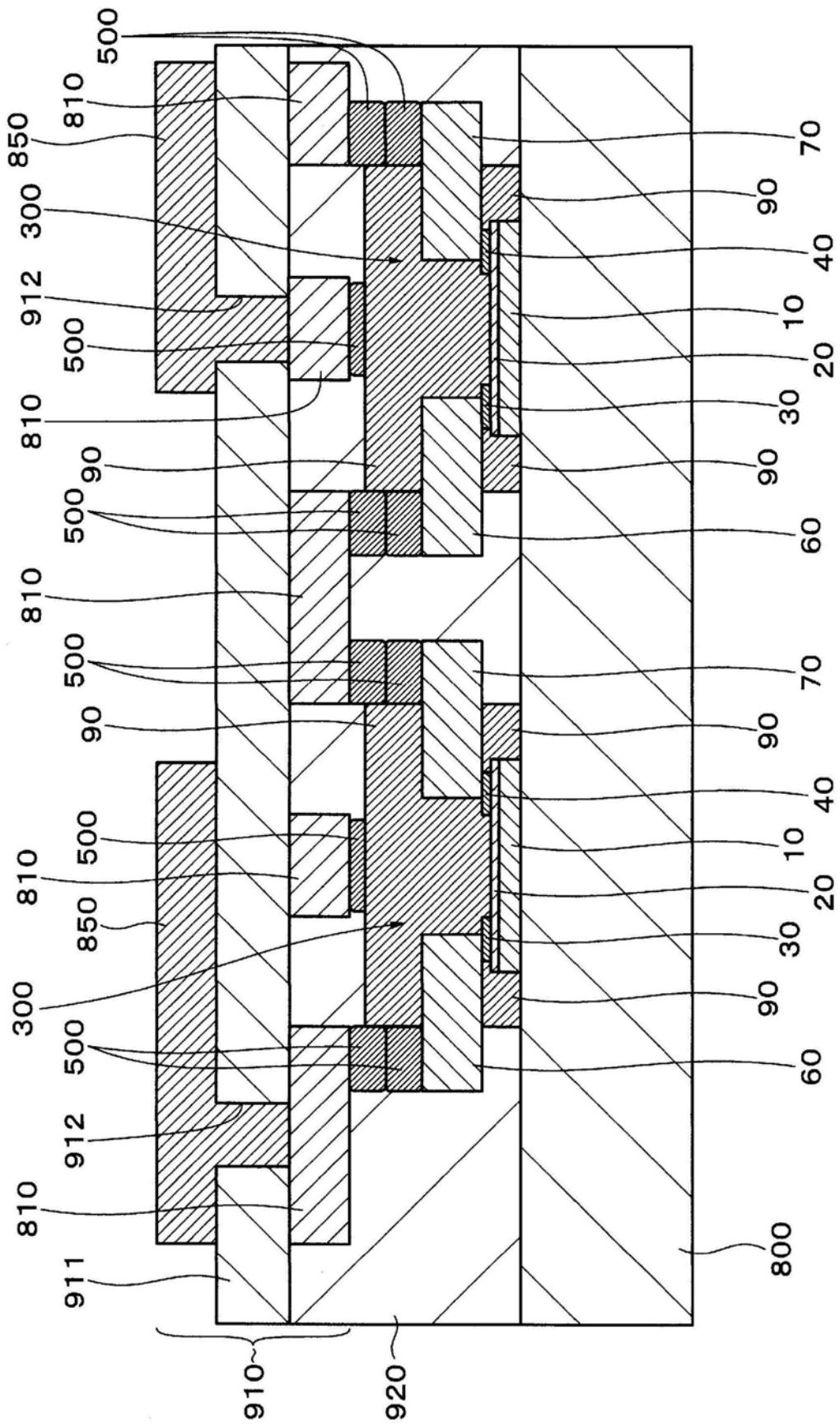

- [0088] 图16是用于说明在本发明的第3实施方式中安装第1实施方式的半导体封装体的方法的剖视图。

- [0089] 图17是用于说明在本发明的第4实施方式中安装第1实施方式的半导体封装体和

GaN系半导体芯片的方法的剖视图。

[0090] 图18是用于说明在本发明的第5实施方式中安装第1实施方式的半导体封装体和GaN系半导体芯片的方法的剖视图。

[0091] 图19是示出本发明的第6实施方式的半导体封装体的剖视图。

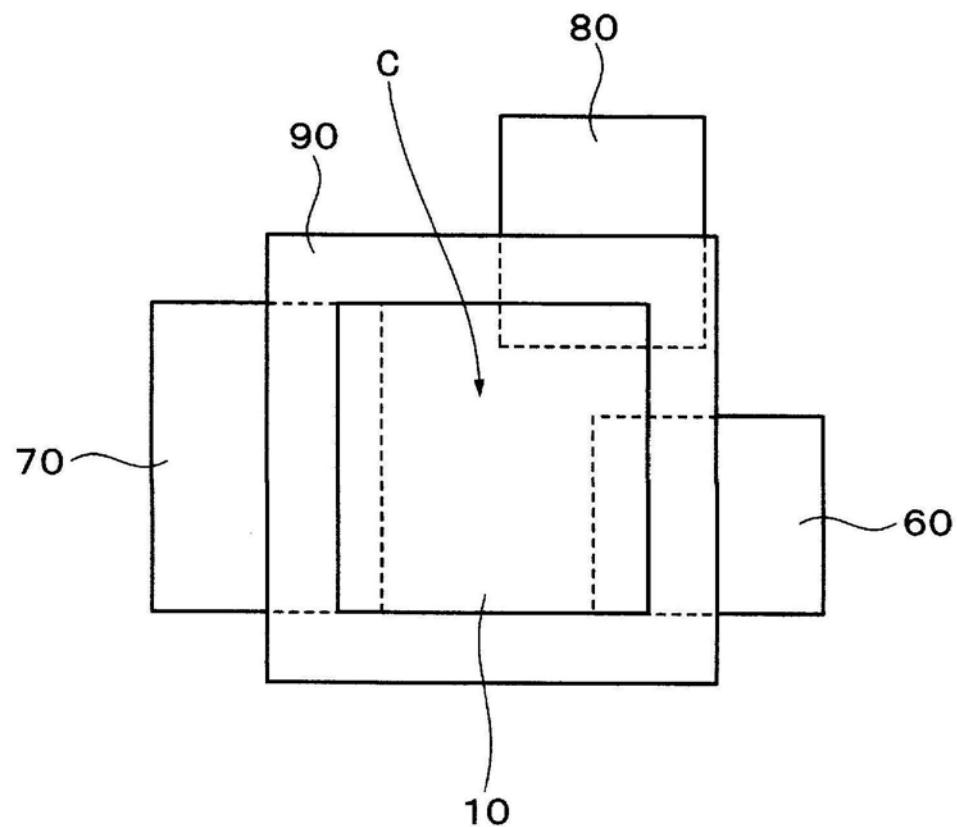

[0092] 图20是示出本发明的第7实施方式的半导体封装体的俯视图。

[0093] 图21是示出本发明的第7实施方式的半导体封装体的仰视图。

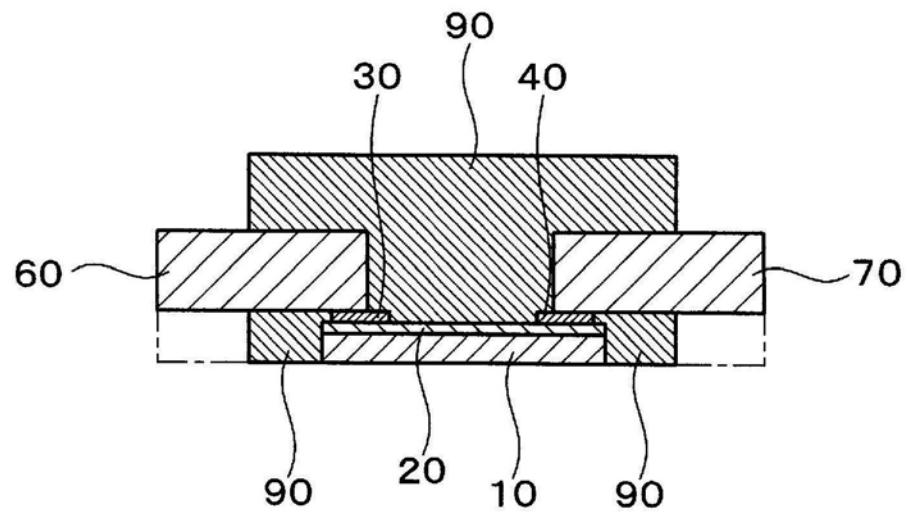

[0094] 图22是沿着图20的X-X线的剖视图。

[0095] 图23是沿着图20的Y-Y线的剖视图。

[0096] 图24A是用于说明本发明的第7实施方式的半导体封装体的制造方法的剖视图。

[0097] 图24B是用于说明本发明的第7实施方式的半导体封装体的制造方法的剖视图。

[0098] 图24C是用于说明本发明的第7实施方式的半导体封装体的制造方法的剖视图。

[0099] 图24D是用于说明本发明的第7实施方式的半导体封装体的制造方法的剖视图。

[0100] 图25A是用于说明本发明的第7实施方式的半导体封装体的制造方法的剖视图。

[0101] 图25B是用于说明本发明的第7实施方式的半导体封装体的制造方法的剖视图。

[0102] 图26A是用于说明本发明的第7实施方式的半导体封装体的制造方法的剖视图。

[0103] 图26B是用于说明本发明的第7实施方式的半导体封装体的制造方法的剖视图。

[0104] 图26C是用于说明本发明的第7实施方式的半导体封装体的制造方法的剖视图。

[0105] 图27是用于说明本发明的第7实施方式的半导体封装体的制造方法的俯视图。

[0106] 图28是用于说明安装本发明的第7实施方式的半导体封装体的方法的剖视图。

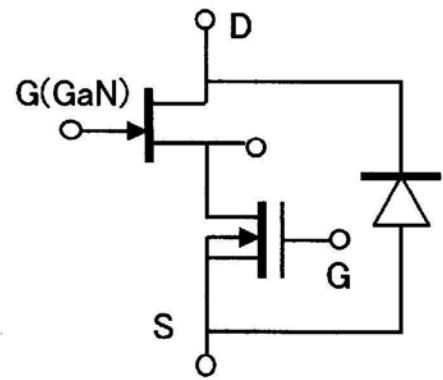

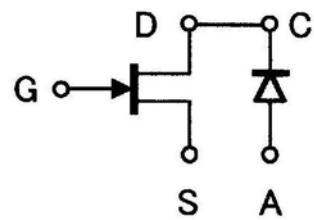

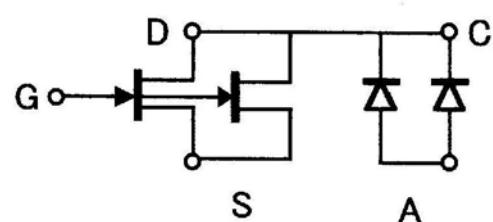

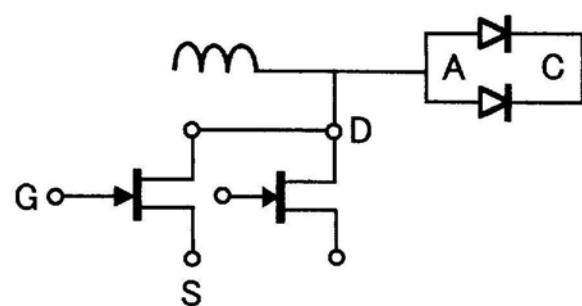

[0107] 图29是示出本发明的第8实施方式的半导体封装体的电路结构的示意图。

[0108] 图30A是示出本发明的第8实施方式的半导体封装体的俯视图。

[0109] 图30B是示出本发明的第8实施方式的半导体封装体的仰视图。

[0110] 图30C是示出本发明的第8实施方式的半导体封装体的剖视图。

[0111] 图31是示出本发明的第9实施方式的半导体封装体的电路结构的示意图。

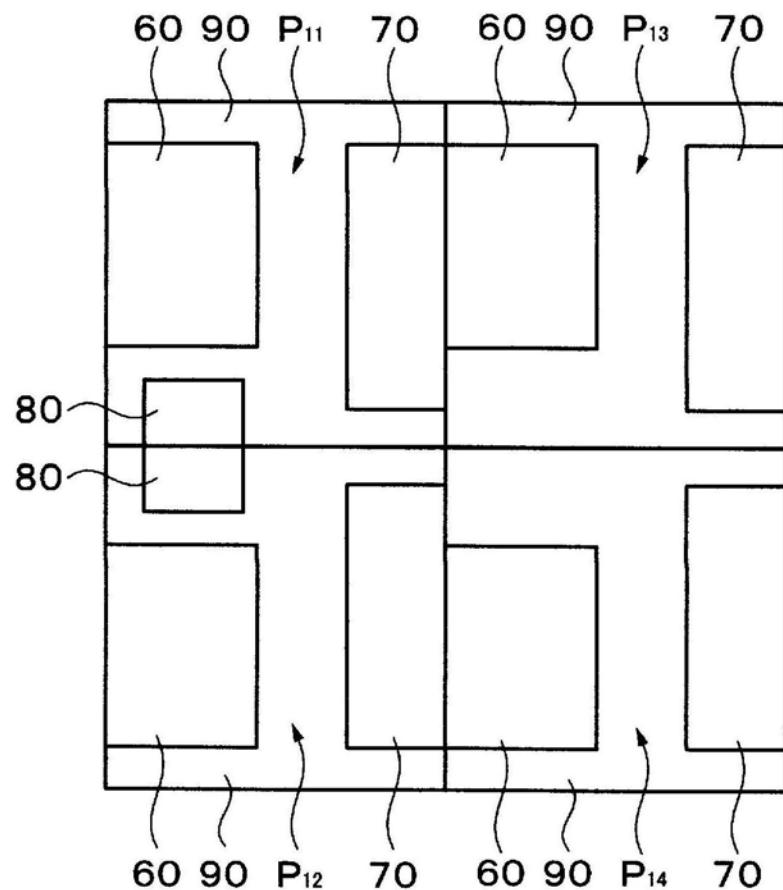

[0112] 图32A是示出本发明的第9实施方式的半导体封装体的俯视图。

[0113] 图32B是示出本发明的第9实施方式的半导体封装体的仰视图。

[0114] 图33是示出本发明的第10实施方式的半导体封装体的电路结构的示意图。

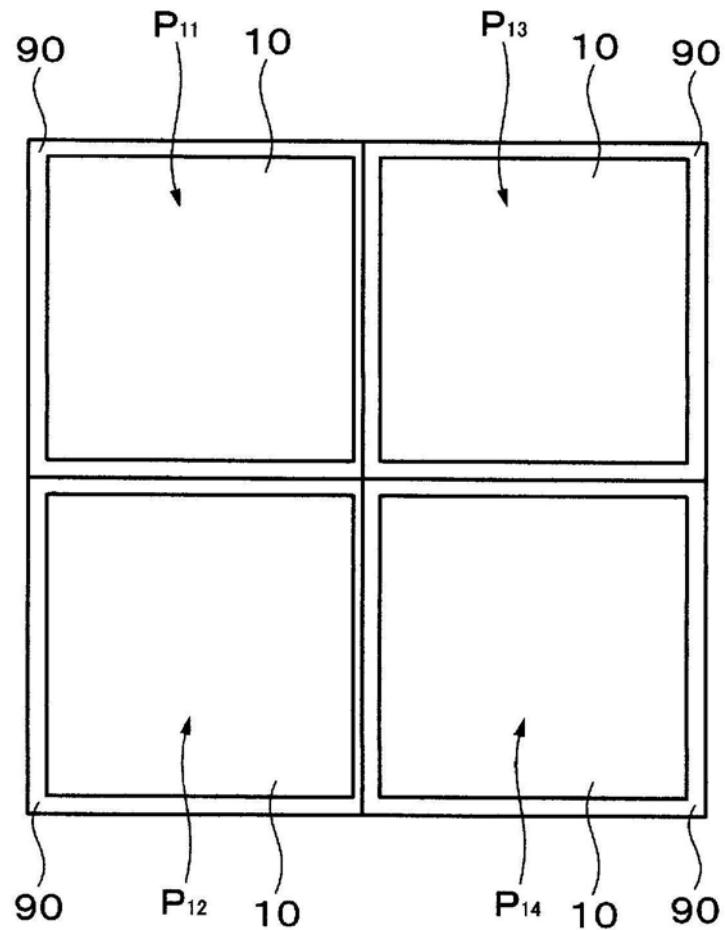

[0115] 图34是示出本发明的第10实施方式的半导体封装体的俯视图。

## 具体实施方式

[0116] 以下,对用于实施发明的方式(以下,称为实施方式)进行说明。

[0117] <1. 第1实施方式>

[0118] [半导体封装体]

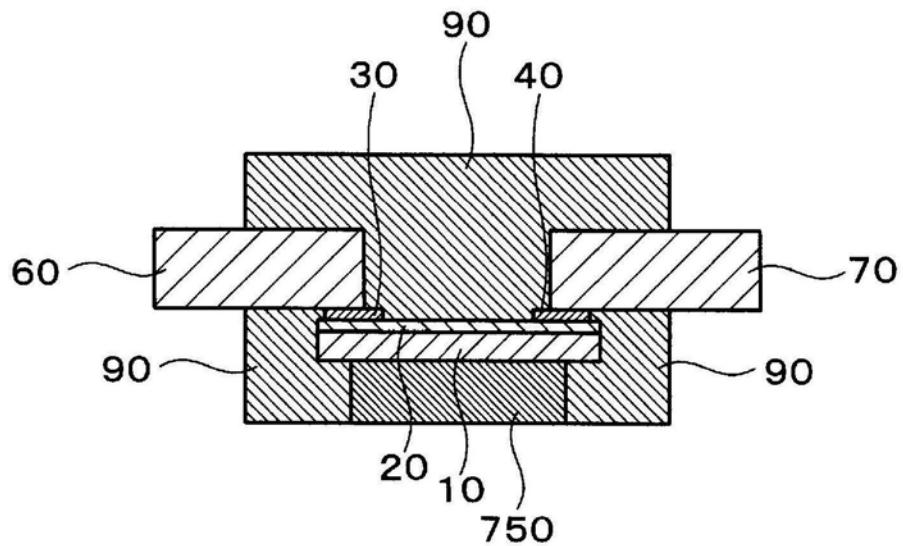

[0119] 对第1实施方式的半导体封装体进行说明。该半导体封装体具有与QFN封装(Quad Flat Non-leaded package:四侧无引脚扁平封装)相同的结构。该半导体封装体是对构成具有源极、漏极及栅极设置在同一面的横型结构的GaN系FET的半导体芯片进行了树脂密封的封装。将该半导体封装体示出在图1～图4。图1是俯视图,图2是仰视图(后视图),图3是沿着图1的X-X线的剖视图,图4是沿着图1的Y-Y线的剖视图。

[0120] 如图1～图4所示,该半导体封装体,除了后述的电极焊盘60、70、80的突出部以外,

整体上具有偏平的长方体形状。在该半导体封装体中，在电绝缘性的绝缘基板10的第一面上设置有构成GaN系FET的半导体层20，在该半导体层20上设置有源极30、漏极40及栅极50的半导体芯片C被树脂密封。虽然不特别限定绝缘基板10，但是在典型的情况下为蓝宝石基板，尤其是C面蓝宝石基板，厚度优选为150μm以下，更优选为120μm以下，且优选为50μm以上。关于半导体层20，一并示意地示出构成GaN系FET的多层GaN系半导体层。能够根据GaN系FET的种类等适当设计半导体层20。该半导体芯片C具有长方形(包含正方形)的平面形状。使该半导体芯片C的四个边在逆时针方向上依次为第1边、第2边、第3边、第4边，分别表示为S<sub>1</sub>、S<sub>2</sub>、S<sub>3</sub>、S<sub>4</sub>。这些源极30、漏极40及栅极50被配置为三角形。换言之，这些源极30、漏极40及栅极50各自的中心配置在三角形的各顶点。源极30与漏极40彼此相对。可以从以往公知的材料中根据需要选择构成这些源极30、漏极40及栅极50的材料。不特别限定这些源极30、漏极40及栅极50的平面形状，可以根据需要选择。在该例子中，源极30具有长方形形状，该长方形具有与半导体芯片C的边S<sub>1</sub>平行的长边和与垂直于边S<sub>1</sub>的边S<sub>2</sub>平行的短边，且源极30靠近边S<sub>1</sub>、S<sub>2</sub>地设置，源极30的长边的长度比边S<sub>1</sub>的长度短。另外，漏极40具有长方形形状，该长方形具有平行于与半导体芯片C的边S<sub>1</sub>相对的边S<sub>3</sub>的长边和与边S<sub>2</sub>平行的短边，且漏极40靠近边S<sub>2</sub>、S<sub>3</sub>地设置，漏极40的长边和短边的长度与源极30大致相同。另外，栅极50具有长方形形状，该长方形具有与半导体芯片C的边S<sub>4</sub>平行的长边和与边S<sub>1</sub>平行的短边，且栅极50在源极30与边S<sub>4</sub>之间的区域中靠近边S<sub>1</sub>、S<sub>4</sub>地设置。源极30和漏极40在典型的情况下形成为梳型结构(interdigital structure)。在图5中示出其一例。

[0121] 在源极30、漏极40及栅极50上分别电连接有电极焊盘60、70、80。由于源极30、漏极40及栅极50配置为三角形，因此这些电极焊盘60、70、80也能够配置为三角形。可以从以往公知的材料中根据需要选择构成这些电极焊盘60、70、80的材料。没有被这些电极焊盘60、70、80覆盖的部分的半导体层20、源极30、漏极40及栅极50的表面与绝缘基板10和半导体层20的侧面被电绝缘性的树脂90覆盖并被密封。覆盖半导体层20、源极30、漏极40及栅极50的表面的树脂90形成为比电极焊盘60、70、80的厚度充分大的厚度，延伸到电极焊盘60、70、80的中途。覆盖绝缘基板10和半导体层20的侧面的树脂90，也可以如在图3和图4中由点划线所示延伸到电极焊盘60、70、80的末端。可以根据需要选择树脂90的材料，例如为环氧树脂。电极焊盘60、70、80向与半导体层20平行的方向延伸，分别垂直地横穿半导体芯片C的边S<sub>1</sub>、S<sub>3</sub>、S<sub>4</sub>并向树脂90的轮廓的外部突出。电极焊盘60以与半导体层20的、包含边S<sub>1</sub>与边S<sub>2</sub>交叉的一个角部的长方形的区域重叠的方式延伸。电极焊盘70以与半导体层20的、包含边S<sub>2</sub>与边S<sub>3</sub>交叉的角部和边S<sub>3</sub>与边S<sub>4</sub>交叉的角部且长边的长度与边S<sub>3</sub>相同的长方形的区域重叠的方式延伸。电极焊盘80以与半导体层20的、包含边S<sub>1</sub>与边S<sub>4</sub>交叉的一个角部的长方形的区域重叠的方式延伸。

[0122] 当例举该半导体封装体的各部分的尺寸的一例时，绝缘基板10的一边的长度为2～5mm，从绝缘基板10的背面到源极30、漏极40及栅极50的上表面为止的高度为约0.15mm，电极焊盘60、70、80的厚度为0.3mm，绝缘基板10的侧面的树脂90的厚度为0.6mm，从电极焊盘60、70、80的上表面到设置在其上的树脂90的上表面为止的高度为0.3mm，电极焊盘60、70、80从树脂90的突出长度为0.7mm。

[0123] [半导体封装体的制造方法]

[0124] 图6A、图6B、图6C、图6D及图6E示出该半导体封装体的制造方法的一例。

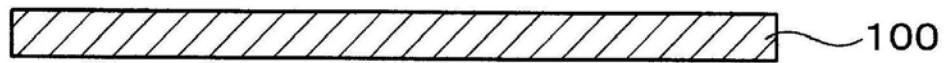

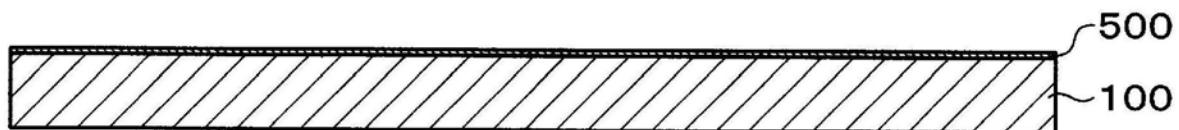

[0125] 如图6A所示,首先,准备引线框架形成用的金属板100。作为金属板100可以从以往公知的材料中根据需要来选择,例如为Cu合金或铁(Fe)-镍(Ni)系合金等。

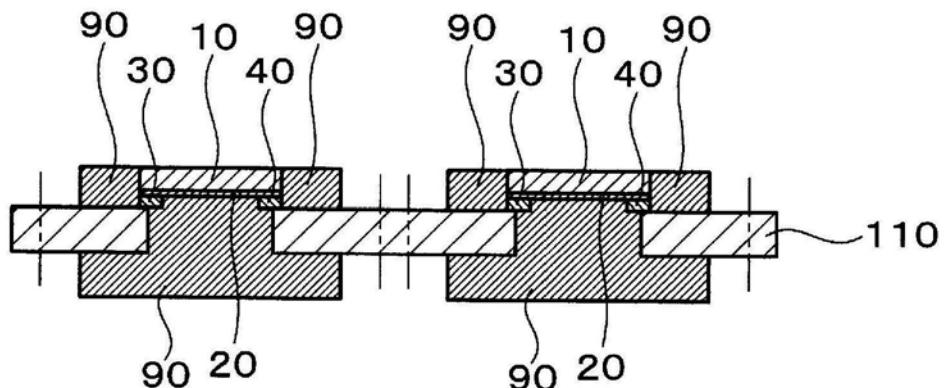

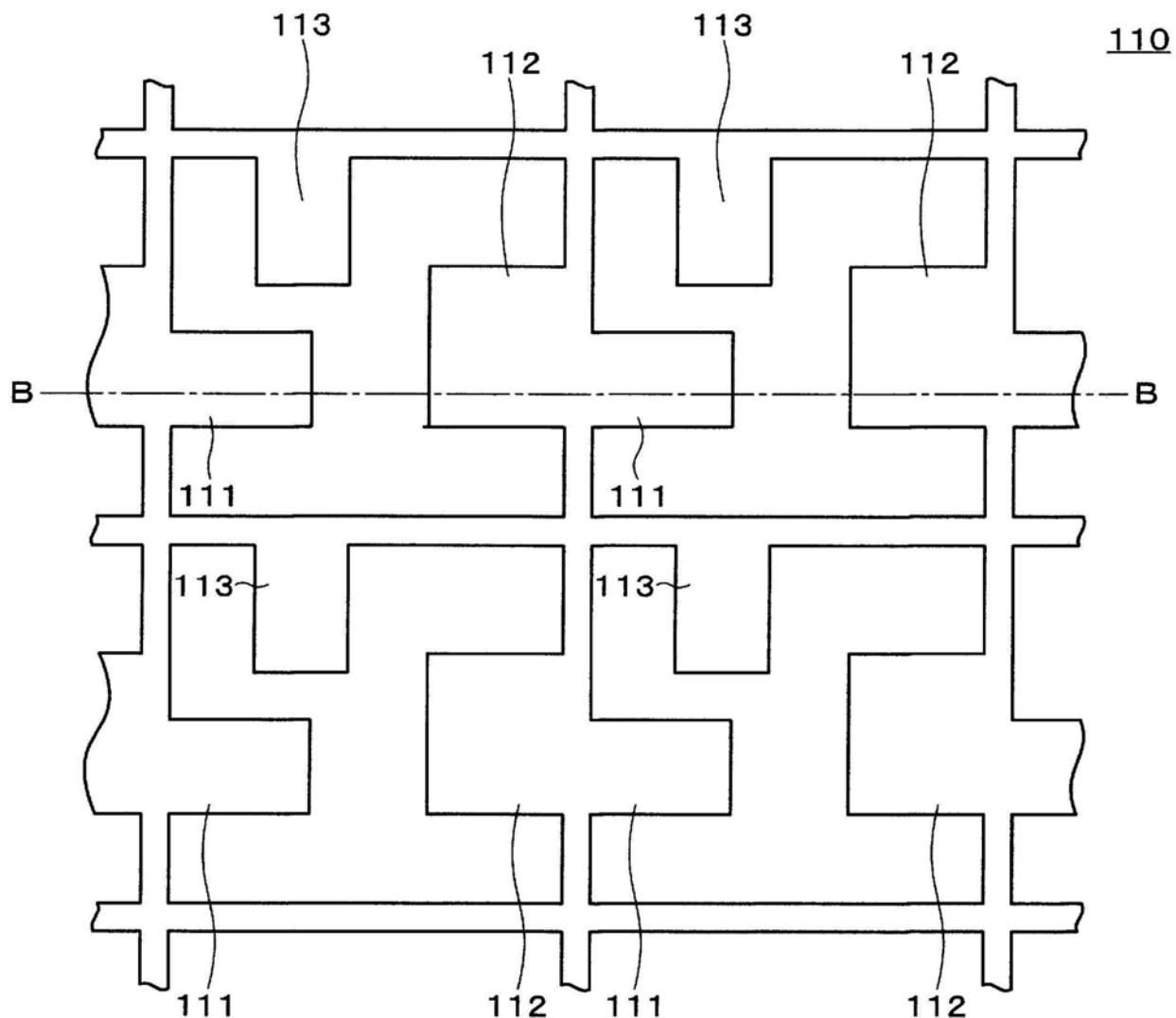

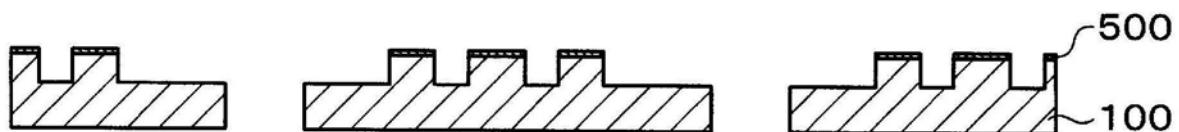

[0126] 接着,如图6B所示,通过冲压加工,以与所制造的QFN封装对应的规定的重复图案来部分地对金属板100进行冲孔,形成规定形状的引线框架110。将该引线框架110的平面形状示出在图7。其中,图7是从下方观察图6B所示的引线框架110时的俯视图。图6B是沿着图7的B-B线的剖视图。在该引线框架110形成最终成为电极焊盘60、70、80的电极焊盘形成部111、112、113。

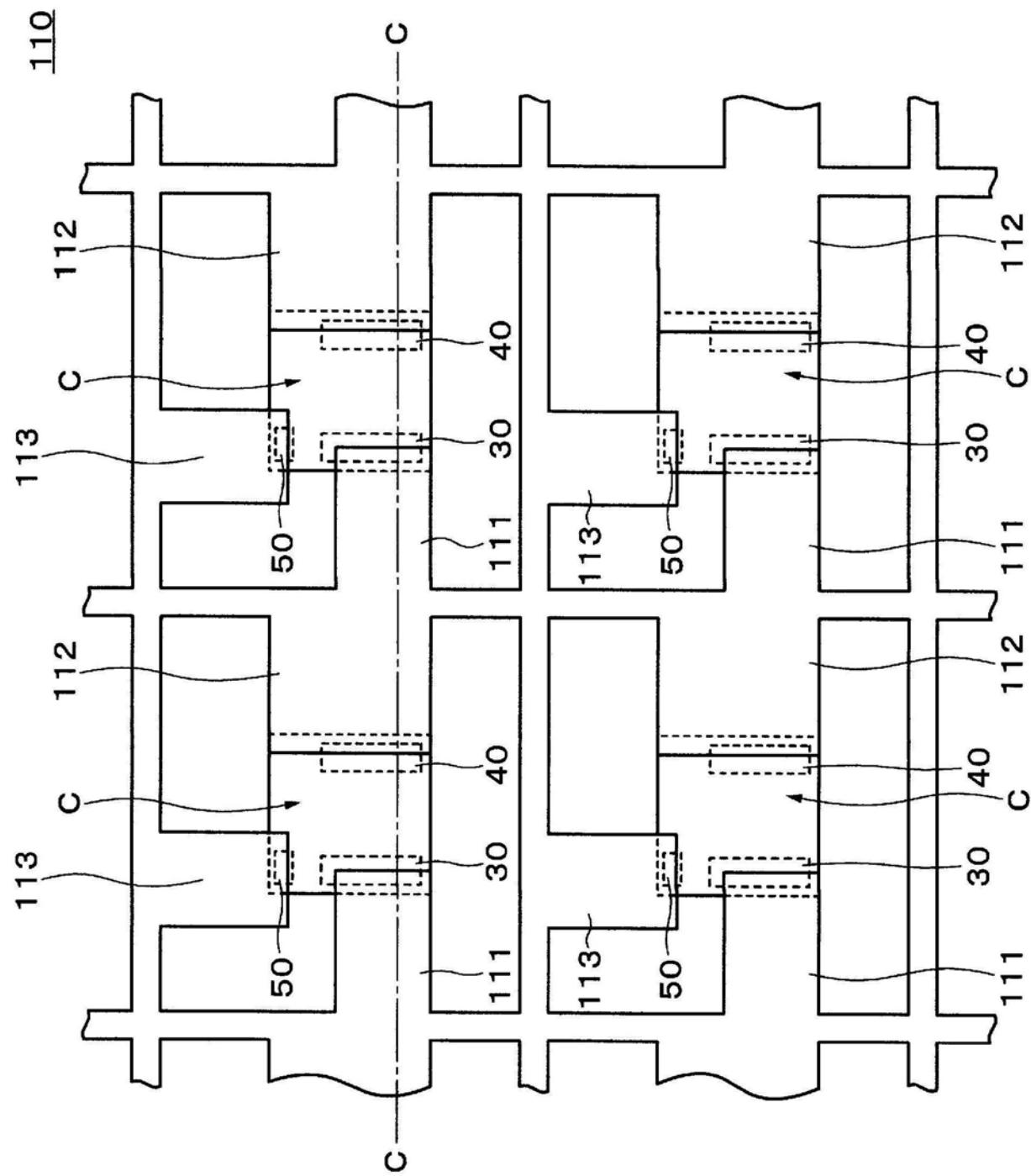

[0127] 接着,如图6C所示,在半导体芯片C的源极30、漏极40及栅极50上分别形成焊料(未图示)的状态下使这些源极30、漏极40及栅极50朝向下方分别接触到引线框架110的冲孔部的周边部的表面之后,通过进行热处理来使焊料熔化。由此,将源极30、漏极40及栅极50分别焊接到引线框架110。将该状态的俯视图示出在图8。其中,图8是从下方观察了图6C所示的引线框架110和半导体芯片C时的俯视图。图6C是沿着图8的C-C线的剖视图。

[0128] 接着,如图6D所示,进行树脂模塑,以填埋引线框架110的冲孔部中的半导体芯片C的半导体层20的下方的空间、或者覆盖绝缘基板10和半导体层20的侧面和电极焊盘60、70、80的根部的部分等,除了绝缘基板10的背面以外通过树脂90对半导体芯片C进行密封。将该状态的俯视图示出在图9。其中,图9是从下方观察了图6D所示的引线框架110、半导体芯片C及树脂90时的俯视图。图6D是沿着图9的D-D线的剖视图。

[0129] 之后,沿着图6D和图9中由双点划线所示的规定的切断线切断引线框架111,如图6E所示进行分割。由此,制造作为目的的图1~图4所示的半导体封装体。

[0130] [GaN系FET的具体例1]

[0131] 图10示出极化超结GaN系FET(参照专利文献2)。如图10所示,在该极化超结GaN系FET中,在GaN系半导体进行C表面生长的、例如C面蓝宝石基板等绝缘基板10上,依次堆叠低温生长GaN缓冲层21、未掺杂GaN层22、厚度为25nm以上47nm以下的未掺杂Al<sub>x</sub>Ga<sub>1-x</sub>N层23(0.17≤x≤0.35)、未掺杂GaN层24及掺杂有Mg的p型GaN层25。该极化超结GaN系FET具有彼此分割设置的极化超结区域(PSJ区域)和p电极接触区域。在p电极接触区域中的p型GaN层25上,还设置有仅在该p电极接触区域中与p型GaN层25接触而比该p型GaN层25更高浓度地掺杂有Mg的p<sup>+</sup>型GaN接触层26。在该p<sup>+</sup>型GaN接触层26上设置有由p电极构成的栅极50。在未掺杂Al<sub>x</sub>Ga<sub>1-x</sub>N层23上设置有源极30和漏极40。这些源极30、漏极40及栅极50配置为三角形。

[0132] [GaN系FET的具体例2]

[0133] 图11示出极化超结GaN系FET(参照专利文献1)。如图11所示,在该极化超结GaN系FET中,在GaN系半导体进行C表面生长的、例如C面蓝宝石基板等绝缘基板10上,依次堆叠低温生长GaN缓冲层21、未掺杂GaN层22、Al<sub>x</sub>Ga<sub>1-x</sub>N层23、未掺杂GaN层24及掺杂有Mg的p型GaN层25。该极化超结GaN系FET具有彼此分割设置的极化超结区域(PSJ区域)和p电极接触区域。p型GaN层25不设置在极化超结区域,仅设置在p电极接触区域。在p电极接触区域中的p型GaN层25上,还设置有仅在该p电极接触区域中与p型GaN层25接触而比该p型GaN层25更高浓度地掺杂有Mg的p<sup>+</sup>型GaN接触层26。在该p<sup>+</sup>型GaN接触层26上设置有由p电极构成的栅极50。在Al<sub>x</sub>Ga<sub>1-x</sub>N层23上设置有源极30和漏极40。这些源极30、漏极40及栅极50配置为三角形。

[0134] [半导体封装体的安装方法]

[0135] 对该半导体封装体的安装方法进行说明。此处,对作为安装基板使用金属基板的情况进行说明。

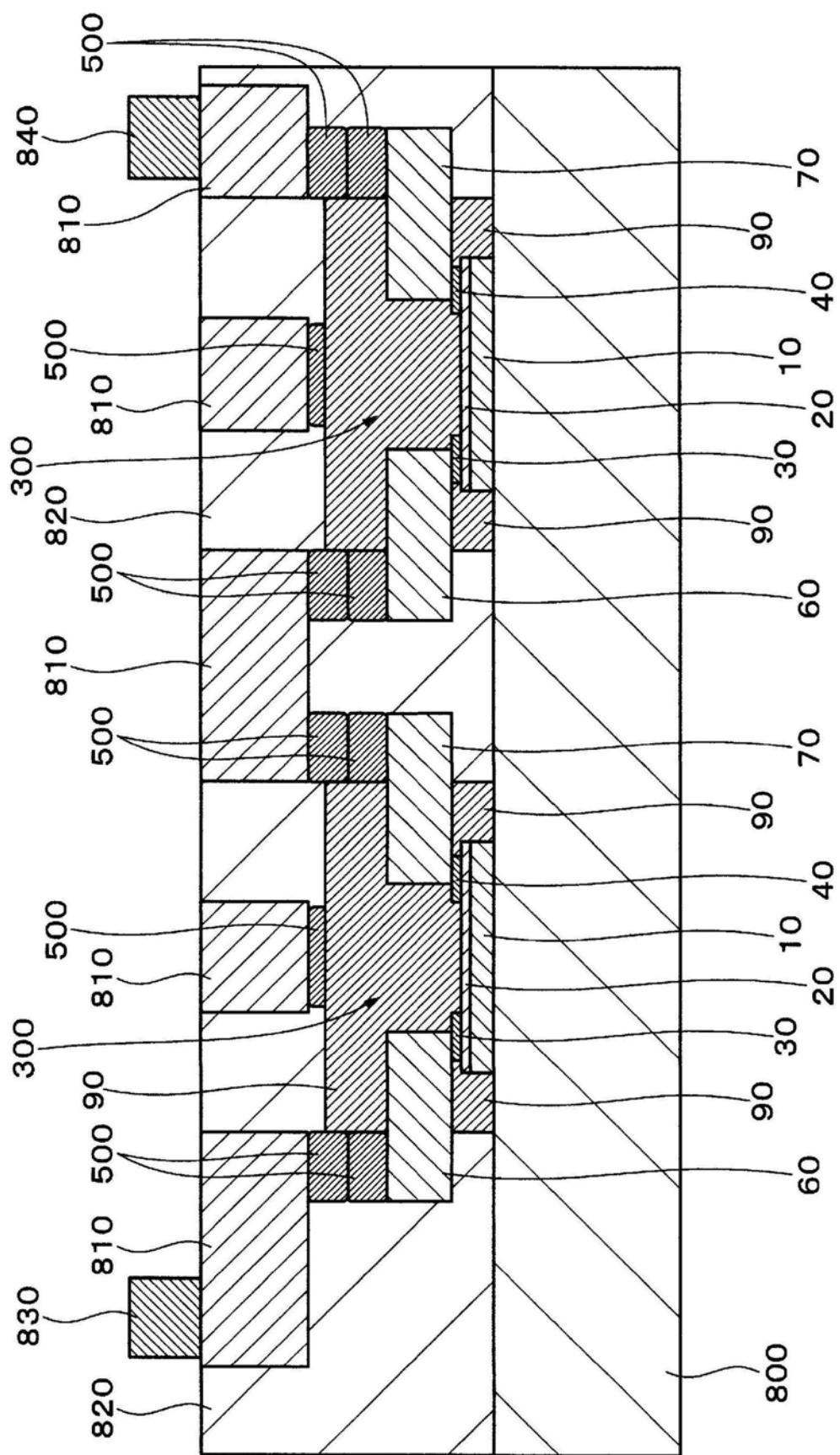

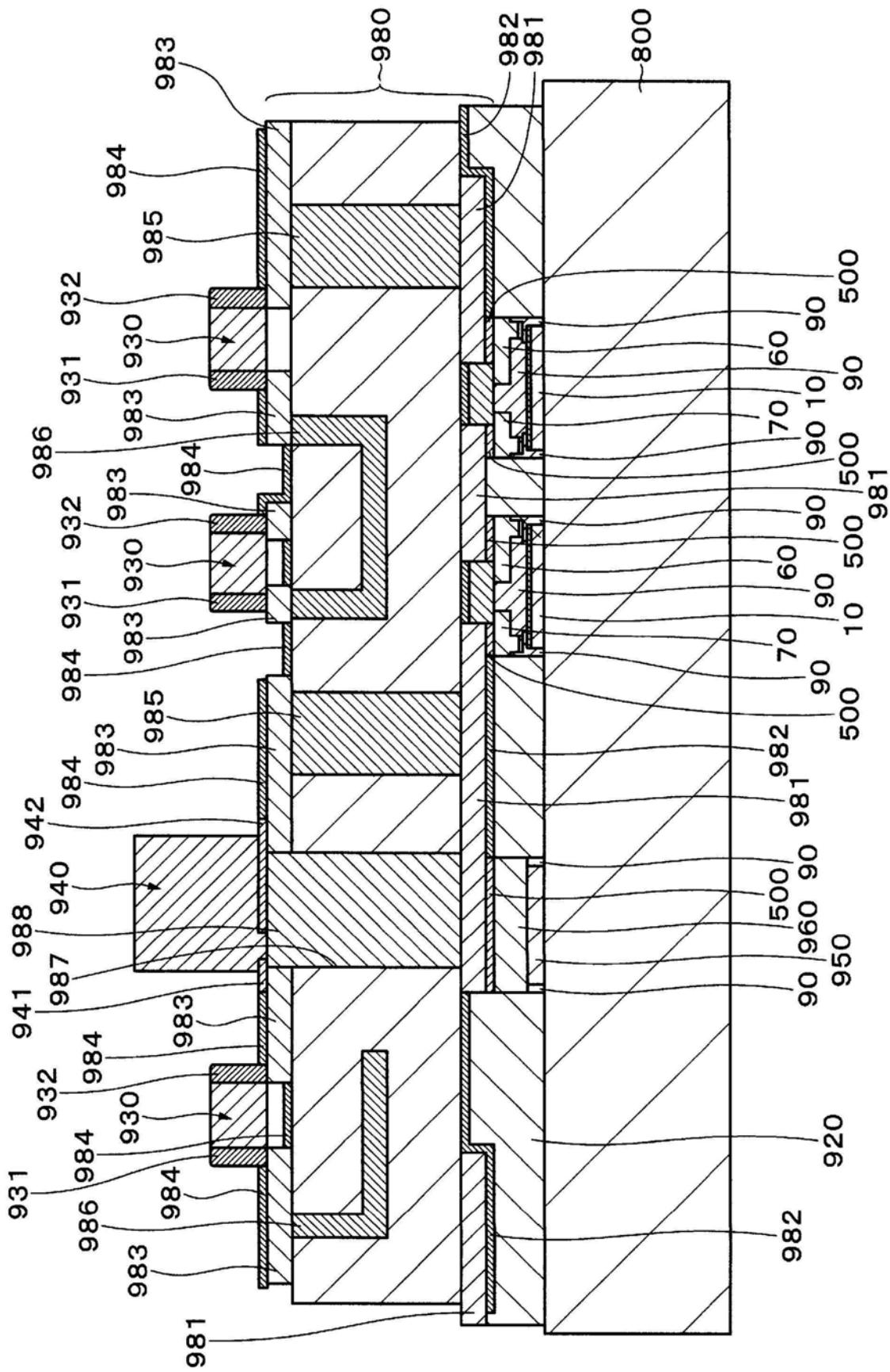

[0136] 图12示出该模块。如图12所示,在该模块中,在作为基底基板的金属基板800上安装有多个第1实施方式的半导体封装体300。此时,各半导体封装体300的绝缘基板10的背面与该金属基板800直接接触。该金属基板800为散热基板,与一般的安装基板不同,没有形成有配线。作为该金属基板800,例如使用Cu基板、Al基板等,但是并不限于此。作为散热基板使用金属基板800,从而能够使对从半导体封装体300产生的热进行散热时的热阻极小化。在图12中的两个半导体封装体300的电极焊盘60、70、80上,通过由双级堆叠的Ag焊剂等构成的导电层500连接有规定的配线810。在典型的情况下,该配线810通过引线框架法而形成。在半导体封装体300的树脂90上,该配线810隔着导电层500设置在树脂90的上表面。金属基板800、半导体封装体300及配线810彼此之间的间隙和配线810之间的间隙通过树脂820而被密封。在配线810的一端和另一端设置有端子830、840。

[0137] [模块的构成例]

[0138] 使该半导体封装体为半导体封装体300。图13A是示出具有使用四个该半导体封装体300、一个市场上销售的SiMOS晶体管SOS封装、四个反接保护用二极管来构成的级联电路的模块的电路图,图13B示出该模块的构成例。另外,在该半导体封装体300中,在作为半导体芯片C使用具体例1、2的功率极化超结GaN系FET时,由于在这些功率极化超结GaN系FET中不具备体二极管,因此不一定需要反接保护用二极管。如图13B所示,在该模块中,为了级联电路的大电流化而并联连接有四个半导体封装体300。在并联连接的半导体封装体300的焊盘电极70与SiMOS晶体管SOS封装600的源极端子601、602之间并联连接有四个反接保护用二极管900。如图14所示,反接保护用二极管900通过在半导体封装体300中省略连接到栅极50的电极焊盘80的形成而构成,将漏极40用作正极,将源极30用作负极。由于在该反接保护用二极管900中也不使用栅极50,因此也可以使用从一开始没有形成栅极50和电极焊盘80的半导体芯片C。如上所述,在没有形成栅极50和电极焊盘80时,将焊盘电极60形成为与焊盘电极70相同的大小,也可以关于边S<sub>1</sub>与边S<sub>3</sub>之间的中心线对称地设置焊盘电极60和焊盘电极70,也可以关于边S<sub>2</sub>与边S<sub>4</sub>之间的中心线对称地设置半导体芯片C上的源极30和漏极40,使源极30和漏极40的边S<sub>4</sub>侧的边与边S<sub>2</sub>侧的边同样靠近边S<sub>4</sub>。如图13B所示,对于四个半导体封装体300的焊盘电极60、70、80、SiMOS晶体管SOS封装600的源极端子601、602、漏极端子603、604、605、栅极端子606及与用作反接保护用二极管900的正极和负极的漏极40和源极30连接的电极焊盘70、60的配线,优选使用通过引线框架法形成的配线810,从上方接触。

[0139] 根据该第1实施方式,能够得到如下所述的各种优点。即,通过树脂90对半导体芯片C进行密封,该半导体芯片C在绝缘基板10的第1主面上设置构成GaN系FET的半导体层20,在半导体层20上以三角形配置源极30、漏极40及栅极50,电极焊盘60、70、80分别从这些源极30、漏极40及栅极50以与半导体层20平行地拉出到该半导体层20的外部,从而能够构成QFN封装状的半导体封装体300。并且,使该半导体封装体300的半导体芯片C的绝缘基板10侧朝向作为基底基板的金属基板800,将电极焊盘60、70、80与形成在半导体封装体300上的配线810连接,从而能够容易使GaN系FET以面朝上安装到金属基板800上,与以往相比能够实现大幅的低成本化、高频化、省体积化、低热阻化等。另外,由于金属基板800与其上的设备部分被完全分割,因此模块的设计容易。另外,由于用作散热基板的金属基板800一般导

热率高且散热性良好,因此能够使热阻极小化。而且,源极30、漏极40及栅极50配置为三角形,因此电极焊盘60、70、80也能够配置为三角形,因此能够使半导体封装体300上的配线形成为彼此不交叉,从而能够容易实现安装有半导体封装体300的高性能的模块。并且,通过使用该模块能够便宜地实现高性能的电气设备。

[0140] <2. 第2实施方式>

[0141] [模块]

[0142] 在第2实施方式中,对将多个第1实施方式的半导体封装体安装到金属基板上的模块进行说明。

[0143] 图15示出该模块。如图15所示,在该模块中,在作为基底基板的金属基板800上安装有多个第1实施方式的半导体封装体300及在这些半导体封装体300上连接有配线810这些点与第1实施方式相同。在该模块中,进一步地在配线810上设置有规定的第二层配线850。该第二层配线850通过由双级堆叠的Ag焊剂等构成分导电层500与第一层配线810的规定部分连接。在配线850上设置有端子860。在图15所示的第二层配线850或者未图示的配线上,根据需要连接有一个或多个无源部件或者有源部件(未图示)。无源部件例如为电容器(电容),有源部件例如为驱动器或级联用SiMOS晶体管等。该模块的其他部分与第1实施方式相同。

[0144] 根据该第2实施方式,能够得到与第1实施方式相同的优点。

[0145] <3. 第3实施方式>

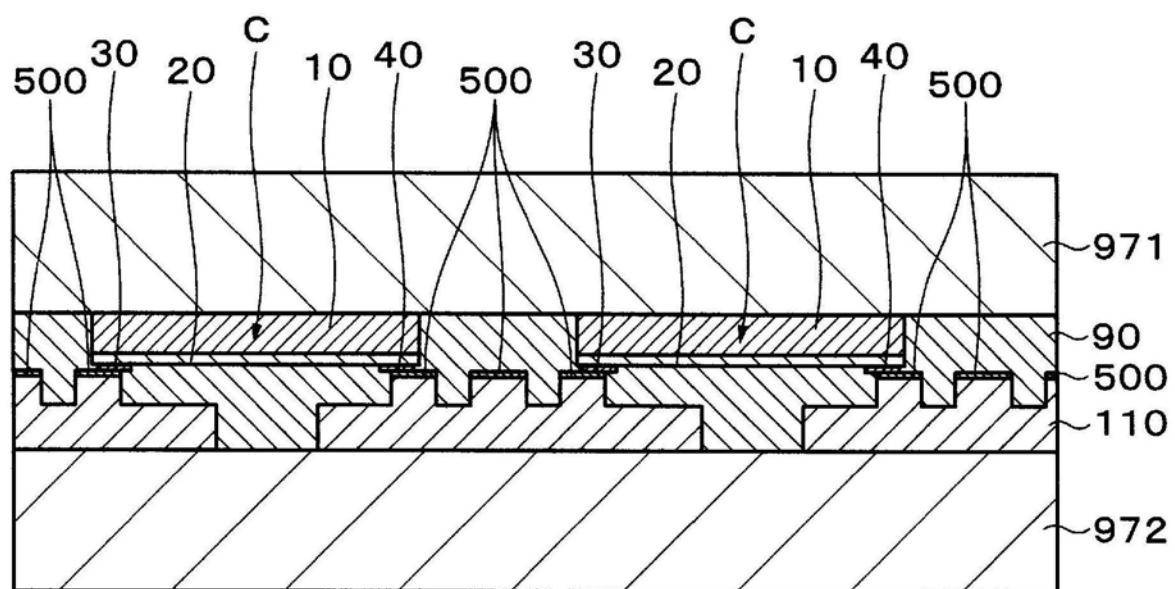

[0146] [模块]

[0147] 在第3实施方式中,对将多个第1实施方式的半导体封装体安装到金属基板上的模块进行说明。

[0148] 图16示出该模块。如图16所示,在该模块中,在作为基底基板的金属基板800上安装有多个第1实施方式的半导体封装体300、在这些半导体封装体300上连接有配线810及在配线810上设置有规定的第二层配线850这些点与第2实施方式相同。在该模块中,配线810和配线850分别形成在双层柔性聚酰亚胺基板910的下表面和上表面这一点与第2实施方式不同。即,配线810通过双层柔性聚酰亚胺基板910的下层的Cu层的图案化而形成,配线850通过双层柔性聚酰亚胺基板910的上层的Cu层的图案化而形成。配线850穿过形成在柔性聚酰亚胺基板911的通孔912与下层的配线810连接。此时,金属基板800、半导体封装体300及配线810彼此之间的间隙及配线810之间的间隙被通过由二氧化硅(SiO<sub>2</sub>)或有机物等电绝缘性材料构成的填料形成的绝缘层920填埋。在第2实施方式中没有设置有在配线850上设置的端子860。与第2实施方式同样,在图16所示的第二层配线850或未图示的配线上,根据需要连接有一个或多个无源部件或者有源部件(未图示)。实际上,例如,在双层柔性聚酰亚胺基板910的配线810上安装有半导体封装体300的部件,以半导体封装体300的绝缘基板10的背面与金属基板800接触的方式粘贴在金属基板800上。该模块的其他部分与第1实施方式相同。

[0149] 根据该第3实施方式,能够得到与第1和第2实施方式相同的优点。

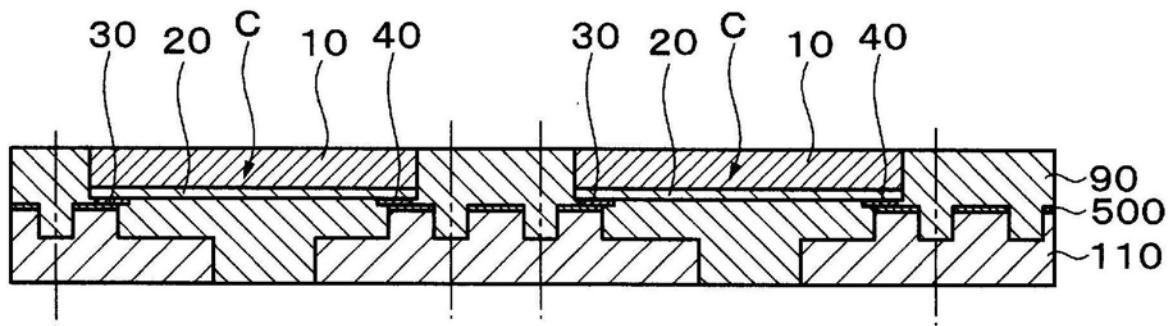

[0150] <4. 第4实施方式>

[0151] [模块]

[0152] 在第4实施方式中,对将多个第1实施方式的半导体封装体和作为裸芯片的GaN系

半导体芯片安装到金属基板上的模块进行说明。

[0153] 图17示出该模块。在该模块中，在作为基底基板的金属基板800上与第3实施方式同样安装有多个第1实施方式的半导体封装体300，省略其图示。如图17所示，与第3实施方式同样，通过双层柔性聚酰亚胺基板910的下层的Cu层的图案化来形成配线810，通过双层柔性聚酰亚胺基板910的上层的Cu层的图案化来形成配线850。配线810连接在半导体封装体300的焊盘电极60、70、80上(未图示)。在该模块中，进一步地安装有三端子半导体元件，尤其是例如形成有已经作为GaN系FET的具体例1、2叙述的极化超结GaN系FET的半导体芯片C。该半导体芯片C具有与半导体封装体300的半导体芯片C相同的结构。该半导体芯片C的绝缘基板10的背面直接与金属基板800接触。该半导体芯片C的源极30、漏极40及栅极50与形成在双层柔性聚酰亚胺基板910的下表面的配线810连接。在双层柔性聚酰亚胺基板910的上层的配线850，安装有电容器等无源部件930，其端子931、932与配线850连接，并且安装有驱动器或级联用SiMOS晶体管等有源部件940，其端子941、942等与配线850连接。金属基板800、半导体封装体300、半导体芯片C及配线810彼此之间的间隙及配线810之间的间隙，被通过由二氧化硅或有机物等电绝缘性材料构成的填料形成的绝缘层920填埋。实际上，例如，在双层柔性聚酰亚胺基板910的配线810上安装半导体封装体300和半导体芯片C且在配线850上安装无源部件930和有源部件940的部件，以半导体封装体300的绝缘基板10的背面和半导体芯片C的绝缘基板10的背面与金属基板800接触的方式粘贴在金属基板800上。该模块的其他部分与第3实施方式相同。

[0154] 根据该第4实施方式，除了能够得到与第1和第2实施方式相同的优点以外，还能够得到作为模块能够容易实现散热特性特别好的IPM(integrated power module，智能功率模块)。

[0155] <5. 第5实施方式>

[0156] [模块]

[0157] 在第5实施方式中，对将多个第1实施方式的半导体封装体和作为裸芯片的GaN系半导体芯片安装到金属基板上的模块进行说明。

[0158] 图18示出该模块。在该模块中，在双层柔性聚酰亚胺基板910的形成于下表面的配线810与金属基板800之间设置有散热用蓝宝石基板950。散热用蓝宝石基板950的背面与金属基板800直接接触。在散热用蓝宝石基板950的表面设置有电极960，该电极960与配线810连接。该模块工作时从GaN系半导体芯片C等产生的热，经由配线810、电极960及散热用蓝宝石基板950高效地传导到金属基板800，从该金属基板800散热。该模块的其他部分与第4实施方式相同。

[0159] 根据该第5实施方式，能够得到与第1、第2及第4实施方式相同的优点。

[0160] <6. 第6实施方式>

[0161] [半导体封装体]

[0162] 对第6实施方式的半导体封装体进行说明。该半导体封装体也与第1实施方式的半导体封装体同样，是对GaN系FET进行了树脂密封的封装，具有与QFN封装相同的结构。图19示出该半导体封装体的剖视图。该半导体封装体的俯视图和仰视图(后视图)与图1和图2所示相同。图19相当于沿着图1的X-X线的剖视图。

[0163] 如图19所示，该半导体封装体除了半导体层20和电极焊盘60、70、80上的树脂90的

厚度大,树脂90从绝缘基板10的侧面延伸到背面的周边部,在绝缘基板10的背面的中央部形成有与由树脂90形成的绝缘基板10相似形状的开口,在该开口的内部与绝缘基板10的背面接触而埋入导热层750这些点以外,与第1实施方式的半导体封装体同样构成。导热层750由例如包含纳米Cu粒子的导电性焊剂等构成。该导热层750的厚度例如为0.15mm。其他结构与第1实施方式相同。

[0164] 当例举该半导体封装体的各部分的尺寸的一例时,绝缘基板10的一边的长度为2~5mm,从绝缘基板10的背面到源极30、漏极40及栅极50的上表面为止的高度为约0.15mm,电极焊盘60、70、80的下方的树脂90的厚度为0.3mm,电极焊盘60、70、80的厚度为0.2mm,绝缘基板10的侧面的树脂90的厚度为0.6mm,导热层750的侧面的树脂90的厚度为1.2mm,从电极焊盘60、70、80的上表面到设置在其上的树脂90的上表面为止的高度为0.8mm,电极焊盘60、70、80从树脂90的突出长度为0.6mm。

[0165] [半导体封装体的制造方法]

[0166] 该半导体封装体的制造方法基本上与第1实施方式的半导体封装体的制造方法相同。导热层750例如能够如下所述形成。即,在引线框架上以在绝缘基板10的背面的中央部形成开口的方式通过树脂模具形成树脂90,之后在引线框架的该树脂90的开口露出的面上涂布包含纳米Cu粒子的导电性焊剂,通过刮刀去除不需要的导电性焊剂,仅在树脂90的开口的内部残留导电性焊剂。之后,通过干燥来形成导热层750。

[0167] [GaN系FET的具体例]

[0168] GaN系FET的具体例例如与第1实施方式的半导体封装体的具体例1、2相同。

[0169] [半导体封装体的安装方法]

[0170] 该半导体封装体的安装方法与在第1实施方式中说明的半导体封装体的安装方法相同。

[0171] [模块的构成例]

[0172] 能够使用半导体封装体300构成与第1实施方式相同的模块。

[0173] 根据该第6实施方式,能够得到与第1实施方式相同的优点。

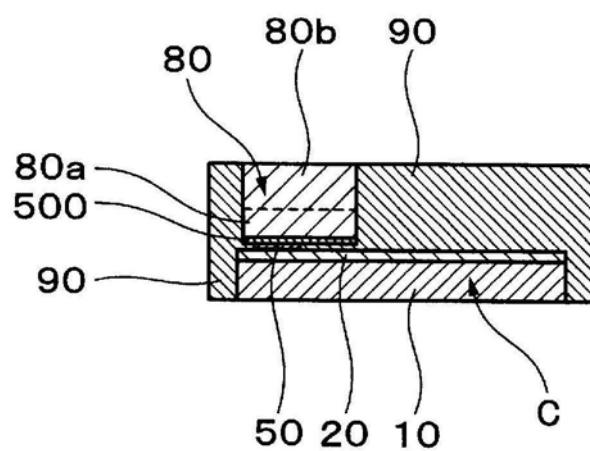

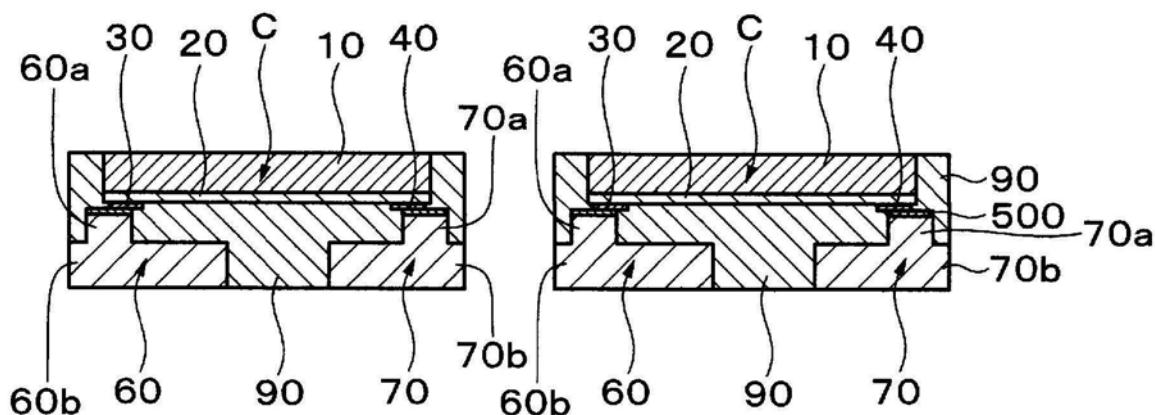

[0174] <7.第7实施方式>

[0175] [半导体封装体]

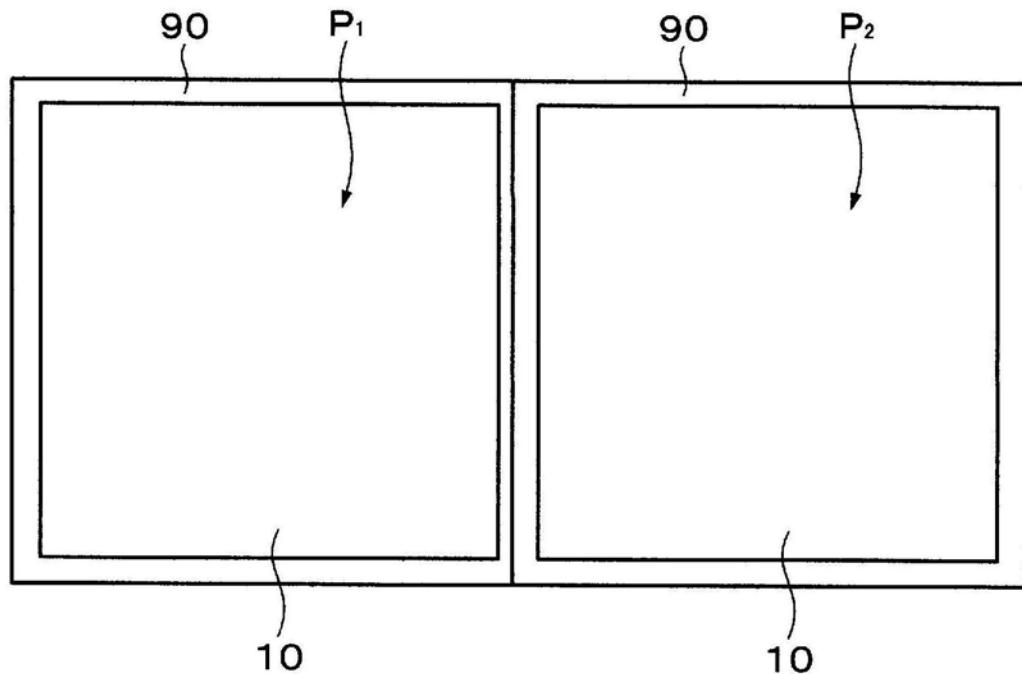

[0176] 对第7实施方式的半导体封装体进行说明。该半导体封装体为CSP (chip size package:芯片尺寸封装)。该半导体封装体也与第1实施方式的半导体封装体同样,对GaN系FET进行了树脂密封。将该半导体封装体示出在图20~图23。图20为俯视图,图21为仰视图(后视图),图22为沿着图20的X-X线的剖视图,图23为沿着图20的Y-Y线的剖视图。

[0177] 如图20~图23所示,该半导体封装体的平面形状为大致正方形,并且作为整体具有偏平的长方体形状。在该半导体封装体中,与第1实施方式相同的半导体芯片C被树脂密封。源极30和漏极40在典型的情况下形成为梳型结构,此时的一例如图5所示。

[0178] 在源极30、漏极40及栅极50上分别通过由包含纳米Ag粒子的导电性焊剂或焊料等构成的导电层500电连接有电极焊盘60、70、80。没有被这些电极焊盘60、70、80覆盖的部分的半导体层20、源极30、栅极50等的表面与绝缘基板10和半导体层20的侧面被电绝缘性的树脂90覆盖并被密封。关于树脂90的轮廓,比半导体芯片C的尺寸大半导体芯片C的侧面的树脂90的厚度的量,但与半导体芯片C的外形基本相似。与源极30连接的电极焊盘60由与源

极30平行地延伸且具有与源极30相同的宽度的直线状的下部60a和跨过半导体层20的边S<sub>1</sub>而在其两侧与半导体层20平行地延伸的具有长方形的平面形状的平板状的上部60b构成。换言之,电极焊盘60是被从源极30相对于半导体层20向垂直上方拉出下部60a之后,上部60b在半导体层20的上方与半导体层20平行地延伸。电极焊盘60的下部60a相对于源极30向源极30的宽度方向偏移,该半导体封装体的中心侧的单侧部分通过形成在该下部60a的上表面的导电层500与源极30电连接。另外,电极焊盘60被设置为,除了源极30的栅极50侧的一端部以外覆盖源极30。与漏极40连接的电极焊盘70,由与漏极40平行地延伸且具有与漏极40相同的宽度的直线状的下部70a和跨过半导体层20的边S<sub>3</sub>而在其两侧与半导体层20平行地延伸的具有长方形的平面形状的平板状的上部70b构成。换言之,电极焊盘70是在被从漏极40相对于半导体层20向垂直上方拉出下部70a之后,上部70b在半导体层20的上方与半导体层20平行地延伸。电极焊盘70的下部70a相对于漏极40向漏极40的宽度方向偏移,该半导体封装体的中心侧的单侧部分通过形成在该下部70a的上表面的导电层500与漏极40电连接。另外,电极焊盘70被设置为覆盖漏极40的全体。与栅极50连接的电极焊盘80由与栅极50平行地延伸且具有与栅极50相同的宽度的直线状的下部80a和跨过半导体层20的边S<sub>4</sub>而在其两侧与半导体层20平行地延伸的具有长方形的平面形状的平板状的上部80b构成。换言之,电极焊盘80是被从栅极50相对于半导体层20向垂直上方拉出下部80a之后,上部80b在半导体层20的上方与半导体层20平行地延伸。电极焊盘80的下部80a相对于栅极50向栅极50的宽度方向偏移,该半导体封装体的中心侧的单侧部分通过形成在该下部80a的上表面的导电层500与栅极50电连接。另外,电极焊盘80被设置为覆盖栅极50的全体。电极焊盘60的外侧的前端、电极焊盘70的外侧的前端及电极焊盘80的外侧的前端与树脂90的轮廓一致。

[0179] 当例举该半导体封装体的各部分的尺寸的一例时,绝缘基板10的一边的长度为2~5mm,从绝缘基板10的背面到源极30、漏极40及栅极50的上表面为止的高度为约0.12mm,电极焊盘60、70、80的下部60a、70a、80a的厚度为约0.15mm,上部60b、70b、80b的厚度为约0.2mm,电极焊盘60与电极焊盘70之间的距离为约1.5mm,源极30、漏极40及栅极50的宽度为约0.15mm,因此电极焊盘60、70、80的下部60a、70a、80a的宽度为约0.15mm。

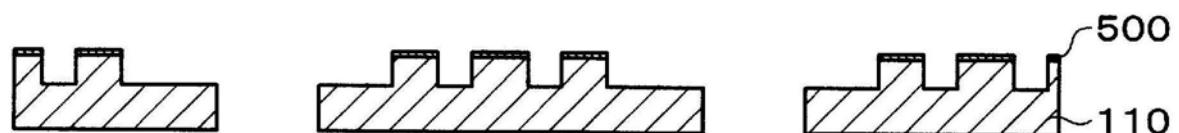

[0180] [半导体封装体的制造方法]

[0181] 图24A、图24B、图24C、图24D、图25A、图25B、图26A、图26B及图26C示出该半导体封装体的制造方法的一例。

[0182] 如图24A所示,首先,准备引线框架形成用的金属板100。作为金属板100根据需要从以往公知的材料中选择,例如为Cu合金或Fe-Ni系合金等。在金属板100上形成有由包含纳米Ag粒子的导电性焊剂或焊料等构成的导电层500。

[0183] 接着,如图24B所示,通过冲压加工,按照与所制造的半导体封装体对应的规定的重复图案,部分地对金属板100和导电层500进行冲孔,以形成比电极焊盘60、70、80的轮廓稍大的轮廓。

[0184] 接着,如图24C所示,通过冲压加工,在金属板100形成阶梯差,以形成与电极焊盘60、70、80的下部60a、70a、80a相当的部分。

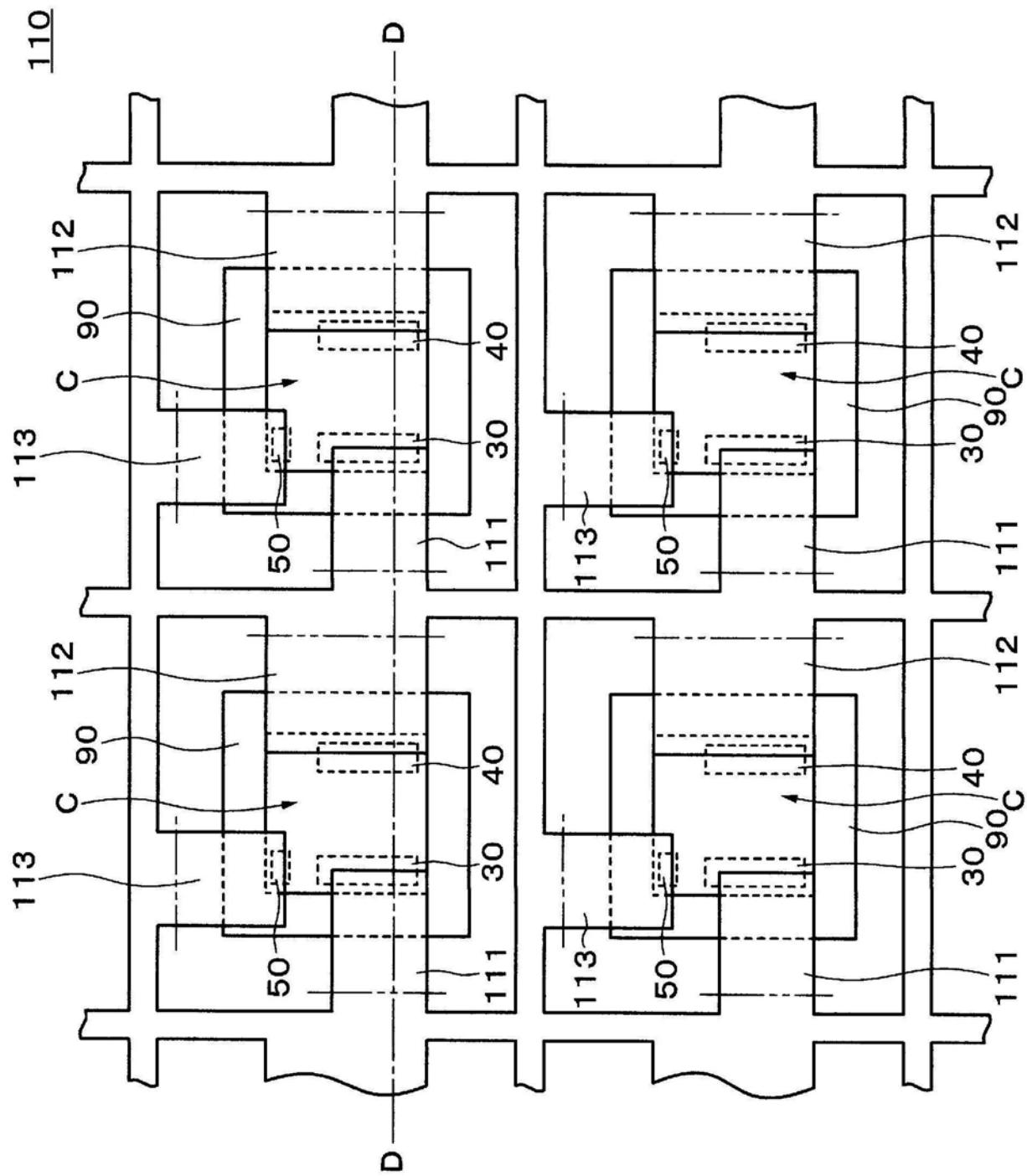

[0185] 接着,如图24D所示,通过冲压加工,部分地对金属板100进行冲孔,以形成电极焊盘60、70、80的轮廓,形成规定形状的引线框架110。将该引线框架110的平面形状示出在图

27。其中,图27是从下方观察了图24D所示的引线框架110时的俯视图。图24D是沿着图27的D-D线的剖视图。在图27中,通过点划线示出最终制造的半导体封装体的轮廓。

[0186] 接着,如图25A所示,在使半导体芯片C的源极30、漏极40及栅极50朝向下方,分别与引线框架110的、电极焊盘60、70、80的下部60a、70a、80a相当的部分的表面的导电层500接触之后,通过进行热处理来接合。

[0187] 接着,如图25B所示,通过厚板971、972夹住图25A所示的结构体的上下。对于厚板971、972,虽然不特别限定,但是例如能够使用玻璃板或者不锈钢等的金属板。

[0188] 接着,如图26A所示,进行树脂模塑以填埋形成在厚板971、972之间的空间,并通过树脂90对半导体芯片C进行密封。

[0189] 接着,如图26B所示,去除厚板971、972。

[0190] 之后,沿着图26B中双点划线所示的规定的切断线切断引线框架110,以图26C所示进行分割。由此,制造作为目的的图20~图23所示的半导体封装体。

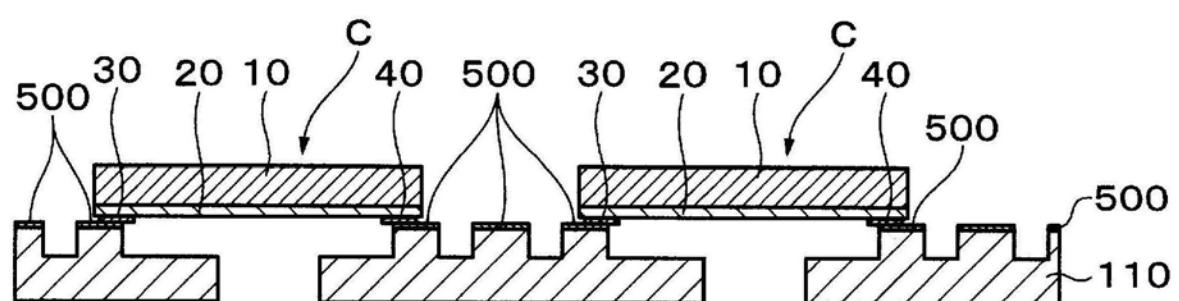

[0191] [半导体封装体的安装方法]

[0192] 对该半导体封装体的安装方法进行说明。此处,对将该半导体封装体安装到金属基板上的模块进行说明。

[0193] 图28示出该模块。如图28所示,在该模块中,在作为基底基板的金属基板800上,安装有多个图20~图23所示的半导体封装体,并且在散热用蓝宝石基板950上设置有电极960的散热用虚拟元件以散热用蓝宝石基板950朝向下方安装在金属基板800。散热用蓝宝石基板950的背面与金属基板800直接接触。可以选择使散热用蓝宝石基板950与电极960的合计厚度与半导体封装体的厚度相同。散热用蓝宝石基板950的侧面被电绝缘性的树脂90覆盖并被密封。在这些半导体封装体和散热用虚拟元件上设置有环氧树脂制的双面印刷配线基板980,形成在双面印刷配线基板980的下表面的配线981与半导体封装体的电极焊盘60、70、80及散热用虚拟元件的电极960通过导电层500电连接。在露出到配线981之间的部分的双面印刷配线基板980的下表面和配线981的表面设置有抗蚀剂掩膜982。此时,金属基板800与双面印刷配线基板980之间的间隙被由填料形成的绝缘层920填埋,该填料由SiO<sub>2</sub>或有机物等电绝缘性材料构成。在双面印刷配线基板980的上表面形成有配线983。在露出到配线983之间的部分的双面印刷配线基板980的上表面和配线983的表面设置有抗蚀剂掩膜984。在双面印刷配线基板980的上表面的配线983,安装有电容器等无源部件930和驱动器或级联用SiMOS晶体管等有源部件940。无源部件930的端子931、932与配线983连接。有源部件940的端子941、942与配线983连接。在双面印刷配线基板980形成有通孔配线985,双面印刷配线基板980的下表面的配线981与上表面的配线983通过该通孔配线985彼此连接。另外,在双面印刷配线基板980形成有埋入配线986。无源部件930彼此通过该埋入配线986连接。在双面印刷配线基板980进而与有源部件940与散热用虚拟元件之间的部分形成有通孔987,在该通孔987被AlN等高导热填料988填埋。

[0194] 根据该第7实施方式,电极焊盘60、70、80的大部分形成在半导体芯片C的半导体层20上,稍微从半导体芯片C突出,因此能够构成CSP状的半导体封装体。并且,使该半导体封装体的半导体芯片C的绝缘基板10侧朝向金属基板800来安装,并且使电极焊盘60、70、80与形成在双面印刷配线基板980的下表面的配线981连接,从而能够容易地使GaN系FET面朝上来安装到金属基板800上,与以往相比能够实现大幅的低成本化、高频化、省体积化、低热阻

化等。而且，源极30、漏极40及栅极50配置为三角形，因此电极焊盘60、70、80也能够配置为三角形，从而能够使形成在双面印刷配线基板980的下表面的配线981形成为彼此不交叉，能够容易实现安装有半导体封装体的高性能的模块。并且，通过使用该模块能够便宜地实现高性能的电气设备。

[0195] <8. 第8实施方式>

[0196] [半导体封装体]

[0197] 对第8实施方式的半导体封装体进行说明。该半导体封装体是将两个CSP一体化的封装，一个CSP为对GaN系FET进行了树脂密封的第11实施方式的半导体封装体，另一个CSP为对GaN系二极管进行了树脂密封的封装。

[0198] 图29示出该半导体封装体的电路。如图29所示，在该半导体封装体中，在GaN系FET的漏极连接GaN系二极管的负极而构成逆变器。

[0199] 图30A、图30B及图30C示出该半导体封装体，图30A是俯视图，图30B是仰视图，图30C沿着图30A的C-C线的剖视图。如图30A、图30B及图30C所示，该半导体封装体是对GaN系FET进行了树脂密封的第7实施方式的CSP状的半导体封装体P<sub>1</sub>与对GaN系二极管进行了树脂密封的CSP状的半导体封装体P<sub>2</sub>通过各自的一个侧面彼此接合的封装，平面形状为长方形且作为全体具有偏平的长方体形状。此处，GaN系二极管通过在第7实施方式的半导体封装体中省略与栅极50连接的电极焊盘80的形成而构成，将漏极40用作正极，将源极30用作负极，作为电极焊盘仅形成有电极焊盘60、70。半导体封装体P<sub>1</sub>的电极焊盘70与半导体封装体P<sub>2</sub>的电极焊盘60将它们的侧面彼此相互接触而电连接。

[0200] 根据该第8实施方式，能够实现具有如图29所示的电路结构的CSP状的半导体封装体。

[0201] <9. 第9实施方式>

[0202] [半导体封装体]

[0203] 对第9实施方式的半导体封装体进行说明。该半导体封装体是使四个CSP一体化的封装，两个CSP是对GaN系FET进行了树脂密封的第11实施方式的半导体封装体，剩下的两个CSP为对GaN系二极管进行了树脂密封的封装。

[0204] 图31示出该半导体封装体的电路。如图31所示，在该半导体封装体中，在并联连接的两个GaN系FET的漏极，连接并联连接的两个GaN系二极管的负极而构成逆变器。

[0205] 图32A和图32B示出该半导体封装体，图32A是俯视图，图32B是仰视图。如图32A和图32B所示，该半导体封装体是对GaN系FET进行了树脂密封的第11实施方式的CSP状的半导体封装体P<sub>11</sub>、P<sub>12</sub>与对GaN系二极管进行了树脂密封的CSP状的半导体封装体P<sub>13</sub>、P<sub>14</sub>通过侧面彼此接合而成，平面形状为大致正方形且作为全体具有偏平的长方体形状。此处，GaN系二极管通过在第7实施方式的半导体封装体中省略与栅极50连接的电极焊盘80的形成而构成，将漏极40用作正极，将源极30用作负极，作为电极焊盘仅形成有电极焊盘60、70。半导体封装体P<sub>11</sub>的电极焊盘70与半导体封装体P<sub>13</sub>的电极焊盘60是它们的侧面彼此相互接触而电连接。半导体封装体P<sub>12</sub>的电极焊盘70与半导体封装体P<sub>14</sub>的电极焊盘60使它们的侧面彼此相互接触而电连接。半导体封装体P<sub>11</sub>的电极焊盘80与半导体封装体P<sub>12</sub>的电极焊盘80使它们的侧面彼此相互接触而电连接。

[0206] 根据该第9实施方式，能够实现具有如图31所示的电路结构的CSP状的半导体封装

体。

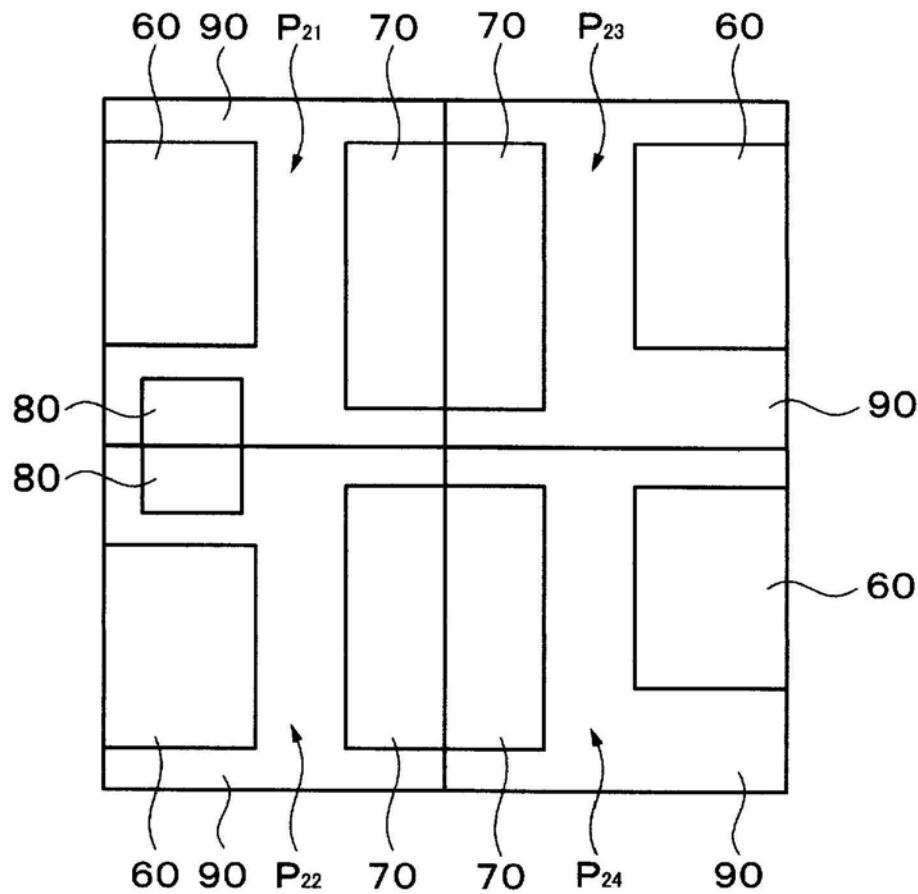

[0207] <10. 第10实施方式>

[0208] [半导体封装体]

[0209] 对第10实施方式的半导体封装体进行说明。该半导体封装体是使四个CSP一体化的封装,两个CSP是对GaN系FET进行了树脂密封的第7实施方式的半导体封装体,剩余的两个CSP是对GaN系二极管进行了树脂密封的封装。

[0210] 图33示出该半导体封装体的电路。如图33所示,在该半导体封装体中,在并联连接的两个GaN系FET的漏极,连接并联连接的两个GaN系二极管的正极而构成DC/DC上变频器。

[0211] 图34是示出该半导体封装体的俯视图。如图34所示,该半导体封装体是对GaN系FET进行了树脂密封的第7实施方式的CSP状的半导体封装体P<sub>21</sub>、P<sub>22</sub>与对GaN系二极管进行了树脂密封的CSP状的半导体封装体P<sub>23</sub>、P<sub>24</sub>通过侧面彼此接合而成的封装,平面形状为大致正方形且作为全体具有偏平的长方体形状。此处,GaN系二极管通过在第7实施方式的半导体封装体中省略与栅极50连接的电极焊盘80的形成而构成,将漏极40用作正极,将源极30用作负极,作为电极焊盘仅形成有电极焊盘60、70。半导体封装体P<sub>21</sub>的电极焊盘70与半导体封装体P<sub>13</sub>的电极焊盘70使它们的侧面彼此相互接触而电连接。半导体封装体P<sub>22</sub>的电极焊盘70与半导体封装体P<sub>24</sub>的电极焊盘70使它们的侧面彼此相互接触而电连接。半导体封装体P<sub>21</sub>的电极焊盘80与半导体封装体P<sub>22</sub>的电极焊盘80使它们的侧面彼此相互接触而连接。

[0212] 根据该第10实施方式,能够实现具有如图33所示的电路结构的CSP状的半导体封装体。

[0213] 以上,虽然具体说明了本发明的实施方式,但是本发明并不限定于上述的实施方式,能够进行基于本发明的技术思想的各种变形。

[0214] 例如,在上述的实施方式中例举的数值、结构、形状、材料等只不过是例子,也可以根据需要使用与这些不同的数值、结构、形状、材料等。

[0215] 另外,在上述的第4和第5实施方式中,虽然将半导体封装体300和半导体芯片C安装到金属基板800上,但是也可以在双层柔性聚酰亚胺基板910的配线810上不安装半导体封装体300,而仅将作为裸芯片的半导体芯片C安装到金属基板800上。此时,在双层柔性聚酰亚胺基板910的配线810上安装半导体芯片C且在配线850上安装无源部件930和有源部件940的部件,以半导体芯片C的绝缘基板10的背面与金属基板800接触的方式粘贴在金属基板800上。由此,能够容易实现散热特性良好的IPM。

[0216] 标号说明

[0217] 10 绝缘基板

[0218] 20 半导体层

[0219] 30 源极

[0220] 40 漏极

[0221] 50 栅极

[0222] 60、70、80 焊盘电极

[0223] 90 树脂

[0224] C 半导体芯片

[0225] 100 金属板

- [0226] 110 引线框架

- [0227] 300 半导体封装体

- [0228] 800 金属基板

- [0229] 900 反接保护用二极管

- [0230] 910 双层柔性聚酰亚胺基板

- [0231] 950 散热用蓝宝石基板

图1

图2

图3

图4

图5

图6A

图6B

图6C

图6D

图6E

图7

图8

图9

图10

图11

图12

图13A

图13B

图14

图15

图16

图17

图18

图19

图20

图21

图22

图23

图24A

图24B

图24C

图24D

图25A

图25B

图26A

图26B

图26C

110

图27

图28

图29

图30A

图30B

图30C

图31

图32A

图32B

图33

图34