**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) Int. Cl.

G11C 11/4091 (2006.01)

(45) 공고일자 2007년05월11일

(11) 등록번호 10-0717225

(24) 등록일자 2007년05월04일

|             |                   |             |                 |

|-------------|-------------------|-------------|-----------------|

| (21) 출원번호   | 10-2001-7010552   | (65) 공개번호   | 10-2001-0113699 |

| (22) 출원일자   | 2001년08월20일       | (43) 공개일자   | 2001년12월28일     |

| 심사청구일자      | 2005년02월03일       |             |                 |

| 번역문 제출일자    | 2001년08월20일       |             |                 |

| (86) 국제출원번호 | PCT/JP2000/000698 | (87) 국제공개번호 | WO 2000/51134   |

| 국제출원일자      | 2000년02월09일       | 국제공개일자      | 2000년08월31일     |

(81) 지정국

국내특허 : 독일, 대한민국, 미국, 싱가포르, 알바니아, 오스트리아, 오스트레일리아, 아제르바이잔, 보스니아 헤르체고비나, 바베이도스, 불가리아, 브라질, 벨라루스, 캐나다, 스위스, 중국, 쿠바, 체코, 덴마크, 에스토니아, 스페인, 핀란드, 영국, 그루지야, 헝가리, 이스라엘, 아이슬랜드, 케냐, 키르키즈스탄, 북한, 카자흐스탄, 세인트루시아, 스리랑카, 리베이라, 레소토, 리투아니아, 룩셈부르크, 라트비아, 몰도바, 마다가스카르, 마케도니아공화국, 몽고, 말라위, 멕시코, 노르웨이, 뉴질랜드, 슬로베니아, 슬로바키아, 타지키스탄, 투르크멘, 터키, 트리니아드토바고, 우크라이나, 우간다, 우즈베키스탄, 베트남, 폴란드, 포르투칼, 루마니아, 러시아, 수단, 스웨덴, 인도, 가나, 감비아, 크로아티아, 인도네시아, 시에라리온, 세르비아 앤 몬테네그로, 짐바브웨, 그라나다, 아랍에미리트, 코스타리카, 도미니카, 모로코, 남아프리카,

AP ARIPO특허 : 케냐, 레소토, 말라위, 수단, 우간다, 시에라리온, 가나, 감비아, 짐바브웨, 스와질랜드, 탄자니아,

EA 유라시아특허 : 아르메니아, 아제르바이잔, 벨라루스, 키르키즈스탄, 카자흐스탄, 몰도바, 러시아, 타지키스탄, 투르크멘,

EP 유럽특허 : 오스트리아, 벨기에, 스위스, 독일, 덴마크, 스페인, 프랑스, 영국, 그리스, 아일랜드, 이탈리아, 룩셈부르크, 모나코, 네덜란드, 포르투칼, 스웨덴, 핀란드, 사이프러스,

OA OAPI특허 : 부르키나파소, 베닌, 중앙아프리카, 콩고, 코트디브와르, 카메룬, 가봉, 기니, 말리, 모리타니, 니제르, 세네갈, 차드, 토고, 기니 비사우,

(30) 우선권주장

JP-P-1999-00042666 1999년02월22일 일본(JP)

(73) 특허권자

가부시키가이샤 히타치세이사쿠쇼

일본국 도쿄도 치요다구 마루노우치 1초메 6반 6고

(72) 발명자

다케무라, 리이찌로

일본 도쿄도 지요다구 마루노우찌 1초메 5-1 신마루노우찌 빌딩 가부시

키가이샤 히타치세이사쿠쇼지적소유권본부 내

이또, 기요

일본 도쿄도 지요다구 마루노우찌 1초메 5-1 신마루노우찌 빌딩 가부시

키가이샤 히타치세이사쿠쇼지적소유권본부 내

세끼구찌, 도모노리

일본 도쿄도 지요다구 마루노우찌 1조메 5-1 신마루노우찌 빌딩 가부시

키가이샤 히타치세이사쿠쇼지적소유권본부 내

사까따, 다께시

일본 도쿄도 지요다구 마루노우찌 1조메 5-1 신마루노우찌 빌딩 가부시

키가이샤 히타치세이사쿠쇼지적소유권본부 내

기무라, 가쓰따까

일본 도쿄도 지요다구 마루노우찌 1조메 5-1 신마루노우찌 빌딩 가부시

키가이샤 히타치세이사쿠쇼지적소유권본부 내

(74) 대리인

장수길

구영창

(56) 선행기술조사문현

05375095

10269772

**심사관 : 고재현**

전체 청구항 수 : 총 32 항

---

**(54) 반도체 장치**

---

**(57) 요약**

메모리 어레이 전압이 저전압화된 경우라도, 메모리 셀에서의 미소 신호를 고속이며, 또한 저소비 전력으로 데이터를 감지하는 감지 증폭기를 개시한다. 오버 드라이브용 구동 스위치를 감지 증폭기 영역 내에 분포 배치하고, 복구용 구동 스위치를 감지 증폭기 열의 일단에 집중하여 설치한다. 오버 드라이브용 전위는 매쉬 형상 전원 배선을 이용하여 공급하도록 구성한다.

상기 오버 드라이브용 구동 스위치에 의해 데이터선 쌍을 데이터선 진폭보다 큰 전압으로 초기 감지할 수 있어서 고속 감지를 실현한다. 구동 스위치를 분포적으로 배치함으로써, 감지 시의 전류를 분산할 수 있고 감지 시의 전압의 원근단 차가 억제된다.

**대표도**

도 1

### 특허청구의 범위

**청구항 1.**

반도체 장치로서,

복수의 메모리 셀로부터 복수의 데이터선에 판독되는 신호를 대응하는 상기 데이터선 상에서 제1 전압으로 증폭하기 위한 복수의 감지 증폭기와,

상기 복수의 감지 증폭기의 일측의 전원 공급 노드에 공통으로 접속하는 제1 배선과,

상기 제1 배선의 일단으로부터 상기 제1 전압을 공급하기 위한 제1 스위치와,

상기 복수의 감지 증폭기를 따라 설치되고, 상기 제1 전압보다 큰 제2 전압이 공급되는 제2 배선과,

상기 제1 배선과 상기 제2 배선 사이에 상기 복수의 감지 증폭기를 따라 분포하여 설치된 제2 스위치와,

상기 복수의 감지 증폭기의 타측의 전원 공급 노드에 공통으로 접속하는 제3 배선과,

상기 복수의 감지 증폭기를 따라 설치되고, 복구 전위를 공급하기 위한 제4 배선과,

상기 제3 배선과 상기 제4 배선 사이에 상기 복수의 감지 증폭기를 따라 분포하여 설치된 제3 스위치

를 포함하는 것을 특징으로 하는 반도체 장치.

## 청구항 2.

제1항에 있어서,

상기 제2 배선은 매쉬 형상 전원 배선인 것을 특징으로 하는 반도체 장치.

## 청구항 3.

제1항에 있어서,

상기 복수의 감지 증폭기를 활성화하는 경우, 상기 제2 스위치를 미리 정해진 기간 도통시킨 후, 상기 제1 스위치를 도통시키는 것을 특징으로 하는 반도체 장치.

## 청구항 4.

복수의 서브 메모리 어레이를 포함하는 메모리 어레이를 갖는 반도체 장치로서,

상기 복수의 서브 메모리 어레이의 각각은,

제1 방향으로 연장하는 복수의 워드선과 제2 방향으로 연장하는 복수의 데이터선의 교점에 설치된 복수의 메모리 셀과,

상기 복수의 데이터선 각각에 대응하여 설치되고, 교차 결합된 제1 도전형의 제1 MISFET 쌍 및 제2 도전형의 제2 MISFET 쌍을 각각에 포함하는 복수의 감지 증폭기와,

상기 제1 방향으로 연장하여 설치되고, 상기 복수의 감지 증폭기의 제1 MISFET 쌍의 소스에 결합되는 제1 공통 소스선과,

상기 제1 방향으로 연장하여 설치되고, 상기 복수의 감지 증폭기의 제2 MISFET 쌍의 소스에 결합되는 제2 공통 소스선과,

상기 제1 방향으로 연장하여 설치되고, 제1 전위가 공급되는 제1 전원 배선과,

상기 제1 방향으로 연장하여 설치되고, 제2 전위가 공급되는 제2 전원 배선과,

제3 전위가 공급되는 제3 전원 배선과,

상기 복수의 감지 증폭기에 대하여 미리 정해진 수의 상기 감지 증폭기마다 설치되고, 상기 제1 공통 소스선과 상기 제1 전원 배선 사이에 상기 복수의 감지 증폭기를 따라 설치된 복수의 제1 스위치와,

상기 복수의 감지 증폭기에 대하여 미리 정해진 수의 상기 감지 증폭기마다 설치되고, 상기 제2 공통 소스선과 상기 제2 전원 배선 사이에 상기 복수의 감지 증폭기를 따라 설치된 복수의 제2 스위치와,

상기 제1 공통 소스선과 상기 제3 전원 배선 사이에 설치된 제3 스위치

를 포함하며,

상기 제3 전위는 상기 제1 전위와 상기 제2 전위 사이에 있으며,

상기 메모리 셀로부터 판독된 신호는 대응하는 상기 데이터선 상에서, 상기 제2 전위 또는 상기 제3 전위로 증폭되는 것을 특징으로 하는 반도체 장치.

## 청구항 5.

제4항에 있어서,

상기 메모리 셀에 기억된 정보를 대응하는 상기 데이터선에 판독하는 경우에, 상기 복수의 워드선 중 하나가 선택된 후, 상기 복수의 제1 및 제2 스위치가 도통 상태가 되고, 미리 정해진 기간 경과 후에 상기 복수의 제1 스위치가 비도통으로 됨과 함께 상기 제3 스위치가 도통 상태가 되는 것을 특징으로 하는 반도체 장치.

## 청구항 6.

제5항에 있어서,

상기 복수의 제1 스위치 각각은 제1 도전형의 제3 MISFET이고, 상기 복수의 제2 스위치 각각은 제2 도전형의 제4 MISFET이며, 상기 제1 도전형은 P형이고, 상기 제2 도전형은 N형이며, 상기 제1 전위는 상기 제3 전위보다 높고, 상기 제3 전위는 상기 제2 전위보다 높은 것을 특징으로 하는 반도체 장치.

## 청구항 7.

제4항에 있어서,

상기 복수의 서브 메모리 어레이에는,

상기 복수의 워드선, 상기 복수의 데이터선 및 상기 복수의 메모리 셀이 배치되고, 하나의 각을 공유하는 제1 변과 제2 변을 갖는 4각형의 제1 영역과,

상기 제1 변을 따라 설치되고 상기 복수의 감지 증폭기, 상기 제1 및 제2 공통 소스선, 상기 제1 및 제2 전원 배선 및 상기 복수의 제1 및 제2 스위치가 배치되는 제2 영역과,

상기 제2 변을 따라 설치되고 상기 복수의 워드선 각각에 대응하여 설치되는 복수의 워드선 구동 회로 또는 상기 복수의 워드선 각각을 상층의 복수의 워드선 배선과 접속하기 위한 복수의 접속부가 배치되는 제3 영역과,

상기 제1 영역의 상기 하나의 각과 상기 제2 및 제3 영역에 의해 둘러싸인 영역에 설치되고 상기 제3 스위치가 배치되는 제4 영역을 포함하는 것을 특징으로 하는 반도체 장치.

## 청구항 8.

제4항에 있어서,

상기 복수의 서브 메모리 어레이의 각각은,

상기 제2 방향으로 연장하여 설치되고, 그 교점에서 상기 제1 전원 배선과 접속되고 상기 제1 전위가 공급되는 복수의 제4 전원 배선과,

상기 제2 방향으로 연장하여 설치되고, 그 교점에서 상기 제2 전원 배선과 접속되고 상기 제2 전위가 공급되는 복수의 제5 전원 배선을 포함하는 것을 특징으로 하는 반도체 장치.

## 청구항 9.

제8항에 있어서,

상기 복수의 제4 및 제5 전원 배선은 상기 복수의 감지 증폭기에 대하여 미리 정해진 수의 상기 감지 증폭기에 1개의 비율로 설치되는 것을 특징으로 하는 반도체 장치.

## 청구항 10.

제4항에 있어서,

상기 복수의 메모리 셀 각각은 1개의 MISFET와 1개의 캐패시터를 포함하는 다이내믹형 메모리 셀인 것을 특징으로 하는 반도체 장치.

## 청구항 11.

복수의 서브 메모리 어레이를 포함하는 메모리 어레이를 갖는 반도체 장치로서,

상기 복수의 서브 메모리 어레이의 각각은,

제1 방향으로 연장하는 복수의 워드선과 제2 방향으로 연장하는 복수의 데이터선의 교점에 설치된 복수의 메모리 셀과,

상기 복수의 데이터선 각각에 대응하여 설치되고, 교차 결합된 제1 도전형의 제1 MISFET 쌍 및 제2 도전형의 제2 MISFET 쌍을 각각에 포함하는 복수의 감지 증폭기와,

상기 제1 방향으로 연장하여 설치되고, 상기 복수의 감지 증폭기의 제1 MISFET 쌍의 소스에 결합되는 제1 공통 소스선과,

상기 제1 방향으로 연장하여 설치되고, 상기 복수의 감지 증폭기의 제2 MISFET 쌍의 소스에 결합되는 제2 공통 소스선과,

상기 제1 방향으로 연장하여 설치되고, 제1 전위가 공급되는 제1 전원 배선과,

상기 제1 방향으로 연장하여 설치되고, 제2 전위가 공급되는 제2 전원 배선과,

제3 전위가 공급되는 제3 전원 배선과,

제4 전위가 공급되는 제4 전원 배선과,

상기 복수의 감지 증폭기에 대하여 미리 정해진 수마다 설치되고, 상기 제1 공통 소스선과 상기 제1 전원 배선 사이에 설치된 복수의 제1 스위치와,

상기 복수의 감지 증폭기에 대하여 미리 정해진 수마다 설치되고, 상기 제2 공통 소스선과 상기 제2 전원 배선 사이에 설치된 복수의 제2 스위치와,

상기 제1 공통 소스선과 상기 제3 전원 배선 사이에 설치된 제3 스위치와,

상기 제2 공통 소스선과 상기 제4 전원 배선 사이에 설치된 제4 스위치

를 포함하며,

상기 제3 및 제4 전위는 상기 제1 전위와 상기 제2 전위 사이에 있으며,

상기 메모리 셀로부터 판독되는 신호는 대응하는 상기 데이터선 상에서 상기 제3 전위 또는 상기 제4 전위로 증폭되고,

상기 제1 스위치와 상기 제2 스위치는 동일한 도전형의 MISFET로 구성되고,

상기 제1 및 제2 양방의 스위치 MISFET의 게이트는 공통으로 형성되는 것을 특징으로 하는 반도체 장치.

## 청구항 12.

제11항에 있어서,

상기 복수의 서브 메모리 어레이에는,

상기 복수의 워드선, 상기 복수의 데이터선 및 상기 복수의 메모리 셀이 배치되고, 하나의 각을 공유하는 제1 변과 제2 변을 갖는 4각형의 제1 영역과,

상기 제1 변을 따라 설치되고 상기 복수의 감지 증폭기, 상기 제1 및 제2 공통 소스선, 상기 제1 및 제2 전원 배선 및 상기 복수의 제1 및 제2 스위치가 배치되는 제2 영역과,

상기 제2 변을 따라 설치되고 상기 복수의 워드선 각각에 대응하여 설치되는 복수의 구동 회로 또는 상기 복수의 워드선 각각을 상총의 복수의 워드선과 접속하기 위한 복수의 접속부가 배치되는 제3 영역과,

상기 제1 영역의 상기 하나의 각과 상기 제2 및 제3 영역에 의해 둘러싸인 영역에 설치되고, 상기 제3 및 제4 스위치가 배치되는 제4 영역을 갖는 것을 특징으로 하는 반도체 장치.

## 청구항 13.

제12항에 있어서,

상기 메모리 셀에 기억된 정보를 상기 데이터선에 판독하는 경우에, 상기 복수의 워드선 중 하나가 선택된 후, 상기 복수의 제1 및 제2 스위치가 도통 상태가 되고, 미리 정해진 기간 경과 후에 상기 복수의 제1 및 제2 스위치는 비도통으로 됨과 함께 상기 제3 및 제4 스위치가 도통 상태가 되는 것을 특징으로 하는 반도체 장치.

## 청구항 14.

제11항에 있어서,

상기 복수의 제1 스위치 각각은 제1 도전형의 제3 MISFET이고, 상기 복수의 제2 스위치 각각은 제2 도전형의 제4 MISFET이고, 상기 제3 스위치는 상기 제1 도전형의 제5 MISFET이고, 상기 제4 스위치는 상기 제2 도전형의 제6 MISFET이며, 상기 제1 도전형은 P형이고, 상기 제2 도전형은 N형이며,

상기 제1 전위는 상기 제3 전위보다 높고, 상기 제3 전위는 상기 제4 전위보다 높고, 상기 제4 전위는 상기 제2 전위보다 높은 것을 특징으로 하는 반도체 장치.

### 청구항 15.

제11항에 있어서,

상기 제3 및 제4 전원 배선은 상기 제1 및 제2 전원 배선에 병렬로 상기 제1 방향으로 연장하여 설치되고,

상기 제3 스위치는 상기 복수의 감지 증폭기에 대하여 미리 정해진 수의 상기 감지 증폭기마다 설치되도록 복수의 제3 단위 스위치로 분할되고,

상기 제4 스위치는 상기 복수의 감지 증폭기에 대하여 미리 정해진 수의 상기 감지 증폭기마다 설치되도록 복수의 제4 단위 스위치로 분할되는 것을 특징으로 하는 반도체 장치.

### 청구항 16.

제15항에 있어서,

상기 복수의 서브 메모리 어레이에는,

상기 복수의 워드선, 상기 복수의 데이터선 및 상기 복수의 메모리 셀이 배치되고, 하나의 각을 공유하는 제1 변과 제2 변을 갖는 4각형의 제1 영역과,

상기 제1 변을 따라 설치되고 상기 복수의 감지 증폭기, 상기 제1 및 제2 공통 소스선, 상기 제1, 제2, 제3 및 제4 전원 배선, 상기 복수의 제1 및 제2 스위치 및 상기 제3 및 제4 스위치가 배치되는 제2 영역과,

상기 제2 변을 따라 설치되고 상기 복수의 워드선 각각에 대응하여 설치되는 복수의 구동 회로 또는 상기 복수의 워드선 각각을 상충의 복수의 워드선과 접속하기 위한 복수의 접속부가 배치되는 제3 영역을 갖는 것을 특징으로 하는 반도체 장치.

### 청구항 17.

제16항에 있어서,

상기 메모리 셀에 기억된 정보를 상기 데이터선에 판독하는 경우에, 상기 복수의 워드선 중 하나가 선택된 후, 상기 복수의 제1 및 제2 스위치가 도통 상태가 되고, 미리 정해진 기간 경과 후에 상기 복수의 제1 및 제2 스위치는 비도통으로 됨과 함께 상기 제3 및 제4 스위치가 도통 상태가 되는 것을 특징으로 하는 반도체 장치.

### 청구항 18.

제15항에 있어서,

상기 복수의 제1 스위치 각각은 제1 도전형의 제3 MISFET이고, 상기 복수의 제2 스위치 각각은 제2 도전형의 제4 MISFET이고, 상기 복수의 제3 단위 스위치 각각은 상기 제1 도전형의 제5 MISFET이고, 상기 복수의 제4 단위 스위치 각각은 상기 제2 도전형의 제6 MISFET이며, 상기 제1 도전형은 P형이고, 상기 제2 도전형은 N형이며,

상기 제1 전위는 상기 제3 전위보다 높고, 상기 제3 전위는 상기 제4 전위보다 높고, 상기 제4 전위는 상기 제2 전위보다 높은 것을 특징으로 하는 반도체 장치.

## 청구항 19.

반도체 장치로서,

복수의 메모리 셀로부터 대응하는 복수의 데이터선에 판독되는 신호를 증폭하기 위한 복수의 감지 증폭기와,

상기 복수의 감지 증폭기의 증폭 신호의 하이 레벨에 관련된 제1 전위를 제1 매쉬 형상 전원 배선으로부터 공급하기 위해서 설치되고, 상기 복수의 감지 증폭기 중 미리 정해진 수의 상기 감지 증폭기마다 설치된 복수의 제1 MISFET와,

상기 복수의 감지 증폭기의 증폭 신호의 로우 레벨에 관련된 제2 전위를 제2 매쉬 형상 전원 배선으로부터 공급하기 위해서 설치되고, 상기 복수의 감지 증폭기 중 미리 정해진 수의 상기 감지 증폭기마다 설치된 복수의 제2 MISFET와,

상기 복수의 제1 및 제2 MISFET는 동일한 도전형으로 됨과 함께, 상기 복수의 제1 및 제2 MISFET의 게이트는 공통의 구동 제어 신호선에 접속되고,

상기 구동 제어 신호선은 상기 복수의 제1 및 제2 MISFET의 도통 상태를 제어하기 위한 제어 신호를 전달하고,

상기 제어 신호의 유효 레벨과 무효 레벨의 전위차의 절대치는 상기 제1 전위와 상기 제2 전위의 전위차의 절대치보다 큰 것을 특징으로 하는 반도체 장치.

## 청구항 20.

제19항에 있어서,

상기 복수의 제1 및 제2 MISFET는 상기 복수의 감지 증폭기를 따라 일방향으로 연장하는 가상선 상에서 제1 MISFET와 제2 MISFET가 교대로 배치되고,

상기 가상선 상에 설치된 상기 구동 신호선은 상기 복수의 제1 및 제2 MISFET의 게이트 전극이 되는 것을 특징으로 하는 반도체 장치.

## 청구항 21.

복수의 서브 메모리 어레이를 포함하는 메모리 어레이를 갖는 반도체 장치로서,

상기 복수의 서브 메모리 어레이의 각각은,

제1 방향으로 연장하는 복수의 워드선과 제2 방향으로 연장하는 복수의 데이터선의 교점에 설치된 복수의 메모리 셀과,

상기 복수의 데이터선 각각에 대응하여 설치되고, 교차 결합된 제1 도전형의 제1 MISFET 쌍 및 제2 도전형의 제2 MISFET 쌍을 각각에 포함하는 복수의 감지 증폭기와,

상기 제1 방향으로 연장하여 설치되고, 상기 복수의 감지 증폭기의 제1 MISFET 쌍의 소스에 결합되는 제1 공통 소스선과,

상기 제1 방향으로 연장하여 설치되고, 상기 복수의 감지 증폭기의 제2 MISFET 쌍의 소스에 결합되는 제2 공통 소스선과,

상기 제1 방향으로 연장하여 설치되고, 제1 전위가 공급되는 제1 전원 배선과,

상기 제1 방향으로 연장하여 설치되고, 제2 전위가 공급되는 제2 전원 배선과,

상기 복수의 감지 증폭기에 대하여 미리 정해진 수의 상기 감지 증폭기마다 설치되고, 상기 제1 공통 소스선과 상기 제1 전원 배선 사이에 소스·드레인 경로가 접속된 상기 제2 도전형의 복수의 제3 MISFET와,

상기 복수의 감지 증폭기에 대하여 미리 정해진 수의 상기 감지 증폭기마다 설치되고, 상기 제2 공통 소스선과 상기 제2 전원 배선 사이에 소스·드레인 경로가 접속된 상기 제2 도전형의 복수의 제4 MISFET와,

상기 제1 방향으로 연장하여 설치되고 상기 복수의 제3 및 제4 MISFET의 게이트에 공통으로 접속된 제1 구동 제어선을 포함하며,

상기 복수의 감지 증폭기의 상기 제1 MISFET 쌍은 상기 제1 방향으로 연장하는 제1 가상선을 따라 배치되고,

상기 복수의 감지 증폭기의 상기 제2 MISFET 쌍은 상기 제1 방향으로 연장하는 제2 가상선을 따라 배치되고,

상기 복수의 제3 및 제4 MISFET는 상기 제1 및 제2 가상선 사이에 설치됨과 함께 상기 제1 방향으로 연장하는 제3 가상선을 따라 배치되는 것을 특징으로 하는 반도체 장치.

## 청구항 22.

삭제

## 청구항 23.

제21항에 있어서,

상기 복수의 제3 및 제4 MISFET는 상기 제3 가상선 상에서 1개씩 교대로 배치되는 것을 특징으로 하는 반도체 장치.

## 청구항 24.

제21항에 있어서,

상기 복수의 서브 메모리 어레이의 각각은,

상기 복수의 워드선, 상기 복수의 데이터선 및 상기 복수의 메모리 셀이 배치되고, 하나의 각을 공유하는 제1 변과 제2 변을 갖는 4각형의 제1 영역과,

상기 제1 변을 따라 설치되고 상기 복수의 감지 증폭기, 상기 제1 및 제2 공통 소스선, 상기 제1 및 제2 전원 배선 및 상기 복수의 제3 및 제4 MISFET가 배치되는 제2 영역과,

상기 제2 변을 따라 설치되고 상기 복수의 워드선 각각에 대응하여 설치되는 복수의 구동 회로 또는 상기 복수의 워드선 각각을 상충의 복수의 워드선과 접속하기 위한 복수의 접속부가 배치되는 제3 영역과,

상기 제1 영역의 상기 하나의 각과 상기 제2 및 제3 영역에 의해 둘러싸인 영역에 설치되고 상기 제1 및 제2 공통 소스선의 일단에 접속되는 프리차지 회로가 배치되는 제4 영역을 갖는 것을 특징으로 하는 반도체 장치.

### 청구항 25.

제21항에 있어서,

상기 복수의 데이터선 상에서 대응하는 메모리 셀로부터 판독된 신호는 상기 제1 전위 또는 제2 전위로 증폭되고,

상기 복수의 감지 증폭기를 활성화하는 경우, 상기 제1 구동 제어선에는 상기 제1 전위와 상기 제2 전위 사이의 전압보다 큰 전압이 인가되는 기간이 있는 것을 특징으로 하는 반도체 장치.

### 청구항 26.

제21항에 있어서,

상기 복수의 서브 메모리 어레이의 각각은,

제3 전위가 공급되는 제3 전원 배선과,

제4 전위가 공급되는 제4 전원 배선과,

상기 제1 공통 소스선의 일단과 상기 제3 전원선 사이에 소스·드레인 경로가 접속된 제5 MISFET와,

상기 제2 공통 소스선의 일단과 상기 제4 전원선 사이에 소스·드레인 경로가 접속된 제6 MISFET를 더 포함하며,

상기 제3 전위 및 제4 전위는 상기 제1 전위와 상기 제2 전위 사이에 있으며, 상기 제1 전위와 상기 제2 전위 사이의 전압은 상기 제3 전위와 상기 제4 전위 사이의 전압보다 크고,

상기 메모리 셀로부터 판독된 신호는 대응하는 상기 데이터선 상에서, 상기 제3 전위 또는 상기 제4 전위로 증폭되고,

상기 메모리 셀로부터 대응하는 상기 데이터선에 판독된 신호를 증폭하는 경우에, 상기 복수의 워드선 중 하나가 선택된 후, 상기 복수의 제3 및 제4 MISFET가 도통 상태가 되고, 미리 정해진 기간 경과 후에 상기 복수의 제3 및 제4 MISFET는 비도통으로 됨과 함께 상기 제5 및 제6 MISFET를 도통 상태로 하는 것을 특징으로 하는 반도체 장치.

### 청구항 27.

삭제

### 청구항 28.

제26항에 있어서,

상기 복수의 제3 및 제4 MISFET를 도통 상태로 하는 경우, 상기 제1 구동 제어선에는 상기 제1 전위와 제2 전위 사이의 전압보다 큰 전압이 인가되는 것을 특징으로 하는 반도체 장치.

### 청구항 29.

제26항에 있어서,

상기 반도체 장치는 상기 복수의 워드선 중 선택된 워드선에 인가하기 위한 승압 전압을 형성하기 위한 승압 회로를 더 포함하고, 상기 복수의 제3 및 제4 MISFET를 도통 상태로 하는 경우, 상기 제1 구동 제어선에는 상기 승압 전압이 인가되는 것을 특징으로 하는 반도체 장치.

### 청구항 30.

제21항에 있어서,

상기 복수의 서브 메모리 어레이의 각각은,

상기 제1 방향으로 연장하여 설치되고, 제3 전위가 공급되는 제3 전원 배선과,

상기 제1 방향으로 연장하여 설치되고, 제4 전위가 공급되는 제4 전원 배선과,

상기 복수의 감지 증폭기에 대하여 미리 정해진 수의 상기 감지 증폭기마다 설치되고, 상기 제1 공통 소스선과 상기 제3 전원 배선 사이에 소스·드레인 경로가 접속된 상기 제2 도전형의 복수의 제5 MISFET와,

상기 복수의 감지 증폭기에 대하여 미리 정해진 수의 상기 감지 증폭기마다 설치되고, 상기 제2 공통 소스선과 상기 제4 전원 배선 사이에 소스·드레인 경로가 접속된 상기 제2 도전형의 복수의 제6 MISFET를 더 포함하며,

상기 제3 전위 및 제4 전위는 상기 제1 전위와 상기 제2 전위 사이에 있으며, 상기 제1 전위와 상기 제2 전위 사이의 전압은 상기 제3 전위와 상기 제4 전위 사이의 전압보다 크고,

상기 복수의 데이터선 상에서 대응하는 메모리 셀로부터 판독된 신호는 상기 제3 전위 또는 상기 제4 전위로 증폭되고,

상기 메모리 셀로부터 대응하는 상기 데이터선에 판독된 신호를 증폭하는 경우에, 상기 복수의 워드선 중 하나가 선택된 후, 상기 복수의 제3 및 제4 MISFET가 도통 상태가 되고, 미리 정해진 기간의 경과 후에 상기 복수의 제3 및 제4 MISFET는 비도통으로 됨과 함께 상기 복수의 제5 및 제6 MISFET를 도통 상태로 하는 것을 특징으로 하는 반도체 장치.

### 청구항 31.

삭제

### 청구항 32.

제30항에 있어서,

상기 복수의 제3 및 제4 MISFET를 도통 상태로 하는 경우, 상기 제1 구동 제어선에는 상기 제1 전위와 제2 전위 사이의 전압보다 큰 전압이 인가되는 것을 특징으로 하는 반도체 장치.

### 청구항 33.

제30항에 있어서,

상기 반도체 장치는 상기 복수의 워드선 중 선택된 워드선에 인가하기 위한 승압 전압을 형성하기 위한 승압 회로를 더 포함하고,

상기 복수의 제3 및 제4 MISFET를 도통 상태로 하는 경우, 상기 제1 구동 제어선에는 상기 승압 전압이 인가되는 것을 특징으로 하는 반도체 장치.

**청구항 34.**

제21항에 있어서,

상기 제1 도전형은 P형이고, 상기 제2 도전형은 N형인 것을 특징으로 하는 반도체 장치.

**청구항 35.**

제21항에 있어서,

상기 복수의 메모리 셀 각각은 1개의 MISFET와 1개의 캐패시터를 포함하는 다이내믹형 메모리 셀인 것을 특징으로 하는 반도체 장치.

**청구항 36.**

삭제

**청구항 37.**

삭제

**청구항 38.**

삭제

**청구항 39.**

삭제

**청구항 40.**

삭제

**명세서**

**기술분야**

본 발명은 반도체 장치에 관한 것으로, 특히 그 장치의 차동 증폭 동작에 관한 부분에 관한 것이다.

**배경기술**

본 명세서에서 참조 문헌의 리스트는 다음과 같고, 부여된 문헌 번호를 참조하는 것으로 한다. [문헌 1]:특개평6-309872 호 공보(대응 미국 특허에는 USP 5,412,605호가 있음), [문헌 2]:초 LSI 메모리 pp.161-167, K.Ito, Baihuukan 저, 培風館, 1994년 11월 5일 초판 발행, [문헌 3]:T. Yamada et al., ISSCC91 Dig. Tech. Papers, pp. 108-109, 1991, [문헌 4]:H. Hidaka et al., IEEE Journal of Solid State Circuit, Vol.27, No.7(1992), pp.1020-1027, [문헌 5]:특개소63-211191호 공보, [문헌 6]:Eto et al., ISSCC98 Dig. Tech. Papers, pp.82-83, 1998.

[문헌 1]에는 DRAM에서 전원 전압이 저전압화했을 때의 감지 증폭기의 동작을 안정화하기 위해서 감지 증폭기의 구동 초기에서 CMOS 감지 증폭기의 소스 노드에 최종적인 증폭 전압(예를 들면 GND)보다 큰 전압(예를 들면, GND보다 낮은 마이너스 전압)을 인가하는 기술이 기재된다. 이 방법은 최종적인 비트선 상에서의 증폭 전압보다 큰 전압으로 감지 증폭기를 구동하는 기간을 갖기 때문에 「오버 드라이브」라 불리고 있다.

[문헌 2]는 DRAM(Dynamic Random Access Memory)에 대하여 주로 기재된 것으로, 161~167 페이지에서는 「감지 회로」로서 메모리 셀로부터의 미소 신호를 증폭하기 위한 회로에 대하여 이미 설치되어 있다. 특히, 163~164 페이지에는 「(2) 전류 분산형 감지 증폭기 구동」으로서 복수의 감지 증폭기의 고속 구동의 방법을 기재한다. 즉, 감지 증폭기의 구동용 전압(데이터선의 최종 증폭 전압과 동등한 전압)을 매쉬 형상 배선으로 공급하고, 분산적으로 배치된 구동용 MOSFET(예를 들면 4개의 감지 증폭기당 1개의 구동용 MOSFET)를 통해 복수의 감지 증폭기를 구동하는 것이다. 또, [문헌 3] 및 [문헌 4]는 [문헌 2] 중에서 상기한 기술의 원 저서로서 인용되어 있는 문헌이다.

본원 발명자 등은 저전압 전원으로 동작시켜야 하는 대용량의 DRAM에 오버 드라이브 회로를 현실에 적용하기 위해서, 본원에 앞서서 DRAM에서의 감지 증폭기와 그 오버 드라이브 구동 회로의 현실적인 배치면에 대하여 검토하였다.

도 25는 본원에 앞서서 검토한 오버 드라이브 구동 회로를 갖는 DRAM의 회로의 주요부를 나타낸 것이다. 이 회로는 데이터선의 고레벨 "H" 전압(VDL)보다 큰 전압 VDH를 이용하여 P측 공통 소스선 CSP를 오버 드라이브하는 것이다. 이 오버 드라이브 구동 회로는 P측 공통 소스선의 일단에 설치된 하나의 PMOS 트랜ジ스터 QDP1을 통해 CSP의 일단으로부터 오버 드라이브 전압 VDH를 공급한다. 오버 드라이브 회로의 부가를 생각하면, 이와 같이 CSP의 일단에 오버 드라이브 구동 회로를 설치하는 것은 회로 면적 저감 측면에서 바람직하다.

도 26에 도 25의 감지 증폭기 동작 시의 공통 소스선의 동작 파형 및 데이터선의 동작 파형을 나타낸다. 감지 증폭기가 증폭을 개시하기 전은 데이터선 및 공통 소스선이 VDL/2에 끊어져 있는 것으로 한다. SP1이 로우 레벨로 되고 QDP1이 도통 상태가 되어 공통 소스선 CSP에 VDH가 공급된 경우, VDH가 공급 노드에 대하여 SAn이 가장 가까운 단에 있으며, SA1이 가장 먼 단이 된다. QDP1을 도통하는 기간, 즉 오버 드라이브 기간 Tod는 데이터선 "H" 레벨측이 VDL까지 고속이고, 또한 VDL을 넘지 않도록 설정된다.

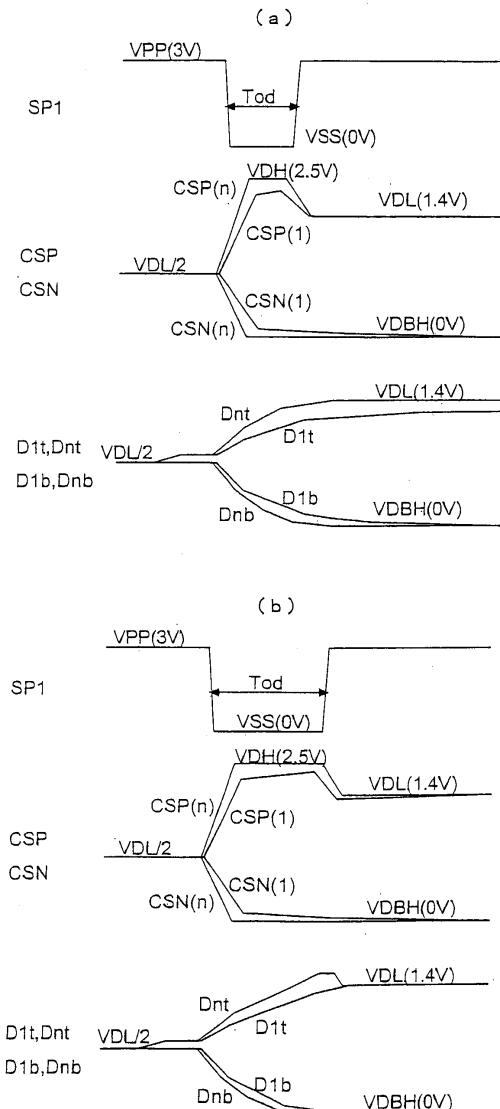

도 26의 (a)는 감지 드라이버의 근단, 즉 SAn에서 Tod를 최적화한 경우이고, 또한 도 26의 (b)는 원단, 즉 SA1에서 Tod를 최적화한 경우를 나타낸다. 도 26의 (a)에 도시한 바와 같이 근단에서 최적화하면 감지 초기의 공통 소스선으로부터 각 SA에 흐르는 전류에 의해 공통 소스선에는 전압 강하가 발생한다. 한편, 원단에서는 충분한 전압[CSP(1)]이 상승하기 전에 OFF가 되고, 원하는 충분한 높은 실효 게이트 전압을 얻을 수 없다. 즉, 데이터선(D1t, D1b)은 저속 동작이 된다. 반대로, 도 26의 (b)에 도시한 바와 같이 원단(SA1)에서 최적화한 경우, 근단에서는 오버 드라이브의 효과가 너무 강해져서 데이터선 전압은 VDL 이상이 된다. 이 때문에, 소비 전력이 증가한다. 이상과 같이 공통 소스선의 저항에 의한 전압 강하에 의해 감지 증폭기의 위치에 따라 감지 속도가 저하하거나 소비 전력이 증가하는 것이 본원 발명자 등에 의해 분명해졌다.

한편, [문헌 2]~[문헌 4]에는 감지 증폭기의 공통 소스선으로의 전류 집중과 그에 따른 전압 효과에 대하여 검토되고 있지만, 감지 증폭기의 오버 드라이브 회로에 대한 적용에 대해서는 고려되어 있지 않다.

즉, 본원 발명의 목적의 하나는 오버 드라이브 시의 복수의 감지 증폭기 사이의 구동의 불균일을 해소하는 데 있다. 본원 발명의 또 다른 목적의 하나는 오버 드라이브 회로의 불균일을 해소하면서 감지 증폭기를 포함한 레이아웃 면적의 증가를 저감하는 것이다.

### 〈발명의 개시〉

본원 발명의 대표적인 수단은 다음과 같다. 오버 드라이브용 구동 스위치를 감지 증폭기 열을 따라 분산 배치하고, 복구용 구동 스위치를 감지 증폭기 열의 일단에 집중 설치한다. 오버 드라이브용 전위는 매쉬 형상 전원 배선을 이용하여 공급하면 좋다.

또한, 감지 증폭기의 하이측과 로우측의 구동 스위치를 동일한 도전형 MISFET로 구성하여 게이트 신호를 공유화하면, 분산 배치한 구동 스위치와 감지 증폭기를 포함한 부분의 레이아웃 면적을 작게 할 수 있다.

또한, 감지 증폭기에 임계치 전압이 낮은 MISFET를 이용한 경우에는 액티브 스탠바이에 있어서의 누설 전류의 저감을 위해서 감지 증폭기의 공통 소스 노드의 전위를 제어하면 좋다. 활성화한 상태의 감지 증폭기의 공통 소스 노드의 전위를 제어하기 위한 수단의 바람직한 예는 임피던스 가변인 감지 증폭기 구동 스위치이다.

### 실시예

이하, 본 발명의 실시예를 도면을 이용하여 상세히 설명한다. 실시예의 각 블록을 구성하는 회로 소자는 특별히 제한되지 않지만, 공지의 CMOS(상보형 MOS 트랜지스터) 등의 접적 회로 기술에 의해 단결정 실리콘과 같은 1개의 반도체 기판 상에 형성된다. MOSFET(Metal Oxide Semiconductor Field Effect Transistor)의 회로 기호는 화살표를 붙이지 않은 N형 MOSFET(NMOS)와, 화살표를 붙인 P형 MOSFET (PMOS)로 구별된다. 이하, MOSFET를 간략하게 MOS라 부르기로 한다. 단, 본원 발명은 금속 게이트와 반도체층 사이에 설치된 산화질연막을 포함하는 전계 효과 트랜지스터만으로 한정되는 것이 아니라 MISFET(Metal Insulator Semiconductor Field Effect Transistor) 등의 일반적인 FET를 이용한 회로에 적용된다.

### 〈제1 실시예〉

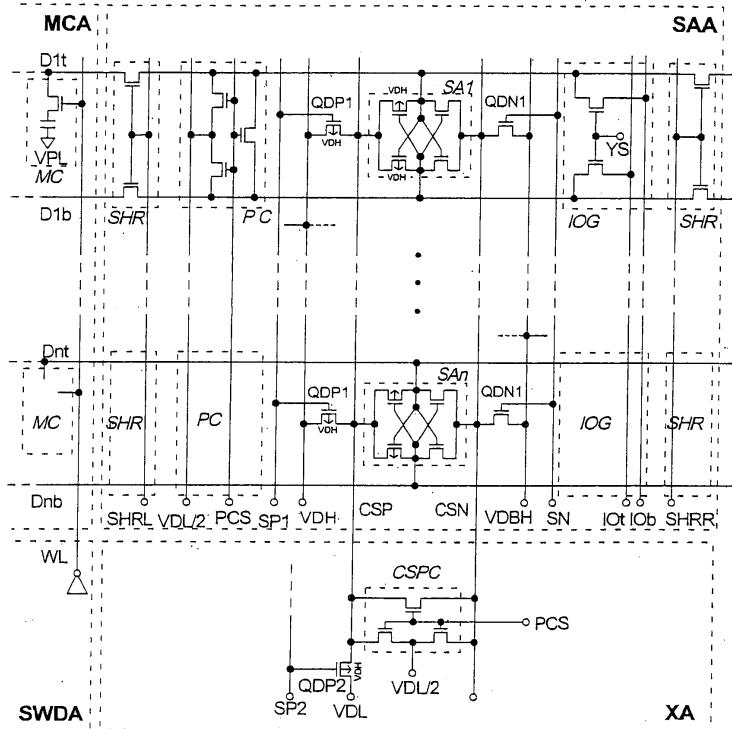

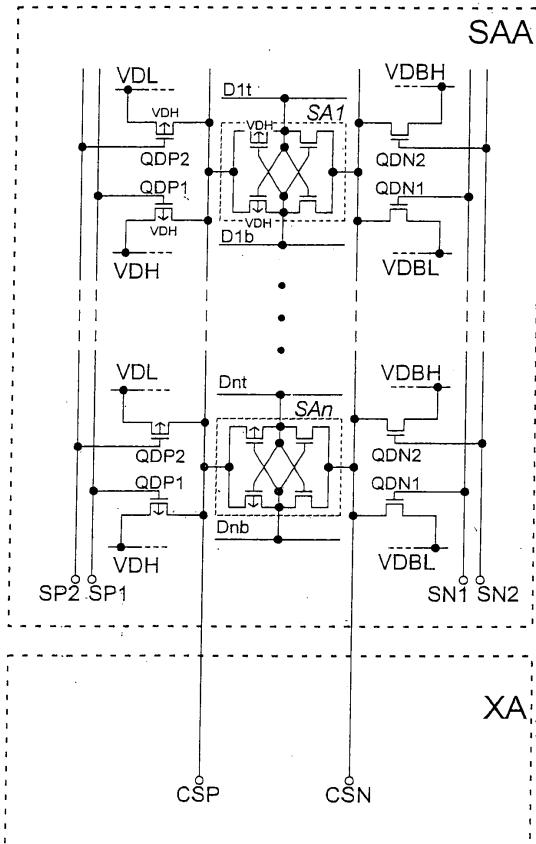

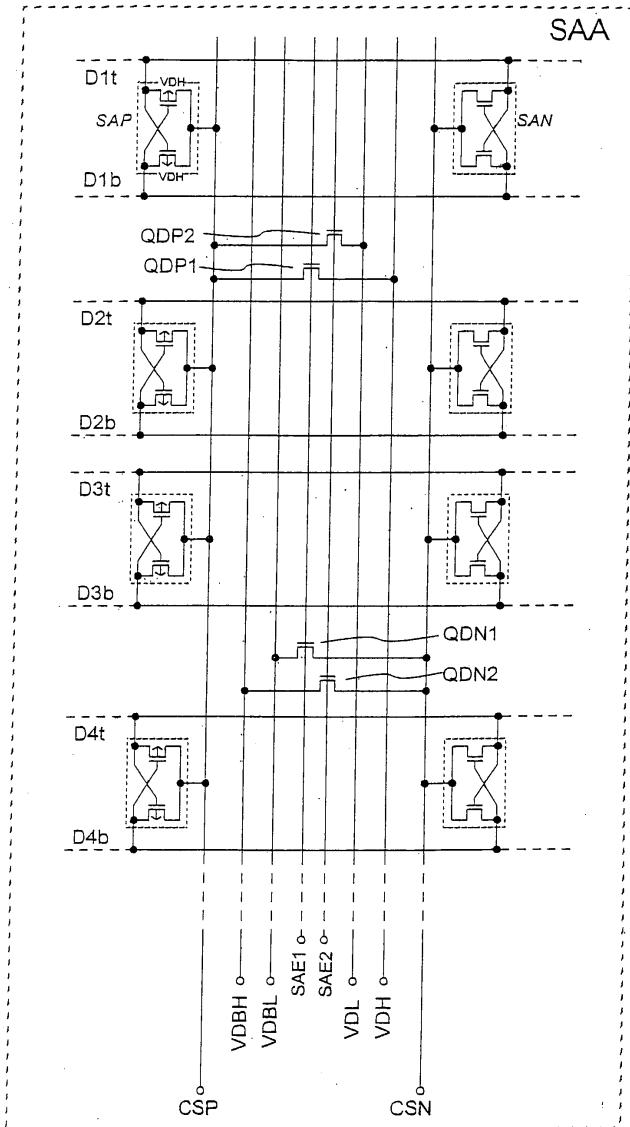

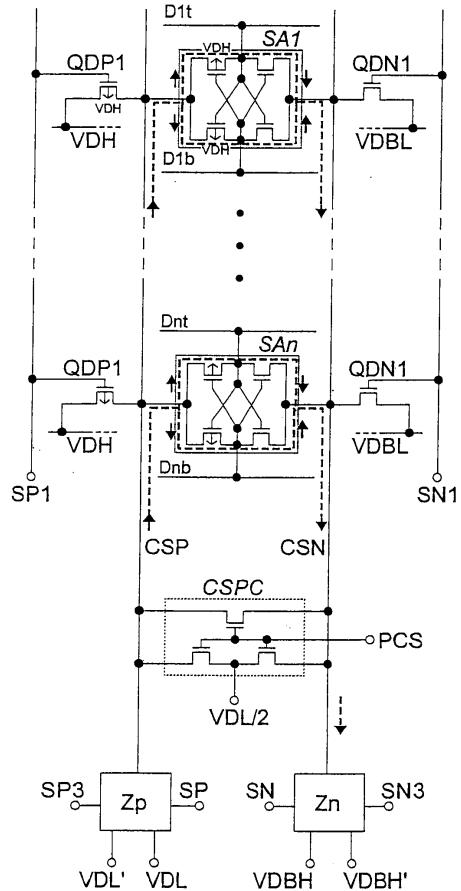

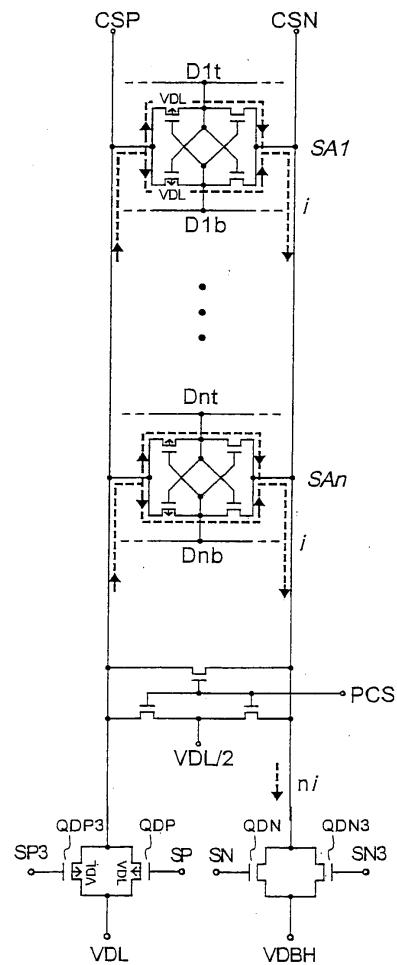

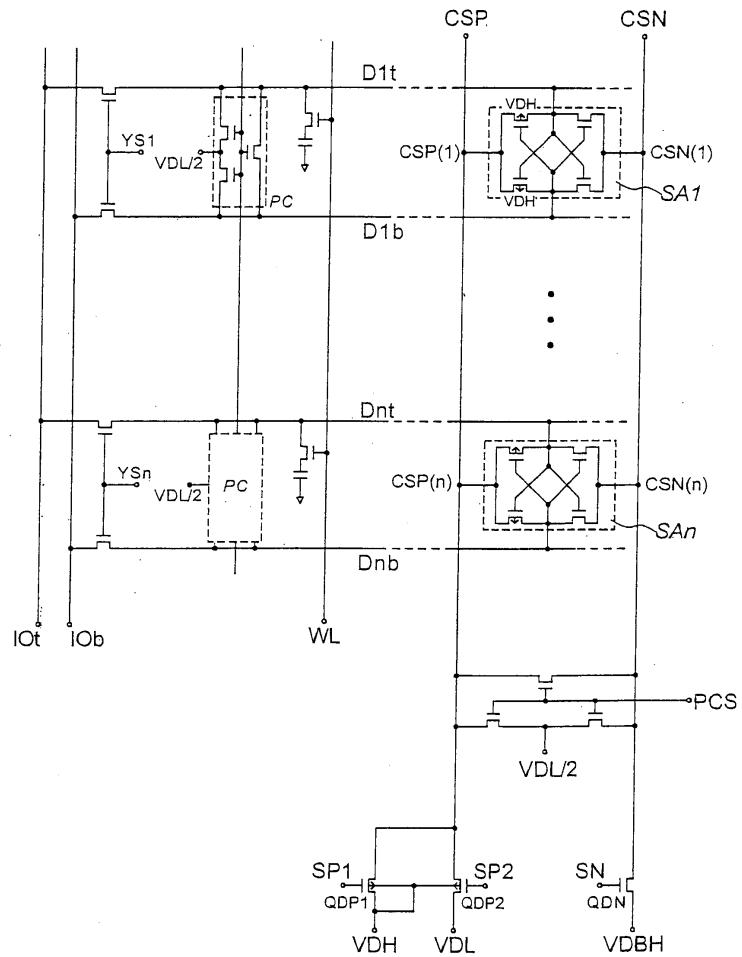

도 1에 다이내믹 메모리의 서브 메모리 어레이 SMA의 상세를 나타낸다. 본 실시예는 감지 증폭기의 P측과 N측의 소스 노드 중 한쪽을 증폭 초기에 오버 드라이브하는 회로를 나타낸 것이다. P측 공통 소스선 CSP를 구동하는 오버 드라이브용 구동 스위치 QDP1을 감지 증폭기 영역 SAA 내에 분산하여 배치하고 있는 것이 특징이다. 도 1의 상세한 설명을 하기 전에, 도 22, 도 23을 사용하여 본원의 대상이 되는 도 1의 회로의 메모리 장치 중에서의 전체적인 포지셔닝을 우선 설명한다.

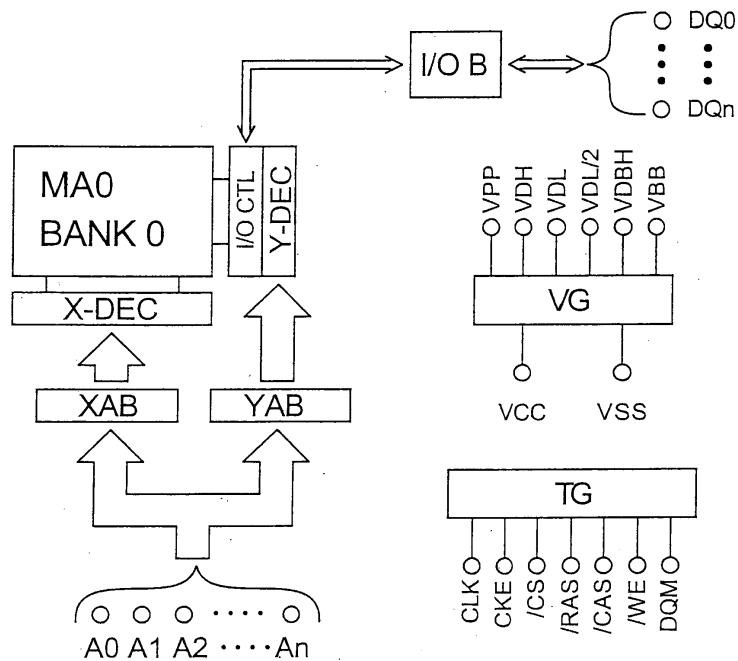

도 22에 본원 발명이 적용되는 SDRAM(Synchronous Dynamic Random Access Memory)의 전체 블록을 나타낸다. 각 회로 블록은 제어 신호가 입력되는 타이밍 신호 생성 회로 TG로 형성되는 내부 제어 신호의 타이밍으로 동작한다. TG에 입력되는 제어 신호에는 클럭 신호 CLK의 타이밍으로 입력되는 칩 선택 신호 /CS, 로우 어드레스 스트로브 신호 /RAS, 컬럼 어드레스 스트로브 신호, 기록 인에이블 신호 /WE가 있다. 이를 제어 신호와 어드레스 신호의 조합은 커맨드라 불린다. 클럭 인에이블 신호 CKE는 클럭 신호의 유효 무효를 결정한다. 또한, 입출력 마스크 신호 DQM은 입출력 단자(DQ0, … DQn)로부터 입출력되는 데이터를 마스크하기 위해서 데이터 입출력 버퍼 I/OB를 제어하기 위한 신호이다.

SDRAM에서는 어드레스 입력 단자(A0, A1, … An)로부터 로우 어드레스나 컬럼 어드레스가 시분할로 입력되는 어드레스 멀티 방식이 채택된다. 로우 어드레스 버퍼 XAB에 입력된 로우 어드레스는 로우 디코더 X-DEC로 해독되어 하나의 메모리 어레이 MA0 중의 특정한 워드선이 선택되고, 그에 따라 1워드분의 메모리 셀이 선택 상태가 된다. 계속해서, 컬럼 어드레스가 컬럼 어드레스 버퍼 YAB에 입력되면 컬럼 어드레스 디코더 Y-DEC에 의해 판독 또는 기입을 행하는 메모리 셀이 더 선택된다. 또한, SDRAM은 통상 뱅크 어드레스로 지정되는 복수의 메모리 어레이(또는 메모리 뱅크)를 갖지만, 이 도면에서는 하나의 메모리 어레이 MA0(BANK0)만을 대표적으로 나타내었다.

도 22에서 도시한 SDRAM의 전압 발생 회로 VG에서 발생되는 내부 전원계에 대하여 설명한다. 여기서는 VSS(0V)를 기준으로 하여 VCC(2.5V)가 외부로부터 공급되는 단일 전원 방식이 채택된다. 가장 전위가 높은 내부 전원은 VPP(3.0V)이고, 차지 펌프 회로를 포함한 승압 회로에 의해 형성되고, 워드선 구동 회로 등에 공급된다. VDH(2.5V=VCC)는 XAB, YAB, IOB, X-DEC 등의 주변 회로의 동작 전원이다. VDL(1.5V)과 VDBH(0V=VSS)는 후술하는 데이터선의 복구 전위를 결정하고, 감지 증폭기에 공급되는 전위이다. VDL은 강압 회로(전압 리미터)에 의해 형성된다. 본 실시예에서는 하프 프리차지 방식을 채택하기 때문에, 대기 시의 데이터선 등에 공급되는 VDL/2(0.75V)도 VDL로부터 형성된다. VDL/2는 메모리 셀의 플레이트 전위 VPL로서도 이용된다. 마지막으로 VBB(-0.75V)는 NMOS의 백 게이트를 시스템의 최저 전위로 바이어스하기 위한 기판 전위로서, 차지 펌프를 포함한 승압 회로에 의해 형성된다.

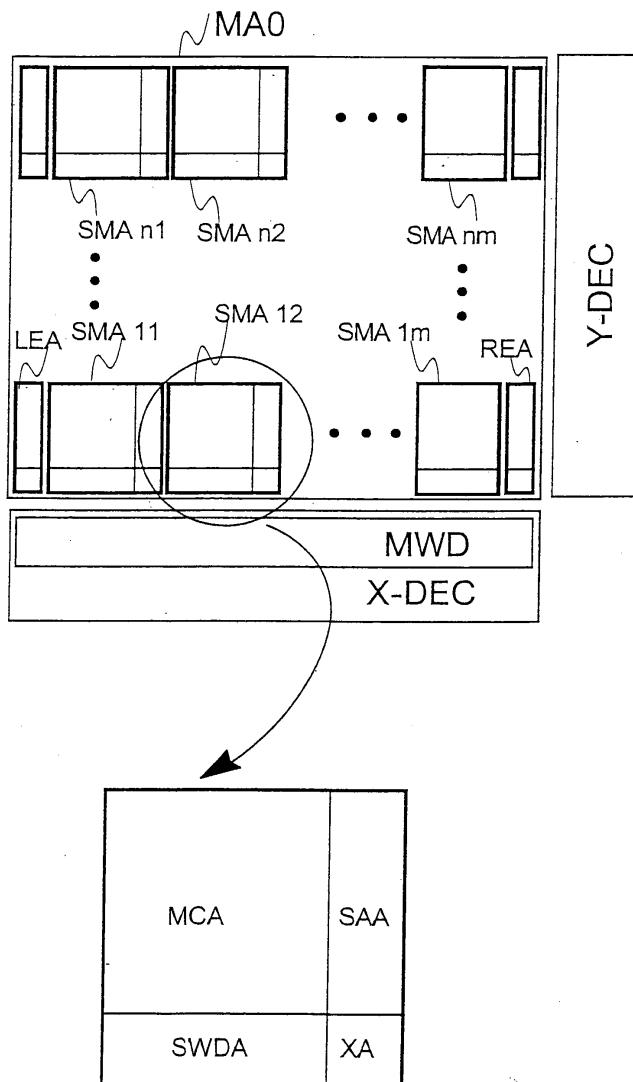

도 23은 도 22의 메모리 어레이 MA0의 내부를 더욱 상세히 도시한 것이다. MA0은 매트릭스형으로 배치된 서브 메모리 어레이 SMA11~SMAAnm을 포함한다. 특별히 제한되지 않지만 이 메모리 어레이에는 계층 워드선 방식을 채택하여 MA0의 1번에는 메인 워드 드라이버 열 MWD가 배치된다. MWD에 접속되는 메인 워드선은 복수의 서브 메모리 어레이(예를 들면 SMA11~SMAn1의 방향으로)에 걸쳐 걸치도록 상층의 금속 배선층에 설치된다. 또한, 컬럼 방향의 선택은 컬럼 디코더 Y-DEC로부터 출력되는 복수의 컬럼 선택선(YS 선)이 복수의 서브 메모리 어레이(예를 들면 SMA1m~SMA11의 방향으로)에 걸쳐 걸치도록 설치되는 공통 Y 디코더 방식이 채택된다. 또, 도 23의 MA0 내에서 SMA11~SMA1m의 좌단과 우단에는 서브 메모리 어레이의 말단 처리를 위한 영역인 우단 영역 LEA와 좌단 영역 REA가 설치된다. LEA와 REA는 SAA 및 XA를 약간 변형한 것이다. 이는 감지 증폭기가 교대 배치형인 공유 감지 방식을 채택하기 위한 매트단의 말단 처리에 대한 배려이다.

도 23의 확대도에 도시한 바와 같이 1개의 서브 메모리 어레이의 내부는 메모리 셀 영역 MCA, 감지 증폭기 영역 SAA, 서브 워드 드라이버 영역 SWDA 및 크로스 영역 XA로 분할된다. 배치로서는 4각형 MCA의 하나의 각을 공유하는 제1 번과 제2 번이 있을 때, SAA는 제1 번을 따라 설치된 장방형 영역이고, SWDA는 제2 번을 따라 설치된 장방형 영역이 된다. 또한, XA는 제1 번과 제2 번을 공유하는 각에 SAA와 SWDA에 의해 둘러싸인 영역이다.

도 1은 도 23의 확대도로 도시된 서브 메모리 어레이의 상세를 나타내고 있다. 우선, 메모리 셀 영역 MCA 내에서 데이터 선 쌍 D1t, D1b … Dnt, Dnb는 메모리 셀 어레이 MCA에서 복수의 워드선 WL과 교차하고, 미리 정해진 교차점에는 다이나믹형 메모리 셀 MC가 접속된다. MC는 데이터를 축적하는 하나의 캐패시터 및 하나의 MOS 트랜지스터, 여기서는 NMOS 트랜지스터로 구성된다. 본 실시예는 소위 이교점 방식의 데이터선과 메모리 셀의 배치를 예로 하고 있으나, 특별히 제한되지 않고 일교점 방식에도 적용할 수 있다.

서브 워드 드라이버 영역 SWDA에는 상기한 복수의 워드선 각각에 대하여 설치된 복수의 서브 워드 드라이버 SWD가 설치된다. 서브 워드 드라이버는 도 23에서 상술한 메인 워드선과 FX 드라이버 FXD의 제어 신호와의 논리합에 의해 활성화된다. FXD는 크로스 영역 XA 내에 설치되지만 도 1에서는 생략하였다. 계층 워드선 방식이 아닌 워드 분로 방식을 채택하는 경우, SWDA 내에는 서브 워드 드라이버 대신에 상층에 설치된 AL 등의 금속으로 형성된 보강용 워드선과 하층 폴리실리콘층의 게이트와 공통인 워드선을 접속하는 관통 허파 컨택트가 설치된다. 이 경우 SWDA는 워드 분로 영역이라 부를 수 있다.

이하, 감지 증폭기 영역 SAA를 설명한다. SAA 내에서는 데이터선 쌍의 한 쌍(D1t, D1b)에 대응하여 좌우의 공유 스위치 SHR, 프리차지 회로 PC, 감지 증폭기 SA1, 컬럼 스위치 IOG 등이 설치된다. 하나의 메모리 셀 영역 MCA의 데이터 쌍의 수로서는 512 내지 2048쌍을 상정하고 있다. 따라서, SAA 내의 감지 증폭기의 수로서는 256 내지 1024개를 배치하게 된다. 감지 증폭기의 교대 배치 구조를 위해 감지 증폭기의 수는 데이터선 쌍의 수의 절반이 되기 때문이다. 공유 스위치는 감지 증폭기 SA1을 좌측과 우측의 메모리 셀 영역으로 공용하기 위한 전환 스위치이다. 여기서, 공유 스위치는 NMOS가 되고, 데이터선의 프리차지 기간에는 그 게이트 제어 신호 SHRL과 SHRR은 VPP, VDH 또는 VDL 전위가 된다. 예를 들면, 좌측의 메모리 셀 영역을 액세스할 때에는 SHRL=VPP 또는 VDH, SHRR=VDBH로서 한쪽만 NMOS의 임계치 전압 저하없이 도통시킨다. PC는 데이터선 프리차지 기간에 제어 신호 PCS에 의해 데이터선 쌍에 VDL/2를 공급한다. 컬럼 스위치 IOG는 컬럼 디코더의 컬럼 선택 신호 YS에 의해 선택된 데이터선 쌍을 공통 입출력선 쌍 IOt, IOb와 접속하여 외부와 데이터의 입출력 경로를 형성하는 것이다.

감지 증폭기 SA는 2개의 CMOS 인버터가 교차 결합된 래치형 증폭 회로이다. 즉, 이 감지 증폭기는 소스가 공통 접속되어 게이트와 드레인의 상호 교차 결합된 PMOS 쌍과, 마찬가지로 결합된 NMOS 쌍을 포함한다. P 및 NMOS 쌍의 소스는 각각 P측 공통 소스선 CSP 및 N측 공통 소스선 CSN에 공통으로 접속된다. 오버 드라이브 방식의 감지 증폭기에는 복구 전위와 오버 드라이브 전위가 필요하다. 복구 전위는 데이터선 상에서의 최종 증폭 시의 하이 레벨과 로우 레벨을 결정하는 전원 전위이다. 메모리 셀에 재기입을 행할 때의 전위와 동일하므로 복구 전위라 불린다. 여기서는 VDL이 하이측 복구 전위이고, VDBH가 로우측 복구 전위가 된다. 본 실시예에서 오버 드라이브 전위는 하이측만 공급되고, VDH (>VDL)이다.

감지 증폭기의 P측에서는 하이측 오버 드라이브 전위 VDH를 공급하기 위한 제1 전원선이 CSP와 병렬 설치된다. 이 제1 전원선과 P측 공통 소스선 CSP 사이에 복수의 스위치 QDP1이 분산 설치된다. 도 1에서는 1개의 감지 증폭기당 1개의 PMOS를 설치하는 구성으로 하고 있다. 한편, 하이측의 복구 전위 VDL은 SAA 내에서는 없고, 크로스 영역 XA에 집중 설치된 스위치 QDP2에 의해 P측 공통 소스선 CSP의 일단으로부터 공급하도록 하고 있다. 또, 공통 소스선의 프리차지 회로 CSPC도 크로스 영역 XA에 설치되고 CSP 및 CSN의 일단으로부터 프리차지를 위한 단락 및 VDL/2의 누설 보상을 하도록 하고 있다.

감지 증폭기의 N측에서는 로우측 복구 전위 VDBH를 공급하기 위한 제2 전원 배선이 N측 공통 소스선 CSN과 병렬로 설치된다. 이 제2 전원선과 N측 공통 소스선 CSN 사이에 복수의 스위치 QDN1이 분산 설치된다. 도 1에서는 QDN1은 1개의 감지 증폭기당 1개의 NMOS의 비율로, 상기한 QDP1과 쌍을 이루도록 설치된다.

SAA 내에서 감지 증폭기의 PMOS 쌍과 오버 드라이브용 스위치 MOS QDP1은 특별히 제한되지 않지만 P형 기판에 형성된 공통의 N형 웰 내에 형성되고, 그 N형 웰에는 P측 기판 바이어스로서 VDH가 인가된다. 즉, 이들 PMOS의 백 게이트는 오버 드라이브 전위와 동등한 VDH에 바이어스된다. 또한, 이들 PMOS의 백 게이트는 VPP에 바이어스하도록 하여도 좋다. 마찬가지로, 감지 증폭기의 NMOS 쌍과 QDN1도 P형에 도핑된 반도체 영역(P형 기판에 직접 또는 P형 기판에 형성된 3중 웰 내)에 공통으로 형성되고, 그 반도체 영역에는 N측 기판 바이어스로서 VDBH 또는 VBB가 인가된다.

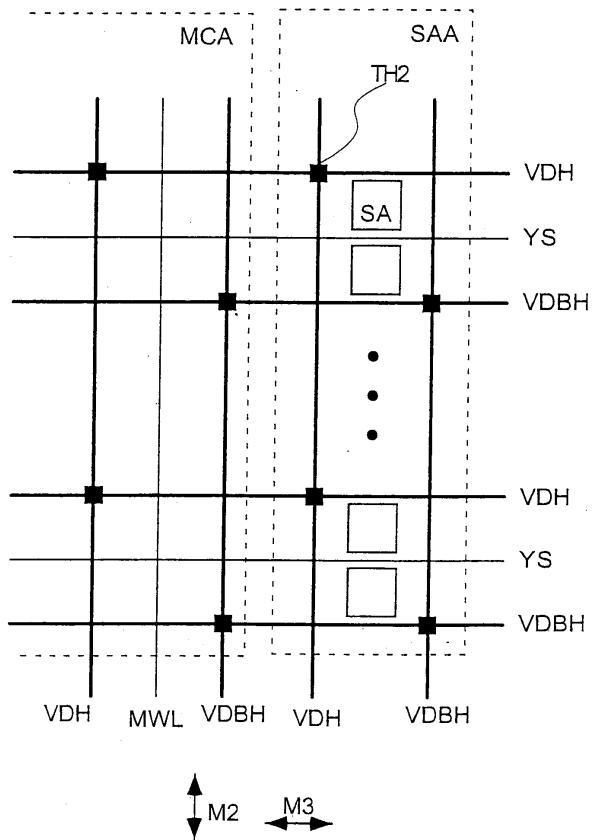

도 24에 도 1의 전원 VDH와 VDBH를 공급하는 배선을 나타낸다. VDH와 VDBH는 이 도면에 도시한 배선 임피던스가 낮은 매쉬 형상 전원 배선에 의해 공급된다. 이 도면의 세로 방향의 배선은 2번째 금속(알루미늄 Al등) 배선층 M2에 형성된 것이다. 메모리 셀 영역 MCA에서는 메인 워드선 MWL 사이를 뚫고 나가도록 MWL과 병행하여 VDH와 VDBH를 공급하

는 배선이 설치된다. 메인 워드선 MWL은 예를 들면 4개 또는 8개 정도의 워드선당 1개 설치하는 것을 상정하고 있다. 또, 감지 증폭기 영역 SAA에도 VDH와 VDBH를 공급하는 배선이 MWL과 병행하도록 설치된다. 이 M2의 VDH와 VDBH의 전원 배선이 상술한 도 1의 제1 전원 배선과 제2 전원 배선이다.

한편, 도 24의 가로 방향 배선은 M2보다 상층인 제3번계 금속(A1 등) 배선층 M3에 형성되는 것이다. 메모리 셀 영역 MCA 및 감지 증폭기 영역 SAA에 걸치도록 컬럼 선택선 YS가 설치된다. YS는 예를 들면 4쌍의 데이터선당 1개 설치된다. 그리고, YS 사이를 뚫고 나가도록 YS에 병행하여 VDH와 VDBH를 공급하는 배선이 설치된다. M2와 M3의 VDH나 VDBH의 전원 배선은 그 교점에서, M2와 M3을 연결하는 관통 훌 컨택트 TH2에 의해 접속된다. 이상, 교차하는 M2와 M3의 전원 배선과 관통 훌로 결합하도록 한 VDH나 VDBH의 매쉬 형상 전원 배선은 임피던스가 낮은 것이 된다.

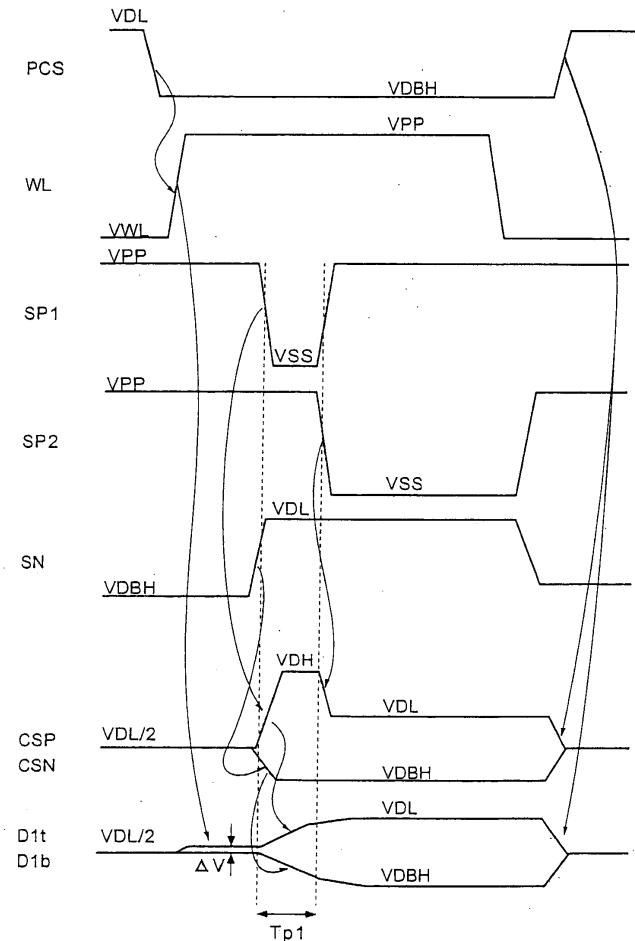

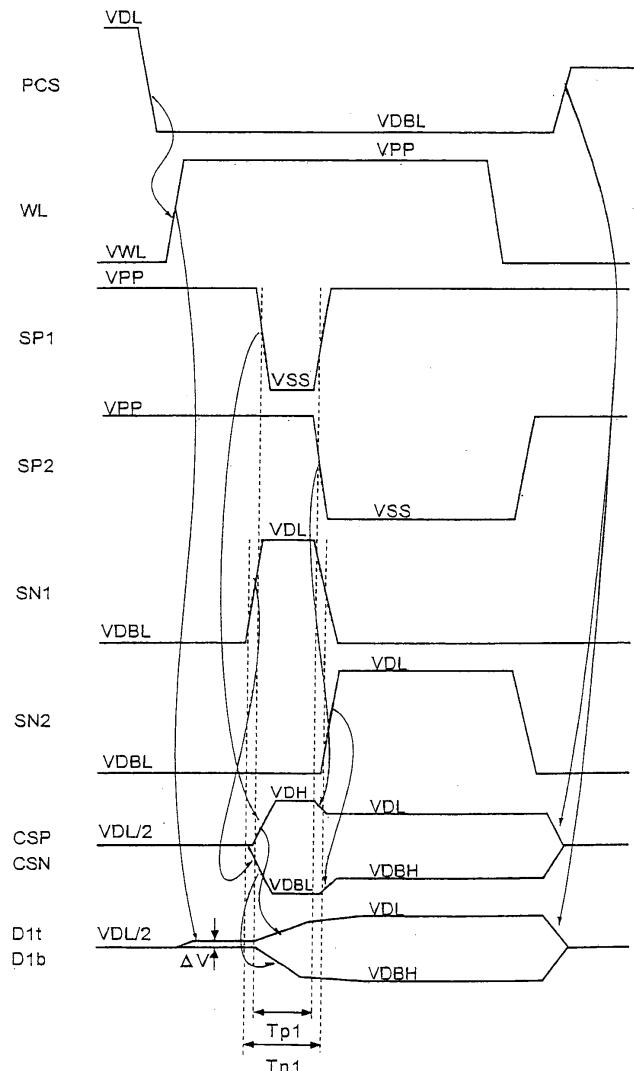

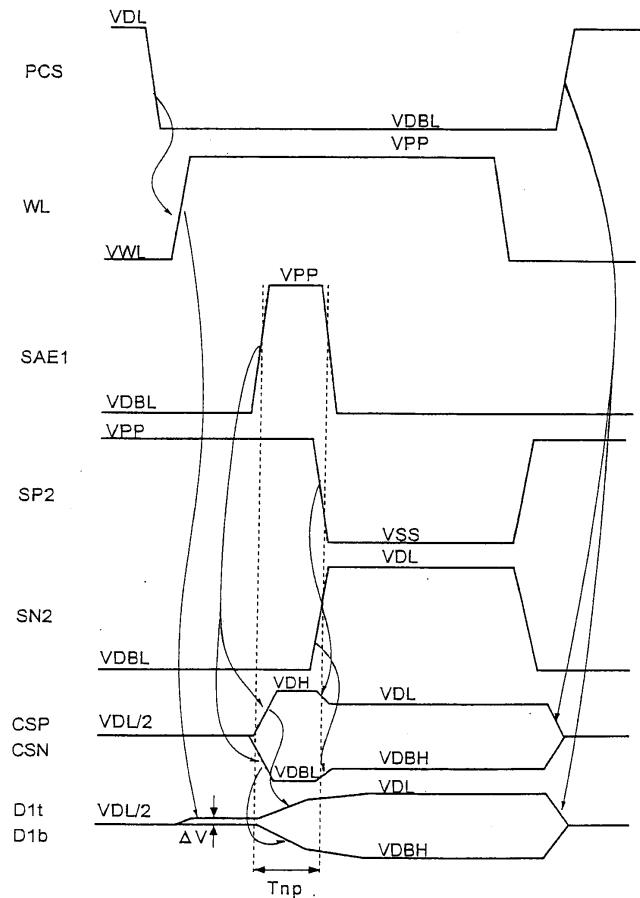

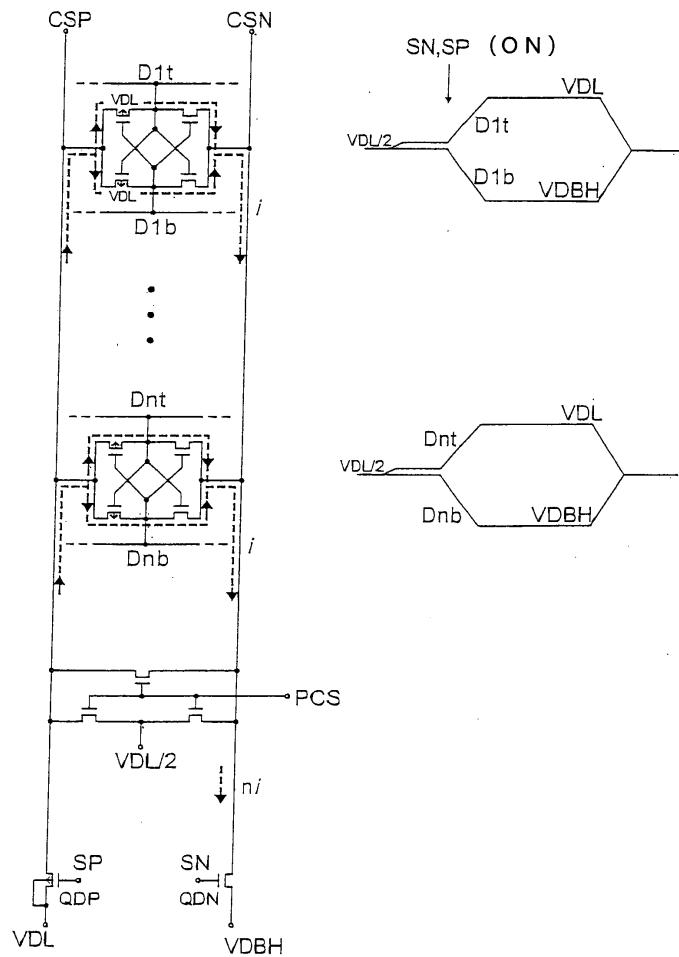

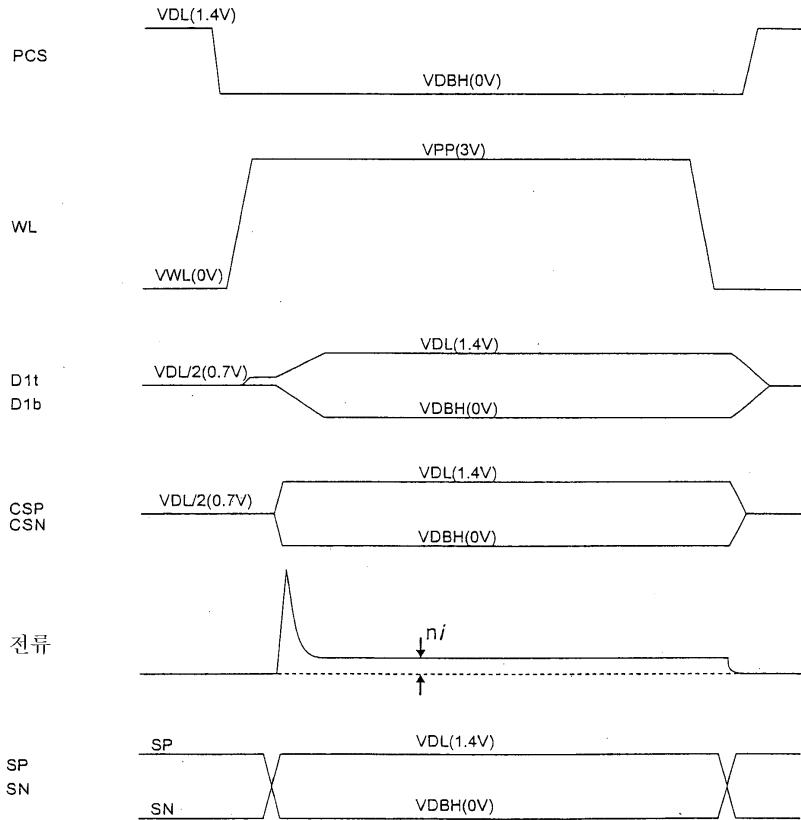

도 2에, 도 1의 서브 메모리 어레이의 동작 타이밍을 나타낸다. SDRAM에서는 로우 액티브 커맨드가 입력되면, 특정한 뱅크의 특정한 메인 워드선에 연결되는 메모리 셀이 일제히 감지 증폭기에 판독되어 증폭된다. 그 후, 프리차지 커맨드가 입력되면, 메모리 셀의 선택을 종료하여, 다음의 판독에 구비한 대기 상태인 프리차지 상태로 된다. 도 2의 과정은 로우 액티브 커맨드로부터 프리차지 커맨드가 투입되기까지의 도 1의 서브 메모리 어레이의 동작을 나타낸 것이다.

데이터선 및 공통 소스선의 프리차지 제어 신호 PCS가 하강 데이터선 및 공통 소스선의 VDL/2 프리차지를 정지한 후, 복수 워드선 중 하나의 워드선 WL이 선택되어 VWL(통상은 VWL=VSS)로부터 VPP가 된다. 그에 따라 선택된 메모리 셀 MC의 NMOS 트랜지스터의 게이트에는 VPP가 인가되어 활성화하고, 데이터를 기억하고 있는 캐패시터로부터 저장되어 있던 전하가 메모리 셀 MC이 접속되어 있는 데이터선 D1t, … Dnt에 판독된다. 셀의 전하에 의해 데이터선 쌍에는 미소 전압 차가 생기고, 셀의 데이터가 "H"일 때에는 D1t가 D1b보다 100mV 정도 높은 레벨이 된다. 여기서는 메모리 셀 MC의 셀 캐패시터에 "H"의 데이터가 기입되어 있던 경우를 상정하고 있다. 저레벨 "L"이 기억되어 있는 경우라도, 전위가 하강되는 것을 제외하면 동일하다.

셀 데이터가 완전하게 판독된 후, 감지 개시 시에는 N측 공통 소스 구동 제어 신호선 SN을 VDBH 내지 VDL 이상의 레벨로 하여 QDN을 활성화하고, CSN을 VDL/2 내지 VDBH에 구동시킨다. 이와 동시 또는 지연 단수 단만큼 지연되어 제1 P측 공통 소스 구동 제어 신호선 SP1을 예를 들면 VPP 내지 VSS로 함으로써 QDP1을 활성화하고, CSP를 VDL/2 내지 VDH로 구동시킨다. 이 때, 도 1, 도 2에서 상술한 바와 같이 VDH는 매쉬 형상 전원 배선이 낮은 임피던스로 공급되고, 또한 분산 배치된 스위치 QDP1을 통해 공급된다. 이 때문에, SA1 내지 SAn이 일제히 거의 동일한 타이밍으로 활성화되기 때문에, SA1 내지 SAn에 대한 오버 드라이브의 변동을 억제할 수 있다. 또한, 공통 소스선 CSP 및 CSN의 고속 구동이 실현된다. 또한, 오버 드라이브 구동에 의해 SA의 PMOS 트랜지스터의 소스·드레인간 전압 및 게이트·소스간 전압은 VDL/2보다 커지기 때문에, 데이터선 쌍의 미소 전압 차 ΔV를 고속 증폭할 수 있다.

감지 증폭기의 오버 드라이브 기간은 데이터선 고레벨측인 D1t의 증폭이 완전히 종료하지 않은 상태에서, 그 데이터선의 전위가 VDL의 근방이 되기까지의 시간 Tp1로 설정된다. 오버 드라이브는 데이터선 전위가 VDL보다 커지기 전에 정지하는 것이 소비 전력 등의 관점에서 바람직하다. Tp1의 기간의 경과 후에 SP1이 VSS 내지 VDH 이상의 레벨, 예를 들면 VPP가 된 후, 제2 P측 공통 소스 구동 제어 신호 SP2가 예를 들면 VPP 내지 VSS가 됨으로써 QDP2가 활성화되어 CSP를 VDL로 설정한다. 이에 따라, 데이터선 고레벨측은 VDL로 유지된다.

또한, 프리차지 커맨드가 들어간 후의 동작에 대해서는 다음과 같다. 선택 워드선 WL이 VPP 내지 VWL이 된다. 그 후, SN을 VDL 또는 VPP 내지 VDBH로 하고 CSN을 VDBH로부터 분리한다. 또한, 거의 동시에 SP2를 VSS 내지 VPP로 하고 CSP를 VDL로부터 분리한다. 전원으로부터 분리된 CSN, CSP 및 데이터선 쌍 D1t, D1b, … Dnt, Dnb는 프리차지 제어 신호 PCS에 의해 VDL/2에 프리차지된다.

이상, 본 실시예에 의해 얻어지는 효과는 다음과 같다. (1) 오버 드라이브 시에 발생하는 오버 드라이브용 전원 VDH로부터 데이터선으로의 충전 전류를 매쉬 형상 전원 배선으로 공급된 배선으로부터 그 배선의 근방이 되도록 분산 배치된 복수의 스위치 QDP1로부터 공급할 수 있기 때문에, 특정한 감지 증폭기 및 공통 소스선 CSP의 일부로의 전류 집중을 피할 수 있고, SA1로부터 SAn의 어느 하나의 SA에서도 동등한 오버 드라이브의 전압(VDH)으로 오버 드라이브를 행할 수 있다. (2) 오버 드라이브 기간의 설정은 QDP1의 게이트 신호 SP1에 의한 활성화되는 시간으로 설정할 수 있고, SA1과 SAn으로 동등하게 할 수 있다. 이들에 의해 오버 드라이브 진폭과 기간의 원근단 차를 작게 할 수 있다. (3) 데이터선으로부터 VDBH 단자로의 방전 전류는 다수 배치된 QDN에서 각각 어레이 상 매쉬 전원 VDBH로 흘러 나오기 때문에, 특정한 감지 드라이브 및 CSN으로의 전류 집중을 피할 수 있다.

또한, 본 실시예에 있어서 QDP1 및 QDP2 중 어느 하나, 또는 양방을 NMOS 트랜지스터로 구성할 수도 있다. 그 경우에는 제어 신호의 논리를 PMOS 트랜지스터로 구성한 경우와 역의 논리로 하는 것이 필요하다. QDP1 및 QDP2를 NMOS로 한 경우에는 비활성화 상태에서 게이트·소스간 전압이 마이너스 전압이 되기 때문에, VDH, VDL로부터 CSP로의 누설 전류를 저감시킬 수 있는 점에 이점이 있다.

또한, 본 실시예에서는 감지 증폭기 1개당 스위치 MOS QDP1과 QDN1을 1개 배치하는 것으로 하였지만, 감지 증폭기 2개, 4개, 8개당, QDP1과 QDN1을 1개 배치하도록 변형하여도 좋다. 또한, 스위치 MOS QDP1이나 QDN1은 감지 증폭기가 배열하는 방향으로 채널을 형성하는 확산층을 절단하지 않고 일렬로 접속된 긴 게이트 폭을 갖는 1개의 MOS로서 형성하여도 좋다. 본원 발명의 특징은 SAA 영역 내에 분포한 스위치 MOS를 오버 드라이브에 이용함으로써, 이 점에서는 미세하게 채널 폭을 절단하는지의 여부는 중요하지 않다.

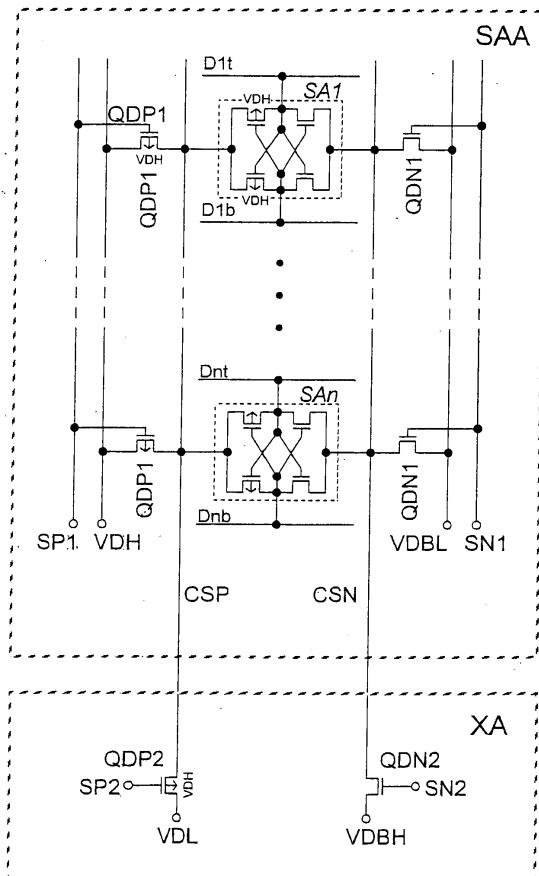

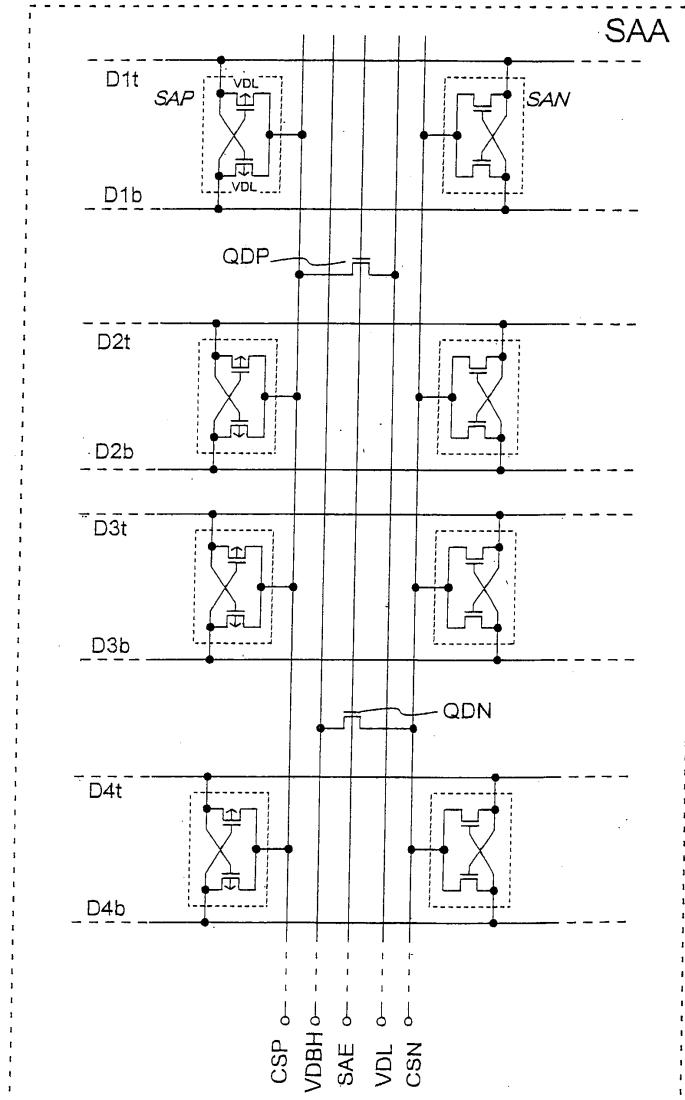

## 〈제2 실시예〉

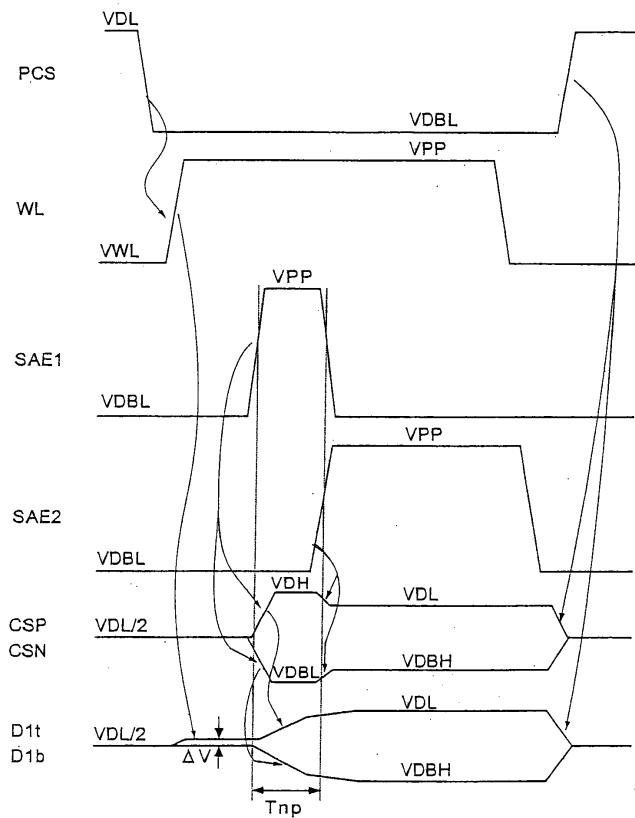

제2 실시예의 감지 증폭기의 구성을 도 3에 도시한다. 본 도면에는 감지 증폭기의 주요부를 나타내고 있으며, 다른 부분에 대해서는 제1 실시예의 기재가 그대로 계승된다. 본 실시예는 도 1의 P측만의 오버 드라이브 외에 N측의 오버 드라이브를 추가한 구조이다. 도 1과 다른 것은 크로스 영역 XA 내에 N측 공통 소스선 CSN의 일단에 집중형 스위치 QDN2를 추가하고, QDN2를 통해 데이터선의 로우측 복구 전위 VDBH(동상 VSS)를 인가하도록 한 점이다. 또한, 매쉬 형상 전원 배선으로서는 VDBH가 아닌, 그보다 낮은 전압 VDBL을 N측의 오버 드라이브용 전원으로서 공급하도록 하고, 분산 배치된 스위치 QDN1을 통해 N측 공통 소스선에 공급하도록 하였다. N측 공통 소스선을 VDBL에서 오버 드라이브하도록 한 것에 대응하여, 감지 증폭기의 NMOS 쌍 및 QDN1의 백 게이트는 적어도 VDBL 또는 그 이하의 전압에 바이어스하도록 한다. 이상에 의해 도 3에서는 하이측과 로우측의 복구 전위가 각각 VDL과 VDBH가 되고, 하이측과 로우측의 오버 드라이브 전위가 각각 VDH(>VDL)와 VDBL(<VDBH)이 된다.

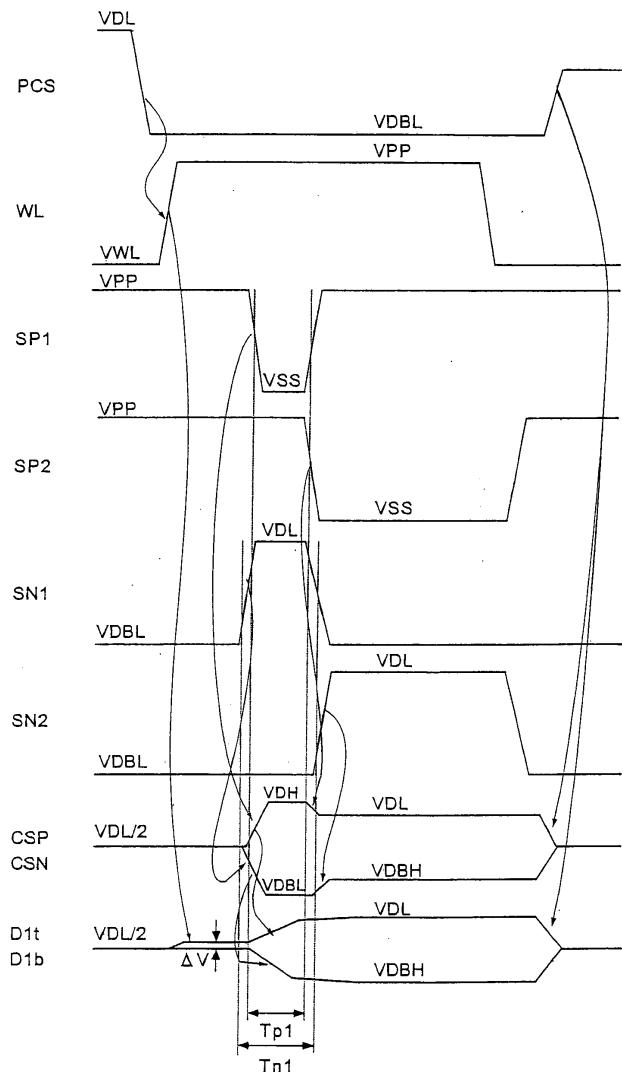

도 4에 도 3의 동작 과정을 나타낸다. 제1 실시예와 마찬가지로 메모리 셀 MC의 셀 캐페시터에 "H"의 데이터가 기입되어 있던 경우를 상정하고 있다. 제1 실시예의 도 2와의 차이는 N측의 오버 드라이브를 추가함으로써 발생된 SN1과 SN2의 제어에 있다.

셀 데이터가 완전하게 판독되고 D1t가 D1b보다 100mV 정도 높은 레벨이 된 후, SN1이 VDBL로부터 VDL 또는 VPP 레벨로 변화하여 QDN1을 활성화한다. 동시 또는 지연 단수 단만큼 지연되어 SP1이 VPP로부터 VSS로 변화하여 QDP1을 활성화한다. 이에 따라, CSN은 VDL/2로부터 VDBL로 천이하고, CSP는 VDL/2로부터 VDH로 천이한다. CSN, CSP이 VDBL, VDH로 천이하기 시작하면, 데이터선 쌍 D1t, D1b에 접속되어 있는 SA1은 활성화되고, 데이터선 사이의 미소 전압 차는 증폭된다. 이 때, SA1은 오버 드라이브 방식에 의해 데이터선 진폭 VDL보다 큰 진폭(VDH-VDBL)으로 활성화되기 때문에, SA1을 구성하는 NMOS 및 PMOS 트랜지스터의 소스·드레인간 전압 및 게이트·소스간 전압은 커지고 고속 동작이 가능해진다. 과대한 증폭 동작에 의한 충/방전 전력의 증가를 방지하기 위해서, QDN1은 데이터선 저레벨측의 VDBL로의 증폭이 완전하게 종료하지 않은 상태, 구체적으로는 VDBH보다 낮은 레벨이 되지 않은 상태까지의 시간 Tn1의 사이에서 활성화된다. 마찬가지로 QDP1은 데이터선 고레벨측의 VDH로의 증폭이 완전하게 종료하지 않은 상태에서 VDL을 넘지 않은 상태까지의 시간 Tp1의 사이만큼 활성화된다. 활성화되는 시간의 제어는 SP1, SN1에 의해 행해진다. 제1 실시예와 마찬가지로, SAn에서의 오버 드라이브 기간은 SA1과 같이 저레벨측이 Tn1로 설정되고, 고레벨측이 Tp1로 설정된다. 또한, 그 때의 오버 드라이브의 전압은 SAn에 가까운 QDN1 및 QDP1에 의해 공급되기 때문에, SA1과 같이 저레벨측이 VDBL로 설정되고, 고레벨측이 VDH로 설정된다.

오버 드라이브 동작 종료 후, SN2를 VDBL 내지 VDL 또는 VPP로 하여 CSN을 VDBH로 설정한다. SN2의 활성화 타이밍은 QDN1과 QDN2가 동시에 활성화되고, VDBL과 VDBH가 CSN을 통해 연결되지 않도록 제어된다. 그에 따라, 데이터선 저레벨측 D1b는 VDBH로 유지된다. 또한, SP2를 VPP 내지 VSS로 함으로써 CSP는 VDL로 설정된다. SP2의 활성화 타이밍은 QDP1과 QDP2가 동시에 활성화되고, VDH와 VDL이 CSP를 통해 연결되지 않도록 제어된다. 그에 따라, 데이터선 고레벨측 D1t는 VDL에 유지된다. 마지막으로 위드선을 하강 프리차지 상태로 복귀하는 동작은 도 2와 동일하다.

제2 실시예의 이점은 다음과 같다. (1) 제1 실시예와 마찬가지로, 데이터선 고레벨측의 오버 드라이브에 대하여, 모든 SA에 대하여 동등한 오버 드라이브 전압과 오버 드라이브 기간을 설정할 수 있으며, 감지 속도의 원근단 차를 작게 할 수 있다. (2) 또한, 본 실시예에서는 제1 실시예에 대하여 데이터선 저레벨측도 오버 드라이브함으로써, 동일한 데이터선 진폭을 이용한 경우에 감지 시간을 단축할 수 있다. 또한, 이 저레벨측 오버 드라이브의 부가에 의해 보다 낮은 데이터선 진폭, 즉 동작 전압의 저하에 대응할 수 있다. (3) 또한, 데이터선 저레벨측의 오버 드라이브에 대해서도 다수 배치한 QDN1과 어

레이 상 매쉬 전원 배선에 의해 감지 시의 감지 드라이버 및 CSN으로의 전류 집중을 피할 수 있어서 오버 드라이브 기간도 SA1 … SAn으로 공통의 신호 SN1로 설정된다. 이에 따라, 오버 드라이브 진폭과 기간의 원근단 차를 작게 할 수 있다. (4) 본 실시예에 있어서의 소자의 증가는 크로스 영역의 1개의 MOS의 증가이고, 감지 증폭기 영역의 면적 증가는 없다.

### 〈제3 실시예〉

다음으로, 제3 실시예의 구성을 도 5에 의해 설명한다. 본 실시예는 도 3의 변형예로서 도 1의 구성을 기본으로 하여 계승된다. 도 3과의 차이는 도 3에서는 크로스 영역 XA 내에 집중 배치하고 있던 복구용 스위치 QDP2와 QDN2를 감지 증폭기 영역 SAA에 분산 배치한 것이다. QDP2와 QDN2의 분산 배치 및 VDL, VDBL의 매쉬 형상 전원 배선은 도 1의 실시예와 마찬가지로 구성된다. 도 6에 이 도 5의 동작 파형을 나타낸다. 이 동작 파형은 도 4의 동작 파형과 동일하다.

제3 실시예의 이점은 다음과 같다. (1) 제2 실시예와 마찬가지로, 데이터선 고레벨, 저레벨의 양측을 오버 드라이브함으로써, 고속 감지를 실현할 수 있다. (2) 모든 SA에서 동등한 오버 드라이브 전압 및 오버 드라이브 기간을 설정할 수 있고, 원근단 차를 작게 할 수 있다. (3) 제2 실시예와 비교하여 복구 시에서 도 감지 증폭기 내에 다수 배치된 QDN2 및 QDP2에 의해 CSN 및 CSP로의 전류 집중을 피할 수 있다. (4) 감지 드라이버를 전부 감지 증폭기 내에 배치하고 있기 때문에, 감지 증폭기 이외의 레이아웃이 용이하게 되는 효과가 있다.

### 〈제4 실시예〉

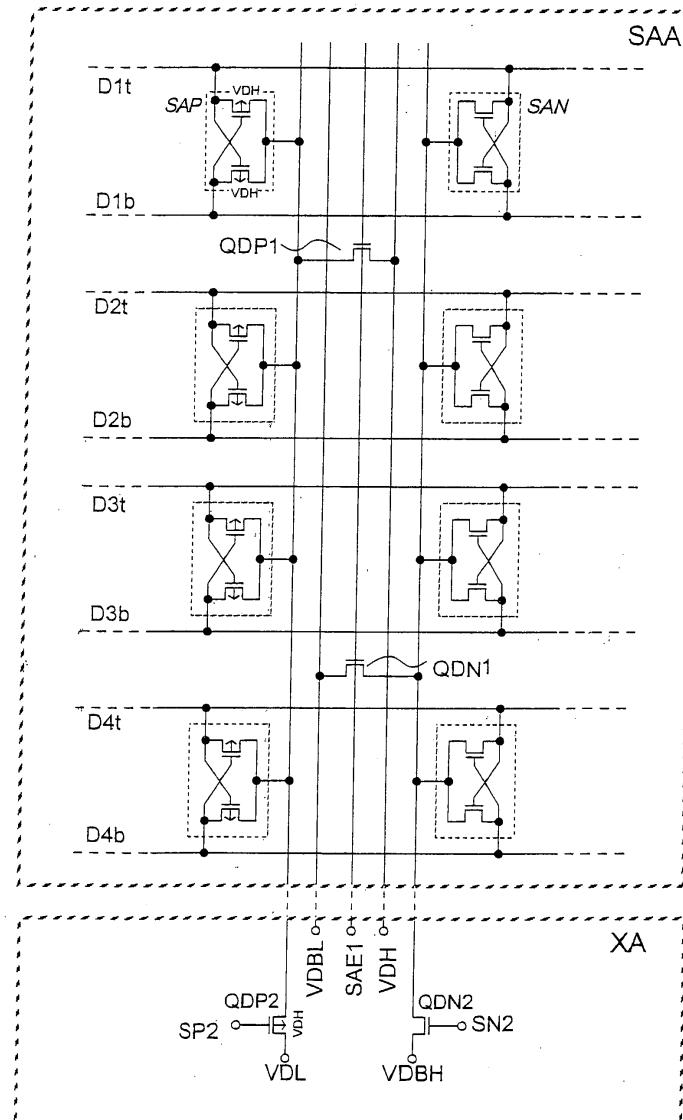

도 7에 제4 실시예를 나타낸다. 본 실시예도 공통 부분은 제1 실시예를 계승한다. 본 실시예는 P측과 N측의 오버 드라이브용 스위치 MOS를 전부 동일한 도전성 트랜지스터, 도면에서는 NMOS 트랜지스터로 구성하고, 이들 게이트 신호를 공통으로 하여 워드선 승압 레벨 VPP 등의 오버 드라이브 전압 VDH보다 충분히 큰 레벨의 신호로 구동하고 있는 것이 특징이다. P측의 스위치도 NMOS로 하였기 때문에 P측의 NMOS에 의한 전압 드롭을 방지하기 위함이다. 본 실시예는 도 3에 있어서의 분산 배치한 오버 드라이브용 스위치 MOS의 변형예의 하나로 볼 수도 있다. 본 실시예에서는 4개의 감지 증폭기당 1개의 P측 오버 드라이브용 스위치 MOS QDP1과, 1개의 N측 오버 드라이브용 스위치 MOS QDN1이 감지 증폭기 영역 SAA 내에 배치된다. QDN1과 QDP1의 게이트는 오버 드라이브 제어 신호선 SAE1에 공통으로 접속된다. 하이측과 로우측의 오버 드라이브 전위 VDH와 VDBL은 다른 실시예와 마찬가지로 매쉬 형상 전원 배선으로부터 공급된다. 복구 전위 VDL과 VDBH의 공급은 도 3의 회로와 마찬가지로, 크로스 영역 XA에 집중적 배치된 QDP2, QDN2에 의해 이루어진다.

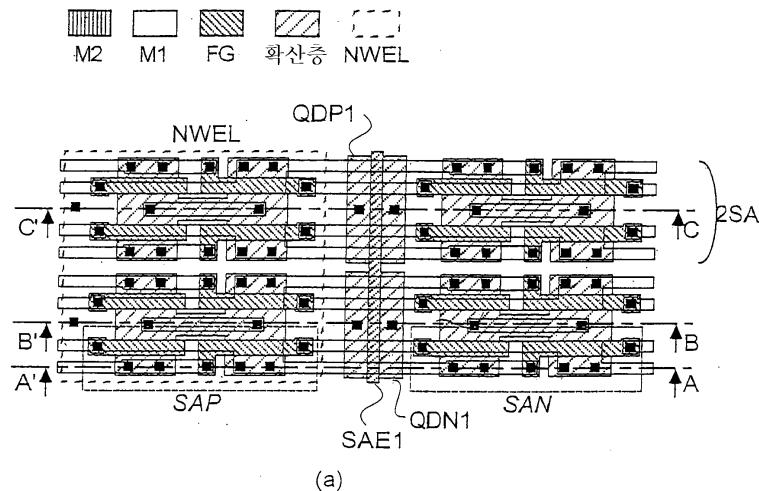

도 12의 (a), (b)에 본 구성을 실현하는 감지 증폭기의 평면 레이아웃을 나타낸다. 도 12의 (a)에는 4조의 데이터선 쌍에 대하여 나타내고, 간단히 제1 금속 배선층(메탈1 M1)과 트랜지스터 게이트 및 게이트 배선(FG), 확산층, NWEL만 나타낸다. SAN은 SA의 NMOS 트랜지스터 부분을 나타내고, SAP는 PMOS 트랜지스터 부분을 나타낸다. QDN1, QDP1은 SAN과 SAP 사이에 게이트를 일렬로 배치한 NMOS로 구성된다. 일렬로 배치된 NMOS를 교대로 QDN1과 QDP1로 할당하고 있는 것이 특징이다. 이 배치에 의해 제어 전극 SAE1이 1개로 공통화되어 레이아웃 면적이 저감된다. 도 12의 (a)의 레이아웃에서는 QDN1과 QDP1의 수는 SAN과 SAP 사이에 4조의 데이터선 쌍에 각각 하나씩 배치하고 있지만 이에 한정되는 것은 아니다. 예를 들면, 8조(또는 16조)의 데이터선에 하나씩 배치하도록 하여도 좋다. 또한, QDN1, QDP1의 감지 증폭기 내에서의 위치는 SAN, SAP 사이가 P측과 N측 양방의 공통 소스와의 접속 측면에서 가장 합리적이지만, 이에 제한되는 것은 아니다.

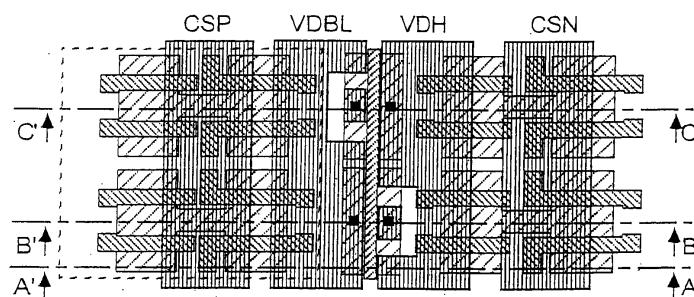

도 12의 (b)는 도 12의 (a)와 동일한 부분에 대하여 M1을 생략하고, M1 보다 상층인 제2 금속 배선층(메탈2 M2)을 추가한 감지 증폭기의 평면 레이아웃이다. M2에는 P측 공통 소스선 CSP, VDBL 공급 전원선 VDBL, VDH 공급 전원선 VDH 및 N측 공통 소스선 CSN이 순서대로 배치된다. 이들 4개의 배선은 모두 감지 증폭기가 열을 이루는 방향(워드선의 연장 방향과 동일함)으로 연장한다. 이 4개의 배선을 배열하는 순서는 본 실시예의 감지 증폭기의 레이아웃 면적을 작게 하기 위한 특징적인 구성이다. 이 모습은 도 7의 회로도와 일치하고 있으며, 이 의미로 도 7의 회로도는 구체적인 레이아웃을 간략히 나타낸 것이다. 또한, 후술하는 도 9 등도 마찬가지로 회로도에 구체적 레이아웃의 핵심이 나타나 있다.

도 12의 (a)에 도시한 QDP1과 QDN1의 채널 폭에 대한 바람직한 구성의 하나는 각각의 채널 폭을 동등하게 하는(동일한 사이즈의 NMOS로 한다) 것이다. 이에 따라, 감지 증폭기의 SAN이 SAP보다 먼저 온하도록 된다. 프로세스 변동에 의한 Vt 변동이 PMOS에 비하여 작은 NMOS 트랜지스터로 구성된 SAN으로 미소 전압 차를 차동 증폭을 개시할 수 있기 때문에, 정밀도가 좋은 차동 증폭을 할 수 있다. QDP1과 QDN1은 모두 NMOS이고, 동일한 P형 웰 내(본 실시예에서는 P형 기판)에 직접 형성되고, 그 P형 웰은 최저 전위(예를 들면, 본 예에서는 VDBL)가 인가된다. 이 때문에, 큰 전위를 인가하는 QDP1이 상대적으로 큰 기판 바이어스가 인가되어 QDP1이 QDN1보다 임계 전압이 커진다. 이 때문에, 임계 전압이 작은 QDN1이 온하기 쉽게 되어, SAN을 최초로 구동시킬 수 있다.

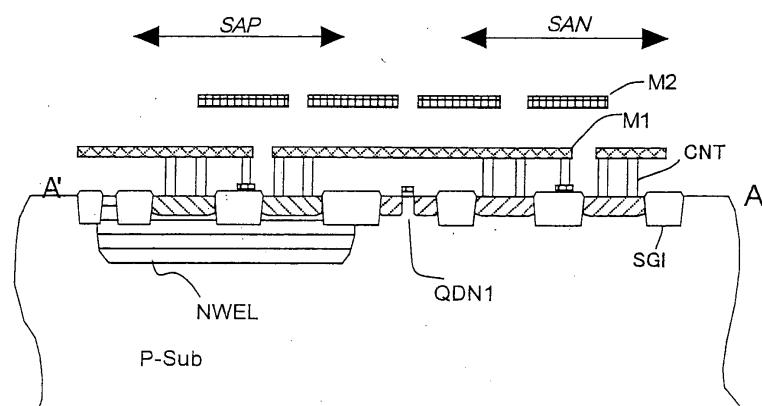

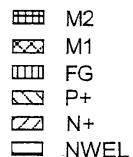

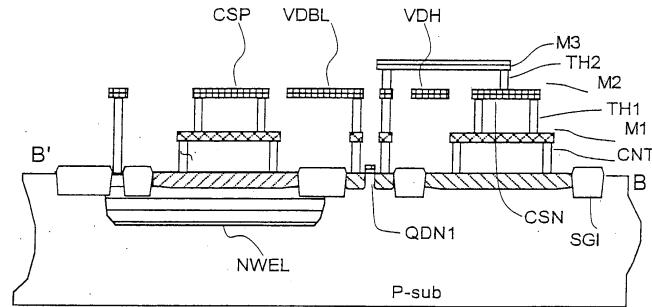

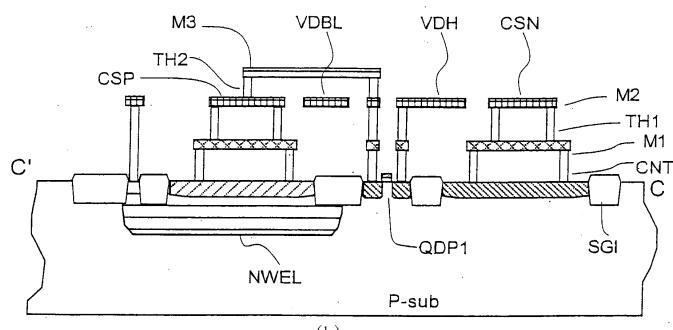

도 13에, 도 12의 (a), (b) 상의 A-A' 사이의 단면도를 나타낸다. 또한, 도 14의 (a), (b)에 B-B' 사이 및 C-C' 사이의 단면도를 각각 나타낸다. 이들 단면도중에서 SGI(Shallow Groove Isolation)는 확산층(도면 중 N<sup>+</sup>, P<sup>+</sup>)을 분리하기 위한 절연부로, 기판에 형성된 얇은 홈을 Si 산화물 등으로 매립한 것이다. 또한, CNT는 메탈1(도면 중 M1)과 확산층 또는 FG와 연결하기 위한 컨택트홀이다. TH1, TH2는 각각 M1-메탈2(도면 중 M2) 사이, M2-메탈3(도면 중 M3) 사이를 연결하는 컨택트홀이다. 도 14의 (a)에 도시한 바와 같이 CSN과 QDN1의 드레인 사이는 M3을 이용하여 결선된다. 이 도면에서 알 수 있는 바와 같이 CSN과 QDN1의 드레인 사이는 단순히 전기적인 결선으로서는 M1이라도 접속할 여유는 있다. M3으로 접속한 이유는 SAN을 구성하는 두 개의 NMOS의 소스와 QDN1의 드레인 사이의 저항이 동등하게 되도록 배려하였기 때문이다. SAN을 구성하는 두 개의 NMOS의 소스 전위가 동등하게 되도록 확산층 P<sup>+</sup>도 접속하도록 하고 있다. 이에 따라 SAN을 구성하는 두 개의 NMOS의 언밸런스가 발생하지 않도록 레이아웃 상의 고안이 되어 있다. CSN과 CSP는 각각 SAN과 SAP 상의 M2에 배선되어 있다. 두 개의 NMOS의 소스와 마찬가지로, 도 14의 (b)에 도시한 바와 같이 CSP와 QDP1의 소스(QDP1이 NMOS 때문에 소스가 됨) 사이는 M3을 이용하여 결선되어 있다. SAP를 구성하는 두 개의 PMOS의 소스와 QDP1의 소스 사이도 상술한 바와 같은 동일한 연구가 되어 있다.

제4 실시예의 동작을 도 8의 과정도를 이용하여 설명한다. 데이터선 프리차지 종료로부터 데이터선에 미소 전압 차를 판독할 때까지는 상술한 실시예와 동일하다. 셀에 저장되어 있는 정보가 데이터선에 판독된 후, SAE1을 VDBL로부터 VPP로 한다. QDN1, QDP1이 활성화되어 CSN은 VDL/2로부터 VDBL로 천이하기 시작하고, CSP는 VDL/2로부터 VDH로 천이하기 시작한다. 이 때, QDP1과 QDN1을 동일한 물리 상수의 NMOS 트랜지스터로 구성한 경우라도 QDP1의 임계치 전압 Vt는 QDN1의 Vt보다 기판 바이어스 효과에 의해 높아지고 있다. 이 때문에, 동일한 전압이 게이트 신호로서 인가되더라도 QDP1보다 QDN1이 먼저 구동된다. QDN1 및 QDP1은 과도하게 데이터선의 증폭 진폭이 크게 됨으로 인한 소비 전류의 증가를 방지하기 위해서, 데이터선의 저레벨측이 VDBH 이하가 되지만, 데이터선의 고레벨측이 VDL을 넘지 않은 Tnp동안만 SAE1에 의해 활성화된다. SAn에서의 오버 드라이브 기간은 게이트 신호 SAE1로 결정되기 때문에 SA1과 동등하게 되어 Tnp가 된다. 그 후, SAE1은 VPP 내지 VDBL이 되어, 오버 드라이브 동작이 종료한다. SAE1가 VDBL이 됨과 동시에 SN2를 VDBL 내지 VDL 또는 VPP로 하여 QDN2를 활성화한다. 그에 따라, CSN을 VDBH로 하여 데이터선 저레벨측인 D1b를 VDBH로 복구한다. 마찬가지로 SAE1이 VDBL이 된 후, SP2를 VPP 내지 VSS로 하여 QDP2를 활성화한다. 그에 따라 CSP를 VDL로 하여, 데이터선 고레벨측인 D1t를 VDL에 복구한다. 마지막으로, 워드선을 하강 프리차지 상태로 하는 동작은 도 1 등과 동일하다.

본 실시예의 이점은 다음과 같다. (1) 레이아웃 상에서 QDP1을 NMOS 트랜지스터로 구성함으로써, QDN1과 QDP1을 감지 증폭기 내에서 일렬로 배치하고, 그 게이트 제어 신호를 QDN1과 공통으로 할 수 있고, 제1 실시예~제3 실시예와 같이 NMOS, PMOS를 배치하는 경우에 비하여 NMOS, PMOS를 2열로 배치한 경우보다 레이아웃을 소면적화할 수 있다. (2) 또한, CSN, CSP 양방을 오버 드라이브하고 있는 도 3의 실시예와 비교하여 오버 드라이브용 제어 신호를 1개로 줄일 수 있어서 제어 신호용 회로를 줄일 수 있다. (3) QDP1과 QDN1을 모두 NMOS로서 동일한 전압으로 백 게이트와 바이어스 하도록 함으로써, 감지 개시 시의 SAE1이 입력되었을 때, QDP1보다 QDN1이 먼저 구동하기 때문에, 프로세스 변동에 의한 Vt 변동이 PMOS에 비하여 작은 NMOS 트랜지스터로 미소 전압 차를 차동 증폭을 개시할 수 있어서 정밀도가 좋은 차동 증폭을 할 수 있다. (4) QDP1을 NMOS 트랜지스터로 구성함으로써, SAE1이 VDBL일 때는 QDP1의 게이트 소스간 전압이 마이너스 전압이 되기 때문에, QDP1 비활성 상태에서의 VDH 내지 VDL/2로의 누설 전류를 억제할 수 있다. (5) 제1 실시예 내지 제3 실시예와 마찬가지로, 모든 SA와 동일한 오버 드라이브 전압과 오버 드라이브 기간을 설정할 수 있고, 오버 드라이브의 원근단 차를 작게 할 수 있다.

또한, 본 실시예는 P측 및 N측의 양방을 오버 드라이브하는 구성을 채택하였지만, 전원 전압과의 관계로, 오버 드라이브가 한쪽으로 충분한 경우에는 도 8에 있어서, VDBL의 전원 배선을 로우 레벨의 복구 전위인 VDBH로 하면 좋다. 이에 따라, VDBL을 공급하는 대용량 마이너스 전원 발생 회로를 준비할 필요가 없게 되고, 칩 면적을 소형화할 수 있는 이점이 있다. 그에 따라, 감지 증폭기용 전원선의 종류를 줄이게 하기 때문에, 매쉬 전원 배선이 용이하게 되는 이점이 있다.

또한, DRAM의 CMOS 감지 증폭기에 하이 레벨과 로우 레벨의 복구 전압을 공급하기 위해서, 양자 모두 NMOS를 이용하는 구성 자체는 [문헌 5]에 기재되어 있다. 그러나, [문헌 5]는 워드선의 구동 전압을 전원 전압 VCC로 하는 전제를 기본으로 하여, P측의 스위치 NMOS의 임계치 전압 Vt 드롭을 의도적으로 일으키게 하고, 데이터선의 하이 레벨의 복구 전위를 VCC-Vt로 저하시키기 위한 구성이고, 본원과는 목적이 다르다. [문헌 5]에서는 원래 스위치 MOS의 분산 배치 등에 대해서는 기재가 없다. 또한, 오버 드라이브에 대한 기재도 없다.

〈제5 실시예〉

도 9에 제5 실시예의 회로를 나타낸다. 본 실시예는 도 7에 있어서의 복구용 스위치 MOS를 NMOS로 함과 동시에 감지 증폭기 영역 SAA에 분산 배치하여, 도 7과 마찬가지로 제어 신호를 공유화한 점이 특징이다. P측 및 N측의 오버 드라이브용 스위치 NMOS QDP1 및 QDN1은 도 7과 동일한 구성이 된다. 이에 대하여, 복구용 스위치 QDP2 및 QDN2도 감지 증폭기 영역 내에 배치된다. QDP2 및 QDN2의 게이트는 공통의 제어선 SAE2에 의해 제어된다. 또한, 하이 및 로우의 복구 전위 VDL, VDBH도 도 24에서 상술한 매쉬 형상 전원 배선에 의해 공급한다. QDP2 및 QDN2는 4개의 감지 증폭기당 각각 1개씩 배치하고 있다. 이상의 QDN1과 QDP1 및 QDN2와 QDP2는 게이트를 2열 갖는 NMOS 트랜지스터로 SAN 열과 SAP 열에 평행하게 1열 배치함으로써 구성된다.

감지 증폭기의 수와 오버 드라이브용 스위치 MOS나 복구용 스위치 MOS 수의 대응 관계는 본 실시예에 한정되는 것은 아니다. 예를 들면, 8개의 감지 증폭기당 QDP1, QDP2, QDN1, QDN2를 1개씩 대응시키는 변형을 하여도 좋다. 또한, 공통 소스선의 충전은 오버 드라이브용 스위치에 의해 주로 행해지기 때문에, 복구용 스위치는 상대적으로는 구동 능력이 작더라도 좋다. 그래서, 오버 드라이브용 스위치 QDP1, QDN1의 수를 QDP2, QDN2의 수보다 많게 하는 구성도 합리적이다. 이를 보다 일반적으로 바꿔 말하면, SAA 내에서 모든 오버 드라이브용 스위치 MOS의 컨덕턴스를 모든 복구용 스위치 MOS의 컨덕턴스보다 크게 하는 구성으로 하면 좋은 것이 된다.

본 실시예의 동작에 대하여 도 10의 파형도를 이용하여 설명한다. 프리차지를 종료하여 SAE1을 VPP에 구동하여 오버 드라이브 개시하기까지는 도 8과 동일하다. QDN1 및 QDP1은 과도 감지에 의한 소비 전류의 증가를 방지하기 위해서, 데이터선의 저레벨측이 VDBH 이하가 되든지, 데이터선 고레벨측이 VDL을 넘지 않은 Tnp 동안만 SAE1에 의해 활성화된다. SAn에서의 오버 드라이브 기간은 게이트 신호 SAE1로 결정되기 때문에 SA1과 동등하게 되어 Tnp가 된다. 그 후, SAE2가 VDBL로부터 VPP가 되고, CSN은 VDBH가 되고, 데이터선 저레벨측인 D1b는 VDBH에 복구된다. 동시에 CSP는 VDL이 되고, 데이터선 고레벨측인 D1t는 VDL에 복구된다. SAE2는 동시에 QDN1과 QDN2 및 QDP1과 QDP2가 활성화되고, 2 전원 VDBL과 VDBH 및 VDH와 VDL이 CSN, CSP를 통해 단락되지 않도록 제어된다.

본 실시예의 이점은 다음과 같다. (1) 감지 증폭기의 레이아웃에서는 감지 드라이버가 NMOS로 구성된 2열 배치가되어 제4 실시예보다 레이아웃 면적이 증대하지만, 감지 증폭기 이외에 감지 드라이버를 배치할 필요없이 감지 증폭기 이외의 레이아웃이 용이하게 된다. (2) 데이터선의 고레벨 및 저레벨의 양방을 오버 드라이브하고 있는 제2 실시예와 비교하여 감지 증폭기의 제어 신호 수를 2개 줄일 수 있어서 제어 신호용 회로를 적게 할 수 있다. (3) 제1 실시예 내지 제4 실시예와 마찬가지로 모든 SA에서 동등한 오버 드라이브 전압과 오버 드라이브 기간을 설정할 수 있고, 원근단 차를 작게 할 수 있다. (4) QDP1 및 QDP2가 NMOS 트랜지스터로 구성되어 있기 때문에, 스텐바이 상태에서는 QDP1 및 QDP2의 게이트·소스간 전압 VGS가 VGS<0V가 되기 때문에 VDH 및 VDL로부터 VDL/2로의 누설 전류가 억제된다.

또한, 감지 속도 개선 효과는 감소하지만, VDBL=VDBH로 하면, 대용량의 마이너스 전원 회로가 불필요해져서 칩 면적을 작게 할 수 있는 효과가 있다. 또한, 그 경우에는 감지 증폭기용 전원선의 종류가 3종류가 되기 때문에 메모리 어레이 상의 전원선의 배선이 용이하게 되는 이점이 있다.

또한, 본 발명은 오버 드라이브 방식을 이용하고 있지 않는 감지 증폭기 구성에 대해서도 적용할 수 있다. 그 경우의 감지 증폭기의 구성 예를 도 11에 도시한다. 오버 드라이브를 이용하고 있지 않기 때문에, 감지 증폭기의 PMOS 쌍 SAP의 기관 전위는 VDL로 설정하고 있다. 또한, 감지 증폭기 이외의 장소에 감지 드라이버가 불필요하고, 그 영역의 레이아웃이 용이하게 되는 이점이 있다.

또한, 도 7~도 11은 감지 드라이버를 전부 NMOS 트랜지스터로 구성하고 있지만, PMOS 트랜지스터로 구성할 수도 있다.

이상의 실시예에 있어서, 감지 드라이버 및 SA 트랜지스터의 Vt에 대해서는 저 Vt라도 고 Vt라도 상관없다. 단, 저 Vt 트랜지스터를 이용한 경우, 고 Vt 트랜지스터를 이용하는 것보다 고속으로 감지 증폭기를 동작시킬 수 있다. 고 Vt 트랜지스터를 이용한 경우, SA의 데이터 보유 상태에서의 누설 전류를 저감시킬 수 있고, 소비 전력을 억제할 수 있다. 단지, 저 Vt 트랜지스터를 이용한 경우에는 후술하는 발명을 이용함으로써 누설 전류를 저감시킬 수 있다. 또한, 감지 드라이버에 고 Vt 트랜지스터를 이용함으로써, 스텐바이 상태에서의 감지 증폭기 전원과 VDL/2의 사이의 누설 전류를 저감시킬 수 있다.

제1 실시예 내지 제5 실시예에 있어서 이용되고 있는 전압 관계는 다음과 같이 하는 것이 바람직하다. 워드선 WL의 진폭 VWL 내지 VPP와 데이터선 진폭 VDBH 내지 VDL 및 초기 감지용 전원 VDBL, VDH 및 기관 전위 VBB의 대소 관계는

VBB=VDBL(-0.75V) < VWL=VDBH=VSS(0V) < VDL(1.5V) < VDH(2.5V) < VPP(3V)로 하면 내부 전원 수를 줄일 수 있다. 또한, 마이너스 전원의 수가 증가하지만, VBB < VDBL(-0.5V)로 하면 메모리 셀의 기판 바이어스의 변동을 억제할 수 있는 효과가 있다. 또한, VDH=VPP(3V)로 함으로써 보다 큰 전원으로 감지 증폭기를 활성화할 수 있다.

또한, 전원 전압의 설정은 [문헌 6]에 기재한 바와 같은 워드선 스탠바이 레벨이 마이너스 전압인 네가티브 워드 방식을 생각할 수 있다. 네가티브 워드선 방식을 상기한 본원 실시예에 적용하기 위해서는 VBB=VDBL=VWL(-0.75V) < VDBH=VSS(0V) < VDL(1.5V) < VDH=VPP(2.25V)로 한다. 이 방식을 채택하면 내부 전원 레벨 수가 적어지는 효과가 있다. 또한, 전원 레벨 수는 증가하지만 VBB < VDBL < VWL 또는 VBB < VWL < VDBL, VBB < VDBL = VWL과 VBB와 다른 전원을 달리 함으로써 메모리 셀 어레이의 기판 바이어스인 VBB의 변동을 낮추면 셀의 데이터 보유 특성이 좋아지는 효과를 얻을 수 있다.

이상의 설명에 있어서 VDH에는 외부 전원 VCC를 이용하는 것이 바람직하지만, 송압 회로에 의한 송압 레벨이나, 강압 회로에 의한 강압 레벨을 이용하여도 좋다.

#### 〈제6 실시예〉

이상의 실시예에서는 오버 드라이브 방식에 대하여 검토하였지만, 전원 전압을 낮춘 경우에는 감지 증폭기의 임계치 전압  $V_t$ 를 저감하는 구성과의 병용 필요성이 발생되는 것을 생각할 수 있다. 저임계치 전압의 MOS를 이용한 감지 증폭기를 오버 드라이브함으로써, 동작 가능한 데이터선의 진폭을 더욱 저감하여 저소비 전력화를 도모할 수 있는 가능성이 있기 때문이다. 그러나, 저임계치 MOS는 서브 임계 전류를 증가시켜서 대기 시의 소비 전류를 증가시키기 때문에, SDRAM에 보이는 액티브 스탠바이 상태와의 정합성이 우려된다. 그래서, 본 실시예에서는 저임계치의 MOS를 이용한 감지 증폭기가 데이터를 래치한 상태에서의 서브 임계 전류의 저감법을 나타낸다.

도 20은 데이터선으로부터의 신호를 증폭하여 감지 증폭기에 래치했을 때의 감지 증폭기의 서브 임계 전류를 나타낸 것이다. SDRAM에서는 로우 액티브 커맨드에 의해 특정한 1워드분의 메모리 셀 데이터를 감지 증폭기로 증폭하여 래치한 상태로 유지하는 액티브 스탠바이라 불리는 동작 상태를 갖는다. 미리 감지 증폭기에 데이터를 보유하고 있어서, 거기에 고속 액세스하기 위함이다. 이 때, 도 20에 도시한 바와 같이 감지 증폭기의 데이터 보유 상태에서는 1개의 감지 증폭기당  $i$ 의 서브 임계 전류가 흐른다. VDL과 VDBH 사이에 직렬 접속된 감지 증폭기의 CMOS는 PMOS나 NMOS 한쪽은 게이트-소스 사이가 0V가 되어 오프 상태가 되지만, 임계치 전압이 낮으면 완전히 오프 되지 않고 고려해야 할 서브 임계 전류가 흐른다. 이 때문에, 도 21의 과정도에 도시한 바와 같이 결국, 전원 VDL 내지 VDBH로는  $ni$ 의 누설 전류가 된다. 예를 들면,  $V_t$ 가 0.1V의 트랜지스터를 이용하여 64k개의 감지 증폭기가 액티브 스탠바이 상태가 된 경우에는 약 3mA의 서브 임계 전류가 흘러 저전력화의 방해가 된다. 또한, 트랜지스터의  $V_t$ 를 0.1V 낮추면 이 전류는 약 10배가 된다. 따라서,  $V_t$ 의 제조 변동이 있는 경우나,  $V_t$ 가 저하하는 고온에는 저  $V_t$  MOS의 서브 임계 전류는 큰 문제가 된다.

도 15에 오버 드라이브 방식의 SA 구성에 본원의 액티브 스탠바이 시의 서브 임계 전류 저감 방식을 적용한 회로를 나타낸다. 공통의 회로 구성은 지금까지 진술한 실시예의 회로를 답습하고 있으며, 특히 도 3에 도시한 회로와 대비하면 이해하기 쉽다.

최초로, 본 발명의 감지 증폭기의 누설 전류를 저감하는 원리를 설명한다. 감지 증폭기 SA가 셀의 데이터를 증폭한 후에서는 CSN은 VDBH로, CSP는 VDL로 되어 있다. 이 때의 SA에 포함되는 MOS 기판 바이어스는 설계되어 있는 값, 예를 들면 NMOS 트랜지스터에서는 VBB이다. 여기서, CSN 레벨이 VDBH 내지 VDBH'(>VDBH)가 되면, 기판 바이어스는 (VDBH'-VDBH)분 상승하고, 기판 바이어스 효과에 의해 NMOS 트랜지스터의  $V_t$ 가 상승한다. 즉, NMOS 게이트와 소스가 단락되어 있는 상태에서 백 게이트에 인가하는 전압(기판 전압)을 일정하게 하여, 소스 전위(=게이트 전위)를 높은 전압으로 한다. 이에 따라, 백 게이트와 소스 사이의 전압이 커지고, 상대적으로 백 게이트에 깊은 바이어스가 걸리기 때문에 NMOS의 임계치가 상승하는 것을 이용하고 있다. 마찬가지로, CSP 레벨이 VDL로부터 VDL'(<VDL)가 됨으로써 PMOS 트랜지스터의  $V_t$ 가 상승한다. CSN 및 CSP 레벨을 변화에 의해  $V_t$ 가 상승함으로써, SA 누설 전류를 결정하고 있는 서브 임계 누설 전류를 저감시킬 수 있고, 그 결과 VDL로부터 VDBH로의 누설 전류를 저감시킬 수 있다. 이상의 효과를 얻기 위한 본 발명의 실시예에서는 공통 소스 CSN, CSP의 레벨을 스탠바이시, 액티브시, 액티브 스탠바이시로 바꾸기 위한 수단을 포함하는 것을 특징으로 한다.

도 15에 있어서의 도 3과의 차이는, P측 및 N측의 복구용 스위치를 각각  $Z_p$ 과  $Z_n$ 으로 치환한 것이다.  $Z_p$  및  $Z_n$ 은 P측 및 N측에서의 복구 전위를 공급함과 함께 그 복구 전위를 제어 신호에 따라 변경하기 위한 수단이다.  $Z_n$ 의 동작을 예로서 그

역 할을 설명한다. 감지 증폭기의 증폭 초기는 QDN1에 의해 CSN을 VDBL에서 오버 드라이브하고, 오버 드라이브의 정지 후에 Zn은 SN의 제어 신호에 따라 CSN에 복구 전위 VDBH를 공급한다. 소정 시간 경과 후, 액티브 스텐바이 상태가 되면, SN3의 제어 신호에 따라 Zn은 CSN을 VDBH'(>VDBH)로 구동한다.

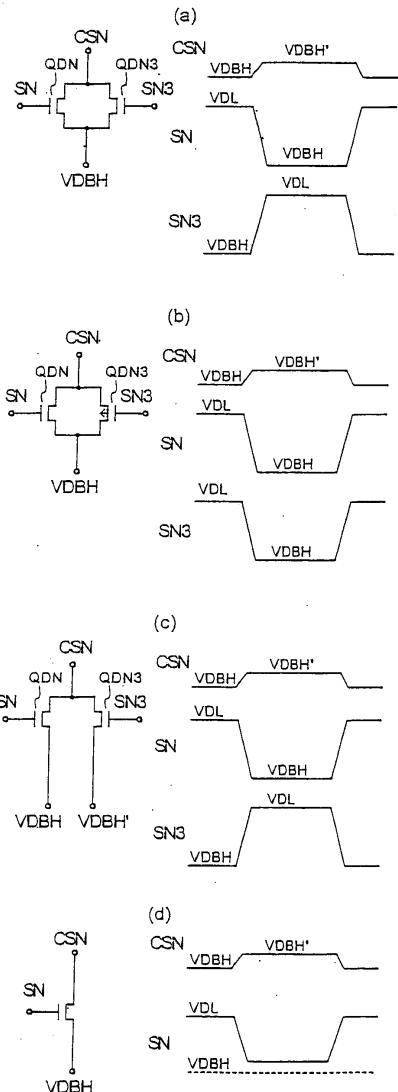

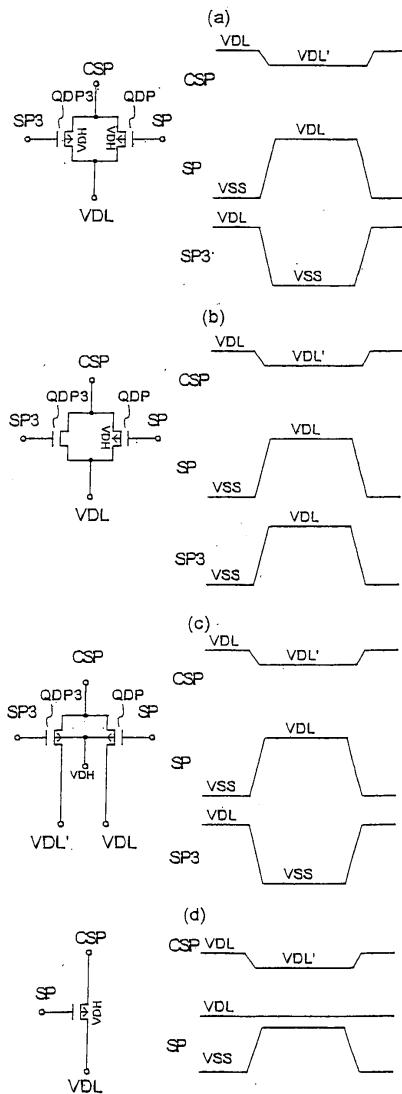

다음으로, 도 16의 (a)~(d)에 도 15 중의 Zn의 구성 예를 나타낸다. 도 16의 (a)에 도시한 구성에서는 CSN과 VDBH 사이에 QDN과 병렬로 고  $V_t$ 의 NMOS QDN3을 부가하고 있다. QDN3은 게이트 길이와 폭의 비 W/L로 QDN에 비하여 1/500 이하인 저 구동력 트랜지스터로 구성되고, 활성화되었을 때 VDBH'(>VDBH)를 CSN에 공급한다. 즉, SN3은 도통하여도 임피던스가 높아 감지 증폭기의 누설 전류가 흐르면 전압 강하가 생기기 때문에, CSN을 VDBH'로 상승시켜서 마이너스 귀환 효과로 누설을 저감한다. QDN3의 기판 전위는 QDN과 동등하게 설정된다. QDN3이 활성화되는 것은 감지 증폭기 활성화 상태에서 적어도 QDN이 비활성 상태 시에 활성화되고, 초기 감지 시에 QDN과 동시에 활성화되더라도 좋다. QDN3을 활성화할 때에는 SN3을 VDBH 내지 VDL로 설정한다.

도 16의 (b)에서는 CSN과 VDBH 사이에 QDN과 병렬로 저  $V_t$ 의 PMOS QDN3을 부가한 구성으로, 게이트 신호 SN3에 의해 활성화된 경우, CSN에는 VDBH보다 QDN3의  $V_t$ 분 높은 전원을 공급한다. QDN3의 기판 전위는 VDL 또는 SA의 PMOS와 동등한 전위로 설정한다. QDN3이 활성화되는 것은 감지 증폭기 활성화 상태에서 적어도 QDN이 비활성 상태 시에 활성화된다. QDN3을 활성화할 때에는 SN3을 VDL 내지 VDBH로 설정한다.

도 16의 (c)에서는 Zn의 구성으로서, VDBH'를 전원으로 하는 고  $V_t$ 의 NMOS QDN3을 CSN에 접속시키고 있다. 따라서, 이 회로에서는 VDBH'(>VDBH)를 형성하는 전원 회로가되어 있는 것이 전제가 된다. VDBH'는 저항 분할 회로나 전압 리미터 회로 등에 의해 형성된다. QDN3의 기판 전위는 QDN의 기판 전위와 동등한 전위로 설정된다. QDN3은 SN3에 의해 활성화되어 CSN에 VDBH'를 공급한다. QDN3이 활성화되는 것은 감지 증폭기 활성화 상태에서 QDN이 비활성 상태 시에 활성화된다. QDN3을 활성화할 때에는 SN3을 VDL 내지 VDBH로 설정한다.

도 16의 (d)에서는 QDN의 게이트 전압의 크기를 SN에 의해 제어하여 Zn의 효과를 QDN에서 실현하는 구성이다. 액티브 스텐바이에 있어서 QDN의 온 저항이 높아져서, CSN의 레벨이 VDBH'가 되도록 게이트 신호 SN3을 제어한다. 본 구성에서는 추가 트랜지스터가 없기 때문에, 다른 실시예에 비하여 SN의 제어가 복잡하게 되지만 감지 증폭기 주변의 레이아웃을 용이하게 할 수 있다.

도 17의 (a) 내지 도 17의 (d)에  $Z_p$ 의 구성 예에 대하여 나타낸다. 이들은 도 16의 (a) 내지 도 16의 (d)에서 진술한 회로를 P측의 하이 레벨용으로 개변한 것이며, 도 16의 회로와 마찬가지로 하여 이해된다.

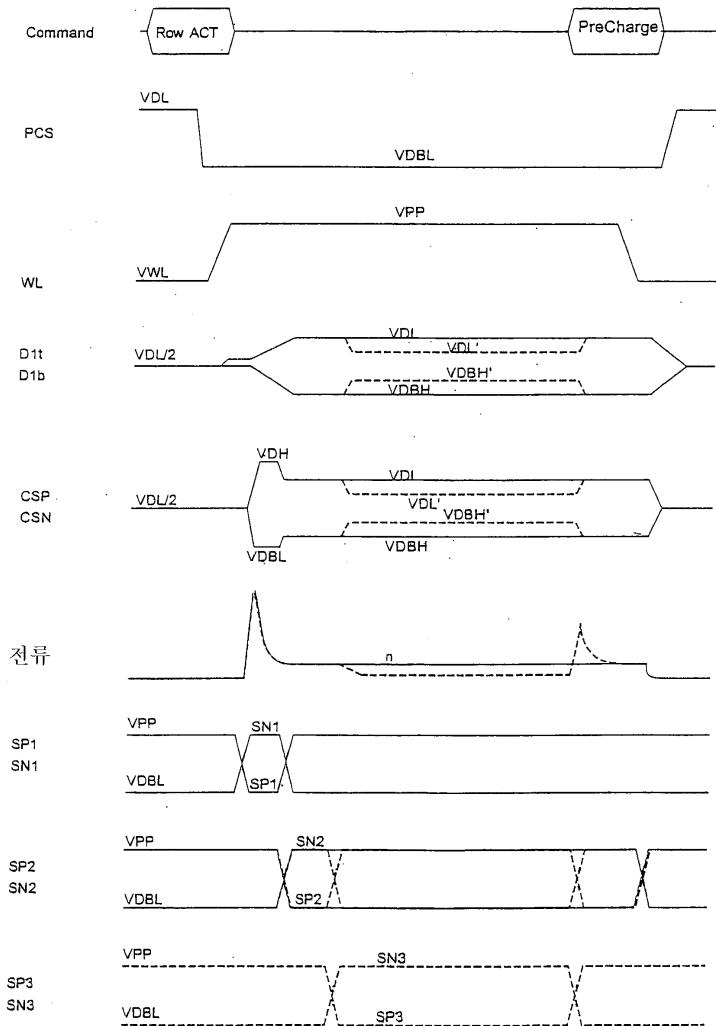

도 18에, 도 15의 구성의 Zn 및  $Z_p$ 에 도 16의 (c) 및 도 17의 (c)를 적용한 경우의 동작 과정도를 나타낸다. 로우 액티브 커맨드(RowACT)가 입력된 후, PCS가 VDL로부터 VDBH로 천이하고, 프리차지 동작이 정지된다. 프리차지 종료 후부터 감지 증폭기가 데이터를 보유하기까지의 동작 순서는 상술한 제2 실시예와 동일하므로 생략한다. SA가 오버 드라이브 동작 및 복구 동작에 의해 증폭 동작을 끝내고 데이터를 확정하고 있는 상태에서 상술한 바와 같이 VDL과 VDBH 사이의 누설 전류가 흐르고, 1개의 SA당 누설 전류를  $i$ 로 하면, 서브 메모리 어레이에 있어서 공통 소스선에  $n$ 개의 SA가 접속되어 있던 경우, VDL 내지 VDBH로의 누설 전류의 총합은  $ni$ 가 된다.

누설 전류를 저감하기 위해서 로우 액티브 신호가 입력되어 일정 시간 경과 후, 감지 증폭기가 셀의 판독 신호를 충분히 증폭한 후, SN 및 SP은 비활성화되고, 대신 SN3 및 SP3이 활성화된다. 그 결과, CSN은 VDBH로부터 VDBH'가 되어 CSP는 VDL로부터 VDL'로 설정된다. 이 때, SA를 구성하는 NMOS의 기판 전위는 상대적으로(VDBH'-VDBH)분 높아지고, 마찬가지로 PMOS의 기판 전위는 상대적으로(VDL-VDL')분 높아지며, 모두 기판 바이어스 효과에 의해 고  $V_t$ 화하고, 서브 임계 누설 전류를 저감시킬 수 있다.

액티브 스텐바이의 데이터선 쌍 사이의 진폭(VDL'-VDBH')의 설계 치의 최소치는 감지 증폭기 감도에 의해 설정된다. 데이터선 진폭 1.4V를 가정한 경우에는 데이터선 쌍의 진폭(VDL' -VDBH')을 600mV 정도로 설정하면 리드 커맨드가 들어가는 경우에 있어서도 데이터 파괴가 발생되지 않고, 액티브 스템바이에서의 누설 전류를 저감시킬 수 있다.

액티브 스템바이 상태를 종료하기 위해 프리차지 커맨드(PreCharge)가 입력된 후의 동작에 대하여 설명한다. 프리차지 커맨드에 의해 SN3 및 SP3을 비활성화하고 SN 및 SP를 활성화한다. 그에 따라, 데이터선 쌍은 VDBH 또는 VDL에 차기 입된다. 그 후, 워드선이 비활성화되고 VPP로부터 VWL이 되어 SN, SP가 비활성화된다. 마지막으로 PCS에 의해 데이터선 쌍 CSN, CSP를 프리차지 레벨 VDL/2에 프리차지를 행한다.

또, 본 발명에 의해 저  $V_t$  MOS를 이용한 프리차지 회로나 컬럼 스위치의 누설 전류도 저감 효과를 얻을 수도 있다. 액티브 스템바이 상태에서는 프리차지 제어 신호 PCS 및 Y 선택 신호 YS0, YS1은 VDBH, VSS, VDBL의 어느 하나로 되어 있다. 감지 증폭기 내의 NMOS의 기판 전위를 공통으로 하고 있는 경우에는 프리차지 회로 PC에 포함된 데이터선 사이에 직렬로 삽입되어 있는 NMOS에서 기판 바이어스 효과가 기능하여  $V_t$ 가 상승하고 나서, 게이트·소스간 전압이 마이너스 전압이 되기 때문에, 프리차지 회로의 누설 전류를 저감시킬 수 있다. 이 때, VDL 내지 VDBH 사이에 흐르는 누설 전류를 저감시킬 수 있다. 동일한 이유에서, 프리차지 회로 PC 내에 포함되는 VDL/2를 공급하여 데이터선 저레벨에 접속되어 있는 NMOS의 VDL/2 내지 VDB로의 누설 전류도 저감시킬 수 있다. 게다가, I/O선 쌍 프리차지 레벨이 데이터선 쌍과 동일하거나 높을 때에는 IO선과 데이터선 저레벨에 접속된 NMOS에서의 누설 전류도 저감시킬 수 있다.

또, 본 발명은 감지 증폭기 액티브 시의 CSN 및 CSP를 활성화 방식 및 활성화하는 MOS의 배치 방식에 대해서는 한정되지 않고, 크로스 커플형 회로 구성을 갖는 SA 구성에 적용할 수 있다. 예를 들면, 오버 드라이브 방식인 제1 실시예 내지 제5 실시예나, 오버 드라이브 방식이 아닌 감지 방식에도 적용 가능하고, 소비 전력을 저감시킬 수 있다.

오버 드라이브 방식을 이용하지 않은 감지 증폭기에 실시한 예를 도 19에 도시한다. 본 구성에서는 감지 증폭기의 PMOS 쌍의 기판 전위를 VDL로 한 구성이 바람직하고, QDP 및 QDP3의 기판 전위도 마찬가지로 VDL로 설정된다.

### 산업상 이용 가능성

본원에 있어서 개시되어 있는 발명 중 대표적인 것에 의해 얻을 수 있는 효과를 간단히 설명하면 다음과 같다. 본 발명에 따르면, 오버 드라이브 방식의 감지 증폭기에 있어서, 오버 드라이브용 감지 드라이버를 감지 증폭기부에 복수 분산 배치함으로써, 복수의 감지 증폭기 사이에서의 감지 시의 공통 소스 전위의 차를 작게 할 수 있다. 또한, 오버 드라이브 기간을 모든 감지 증폭기에 있어서 게이트 신호로 제어할 수 있다. 그 때문에, 오버 드라이브의 원근단 작게 할 수 있는 이점이 있다. 그 결과, 고속 감지 동작을 보증하면서 소비 전력을 억제하여 저소비 전력화할 수 있다.

### 도면의 간단한 설명

도 1은 본 발명의 제1 실시예의 감지 증폭기 부분을 나타내는 도면.

도 2는 제1 실시예의 동작 과정도를 나타낸 도면.

도 3은 본 발명의 제2 실시예의 감지 증폭기 주요 부분을 나타내는 도면.

도 4는 제2 실시예의 동작 과정도를 나타낸 도면.

도 5는 본 발명의 제3 실시예의 감지 증폭기 주요 부분을 나타내는 도면.

도 6은 제3 실시예의 동작 과정도를 나타낸 도면.

도 7은 본 발명의 제4 실시예의 감지 증폭기 부분을 나타내는 도면.

도 8은 제4 실시예의 동작 과정도를 나타낸 도면.

도 9는 본 발명의 제5 실시예의 감지 증폭기 주요 부분을 나타내는 도면.

도 10은 제5 실시예의 동작 과정도를 나타낸 도면.

도 11은 본 발명을 통상의 감지 방식에 적응한 경우의 실시예를 나타내는 도면.

도 12의 (a), (b)는 제4 실시예 및 제5 실시예의 감지 증폭기 부분의 레이아웃 실시예를 나타내는 도면.

도 13은 도 12의 (a), (b)의 감지 증폭기 레이아웃의 A-A'선을 따른 부분의 단면 구조예를 나타내는 도면.

도 14의 (a), (b)는 도 12의 (a), (b)의 감지 증폭기 레이아웃의 각각 B-B'선 및 C-C'선을 따른 부분의 단면 구조예를 나타내는 도면.

도 15는 본 발명의 제6 실시예의 감지 증폭기 부분을 나타내는 도면.

도 16의 (a) 내지 도 16의 (d)는 도 15의 Zn의 구성을 나타낸 도면.

도 17의 (a) 내지 도 17의 (d)는 도 15의 Zp의 구성을 나타낸 도면.

도 18은 도 15의 구성의 Zn 및 Zp에 도 16의 (c) 및 도 17의 (c)를 적용한 경우의 동작 파형을 나타내는 도면.

도 19는 저 Vt 감지 증폭기에 적용한 구성예를 나타내는 도면.

도 20은 액티브 스텐바이에 있어서의 누설 전류 경로를 나타내고 있는 도면.

도 21은 도 20에 있어서의 동작 파형을 나타내는 도면.

도 22는 본원이 적용되는 SDRAM의 전체 구성도.

도 23은 하나의 메모리 어레이 내의 서브 메모리 어레이의 분할을 나타내는 도면.

도 24는 서브 메모리 어레이 내의 매쉬 형상 전원 배선을 나타내는 도면.

도 25는 본원에 앞서서 검토한 오버 드라이브 구동 회로를 갖는 DRAM 회로의 주요부를 나타내는 회로도.

도 26의 (a), (b)는 도 25의 감지 증폭기 동작 시의 공통 소스선의 동작 파형 및 데이터선의 동작 파형이 예를 나타내는 도면.

**도면**

## 도면1

## 도면2

## 도면3

## 도면4

도면5

## 도면6

## 도면7

## 도면8

## 도면9

## 도면10

## 도면11

도면12

(a)

(b)

도면13

도면14

|    |    |      |

|----|----|------|

| M3 | FG | NWEL |

| M2 | P+ |      |

| M1 | N+ |      |

(a)

(b)

## 도면15

## 도면16

## 도면17

## 도면18

도면19

도면20

도면21

도면22

## 도면23

도면24

M2 M3

## 도면25

## 도면26