(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7065794号

(P7065794)

(45)発行日 令和4年5月12日(2022.5.12)

(24)登録日 令和4年4月28日(2022.4.28)

(51)国際特許分類

|         |                  |     |         |        |

|---------|------------------|-----|---------|--------|

| G 0 6 F | 30/347 (2020.01) | F I | G 0 6 F | 30/347 |

| G 0 6 F | 16/903 (2019.01) |     | G 0 6 F | 16/903 |

請求項の数 16 外国語出願 (全17頁)

(21)出願番号 特願2019-1636(P2019-1636)

(22)出願日 平成31年1月9日(2019.1.9)

(65)公開番号 特開2019-121404(P2019-121404

A)

(43)公開日 令和1年7月22日(2019.7.22)

審査請求日 令和3年11月11日(2021.11.11)

(31)優先権主張番号 10 2018 100 423.0

(32)優先日 平成30年1月10日(2018.1.10)

(33)優先権主張国・地域又は機関

ドイツ(DE)

早期審査対象出願

(73)特許権者 506012213

ディスペース ゲー・エム・ベー・ハー

d S P A C E G m b H

ドイツ連邦共和国 パデルボルン ラーテ

ナウシュトラーセ 26

R a t h e n a u s t r . 2 6 , D - 3

3 1 0 2 P a d e r b o r n , G e r

m a n y

100114890

弁理士 アインゼル・フェリックス=ラ

インハルト

100098501

弁理士 森田 拓

100116403

弁理士 前川 純一

最終頁に続く

(54)【発明の名称】 グラフベースの類似度検索を用いたFPGA実装のインクリメンタル方式による生成

## (57)【特許請求の範囲】

## 【請求項1】

FPGAモデルであるFPGAデザイン(10)および/またはハードウェア記述に基づき、FPGA実装(14)を生成する方法であって、前記方法は、

前記FPGAデザイン(10)からネットリスト(12)を合成するステップと、

前記FPGAデザイン(10)に基づきグラフベース表現を生成するステップと、

類似FPGA実装(14)を検索するステップと、

前記類似FPGA実装(14)を使用して、前記ネットリスト(12)から前記FPGA実装(14)を生成するステップと、

を含み、

類似FPGA実装(14)を検索する前記ステップは、前記FPGAデザイン(10)の前記グラフベース表現と、前記類似FPGA実装(14)のグラフベース表現と、を比較するステップを含む

ことを特徴とする方法。

## 【請求項2】

前記FPGAデザイン(10)は、部分実装を含み、

類似FPGA実装(14)を検索する前記ステップは、類似部分実装の検索を含み、

前記類似部分実装を使用して、前記FPGA実装(14)を生成する前記ステップを行う、

請求項1記載の方法。

## 【請求項3】

類似 F P G A 実装 ( 1 4 ) を検索する前記ステップは、以前の F P G A 実装 ( 1 4 ) のデータベース ( 2 2 ) 内の類似 F P G A 実装 ( 1 4 ) の検索を含む、

請求項 1 または 2 記載の方法。

**【請求項 4】**

前記方法は、前記 F P G A デザイン ( 1 0 ) の変更された部分領域を識別するステップをさらに含み、

前記ネットリスト ( 1 2 ) を合成する前記ステップは、前記 F P G A デザイン ( 1 0 ) の前記変更された部分領域に対する前記ネットリスト ( 1 2 ) の合成を含み、

F P G A 実装 ( 1 4 ) を生成する前記ステップは、前記 F P G A デザイン ( 1 0 ) の前記変更された部分領域の前記ネットリスト ( 1 2 ) に対する前記 F P G A 実装 ( 1 4 ) の生成を含む、

10

請求項 1 から 3 までのいずれか 1 項記載の方法。

**【請求項 5】**

前記方法は、

前記 F P G A デザイン ( 1 0 ) の前記グラフベース表現と、少なくとも 1 つの前記類似 F P G A 実装 ( 1 4 ) の前記グラフベース表現と、の間の類似度の大きさを特定するステップと、

前記類似度の大きさが限界値を下回っているならば、類似 F P G A 実装 ( 1 4 ) を使用せずに、前記ネットリスト ( 1 2 ) から前記 F P G A 実装 ( 1 4 ) を生成するステップと、

20

請求項 1 から 4 までのいずれか 1 項記載の方法。

**【請求項 6】**

前記 F P G A デザイン ( 1 0 ) の前記グラフベース表現と、前記類似 F P G A 実装 ( 1 4 ) の前記グラフベース表現と、を比較する前記ステップは、線形最適化問題の解決を含み、前記解決にあたり、1 つのノードを二重に割り当てる事なく、一方のグラフ内の各ノードに対し他方のグラフ内の最類似ノードを識別する、

請求項 1 から 5 までのいずれか 1 項記載の方法。

**【請求項 7】**

前記方法は、前記 F P G A デザイン ( 1 0 ) の前記グラフベース表現のノードと、少なくとも 1 つの前記類似 F P G A 実装 ( 1 4 ) の前記グラフベース表現のノードと、の類似度を、細分化点の一致の検出によって特定するステップをさらに含む、

30

請求項 1 から 6 までのいずれか 1 項記載の方法。

**【請求項 8】**

細分化点の一致を検出する前記ステップは、前記細分化点の重み付けを含む、

請求項 7 記載の方法。

**【請求項 9】**

前記方法は、

データベース ( 2 2 ) 内に含まれている複数のグラフ ( 2 4 ) の類似度分析を実施する付加的なステップと、

算出された類似度を類似度グラフ ( 3 0 ) または類似度マトリックスに記憶するステップと、

40

をさらに含む、

請求項 1 から 8 までのいずれか 1 項記載の方法。

**【請求項 10】**

前記方法は、前記データベース ( 2 2 ) 内に含まれる前記複数のグラフ ( 2 4 ) 間の関係性類似度を算出するステップをさらに含む、

請求項 9 記載の方法。

**【請求項 11】**

前記方法は、すでに特定された類似度に基づき、未特定の関係性について予期される高い類似度を事前に求めるステップをさらに含む、

50

請求項 1 から 10 までのいずれか 1 項記載の方法。

【請求項 12】

前記 F P G A デザイン (10) の前記グラフベース表現と、前記類似 F P G A 実装 (14) のグラフベース表現と、を比較する前記ステップは、近傍関係を考慮する近傍マッチングを含む。

請求項 1 から 11 までのいずれか 1 項記載の方法。

【請求項 13】

前記 F P G A デザイン (10) に基づきグラフベース表現を生成する前記ステップは、仮想接続を考慮しながら前記 F P G A デザイン (10) を非階層化するステップと、前記 F P G A デザイン (10) の前記非階層化に基づき変換関数を適用するステップと、を含む、請求項 1 から 12 までのいずれか 1 項記載の方法。

10

【請求項 14】

前記 F P G A デザイン (10) から前記ネットリスト (12) を合成する前記ステップと、前記 F P G A デザイン (10) に基づき前記グラフベース表現を生成する前記ステップと、を並列に実行する、

請求項 1 から 13 までのいずれか 1 項記載の方法。

【請求項 15】

前記 F P G A デザイン (10) の前記グラフベース表現と、少なくとも 1 つの前記類似 F P G A 実装 (14) のグラフベース表現と、を比較するステップは、グラフを類似度分析するアルゴリズムに基づき行われる、

20

請求項 1 から 14 までのいずれか 1 項記載の方法。

【請求項 16】

F P G A モデルである F P G A デザイン (10) および / またはハードウェア記述に基づきビットストリーム (16) を生成する方法であって、前記方法は、

請求項 1 から 15 までのいずれか 1 項に従い、F P G A モデルである F P G A デザイン (10) および / またはハードウェア記述に基づき F P G A 実装 (14) を生成するステップと、

生成された前記 F P G A 実装 (14) からビットストリーム (16) を生成するステップと、

を含む方法。

30

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、F P G A モデルである F P G A デザインおよび / またはハードウェア記述に基づき、F P G A 実装を生成する方法に関する。この方法は、F P G A デザインからネットリストを合成するステップと、このネットリストから F P G A 実装を生成するステップと、を含む。ただしこの方法は類似 F P G A 実装の検索を含み、ネットリストから F P G A 実装を生成するステップは、この類似 F P G A 実装を使用しながら行われる。

【0002】

さらに本発明は、F P G A モデルである F P G A デザインおよび / またはハードウェア記述に基づきビットストリームを生成する方法に関する。この方法は、F P G A モデルである F P G A デザインおよび / またはハードウェア記述に基づき F P G A 実装を生成する上述のステップと、生成された F P G A 実装からビットストリームを生成することとを含む。

40

【背景技術】

【0003】

かかる方法は、F P G A (Field Programmable Gate Array) のためのコードを生成する目的で使用される。F P G A は、論理回路をロード可能な集積回路である。その際にプログラミングには、公知のプログラミング言語による古典的なプログラミングとは対照的に時系列の設定は僅かであり、それとは異なり所望の回路構造の定義が含まれている。

【0004】

50

この場合、所望の回路構造を定義するための F P G A デザインは、一般にグラフィック F P G A モデルとして生成され、これが例えば V H D L などのようなハードウェア記述言語に書き換えられる。基本的には F P G A デザインを直接、ハードウェア記述言語で生成することもできる。

#### 【 0 0 0 5 】

F P G A デザインは、次いで合成ステップにおいて相応のソフトウェアにより最初に、F P G A において個々の論理素子をどのように結線すべきかを設定するネットリストに書き換えられる。したがってこれは、F P G A のコンフィギュレーションとも呼ばれる。論理素子およびそれらの結線を含むネットリストは、あとで利用するために記憶される。

#### 【 0 0 0 6 】

F P G A 実装を生成するステップがこれに続く。このステップは、一般的に「配置配線」("Place and Route") と呼ばれる。この場合、F P G A のためにネットリストに記憶されている論理素子が配置され (Place)、ネットリストに従って互いに配線される (Route)。その成果物が F P G A 実装である。

#### 【 0 0 0 7 】

次いで F P G A 実装からビットストリームが生成され、F P G A に所望の機能を実装する目的でこの F P G A に伝送される。

#### 【 0 0 0 8 】

これまでに挙げたステップは、しばしば一括りに「ビルド」("Build") と呼ばれる。

#### 【 0 0 0 9 】

その際に今日では簡単に取り扱えるツールが存在しており、それらのツールによって例えば、抽象化を行う F P G A 開発環境が顧客に提供され、その結果として顧客は、F P G A およびツールフローに関する詳細な知識がなくても、自身のハードウェアを開発できるようになる。これによって顧客は、F P G A デザインを作成して実装し、相応の F P G A ハードウェアである F P G A において駆動することができる。例えばラピッドコントロールプロトタイピングなどの場合であると、F P G A モデルにおける規則的な変更およびそれに続くリビルドは、かかる開発プロセスの通常の構成要素である。

#### 【 0 0 1 0 】

その際に問題となるのは、ビルド時間がしばしば著しく長くなることであり、このように著しく長いビルド時間は、F P G A モデルをごく僅かにしか変更しなくても、F P G A のリビルドのために必要とされる場合もある。この場合、ビルド時間はしばしば数時間という範囲に及んでしまう。F P G A はいっそう複雑になり続け、レジスタ、ロジック、D S P ブロックまたはメモリの形態でいっそう多くのリソースを提供するので、ビルド時間はさらにいっそう長くなる。このことは、アルゴリズムを改善しビルドを実施するコンピュータを高速化しても、部分的にしか相殺できない。その際に特に時間がかかるステップは、たいていは配置配線である。

#### 【 0 0 1 1 】

目下の F P G A ツールには、ビルド時間を短縮するために 2 つのアプローチがある。両方のアプローチとも、すでに生成に成功している F P G A 実装の非変更の領域 / 構成要素を再利用する、ということに基づいている。1 つめのアプローチによれば、各構成要素に F P G A 内の 1 つの（矩形）領域が割り当てられる。ある構成要素が変更されると、その構成要素を含む領域が新たに実装される一方、F P G A 実装の残りの部分は変更されないまま維持されて、再利用することができる。ここではインクリメンタルビルドと称する 2 つめのアプローチによれば、事前定義された領域は必要とされない。実装にあたり、すでに実装された F P G A 実装が参照として指定される。一致部分が大きければ、多くの配置配線を自動的に引き継ぐことができ、F P G A 実装の生成にかかる時間が短縮される。

#### 【 0 0 1 2 】

この場合、当初からすでに、個々のモジュールもしくは部分実装を再利用できるように F P G A 実装を生成すると、有利なものとなり得る。このアプローチは、F P G A モデルの自動モジュール化を追求するものである。このようなモジュールベースにおいて、フロア

10

20

30

40

50

プランニングすなわち複数の領域への分割を行うことができる。個々のモジュールについてさらにリザーブも設けられているならば、FPGAモデルの変更を個々のモジュールに限定したままにすることができる。

【0013】

さらに、再プランニングのための方法が知られている。顧客が自身のFPGAモデルに対し変更を加えた場合に、直前のビルド結果が使用される。これに基づき、変更されたモジュールが個別にビルドされ、ついでそれらが全体的なビルドにおいて取り替えられる。複数のモジュールが該当するケースであれば、変更されたそれらのモジュールのためのビルドをそれぞれ異なるコンピュータにおいて行えば、それによってビルド時間を短縮することができる。つまり、変更された複数のモジュールの並列なビルドが実施される。この場合、再利用を簡単に目的で、様々なバージョンのモジュールのバージョニングを設けることができる。

10

【0014】

これらの方針によってビルド時間をすでに短縮できるけれども、さらに改善の余地がある。つまり例えば細粒度のモジュール化の場合には、無駄な部分が大きくなり、また、タイミングが損なわれるリスクが高まる。なぜならば、モジュール境界を越えて最適化することはできず、それらのモジュールのためにそれ相応のリザーブを含む広めの領域をそれぞれ設けなければならないからである。しかもこの方法は、製品開発において多大な実装コストをかけることによってしか実現できない。

20

【0015】

2つのデザインの類似度を突き止める目的で、目下の合成ツールによれば、参照ネットリストが新たに配置配線すべきネットリストと比較される。その際にこの比較はもっぱら、ネットリストパス名の名前の比較に基づいている。このことは問題を孕むものであり、その理由は、Xilinx Vivado System Generator, Xilinx Vivado HLS, Xilinx Vivado S DSoCといった抽象化を行うハイレベルFPGAデザインツールの場合には、例えばサブシステムなどにおいて、同一のFPGA構成要素が即座に名称変更および再編成されるのが一般的だからである。これによって、本来は同一である構成要素についても新たなネットリストパスが自動的に発生する。このような名称変更を、目下の合成ツールでは識別することができない。

30

【0016】

したがって上述の従来技術から出発して本発明の基礎とする課題は、FPGAモデルであるFPGAデザインおよび/またはハードウェア記述に基づきFPGA実装を生成する方法、ならびにFPGAモデルであるFPGAデザインおよび/または上述の形式のハードウェア記述に基づきビットストリームを生成する方法において、特にすでに存在している類似FPGA実装を使用しながら、FPGA実装の簡単かつ効率的な生成を可能にすることである。

【発明の概要】

【発明が解決しようとする課題】

【0017】

本発明によればこの課題は、独立請求項記載の構成要件により解決される。従属請求項には本発明の有利な構成が記載されている。

40

【課題を解決するための手段】

【0018】

したがって本発明によれば、FPGAモデルであるFPGAデザインおよび/またはハードウェア記述に基づき、FPGA実装を生成する方法が設けられており、この方法は、FPGAデザインからネットリストを合成するステップと、このネットリストからFPGA実装を生成するステップと、を含み、ただしこの方法は類似FPGA実装の検索を含み、この類似FPGA実装を使用して、ネットリストからFPGA実装を生成するステップを行う。さらにこの方法は、FPGAデザインに基づきグラフベース表現を生成するステップを含み、類似FPGA実装を検索するステップは、FPGAデザインのグラフベース表

50

現を、少なくとも 1 つの類似 F P G A 実装のグラフベース表現と比較することを含む。

#### 【 0 0 1 9 】

本発明によればさらに、F P G A モデルである F P G A デザインおよび / またはハードウェア記述に基づきビットストリームを生成する方法が設けられており、この方法は、F P G A モデルである F P G A デザインおよび / またはハードウェア記述に基づき F P G A 実装を生成する上述のステップと、生成された F P G A 実装からビットストリームを生成することを含む。

#### 【 0 0 2 0 】

つまり本発明の基本的な着想は、目下の F P G A モデルと他の F P G A モデル例えば以前の F P G A モデルとの類似性を見つけ出し、F P G A 実装の効率的な生成を実施するために使用する、ということである。これに基づき、少なくとも 1 つの存在する類似 F P G A 実装をベースとする目下の F P G A 実装のインクリメンタル方式による生成が実施される。次いで、目下の F P G A 実装を生成するために、類似 F P G A 実装またはそれらのうち少なくとも類似部分が使用される。一般的に、F P G A 実装を生成するための F P G A 口ジックの配置配線に F P G A ビルドの大半の時間が費やされるので、これによって F P G A ビルドの生成にかかる時間の短縮を達成することができる。

10

#### 【 0 0 2 1 】

F P G A デザインは、一般にグラフィック F P G A モデルとして生成され、このモデルがハードウェア記述言語に書き換えられる。基本的には F P G A デザインを直接、ハードウェア記述言語で生成することもできる。ハードウェア記述言語として、例えば V H D L が知られている。V H D L は、超高速集積回路ハードウェア記述言語として知られている (V H S I C ハードウェア記述言語とも称する)。

20

#### 【 0 0 2 2 】

F P G A デザインは、次いで合成ステップにおいて相応のソフトウェアにより最初に、F P G A において個々の論理素子をどのように結線すべきかを設定するネットリストに書き換えられる。したがってこれは、F P G A のコンフィギュレーションとも呼ばれる。論理素子およびそれらの結線を含むネットリストは、あとで利用するために記憶される。

#### 【 0 0 2 3 】

F P G A 実装を生成するステップがこれに続く。このステップは、一般的に「配置配線」 ("Place and Route") と呼ばれる。この場合、F P G A のためにネットリストに記憶されている論理素子が配置され (Place) 、ネットリストに従い互いに配線される (Route)。その成果物が F P G A 実装である。

30

#### 【 0 0 2 4 】

次いで F P G A 実装からビットストリームが生成され、F P G A に所望の機能を実装する目的でこの F P G A に伝送される。

#### 【 0 0 2 5 】

これまでに挙げたステップは、しばしば一括りに「ビルド」 ("Build") と呼ばれる。

#### 【 0 0 2 6 】

好ましくは、合成されたネットリストが個々の F P G A モデルのアーチファクトとしてデータベース内に保管され、その目的は、以降のビルドにあたり対応する F P G A 実装を、必要に応じて類似 F P G A 実装を検索するための参照として、利用できるようにするためである。すでに合成中に、参照としてできるかぎり類似した F P G A 実装を検索することもできる。この目的で最初に、F P G A デザインに基づきグラフベース表現が作成され、すでに事前に実装された F P G A デザインのグラフと比較される。

40

#### 【 0 0 2 7 】

その際、少なくとも 1 つの類似 F P G A 実装のグラフの作成は一般に、類似 F P G A 実装の対応するビルド中に行われる。つまりこのことは、類似 F P G A 実装は慣用のように生成され、または対応する F P G A デザインから出発して本明細書に記載された方法に従っても生成される、ということを意味する。次いでこれらの F P G A 実装のグラフが、やはり個々の F P G A デザインに基づき生成される。

50

## 【 0 0 2 8 】

全体として、この方法を簡単に具現化することができ、その際に様々なステップを並列に実行することができる。したがってリソースを効率的に活用することができる。その際、類似 F P G A 実装を F P G A デザインのためのベースとして使用する目的で、最類似 F P G A 実装を選択することができ、または最小類似度が前提とされる。十分な類似性があるならば、対応する F P G A 実装を参照として使用することができる。まだ類似度について調査されていないさらに別の F P G A デザインが存在するならば、それらの F P G A デザインについて類似 F P G A 実装または最類似 F P G A 実装の検索を続けることができる。

## 【 0 0 2 9 】

F P G A デザインからグラフを作成する際に、ノードおよび信号ラインに対する F P G A モデルのブロックがエッジに変換される。この方法を階層的に適用することができる。グラフィックのサブシステムを、最初の高速な推定についてブロックとして解釈することができ、または完全に行われた状態に至るまで任意の深さで非階層化することができる。変換関数によって例えば、F P G A モデルをとりわけそれらのベースブロックに至るまで、仮想接続 (Goto/From, DataStoreRead/DataStoreMemory/DataStoreWrite, Triggerport, Actionport等) を考慮しながら非階層化し、そこから有向グラフを生成することができる。その際に F P G A モデルは、1つのつながったグラフから成るものとすることができるだけでなく、複数の別個のグラフを含むことができる。かかる別個のグラフが発生するのは例えば、1つの F P G A デザイン内で互いに独立した複数の部分機能が実装される場合である。

10

## 【 0 0 3 0 】

F P G A デザインのグラフベース表現と少なくとも1つの類似 F P G A 実装のグラフベース表現との比較は、グラフを類似度分析するアルゴリズムに基づき行われる。2つのグラフのそれぞれ2つのノード間の類似度の大きさに基づき、公知のアルゴリズムを適用することができる。2つのノードの類似度の大きさが、ブロックパス / ネットリストパス (部分的にも)、ブロックタイプ / ネットリストタイプ (例えば加算、乗算) およびブロックパラメータ / ネットリストパラメータ / ネットリスト属性 (例えばビット幅、2進小数点位置) の一致の程度に基づき特定される。

20

## 【 0 0 3 1 】

本発明の有利な実施形態によれば、F P G A デザインは部分実装を含み、類似 F P G A 実装の検索は類似部分実装の検索を含み、この類似部分実装を使用して F P G A 実装を生成するステップが行われる。したがって類似度検索の問題を、これらの部分実装に関する類似度を求めて比較することによって、種々の部分問題に分けることができる。

30

## 【 0 0 3 2 】

本発明の有利な実施形態によれば、類似 F P G A 実装の検索は、以前の F P G A 実装のデータベース内の類似 F P G A 実装の検索を含む。データベース内に、例えばすべての F P G A 実装を記憶させることができ、その目的は、これらの F P G A 実装をあとで使用するために用意しておくことである。その際にデータベースは好ましくは、1つのプロジェクトの枠内で生成された F P G A 実装を含んでおり、それというのもこのようにすれば、類似 F P G A 実装について高められた確率から出発できるからである。よって、類似 F P G A 実装の検索をその範囲に限定することができる。

40

## 【 0 0 3 3 】

本発明の有利な実施形態によればこの方法は、F P G A デザインの変更された部分領域を識別するステップを含み、ネットリストの合成は、F P G A デザインの変更された部分領域からのネットリストの合成を含み、F P G A 実装の生成は、F P G A デザインの変更された部分領域のネットリストに対する F P G A 実装の生成を含む。したがって新たな F P G A 実装の作成を、最初から F P G A デザインの変更された部分領域に限定することができる。好ましくは、F P G A 実装を個別に新たに実施可能な F P G A デザインのブロックが考察される。

## 【 0 0 3 4 】

50

本発明の有利な実施形態によればこの方法は、FPGAデザインのグラフベース表現と、少なくとも1つの類似FPGA実装のグラフベース表現との間の類似度の大きさを特定するステップを含み、さらにこの方法は、類似度の大きさが限界値を下回っているならば、類似FPGA実装を使用せずに、ネットリストからFPGA実装を生成する慣用のステップを含む。つまり適切な類似FPGA実装が参照として見つけられたならば、目下のFPGA実装の生成中にそれを利用することができる。そうでなければ、FPGAモデルをまったく新たに実装する必要がある。限界値よりも大きい類似度の大きさをもつ有用なFPGA実装が参照として存在しないことが、いっそう早く事前に認識されればされるほど、類似FPGA実装を検索するためにいっそう僅かなリソースしか必要とされない。このことから、FPGAモデルが著しく異なっているのであれば、つまり類似度の大きさが限界値を下回っている場合には、インクリメンタルビルドよりも通常のビルドを用いることで、ビルドにかかる時間を短縮することができる。好ましくは限界値は75%の類似度のところにある。さらに好ましくは限界値は85%の類似度のところにあり、さらにいっそう好ましくは90%のところにある。

#### 【0035】

本発明の有利な実施形態によれば、FPGAデザインのグラフベース表現を少なくとも1つの類似FPGA実装のグラフベース表現と比較するステップは、線形最適化問題の解決を含み、この解決にあたり、1つのノードを二重に割り当てる事なく、一方のグラフ内の各ノードに対し他方のグラフ内の最類似ノードが識別される。この場合、Kuhnによる「ハンガリー法」として知られた方法が適用される。ハンガリー法は線形最適化問題の解決にあたり、1つのノードに二重に割り当てる事なく、一方のグラフの各ノードに対し他方のグラフにおける最類似ノードを見つけるために用いられる。この方法によって総類似度が最大化される。ただし近傍関係を、2つのブロックの類似度に関する大きさとして一緒に算入することができる。この方法は基本的には、近傍関係を考慮せずに実施される。

#### 【0036】

本発明の有利な実施形態によればこの方法は、FPGAデザインのグラフベース表現のノードと、少なくとも1つの類似FPGA実装のグラフベース表現のノードとの類似度を、細分化点の一致の検出によって特定するステップを含む。細分化点には例えば、ブロックパス/ネットリストパス(部分的にも)、ブロックタイプ/ネットリストタイプ例えば加算/乗算、ブロックパラメータ/ネットリストパラメータ例えばビット幅、2進小数点位置が含まれる。

#### 【0037】

本発明の有利な実施形態によれば、細分化点の一致を検出するステップは細分化点の重み付けを含む。この重み付けによって、細分化点を異なる強さで考慮することができる。

#### 【0038】

本発明の有利な実施形態によればこの方法は、データベース内に含まれている複数のグラフの類似度分析を実施する付加的なステップと、算出された類似度を類似度グラフまたは類似度マトリックスに記憶することを含む。したがって類似度分析において見つけ出されるかかる類似度を記憶することができ、その目的は、類似FPGA実装の以降の検索を、FPGAデザインのグラフベース表現と少なくとも1つの類似FPGA実装のグラフベース表現との比較によって簡単にすることである。算出された類似度はここでは、類似FPGA実装の検索において求められる類似度に該当する。

#### 【0039】

本発明の有利な実施形態によればこの方法は、データベース内に含まれる複数のグラフ間の関係性類似度を算出する付加的なステップを含む。したがって例えば、グラフまたは部分グラフを事前に分析し、それらの構造を捕捉して記憶することで、一種の「ハッシング」を実施することができる。この構造を例えば、いわゆるハッシュ値として記憶することができる。したがってグラフの類似度を以降で比較する際に、算出された関係性類似度に基づきこの比較を実施することができ、これによって、FPGAデザインのグラフベース表現と少なくとも1つの類似FPGA実装のグラフベース表現との比較による類似FPG

A 実装の検索が、この構造を通して簡単にされる。データベース内に含まれるグラフ間の関係性類似度を算出するステップには多大な計算コストが付随し、空きリソースを利用するフェーズ中に行うのが望ましく、例えば僅かな計算負荷で F P G A デザインが生成される開発者のモデリングフェーズ中に行うのが望ましい。この場合に好ましくは、複数の F P G A モデルから 1 つの類似度グラフが作成され、このグラフによって、互いに比較されたすべての F P G A モデル間の類似度分析の結果が記憶される。この場合、2 つの F P G A モデル間で調査された類似度が、対応する 2 つのノード間のエッジとして、例えば類似度の大きさである重みと共に表されている。完全にメッシュ化された類似度グラフの場合には、F P G A モデル各々と別の F P G A モデル各々との類似度が表されている。完全な類似度グラフによれば、インクリメンタル F P G A ビルドにとって理想的な開始点を見つけることができる。様々な手法によって、そのように完全なものとすることができます。第 1 のバリエーションとして総当たり方式に従い、類似度グラフを完全にメッシュ化するために欠けているエッジを、さらなる類似度分析を通して補うことができる。この結果として、すでに述べたように多大な計算能力が要求されることとなり、したがって例えば F P G A デザイン作成中、C P U 負荷が僅かなときに例えばバックグラウンドで行うことができる。第 2 のバリエーションは、存在する F P G A 実装の効率的な計算順序に基づくものである。これによれば、場合によっては高い類似度が生じる可能性をもって存在しているエッジに基づき、2 つのノード間の類似度が推定され、その目的はそれらについて優先的に類似度分析を実施するためである。これによって、類似度グラフのメッシュ化をさらに完全なものとすることができます。その際に例えば確率のアプローチを適用することができる。これによれば確率と同様に類似度が、存在する複数のエッジを経由する 1 つの経路に沿って乗算される：経路 2 - 1 - 4 = 4 5 % × 8 5 % = 3 8 %。第 3 のバリエーションによれば 2 つのノード間の類似度が、存在するエッジに基づきバリエーション 2 のアプローチによって推定される。F P G A デザインの正確な類似度は、このアプローチの場合には分析されない。

#### 【 0 0 4 0 】

本発明の有利な実施形態によればこの方法は、すでに特定された類似度に基づき、未特定の関係性について予期される高い類似度を事前に求める付加的なステップを含む。いずれの類似 F P G A 実装を参照として利用できるのか、または類似 F P G A を参照として利用できるのか否かについて、いっそう早く事前に識別できればできるほど、この方法をいっそう効率的に実施することができる。

#### 【 0 0 4 1 】

本発明の有利な実施形態によれば、F P G A デザインのグラフベース表現と少なくとも 1 つの類似 F P G A 実装のグラフベース表現とを比較するステップは、近傍関係を考慮する近傍マッチングを含む。かかる方法は例えば、Nikolic による "Measuring Similarity of Graph Nodes by Neighbor Matching" として知られている。これによれば類似度が 2 つのグラフ間の類似度として求められ、これは最適化の最適なノード対応関係についてのノード類似度の総計をノード数で除算することによって得られる。

#### 【 0 0 4 2 】

本発明の有利な実施形態によれば、F P G A デザインに基づきグラフベース表現を生成するステップは、仮想接続を考慮しながら F P G A デザインを非階層化すること、および F P G A デザインの非階層化に基づき変換関数を適用することを含む。階層型のサブシステムの場合にはそれらのサブシステムを、最初の高速な推定についてロックとして解釈することができ、または完全に行われた状態に至るまで任意の深さで非階層化することができる。仮想接続および階層型のロックの依存性を捕捉し、かかるロックを F P G A 実装を作成するためのベースとして適用するときに正しく使用する目的で、変換が必要である。仮想接続は例えば、Goto/From, DataStoreRead/DataStoreMemory/DataStore Write, Triggerport, Actionport 等といった接続を含むことができる。

#### 【 0 0 4 3 】

次に、添付の図面を参照しながら好ましい実施形態に基づき、本発明について詳しく説明

10

20

30

40

50

する。

【図面の簡単な説明】

【0044】

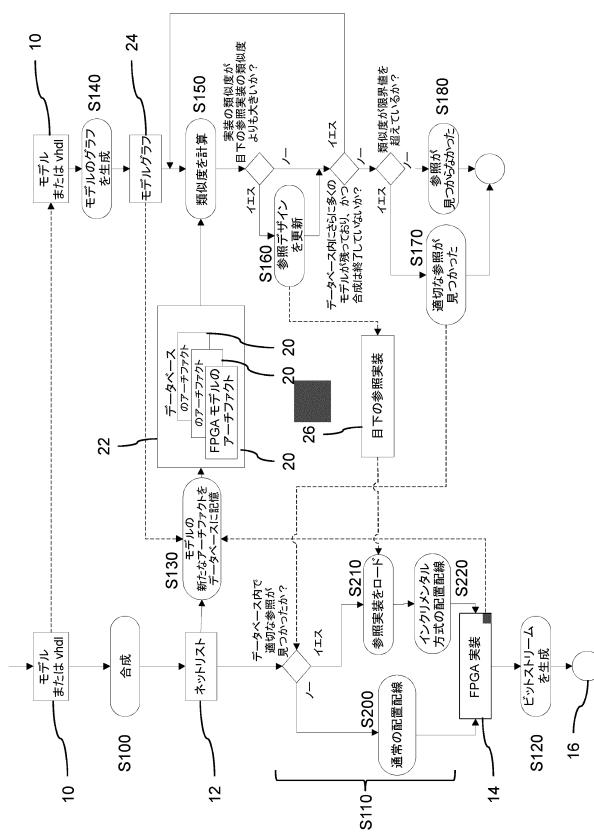

【図1】第1の好ましい実施形態に従いFPGAデザインに基づき、FPGA実装およびこのFPGA実装からのビットストリームを生成するための方法を実施するフローチャートである。

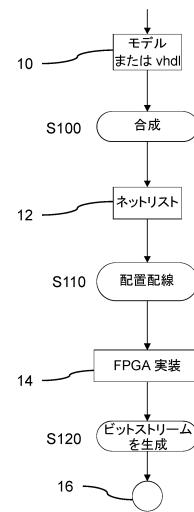

【図2】第1の実施形態に従いFPGA実装およびビットストリームを生成するための図1のフローチャートの詳細図である。

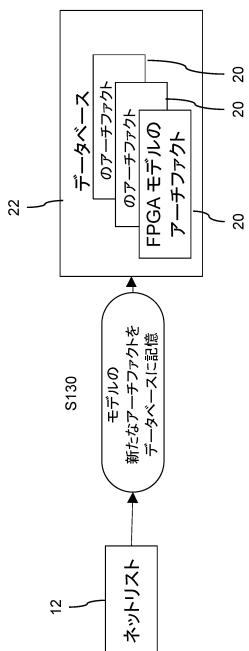

【図3】第1の実施形態に従いデータベースへのエントリを行うための図1のフローチャートの詳細図である。

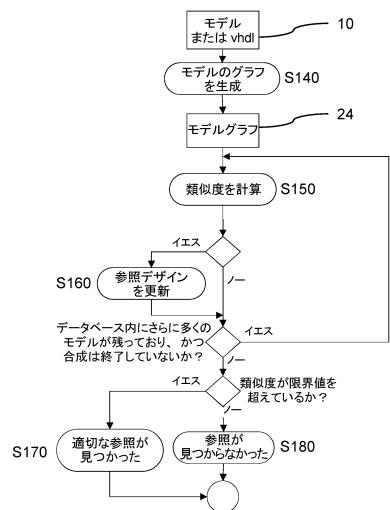

【図4】第1の実施形態に従い類似FPGAデザインを求めるための図1のフローチャートの詳細図である。

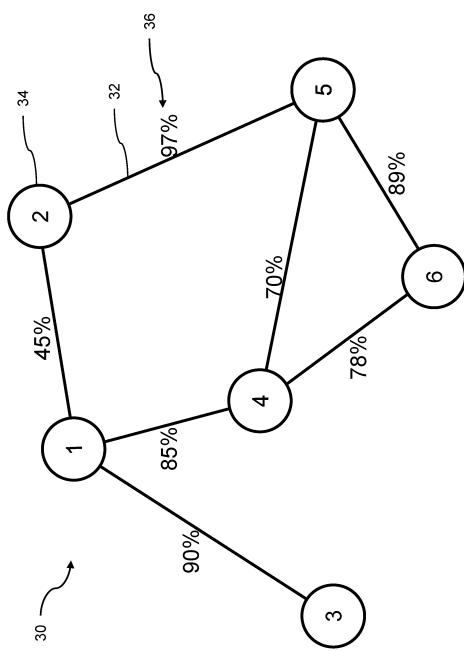

【図5】第1の実施形態による第1の例として、類似度グラフをそのノード34間の複数のエッジと共に概略的に示す図である。

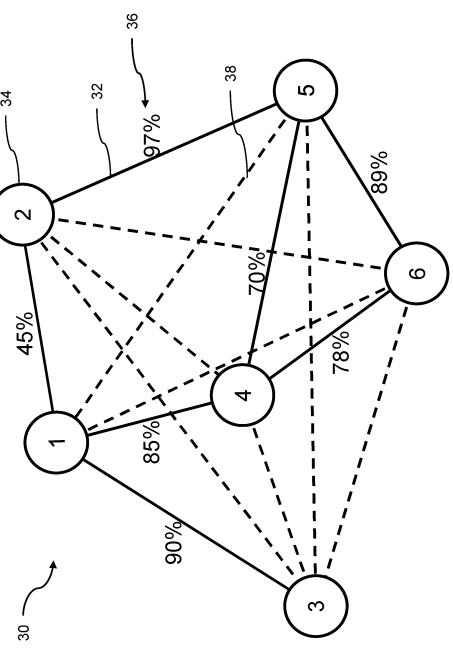

【図6】第1の実施形態による第2の例として、すべてのノード間に1つのエッジが形成されている類似度グラフを概略的に示す図である。

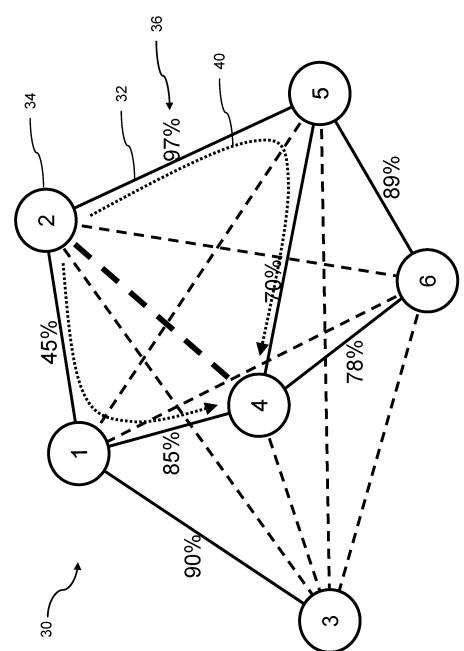

【図7】第1の実施形態による第3の例として、すべてのノード間に1つのエッジが形成されている類似度グラフを概略的に示す図であって、ただしノード間において明示的には求められない類似度が、ノード間において特定された類似度に基づき求められることを示す図である。

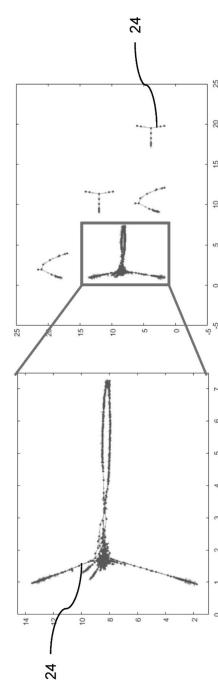

【図8】第1の実施形態による例示的なモデルグラフを概略的に示す図である。

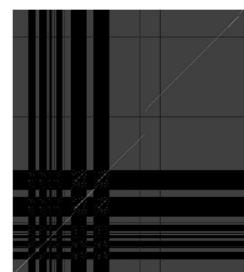

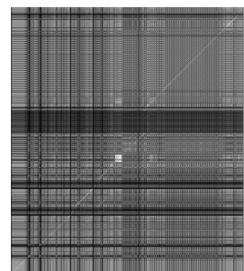

【図9】第1の実施形態による2つのモデルグラフのノード間の2つの類似度マトリックスを概略的に示す図であって、左側には「近傍マッチング」なしのイメージを、右側には「近傍マッチング」ありのイメージを示す図である。

【発明を実施するための形態】

【0045】

図1～図4には、FPGAモデルであるFPGAデザインおよび/またはハードウェア記述に基づき、FPGA実装およびこのFPGA実装からのビットストリームを生成するための方法が示されている。

【0046】

この方法の出発点として、ここではFPGAデザイン10がグラフィックFPGAモデルとして生成されて準備される。次いでこのFPGAモデルが、ここでは例えばVHDL (Very High Speed Integrated Circuit Hardware Description Language 超高速集積回路ハードウェア記述言語) であるハードウェア記述言語に書き換えられる。

【0047】

ここから出発してビルドをスタートさせることができ、ビルドはまずは以下で詳しく説明するステップS100, S110およびS120を含む。

【0048】

ステップS100において、FPGAデザイン10からネットリスト12の合成が行われる。ネットリスト12は、FPGAデザイン10に記述されているような論理素子およびそれらの結線を含む。

【0049】

ステップS110において、ネットリスト12からFPGA実装14が生成される。このステップは、一般的に「配置配線」("Place and Route")と呼ばれる。この場合、FPGAのためにネットリスト12に記憶されている論理素子が配置され(Place)、ネットリスト12に従って互いに配線される(Route)。その成果物がFPGA実装14である。ステップS110の詳細についてはあとで説明する。

【0050】

ステップS120において、生成されたFPGA実装14から、FPGAへ伝送するための、およびFPGAと共に使用するためのビットストリーム16が生成される。

10

20

30

40

50

**【 0 0 5 1 】**

図4に詳しく示されているように、類似FPGAデザインを求めるステップS140～S180は、先行するステップに並列に、特にステップS100に並列に、実施される。

**【 0 0 5 2 】**

したがってステップS140においてFPGAデザイン10から、グラフベース表現としてモデルグラフ24がFPGAデザイン10に基づき生成される。FPGAデザイン10からモデルグラフ24を作成する際に、ノードおよび信号ラインに対するFPGAモデル10のブロックがエッジに変換される。図8にはモデルグラフ24が例示的に描かれており、その際にこの図には、複数の独立したモデルグラフ24が共に実装されて描かれている。この場合、グラフィックのサブシステムを、最初の高速な推定についてブロックとして解釈することができ、またはそれらのサブシステムを完全に行われた状態に至るまで任意の深さで非階層化することができる。変換関数によって例えば、FPGAモデルをとりわけそれらのベースブロックに至るまで、仮想接続(Goto/From, DataStoreRead/DataStoreMemory/DataStoreWrite, Triggerport, Actionport等)を考慮しながら非階層化し、そこから有向グラフを生成することができる。FPGAデザイン10の非階層化に際して仮想接続が考慮され、FPGAデザイン10の非階層化に基づき変換関数が適用される。

10

**【 0 0 5 3 】**

ステップS150において、モデルグラフ24の類似度がデータベース22からのモデルグラフ24と比較される。データベース22からのモデルグラフ24は、先行のFPGA実装14のグラフベース表現である。

20

**【 0 0 5 4 】**

その際に最初に、目下のFPGAデザイン10のモデルグラフ24と、データベース22からの先行のFPGA実装14のモデルグラフ24との比較が、グラフの類似度分析のためのアルゴリズムに基づき実施される。2つのモデルグラフ24のそれぞれ2つのノード34間の類似度の大きさをベースにして、ノード34の類似度の大きさが、ブロックパス/ネットリストパス(部分的にも)、ブロックタイプ/ネットリストタイプ(例えば加算、乗算)およびブロックパラメータ/ネットリストパラメータ/ネットリスト属性(例えばビット幅、2進小数点位置)の一一致の程度に基づき特定される。

30

**【 0 0 5 5 】**

さらにこの比較には線形最適化問題の解決も含まれ、これによれば1つのノード34が二重に割り当てられることなく、一方のモデルグラフ24内のノード34各自について、他方のモデルグラフ24内の最類似ノード34が識別される。これはKuhnによる「ハンガリーフ」法として基本的に知られている。

**【 0 0 5 6 】**

目下のFPGAデザイン10のモデルグラフ24と、データベース22からのFPGA実装14のモデルグラフ24との比較にはさらに、近傍関係を考慮するための近傍マッチングが含まれる。かかる方法は例えば、Nikolicによる"Measuring Similarity of Graph Nodes by Neighbor Matching"として知られている。これに関連して図9には、2つのモデルグラフ24のノード34間の2つの類似度マトリックスが示されている。図9の左側のイメージには「近傍マッチング」なしの類似度マトリックスが、右側のイメージには「近傍マッチング」ありの類似度マトリックスが示されている。

40

**【 0 0 5 7 】**

この場合、目下のFPGAデザイン10のモデルグラフ24のノード34と、データベース22からのFPGA実装14のモデルグラフ24のノード34との類似度は、細分化点の一致に基づき求められる。細分化点には例えば、ブロックパス/ネットリストパス、ブロックタイプ/ネットリストタイプ(例えば加算/乗算)、ブロックパラメータ/ネットリストパラメータ(例えばビット幅、2進小数点位置)が含まれる。ここでは細分化点の重み付けが行われる。

**【 0 0 5 8 】**

50

さてここで、両方のモデルグラフ 2 4 の類似度についてこのようにして特定された大きさから出発して、目下の F P G A デザイン 1 0 のモデルグラフ 2 4 とデータベース 2 2 からの F P G A 実装 1 4 のモデルグラフ 2 4 との類似度が、目下の F P G A デザイン 1 0 のモデルグラフ 2 4 とデータベース 2 2 からの最良モデルグラフ 2 4 との類似度よりも高いか否か、についてチェックされる。データベース 2 2 からのモデルグラフ 2 4 が、目下の F P G A デザイン 1 0 のモデルグラフ 2 4 との類似度を求める最初のモデルグラフ 2 4 であるならば、データベース 2 2 からのモデルグラフ 2 4 が最良モデルグラフ 2 4 または参照 2 6 として引き継がれる。これとは異なり、データベース 2 2 からのモデルグラフ 2 4 がこれまでの参照 2 6 よりも高い類似度を有している場合のみ、参照 2 6 が変更される。このことは、適用可能であれば、ステップ S 1 6 0 において行われる。データベース 2 2 内に比較のためにさらに別のモデルグラフ 2 4 が含まれているのであれば、この方法はステップ S 1 5 0 に戻る。ステップ S 1 0 0 による合成がすでに終了しているか否かについても、チェックされる。ステップ S 1 0 0 による合成がまだ終了していない場合のみ、ステップ S 1 5 0 において比較が続けられる。

#### 【 0 0 5 9 】

つまりステップ S 1 0 0 による合成が終了しているならば、またはデータベース 2 2 内に比較のためにさらに別のモデルグラフ 2 4 が含まれていなければ、目下の参照 2 6 の類似度の大きさが限界値と比較される。類似度の大きさが限界値よりも大きいならば、ステップ S 1 1 0 において F P G A 実装 1 4 を生成するための参照 2 6 として、相応のモデルグラフ 2 4 がステップ S 1 7 0 において準備される。そうでなければ、この方法のこの部分は、ステップ S 1 8 0 において結果を伴わずに中止される。ここで限界値は例えば、90 % の類似度のところにある。

#### 【 0 0 6 0 】

ステップ S 1 1 0 における F P G A 実装 1 4 の生成は、以下のようにして実施される。最初に、ステップ S 1 7 0 により類似 F P G A 実装 1 4 がモデルグラフ 2 4 に基づき求められて準備されたか否か、についてチェックされる。これが当てはまらなければ、F P G A 実装 1 4 を作成する目的で、ステップ S 2 0 0 において通常の慣用の配置配線が実施される。そうでなければ、この方法はステップ S 2 1 0 と共に続けられる。

#### 【 0 0 6 1 】

ステップ S 2 1 0 において、参照のためにデータベース 2 2 から F P G A 実装 1 4 がロードされる。次いでステップ S 2 2 0 において、データベース 2 2 からの F P G A 実装 1 4 に基づき、インクリメンタル方式で配置配線が行われる。

#### 【 0 0 6 2 】

図 3 に示されているように、データベース 2 2 へのエントリが行われる。ステップ S 1 3 0 において、それぞれ目下の F P G A デザイン 1 0 のネットリスト 1 2 、それに属するモデルグラフ 2 4 および生成された F P G A 実装 1 4 が、F P G A モデル 1 0 のアーチファクト 2 0 としてデータベース 2 2 に記憶される。このように各 F P G A デザイン 1 0 は、その後の新たな F P G A デザイン 1 0 についての以降の比較のために、データベース 2 2 内にアーチファクト 2 0 を自動的に形成する。

#### 【 0 0 6 3 】

ここには示されていないバックグラウンドステップとして付加的に、データベース 2 2 内に含まれているモデルグラフ 2 4 間の関係性類似度が計算される。この場合、データベース 2 2 内に含まれているアーチファクト 2 0 のモデルグラフ 2 4 間の関係性類似度を算出するステップは、空きリソースを利用するフェーズ中に行われる。その際に複数の F P G A モデル 1 0 から、1 つの類似度グラフ 3 0 が作成される。図 5 ~ 図 7 には、種々の類似度グラフ 3 0 が示されている。この場合、2 つの F P G A モデル 1 0 間で調査された類似度が、F P G A モデル 1 0 を表現する対応する2つのノード 3 4 間のエッジ 3 2 として、類似度の大きさである重み 3 6 と共に記載されている。類似度グラフ 3 0 は、類似度線図とも呼ばれる。

#### 【 0 0 6 4 】

10

20

30

40

50

この場合、図 5 の類似度グラフ 3 0 は、少数のノード 3 4 間のエッジ 3 2 だけしか示していないのに対し、図 6 および図 7 の類似度グラフ 3 0 は、完全な類似度グラフ 3 0 である。ノード 3 4 間においてエッジ 3 2 として直線で表されているすでに求められた類似度から出発して、破線として表されている付加的なエッジ 3 8 の重み 3 6 が求められる。様々な手法によって、このように完全なものとすることができます。この目的で総当たり方式に従い類似度グラフ 3 0 を完全なものとするために、付加的なエッジ 3 8 の重み 3 6 がさらなる類似度分析を通して逐次、補われる。

#### 【 0 0 6 5 】

図 7 には、F P G A デザイン 1 0 に存在するエッジ 3 2 の効率的な計算順序に基づき、そこにある類似度グラフ 3 0 を完全なものとするための 1 つのバリエーションが示されている。これによれば、場合によって高い類似度が生じる可能性をもって存在しているエッジ 3 2 に基づき、2 つのノード 3 4 間の類似度が推定され、その目的はそれらについて優先的に類似度分析を実施するためである。このようにすれば付加的なエッジ 3 8 を、存在しているエッジ 3 2 の重み 3 6 の乗算によって推定することができる。これは図 7 によれば例えば、「2」および「4」で表されたノード 3 4 間の付加的なエッジ 3 8 について、これら双方のノード 3 4 間の類似度を推定する目的で、点線矢印 4 0 に沿って類似度を乗算することによって行われる。このことから出発して、求められた高い類似度を有するエッジ 3 2 に対する重み 3 6 を第一に特定することができる。

10

#### 【 0 0 6 6 】

類似度グラフ 3 0 に基づき、ステップ S 1 5 0 における比較を簡単にすることができます、かつ加速することができる。

20

#### 【 符号の説明 】

#### 【 0 0 6 7 】

- 1 0 F P G A デザイン

- 1 2 ネットリスト

- 1 4 F P G A 実装

- 1 6 ビットストリーム

- 2 0 アーチファクト

- 2 2 データベース

- 2 4 モデルグラフ

- 2 6 参照

- 3 0 類似度グラフ、類似度線図

- 3 2 エッジ

- 3 4 ノード

- 3 6 重み

- 3 8 付加的なエッジ

- 4 0 点線矢印

30

40

50

【図面】

【図 1】

【図 2】

10

20

【図 3】

【図 4】

30

40

50

【図 5】

【図 6】

【図 7】

【図 8】

10

20

30

40

50

【図9】

10

20

30

40

50

---

フロントページの続き

(74)代理人 100135633

弁理士 二宮 浩康

(74)代理人 100162880

弁理士 上島 類

(72)発明者 ドミニク ルーベライ

ドイツ連邦共和国 パデルボルン ラーテナウシュトラーセ 26 ケア・オブ ディスペーク ゲゼ

ルシャフト ミット ベシュレンクテル ハフツング

(72)発明者 ハイコ カルテ

ドイツ連邦共和国 パデルボルン ラーテナウシュトラーセ 26 ケア・オブ ディスペーク ゲゼ

ルシャフト ミット ベシュレンクテル ハフツング

審査官 甲斐 哲雄

(56)参考文献

特開2017-191556 (JP, A)

特開平07-152801 (JP, A)

特表2001-515247 (JP, A)

特開平11-219379 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

G 06 F 30/00 - 30/398

G 06 F 16/00 - 16/958