(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2008년07월02일

(11) 등록번호 10-0843225

(24) 등록일자 2008년06월26일

(51) Int. Cl.

H03B 5/08 (2006.01)

(21) 출원번호 10-2007-0002174

(22) 출원일자 2007년01월08일

심사청구일자 2007년01월08일

(56) 선행기술조사문헌

KR1020070008739 A

US6838952 B2

JP2002118445 A

전체 청구항 수 : 총 17 항

(73) 특허권자

삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자

김우년

경기 용인시 기흥구 보정동 죽전택지개발지구38블

력 죽현마을현대아이파크1차아파트 201-301

(74) 대리인

리엔목특허법인

심사관 : 조성찬

(54) 위상 잡음을 제어하는 전압 제어 발진기 및 그 이용 방법

**(57) 요약**

위상 잡음을 제어하는 전압 제어 발진기 및 그 이용 방법이 개시된다. 상기 전압 제어 발진기는 전압 제어 발진부 및 증폭부를 구비하는 것을 특징으로 한다. 상기 전압 제어 발진부는 전원 전압에 대응되는 발진주파수를 갖는 제 1 출력 신호들을 생성한다. 상기 증폭부는 상기 제 1 출력 신호들을 수신하고, 상기 수신된 각각의 제 1 출력 신호의 전달 컨덕턴스 성분을  $n$ ( $n$ 은 자연수)차 미분한 값을 증폭하여 제 2 출력 신호로서 출력한다. 상기 위상 잡음을 제어하는 전압 제어 발진기 및 그 이용 방법은 구형파와 유사한 형태의 파형을 가지는 출력 신호를 출력함으로써 전압 제어 발진기의 출력 신호의 위상 잡음을 효율적으로 감소시킬 수 있는 장점이 있다.

**대표도 - 도2**

## 특허청구의 범위

### 청구항 1

전원 전압에 대응되는 발진주파수를 갖는 제 1 출력 신호들을 생성하는 전압 제어 발진부; 및

상기 제 1 출력 신호들을 수신하고, 상기 수신된 각각의 제 1 출력 신호의 전달 컨덕턴스 성분을  $n$ ( $n$ 은 자연

수)차 미분한 값을 증폭하여 제 2 출력 신호로서 출력하는 증폭부를 구비하는 것을 특징으로 하는 전압 제어

발진기.

### 청구항 2

제1항에 있어서, 상기 증폭부는,

상기 각각의 제 1 출력 신호의 전달 컨덕턴스 성분을 2차 미분한 값을 증폭하여 제 2 출력 신호로서 출력하는

것을 특징으로 하는 전압 제어 발진기.

### 청구항 3

제1항에 있어서, 상기 증폭부는,

바이어스 전압이 인가되고, 상기 바이어스 전압을 조절하여 상기 각각의 제 1 출력 신호의 전달 컨덕턴스 성분

을  $n$ ( $n$ 은 자연수)차 미분한 값을 증폭하여 제 2 출력 신호로서 출력하는 것을 특징으로 하는 전압 제어

발진기.

### 청구항 4

제3항에 있어서, 상기 바이어스 전압은,

상기 제 1 출력 신호들 중 양의 기울기를 가지는 제 1 출력 신호와 음의 기울기를 가지는 제 1 출력 신호가 교

차하는 부분의 전압인 것을 특징으로 하는 전압 제어 발진기.

### 청구항 5

제1항에 있어서, 상기 증폭부는,

제 1 저항 및 제 1 커패시터와 게이트가 연결되고 상기 전원 전압이 제 1 단에 연결되며 제 2 커패시터 및 상기

전압 제어 발진기의 제 1 출력단과 제 2 단이 연결되는 제 1 트랜지스터; 및

제 2 저항 및 상기 제 2 커패시터의 타단과 게이트가 연결되고 상기 전원 전압이 제 1 단에 연결되며 상기 제 1

커패시터의 타단 및 상기 전압 제어 발진기의 제 2 출력단과 제 2 단이 연결되는 제 2 트랜지스터를 구비하고,

상기 제 1 저항의 타단, 상기 제 2 저항의 타단 및 바이어스 전압이 연결되는 것을 특징으로 하는 전압 제어

발진기.

### 청구항 6

제5항에 있어서, 상기 제 1 트랜지스터 및 제 2 트랜지스터는,

PMOS 트랜지스터인 것을 특징으로 하는 전압 제어 발진기.

### 청구항 7

제1항에 있어서, 상기 전압 제어 발진부는,

상기 전원 전압과 제 1 단이 연결되는 제 1 차동 증폭기;

접지 전압과 제 1 단이 연결되는 제 2 차동 증폭기; 및

상기 제 1 차동 증폭기의 제 2 단 및 제 2 차동 증폭기의 제 2 단과 연결되는 LC 공진기를 구비하고,

상기 LC 공진기의 양단은 상기 증폭부와 연결되는 것을 특징으로 하는 전압 제어 발진기.

### 청구항 8

제7항에 있어서, 상기 LC 공진기는,

두 개의 직렬 연결된 베액터 다이오드(varactor diode)들과 인더터가 병렬로 연결되는 제 1 공진 회로를 구비하는 것을 특징으로 하는 전압 제어 발진기.

### 청구항 9

제8항에 있어서, 상기 LC 공진기는,

인더터 및 커패시터가 병렬 연결되며 상기 제 1 공진 회로의 제 1 단과 연결되는 제 2 공진 회로; 및

인더터 및 커패시터가 병렬 연결되며 상기 제 1 공진 회로의 제 2 단과 연결되는 제 3 공진 회로를 더 구비하는 것을 특징으로 하는 전압 제어 발진기.

### 청구항 10

제7항에 있어서, 상기 제 1 차동 증폭기 및 제 2 차동 증폭기는,

두 개의 트랜지스터가 크로스 커플(cross couple)된 래치 회로인 것을 특징으로 하는 전압 제어 발진기.

### 청구항 11

제7항에 있어서, 상기 전달 컨덕턴스는,

상기 제 1 차동 증폭기 및 제 2 차동 증폭기의 트랜지스터들 중 턴 온(turn on)되어 있는 트랜지스터들의 전달 컨덕턴스 성분의 합인 것을 특징으로 하는 전압 제어 발진기.

### 청구항 12

전원 전압에 대응되는 발진주파수를 갖는 제 1 출력 신호들을 생성하는 단계; 및

상기 각각의 제 1 출력 신호의 전달 컨덕턴스 성분을  $n$ ( $n$ 은 자연수)차 미분한 값을 증폭하여 제 2 출력 신호로서 출력하는 단계를 구비하는 것을 특징으로 하는 전압 제어 발진기의 위상 잡음 개선 방법.

### 청구항 13

제12항에 있어서, 상기 제 2 출력 신호로서 출력하는 단계는,

상기 각각의 제 1 출력 신호의 전달 컨덕턴스 성분을 2차 미분한 값을 증폭하여 제 2 출력 신호로서 출력하는 단계인 것을 특징으로 하는 전압 제어 발진기의 위상 잡음 개선 방법.

### 청구항 14

제12항에 있어서, 상기 제 2 출력 신호로서 출력하는 단계는,

바이어스 전압을 인가하는 단계; 및

상기 바이어스 전압을 조절하여 상기 각각의 제 1 출력 신호의 전달 컨덕턴스 성분을  $n$ ( $n$ 은 자연수)차 미분한 값을 증폭하여 제 2 출력 신호로서 출력하는 단계를 구비하는 것을 특징으로 하는 전압 제어 발진기의 위상 잡음 개선 방법.

### 청구항 15

제14항에 있어서, 상기 바이어스 전압은,

상기 제 1 출력 신호들 중 양의 기울기를 가지는 제 1 출력 신호와 음의 기울기를 가지는 제 1 출력 신호가 교차하는 부분의 전압인 것을 특징으로 하는 전압 제어 발진기의 위상 잡음 개선 방법.

### 청구항 16

제12항에 있어서, 상기 전달 컨덕턴스는,

상기 제 1 출력 신호들을 생성하는 단계에 관여하는 상기 전압 제어 발진기의 트랜지스터들 중 턴 온(turn on)되어 있는 트랜지스터들의 전달 컨덕턴스 성분의 합인 것을 특징으로 하는 전압 제어 발진기의 위상 잡음 개선

방법.

## 청구항 17

제8항에 있어서, 상기 LC 공진기는,

복수의 직렬 연결된 인덕터들 및 복수의 직렬 연결된 커패시터들이 병렬 연결되며 상기 제 1 공진 회로의 제 1 단과 연결되는 제 2 공진 회로; 및

복수의 인덕터들 및 복수의 커패시터들이 병렬 연결되며 상기 제 1 공진 회로의 제 2 단과 연결되는 제 3 공진 회로를 더 구비하는 것을 특징으로 하는 전압 제어 발진기.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

- <11> 본 발명은 위상 잡음(phase noise) 제어에 관한 것으로, 특히 위상 잡음을 제어하는 전압 제어 발진기(VCO : Voltage Controlled Oscillator) 및 전압 제어 발진기(VCO)의 위상 잡음을 제어하는 방법에 관한 것이다.

- <12> 전압 제어 발진기(VCO)는 인가된 전원 전압으로 원하는 발진 주파수를 출력할 수 있게 해주는 장치로서, 이동 통신 단말기 등에서 주로 사용된다. 전압 제어 발진기(VCO)는 이동 통신 기기에서 PLL(Phase Locked Loop) 모듈에 사용되어 채널을 할당하고 주파수를 무선 주파수(RF : Radio Frequency) 또는 중간 주파수(IF : Intermediate Frequency)로 변환하는 국부 발진기(Local Oscillator) 역할을 한다.

- <13> 현재, 고주파수용 전압 제어 발진기(VCO)에 주로 쓰이고 있는 것은 LC 공진기(Oscillator)를 내장한 CMOS 타입이다. 최근에 휴대용 이동 통신 시장의 수요가 증가하고 더욱 많은 기능을 한 곳에 집적시킨 저전력 시스템 IC 개발이 요구되면서, CMOS 회로는 낮은 생산 단가와 집적 용이성 및 높은 제조 공정의 신뢰성으로 인해 일반적으로 널리 사용되고 있다. 그러나, CMOS 회로는 이러한 높은 생산성과 집적성에도 불구하고 열악한 잡음 특성, 낮은 항복 전압(breakdown voltage) 및 낮은 이득(gain)으로 인하여 회로 설계에 어려움이 있다. 따라서, CMOS 회로의 장점을 살리면서 전압 제어 발진기(VCO)의 성능을 극대화하기 위하여 위상 잡음(phase noise)을 개선하기 위한 연구가 활발하게 진행되고 있다.

- <14> 전압 제어 발진기(VCO)에 관한 구체적인 예는 미국공개특허공보 제2004-0085144호 (2004. 05. 06 공개)에 개시되어 있다.

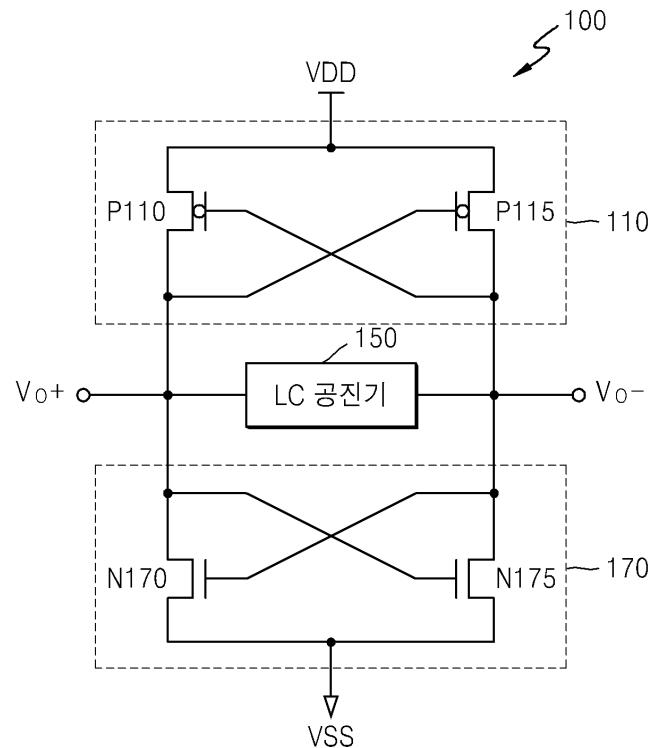

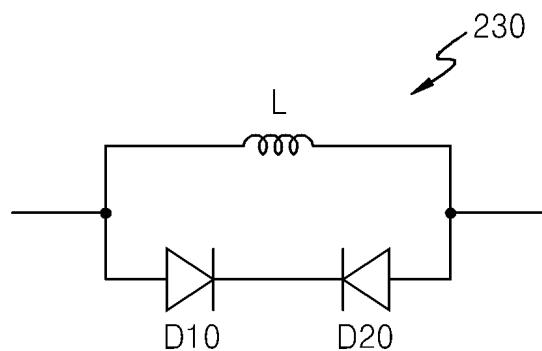

- <15> 도 1은 종래의 LC 공진기(Oscillator)를 이용한 전압 제어 발진기(100)의 회로도이다.

- <16> 도 1을 참조하면, 전압 제어 발진기(100)는 차동 증폭기들(110, 170) 및 LC 공진기(150)를 구비한다. 차동 증폭기(110)는 두 개의 PMOS 트랜지스터들(P110, P115)이 크로스 커플(cross couple)된 래치 회로이다. 즉, PMOS 트랜지스터(P110)는 게이트에 PMOS 트랜지스터(P115)의 제 1 단이 연결되고 제 1 단이 PMOS 트랜지스터(P115)의 게이트와 연결되며 제 2 단이 전원 전압(VDD)에 연결된다. 마찬가지로, PMOS 트랜지스터(P115)는 게이트에 PMOS 트랜지스터(P110)의 제 1 단이 연결되고 제 1 단이 PMOS 트랜지스터(P110)의 게이트와 연결되며 제 2 단이 전원 전압(VDD)에 연결된다. 차동 증폭기(170)도 두 개의 NMOS 트랜지스터들(N170, N175)이 크로스 커플된 래치 회로로서, PMOS 트랜지스터들(P110, P115) 대신 NMOS 트랜지스터들(N170, N175)이 연결되고 전원 전압(VDD) 대신에 접지 전압(Vss)에 연결되는 점을 제외하면 차동 증폭기(110)와 동일하다.

- <17> 차동 증폭기들(110, 170) 사이에 LC 공진기(150)가 연결된다. LC 공진기(150)은 인덕턴스 성분 또는 커패시턴스 성분의 가변으로 주파수를 결정한다.

- <18> 차동 증폭기들(110, 170)과 LC 공진기(150)가 연결되는 부분이 전압 제어 발진기(100)의 출력단들(Vo+, Vo-)이 된다.

- <19> 앞서 살펴보았듯이 최근 휴대용 이동 통신 시장의 수요가 증가하고 더욱 많은 기능을 한 곳에 집적시킨 저전력 시스템 IC 개발이 요구되면서 종래의 전압 제어 발진기(100)에 비하여 위상 잡음(phase noise)이 훨씬 개선되어야 할 필요성이 대두 되었다.

### 발명이 이루고자 하는 기술적 과제

- <20> 본 발명이 이루고자하는 기술적 과제는 구형파와 유사한 형태의 출력 신호를 출력함으로써 위상 잡음(noise phase)을 제어하는 전압 제어 발진기(VCO)를 제공하는데 있다.

- <21> 본 발명이 이루고자하는 다른 기술적 과제는 상기 전압 제어 발진기(VCO)를 사용하여 위상 잡음을 제어하는 방법을 제공하는데 있다.

- 발명의 구성 및 작용

- <22> 상기 기술적 과제를 달성하기 위한 본 발명의 실시예에 따른 전압 제어 발진기는 전압 제어 발진부 및 증폭부를 구비하는 것을 특징으로 한다. 상기 전압 제어 발진부는 전원 전압에 대응되는 발진주파수를 갖는 제 1 출력 신호들을 생성한다. 상기 증폭부는 상기 제 1 출력 신호들을 수신하고, 상기 수신된 각각의 제 1 출력 신호의 전달 컨덕턴스 성분을  $n$ ( $n$ 은 자연수)차 미분한 값을 증폭하여 제 2 출력 신호로서 출력한다.

- <23> 상기 증폭부는 상기 각각의 제 1 출력 신호의 전달 컨덕턴스 성분을 2차 미분한 값을 증폭하여 제 2 출력 신호로서 출력하는 것이 바람직하다.

- <24> 상기 증폭부는 바이어스 전압이 인가되고, 상기 바이어스 전압을 조절하여 상기 각각의 제 1 출력 신호의 전달 컨덕턴스 성분을  $n$ ( $n$ 은 자연수)차 미분한 값을 증폭하여 제 2 출력 신호로서 출력하는 것이 바람직하다.

- <25> 상기 바이어스 전압은 상기 제 1 출력 신호들 중 양의 기울기를 가지는 제 1 출력 신호와 음의 기울기를 가지는 제 1 출력 신호가 교차하는 부분의 전압인 것이 바람직하다.

- <26> 상기 증폭부는 제 1 저항 및 제 1 커패시터와 게이트가 연결되고 상기 전원 전압이 제 1 단에 연결되며 제 2 커패시터 및 상기 전압 제어 발진기의 제 1 출력단과 제 2 단이 연결되는 제 1 트랜지스터 및 제 2 저항 및 상기 제 2 커패시터의 타단과 게이트가 연결되고 상기 전원 전압이 제 1 단에 연결되며 상기 제 1 커패시터의 타단 및 상기 전압 제어 발진기의 제 2 출력단과 제 2 단이 연결되는 제 2 트랜지스터를 구비하고, 상기 제 1 저항의 타단, 상기 제 2 저항의 타단 및 바이어스 전압이 연결되는 것이 바람직하다.

- <27> 상기 전압 제어 발진부는 상기 전원 전압과 제 1 단이 연결되는 제 1 차동 증폭기, 접지 전압과 제 1 단이 연결되는 제 2 차동 증폭기 및 상기 제 1 차동 증폭기의 제 2 단 및 제 2 차동 증폭기의 제 2 단과 연결되는 LC 공진기를 구비하고, 상기 LC 공진기의 양단은 상기 증폭부와 연결되는 것이 바람직하다.

- <28> 상기 LC 공진기는 두 개의 직렬 연결된 버랙터 다이오드(varactor diode)들과 인덕터가 병렬로 연결되는 제 1 공진 회로를 구비하는 것이 바람직하다.

- <29> 또한 상기 LC 공진기는 상기 제 1 공진 회로, 인덕터 및 커패시터가 병렬 연결되며 상기 제 1 공진 회로의 제 1 단과 연결되는 제 2 공진 회로 및 인덕터 및 커패시터가 병렬 연결되며 상기 제 1 공진 회로의 제 2 단과 연결되는 제 3 공진 회로를 구비하는 것이 바람직하다.

- <30> 상기 전달 컨덕턴스는 상기 제 1 차동 증폭기 및 제 2 차동 증폭기의 트랜지스터들 중 턴 온(turn on)되어 있는 트랜지스터들의 전달 컨덕턴스 성분의 합인 것이 바람직하다.

- <31> 상기 기술적 과제를 달성하기 위한 본 발명의 다른 실시예에 따른 전압 제어 발진기의 위상 잡음 개선 방법은 전원 전압에 대응되는 발진주파수를 갖는 제 1 출력 신호들을 생성하는 단계, 상기 각각의 제 1 출력 신호의 전달 컨덕턴스 성분을  $n$ ( $n$ 은 자연수)차 미분한 값을 증폭하여 제 2 출력 신호로서 출력하는 단계를 구비하는 것을 특징으로 한다.

- <32> 상기 제 2 출력 신호로서 출력하는 단계는 바이어스 전압을 인가하는 단계 및 상기 바이어스 전압을 조절하여 상기 각각의 제 1 출력 신호의 전달 컨덕턴스 성분을  $n$ ( $n$ 은 자연수)차 미분한 값을 증폭하여 제 2 출력 신호로서 출력하는 단계를 구비하는 것이 바람직하다.

- <33> 본 발명과 본 발명의 동작상의 이점 및 본 발명의 실시예에 의하여 달성되는 목적을 충분히 이해하기 위해서는 본 발명의 바람직한 실시예를 예시하는 첨부 도면 및 도면에 기재된 내용을 참조하여야 한다.

- <34> 이하, 첨부한 도면을 참조하여 본 발명의 바람직한 실시예를 설명함으로써, 본 발명을 상세히 설명한다. 각 도면에 제시된 동일한 참조부호는 동일한 부재를 나타낸다.

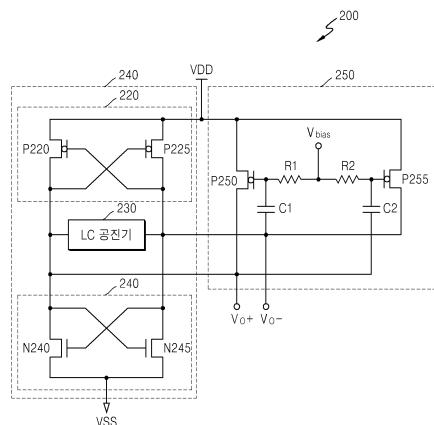

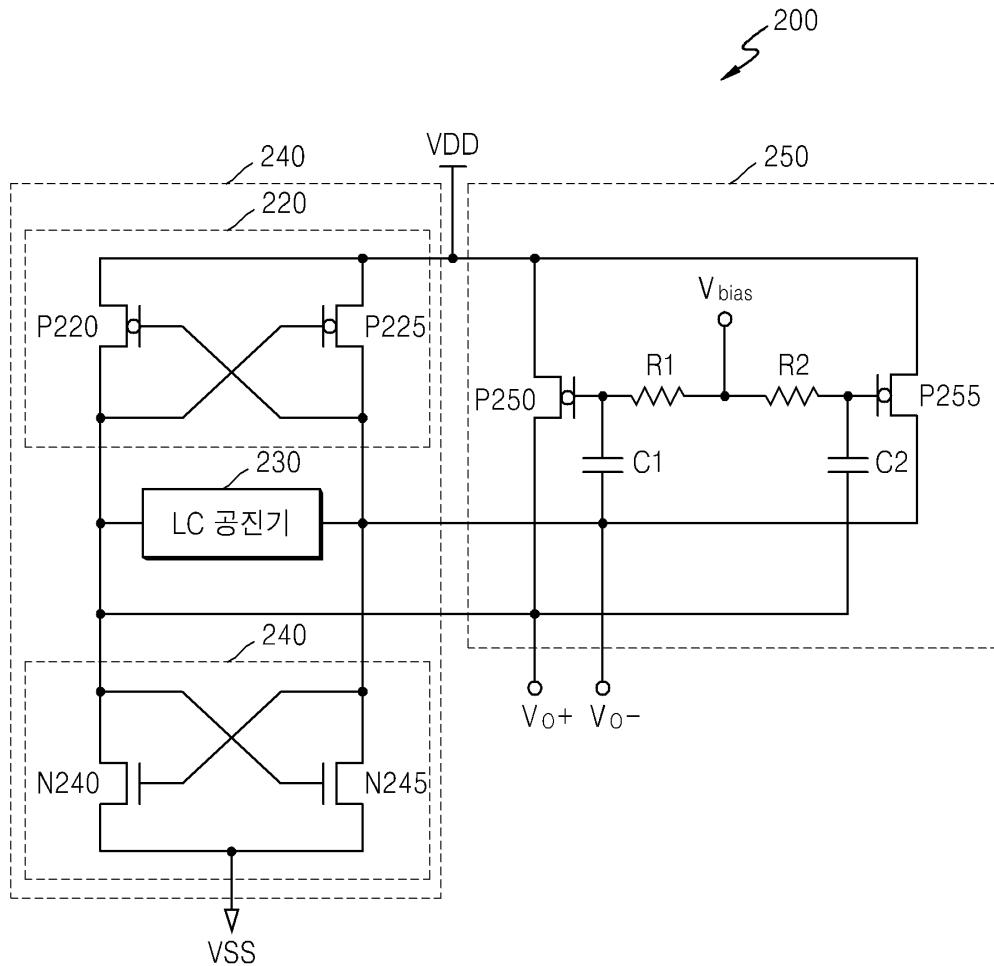

- <35> 도 2는 본 발명의 실시예에 따른 전압 제어 발진기(VCO : Voltage Controlled Oscillator)(200)의 회로도이다.

- <36> 도 2를 참조하면, 전압 제어 발진기(200)는 전압 제어 발진부(210) 및 증폭부(250)를 구비한다. 전압 제어 발진부(210)는 제 1 차동 증폭기(Differential Amplifier)(220), LC 공진기(Oscillator)(230) 및 제 2 차동 증폭기(240)를 구비한다. 제 1 차동 증폭기(220)는 두 개의 트랜지스터들(P220, P225)이 크로스 커플(cross couple)된 래치 회로이다. 즉, 트랜지스터(P220)는 게이트에 트랜지스터(P225)의 제 1 단이 연결되고 제 1 단이 트랜지스터(P225)의 게이트와 연결되며 제 2 단이 전원 전압(VDD)에 연결된다. 마찬가지로, 트랜지스터(P225)는 게이트에 트랜지스터(P220)의 제 1 단이 연결되고 제 1 단이 트랜지스터(P220)의 게이트와 연결되며 제 2 단이 전원 전압(VDD)에 연결된다. 상기 트랜지스터들(P220, P225)은 PMOS 트랜지스터인 것이 바람직하다.

- <37> 제 2 차동 증폭기(240)도 두 개의 트랜지스터들(N240, N245)이 크로스 커플된 래치 회로로서 제 1 차동 증폭기(220)와 그 구성은 동일하다. 다만, 제 2 차동 증폭기(240)는 제 1 차동 증폭기(220)와 달리 전원 전압(VDD) 대신에 접지 전압(Vss)이 연결되고 트랜지스터들(N240, N245)은 NMOS 트랜지스터인 것이 바람직하다.

- <38> 제 1 차동 증폭기(220) 및 제 2 차동 증폭기들(240) 사이에 LC 공진기(230)가 연결된다. LC 공진기(230)가 인덕턴스 성분 또는 커패시턴스 성분의 가변으로 주파수를 결정한다는 것은 공지된 사실이다. LC 공진기(230)의 구체적 구성에 대하여는 도 3(a) 및 도 3(b)에서 상세히 설명한다.

- <39> 증폭부(250)는 복수의 저항들, 복수의 커패시터들 및 복수의 트랜지스터들을 구비할 수 있다. 상기 트랜지스터들 중 제 1 트랜지스터(P250)는 제 1 저항(R1) 및 제 1 커패시터(C1)와 게이트가 연결되고 전원 전압(VDD)이 제 1 단에 연결되며 제 2 커패시터(C2)가 제 2 단에 연결된다. 또한, 제 2 트랜지스터(P255)는 제 2 저항(R2) 및 제 2 커패시터(C2)의 타단과 게이트가 연결되고 전원 전압(VDD)이 제 1 단에 연결되며 제 1 커패시터(C1)의 타단과 제 2 단이 연결된다. 제 1 트랜지스터(P250) 및 제 2 트랜지스터(P255)는 PMOS 트랜지스터인 것이 바람직하다. 제 1 저항(R1)의 타단, 제 2 저항(R2)의 타단 및 바이어스 전압(Vbias)은 하나의 노드(node)에 연결되어 있다.

- <40> 전압 제어 발진부(210)와 증폭부(250)는 전압 제어 발진기(200)의 출력단(Vo+, Vo-)과 연결되어 있다. 즉, LC 공진기(230)의 일단과 제 1 커패시터(C1)와 제 2 트랜지스터(P255)의 제 2 단이 하나의 노드(node)에 연결되고, 상기 노드가 전압 제어 발진기(200)의 제 1 출력단(Vo+)이다. 또한, LC 공진기(230)의 타단과 제 2 커패시터(C2)와 제 1 트랜지스터(P250)의 제 2 단이 다른 하나의 노드에 연결되고, 상기 노드가 전압 제어 발진기(200)의 제 2 출력단(Vo-)이다. 전압 제어 발진기(200)의 동작에 관하여는 도 4에서 상세히 설명한다.

- <41> 도 3(a)는 도 2의 LC 공진기(230)의 일 실시예를 나타내는 회로도이다.

- <42> 도 3(a)를 참조하면, 종래의 일반적인 LC 공진기의 회로도로서, LC 공진기(230)는 인덕터(L)와 두개의 베랙터 다이오드(varactor diode)(D10, D20)를 구비한다. 베랙터 다이오드(D10, D20)는 인가되는 전압에 따라 커패시턴스가 변하는 소자이다. 베랙터 다이오드(D10, D20)에 인가되는 전압이 변하면 내부의 등가 커패시턴스가 변하게 되므로, LC 공진기(230)의 공진 주파수가 변화하여 전압 제어 발진부(210)의 출력 신호의 발진 주파수가 변하게 된다. 즉, 인가되는 전압을 제어함으로써 전압 제어 발진부(210)의 출력 신호의 발진 주파수를 변화시킬 수 있다.

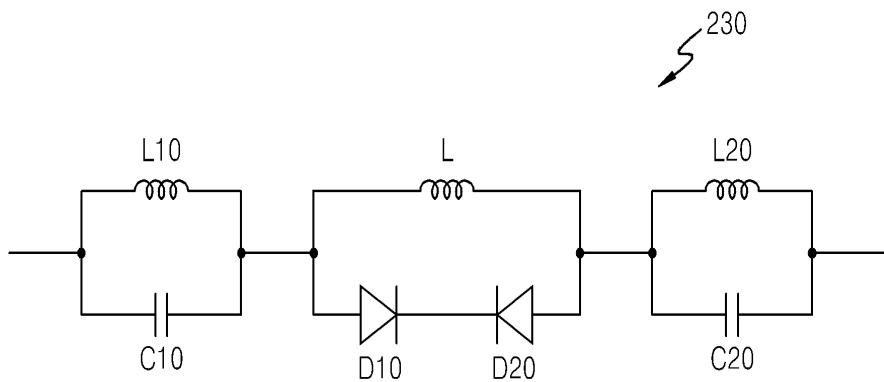

- <43> 도 3(b)는 도 2의 LC 공진기(230)의 다른 일 실시예를 나타내는 회로도이다.

- <44> 도 3(b)를 참조하면, LC 공진기(230)는 고조파(harmonic) 튜닝된 LC 공진기를 나타낸다. LC 공진기(230)는 제 1 공진 회로, 제 2 공진 회로 및 제 3 공진 회로를 구비한다. 상기 제 1 공진 회로는 도 3(a)와 같이 구성된다. 상기 제 2 공진 회로는 인덕터(L10) 및 커패시터(C10)가 병렬 연결되며 상기 제 1 공진 회로의 제 1 단과 연결된다. 상기 제 3 공진 회로는 인덕터(L20) 및 커패시터(C20)가 병렬 연결되며 상기 제 1 공진 회로의 제 2 단과 연결된다. 도 3(b)에서는 제 2 공진 회로 또는 제 3 공진 회로가 하나의 인덕터와 하나의 커패시터가 연결된 경우에 대하여만 도시하였으나, 복수의 인덕터들과 복수의 커패시터들이 병렬 연결된 경우에도 본 발명과 동일한 효과를 얻을 수 있음을 당해 기술분야에서 통상의 지식을 가진 자에게 자명한 사항이다.

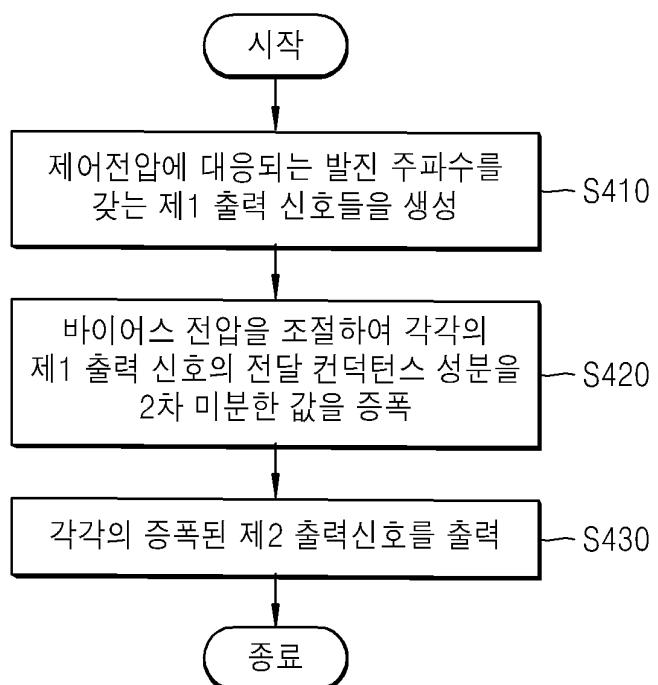

- <45> 도 4는 본 발명의 실시예에 따른 전압 제어 발진기의 위상 잡음 제어 방법의 흐름도이다.

- <46> 도 2 및 도 4를 참조하여 전압 제어 발진기(200)의 위상 잡음을 제어하는 방법에 관하여 설명한다. 전원 전압(VDD)을 인가하면 전압 제어 발진부(210)는 전원 전압(VDD)에 대응되는 발진 주파수를 가지는 제 1 출력 신호들을 생성한다(S410 단계). 증폭부(250)는 바이어스 전압(Vbias), 트랜지스터들(P250, P255), 저항들(R1, R2) 및 커패시터들(C1, C2)의 값을 조절하여 상기 각각의 제 1 출력 신호의 전달 컨덕턴스(transconductance) 성분을 2

차 미분한 값을 증폭한다(S420 단계). 바이어스 전압(Vbias)은 상기 제 1 출력 신호들이 일정한 기울기를 가지고 만나는 부분의 전압인 것이 바람직하다. 즉, LC 공진기(230)의 양단에서 측정되는 각각의 제 1 출력 신호들은 반대의 위상을 가지므로, 바이어스 전압(Vbias)은 양의 기울기를 가지는 제 1 출력 신호와 음의 기울기를 가지는 다른 하나의 제 1 출력 신호가 만나는 부근의 전압이 된다. 일반적인 전압 제어 발진기의 경우 각각의 출력 전압이 일정한 기울기를 가지고 만나는 부분의 근처에서 위상 잡음(phase noise)이 가장 크다. 따라서, 본 발명의 전압 제어 발진기(200)는 상기 위상 잡음이 가장 큰 부분의 출력 전압의 기울기를 매우 크게 하여 거의 구형파에 가까운 출력 파형을 출력함으로써 상기 위상 잡음을 제거하기 위하여, 바이어스 전압(Vbias)을 상기와 같이 설정한다.

<47> 상기 전달 컨덕턴스 성분은 제 1 차동 증폭기(220) 및 제 2 차동 증폭기(240)의 트랜지스터들(P220, P225, N240, N245) 중 턴 온(turn on)되어 있는 트랜지스터들의 전달 컨덕턴스 성분을 합한 값이다. 예를 들어, 제 1 차동 증폭기(220)에서 PMOS 트랜지스터(P220)가 턴 온되어 있고, 제 2 차동 증폭기(240)에서 NMOS 트랜지스터(N245)가 턴 온되어 있다고 가정하자. 이 경우, 전달 컨덕턴스 성분은 PMOS 트랜지스터(P220)의 전달 컨덕턴스 성분 및 NMOS 트랜지스터(N245)의 전달 컨덕턴스 성분을 합한 값이 된다. 증폭부(250)는 상기 전달 컨덕턴스 성분을  $n$ ( $n$ 은 자연수)차 미분한 값을 증폭한다. 여기서  $n$ 은 2인 것이 바람직하다.

<48> 수학식 1은 FET(Field Effect Transistor)가 새츄레이션 영역(saturation region)에서 동작하는 경우 동작 바이어스(bias) 근처에서의 맥급수(power series)를 나타낸다.

## 수학식 1

$$i_d(v_{gs}) = g_{m1} * v_{gs} + g_{m2} * v_{gs}^2 + g_{m3} * v_{gs}^3 + \dots$$

<49> 수학식 1에서, 상기  $i_d$ 는 상기 트랜지스터의 드레인(drain)과 소스(source)간 흐르는 전류이고, 상기  $v_{gs}$ 는 게이트(gate)와 소스(source) 사이의 전압이다. 상기  $g_{m1}$ 이 앞서 설명한 트랜지스터의 전달 컨덕턴스이고,  $g_{m2}$ 와  $g_{m3}$ 는 각각 입력에 대한 2차와 3차 비선형 계수를 나타낸다. 본 발명에서 상기 전달 컨덕턴스( $g_{m1}$ )를 2차 미분한 값은  $g_{m3}$ 이고, 증폭부(250)는  $g_{m3}$ 를 증폭한다.

<51> 즉, 증폭부(250)가 상기 전달 컨덕턴스 성분을 2차 미분한 값( $g_{m3}$ )을 증폭함으로써, 전압 제어 발진기(200)는 상기 각각의 제 1 출력 신호의 홀수차 고조파를 증가시켜 구형파와 유사한 파형의 제 2 출력 신호를 출력단( $V_{o+}$ ,  $V_{o-}$ )을 통하여 출력한다(S430 단계). 구형파와 유사한 신호란 각각의 출력단( $V_{o+}$ ,  $V_{o-}$ )을 통하여 출력되는 각각의 출력 신호의 기울기가 매우 큼을 의미한다. 따라서, 상기 설명한 바와 같이 위상 잡음을 더욱 효과적으로 제거할 수 있다.

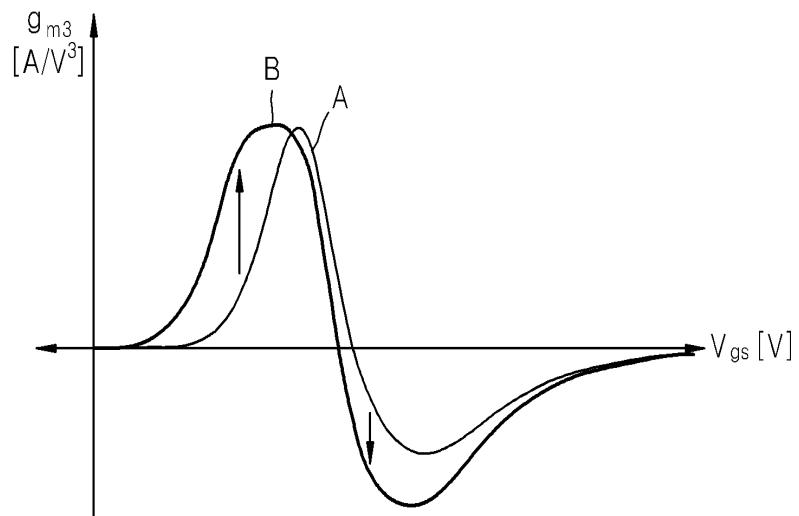

<52> 도 5는 도 2의 증폭부(250)에 의하여 전달 컨덕턴스 성분을 2차 미분한 값( $g_{m3}$ )이 증폭되는 모습을 나타내는 그래프이다.

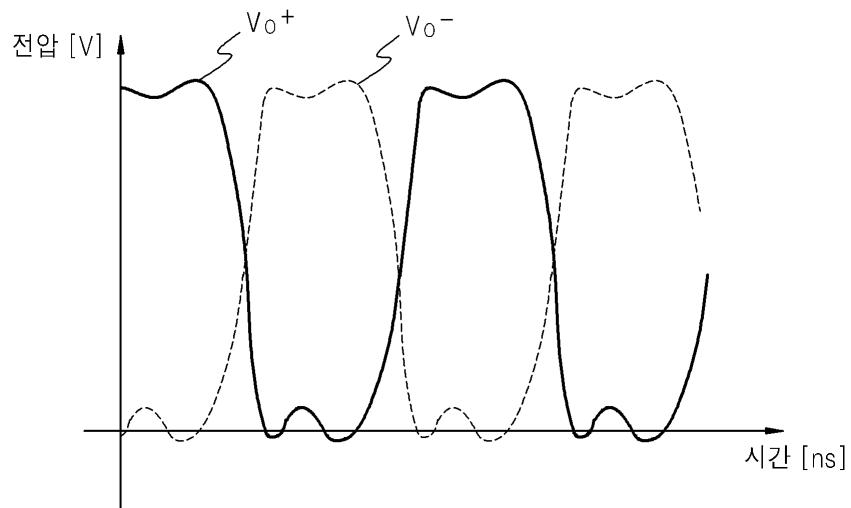

<53> 도 2 및 도 5를 참조하면, 본 발명의 증폭부(250)가 동작하지 않는 경우가 A 곡선이고, 증폭부(250)가 동작하는 경우가 B 곡선이다. 즉, 증폭부(250)에서 바이어스 전압(Vbias)을 조절하여 상기 각각의 제 1 출력 신호의 전달 컨덕턴스 성분을 2차 미분한 값( $g_{m3}$ )을 양의 영역 및 음의 영역 모두에서 증폭시키고 있다. 그 결과, 도 6(b)와 같은 전압 제어 발진기(200)의 제 2 출력 신호가 나타나게 된다.

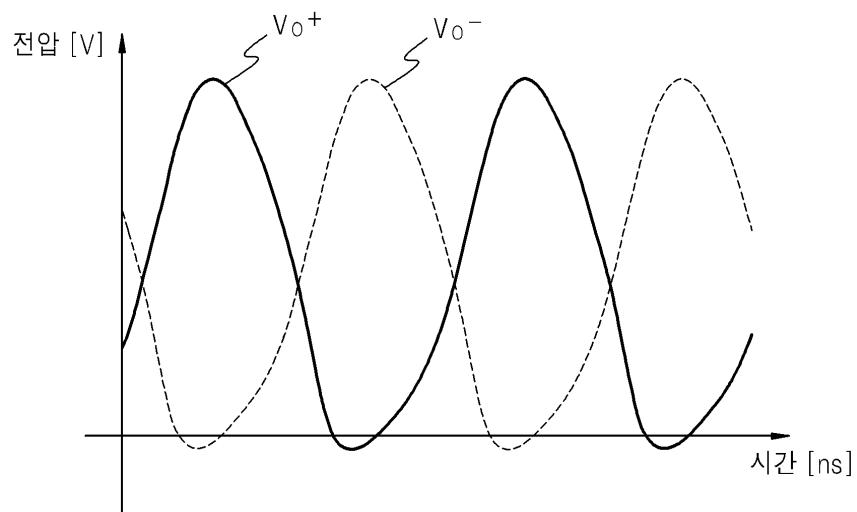

<54> 도 6(a)는 종래 기술에 따른 전압 제어 발진기의 출력 신호의 파형을 나타내는 그래프이고, 도 6(b)는 도 2의 전압 제어 발진기(200)의 출력 신호의 파형을 나타내는 그래프이다.

<55> 도 6(a) 및 도 6(b)를 참조하면, 전압 제어 발진기의 출력단들( $V_{o+}$ ,  $V_{o-}$ )을 통하여 출력되는 종래의 출력 신호는 사인파와 유사한 형태의 파형임을 알 수 있다. 그러나, 본 발명의 실시예에 따른 전압 제어 발진기(200)의 출력단들( $V_{o+}$ ,  $V_{o-}$ )을 통하여 출력되는 제 2 출력 신호는 구형파와 유사한 형태의 파형이다. 즉, 본 발명에 의한 경우 종래에 비하여 전압 제어 발진기의 출력 신호의 기울기가 매우 크기 때문에 전압 제어 발진기의 출력 신호의 위상 잡음을 효율적으로 감소시킬 수 있다.

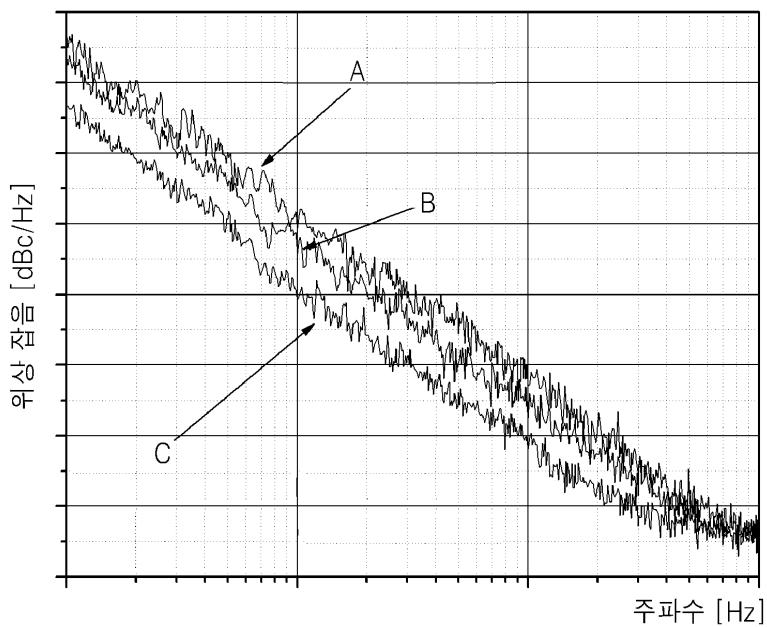

<56> 도 7은 종래 기술과 본 발명에 있어서 위상 잡음(phase noise)의 정도를 비교한 그래프이다.

<57> 도 7을 참조하면, 도 1의 전압 제어 발진기(100) 중 LC 공진기(150)가 도 3(a)와 같이 구성된 경우가 A이고, 도 1의 전압 제어 발진기(100) 중 LC 공진기(150)가 도 3(b)와 같이 구성된 경우가 B이다. 그리고, C가 본 발

명의 실시예에 따른 도 2의 전압 제어 발진기(200)의 경우의 위상 잡음을 나타낸 그래프이다. 상기 그래프들을 비교하여 보면 종래의 전압 제어 발진기(100) 중 LC 공진기(150)를 도 3(b)와 같이 구성한 경우인 B는 A에 비하여 약간의 위상 잡음이 개선된 것을 볼 수 있다. 그러나, 본 발명의 실시예에 따른 C 그래프는 종래 기술인 A 및 B에 비하여 훨씬 위상 잡음이 개선된 것을 알 수 있다.

<58> 이상에서와 같이 도면과 명세서에서 최적 실시예가 개시되었다. 여기서 특정한 용어들이 사용되었으나, 이는 단지 본 발명을 설명하기 위한 목적에서 사용된 것이지 의미한정이나 특허청구범위에 기재된 본 발명의 범위를 제한하기 위하여 사용된 것은 아니다. 그러므로 본 기술분야의 통상의 지식을 가진 자라면 이로부터 다양한 변형 및 균등한 타 실시예가 가능하다는 점을 이해할 것이다. 따라서, 본 발명의 진정한 기술적 보호범위는 첨부된 특허청구범위의 기술적 사상에 의해 정해져야 할 것이다.

### 발명의 효과

<59> 상술한 바와 같이 본 발명에 따른 위상 잡음을 제어하는 전압 제어 발진기 및 그 이용 방법은 구형파와 유사한 형태의 파형을 가지는 출력 신호를 출력함으로써 전압 제어 발진기의 출력 신호의 위상 잡음을 효율적으로 감소시킬 수 있는 장점이 있다. 즉, 종래에 비하여 전압 제어 발진기의 출력 신호의 기울기가 매우 크기 때문에 상기 출력 신호의 위상 잡음이 개선되는 효과가 있다.

### 도면의 간단한 설명

- <1> 본 발명의 상세한 설명에서 인용되는 도면을 보다 충분히 이해하기 위하여 각 도면의 간단한 설명이 제공된다.

- <2> 도 1은 종래의 LC 공진기(Oscillator)를 이용한 전압 제어 발진기(Voltage Controlled Oscillator)의 회로도이다.

- <3> 도 2는 본 발명의 실시예에 따른 전압 제어 발진기의 회로도이다.

- <4> 도 3(a)는 도 2의 LC 공진기의 일 실시예를 나타내는 회로도이다.

- <5> 도 3(b)는 도 2의 LC 공진기의 다른 일 실시예를 나타내는 회로도이다.

- <6> 도 4는 본 발명의 실시예에 따른 전압 제어 발진기의 위상 잡음 제어 방법의 흐름도이다.

- <7> 도 5는 도 2의 증폭부에 의하여 전달 컨덕턴스(transconductance) 성분을 2차 미분한 값이 증폭되는 모습을 나타내는 그래프이다.

- <8> 도 6(a)는 종래 기술에 따른 전압 제어 발진기의 출력 신호의 파형을 나타내는 그래프이다.

- <9> 도 6(b)는 도 2의 전압 제어 발진기의 출력 신호의 파형을 나타내는 그래프이다.

- <10> 도 7은 종래 기술과 본 발명에 있어서 위상 잡음(phase noise)의 정도를 비교한 그래프이다.

도면

도면1

## 도면2

## 도면3a

도면3b

도면4

도면5

도면6a

도면6b

도면7