# (19)대한민국특허청(KR) (12) 등록특허공보(B1)

(51) 。Int. Cl. H01L 21/78 (2006.01) (45) 공고일자

2007년02월09일

(11) 등록번호

10-0681264

(24) 등록일자

2007년02월05일

(21) 출원번호 (22) 출원일자 10-2005-0046224

(65) 공개번호

10-2006-0124349

심사청구일자

2005년05월31일 2005년05월31일 (43) 공개일자

2006년12월05일

(73) 특허권자

전자부품연구원

경기도 성남시 분당구 야탑동 68번지

(72) 발명자

김건년

경기도 오산시 부산동 운암주공아파트315-803

이강열

경기도 용인시 기흥읍 구갈리 410-20

(74) 대리인

정종옥 진천웅

조현동

(56) 선행기술조사문헌

KR1020040081310 A \* KR1020020001948 A

\* 심사관에 의하여 인용된 문헌

KR1020050016021 A \* KR1020040047659 A

심사관: 김상걸

전체 청구항 수 : 총 4 항

# (54) 전자소자 패키지 및 그의 제조 방법

#### (57) 요약

본 발명은 전자소자 패키지 및 그의 제조 방법에 관한 것으로, 복수개의 전자 소자들이 형성된 베이스 기판에 다이싱 홈을 형성하고, 다이싱 홈이 형성된 덮개용 기판과 본당한 후, 기계적인 힘에 의해 개별 패키지로 분리시킴으로써, 웨이퍼 단위 로 일괄 공정을 수행하여 공정을 단순화시킬 수 있는 효과가 있다.

#### 대표도

도 5e

# 특허청구의 범위

### 청구항 1.

삭제

# 청구항 2.

삭제

#### 청구항 3.

삭제

#### 청구항 4.

삭제

## 청구항 5.

베이스 기판 상부에 복수개의 전자 소자들을 형성하고, 이웃하는 한 쌍의 전자 소자들 사이 각각에, 그 한 쌍의 전자 소자들에 전기적으로 연결되는 전극 라인을 형성하는 단계와;

상기 전극 라인 중심과 대응되는 영역의 베이스 기판 하부에 제 1 다이싱 홈을 형성하고, 상기 각 쌍의 전자 소자들 사이에 대응되는 영역의 베이스 기판 하부에 제 2 다이싱 홈을 형성하는 단계와;

상기 각 쌍의 전자 소자를 각각 내부에 위치시키는 복수개의 홈을 덮개용 기판 하부에 형성하고, 상기 덮개용 기판 상부에 상기 제 1과 2 다이싱 홈과 대응되는 제 3과 4 다이싱 홈들을 형성하고, 상기 제 1 다이싱 홈에 대응되는 제 3 다이싱 홈 양측으로부터 이격된 덮개용 기판 상부에 제 5 다이싱 홈을 형성하는 단계와;

상기 덮개용 기판에 있는 복수개 홈 각각의 내부에 상기 베이스 기판에 형성된 각 쌍의 전자 소자들이 위치되도록, 상기 베이스 기판 상부에 덮개용 기판을 본당하는 단계와;

상기 제 1 내지 5 다이싱 홈에 기계적인 충격을 주어 상기 각각의 전자 소자를 구비한 구조물을 낱개로 분리시키는 단계를 포함하여 구성된 전자소자 패키지의 제조 방법.

#### 청구항 6.

베이스 기판 상부에 상호 이격된 복수개의 홈을 형성하고, 상기 각각의 홈 내부 바닥면에 상호 이격된 한 쌍의 전자 소자들을 형성하고, 상기 한 쌍의 전자 소자들 각각에 전기적으로 연결되는 전극 라인을 한 쌍의 전자 소자들 사이 각각에 형성하는 단계와;

상기 전극 라인 중심과 대응되는 영역의 베이스 기판 하부에 제 1 다이싱 홈을 형성하고, 상기 각 쌍의 전자 소자들 사이에 대응되는 영역의 베이스 기판 하부에 제 2 다이싱 홈을 형성하는 단계와;

상기 제 1과 2 다이싱 홈과 대응되는 제 3과 4 다이싱 홈들을 덮개용 기판 상부에 형성하고, 상기 제 1 다이싱 홈에 대응되는 제 3 다이싱 홈 양측으로부터 이격된 덮개용 기판 상부에 제 5 다이싱 홈을 형성하는 단계와;

상기 베이스 기판 상부에 덮개용 기판을 본딩하는 단계와;

상기 제 1 내지 5 다이싱 홈에 기계적인 충격을 주어 상기 각각의 전자 소자를 구비한 구조물을 낱개로 분리시키는 단계를 포함하여 구성된 전자소자 패키지의 제조 방법.

#### 청구항 7.

제 5 항 또는 제 6 항에 있어서,

상기 베이스 기판은 반도체 기판이고.

상기 전자 소자는 반도체 기판에 집적된 소자인 것을 특징으로 하는 전자소자 패키지의 제조 방법.

### 청구항 8.

제 5 항 또는 제 6 항에 있어서,

상기 전자 소자는,

센싱(Sensing) 소자인 것을 특징으로 하는 전자소자 패키지의 제조 방법.

#### 명세서

#### 발명의 상세한 설명

### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 전자소자 패키지 및 그의 제조 방법에 관한 것으로, 보다 상세하게는 복수개의 전자 소자들이 형성된 베이스 기판에 다이싱 홈을 형성하고, 다이싱 홈이 형성된 덮개용 기판과 본당한 후, 기계적인 힘에 의해 개별 패키지로 분리시킴으로써, 웨이퍼 단위로 일괄 공정을 수행하여 공정을 단순화시킬 수 있는 전자소자 패키지 및 그의 제조 방법에 관한 것이다.

일반적으로, 전자 소자는 베이스 기판에 복수개로 형성하고, 복수개로 형성된 전자 소자용 소자를 다이싱(Dicing)하여 낱 개의 칩으로 분리한다.

여기서, 전자 소자는 실리콘 기판과 같은 반도체 기판에 집적해서 형성하는 것을 포함한다.

그 후, 전자 소자를 외부로부터 보호받을 수 있도록 패키징하여 마더 보드(Mother board)에 실장하여 사용한다.

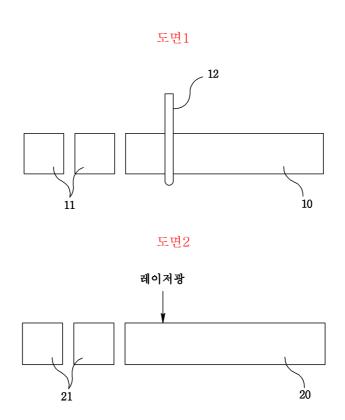

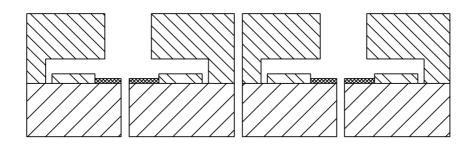

도 1은 종래 기술에 따른 브레이드를 이용한 다이싱(Dicing) 공정을 설명하기 위한 개략적인 단면도로서, 복수개의 전자소자들이 형성된 베이스 기판(10)을 브레이드(12)로 다이싱하여 각각의 낱개의 전자 소자 칩(11)으로 분리한다.

이런, 브레이드를 이용한 다이싱 공정은 수십 ~ 수백 마이크론의 두께를 갖는 원형 브레이드를 회전시켜 베이스 기판을 완전히 절단하여 분리하는 방법이다.

그러므로, 원형 브레이드로 베이스 기판을 절단하기 때문에, 브레이드를 이용한 다이싱 공정은 베이스 기판 및 전자 소자용 소자에 크랙(Crack)과 같은 손상을 부여시켜, 전자 소자용 소자의 특성이 저하되는 문제점이 발생한다.

도 2는 종래 기술에 따른 레이저 다이싱 공정을 설명하기 위한 개략적인 단면도로서, 복수개의 전자 소자들이 형성된 베이스 기판(20)을 레이저 광으로 다이싱하여 각각의 낱개의 전자 소자 칩(21)으로 분리한다.

이 레이저 다이싱 공정은 브레이드를 이용한 다이싱 공정에 비하여, 베이스 기판에 인가되는 충격이 월등히 작기 때문에 최근 많이 이용되고 있다.

한편, 전술된 브레이드 및 레이저를 이용한 다이싱 공정은 열이 많이 발생되어 냉각수를 다이싱 영역에 공급하면서 공정을 수행한다.

그러나, 전술된 다이싱 공정은 공정 중에 절단된 미세 입자와 같은 부산물이 생성되고, 이 미세 입자들이 냉각수를 통해 외부로 버려지기 때문에 오염의 원인이 된다.

그리고, 다이싱의 단면이 불균일하고, 다이싱 두께의 조절이 용이하지 않은 단점이 있다.

또한, 낱개로 분리된 칩이 독자적으로 활용될 수 없기 때문에, 외부의 이물질 및 외력으로부터 칩을 보호하기 위하여, 추가적인 패키징 공정을 수행하는 단점이 있다.

#### 발명이 이루고자 하는 기술적 과제

이에 본 발명은 상기한 바와 같은 문제점을 해결하기 위하여 안출된 것으로, 복수개의 전자 소자들이 형성된 베이스 기판에 다이싱 홈을 형성하고, 다이싱 홈이 형성된 덮개용 기판과 본딩한 후, 기계적인 힘에 의해 개별 패키지로 분리시킴으로써, 웨이퍼 단위로 일괄 공정을 수행하여 공정을 단순화시킬 수 있는 전자소자 패키지 및 그의 제조 방법을 제공하는 데 그목적이 있다.

상기한 본 발명의 목적을 달성하기 위한 바람직한 제 1 양태(樣態)는,

베이스 기판과;

상기 베이스 기판 상부에 형성된 전자 소자와;

상기 전자 소자에 전기적으로 연결되고, 상기 전자 소자의 측면으로 인출된 전극 라인과;

하부에 홈이 형성되어 있으며, 이 홈 내부에 전자 소자를 위치시키고, 상기 전극 라인의 일부를 노출시키며 상기 베이스 기판에 본딩되어 있는 덮개용 기판을 포함하여 이루어진 전자소자 패키지가 제공된다.

상기한 본 발명의 목적을 달성하기 위한 바람직한 제 2 양태(樣態)는,

상부에 홈이 형성되어 있는 베이스 기판과;

상기 베이스 기판의 홈 내부 바닥면에 형성된 전자 소자와;

상기 전자 소자에 전기적으로 연결되고, 상기 전자 소자의 측면으로 인출된 전극 라인과;

상기 전극 라인의 일부를 노출시키며 상기 베이스 기판에 본딩되어 있는 덮개용 기판을 포함하여 이루어진 전자소자 패키지가 제공된다.

상기한 본 발명의 목적을 달성하기 위한 바람직한 제 3 양태(樣態)는,

베이스 기판 상부에 복수개의 전자 소자들을 형성하고, 이웃하는 한 쌍의 전자 소자들 사이 각각에 그 한 쌍의 전자 소자들에 전기적으로 연결되는 전극 라인을 형성하는 단계와;

상기 전극 라인 중심과 대응되는 영역의 베이스 기판 하부에 제 1 다이싱 홈을 형성하고, 상기 각 쌍의 전자 소자들 사이에 대응되는 영역의 베이스 기판 하부에 제 2 다이싱 홈을 형성하는 단계와;

상기 각 쌍의 전자 소자를 각각 내부에 위치시키는 복수개의 홈을 덮개용 기판 하부에 형성하고, 상기 덮개용 기판 상부에 상기 제 1과 2 다이싱 홈과 대응되는 제 3과 4 다이싱 홈들을 형성하고, 상기 제 1 다이싱 홈에 대응되는 제 3 다이싱 홈 양측으로부터 이격된 덮개용 기판 상부에 제 5 다이싱 홈을 형성하는 단계와;

상기 덮개용 기판에 있는 복수개 홈 각각의 내부에 상기 베이스 기판에 형성된 각 쌍의 전자 소자들이 위치되도록, 상기 베이스 기판 상부에 덮개용 기판을 본당하는 단계와;

상기 제 1 내지 5 다이싱 홈에 기계적인 충격을 주어 상기 각각의 전자 소자를 구비한 구조물을 낱개로 분리시키는 단계를 포함하여 구성된 전자소자 패키지의 제조 방법이 제공된다.

상기한 본 발명의 목적을 달성하기 위한 바람직한 제 4 양태(樣態)는,

베이스 기판 상부에 상호 이격된 복수개의 홈을 형성하고, 상기 각각의 홈 내부 바닥면에 상호 이격된 한 쌍의 전자 소자들을 형성하고, 상기 한 쌍의 전자 소자들 각각에 전기적으로 연결되는 전극 라인을 한 쌍의 전자 소자들 사이 각각에 형성하는 단계와;

상기 전극 라인 중심과 대응되는 영역의 베이스 기판 하부에 제 1 다이싱 홈을 형성하고, 상기 각 쌍의 전자 소자들 사이에 대응되는 영역의 베이스 기판 하부에 제 2 다이싱 홈을 형성하는 단계와;

상기 제 1과 2 다이싱 홈과 대응되는 제 3과 4 다이싱 홈들을 덮개용 기판 상부에 형성하고, 상기 제 1 다이싱 홈에 대응되는 제 3 다이싱 홈 양측으로부터 이격된 덮개용 기판 상부에 제 5 다이싱 홈을 형성하는 단계와;

상기 베이스 기판 상부에 덮개용 기판을 본당하는 단계와;

상기 제 1 내지 5 다이싱 홈에 기계적인 충격을 주어 상기 각각의 전자 소자를 구비한 구조물을 낱개로 분리시키는 단계를 포함하여 구성된 전자소자 패키지의 제조 방법이 제공된다.

#### 발명의 구성

이하, 첨부된 도면을 참조하여 본 발명의 바람직한 실시예를 설명하면 다음과 같다.

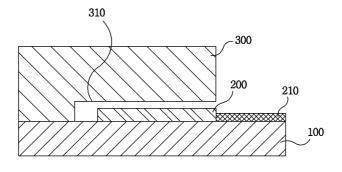

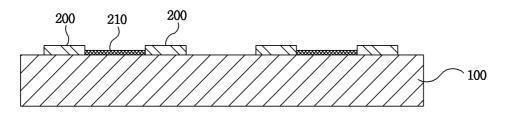

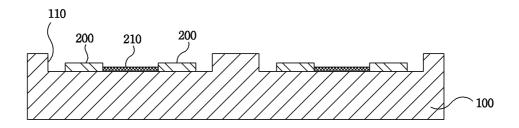

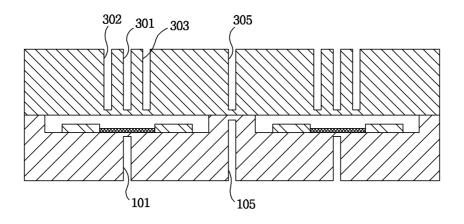

도 3은 본 발명의 제 1 실시예에 따른 전자소자 패키지의 단면도로서, 베이스 기판(100)과; 상기 베이스 기판(100) 상부에 형성된 전자 소자(200)와; 상기 전자 소자(200)에 전기적으로 연결되고, 상기 전자 소자(200)의 측면으로 인출된 전극 라인(210)과; 하부에 홈(110)이 형성되어 있으며, 이 홈(110) 내부에 전자 소자(200)를 위치시키고, 상기 전극 라인(210)의 일부를 노출시키며 상기 베이스 기판(100)에 본딩되어 있는 덮개용 기판(300)으로 구성된다.

이렇게 구성된 본 발명의 전자 소자 패키지는 베이스 기판(100)에 형성된 전자 소자(200)를 덮개용 기판(300)을 베이스 기판(100)에 본딩하여 구성함으로써, 패키지 구성을 단순화시킬 수 있다.

그리고, 상기 베이스 기판(100)은 반도체 기판이고, 상기 전자 소자는 반도체 기판에 집적된 소자인 것이 바람직하다.

또한, 상기 전자 소자(200)는 센싱(Sensing) 소자가 바람직하다.

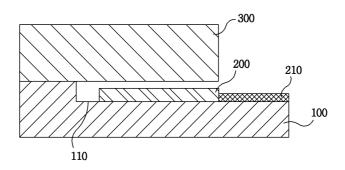

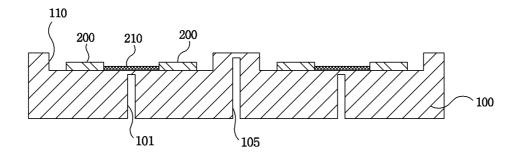

도 4는 본 발명의 제 2 실시예에 따른 전자 소자 패키지의 단면도로서, 상부에 홈(110)이 형성되어 있는 베이스 기판(100)과; 상기 베이스 기판(100)의 홈(110) 내부 바닥면에 형성된 전자 소자(200)와; 상기 전자 소자(200)에 전기적으로 연결되고, 상기 전자 소자(200)의 측면으로 인출된 전극 라인(210)과; 상기 전극 라인(210)의 일부를 노출시키며 상기 베이스 기판(100)에 본딩되어 있는 덮개용 기판(300)으로 구성된다.

도 5a 내지 5e는 본 발명의 제 1 실시예에 따른 전자 소자 패키지의 제조 공정을 설명하기 위한 단면도로서, 먼저, 도 5a에 도시된 바와 같이, 베이스 기판(100) 상부에 복수개의 전자 소자(200)들을 형성하고, 이웃하는 한 쌍의 전자 소자들 사이 각각에 그 한 쌍의 전자 소자들에 전기적으로 연결되는 전극 라인(210)을 형성한다.

여기서, 상기 전자 소자들은 상기 베이스 기판에 집적된 소자들인 것이 바람직하다.

그리고. 상기 베이스 기판은 반도체 기판이 바람직하다.

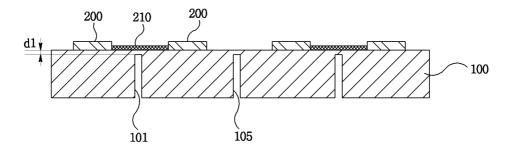

그 후, 상기 전극 라인(210) 중심과 대응되는 영역의 베이스 기판(100) 하부에 제 1 다이싱 홈(101)을 형성하고, 상기 각 쌍의 전자 소자들 사이에 대응되는 영역의 베이스 기판(100) 하부에 제 2 다이싱 홈(105)을 형성한다.(도 5b)

이 때, 상기 다이싱 홈에서 상기 베이스 기판 상부면까지의 두께(d1)는 그 영역이 인가된 기계적인 충격에 절단되도록 얇게 형성한다.

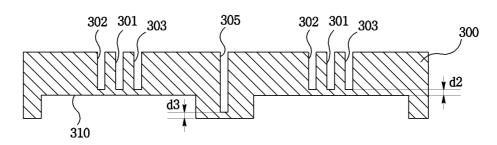

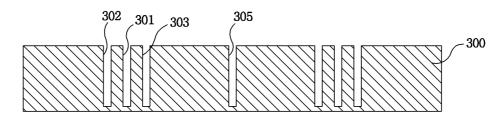

연이어, 상기 각 쌍의 전자 소자(200)를 각각 내부에 위치시키는 복수개의 홈(310)을 덮개용 기판(300) 하부에 형성하고, 상기 덮개용 기판(300) 상부에 상기 제 1과 2 다이싱 홈(101,105)과 대응되는 제 3과 4 다이싱 홈(301,305)들을 형성하고, 상기 제 1 다이싱 홈(101)에 대응되는 제 3 다이싱 홈(301) 양측으로부터 이격된 덮개용 기판(300) 상부에 제 5 다이싱 홈(302,303)을 형성한다.(도 5c)

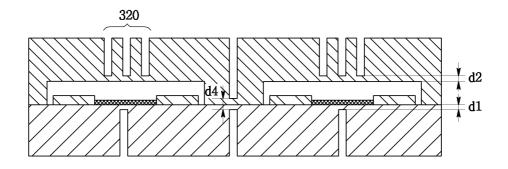

그 다음, 상기 덮개용 기판(300)에 있는 복수개 홈(310) 각각의 내부에 상기 베이스 기판(100)에 형성된 각 쌍의 전자 소자들이 위치되도록, 상기 베이스 기판(100) 상부에 덮개용 기판(300)을 본당한다.(도 5d)

한편, 도 5c와 5d의 도면에 도시된 바와 같이, 'd2,d3,d4'는 그 영역이 인가된 기계적인 충격에 절단되도록 얇게 형성한다.

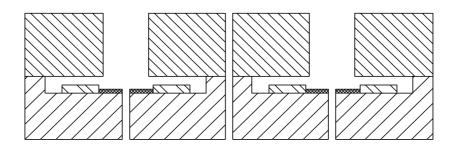

마지막으로, 상기 제 1 내지 5 다이싱 홈(101,105,301,302,303,305)에 기계적인 충격을 주어 상기 각각의 전자 소자 (200)를 구비한 구조물을 낱개로 분리시킨다.(도 5e)

이런 기계적인 충격으로, 도 5d의 '320'영역은 쉽게 절단되어 구조물로부터 분리된다.

이와 같이, 본 발명의 전자 소자 패키징 공정은 복수개의 전자 소자들이 형성된 베이스 기판을 다이싱하여 개별의 칩으로 분리한 후 분리된 개별의 칩을 각각 패키징하는 종래기술과는 다르게, 복수개의 전자 소자들이 형성된 베이스 기판에 다이 싱 홈을 형성하고, 다이싱 홈이 형성된 덮개용 기판과 본당한 후, 기계적인 힘에 의해 개별 패키지로 분리시킴으로써, 웨이 퍼 단위로 일괄 공정을 수행하여 공정을 단순화시킬 수 있는 장점이 있다.

도 6a 내지 6e는 본 발명의 제 2 실시예에 따른 전자 소자 패키지의 제조 공정을 설명하기 위한 단면도로서, 먼저, 베이스 기판(100) 상부에 상호 이격된 복수개의 홈(110)을 형성하고, 상기 각각의 홈(110) 내부 바닥면에 상호 이격된 한 쌍의 전자 소자들(200)을 형성하고, 상기 한 쌍의 전자 소자들(200) 각각에 전기적으로 연결되는 전국 라인(210)을 한 쌍의 전자 소자들 사이 각각에 형성한다.(도 6a)

연이어, 상기 전극 라인(210) 중심과 대응되는 영역의 베이스 기판(100) 하부에 제 1 다이싱 홈(101)을 형성하고, 상기 각쌍의 전자 소자들 사이에 대응되는 영역의 베이스 기판(100) 하부에 제 2 다이싱 홈(105)을 형성한다.(도 6b)

그 후, 상기 제 1과 2 다이싱 홈(101,105)과 대응되는 제 3과 4 다이싱 홈(301,305)들을 덮개용 기판(300) 상부에 형성하고, 상기 제 1 다이싱 홈(101)에 대응되는 제 3 다이싱 홈(301) 양측으로부터 이격된 덮개용 기판(300) 상부에 제 5 다이싱 홈(302,303)을 형성한다.(도 6c)

그 다음, 상기 베이스 기판(100) 상부에 덮개용 기판(300)을 본딩한다.(도 6d)

마지막으로, 상기 제 1 내지 5 다이싱 홈(101,105,301,302,303,305)에 기계적인 충격을 주어 상기 각각의 전자 소자 (200)를 구비한 구조물을 낱개로 분리시킨다.(도 6e)

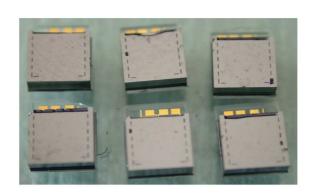

전술된 바와 같이, 본 발명의 제 1과 2 실시예에 의한 공정으로 도 7과 같은 개별의 전자 소자 패키지를 제조할 수 있게 된다.

#### 발명의 효과

본 발명은 복수개의 전자 소자들이 형성된 베이스 기판에 다이싱 홈을 형성하고, 다이싱 홈이 형성된 덮개용 기판과 본당한 후, 기계적인 힘에 의해 개별 패키지로 분리시킴으로써, 웨이퍼 단위로 일괄 공정을 수행하여 공정을 단순화시킬 수 있는 효과가 발생한다.

본 발명은 구체적인 예에 대해서만 상세히 설명되었지만 본 발명의 기술사상 범위 내에서 다양한 변형 및 수정이 가능함은 당업자에게 있어서 명백한 것이며, 이러한 변형 및 수정이 첨부된 특허청구범위에 속함은 당연한 것이다.

#### 도면의 가단한 설명

도 1은 종래 기술에 따른 브레이드를 이용한 다이싱(Dicing) 공정을 설명하기 위한 개략적인 단면도

도 2는 종래 기술에 따른 레이저 다이싱 공정을 설명하기 위한 개략적인 단면도

도 3은 본 발명의 제 1 실시예에 따른 전자소자 패키지의 단면도

도 4는 본 발명의 제 2 실시예에 따른 전자 소자 패키지의 단면도

도 5a 내지 5e는 본 발명의 제 1 실시예에 따른 전자 소자 패키지의 제조 공정을 설명하기 위한 단면도

도 6a 내지 6e는 본 발명의 제 2 실시예에 따른 전자 소자 패키지의 제조 공정을 설명하기 위한 단면도

도 7은 본 발명에 따라 제조되어 분리된 개별 전자 소자 패키지의 사진도

<도면의 주요부분에 대한 부호의 설명>

100 : 베이스 기판

101,105,301,302,303,305 : 다이싱 홈

110,310 : 홈 200 : 전자소자

210 : 전극라인 300 : 덮개용 기판

#### 도면

# 도면3

도면4

도면5a

도면5b

도면5c

# 도면5d

도면5e

도면6a

도면6b

도면6c

# 도면6d

도면6e

도면7