(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4975038号

(P4975038)

(45) 発行日 平成24年7月11日(2012.7.11)

(24) 登録日 平成24年4月20日(2012.4.20)

(51) Int.Cl.

F 1

|                    |                  |             |         |

|--------------------|------------------|-------------|---------|

| <b>H03K 17/687</b> | <b>(2006.01)</b> | H03K 17/687 | A       |

| <b>H03K 17/78</b>  | <b>(2006.01)</b> | H03K 17/78  | E       |

| <b>G09G 3/20</b>   | <b>(2006.01)</b> | G09G 3/20   | 6 4 1 A |

| <b>G09G 3/32</b>   | <b>(2006.01)</b> | G09G 3/20   | 6 1 1 H |

|                    |                  | G09G 3/32   | A       |

請求項の数 15 (全 11 頁)

(21) 出願番号 特願2008-538478 (P2008-538478)

(86) (22) 出願日 平成18年11月1日 (2006.11.1)

(65) 公表番号 特表2009-515405 (P2009-515405A)

(43) 公表日 平成21年4月9日 (2009.4.9)

(86) 國際出願番号 PCT/IB2006/054038

(87) 國際公開番号 WO2007/054856

(87) 國際公開日 平成19年5月18日 (2007.5.18)

審査請求日 平成21年10月30日 (2009.10.30)

(31) 優先権主張番号 05110481.8

(32) 優先日 平成17年11月8日 (2005.11.8)

(33) 優先権主張国 歐州特許庁 (EP)

(73) 特許権者 590000248

コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ

オランダ国 5 6 2 1 ベーーー アインドーフェン フルーネヴァウツウェッハ

1

(74) 代理人 100087789

弁理士 津軽 進

(74) 代理人 100122769

弁理士 笛田 秀仙

(72) 発明者 ニーセン パトリック セー イエー ヘー

オランダ エヌエルー 5 6 5 6 アーーー

アイントホーフェン プロフ ホルスト

ラーン 6

最終頁に続く

(54) 【発明の名称】回路装置および回路装置の駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

回路装置であって、

この回路装置に電流を供給する電源のための接続部と、

少なくとも1つの第1電気デバイスおよびこれと直列に接続された少なくとも1つの第2電気デバイスと、

少なくともゲート、ソースおよびドレインを有し、ドレインおよびソースにより前記第1電気デバイスと並列に接続された、前記第1電気デバイスを制御するための、少なくとも1つの半導体スイッチと、

半導体スイッチに第1制御信号を供給すると共に、第2電気デバイスに第2制御信号を供給するように構成された制御ユニットと、を備え、

前記第2電気デバイスは、回路装置を使用する際の電流の方向において、前記第1電気デバイスおよび前記半導体スイッチの下流側に位置し、

少なくとも1つの電気部品が、ゲートとソースとの間に設けられており、この電気部品を通して電流が送られるとき、この電気部品の両端間に電圧差が発生し、

更に第1制御信号は、前記ゲートおよび前記電気部品への第1制御電流信号を含み、

第1制御電流信号は、実質的に前記電流に付加され、増加した電流を供給し、

制御ユニットは、付加された第1制御電流の影響を補正するように、第1制御信号に応じて第2制御信号を適応させるように構成されている回路装置。

## 【請求項 2】

10

20

半導体スイッチが、絶縁ゲートトランジスタスイッチからなる、請求項 1 記載の回路装置。

**【請求項 3】**

絶縁ゲートトランジスタスイッチは、J F E T または M O S F E T を含む、請求項 2 記載の回路装置。

**【請求項 4】**

電気部品は、抵抗器を含む、請求項 1 乃至 3 のいずれか 1 項に記載の回路装置。

**【請求項 5】**

前記抵抗は、 $0.5 \sim 500\text{ k}\Omega$  の値、好ましくは $1 \sim 100\text{ k}\Omega$  の値を有する、請求項 4 記載の回路装置。 10

**【請求項 6】**

第 2 電気デバイスは、前記第 2 電気デバイスを制御するための追加絶縁ゲート半導体スイッチを備え、このスイッチは少なくともゲート、ソースおよびドレインを備え、ドレンおよびソースにより前記第 2 電気デバイスと並列に接続されている、請求項 1 乃至 5 のいずれか 1 項に記載の回路装置。

**【請求項 7】**

第 1 および / または第 2 電気デバイスは、L E D を備える、請求項 1 乃至 6 のいずれか 1 項に記載の回路装置。

**【請求項 8】**

第 1 および / または第 2 制御信号は、あるデューティサイクルを有するパルス幅変調された電流信号からなる、請求項 1 乃至 7 のいずれか 1 項に記載の回路装置。 20

**【請求項 9】**

第 2 制御信号のデューティサイクルは、第 1 制御信号に依存する、請求項 8 記載の回路装置。

**【請求項 10】**

直列に接続された複数の第 1 および第 2 電気デバイスと、複数の第 1 および第 2 電気デバイスのうちの 1 つ以上と各々並列に接続された複数の半導体スイッチと、を備え、

制御ユニットは、半導体スイッチの各々にそれぞれ制御信号を供給するように構成されており、各制御信号は、前記電流に付加される制御電流信号を含み、

制御ユニットは、個々の半導体スイッチの上流側にあるすべての半導体スイッチに対するそれぞれの制御信号のすべてに依存して、付加された制御電流信号の影響を補正するよう、各個々の半導体スイッチのそれぞれの制御信号を適応させるように構成されている、請求項 1 乃至 9 のいずれか 1 項に記載の回路装置。 30

**【請求項 11】**

直列に接続された第 1 、第 2 および第 3 電気デバイスを備え、電気デバイスの各々は、それぞれこれらデバイスに対して並列に接続された第 1 、第 2 および第 3 半導体スイッチを備え、前記第 1 、第 2 および第 3 半導体スイッチは、制御ユニットからそれぞれの第 1 、第 2 および第 3 制御信号を受け取り、

第 1 制御信号は、第 1 制御電流信号を含み、この第 1 制御電流信号は実質的に前記電流に付加され、増加した電流を供給し。 40

第 2 制御信号は、第 2 制御電流信号を含み、この第 2 制御電流信号は実質的に前記電流に付加され、増加した電流を供給し、

制御ユニットは、付加された第 1 制御電流の影響を補正するように、第 1 制御信号に応じて第 2 制御信号を適応させるように構成され、

制御ユニットは、付加された第 2 制御電流の影響を補正するように、第 2 制御信号に応じて第 3 制御信号を適応させるように構成されている、請求項 1 乃至 10 のいずれか 1 項に記載の回路装置。

**【請求項 12】**

回路装置を駆動する方法であって、

回路装置が、少なくとも 1 つの第 1 電気デバイスおよびこれと直列に接続された少なく 50

とも 1 つの第 2 電気デバイスを備えており、第 1 電気デバイスが半導体スイッチにより制御され、半導体スイッチが、少なくともゲート、ソースおよびドレインを有し、ドレインおよびソースにより、前記第 1 電気デバイスと並列に接続され、回路装置を使用する際の電流の方向において、前記第 2 電気デバイスが前記第 1 電気デバイスおよび前記半導体スイッチの下流側に位置するように構成されており、

前記方法は、

半導体スイッチを切り換える第 1 制御信号を前記ゲートと前記ソースとの間に供給して、第 1 電気デバイスを制御するステップを備え、

第 1 制御信号は、第 1 制御電流信号を含み、第 1 制御電流信号は、実質的に前記電流に付加され、増加した電流を供給し、

更に、第 2 制御信号を供給して、前記第 2 電気デバイスを制御するステップを備え、

第 2 制御信号は、付加された第 1 制御電流の影響を補正するように、第 1 制御信号に応じて決定される、回路装置の駆動方法。

#### 【請求項 1 3】

回路装置が、請求項 1 乃至 1 0 のいずれか 1 項に記載の回路装置である、請求項 1 2 記載の方法。

#### 【請求項 1 4】

第 1 制御信号を供給するステップは、ゲートとソースとの間に抵抗要素を設けて、この抵抗要素を通して電流信号を供給することを含み、

電流信号の値に応じて第 2 制御信号を決定する、請求項 1 2 または 1 3 記載の方法。

#### 【請求項 1 5】

直列に接続された複数の第 1 および第 2 電気デバイスだけでなく、これら複数の第 1 および第 2 電気デバイスのうちの 1 つ以上と各々並列に接続されている複数の半導体スイッチが設けられており、各半導体スイッチはそれぞれの制御信号を受け取り、各制御信号は、前記電流に付加される制御電流信号を含み、

各個々の半導体スイッチのそれぞれの制御信号は、付加された制御電流信号の影響を補正するように、前記個々の半導体スイッチの上流側のすべての半導体スイッチに対するそれぞれの制御信号のすべてに応じて決定される、請求項 1 2 乃至 1 4 のいずれか 1 項に記載の方法。

#### 【発明の詳細な説明】

30

#### 【技術分野】

#### 【0 0 0 1】

本発明は回路装置に関し、この回路装置は、回路装置に電流を供給する電源のための接続部と、互いに直列に接続された少なくとも 1 つの第 1 電気デバイスおよび少なくとも 1 つの第 2 電気デバイスと、少なくともゲート、ソースおよびドレインを有しており、ドレインおよびソースにより前記第 1 電気デバイスと並列に接続された、前記第 1 電気デバイスを制御するための少なくとも 1 つの半導体スイッチと、前記半導体スイッチに第 1 制御信号を供給すると共に、前記第 2 電気デバイスに第 2 制御信号を供給するようになっている制御ユニットとを備え、前記第 2 電気デバイスが、前記回路装置を使用する際の電流の方向において、前記第 1 電気デバイスおよび前記半導体スイッチの下流側に存在する。

40

#### 【背景技術】

#### 【0 0 0 2】

トランジスタで制御される電気デバイスを直列接続することは周知である。例えば米国特許第 6,153,980 号は、アクティブ分路スイッチ装置を有する L E D アレイを開示しており、このスイッチ装置では、直列に接続された複数の L E D の各々は L E D の両端に接続されたパワー M O S F E T のようなアクティブ分路（短絡）を有する。各分路（短絡）スイッチにはデジタルロジックが接続されており、このデジタルロジックはアクティブ分路を順次に附勢するように働く。

#### 【0 0 0 3】

電気デバイスを直列接続することは、各デバイスを通過する電流が同じとなるという点

50

で有効である。多くのタイプの電気デバイスの性能は電流に依存しているので、このような直列接続はデバイスに対する電気作動条件を設定するための有効な特徴となっている。

#### 【発明の開示】

##### 【発明が解決しようとする課題】

##### 【0004】

電気デバイスの直列接続された回路装置内でアクティプ半導体スイッチを使用すると、次のような問題が生じる。すなわち、この半導体デバイスはソースおよびドレインで1つ又はそれ以上の電気デバイスと並列に接続されており、ゲートはそのように接続されていない。閉状態または開状態となるには（すなわち、電気デバイスを分路するかどうかを決定するためには）、スイッチは、そのゲートとソースとの間に所定の電圧差を必要とする。しかしながら、個々の半導体スイッチのソースの電圧は個々の半導体スイッチの上流側にある電気デバイスの状態、特に個々の半導体スイッチの上流部にある他の半導体スイッチの状態に応じて決まる。従って、単に特定の電圧をゲートに印加することに頼るだけでは、上記電圧差は良好に定められた値とはならず、このことが欠点となっている。例えば半導体スイッチの一部が導通状態となる場合もあり、このことはスイッチで望ましくないエネルギー損失があること、すなわち意図しない状況であることを意味する。

##### 【0005】

本発明の目的は、半導体スイッチで制御される電気デバイスの性能の制御を改良できる、冒頭記載のタイプの回路装置を提供することにある。

##### 【課題を解決するための手段】

##### 【0006】

前記目的は、本発明によれば、上述のタイプの回路装置によって達成され、ゲートとソースとの間に少なくとも1つの電気部品が設けられ、前記部品を通して電流が送られる、前記電気部品の両端に電圧差が発生し、更に前記第1制御信号は前記ゲートおよび前記電気部品への制御電流信号を含み、前記制御ユニットは、前記第1制御信号に応じて前記第2制御信号を適応させるようになっている。

##### 【0007】

通常、電気部品を横切って電流を供給することによって、良好に定められた電圧差を提供する方法は、直列接続内の各デバイスに対する電流が等しくなるという上記利点と対立する。その理由は、半導体スイッチのソース - ドレイン接続と電気デバイスとの並列接続部を通過する電流に、必ず電気部品の電流が加わるからである。本発明によれば、半導体スイッチの両端間に良好に定められた電圧差を発生させるローカルフローティング電圧を利用する一方で、制御ユニットに、当該スイッチの下流側にある各半導体スイッチに対する制御電流を適応させることによって、電気部品を通り且つ電気デバイスの直列接続内に流れる電流の効果を補正する。このフローティング電圧は、特に多数のデバイスが直列接続されている場合に有効である。その理由は、本発明を使用しない場合、上流側の制御信号に応じて絶対電圧が変化するので、ドランジスタのための良好に定められたソース電圧を供給することが次第に困難となるからである。

##### 【0008】

スイッチのソースまたはドレインに単に絶対的電圧を供給することは信頼性がないことに留意されたい。その理由は、多くの電気デバイスが直列に接続されている場合（例えば多くのマルチL E D アプリケーションの場合）、前記電圧の絶対値は、L E D の数にL E D の電圧を乗算した値となり、この値は数百ボルトにもなり得るからである。このことは、例えば仕様または安全基準の理由で、多くの半導体スイッチに対しては許容されない。

##### 【0009】

本発明によれば、下流側に直列接続されている電気デバイスでのこの余分な電流の効果が分かる。というのは、この効果は既知である電気部品の特性および電流信号だけに依存しているからである。従って、制御ユニットは、下流側の電流への上流側の電流信号の効果を予測することが可能である。下流側スイッチに対する制御電流は、ある知識（例えばルックアップテーブル）に依存して適応される。他の方法についても後述する。

10

20

30

40

50

**【0010】**

電源への接続を提供すれば十分であるが、電源を設け、電源を含むようにすれば、より好ましい。この電源は実質的に一定の電流を供給する電流源を含むことが好ましい。

**【0011】**

本発明では、原則として各タイプの半導体スイッチ、例えばバイポーラトランジスタ等を使用できる。しかしながら、本発明は半導体スイッチが絶縁ゲートトランジスタスイッチを含むような回路装置に対して極めて有利である。特に、この絶縁ゲートトランジスタスイッチはJ F E TまたはM O S F E Tを含む。これらの場合、トランジスタが非導通状態から導通状態（またはその逆）に切り替わるには、まずゲート - ソース間の容量を充電（または放電）しなければならないので、これらスイッチの立ち上がり時間がゲートとソースの間の電流に依存するという点で、これらの効果および利点がより明らかとなる。供給される電流が極めて小さいとき、このスイッチングには比較的長い時間がかかることがあるので、これは望ましくない。後述するように、所望するスイッチ特性が得られるようには回路設計を適応させることができるようにすることによって、本発明はこの時間を良好に制御できる。ここでは当然ながら電流信号は、両端間に電圧を発生する電気部品と半導体スイッチのゲートとに分路されることに注目されたい。しかしながら、ほとんどすべてのケースでは、ゲート（リーク）電流は電気部品を通過する電流よりもかなり小さいので、特定のすべての実用的目的に対し、ゲート電流を無視できる。しかしながら、例えばバイポーラトランジスタの場合、ゲート電流を含めなければならないことが多い。全制御電流に対するゲート電流の寄与分の補正は、トランジスタの特性に応じて行うことができる。以下、好ましい実施形態の説明において、このことを詳述する。

**【0012】**

前記少なくとも1つの電気部品とは、別の部品であることを意味し、物理的に別でない固有の部品、例えば浮遊容量ではないことに留意されたい。

**【0013】**

特別な実施形態では、電気部品は抵抗器からなる。これは極めて簡単で、小型且つ安価な特徴的部品であり、（制御）電流が通過する際に両端間に電圧を発生するという義務を果たす。この電圧は他の受動的部品、例えばコンデンサ、インダクタンスと比較して極めて良好に制御できるが、これらの使用を排除するものではない。

**【0014】**

特に抵抗器は0.5 ~ 500K の間の抵抗値、好ましくは1 ~ 100K の間の抵抗値を有する。このような値の抵抗の場合、スイッチが十分高速で開閉することを容易に補償できる。換言すれば、信頼できる作動をするのに立ち上がり時間を十分短くできる。

**【0015】**

特別な実施形態では、第2電気デバイスは、前記第2電気デバイスを制御するための追加絶縁ゲート半導体スイッチを備え、このスイッチは少なくともゲート、ソースおよびドレインを備え、ドレインおよびソースにより第2電気デバイスと並列に接続されている。このような回路構造は、同じ制御ユニットで、かつ第1電気デバイスと同じように、第2電気デバイスを制御できるという利点を有する。他の制御方法だけでなく、他の制御ユニットも使用が可能であることに留意されたい。更に、本明細書で使用する「制御ユニット」なる表現には、種々の電気デバイスを制御するための複数の別個の制御ユニットも含まれると見なすべきである。

**【0016】**

特別な実施形態では、第1および/または第2電気デバイスはL E Dを含む。これらL E Dは多数使用されることが多く、更にL E Dを通る電流にかなり依存するような性能（すなわち、光出力）を有するので、直列接続で使用されることが多い。従って、L E Dの出力をクリティカルに制御することが望ましく、このような制御は本発明に係る回路装置によって行うことができる。

**【0017】**

特定の実施形態では、第1および/または第2制御信号は、あるデューティサイクルを

10

20

30

40

50

有するパルス幅変調された（P W M）電流信号からなる。当業者に知られているように、パルス幅変調信号とは、所定の周波数を有し、パルスの強度を決定する制御可能な幅を有する、規則的に発生されるパルスを含む制御信号のことである。この信号はノーマルハイでもよいし、ノーマルロウでもよい。このタイプの制御信号は、ランプを調光できるように使用され、常時同じオン電流を有する。このことは、電気デバイスの特性が、連続的範囲の（電流）条件となる代わりに、2つの状態になるだけでよいという点で好ましい。例えば常時同じオン電流にすることは、ゲート - ソース間の電圧差が他の上流側の制御電流から独立することを保証する。従って、これらスイッチは等しく高速でスイッチングされ、回路装置全体に対しても同じような見解が成り立つ。

## 【0018】

10

特別な実施形態では、第2制御信号のデューティサイクルは、第1制御信号に応じて決まる。このことが本発明で苦心した点であり、ここでは、第2制御信号のデューティサイクルに適応するために、例えば、第1制御信号の瞬間値（第2制御信号の極めて高速の適応を行うため）、または第1制御信号の平均値またはデューティサイクル（第2制御信号のより低速の適応を行うため）を使用する。パルス幅変調では、信号の値が標準的な値でない時間の割合を示すのに、デューティサイクルが使用される。例えばノーマルロウ信号の場合、周波数が100 H zであると、パルス時間が10 m sで、信号が各パルス中に2 m sの間ハイであると、デューティサイクルは0.2、すなわち20%となる。これは、L E Dをその公称強度の値の20%で駆動したい場合に使用できる。ここで、当該L E Dの上流側にある他の1つのL E Dが異なる強度の値に切り換えられ、そしてこの値が上流側の他のL E Dの異なる制御信号に対応すると仮定する。これは、順次に、異なる制御電流が直列接続内に送られ、従って当該L E Dで検出される全電流が変化することを意味する。従って、当該L E Dへの制御信号の補正が適応されなければならず、制御電流は（少なくとも平均として）大きくまたは小さくしなければならないか、または同じように当該L E Dについてのデューティサイクルが適合されなければならない。

## 【0019】

20

特定の制御信号を適応させるために別の上流側の制御信号を使用する方法は、制限されていない。しばしば、適当な制御信号を決定するのに、上流側の他の制御信号を処理できるコンピュータまたは同様な回路を設けることができる。それに加え、上流側のすべての制御信号を知り、特定のスイッチ / デバイスにどのような制御信号を供給すべきかを記述するような、ルックアップテーブルの形態での回路装置全体の知識を使用してもよい。変形例では、制御ユニットが適当な制御信号を決定できる根拠に基づいて、特定のデバイスについての電流の表示を提供する構成で電流センサデバイスを使用することが可能である。例えば上記ケースの各々において、特定のスイッチ / デバイスに対するP W M信号を適応させてもよい。

## 【0020】

30

特定の実施形態では、本発明の回路装置は、直列に接続された複数の第1および第2電気デバイスと、前記複数の第1および第2電気デバイスのうちの1つ以上と各々が並列に接続された複数の半導体スイッチとを備え、制御ユニットが、前記半導体スイッチの各々にそれぞれの制御信号を供給するようになっており、前記制御ユニットは、前記個々の半導体スイッチの上流側にあるすべての半導体スイッチに対するすべての各制御信号に依存して、各個々の半導体スイッチのそれぞれの制御信号を適応させるようになっている。この実施形態では、より多数のデバイス、特に10個以上または更に50個以上の第1および / または第2デバイス、例えばL E Dを多数のトランジスタによって制御する、より複雑な設定で、本発明の利点を活用できる。特定の利点が、個々の半導体スイッチのゲート - ソース間の適当な電圧差を定めることができることを繰り返す。

## 【0021】

40

各ケースにおいて、单一の第1または第2半導体スイッチにより、1つ以上の第1および / または第2電気デバイスを制御できるので、第1および / または第2半導体スイッチの数は第1および / または第2電気デバイスの数に対応していなくてもよいことに留意さ

50

れたい。電気デバイスが複数のサブデバイスを含むような状況として、この状況で考慮することもできる。

#### 【0022】

特定の実施形態では、この回路装置は、直列に接続された第1、第2および第3電気デバイスを備え、前記電気デバイスの各々は、これらデバイスに対して並列に接続されたそれぞれの半導体スイッチを備え、前記半導体スイッチは、制御ユニットからそれぞれの制御信号を受信でき、個々の半導体スイッチに対する制御信号は、前記個々の半導体スイッチの上流側にあるすべての半導体スイッチに対するそれぞれの制御信号に依存する。好ましくは、第1、第2および第3電気デバイスは、各々異なる色のLEDからなる。例えば、第1デバイスは赤色LEDであり、第2デバイスは緑色LEDであり、第3デバイスは青色LEDである。より好ましくは、この回路装置は第1LED、第2LEDおよび第3LEDと色が異なる色を有する第4LEDを更に含む。これら実施形態は、LED装置の良好な色および強度制御を提供するのに極めて有利である。例えば、赤色LED、緑色LEDおよび青色LEDを有する周知のRGBシステムが使用されている。変形例では、カラーレンダリングを良好にするよう、第4の色を追加され、例えば、アンバーカラーのLEDを追加したRGBAシステムとすることができる。第1～第3または第4の電気デバイスの第1セットに直列および/または並列に接続された第1～第3のまたは更に第4の電気デバイスの1つ以上の追加セットを追加することも可能であることに留意されたい。有利には、追加セットは、本発明に従って接続された半導体スイッチを含む。

10

#### 【0023】

本発明は、少なくとも1つの第1電気デバイスおよび直列に接続された少なくとも1つの第2電気デバイスを備えた回路装置を駆動する方法に関し、少なくともゲート、ソースおよびドレインとを備え、ドレインおよびソースにより前記第1電気デバイスと並列に接続された、第1電気デバイスを制御するための半導体スイッチによる方法であって、前記回路装置を使用する際ににおける電流の方向において、前記第2電気デバイスは前記第1電気デバイスおよび前記半導体スイッチの下流側に位置し、この方法は、前記半導体スイッチを切り換えて前記第1電気デバイスを制御するための第1制御信号を前記ゲートと前記ソースとの間に供給するステップと、前記第2電気デバイスを制御するための第2制御信号を供給するステップを備え、前記第2制御信号は前記第1制御信号に応じて決定されるようになっている。従来の方法に対するこの方法の利点は、本発明の回路装置の利点に対応する。この説明については既に述べたとおりである。特に、この方法は本発明の回路装置に適用できる。

20

#### 【0024】

特定の実施形態では、第1制御信号を供給するステップは、前記ゲートと前記ソースとの間に抵抗要素を設け、この抵抗要素を通して電流信号を供給することを含み、この電流信号の値に応じて第2制御信号を決定する。かかる抵抗要素によって、良好に定められた電流で良好に定められた電圧を提供する、簡単でかつ安価な方法が可能となる。抵抗値を正しく選択することにより、半導体スイッチの立ち上がり時間を十分短くできる。適当な抵抗値は約500～500Kの間、特に約1～100Kの間にある。

30

#### 【0025】

特別な方法では、直列に接続された複数の第1および第2電気デバイスだけでなく、これら複数の第1および第2電気デバイスのうちの1つ以上と各々が並列に接続されている複数の半導体スイッチを設け、各々がそれぞれの制御信号を受け取り、各個々の半導体スイッチのそれぞれの制御信号は、前記個々の半導体スイッチの上流側のすべての半導体スイッチに対するすべての各制御信号に応じて決定される。この実施形態では、より複雑な状況において本発明の方法が実行され、本発明の方法によって上流側の制御信号によって影響を受けるすべてのデバイスに対し、個々に適応され、補正された制御信号を発生できるというすべての利点が得られる。

40

#### 【0026】

添付図面と共に、発明を限定しない実施形態の、次の詳細な説明を読めば、本発明の上

50

記およびそれ以外の目的、特徴および利点がより明らかとなろう。

**【発明を実施するための最良の形態】**

**【0027】**

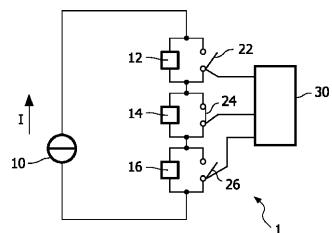

本明細書において番号10は矢印方向の電流Iのための電流源を示す。3つの電気デバイス12、14、16だけでなく、3つのスイッチ22、24、26および制御ユニット30も示されている。ここに示されるように、電流源10は回路装置1内に含まれているが、外部電流源への接続部だけを設けることも可能である。この電流源は特に限定されるものではなく、使用される電気デバイスの電流および電力条件に従って選択できる。

**【0028】**

デバイス12、14、16は、極めて一般的にしか示されておらず、これらのデバイスの数を2個、並びに4個、5個、およびそれ以上の個数とすることもできる。どの電気デバイス12、14、16も、自らのスイッチ22、24、26をそれぞれ有しており、これらスイッチは1つの電気デバイスだけに並列に接続されている。図示されている3つのデバイスに直列および/または並列に追加の電気デバイスを設けることも可能であることに留意されたい。また、これらスイッチ22、24、26の各々は、1つ以上の電気デバイスを制御できる。ここに示されている実施形態は、例えばRGBシステムのための3つの異なるカラーのLEDを備える。

**【0029】**

制御ユニット30は、各スイッチ22、24、26を制御するように示されているが、各々が複数のスイッチ22、24、26のうちの1つ以上を制御する数個の制御サブユニットを有する制御ユニットを設けることもできる。この制御ユニット30は、コンピュータまたは同様な制御回路であることが多い。

**【0030】**

本発明は、スイッチ22、24を制御することが下流のスイッチ24、26の制御に与える効果、およびその制御の補正に関する。

**【0031】**

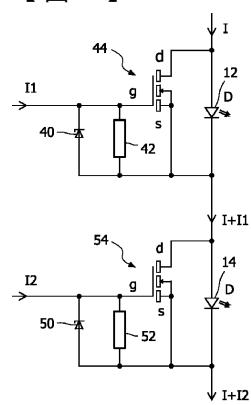

図2は、本発明の回路装置の特定の実施形態を略図で示す。ここで、番号12および14はそれぞれ第1LEDおよび第2LEDであり第1および第2MOSFETスイッチは番号44および54でそれぞれ示されている。各スイッチは図示されるようにゲートg、ドレインdおよびソースsを有する。

**【0032】**

2つのウェナーダイオードおよび2つの抵抗器は、番号40、50および42、52でそれぞれ示されている。

**【0033】**

更に、それぞれの矢印が示すように、メイン電流I、第1制御電流I<sub>1</sub>および第2制御電流I<sub>2</sub>が注入される。

**【0034】**

(図には示されていない)電流源が直列接続されたLEDに電流Iを注入すると仮定し、更にLED12がオンとなっていると仮定すると、この場合、このことは、制御電流I<sub>1</sub>がゼロであることを意味する。すなわちI+I<sub>1</sub>=Iであり、第2LED14は同じ電流を受け取る。

**【0035】**

次に、LED12をオフに切り替えたいと仮定する。この切り替えは、第1スイッチ44内に制御電流I<sub>1</sub>を注入することによって達成できる。制御電流I<sub>1</sub>を注入することにより、抵抗器42の両端間に電圧が発生し、この電圧は同じようにゲートgとソースsとの間に電圧を発生する。すると、スイッチ44の立ち上がり時間後、スイッチ44は導通状態を開始し、LED12を分路(短絡)する。

**【0036】**

この結果、電流IはLEDを通過せず、その代わりに、少なくとも実質的にスイッチ44を通過する。しかしながら、電流IにI<sub>1</sub>が追加されるので、I+I<sub>1</sub>=Iとなる。この

10

20

30

40

50

増加した電流は第 2 LED 14 を通して送られる。このことは、第 1 LED、すなわち上流側の電気デバイスのための制御信号がどの下流側 LED（または電気デバイス）に対しても影響することの明らかな例である。しかしながら、本発明によれば、このことは次のように補正できる。まず、計算を簡単にするために制御電流  $I_1$  は 0.02 I であると仮定し、更に LED 12 および 14 の強度が電流に対して線形依存していると仮定する。換言すれば、ここでは第 2 LED 14 は 2 % 大きい光を発生する。このことは、 $2 / 102 \times 100\% = 2\%$  の時間の間、第 2 LED 14 をオフに切り換えることによって補正できる。対応する PWM 制御信号を、PWM の第 2 制御電流  $I_2$  の形態で第 2 LED 14 に供給してもよい。この第 2 制御電流  $I_2$  は第 1 制御電流  $I_1$  と同じように、第 2 スイッチ 54 に供給できる。

10

#### 【0037】

概してこの結果として、第 1 LED 12 はオフに切り換えられ、一方、第 2 LED 14 は前と同じ強度の光を発光する。当然ながら、互いに完全に独立するように、各 LED 12、14 を制御することも同じように可能である。注入される制御信号  $I_1$ 、 $I_2$  などによる影響を補正するように、第 2 LED 14 の下流側の別のデバイスも同じように制御できることにも留意されたい。更に、余分な制御電流は、制御ユニットへ戻す電気接続（図示せず）により、電流源に再び進入するメイン電流  $I$  から分岐されることにも留意されたい。制御回路を閉じるこの接続を介して制御電流が流れる。

#### 【0038】

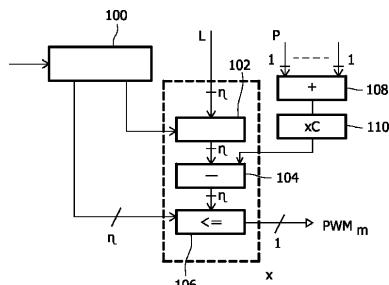

図 3 は、本発明にかかる方法のフローチャートを示す。ここで、番号 100 はカウンターを示し、番号 102 は幅レジスタを示し、番号 104 は減算器を示し、番号 106 はコンパレータを示し、番号 108 は加算器を示し、番号 110 は乗算器を示す。

20

#### 【0039】

簡単に説明すれば、カウンター 100 は、カウントを 0 から  $2^n - 1$  まで繰り返す。この場合、n は使用するビット数、すなわち分解能である。パルス幅変調された信号 PWM m によって制御すべきスイッチ m に対して、所望するパルス幅が、クロック制御されたコードオンキャリー信号を介して（すなわちカウンター 100 から幅レジスタ 102 への矢印）、幅レジスタ 102 へ入力される。また、このパルス幅は n ビットの幅を有していてもよく、この値は LED の所望する強度に基づいていてよい。補正なしのシステムでは、所望するカウンター値でハイ値を発生するように、コンパレータ 106 は、カウンター 100 の値が少なくとも所望するパルス幅に等しくなっているかどうかを判断する。換言すれば、部品 104、当然ながら、部品 108 および 110 は存在しない。

30

#### 【0040】

本発明によれば、この方法が補正される。この場合、上流側のスイッチのすべてのパルス幅変調信号、すなわち PWM 0 ~ PWM (m - 1) が使用される。これらの PWM m に対する信号の効果を組み込むために、加算器 108 でそれらの値を加算し、その後、乗算器 110 内で加算値に補正值 c を乗算する。こうして得られた値を幅レジスタの値から減算する。

#### 【0041】

補正值 c は、例えば、図 2 内の LED 電流  $I$  のようなメイン電流に対する、図 2 における  $I_1$  のようなそれぞれの平均制御電流の比に依存する。この比は LED の強度が電流にリニアに依存するとの仮定に基づく。当然ながら、別のデバイスを使用する場合、別の依存性が有利となる場合があり、異なる補正ファクター c または異なる補正方式も使用することができる。しかしながら、この依存性が既知である限り、制御電流を最適に補正するよう、回路またはプログラムが組み込まれたコンピュータでこのことを実現してもよい。例えばバイポーラトランジスタの場合、このファクター c は、制御電流の一部だけが抵抗要素を通過し、一方、別の部分がゲート電流としてトランジスタを通過するような状況に起因する、補正量を含むことができる。

40

#### 【図面の簡単な説明】

#### 【0042】

50

【図1】本発明にかかる回路装置を略図で示す。

【図2】本発明の回路装置の特定の実施形態の細部を略図で示す。

【図3】本発明にかかる方法のフローチャートを示す。

【符号の説明】

【0043】

|            |            |    |

|------------|------------|----|

| 1          | 回路装置       |    |

| 10         | 電流源        |    |

| 12、14、16   | 電気デバイス     | 10 |

| 22、24、26   | スイッチ       |    |

| 30         | 制御ユニット     |    |

| 40、50      | ツエナーダイオード  |    |

| 42、52      | 抵抗器        |    |

| 44、54      | MOSFETスイッチ |    |

| 100        | カウンター      | 20 |

| 102        | 幅レジスタ      |    |

| 104        | 減算器        |    |

| 106        | コンパレータ     |    |

| 108        | 加算器        |    |

| 110        | 乗算器        |    |

| I          | メイン電流      |    |

| $I_1, I_2$ | 制御電流       |    |

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3

---

フロントページの続き

(72)発明者 クラウト ラモン アー ウェー

オランダ エヌエル-5656 アーアー アイントホーフェン プロフ ホルストラーン 6

審査官 栗栖 正和

(56)参考文献 米国特許出願公開第2005/0243022(US,A1)

実開平01-104754(JP,U)

特開2005-310997(JP,A)

米国特許第6153980(US,A)

(58)調査した分野(Int.Cl., DB名)

H03K 17/00-17/70

H03K 17/78

G09G 3/20

G09G 3/32