## (12) 发明专利

(10) 授权公告号 CN 110709965 B

(45) 授权公告日 2023.05.02

(21) 申请号 201880037037.8

(74) 专利代理机构 永新专利商标代理有限公司

(22) 申请日 2018.05.24

72002

(65) 同一申请的已公布的文献号

专利代理人 吕文卓

申请公布号 CN 110709965 A

(51) Int.CI.

(43) 申请公布日 2020.01.17

H01L 21/301 (2006.01)

(30) 优先权数据

B24B 27/06 (2006.01)

2017-117856 2017.06.15 JP

H01L 21/52 (2006.01)

(85) PCT国际申请进入国家阶段日

(56) 对比文件

2019.12.04

JP 2015053428 A, 2015.03.19

(86) PCT国际申请的申请数据

JP 2007073844 A, 2007.03.22

PCT/JP2018/020005 2018.05.24

JP 2006086509 A, 2006.03.30

(87) PCT国际申请的公布数据

US 2002016047 A1, 2002.02.07

W02018/230297 JA 2018.12.20

JP 2006222359 A, 2006.08.24

(73) 专利权人 株式会社电装

JP 2001127010 A, 2001.05.11

地址 日本爱知县

JP 2001085736 A, 2001.03.30

(72) 发明人 山田骏太郎 神田明典 吉冈彻雄

CN 103515250 A, 2014.01.15

长尾高成 宫下耕一

审查员 杨福华

权利要求书2页 说明书6页 附图8页

## (54) 发明名称

半导体装置及其制造方法

## (57) 摘要

具备具有表面(20a)及背面(20b)的基板(20)、和粘贴于背面(20b)的膜(30)的半导体装置的制造方法，具备如下步骤：向背面(20b)粘贴膜(30)的步骤；将基板(20)与膜(30)一起从背面(20b)进行半切割而形成背面侧槽部(80)的步骤；在形成背面侧槽部(80)的步骤之后对膜(30)粘贴保护部件(90)的步骤；在粘贴保护部件(90)的步骤之后，从表面(20a)进行基板(20)的划片切割而形成与背面侧槽部(80)连结的表面侧槽部(110)的步骤。

1. 一种半导体装置的制造方法，

该半导体装置具备：

基板(20)，具有表面(20a)及背面(20b)；以及

膜(30)，粘贴于上述背面，

该半导体装置的制造方法的特征在于，具备以下步骤：

向上述背面膜粘贴上述膜的步骤；

从上述背面将上述基板与上述膜一起进行半切割而形成背面侧槽部(80)的步骤；

在形成上述背面侧槽部的步骤之后将保护部件(90)向上述膜进行粘贴的步骤；

在粘贴上述保护部件的步骤之后，从上述表面进行上述基板的划片切割而形成与上述背面侧槽部相连结的表面侧槽部(110)的步骤；以及

将键合线(50)与上述表面连接的步骤，

在形成上述表面侧槽部的步骤中，至少进行1次在1个槽部的底部形成与该槽部相比开口宽度小的其他槽部的步骤，使得上述表面侧槽部成为随着朝向上述背面而宽度变窄的台阶形状，

在连接上述键合线的步骤中，使上述键合线穿过通过使上述表面侧槽部成为上述台阶形状从而在上述基板的上述表面与侧面(20c)之间的角部形成的凹部(20e)。

2. 如权利要求1所述的半导体装置的制造方法，其中，

在形成上述背面侧槽部的步骤中，对上述基板进行半切割，使得上述基板中的被上述背面侧槽部和上述表面夹着的部分的抗弯强度高于在形成上述表面侧槽部的步骤中上述基板发生破裂的抗弯强度。

3. 如权利要求1所述的半导体装置的制造方法，其中，

在形成上述表面侧槽部的步骤中，在上述表面形成了第1表面侧槽部(111)之后，在上述第1表面侧槽部的底部形成与上述第1表面侧槽部相比开口宽度小的第2表面侧槽部(112)，使上述第2表面侧槽部与上述背面侧槽部相连结。

4. 如权利要求1所述的半导体装置的制造方法，其中，

在形成上述表面侧槽部的步骤中，与上述背面侧槽部的宽度相比，使上述表面侧的上述其他槽部的宽度较窄。

5. 如权利要求1所述的半导体装置的制造方法，其中，

在形成上述表面侧槽部的步骤中，多次进行在上述1个槽部的底部形成上述其他槽部的处理，与上述背面侧槽部的宽度相比，使上述其他槽部中的与上述背面侧槽部相连结的槽部的宽度较窄。

6. 如权利要求1所述的半导体装置的制造方法，其中，

在形成上述表面侧槽部的步骤中，使上述1个槽部的宽度比上述背面侧槽部的宽度窄。

7. 如权利要求1所述的半导体装置的制造方法，其中，

在形成上述表面侧槽部的步骤中，以使上述基板中的被上述背面侧槽部和形成于上述表面的1个槽部所夹着的部分的抗弯强度高于在该1个槽部的底部形成其他槽部时上述基板发生破裂的抗弯强度的方式，形成该1个槽部。

8. 如权利要求1至7中任一项所述的半导体装置的制造方法，其中，

在形成上述表面侧槽部的步骤中，在划片刀(100, 130)与上述保护部件相分离的状态

下进行划片。

9. 如权利要求1至5中任一项所述的半导体装置的制造方法,其中,

在形成上述表面侧槽部的步骤中,利用划片刀(100,130)进行上述划片切割,

在形成上述背面侧槽部的步骤中,使上述背面侧槽部的深度(H2)大于上述划片刀的圆化了的前端部的长度(H31)。

10. 一种半导体装置,

具备:

基板(20),具有表面(20a)及背面(20b);以及

膜(30),粘贴于上述背面,

该半导体装置的特征在于,

上述表面及上述背面的外周部比内周部凹陷,从而从上述表面的内周部经由上述表面的外周部、上述基板的侧面(20c)、上述背面的外周部而到达上述背面的内周部的部分成为台阶形状,

上述膜被粘贴于上述背面的内周部,

在上述基板的上述表面与上述侧面之间的角部形成有凹部,

与上述表面连接的键合线(50)以穿过上述凹部的方式配置。

11. 如权利要求10所述的半导体装置,其中,

在上述基板的上述表面与上述侧面之间的角部形成有第一凹部(20e),上述表面的外周端部成为比内周部凹陷的形状,该第一凹部成为多级的台阶形状。

12. 如权利要求10所述的半导体装置,其中,

在上述基板的上述背面与上述侧面之间的角部形成有第二凹部(20d),

在上述基板的上述表面与上述侧面之间的角部形成有第一凹部(20e),

在上述基板的上述表面与上述侧面之间的角部形成的上述第一凹部的宽度窄于在上述背面与上述侧面之间的角部形成的上述第二凹部的宽度。

## 半导体装置及其制造方法

[0001] 关联申请的相互参照

[0002] 本申请基于2017年6月15日申请的日本专利申请第2017-117856号,这里通过参照而引入其记载内容。

### 技术领域

[0003] 本公开涉及半导体装置及其制造方法。

### 背景技术

[0004] 以往,作为粘贴有DAF(Die Attach Film:芯片贴装膜)的半导体芯片的制造方法,例如在专利文献1中提出了如下那样的制造方法。即,在该制造方法中,以在晶片背面粘贴有保持用粘接带的状态从表面侧进行半切割,将保持用粘接带重新粘贴于晶片表面后,从晶片背面侧对晶片进行研磨,并将晶片分割为芯片单位。然后,在被分割为芯片单位的晶片的背面粘贴DAF,用拉拽力使DAF中的未被安装于晶片的部分断裂,从而制造在背面粘贴有DAF的半导体芯片。

[0005] 现有技术文献

[0006] 专利文献

[0007] 专利文献1:日本特开2004-193241号公报

[0008] 但是,在专利文献1所记载的方法中,需要将DAF切断为与晶片相同的形状,并正确地粘贴于晶片。另外,由于以在晶片的表面侧粘贴有保持用粘接带的状态粘贴DAF,因此通过DAF粘贴时的晶片的加热,保持用粘接带的粘接层的流动性增加从而粘接力增加,保持用粘接带的剥离有可能变困难。

[0009] 另外,在用拉拽力使DAF断裂时,保持用粘接带有可能发生松弛。作为避免发生松弛的方法,例如考虑在芯片的背面膜被切断为与芯片相同大小的DAF的方法。但是,根据该方法,随着芯片的小型化,与芯片的大小一致地将DAF切断并粘贴于芯片变得困难。

[0010] 另外,考虑在将晶片分割为芯片单位前将DAF粘贴于晶片、不是通过基于拉拽力的断裂而是通过划片(dicing)而将DAF连同晶片一起切断的方法。

[0011] 但是,例如在向晶片的背面粘贴DAF、将DAF的外侧的面粘贴于保持用粘接带、并从晶片的表面进行划片的情况下,DAF被容易变形的保持用粘接带支承。于是,当接触到划片刀时DAF变形,DAF附着于划片刀的表面的凹凸,会产生DAF的切削毛刺。

[0012] 若存在切削毛刺,则有可能切削毛刺潜入到芯片之下从而妨碍拾取(pick up)、或者切削毛刺与布线接触从而发生短路。另外,在半导体芯片包括传感器元件的情况下,若在向安装基板进行安装时切削毛刺潜入到安装基板与半导体芯片之间,则传感器的水平度降低,传感器精度降低。

### 发明内容

[0013] 本公开鉴于上述点,目的在于,在将DAF粘贴于晶片的状态下进行的划片切割中抑

制切削毛刺的产生。

[0014] 为了达成上述目的,根据本公开的一个方式,一种半导体装置的制造方法,该半导体装置具备具有表面及背面的基板和粘贴于背面的膜,该半导体装置的制造方法具备以下步骤:对背面膜粘贴膜的步骤;将基板与膜一起从背面进行半切割而形成背面侧槽部的步骤;在形成背面侧槽部的步骤之后,对膜粘贴保护部件的步骤;在粘贴保护部件的步骤之后,从表面进行基板的划片切割而形成与背面侧槽部连结的表面侧槽部的步骤。

[0015] 这样,在将基板与在基板的背面膜粘贴的膜一起从背面侧进行半切割的情况下,膜在被支承于较硬的基板的状态下被切断,所以能够抑制膜的切削毛刺的产生。

[0016] 另外,根据其他式,一种半导体装置,具备具有表面及背面的基板和粘贴于背面的膜,该半导体装置中,表面及背面的外周部比内周部凹陷,从而从表面的内周部经由表面的外周部、基板的侧面、背面的外周部而到达背面的内周部的部分成为台阶形状,膜被粘贴于背面的内周部。

[0017] 这样的半导体装置通过如下处理而形成:在基板的背面膜粘贴膜,将基板与膜一起从背面侧进行半切割而形成背面侧槽部之后,从基板的表面侧改变划片刀的宽度地进行多次划片切割,形成与背面侧槽部连结的台阶形状的表面侧槽部。

[0018] 这样,在将基板与在基板的背面膜粘贴的膜一起从背面侧进行半切割的情况下,膜在被支承于较硬的基板的状态下被切断,所以能够抑制膜的切削毛刺的产生。

[0019] 另外,对各构成要素等标注的带括弧的参照符号表示该构成要素等与后述实施方式中记载的具体构成要素等的对应关系的一例。

## 附图说明

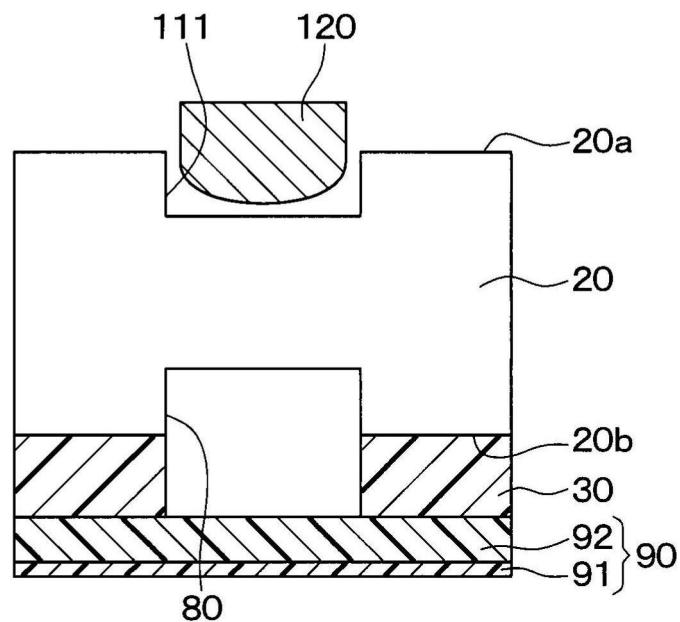

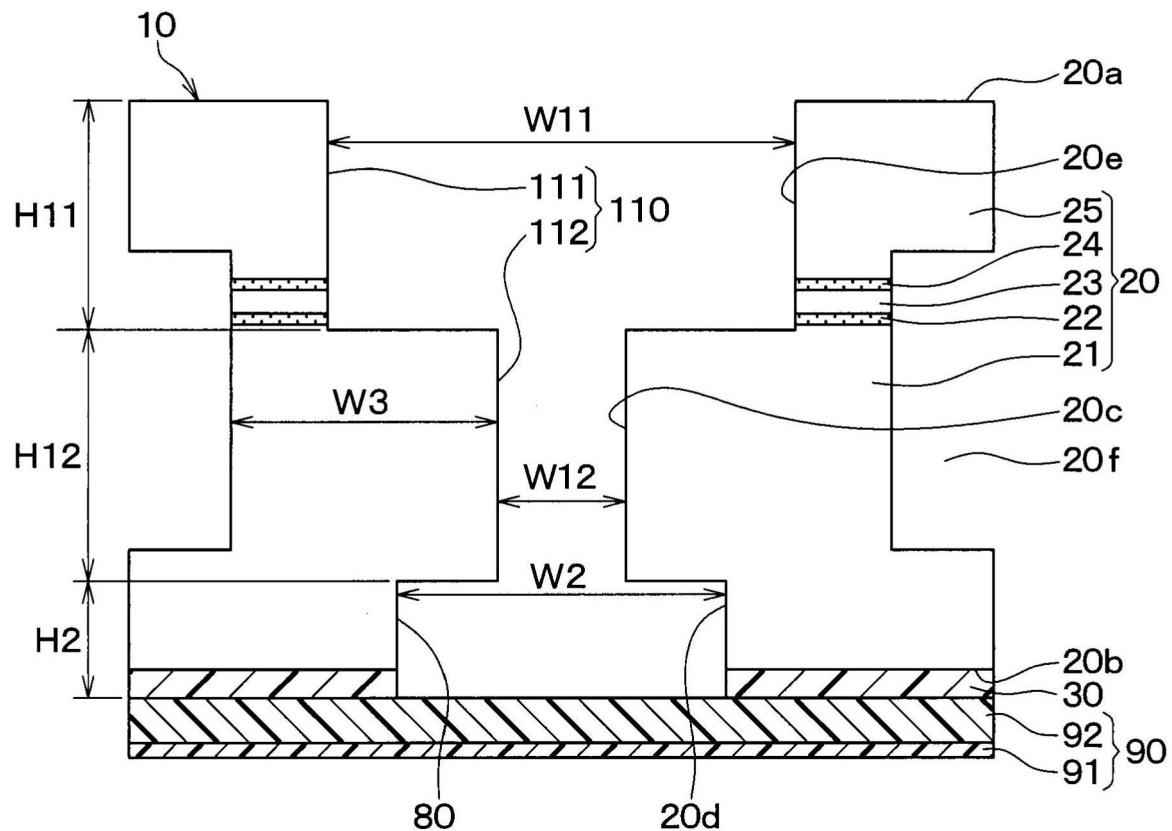

- [0020] 图1是第1实施方式的半导体装置的剖视图。

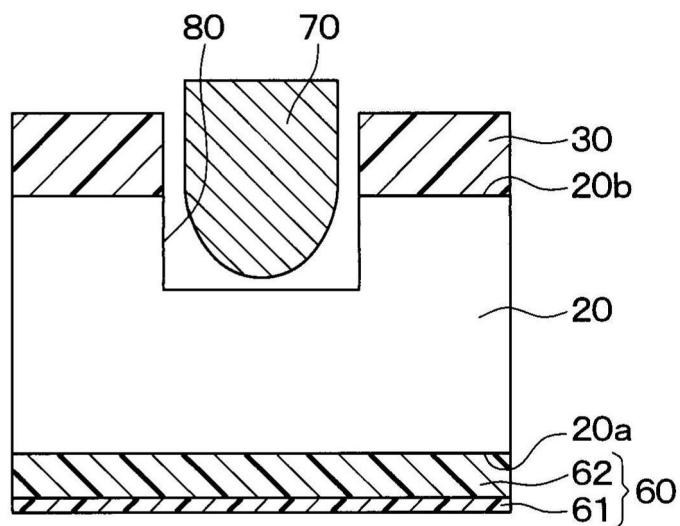

- [0021] 图2A是表示第1实施方式的半导体装置的制造工序的剖视图。

- [0022] 图2B是表示接着图2A的半导体装置的制造工序的剖视图。

- [0023] 图2C是表示接着图2B的半导体装置的制造工序的剖视图。

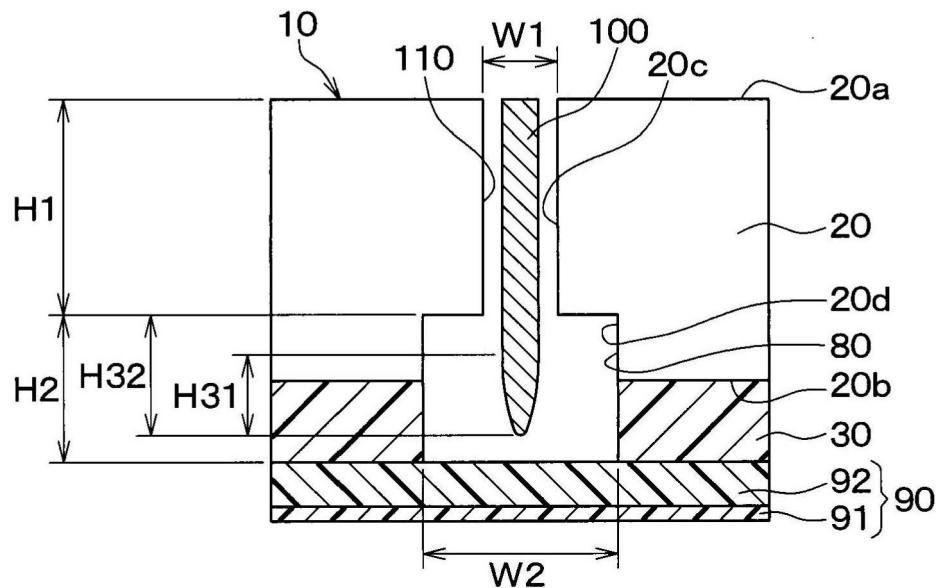

- [0024] 图2D是表示接着图2C的半导体装置的制造工序的剖视图。

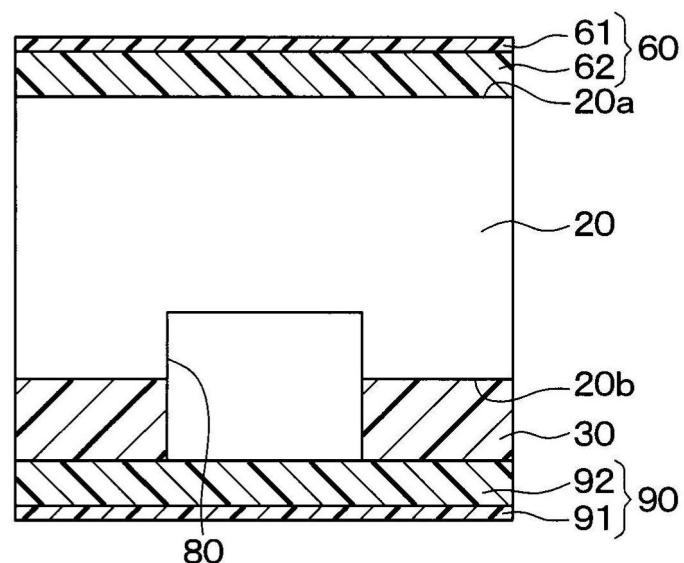

- [0025] 图2E是表示接着图2D的半导体装置的制造工序的剖视图。

- [0026] 图2F是表示接着图2E的半导体装置的制造工序的剖视图。

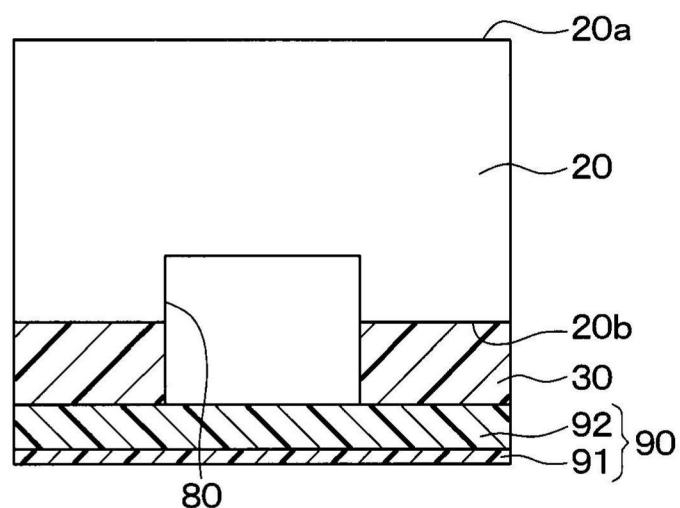

- [0027] 图3是表示比较例中的发生崩刀的样子的剖视图。

- [0028] 图4是表示第1实施方式中的发生崩刀的样子的剖视图。

- [0029] 图5是表示比较例中的发生崩刀的样子的剖视图。

- [0030] 图6是表示第2实施方式的半导体装置的剖视图。

- [0031] 图7A是表示第2实施方式的半导体装置的制造工序的剖视图。

- [0032] 图7B是表示接着图7A的半导体装置的制造工序的剖视图。

- [0033] 图8是用于说明第2实施方式的效果的剖视图。

- [0034] 图9是第3实施方式的半导体装置的剖视图。

- [0035] 图10是表示第3实施方式的半导体装置的制造工序的剖视图。

## 具体实施方式

[0036] 以下，基于附图对本公开的实施方式进行说明。另外，在以下的各实施方式中，对彼此相同或者等同的部分附以同一符号进行说明。

[0037] (第1实施方式)

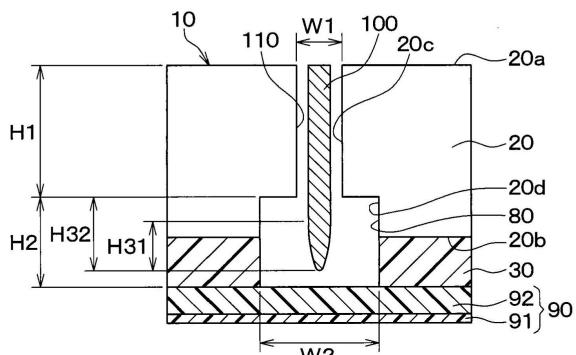

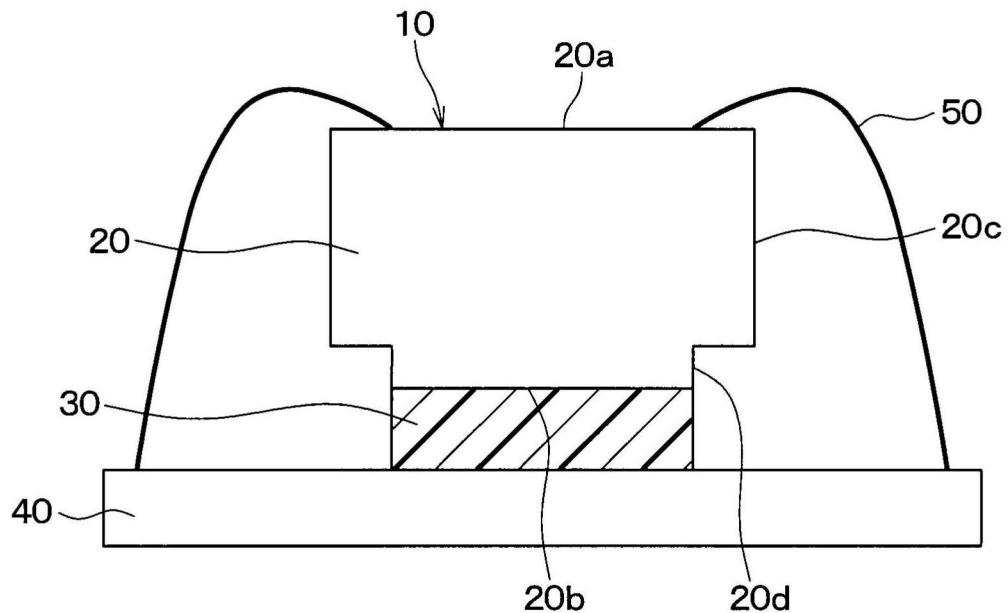

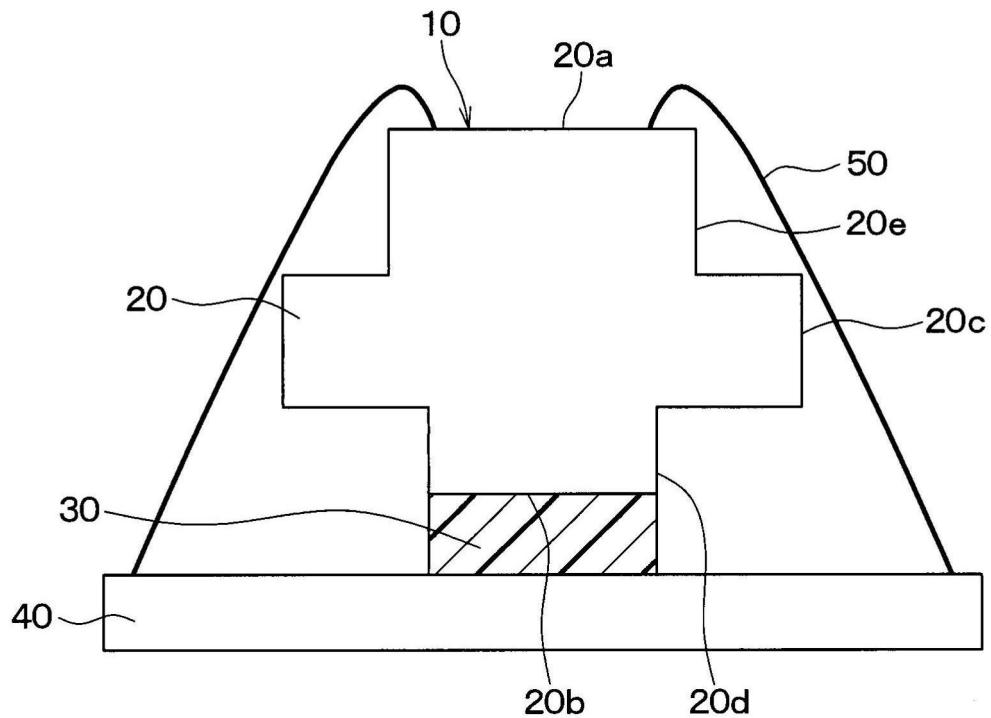

[0038] 对第1实施方式进行说明。如图1所示，本实施方式的半导体装置具备半导体芯片10、粘贴于半导体芯片10具备的基板20的DAF30、安装基板40、以及键合线50。

[0039] 半导体芯片10在由Si等构成的基板20上形成有传感器元件等未图示的半导体元件。在基板20的表面20a形成有未图示的焊盘，键合线50将该焊盘与安装基板40连接。

[0040] DAF30粘贴于基板20的背面20b，半导体芯片10通过DAF30而被固定于安装基板40。在本实施方式中，在基板20的背面20b与侧面20c之间的角部形成有凹部20d，背面20b的外周端部与内周部相比形成为凹陷的形状。DAF30粘贴于背面20b的内周部。

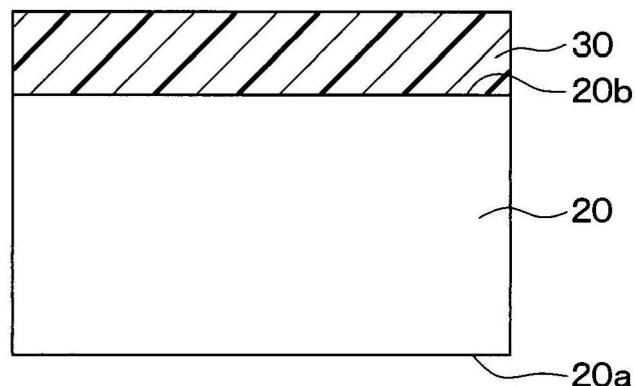

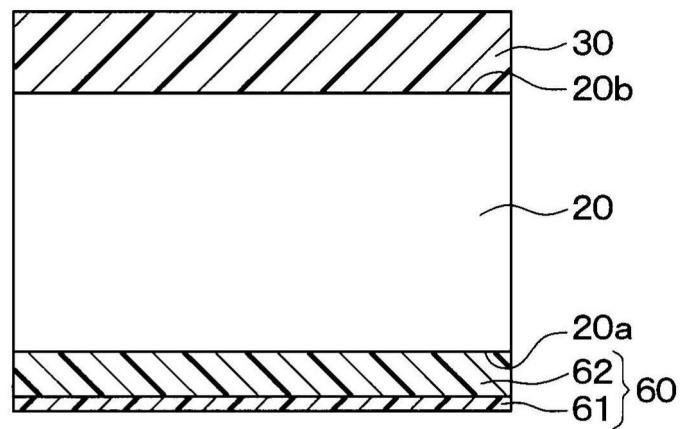

[0041] 关于半导体装置的制造方法，使用图2A～图2F进行说明。在图2A所示的工序中，准备晶片状的基板20，在基板20上形成了未图示的半导体元件、键合焊盘(bonding pad)等后，使用DAF粘贴机向基板20的背面20b粘贴DAF30，并将DAF30沿着基板20的缘部进行切断。由此，对基板20的背面20b整体粘贴圆形的DAF30。

[0042] 在图2B所示的工序中，向基板20的表面20a粘贴保护部件60。在本实施方式中，作为保护部件60，采用层叠了支承层61和通过被照射紫外线而固化的粘接层62而成的结构，将粘接层62粘贴于表面20a。

[0043] 另外，若在图2A所示的工序之前进行图2B所示的工序，则在将晶片状的基板20固定为环形的状态下粘贴DAF30。作为这样的方法，例如可以考虑将DAF30粘贴于基板20后、以不将保护部件60切断的方式将DAF30切断为与基板20相同的形状。但是，由于基板20较薄，因此以不将保护部件60切断的方式将DAF30切断为与基板20相同的形状是困难的。另外，可以考虑将预先加工为与基板20相同形状的DAF30粘贴于基板20的方法。但是，在该方法中，基板20与DAF30的位置容易发生错位。因此，优选的是，在通过图2A所示的工序粘贴了DAF30后进行图2B所示的工序。

[0044] 在图2C所示的工序中，利用划片刀70，从背面20b将基板20与DAF30一起进行半切割。即，将基板20切削至厚度方向的中途，在基板20形成槽部80。构成基板20的Si使红外线透射，所以能够利用红外相机从背面20b侧观察表面20a侧的图案而进行对准。槽部80相当于背面侧槽部。

[0045] 另外，若槽部80的宽度较小，则难以使后述的图2F所示的工序中形成的槽部110的位置与槽部80一致。因此，优选的是，使槽部80的宽度在某种程度上较大。

[0046] 另外，如后所述，若槽部80的深度过大，则基板20中的被表面20a与槽部80夹着的部分的抗弯强度降低，在图2F所示的工序中基板20有可能破裂。因此，在图2C所示的工序中，将基板20中的被表面20a与槽部80夹着的部分的厚度、即后述的槽部110的深度设为H1，将槽部80的深度设为H2，以使H1以某种程度增大的方式设定深度H2。

[0047] 在图2D所示的工序中，向DAF30粘贴保护部件90。在本实施方式中，作为保护部件90，采用将支承层91和通过被照射紫外线而固化的粘接层92层叠而成的结构，将粘接层92粘贴于DAF30中的与基板20相反侧的面。

[0048] 在图2E所示的工序中，对粘贴于表面20a的保护部件60照射紫外线，减弱粘接层62

的粘接力,将保护部件60从表面20a剥离。由此,表面20a露出。

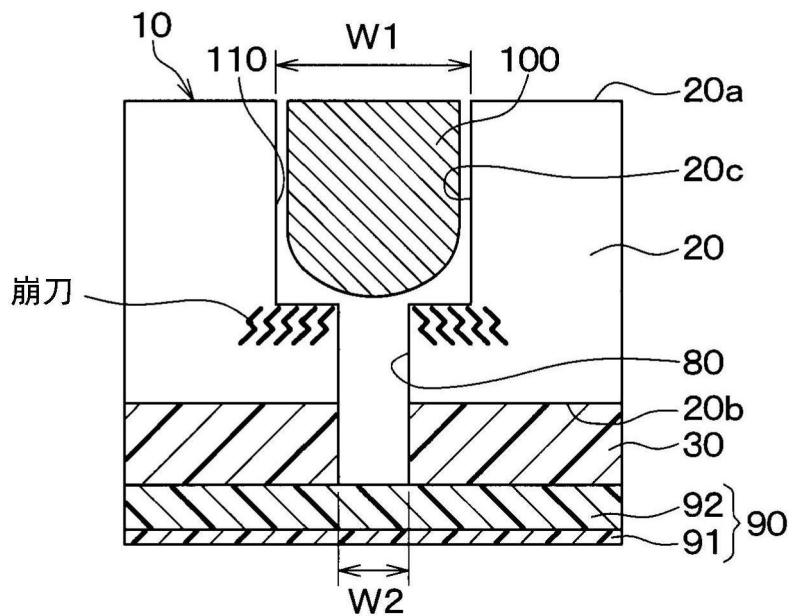

[0049] 在图2F所示的工序中,利用划片刀100,从表面20a侧进行基板20的划片切割,形成槽部110。槽部110相当于表面侧槽部。

[0050] 另外,在图2F所示的工序中,以形成于表面20a的划片槽(scribe line)等为基准而进行对准,使槽部110与槽部80连结。另外,为了使槽部110的宽度W1比槽部80的宽度W2小,作为划片刀100,使用比划片刀70细的划片刀。由此,形成了槽部110的宽度W1比槽部80的宽度W2小的台阶形状的槽。然后,将基板20分割为芯片单位而形成半导体芯片10,并且在基板20的侧面20c与背面20b之间的角部形成凹部20d。

[0051] 另外,在图2F所示的工序中,为了不对粘贴于背面20b的保护部件90进行切削,一边维持划片刀100与保护部件90分离的状态一边进行基板20的切削。

[0052] 在图2F所示的工序之后,将半导体芯片10及DAF30从保护部件90剥离,通过DAF30将半导体芯片10固定于安装基板40。然后,进行引线键合,通过键合线50将在基板20的表面20a形成的未图示的焊盘与安装基板40连接。这样,制造出半导体装置。

[0053] 这样,利用比切割带等硬的由Si等构成的基板20将DAF30从下方支承而进行切削,从而能够抑制划片刀70与DAF30接触时的DAF30的变形。因此,与用切割带等支承DAF30而进行切割的情况相比,能够抑制由于DAF附着于划片刀的表面的凹凸而引起的切削毛刺的产生。

[0054] 另外,若划片刀100的宽度比划片刀70的宽度大,则如图3所示那样,槽部110的宽度W1比槽部80的宽度W2大。若这样形成槽部110,则在基板20中的槽部80的外侧的区域产生由于与划片刀100的接触而引起的应力,有可能在大范围内发生崩刀(tipping)。并且,由于这样的崩刀而在侧面20c产生裂纹,基板20的强度降低。

[0055] 另一方面,若如图4所示那样为了使宽度W1比宽度W2小而使用与划片刀70相比宽度小的划片刀作为划片刀100,则由划片刀100引起的应力被释放,因此崩刀的发生得以抑制。另外,由于在槽部80的外侧发生崩刀的情况得到抑制,因此能够抑制由裂纹引起的基板20的强度降低。

[0056] 另外,若在划片时划片刀100与保护部件90接触,则有可能保护部件90变形而在槽部80的周边发生胶体残留。另外,若划片刀劣化则前端变圆,因此在划片刀100的前端部有可能无法正常地切削。

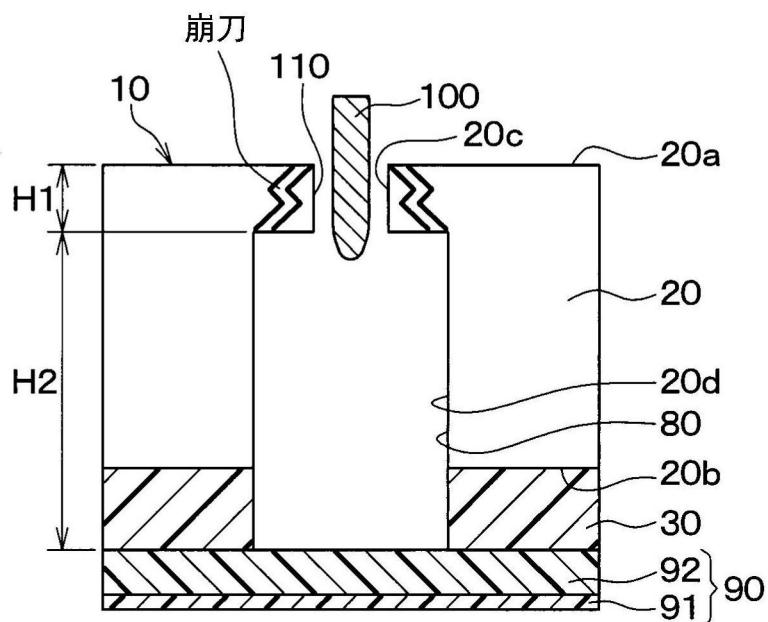

[0057] 因此,为了抑制划片刀100与保护部件90的接触、并且用划片刀100中的远离前端部的部分进行划片,优选使槽部80的深度H2以某种程度增大。具体而言,将划片刀100的圆化了的前端部的长度设为H31,将划片刀100进入槽部80的深度设为H32,使 $H2 > H32 > H31$ 是优选的。由此,能够一边维持划片刀100与保护部件90相分离的状态,一边用划片刀100中的远离前端部的部分正常地切削。

[0058] 但是,若槽部80的深度H2过大,则基板20中的被表面20a与槽部80夹着的部分的抗弯强度降低,当如图5所示那样发生崩刀时,基板20可能因来自划片刀100的力而破裂。因此,优选的是,使深度H2以某种程度减小,以使基板20中的被槽部80与表面20a夹着的部分的抗弯强度高于在图2F所示的工序中发生基板20的破裂的抗弯强度。

[0059] 另外,基板20的抗弯强度除了根据深度H2变化以外,还根据槽部80的宽度W2、基板20的材料而变化。并且,发生崩刀时的基板20的抗弯强度还根据划片刀100的宽度等而变

化,因此优选的是,考虑基板20的材料、划片刀100的宽度等来设定深度H1、H2、宽度W2。

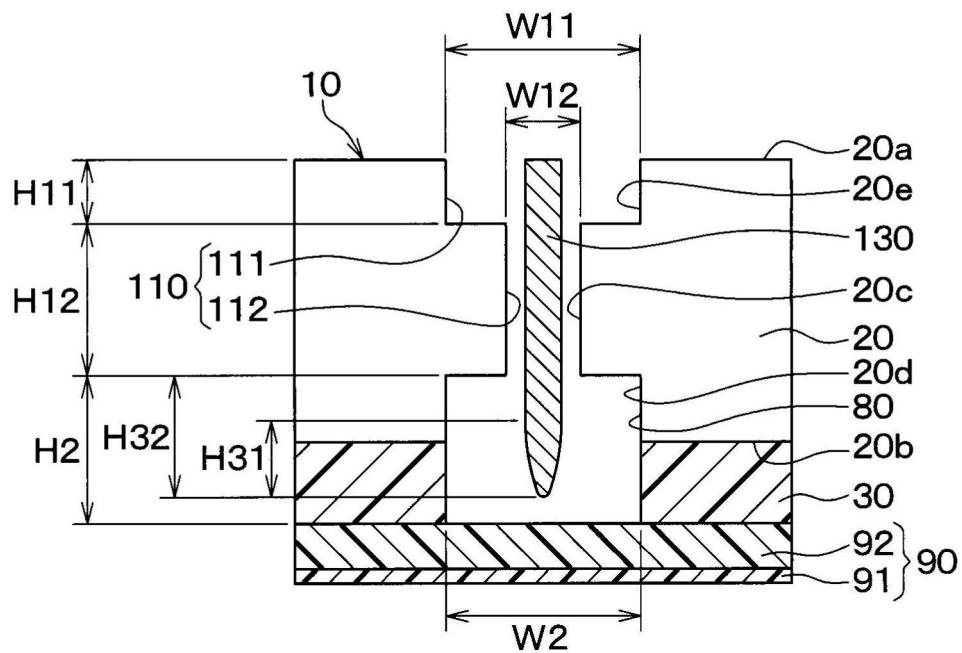

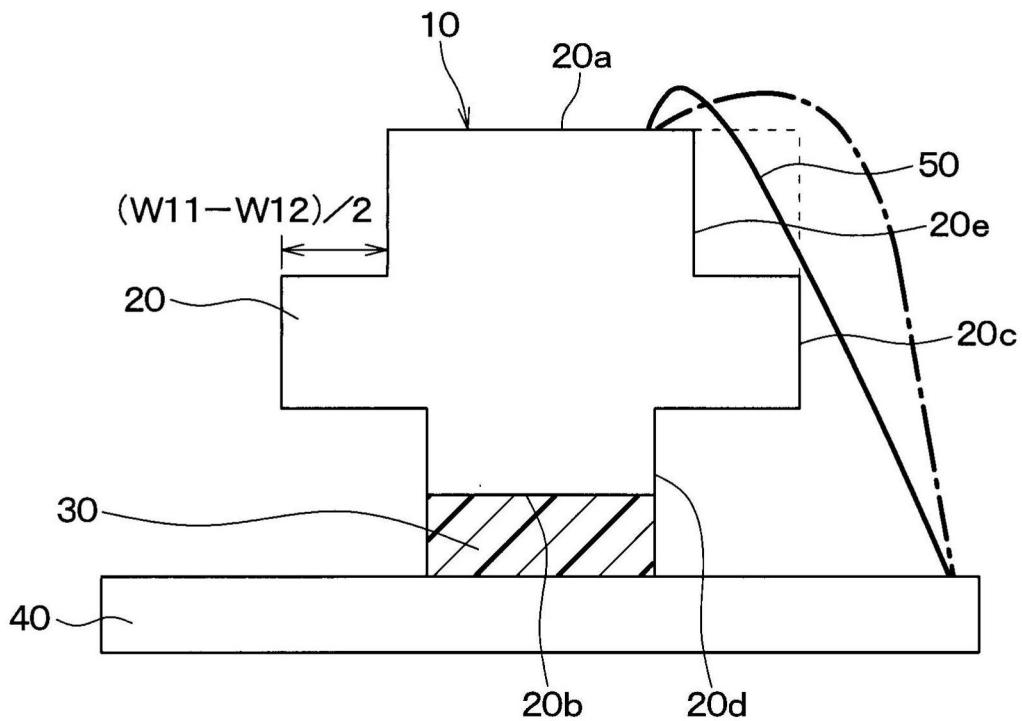

[0060] (第2实施方式)

[0061] 对第2实施方式进行说明。本实施方式相对于第1实施方式而言,变更了基板20的形状,除此以外与第1实施方式是同样的,因此仅对与第1实施方式不同的部分进行说明。

[0062] 如图6所示那样,在本实施方式中,在基板20的表面20a与侧面20c之间的角部形成凹部20e,表面20a的外周端部形成为比内周部凹陷的形状。由此,从表面20a的内周部起经过表面20a的外周部、侧面20c、背面20b的外周部而到达背面20b的内周部的部分成为台阶形状。并且,键合线50与表面20a的内周部连接。

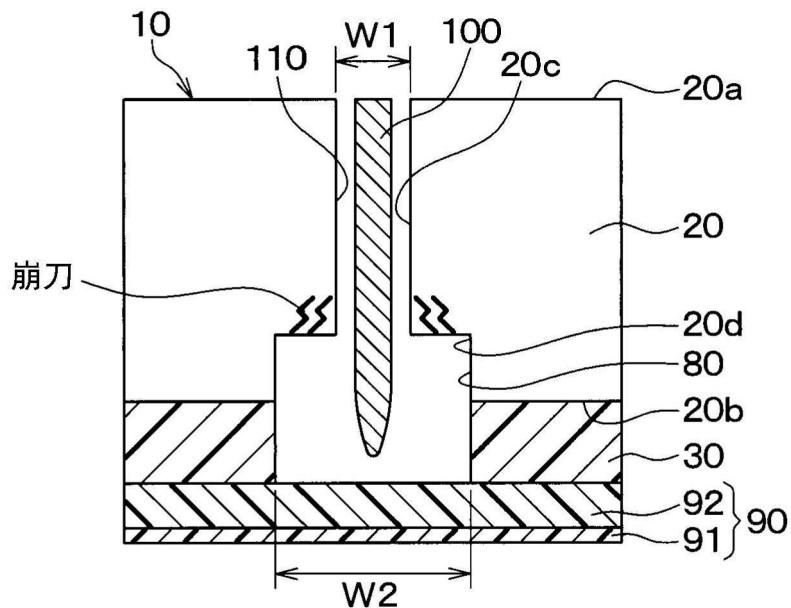

[0063] 在本实施方式中,在与第1实施方式同样地进行了从图2A所示的工序到图2E所示的工序后,在1个槽部的底部形成与该槽部相比开口宽度较小的其他槽部,以使得槽部110成为随着朝向背面20b而宽度变窄的台阶形状。

[0064] 具体而言,以在基板20的表面20a形成的划片槽等为基准进行对准,如图7A所示那样与形成于背面20b的槽部80对准地配置划片刀120,在表面20a形成槽部111。然后,如图7B所示,利用划片刀130,在槽部111的底部形成槽部112。此时,将槽部111、112的宽度分别设为W11、W12,为了使宽度W12比宽度W11小,作为划片刀130,使用与划片刀120相比宽度小的划片刀。槽部111、112分别相当于第1、第2表面侧槽部。

[0065] 由此,形成由槽部111和槽部112构成的台阶形状的槽部110,槽部110在槽部112处与槽部80连结。之后,将基板20分割为芯片单位,并且在基板20的背面20b与侧面20c之间的角部形成凹部20d,在表面20a与侧面20c之间的角部形成凹部20e。

[0066] 另外,在本实施方式中,也与第1实施方式同样地,为了使槽部111、槽部112与槽部80之间的对位较容易,优选使槽部80的宽度W2以某种程度增大。另外,为了抑制崩刀及裂纹的发生,优选使槽部112的宽度W12比槽部80的宽度W2小。

[0067] 另外,与第1实施方式同样地,为了一边维持划片刀130与保护部件90相分离的状态一边用划片刀130中的远离前端部的部分正常地切削,优选使 $H2 > H32 > H31$ 。另外,优选的是,使深度H2以某种程度减小,以使基板20中的被槽部80与表面20a夹着的部分的抗弯强度高于在图7A所示的工序中发生基板20的破裂的抗弯强度。另外,优选的是,使深度H11、H2以某种程度减小,以使基板20中的被槽部80和槽部111夹着的部分的抗弯强度高于在图7B所示的工序中发生基板20的破裂的抗弯强度。

[0068] 在基板20形成有凹部20e的本实施方式中,如图8所示,与第1实施方式相比,能够对应于表面20a与侧面20c之间的角部的欠缺量来减小环线(wire looping)。由此,能够缩短键合线50。另外,通过缩短键合线50,能够提高键合线50的强度。另外,在图8中,虚线表示第1实施方式的基板20的角部的形状,单点划线表示第1实施方式的键合线50的形状。

[0069] 另外,在基板20未形成凹部20e的情况下,如果使在表面20a形成的未图示的键合焊盘的位置靠近基板20的端部,则也能够缩短键合线50。但是,如果这样配置键合焊盘,则键合线50会大幅弯曲,键合线50的强度降低。相对于此,在基板20设置有凹部20e的本实施方式中,能够抑制键合线50的变形并且使安装基板40上的焊盘位置靠近基板20的端部,实现高密度安装。

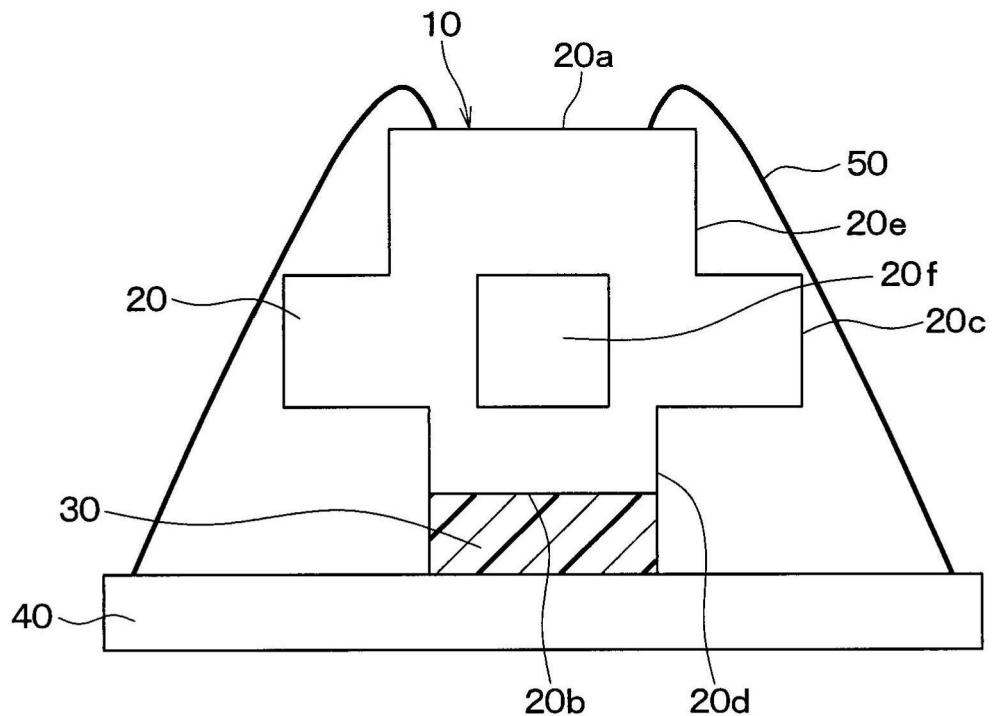

[0070] (第3实施方式)

[0071] 对第3实施方式进行说明。本实施方式相对于第2实施方式而言变更了基板20的结

构,除此以外与第2实施方式是同样的,因此仅对与第2实施方式不同的部分进行说明。

[0072] 如图9所示,在本实施方式中,在基板20的内部形成有中空部20f。作为这样的基板20,例如举出如图10所示那样将Si层21、氧化膜22、Si层23、氧化膜24、Si层25依次层叠而成的结构。

[0073] 在中空部20f形成有对加速度等进行检测的未图示的传感器部。键合线50将通过形成于Si层25的未图示的TSV而与Si层23连接的未图示的键合焊盘、与安装基板40上的未图示的键合焊盘相连接。

[0074] 在本实施方式中,在图2A所示的工序之前,对Si层21的表面进行热氧化而形成氧化膜22,通过蚀刻将Si层21及氧化膜22的一部分去除而形成凹部,并隔着氧化膜22对Si层21粘合Si层23。然后,在Si层23形成未图示的传感器部。另外,在Si层25的表面形成氧化膜24,通过蚀刻将Si层25及氧化膜24的一部分去除而形成凹部,隔着氧化膜24对Si层23粘合Si层25,并在Si层25形成未图示的TSV及键合焊盘。这样,制造出形成有中空部20f的基板20。并且,在进行了图2A所示的工序至图2E所示的工序后,如图10所示,形成台阶形状的槽部110。另外,在本实施方式中,在图2C所示的工序中,能够利用红外相机从背面20b侧观察中空部20f及表面20a侧的图案而进行对准。

[0075] 在基板20具备由不同的材料构成的多个层的情况下,优选相应于材料而选择划片刀。通过如图7A、图7B所示那样通过多次的划片切割来形成槽部110,从而能够提高划片条件的自由度。

[0076] 另外,在基板20的内部形成有中空部20f的情况下,随着基板20中的被槽部112与中空部20f夹着的部分的宽度W3的变小,基板20的抗弯强度降低。因此,为了抑制基板20的抗弯强度的降低,优选使宽度W3以某种程度增大。

[0077] (其他实施方式)

[0078] 另外,本公开并不限定于上述实施方式,能够适当变更。另外,上述各实施方式不是彼此无关,除了明显不能组合的情况以外,能够适当组合。另外,在上述各实施方式中,构成实施方式的要素,除了特别明示是必须的情况及在原理上认为明显是必须的情况等以外,当然并不绝对是必须的。另外,在上述各实施方式中,在提及了实施方式的构成要素的个数、数值、量、范围等数值的情况下,除了特别明示是必须的情况及在原理上明显被限定为特定的数量的情况等以外,并不限定于该特定的数量。另外,在上述各实施方式中,提及了构成要素等的形状、位置关系时,除了特别明示的情况及在原理上被限定为特定的形状、位置关系等的情况等以外,并不限定于该形状、位置关系等。

[0079] 例如,可以将上述第1实施方式应用于具有在内部形成有中空部20f的基板20的半导体装置。

[0080] 另外,在上述第2实施方式中,槽部110包括槽部111和槽部112,且形成为2级的台阶形状,但也可以使槽部110为3级以上台阶形状。即,也可以在进行了图2E所示的工序后,多次进行在1个槽部的底部形成与该槽部相比开口宽度小的其他槽部的处理,以使得槽部110成为随着朝向背面20b而宽度变窄的台阶形状。

图1

图2A

图2B

图2C

图2D

图2E

图2F

图3

图4

图5

图6

图7A

图7B

图8

图9

图10