(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7021821号**

**(P7021821)**

(45)発行日 令和4年2月17日(2022.2.17)

(24)登録日 令和4年2月8日(2022.2.8)

(51)国際特許分類

F I

|        |                   |        |             |

|--------|-------------------|--------|-------------|

| H 01 L | 27/11521(2017.01) | H 01 L | 27/11521    |

| H 01 L | 27/11541(2017.01) | H 01 L | 27/11541    |

| H 01 L | 27/11543(2017.01) | H 01 L | 27/11543    |

| H 01 L | 27/11546(2017.01) | H 01 L | 27/11546    |

| H 01 L | 21/336(2006.01)   | H 01 L | 29/78 3 7 1 |

請求項の数 31 (全18頁) 最終頁に続く

(21)出願番号 特願2018-506188(P2018-506188)

(86)(22)出願日 平成28年8月5日(2016.8.5)

(65)公表番号 特表2018-526821(P2018-526821

A)

(43)公表日 平成30年9月13日(2018.9.13)

(86)国際出願番号 PCT/US2016/045895

(87)国際公開番号 WO2017/024274

(87)国際公開日 平成29年2月9日(2017.2.9)

審査請求日 令和1年7月31日(2019.7.31)

(31)優先権主張番号 14/819,401

(32)優先日 平成27年8月5日(2015.8.5)

(33)優先権主張国・地域又は機関

米国(US)

(73)特許権者 507107291

テキサス インスツルメンツ インコーポ

レイテッド

アメリカ合衆国 テキサス州 75265

- 5474 ダラス メイル ステイション

3999 ピーオーボックス 655474

(74)代理人 100098497

弁理士 片寄 恒三

ニン タン

(72)発明者 アメリカ合衆国 75013 テキサス州

アレン, コマンチ ドライブ 1426

ウエイドン ティエン

アメリカ合衆国 75252 テキサス州

ダラス, ベンチャーマーク ドライブ 17

843

最終頁に続く

(54)【発明の名称】 金属ゲートプロセスに基づく低成本のフラッシュメモリ製造フロー

**(57)【特許請求の範囲】****【請求項1】**

フラッシュメモリを含む集積回路であって、

半導体材料を含む基板と、

前記フラッシュメモリの感知トランジスタであって、

前記基板の頂部表面において配置されるゲート誘電体層と、

前記ゲート誘電体層上に配置される少なくとも400ナノメートル幅のポリシリコンの浮遊ゲートと、

前記浮遊ゲートの側部上に位置される誘電体オフセットスペーサとソース／ドレイン側壁スペーサと、

前記基板に配置される第1及び第2のソース／ドレイン領域であって、前記浮遊ゲートの下に中途まで延在して200ナノメートル未満で分離される、前記第1及び第2のソース／ドレイン領域と、

前記浮遊ゲートと前記誘電体オフセットスペーサと前記ソース／ドレイン側壁スペーサとの上に配置される頂部ゲート誘電体層であって、前記浮遊ゲートの一方の側部に位置する前記ソース／ドレイン側壁スペーサの第1のものから前記浮遊ゲートの他方の側部に位置する前記ソース／ドレイン側壁スペーサの第2のものに延在する单一の同質の層を含む、

前記頂部ゲート誘電体層と、

前記頂部ゲート誘電体層上に配置される金属感知ゲートであって、前記頂部ゲート誘電体層と直接に接触する金属層を含む、前記金属感知ゲートと、

を含む、前記感知トランジスタと、

を含む、集積回路。

**【請求項 2】**

請求項 1 に記載の集積回路であって、

前記金属感知ゲートが、タンタルと窒化タンタルとチタンとチタン窒化物とから成るグループから選択される金属を含む、集積回路。

**【請求項 3】**

請求項 1 に記載の集積回路であって、

前記頂部ゲート誘電体層が、二酸化シリコンのサブ層とシリコン窒化物のサブ層とを含む層スタックである、集積回路。

10

**【請求項 4】**

請求項 1 に記載の集積回路であって、

前記感知トランジスタの前記第 1 及び第 2 のソース / ドレイン領域が、前記浮遊ゲートの外方に配置されるディープソース / ドレイン部分を含む、集積回路。

**【請求項 5】**

請求項 4 に記載の集積回路であって、

前記第 1 及び第 2 のソース / ドレイン領域の前記ディープソース / ドレイン部分の上の前記基板の前記頂部表面における金属シリサイドを更に含む、集積回路。

**【請求項 6】**

請求項 1 に記載の集積回路であって、

前記金属感知ゲートが 40 ナノメートル ~ 80 ナノメートルの間の範囲の厚みである、集積回路。

20

**【請求項 7】**

請求項 1 に記載の集積回路であって、

前記金属感知ゲートと同じ金属のトレンチライナーを含む銅ダマシン構造を備える金属相互接続を更に含む、集積回路。

**【請求項 8】**

請求項 1 に記載の集積回路であって、

前記感知トランジスタの前記ゲート誘電体層と同じ厚みのゲート誘電体層を有する論理 n チャネル金属酸化物半導体 (MOS) トランジスタを更に含む、集積回路。

30

**【請求項 9】**

フラッシュメモリを含む集積回路であって、

半導体材料を含む基板と、

前記フラッシュメモリの感知トランジスタであって、

前記基板の頂部表面に配置されるゲート誘電体層と、

前記ゲート誘電体層上に配置される幅を有するポリシリコンの浮遊ゲートと、

前記浮遊ゲートの側部に位置される誘電体オフセットスペーサ及びソース / ドレイン側壁スペーサと、

前記基板内に配置される第 1 及び第 2 のソース / ドレイン領域であって、前記幅の少なくとも 25 % の距離まで前記浮遊ゲートの下に途中まで延在する、前記第 1 及び第 2 のソース / ドレイン領域と、

前記浮遊ゲートと前記誘電体オフセットスペーサとソース / ドレイン側壁スペーサとの上に配置される頂部ゲート誘電体層であって、前記浮遊ゲートの一方の側部に位置する前記ソース / ドレイン側壁スペーサの第 1 のものから前記浮遊ゲートの他方の側部に位置する前記ソース / ドレイン側壁スペーサの第 2 のものに延在する单一の同質の層を含む、前記頂部ゲート誘電体層と、

前記頂部ゲート誘電体層上に配置される金属感知ゲートであって、前記頂部ゲート誘電体層と直接に接触する金属層を含む、前記金属感知ゲートと、

を含む、前記感知トランジスタと、

を含む、集積回路。

40

50

**【請求項 10】**

請求項 9 に記載の集積回路であって、

ゲートとアクセスソース / ドレイン領域とを備える n 型アクセストランジスタを更に含み、

前記第 1 及び第 2 のソース / ドレイン領域が、前記アクセスソース / ドレイン領域が前記

n 型アクセストランジスタのゲートの下に延在するよりも更に前記浮遊ゲートの下に延在

する、集積回路。

**【請求項 11】**

請求項 9 に記載の集積回路であって、

前記浮遊ゲートの幅が 400 ナノメートルであり、前記浮遊ゲートの下に延在する前記第

1 及び第 2 のソース / ドレイン領域の距離が少なくとも 100 ナノメートルである、集積

回路。 10

**【請求項 12】**

請求項 9 に記載の集積回路であって、

前記金属感知ゲートが前記浮遊ゲートの端部を過ぎて前記第 1 及び第 2 のソース / ドレイ

ン領域の上に延在しない、集積回路。

**【請求項 13】**

請求項 9 に記載の集積回路であって、

前記金属感知ゲートが、タンタルと窒化タンタルとチタンと窒化チタンとからなるグループ

から選択される金属を含む、集積回路。

**【請求項 14】**

請求項 9 に記載の集積回路であって、

前記頂部ゲート誘電体層が、二酸化シリコンのサブ層と窒化シリコンのサブ層とを含む層

スタックである、集積回路。 20

**【請求項 15】**

電子デバイスであって、

半導体材料を含む基板と、

トランジスタであって、

前記基板の頂部表面に配置されるゲート誘電体と、

前記ゲート誘電体上に配置される少なくとも 400 ナノメートルの幅のポリシリコンの浮

遊ゲートと、 30

前記浮遊ゲートの側部に捻れて位置されるソース / ドレイン側壁スペーサと、

前記基板内に配置される第 1 及び第 2 のソース / ドレイン領域であって、前記浮遊ゲート

の下に途中まで延在し、200 ナノメートルで分離される、前記第 1 及び第 2 のソース /

ドレイン領域と、

前記浮遊ゲートと前記ソース / ドレイン側壁スペーサとの上に配置される頂部ゲート誘電

体層であって、前記浮遊ゲートの一方の側部に位置する前記ソース / ドレイン側壁スペー

サの第 1 のものから前記浮遊ゲートの他方の側部に位置する前記ソース / ドレイン側壁ス

ペーサの第 2 のものに延在する単一の同質の層を含む、前記頂部ゲート誘電体層と、

前記頂部ゲート誘電体層上に配置される金属感知ゲートであって、前記頂部ゲート誘電体

層と直接に接触する金属層を含む、前記金属感知ゲートと、

を含む、前記トランジスタと、 40

を含む、電子デバイス。

**【請求項 16】**

請求項 15 に記載の電子デバイスであって、

前記第 1 及び第 2 のソース / ドレイン領域が 200 ナノメートル未満で分離されている、

電子デバイス。

**【請求項 17】**

請求項 15 に記載の電子デバイスであって、

前記頂部ゲート誘電体層が二酸化シリコンのサブ層と窒化シリコンのサブ層とを含む層ス

タックを含む、電子デバイス。 50

**【請求項 18】**

請求項 15 に記載の電子デバイスであって、

前記トランジスタの前記第 1 及び第 2 のソース / ドレイン領域が前記浮遊ゲートの外側に配置される深いソース / ドレイン部を含む、電子デバイス。

**【請求項 19】**

請求項 18 に記載の電子デバイスであって、

前記第 1 及び第 2 のソース / ドレイン領域の前記深いソース / ドレイン部の上の前記基板の頂部表面における金属シリサイドを更に含む、電子デバイス。

**【請求項 20】**

請求項 15 に記載の電子デバイスであって、

前記金属感知ゲートが 40 ナノメートルと 80 ナノメートルの間の範囲の厚さを有する、電子デバイス。

**【請求項 21】**

フラッシュメモリを含む集積回路を形成する方法であって、

半導体材料を含む基板を提供することと、

感知ソース / ドレインマスクを前記基板の頂部表面の上に形成することであって、前記感知ソース / ドレインマスクが、前記フラッシュメモリの感知トランジスタの第 1 及び第 2 の感知ソース / ドレイン領域のためのエリアにおいて前記基板を露出させ、前記第 1 及び第 2 の感知ソース / ドレイン領域のための前記エリア間の前記基板を覆う、前記感知ソース / ドレインマスクを形成することと、

前記感知ソース / ドレインマスクにより露出された前記エリアにおける前記基板にドーパントを注入することと、

前記感知ソース / ドレインマスクを取り除くことと、

前記感知ソース / ドレインマスクを取り除いた後に前記基板の前記頂部表面上に前記感知トランジスタのゲート誘電体層を形成することと、

前記ゲート誘電体層上に少なくとも 400 ナノメートル幅のポリシリコンの浮遊ゲートを形成することと、

前記浮遊ゲートの下に中途まで延在して 200 ナノメートル未満で分離される第 1 及び第 2 の感知ソース / ドレイン領域を形成するために、前記注入されたドーパントを活性化することと、

前記浮遊ゲートの上に頂部ゲート誘電体層を形成することと、

前記頂部ゲート誘電体層の上にゲート金属の層を形成することと、

前記浮遊ゲートの上の金属感知ゲートのためのエリアを覆うように前記ゲート金属の層の上にマスクを形成することと、

前記頂部ゲート誘電体層上に前記金属感知ゲートを形成するために前記マスクにより露出された箇所の前記ゲート金属の層を取り除くことと、

を含む、方法。

**【請求項 22】**

請求項 21 に記載の方法であって、

前記金属感知ゲートが、タンタルと窒化タンタルとチタンとチタン窒化物とから成るグループから選択される金属を含む、方法。

**【請求項 23】**

請求項 21 に記載の方法であって、

前記第 1 及び第 2 の感知ソース / ドレイン領域のディープソース / ドレイン部分を形成するために前記浮遊ゲートをマスクとして用いて前記浮遊ゲートに近接する前記基板にドーパントを注入することであって、前記ディープソース / ドレイン部分が前記浮遊ゲートの外方に配置される、前記基板にドーパントを注入することを更に含む、方法。

**【請求項 24】**

請求項 23 に記載の方法であって、

前記第 1 及び第 2 の感知ソース / ドレイン領域の前記ディープソース / ドレイン部分上に

10

20

30

40

50

金属シリサイドを形成することを更に含む、方法。

**【請求項 25】**

請求項 24 に記載の方法であって、

前記浮遊ゲートと前記第 1 及び第 2 の感知ソース / ドレイン領域の前記ディープソース / ドレイン部分との上にシリサイドブロック誘電体材料の層を形成することと、

前記金属シリサイドを形成する前に、前記浮遊ゲートの上に前記シリサイドブロック誘電体材料の層を残すように前記シリサイドブロック誘電体材料の層をパターニングして前記第 1 及び第 2 の感知ソース / ドレイン領域の前記ディープソース / ドレイン部分の上のシリサイドブロック誘電体材料の前記層を取り除くことと、

前記ゲート金属の層を形成する前に、前記浮遊ゲート上の前記シリサイドブロック誘電体材料の層の上と前記金属シリサイドの上とに誘電体障壁層を形成することと、

前記金属感知ゲートを形成するために前記ゲート金属の層を取り除いた後に前記金属シリサイドの上から前記誘電体障壁層を取り除くことと、

を更に含み、

前記シリサイドブロック誘電体材料の層と前記誘電体障壁層との組合せが前記頂部ゲート誘電体層を提供する、方法。

**【請求項 26】**

請求項 25 に記載の方法であって、

前記シリサイドブロック誘電体材料の層が二酸化シリコンを含み、前記誘電体障壁層が二酸化シリコンのサブ層とシリコン窒化物のサブ層とを含む層スタックである、方法。

**【請求項 27】**

請求項 21 に記載の方法であって、

誘電体層に相互接続トレンチを形成することと、

前記相互接続トレンチの側壁と底部との上にトレンチライナーを形成することと、

前記トレンチライナー上に銅を形成することと、

を更に含み、

前記トレンチライナーが前記金属感知ゲートと同じ組成を有する、方法。

**【請求項 28】**

請求項 21 に記載の方法であって、

前記金属感知ゲートを形成するために前記マスクにより露出された箇所の前記ゲート金属の層を取り除くことが、ウェットエッティングプロセスによって実施される、方法。

**【請求項 29】**

請求項 28 に記載の方法であって、

前記ウェットエッティングプロセスが、濃縮水酸化アンモニウムと過酸化水素との水溶液を含む、方法。

**【請求項 30】**

請求項 21 に記載の方法であって、

前記感知トランジスタの前記ゲート誘電体層と同時に論理 MOS トランジスタのゲート誘電体層を形成することを更に含む、方法。

**【請求項 31】**

フラッシュメモリを含む集積回路を形成する方法であって、

半導体材料を含む基板を提供することと、

前記基板の頂部表面の上に感知ソース / ドレインマスクを形成することであって、前記感知ソース / ドレインマスクが、前記フラッシュメモリの感知トランジスタの感知ソースドレイン領域のためのエリアにおいて前記基板を露出させ、前記感知ソースドレイン領域のための前記エリア間で前記基板を覆う、前記感知ソース / ドレインマスクを形成することと、

前記感知ソース / ドレインマスクにより露出された前記エリアにおける前記基板にドーパントを注入することと、

前記感知ソース / ドレインマスクを取り除くことと、

10

20

30

40

50

前記感知ソース／ドレインマスクを取り除いた後に前記基板の前記頂部表面上に前記感知トランジスタのゲート誘電体層を形成することと、

前記ゲート誘電体層上に少なくとも400ナノメートル幅のポリシリコンの前記感知トランジスタの浮遊ゲートを形成することと、

前記浮遊ゲートの下に中途まで延在して200ナノメートル未満で分離される前記感知トランジスタの感知ソース／ドレイン領域を形成するために、前記注入されたドーパントを活性化することと、

前記感知ソース／ドレイン領域のディープソース／ドレイン部分を形成するために、前記浮遊ゲートをマスクとして用いて前記浮遊ゲートに近接する前記基板にドーパントを注入することであって、前記ディープソース／ドレイン部分が前記浮遊ゲートの外方に配置されている、前記ドーパントを注入することと、

前記浮遊ゲートと前記感知ソース／ドレイン領域の前記ディープソース／ドレイン部分との上にシリサイドブロック誘電体材料の層を形成することと、

前記浮遊ゲートの上のシリサイドブロック誘電体材料の層を残すために、前記シリサイドブロック誘電体材料の層をパターニングして前記感知ソース／ドレイン領域の前記ディープソース／ドレイン部分の上の前記シリサイドブロック誘電体材料の層を取り除くことと、前記感知ソース／ドレイン領域の前記ディープソース／ドレイン部分上に耐火性金属の層を形成し、前記ディープソース／ドレイン部分上に金属シリサイド形成するために前記基板を加熱し、前記浮遊ゲート上のシリサイドブロック誘電体材料の前記パターニングされた層が前記浮遊ゲート上に金属シリサイドが形成しないようにし、その後、反応しなかつた金属を取り除くことと、

前記浮遊ゲート上のシリサイドブロック誘電体材料の前記パターニングされた層の上と前記金属シリサイドの上とに誘電体障壁層を形成することと、

前記誘電体障壁層の上にゲート金属の層を形成することと、

前記ゲート金属の層の上にハードマスク層を形成することと、

前記浮遊ゲートの上にハードマスクを形成するために前記金属シリサイドの上の前記ハードマスク層を取り除くことと、

前記浮遊ゲートの上に前記感知トランジスタの金属感知ゲートを形成するために前記ハードマスクにより露出された箇所の前記ゲート金属の層を取り除くことと、

前記金属感知ゲートを形成した後に前記金属シリサイドの上から前記誘電体障壁層を取り除くことと、

を含み、

前記シリサイドブロック誘電体材料の層と前記誘電体障壁層との組合せが前記感知トランジスタの頂部ゲート誘電体層を提供する、方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本願は、概して集積回路に関し、更に特定して言えば、集積回路におけるフラッシュメモリセルに関連する。

##### 【背景技術】

##### 【0002】

或る集積回路が、感知トランジスタの頂部ゲートが浮遊ゲートの上の金属プレートである、フラッシュメモリセルを含む。このフラッシュセルは、一つの余分のフォトリソグラフィオペレーションを附加することで、相補型金属酸化物半導体(CMOS)製造フローに統合され得る。頂部ゲートは、金属プレートをアンダーカットするウェットエッチングプロセスにより形成され、そのため浮遊ゲートが大型にされる必要がある。浮遊ゲートを大型にすることは、増大されるホットキャリア注入に起因して、フラッシュセルに対する信頼性の問題につながり得る。大型の浮遊ゲートは、効率的なホットキャリア注入プログラミングのために大きな横方向フィールドを要する。或るプロセスでは、必要とされる値を達成することが物理的に不可能である。6ボルト未満など、低ドレイン電圧での効率的な

10

20

30

40

50

H C I プログラミングを可能にするため、チャネル長が低減される必要がある。

【発明の概要】

【0 0 0 3】

記載される例において、集積回路がフラッシュセルを含み、感知トランジスタの頂部ゲートが、浮遊ゲートの上の金属感知ゲートである。感知トランジスタのソース／ドレイン領域は、ソース領域が、200ナノメートル未満、感知チャネル長によりドレイン領域から分離されるように、浮遊ゲートの下に延在する。金属感知ゲートは、ソース及びドレイン領域の上を浮遊ゲートを超えて延在しない。浮遊ゲートは少なくとも400ナノメートル幅であり、そのため、感知トランジスタのソース／ドレイン領域は、浮遊ゲートの下に各側で少なくとも100ナノメートル延在する。集積回路は、浮遊ゲートを形成する前に、感知トランジスタソース及びドレイン領域を形成することにより形成される。

10

【図面の簡単な説明】

【0 0 0 4】

【図1】例示の集積回路の断面図である。

【0 0 0 5】

【図2 A】例示の製造シーケンスの連続的な段階において示される、図1の集積回路の断面図である。

【図2 B】例示の製造シーケンスの連続的な段階において示される、図1の集積回路の断面図である。

【図2 C】例示の製造シーケンスの連続的な段階において示される、図1の集積回路の断面図である。

20

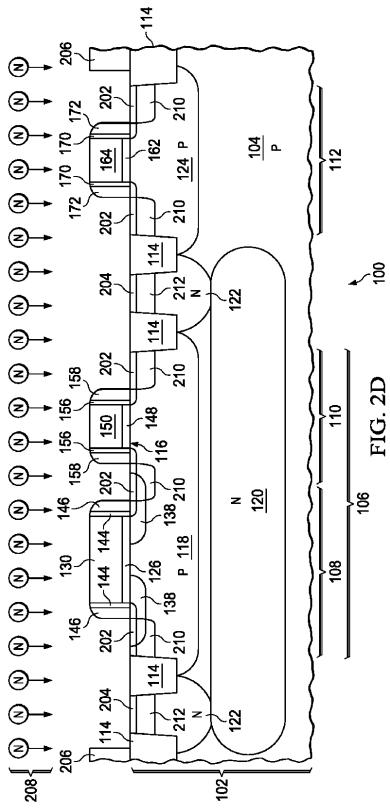

【図2 D】例示の製造シーケンスの連続的な段階において示される、図1の集積回路の断面図である。

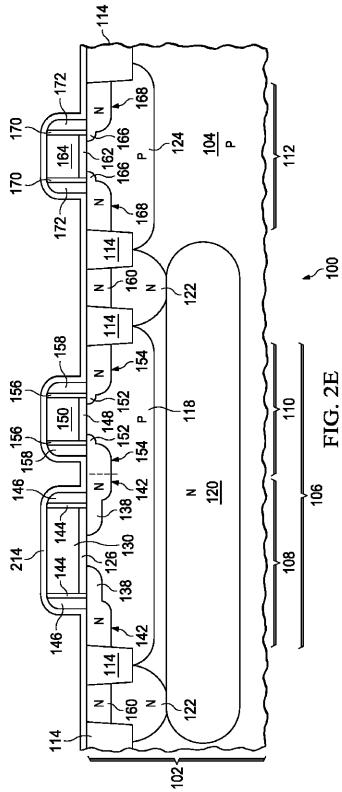

【図2 E】例示の製造シーケンスの連続的な段階において示される、図1の集積回路の断面図である。

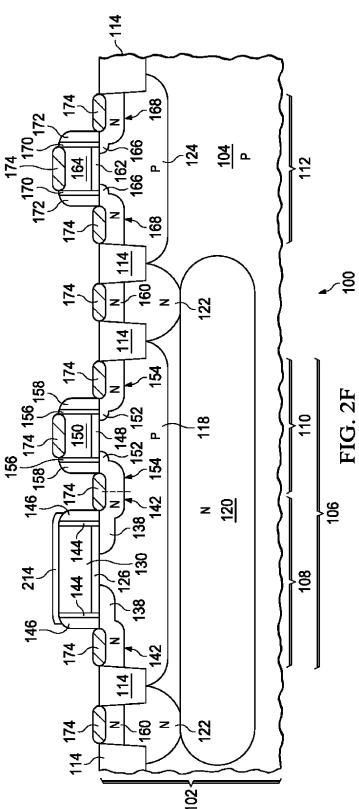

【図2 F】例示の製造シーケンスの連続的な段階において示される、図1の集積回路の断面図である。

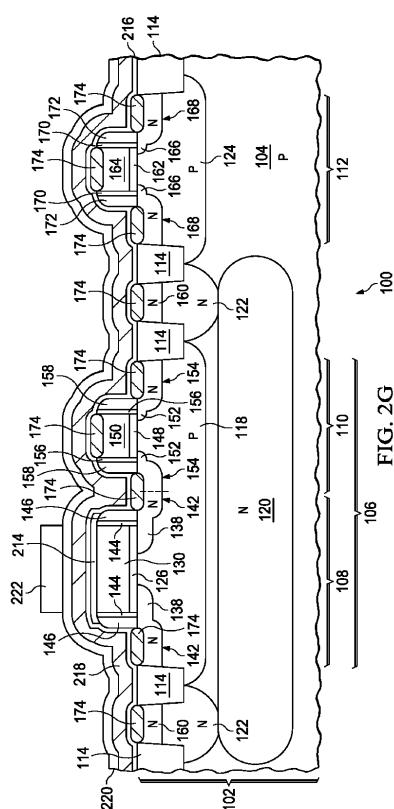

【図2 G】例示の製造シーケンスの連続的な段階において示される、図1の集積回路の断面図である。

【図2 H】例示の製造シーケンスの連続的な段階において示される、図1の集積回路の断面図である。

30

【図2 I】例示の製造シーケンスの連続的な段階において示される、図1の集積回路の断面図である。

【図2 J】例示の製造シーケンスの連続的な段階において示される、図1の集積回路の断面図である。

【発明を実施するための形態】

【0 0 0 6】

図面は一定の縮尺で描いてはいない。幾つかの行為は、異なる順序で、及び／又は他の行為又は事象と同時に成されてもよい。また、全ての図示した行為又は事象が、例示の実施例に従った手法を実装する必要はない。

40

【0 0 0 7】

集積回路がフラッシュセルを含み、感知トランジスタの頂部ゲートが、浮遊ゲートの上の金属感知ゲートである。感知トランジスタのソース／ドレイン領域は、ソース領域が、200ナノメートル未満、感知チャネル長によりドレイン領域から分離されるように、浮遊ゲートの下に途中まで延在する。金属感知ゲートは、ソース及びドレイン領域の上を浮遊ゲートを超えて延在しない。浮遊ゲートは、少なくとも400ナノメートル幅であり、そのため、感知トランジスタのソース／ドレイン領域は、各側で少なくとも100ナノメートル、浮遊ゲートの下に延在する。集積回路は、浮遊ゲートを形成する前に、感知トランジスタソース及びドレイン領域を形成することにより形成される。

【0 0 0 8】

50

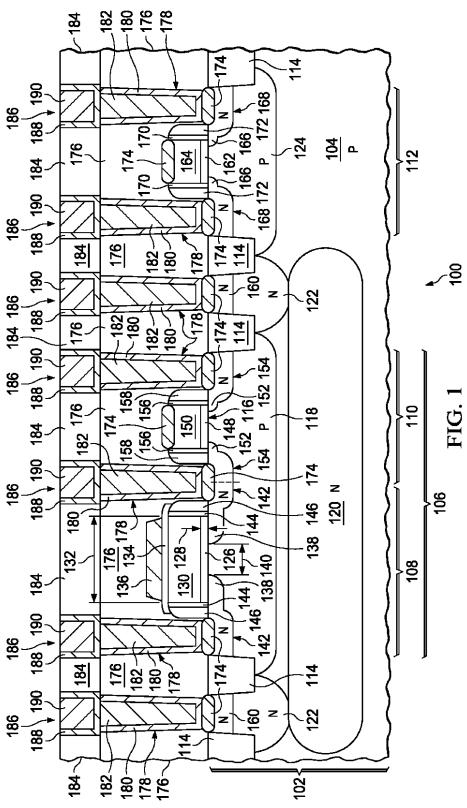

図1は例示の集積回路の断面図である。集積回路100は、半導体材料104を含む基板102上に形成される。例えば、基板102は単結晶シリコンであり得る。半導体材料104も単結晶シリコンであり得る。この例では、半導体材料104はp型である。集積回路100はフラッシュメモリ106を含み、フラッシュメモリ106は、少なくとも一つの感知トランジスタ108を有し、アクセストランジスタ110を有し得る。この例では、感知トランジスタ108及びアクセストランジスタ110は、nチャネル金属酸化物半導体(NMOS)トランジスタである。集積回路100はまた、フラッシュメモリ106から離れた、少なくとも一つの論理NMOSトランジスタ112を含み得る。フィールド酸化物114が、集積回路100の構成要素を横方向に隔離するように基板102の頂部表面116において配置される。感知トランジスタ108及びアクセストランジスタ110は、基板102における隔離されたp型ウェル118において配置される。隔離されたp型ウェル118は、隔離されたp型ウェル118の下の基板102に配置されるディープn型ウェル120と、隔離されたp型ウェル118を横方向に囲むn型ウェル122との組み合わせにより電気的に隔離される。論理NMOSトランジスタ112は、基板102のp型半導体材料104に接するp型ウェル124に配置される。

#### 【0009】

感知トランジスタ108は、隔離されたp型ウェル118において基板102の頂部表面116上の厚み128を有するゲート誘電体層126、及びゲート誘電体層126上の幅132を有する浮遊ゲート130を含む。ゲート誘電体層126の厚み128は、3.0ナノメートル未満であり、1.5ナノメートル～2.5ナノメートルであり得る。例えば、浮遊ゲート130は、本明細書においてポリシリコンと称する多結晶シリコンであり得る。幅132は少なくとも400ナノメートルである。頂部ゲート誘電体層134が、浮遊ゲート130の幅132にわたって延在して、浮遊ゲート130の上に配置され、頂部ゲート誘電体層134の上に金属感知ゲート136が配置される。金属感知ゲート136は、感知トランジスタ108のソース及びドレイン側で浮遊ゲート130を超えて延在しない。例えば、金属感知ゲート136は、40ナノメートル～80ナノメートルの厚みであり得る。n型感知ソース／ドレイン領域138は、隔離されたp型ウェル118に配置され、浮遊ゲート130の下に途中まで延在する。感知ソース／ドレイン領域138は、浮遊ゲート130の下で感知チャネル長140により分離される。感知チャネル長140は200ナノメートル未満であり、そのため、感知ソース／ドレイン領域138は、感知トランジスタ108の各ソース及びドレイン側で少なくとも100ナノメートル、浮遊ゲート130の下に延在する。例えば、類似の論理トランジスタのソース／ドレイン領域が、各ソース及びドレイン側で、対応する論理ゲートの下に25ナノメートル未満、延在し得る。感知ソース／ドレイン領域138は、浮遊ゲート130の外方に配置されるディープソース／ドレイン部分142を含み得る。オフセットスペーサ144が、浮遊ゲート130の側壁上に配置され、ソース／ドレイン側壁スペーサ146が、オフセットスペーサ144上に配置される。

#### 【0010】

アクセストランジスタ110は、隔離されたp型ウェル118における基板102の頂部表面116上に配置されるゲート誘電体層148と、ゲート誘電体層148上のゲート150とを含む。ゲート誘電体層148は、感知トランジスタ108のゲート誘電体層126と同じ組成及び厚みを有する。ゲート150は、感知トランジスタ108の浮遊ゲート130と同じ組成を有する。n型アクセスソース／ドレイン領域152が、隔離されたp型ウェル118に配置され、ゲート150の下に途中まで延在する。アクセスソース／ドレイン領域152は、感知ソース／ドレイン領域138が浮遊ゲート130の下に延在するほど遠くまでゲート150の下に延在しない。例えば、アクセスソース／ドレイン領域152は、浮遊ゲート130の下に25ナノメートル未満、延在し得る。アクセスソース／ドレイン領域152は、ゲート150の外方に配置されるディープソース／ドレイン部分154を含む。アクセストランジスタ110のディープソース／ドレイン部分154は、感知トランジスタ108のディープソース／ドレイン部分142と同様のドーピング分

10

20

30

40

50

布を有する。感知トランジスタ 108 に近接するアクセスソース／ドレイン領域 152 は、想像線により図 1 に示すようにアクセストランジスタ 110 に近接する感知ソース／ドレイン領域 138 と連続的である。ゲート 150 の側壁上にオフセットスペーサ 156 が配置され、オフセットスペーサ 156 上にソース／ドレイン側壁スペーサ 158 が配置される。

#### 【0011】

感知トランジスタ 108 及びアクセストランジスタ 110 を囲む n 型ウェル 122 における基板 102 の頂部表面 116において、n 型コンタクト領域 160 が配置され得る。コンタクト領域 160 は、感知トランジスタ 108 のディープソース／ドレイン部分 142 及びアクセストランジスタ 110 のディープソース／ドレイン部分 154 と同様のドーピング分布を有し得る。10

#### 【0012】

論理 NMOS トランジスタ 112 は、p 型ウェル 124 における基板 102 の頂部表面 116 上に配置されるゲート誘電体層 162、及びゲート誘電体層 162 上のゲート 164 を含む。ゲート誘電体層 162 は、感知トランジスタ 108 のゲート誘電体層 126 と同じ組成及び厚みを有する。ゲート 164 は、感知トランジスタ 108 の浮遊ゲート 130 と同じ組成を有する。n 型論理ソース／ドレイン領域 166 が、p 型ウェル 124 に配置され、ゲート 164 の下に途中まで延在する。論理ソース／ドレイン領域 166 は、感知ソース／ドレイン領域 138 が浮遊ゲート 130 の下に延在するほど遠くまでゲート 164 の下に延在しない。論理ソース／ドレイン領域 166 は、ゲート 164 の外方に配置されるディープソース／ドレイン部分 168 を含む。論理 NMOS トランジスタ 112 のディープソース／ドレイン部分 168 は、感知トランジスタ 108 のディープソース／ドレイン部分 142 と同様のドーピング分布を有する。ゲート 164 の側壁上にオフセットスペーサ 170 が配置され、オフセットスペーサ 170 上にソース／ドレイン側壁スペーサ 172 が配置される。20

#### 【0013】

金属シリサイド 174 が、感知トランジスタ 108 のディープソース／ドレイン部分 142、アクセストランジスタ 110 のディープソース／ドレイン部分 154、n 型ウェル 122 におけるコンタクト領域 160、及び論理 NMOS トランジスタ 112 のディープソース／ドレイン部分 168 など、露出されたシリコン上の基板 102 の頂部表面 116 において、及び任意選択で、アクセストランジスタ 110 のゲート 150 及び論理 NMOS トランジスタ 112 のゲート 164 上に、配置され得る。金属シリサイド 174 は、感知トランジスタ 108 の浮遊ゲート 130 上に配置されない。30

#### 【0014】

プレメタル誘電体（PMD）層 176 が、基板 102 の頂部表面 116 の上、並びに、金属シリサイド 174、感知トランジスタ 108、アクセストランジスタ 110、及び論理 MOS トランジスタ 112 の上に配置される。PMD 層 176 は層スタックであり得、この層スタックは、シリコン窒化物の PMD ライナーと、ボロンリン珪酸ガラス（BPSG）又は二酸化シリコンのメイン層と、シリコン窒化物、シリコンカーバイド、シリコンカーバイド窒化物、又は、タングステン化学機械研磨（CMP）プロセスのためのストップ層に適したその他のハード誘電体材料のキャップ層とを含み得る。金属シリサイド 174 を介する、感知トランジスタ 108、アクセストランジスタ 110、及び論理 NMOS トランジスタ 112 への電気的接続を提供するために、PMD 層 176 を通してコンタクト 178 が配置される。コンタクト 178 は、PMD 層 176 に接するチタン及びチタン窒化物のコンタクトライナー 180 と、コンタクトライナー 180 上のタングステンのコンタクト充填金属 182 とを含む。コンタクト 178 は、PMD 層 176 を通してコンタクトホールを形成すること、コンタクトホールの側壁及び底部上にコンタクトライナー 180 を形成すること、及びコンタクトライナー 180 上にコンタクト充填金属 182 の層を形成すること、及びその後、金属 CMP プロセス又はエッチバックプロセスなどによって、PMD 層 176 の頂部表面からコンタクト充填金属 182 及びコンタクトライナー 1840

0を取り除くことによって形成され得る。

【0015】

PMD層176上に金属間誘電体（IMD）層184が配置される。IMD層184は、シリコンカーバイド又はシリコンカーバイド窒化物のエッチストップ層と、有機シリケートガラス（OSG）などの二酸化シリコン又は低k誘電体材料のメイン層と、シリコン窒化物、シリコンカーバイド、シリコンカーバイド窒化物、又は銅CMPプロセスのためのストップ層に適したその他のハード誘電体材料のキャップ層とを含み得る。コンタクト178への電気的接続を提供するために、金属相互接続186がIMD層184を通して配置される。金属相互接続186は銅ダマシン構造を有し、この銅ダマシン構造は、IMD層184に接し、コンタクト178への接続を成す、タンタル窒化物のトレニチライナー188と、トレニチライナー188上の銅充填金属190とを備える。金属相互接続186は、銅ダマシンプロセスにより形成され得、銅ダマシンプロセスは、IMD層184を通して相互接続トレニチを形成すること、相互接続トレニチの側壁及び底部上にトレニチライナー188を形成すること、スパッタリングによりトレニチライナー188上に銅充填金属190の第1の部分として銅シード層を形成すること、銅シード層上に銅充填金属190の第2の部分として電気めつきにより充填銅層を形成すること、及びその後、銅CMPプロセスにより銅充填金属190及びトレニチライナー188を取り除くことを含み得る。

10

【0016】

感知トランジスタ108の金属感知ゲート136は、コンタクト178のコンタクトライナー180に類似する、又は金属相互接続186のトレニチライナー188に類似する組成を有し得、反応性スパッタツール又は原子層堆積ツールなど、同じツールにおいて形成され得る。コンタクトライナー180又はトレニチライナー188と同じツールにおいて金属感知ゲート136を形成することは、有利にも、集積回路100の製造コストを低減し得る。

20

【0017】

集積回路100のオペレーションの間、感知トランジスタ108は、浮遊ゲート130の下の感知チャネル長140が200ナノメートル未満であること起因して、所望のレベルの信頼性を示し得る。感知トランジスタ108は、浮遊ゲート130の幅132が少なくとも400ナノメートルであるので、1ミリ秒よりずっと短いプログラム時間及び所望の低プログラム電圧を有し得、金属感知ゲート136を画定するためのウェットエッチングプロセスによるアンダーカットに因る幅低減の後の金属感知ゲート136のための充分な幅が可能となる。データ保持及び持続性もまた、浮遊ゲートの幅が300ナノメートル未満である感知トランジスタよりも著しく優れたものとなり得る。

30

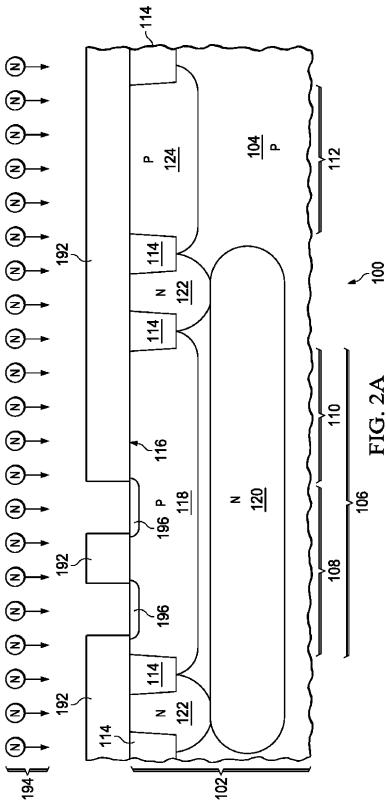

【0018】

図2A～図2Jは、例示の製造シーケンスの連続的な段階において示される、図1の集積回路の断面図である。図2Aを参照すると、集積回路100が基板102内及び上に形成される。例えば、基板102はシリコンウェハであり得る。半導体材料104は、バルクシリコンウェハの頂部であり得、又は、バルクシリコンウェハ上に形成されるエピタキシャル層であり得る。例えば、フィールド酸化物114は、シャロートレンチアイソレーション（STI）プロセスにより形成される。その後、ディープn型ウェル120が、n型ドーパント（リンなど）を基板102内に注入することによって形成され得る。例えば、 $1000 \text{ keV} \sim 1500 \text{ keV}$ のエネルギーで $2 \times 10^{12} \text{ cm}^{-2} \sim 5 \times 10^{12} \text{ cm}^{-2}$ のドーズ量での、フォトレジストを含む注入マスクを用いる注入が、基板102の頂部表面116の1ミクロン～1.5ミクロン下に所望のピークドーパント分布を生成し得る。隔離されたp型ウェル118及びp型ウェル124が、 $250 \text{ keV} \sim 350 \text{ keV}$ のエネルギーで $5 \times 10^{12} \text{ cm}^{-2} \sim 1 \times 10^{13} \text{ cm}^{-2}$ のドーズ量で、フォトレジストを含む注入マスクを用いてボロンなどのp型ドーパントを基板102内に注入することにより形成され得、これにより、基板102の頂部表面116の0.6ミクロン～0.9ミクロン下にピークドーパント分布が生成される。感知トランジスタ108、アクセス

40

50

トランジスタ 110、及び論理MOSトランジスタ 112のためのパンチスルーレベル低減領域及び閾値調節領域を形成するために、付加的なp型ドーパントが同時に注入され得る。n型ウェル 122は、400 keV ~ 600 keV のエネルギーで  $5 \times 10^{12} \text{ cm}^{-2}$  ~  $2 \times 10^{13} \text{ cm}^{-2}$  のドーズ量で、フォトレジストを含む注入マスクを用いてn型ドーパント(リンなど)を基板 102 内に注入することにより形成され得、これにより、基板 102 の頂部表面 116 の 0.4 ミクロン ~ 0.8 ミクロン下にピークドーパント分布が生成される。その後、基板 102 は、注入されたドーパントを活性化するためにアニーリングされる。

#### 【0019】

感知ソース / ドレインマスク 192 が基板 102 の上に形成され、これは、図 1 の感知ソース / ドレイン領域 138 のためのエリアにおいて基板 102 を露出させる。感知ソース / ドレインマスク 192 は、感知ソース / ドレイン領域 138 のためのエリア間の基板 102 を覆う。感知ソース / ドレインマスク 192 は、任意選択で、n型ソース / ドレインエリア又はコンタクト領域のための他のエリアを露出させ得る。n型ドーパント 194 (リン及びヒ素など) が、30 keV ~ 70 keV のエネルギーで  $5 \times 10^{13} \text{ cm}^{-2}$  ~  $3 \times 10^{14} \text{ cm}^{-2}$  の総ドーズなどで、感知ソース / ドレインマスク 192 により露出された基板 102 に注入されて、感知ソース / ドレイン領域 138 のためのエリアにおいて感知ソース / ドレイン注入された領域 196 を形成する。その後、アッシングプロセス及びその後続くウェット洗浄プロセスなどにより、感知ソース / ドレインマスク 192 が取り除かれる。

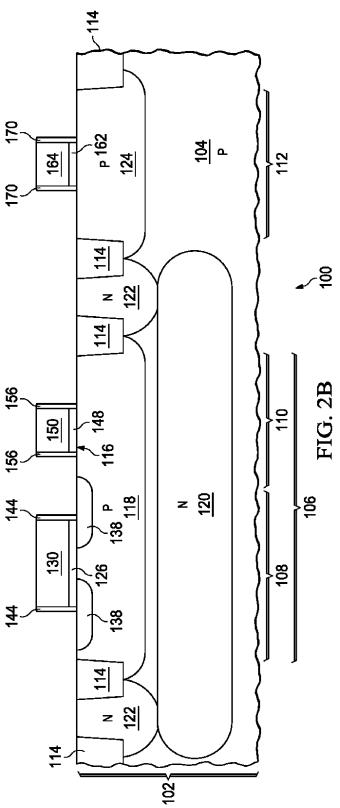

#### 【0020】

図 2B を参照すると、それぞれ、感知トランジスタ 108、アクセストランジスタ 110、及び論理NMOSトランジスタ 112 の、ゲート誘電体層 126、148、及び 162 が同時に形成される。ゲート誘電体層 126、148、及び 162 は、熱酸化により形成され得、及び任意選択で、窒素含有プラズマへの暴露などにより窒化され得る。ゲート誘電体層 126、148、及び 162 は、任意選択で、ハフニウム酸化物又はジルコニウム酸化物などの高k誘電体材料を含み得る。図 2A の感知ソース / ドレイン注入された領域 196 における注入されたドーパントは、感知ソース / ドレイン領域 138 を形成するため、ゲート誘電体層 126、148、及び 162 の形成の間、少なくとも部分的にアクティブにされ得る。

#### 【0021】

その後、感知トランジスタ 108 の浮遊ゲート 130、アクセストランジスタ 110 のゲート 150、及び論理NMOSトランジスタ 112 のゲート 164 が、それぞれ、ゲート誘電体層 126、148、及び 162 上に同時に形成される。例えば、浮遊ゲート 130、ゲート 150、及びゲート 164 は、ゲート誘電体材料の共通層上にポリシリコンの層を  $150 \text{ ナノメートル} \sim 200 \text{ ナノメートル}$  の厚みで形成すること、nチャネルトランジスタのゲートのためのエリアにおいてポリシリコンの層を  $1 \times 10^{15} \text{ cm}^{-2}$  ~  $6 \times 10^{15} \text{ cm}^{-2}$  の総ドーズ量で n型ドーパント (リン及び場合によってはヒ素など) で注入することによって形成され得る。その後、ゲートエッチングマスクが、浮遊ゲート 130、ゲート 150、及びゲート 164 を含む、NMOSトランジスタのゲートのための、及び pチャネル金属酸化物半導体 (PMOS) トランジスタのゲートのためのエリアを覆うために、ポリシリコンの層の上に形成される。ポリシリコンの層は、浮遊ゲート 130、ゲート 150、及びゲート 164 を形成するためにポリシリコンを残して、反応性イオンエッチング (RIE) プロセスにより、ゲートエッチングマスクにより露出されたエリアにおいて取り除かれる。ゲート誘電体層 126、148、及び 162 の外のゲート誘電体材料の共通層は、RIE プロセスにより低減され又は取り除かれ得る。

#### 【0022】

オフセットスペーサ 144、156、及び 170 は、浮遊ゲート 130、ゲート 150、及びゲート 164 上に、場合によっては同時に、形成される。オフセットスペーサ 144、156、及び 170 は、熱酸化物を、及び任意選択でプラズマエンハンス化学気相成長

10

20

30

40

50

(P E C V D) によって形成される二酸化シリコン及び / 又はシリコン窒化物の一つ又は複数の層を、含み得る。

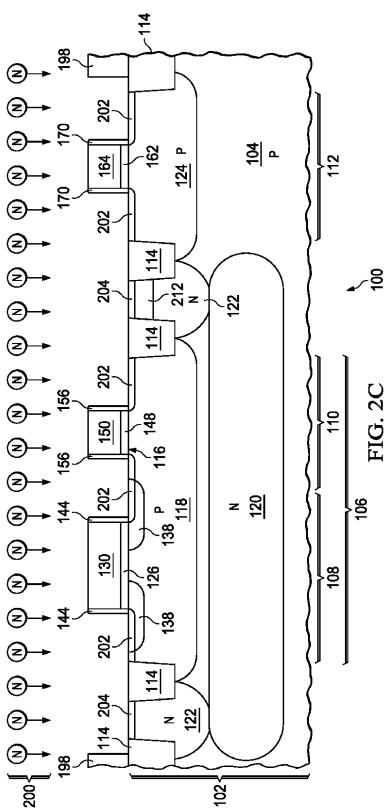

#### 【 0 0 2 3 】

図 2 C を参照すると、軽くドープされたドレインマスク 198 が、基板 102 の上に形成され、これは、浮遊ゲート 130、ゲート 150、及びゲート 164 に近接するエリア、及び任意選択で n 型ウェル 122 におけるエリアを露出させる。n 型ドーパント 200 (リン及び場合によってはヒ素など) が、30 keV ~ 60 keV のエネルギーで  $2 \times 10^{13} \text{ cm}^{-2} \sim 1 \times 10^{14} \text{ cm}^{-2}$  の総ドーズなどで、LDD マスク 198 により露出された基板 102 に注入されて、浮遊ゲート 130、ゲート 150、及びゲート 164 に近接するドレイン拡張注入された領域 202、並びに、n 型ウェル 122 におけるウェルタップ注入された領域 204 を形成する。浮遊ゲート 130、ゲート 150、及びゲート 164 は、n 型ドーパント 200 をブロックする。その後、LDD マスク 198 は、例えば図 2 A を参照して説明されるように、取り除かれる。10

#### 【 0 0 2 4 】

図 2 D を参照すると、ディープソース / ドレインマスク 206 が、基板 102 の上に形成され、これは、アクセストランジスタ 110 及び論理 NMOS ランジスタ 112 及び n 型ウェル 122 を露出させ、及び任意選択で、図 2 D に示されるように感知トランジスタ 108 を露出させ得る。n 型ドーパント 208 (リン及びヒ素など) が、40 keV ~ 70 keV のエネルギーで  $1 \times 10^{15} \text{ cm}^{-2} \sim 5 \times 10^{15} \text{ cm}^{-2}$  の総ドーズなどで、浮遊ゲート 130、ゲート 150、及びゲート 164 に近接する基板 102 内に、及び n 型ウェル 122 において注入されて、浮遊ゲート 130、ゲート 150、及びゲート 164 に近接するディープソース / ドレイン注入された領域 210 を形成し、及び n 型ウェル 122 におけるコンタクト注入された領域 212 を形成する。浮遊ゲート 130、ゲート 150、及びゲート 164 は、n 型ドーパント 208 をブロックする。その後、ディープソース / ドレインマスク 206 は、例えば図 2 A を参照して説明されるように、取り除かれる。20

#### 【 0 0 2 5 】

図 2 E を参照すると、基板 102 は、図 2 D のドレイン拡張注入された領域 202、ウェルタップ注入された領域 204、ディープソース / ドレイン注入された領域 210、及びコンタクト注入された領域 212 において、注入されたドーパントを活性化するためにアニーリングされて、感知ソース / ドレイン領域 138 のディープソース / ドレイン部分 142 を形成し、アクセスソース / ドレイン領域 152 のディープソース / ドレイン部分 154 を形成し、論理ソース / ドレイン領域 166 のディープソース / ドレイン部分 168 を形成し、及び、n 型ウェル 122 においてコンタクト領域 160 を形成する。基板 102 は、例えば、高速熱的処理 (RTP) ツールにおけるスパイクアニールプロセスにより、又はフラッシュアニールプロセスにより、又はレーザーアニールプロセスなどによりアニーリングされ得る。30

#### 【 0 0 2 6 】

シリサイドブロック誘電体材料 214 の層が、集積回路 100 の既存の頂部表面の上に形成される。例えば、シリサイドブロック誘電体材料 214 の層は、10 ナノメートル ~ 50 ナノメートルの総厚を有する、二酸化シリコン及び場合によってはシリコン窒化物の一つ又は複数のサブ層を含み得る。シリサイドブロック誘電体材料 214 の層において二酸化シリコンが、PECVD プロセスにより形成され得る。40

#### 【 0 0 2 7 】

図 2 F を参照すると、図 2 E のシリサイドブロック誘電体材料 214 の層は、図 1 の頂部ゲート誘電体層 134 の第 1 の部分を形成するために感知トランジスタ 108 の浮遊ゲート 130 を覆うように、及び感知ソース / ドレイン領域 138 のディープソース / ドレイン部分 142、アクセスソース / ドレイン領域 152 のディープソース / ドレイン部分 154、論理ソース / ドレイン領域 166 のディープソース / ドレイン部分 168、及び n 型ウェル 122 におけるコンタクト領域 160、アクセストランジスタ 110 のゲート 150

50、及び論理N M O Sトランジスタ112のゲート164を露出させるように、パターニングされる。シリサイドブロック誘電体材料214の層は、フォトリソグラフィプロセスによりエッティングマスクを形成すること、及びエッティングマスクにより露出された箇所のシリサイドブロック誘電体材料214の層をウェットエッティングプロセス又はR I Eプロセスにより取り除くことによって、パターニングされ得る。

#### 【0028】

シリサイドブロック誘電体材料214のパターニングされた層によって露出されたシリコン上に、金属シリサイド174が形成される。例えば、金属シリサイド174は、露出されたシリコン上に、チタン、コバルト、又はニッケルなどの耐火性金属の層を形成すること、及び、金属シリサイド174を形成するため露出されたシリコンを耐火性金属と反応させるために基板102を加熱することによって形成され得る。反応しなかった金属は、その後、硫酸及び過酸化水素の水溶性混合物、又は水酸化アンモニウム及び過酸化水素の水溶性混合物などのウェットエッティングプロセスによって取り除かれる。

10

#### 【0029】

図2Gを参照すると、誘電体障壁層216が、金属シリサイド174の上に形成され、及び図1の頂部ゲート誘電体層134の上に部分的に形成される。誘電体障壁層216は、5ナノメートル～20ナノメートルの厚みの二酸化シリコンの第1のサブ層と、二酸化シリコンの第1のサブ層上の5ナノメートル～20ナノメートルの厚みのシリコン窒化物のサブ層と、シリコン窒化物のサブ層上の5ナノメートル～20ナノメートルの厚みの二酸化シリコンの第2のサブ層とを含む層スタックであり得る。誘電体障壁層216における二酸化シリコンが、テトラエトキシシラン(TEOS)を用いるP E C V Dにより形成され得る。誘電体障壁層216におけるシリコン窒化物が、ビスター・シャリップチルアミノシラン(BT B A S)を用いるP E C V Dにより形成され得る。誘電体障壁層216のための他の層構造又は組成も本例の範囲内にある。例えば、誘電体障壁層216の総厚は20ナノメートル～40ナノメートルであり得る。

20

#### 【0030】

誘電体障壁層216上にゲート金属218の層が形成される。例えば、ゲート金属218の層は、40ナノメートル～80ナノメートルの厚みであり得、窒化タンタル、タンタル、チタン窒化物、又はチタンを含み得る。ゲート金属218におけるチタン及びタンタルの層が、スパッタリングにより形成され得る。ゲート金属218におけるタンタル窒化物及びチタン窒化物の層が、窒素雰囲気における反応性スパッタリング、又は原子層堆積により形成され得る。

30

#### 【0031】

ゲート金属218の層上にハードマスク層220が形成される。ハードマスク層220は、P E C V Dによって形成されるシリコン窒化物を含み得、25ナノメートル～50ナノメートルの厚みであり得る。

#### 【0032】

図1の金属感知ゲート136のためのエリアを覆うハードマスク層220の上に、ゲートマスク222が形成される。ゲートマスク222は、感知トランジスタ108のディープソース/ドレイン部分142の上及びアクセストランジスタ110及び論理M O Sトランジスタ112の上を含む、その他の箇所のハードマスク層220を露出させる。ゲートマスク222は、フォトリソグラフィプロセスによりフォトレジストで形成され得る。ゲートマスク222の幅が、ゲート金属218の層のウェットエッティングプロセスの間のアンダーカットを考慮して、金属感知ゲート136の所望の幅を提供するように選択される。図1を参照して説明されたように、少なくとも400ナノメートルの幅を有するように浮遊ゲート130を形成することは、有利にも、所望の金属感知ゲート136の幅を提供するために充分な幅を有してゲートマスク222が形成され得るようにする。

40

#### 【0033】

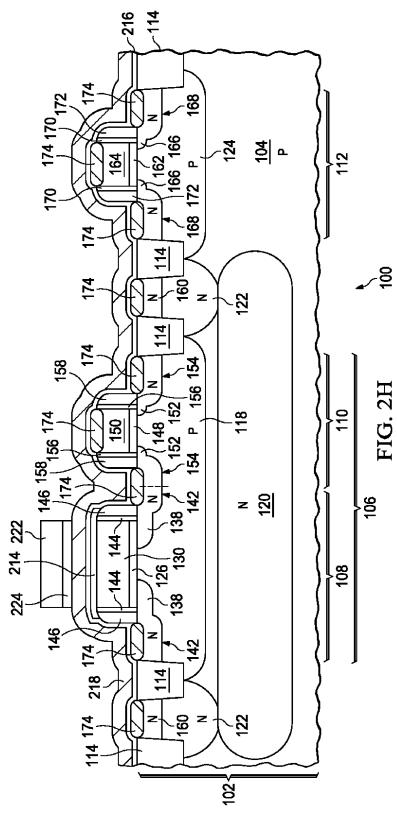

図2Hを参照すると、ハードマスク224を形成するためにゲートマスク222の下のハードマスク層220を残して、R I Eプロセスにより、ゲートマスク222により露出さ

50

れた箇所の図 2 G のハードマスク層 220 が取り除かれる。ゲートマスク 222 は、後続の金属ゲートエッチプロセスの間、取り除かれ得、又は、その場に残り得る。

【 0034 】

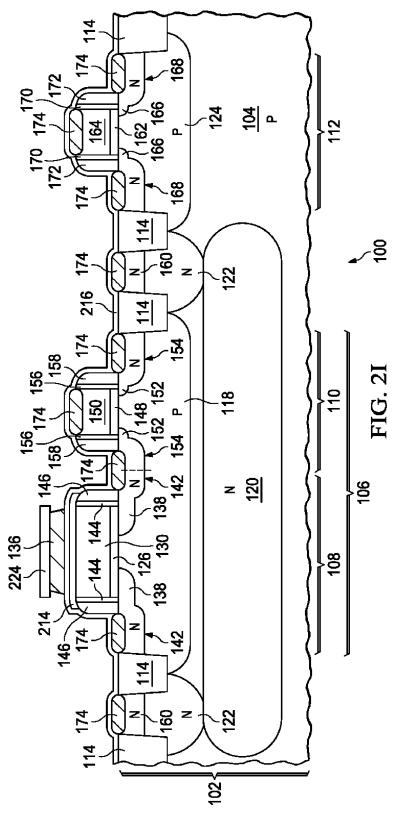

図 2 I を参照すると、金属感知ゲート 136 を提供するためにハードマスク 224 の下のゲート金属 218 の層を残して、ハードマスク 224 により露出された箇所の図 2 H のゲート金属 218 の層が取り除かれる。ゲート金属 218 の層は、濃縮水酸化アンモニウム及び過酸化水素の水溶性混合物を用いるウェットエッチングプロセスにより取り除かれ得る。ゲート金属 218 の層をエッチングするための他の方法も本例の範囲内である。図 2 H のゲートマスク 222 は、ウェットエッチングプロセスにより腐食され得、又は、図 2 I に示されるように完全に取り除かれ得る。ウェットエッチングプロセスは、ゲート金属 218 の層をアンダーカットし得る。誘電体障壁層 216 は、ゲート金属 218 の層の除去の間、金属シリサイド 174 を保護する。ハードマスク 224 が取り除かれ得る一方、誘電体障壁層 216 は、その場に残り、又は、後続の製造工程の間に取り除かれ得る。

10

【 0035 】

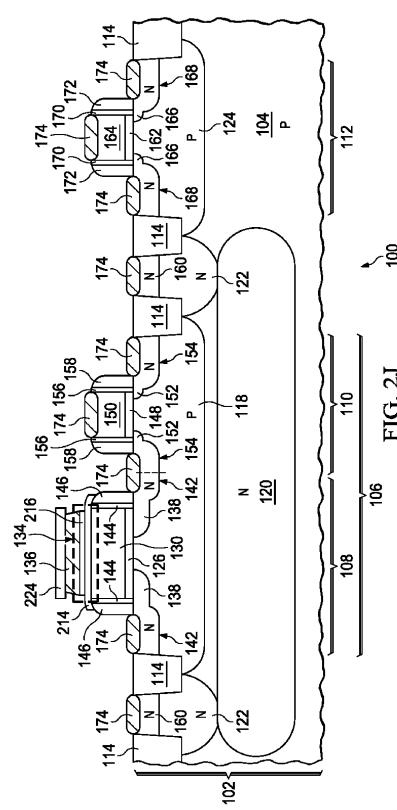

図 2 J を参照すると、金属感知ゲート 136 により露出された箇所の図 2 I の誘電体障壁層 216 が取り除かれる。誘電体障壁層 216 は、金属シリサイド 174 に対して選択的なプラズマエッチングプロセスにより取り除かれ得る。誘電体障壁層 216 は、頂部ゲート誘電体層 134 の第 2 の部分を提供するため、金属感知ゲート 136 の下に残る。シリサイドブロック誘電体材料 214 のパターニングされた層と誘電体障壁層 216 の組み合せが、頂部ゲート誘電体層 134 を提供する。

20

【 0036 】

若し残っている場合、ハードマスク 224 が取り除かれる。集積回路 100 の製造は、図 1 の PMD 層 176 の形成で継続する。そのため、フラッシュメモリ 106 が、一つの余分のフォトリソグラフィオペレーションで形成され、図 2 G のゲートマスク 222 により、3つの余分のフォトリソグラフィオペレーションを要する従来の埋め込みフラッシュメモリを備える等価の集積回路に比して、集積回路 100 のコストが有利に低減される。

【 0037 】

本発明の特許請求の範囲内で、説明した例示の実施例に変形が成され得、他の実施例が可能である。

30

40

50

【図面】

【図 1】

【図2A】

10

20

【図2B】

【図2C】

30

40

【図2D】

【図2E】

10

20

【図2F】

【図2G】

30

40

【図2H】

【図21】

【図2】

10

20

30

40

50

---

フロントページの続き

(51)国際特許分類 F I

H 01 L 29/788 (2006.01)

H 01 L 29/792 (2006.01)

審査官 宮本 博司

(56)参考文献 特開2008-205379 (JP, A)

特開2000-164736 (JP, A)

特開2015-070261 (JP, A)

特開2009-044053 (JP, A)

特開2013-197533 (JP, A)

特表2012-514346 (JP, A)

米国特許第06642111 (US, B1)

米国特許出願公開第2009/0134444 (US, A1)

特開2000-164835 (JP, A)

特開2012-186438 (JP, A)

特開平09-129837 (JP, A)

特開2009-016688 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H 01 L 27 / 11521

H 01 L 27 / 11541

H 01 L 27 / 11543

H 01 L 27 / 11546

H 01 L 21 / 336