(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3789051号

(P3789051)

(45) 発行日 平成18年6月21日(2006.6.21)

(24) 登録日 平成18年4月7日(2006.4.7)

(51) Int.C1.

F 1

|                          |                  |

|--------------------------|------------------|

| HO 1 L 27/108 (2006.01)  | HO 1 L 27/10 651 |

| HO 1 L 21/8242 (2006.01) | HO 1 L 27/04 C   |

| HO 1 L 27/04 (2006.01)   | C 23 C 16/40     |

| HO 1 L 21/822 (2006.01)  |                  |

| C 23 C 16/40 (2006.01)   |                  |

請求項の数 10 (全 12 頁)

(21) 出願番号 特願平11-55838

(22) 出願日 平成11年3月3日(1999.3.3)

(65) 公開番号 特開2000-124424 (P2000-124424A)

(43) 公開日 平成12年4月28日(2000.4.28)

審査請求日 平成14年11月27日(2002.11.27)

(31) 優先権主張番号 98P42715

(32) 優先日 平成10年10月13日(1998.10.13)

(33) 優先権主張国 韓国(KR)

(73) 特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区梅灘洞416

416, Maetan-dong, Yeongtong-gu, Suwon-si

Gyeonggi-do, Republic

of Korea

(74) 代理人 100072349

弁理士 八田 幹雄

(74) 代理人 100102912

弁理士 野上 敦

(74) 代理人 100110995

弁理士 奈良 泰男

最終頁に続く

(54) 【発明の名称】部分的に異なる厚さを有するキャパシタの誘電膜の形成方法

## (57) 【特許請求の範囲】

## 【請求項1】

(a) 表面に屈曲型結晶粒によって曲率半径が比較的に大きな凸部と曲率半径が比較的に小さな凹部が形成されている下部電極上に誘電膜の形成に必要な第1反応物を供給し、前記第1反応物の少なくとも1個の構成原子が前記下部電極の表面に化学的に結合されてなった化学的吸着層と前記第1反応物の少なくとも1個の構成物質が前記化学的吸着層上に物理的に結合されてなった物理的吸着層を形成する段階と、

(b) 前記凹部でのみ前記物理的吸着層の一部が前記化学的吸着層上に残存するように前記物理的吸着層の残り一部を除去する段階と、

(c) 前記化学的吸着層及び前記残存する物理的吸着層を前記誘電膜の形成に必要な第2反応物と反応させ、前記下部電極の表面に前記凸部上より前記凹部上にさらに厚く薄膜を形成する段階とを含むことを特徴とするキャパシタの誘電膜の形成方法。 10

## 【請求項2】

前記第1反応物は  $\text{Al}(\text{CH}_3)_3$  であり、前記第2反応物は  $\text{H}_2\text{O}$  であり、前記誘電膜は  $\text{Al}_2\text{O}_3$  膜であることを特徴とする請求項1に記載のキャパシタの誘電膜の形成方法。

## 【請求項3】

前記段階(b)で前記物理的吸着層の残り一部は不活性ガスを使用してバージング方法によって除去されることを特徴とする請求項1に記載のキャパシタの誘電膜の形成方法。

## 【請求項4】

前記段階(b)で前記物理的吸着層の残り一部はポンピングによって除去されることを特 20

徴とする請求項 1 に記載のキャパシタの誘電膜の形成方法。

【請求項 5】

所望の厚さの前記誘電膜が得られるまで前記段階 ( a ) ないし段階 ( c ) を所定回数繰り返すことを特徴とする請求項 1 に記載のキャパシタの誘電膜の形成方法。

【請求項 6】

前記段階 ( c ) は、

( c - 1 ) 前記物理的吸着層の残り一部が除去された結果物上に前記第 2 反応物を供給し、前記化学的吸着層及び前記残存する物理的吸着層と化学的に反応させる段階と、

( c - 2 ) 前記段階 ( c - 1 ) から発生された反応副産物を除去する段階とを含むことを特徴とする請求項 1 に記載のキャパシタの誘電膜の形成方法。 10

【請求項 7】

前記段階 ( c - 2 ) で前記反応副産物は不活性ガスを使用してバージング方法によって除去されることを特徴とする請求項 6 に記載のキャパシタの誘電膜の形成方法。

【請求項 8】

前記段階 ( c - 2 ) で前記反応副産物はポンピングによって除去されることを特徴とする請求項 6 に記載のキャパシタの誘電膜の形成方法。

【請求項 9】

前記段階 ( a ) ないし段階 ( c ) は 300 の温度で行なわれることを特徴とする請求項 2 に記載のキャパシタの誘電膜の形成方法。

【請求項 10】 20

前記段階 ( a ) ないし段階 ( c ) は 1 ないし 5 Torr の圧力下で行なわれることを特徴とする請求項 2 に記載のキャパシタの誘電膜の形成方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は半導体素子の製造方法に係り、特にキャパシタの誘電膜の形成方法に関する。

【0002】

【従来の技術】

DRAM 素子の高集積化によって単位メモリセルの面積が小さくなり、それによって素子動作のための十分なセルキャパシタンスを有するキャパシタを製造する必要がある。 30

【0003】

半導体メモリ装置のキャパシタンスはメモリ装置の記憶容量を決定する重要な変数であって、キャパシタンスの減少はメモリセルの読み出し能力を低下させてソフトエラー率を増加させる。したがって、半導体メモリ装置の高集積化のためには必ず特定値以上のセルキャパシタンスを確保すべきである。

【0004】

制限されたセル面積内でキャパシタンスを増加させるための多くの方法が提案された。その中、下部電極の表面に屈曲型結晶粒としていわゆる HSG ( Hemispherical Grain ) を成長させることによって電極の表面積を増加させてキャパシタの有効面積を広げる方法が多用されている。 40

【0005】

通常、キャパシタのキャパシタンスは誘電膜の厚さに反比例して、誘電膜と電極との接触面積に正比例する。したがって、誘電膜の厚さを最小化して誘電膜と電極との接触面積を最大化する必要がある。このためには、下部電極上に誘電膜を形成する時優秀なステップカバレージ ( step coverage ) を得ることが重要である。

【0006】

特に、前記のように屈曲型結晶粒が形成された下部電極上に誘電膜を形成する時には大きなキャパシタンスを得ると同時に漏れ電流を抑制するために優秀なステップカバレージを得ることは必須である。

【0007】 50

しかし、従来の CVD (Chemical Vapor Deposition) または PVD (Physical Vapor Deposition) 方法を利用して誘電膜を形成すれば優秀なステップカバレージを得にくく。特に、従来の CVD 方法においては、サーフェイスカイネチックモード (surface kinetic mode) を活用する蒸着工程によって比較的優秀なステップカバレージを有する誘電膜を得ることはできるが、誘電膜の蒸着に必要な反応物が基板上に同時に伝達されるので特定の部分におけるステップカバレージを必要によって調節することはむずかしい。

#### 【0008】

特に、屈曲型結晶粒が形成された 3 次元形状の下部電極のように凹凸状に段差が形成された構造物上では優秀なステップカバレージを得にくく、段差の低い凹部に蒸着される膜厚が薄くなりやすい。

10

#### 【0009】

一方、下部電極に屈曲型結晶粒が形成されたキャパシタにおいて電極の表面中曲率半径の小さな部分では曲率半径の大きな部分より電位 (electric potential) が大きく作用する。

#### 【0010】

通常、下部電極に屈曲型結晶粒が形成されたキャパシタにより形成されるスフェリカルキャパシタ (spherical capacitor) において、電位はキャパシタを構成する二つの電極の曲率半径の差に正比例して、各曲率半径の積に反比例する。反面、キャパシタンスはキャパシタを構成する二つの電極の曲率半径の差に反比例し、各曲率半径の積に正比例する。この際、キャパシタンスはキャパシタの全体面積に渡って影響を受ける反面、電位によって現れる漏れ電流の特性はキャパシタの全体面積中最も脆弱な部分、すなわち電極の表面中屈曲型結晶粒によって形成された曲率半径が小さな部分により決定される。すなわち、下部電極に屈曲型結晶粒が形成されたキャパシタにおいて、電極の表面中曲率半径が小さな部分では曲率半径が大きな部分より電位が大きく作用するので漏れ電流がさらに多く流れる。

20

#### 【0011】

前記のようにキャパシタ電極の曲率半径が小さな部分は下部電極の表面にある屈曲型結晶粒の間に形成される複数の凹部に該当する部分である。これら凹部は従来の蒸着方法によって誘電膜を形成する時、屈曲型結晶粒によって形成される凸部に比べて誘電膜が薄く形成される恐れがある。このように、誘電膜が薄く形成された部分へ集中する電位によって漏れ電流が増えることを防止するために、曲率半径が小さな凹部における誘電膜を十分に厚く形成しようとする時、従来の誘電膜の形成方法によれば所望しない部分の誘電膜までも必要以上に厚くなり、所望のキャパシタンスが得られなくなる。

30

#### 【0012】

その結果、従来の誘電膜の形成方法によれば、優秀なステップカバレージを得にくく、優秀なステップカバレージを得たとしても曲率半径の小さな凹部で現れる漏れ電流の増加現象は解決できない。

#### 【0013】

##### 【発明が解決しようとする課題】

本発明の目的は前記従来の問題点を解決するために、下部電極の表面に屈曲型結晶粒が形成されたキャパシタで電位が強く作用する部分から発生される漏れ電流を最大限抑制すると同時に素子動作に必要なセルキャパシタンスを十分に確保することができる誘電膜の形成方法を提供することである。

40

#### 【0014】

##### 【課題を解決するための手段】

前記目的を達成するための本発明に係るキャパシタの誘電膜の形成方法は、表面に屈曲型結晶粒によって曲率半径が比較的大きな凸部と曲率半径が比較的小さな凹部が形成されている下部電極上に誘電膜の形成に必要な第 1 反応物を供給し、前記第 1 反応物の少なくとも 1 個の構成原子が前記下部電極の表面に化学的に結合されてなった化学的吸着層 (chemical adsorption layer) と前記第 1 反応物の少なくとも 1 個の構成物質が前記化学的吸着層上

50

に物理的に結合されてなった物理的吸着層 ( physisorption layer ) を形成する。前記凹部でのみ前記物理的吸着層の一部が前記化学的吸着層上に残存するように前記物理的吸着層の残り一部を取り除く。前記化学的吸着層及び前記残存する物理的吸着層を前記誘電膜の形成に必要な第2反応物と反応させ、前記下部電極の表面に前記凸部上より前記凹部上にさらに厚く薄膜を形成する。

【0015】

好ましくは、前記第1反応物は  $\text{Al}(\text{CH}_3)_3$  であり、前記第2反応物は  $\text{H}_2\text{O}$  であり、前記誘電膜は  $\text{Al}_2\text{O}_3$  膜である。

【0016】

前記物理的吸着層の残り一部は不活性ガスを使用してパージング ( purging ) 方法によつて除去されたり、またはポンピング ( pumping out ) によって除去される。 10

【0017】

前記本発明に係るキャパシタの誘電膜の形成方法を所定回数繰り返して所望の厚さの前記誘電膜を得ることができる。

【0018】

前記薄膜を形成するために、まず前記物理的吸着層の残り一部が除去された結果物上に前記第2反応物を供給し、前記化学的吸着層及び前記残存する物理的吸着層と化学的に反応させてから前記反応副産物を取り除く。

【0019】

前記反応副産物を除去するために不活性ガスを使用してパージングしたり、またはポンピングによって前記反応副産物を取り除く。 20

【0020】

前記誘電膜として  $\text{Al}_2\text{O}_3$  膜を形成するために、前記工程温度は 300 、工程圧力は 1 ないし 5 Torr とする。

【0021】

本発明によれば、素子動作に必要なセルキャパシタンスを十分に確保すると同時に曲率半径が小さな凹部で強く作用する電位による漏れ電流の増加現像を防止しうる。

【0022】

【発明の実施の形態】

以下、本発明の好ましい実施例に対して添付図面を参照して詳しく説明する。 30

【0023】

キャパシタの二つの電極の間に一定な電位が存在すれば、誘電膜を通して流れる漏れ電流は誘電膜が厚いほど減少する。したがって、本発明ではキャパシタの誘電膜の中でほかの部分より電位が大きくて漏れ電流の特性が劣悪な部分、すなわち屈曲型結晶粒が形成された下部電極上で曲率半径が小さな凹部にのみ選択的に誘電膜をほかの部分より厚く形成することによってキャパシタ全体で必要とするキャパシタンスを十分に確保しながらキャパシタ全体の漏れ電流の特性を改善しようとする。

【0024】

上述したように、サーフェスカイナチックモードを活用する従来の CVD 蒸着工程では誘電膜の蒸着に必要な反応物が基板上に同時に伝達されるので特定の部分におけるステップカバレージを必要によって調節しにくい。 40

【0025】

しかし、本発明では誘電膜の蒸着に必要なそれぞれの反応物をガスパルシング ( gas pulsing ) 方法で順次に基板上に供給することによって複数の原子層により高純度の誘電膜を形成する A L D ( Atomic Layer Deposition ) 方法を利用する。ここで、ガスパルシング方法は反応ガスとパージングガスを交代に供給する方法を意味する。

【0026】

通常、 A L D 方法による薄膜形成方法では厚さ調節が容易で優秀なステップカバレージが得られる。本発明では A L D 方法によって誘電膜の蒸着に必要な反応ガスを順次に基板上に供給して屈曲型結晶粒が形成された下部電極の表面に化学的吸着層及び物理的吸着層を 50

形成させた後、パージング時間を調節することによって下部電極の表面中曲率半径が小さな凹部では前記物理的吸着層を完全に除去せず残す方法によって他部より厚い膜が形成されるようとする。その結果、ALD方法によって形成された誘電膜の中で下部電極の表面中曲率半径が大きい凸部上には100%の優秀なステップカバレージを有する誘電膜を形成できると同時に曲率半径が小さな凹部上にはその増えた厚さによって100%を越えるステップカバレージを有する誘電膜を形成することができる。したがって、曲率半径が小さな凹部上に増えた厚さの誘電膜が形成されることによって、曲率半径が小さな凹部で強く作用する電位による漏れ電流の増加現像を防止できる。

【0027】

本明細書の全般に渡って記載された用語”ステップカバレージ”は凹部及び凸部によって3次元形状の表面を有する下地膜上に形成される薄膜において、前記凹部に形成される前記薄膜の厚さd1と前記凸部に形成される前記薄膜の厚さd2の百分率、すなわちd1/d2×100で定義される。

【0028】

本発明はALD方法のみならずサイクリック(cyclic)CVD、デジタル(digital)CVD、アドバンスト(advanced)CVD等のようにそれぞれの反応物を周期的に供給してパージングする段階を繰り返して行なう蒸着法であればいかなる方法でも適用可能である。

【0029】

便宜上、本実施例ではALD方法によって誘電膜を形成する方法に対して説明する。本発明は前記他の方法に対しても同様に適用可能なのはもちろんである。

【0030】

本発明では特定の部分で増えた厚さを有する誘電膜を形成するためにALD方法におけるパージング効率を減少させる方法を利用する。この方法によって部分的に厚くなつた誘電膜を形成しても得られた誘電膜の物性はそれほど変化しないとのことは次の実験結果から確認することができる。

【0031】

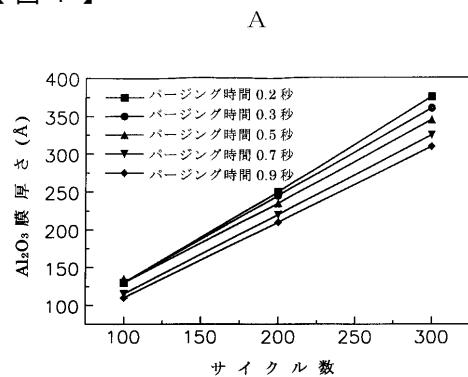

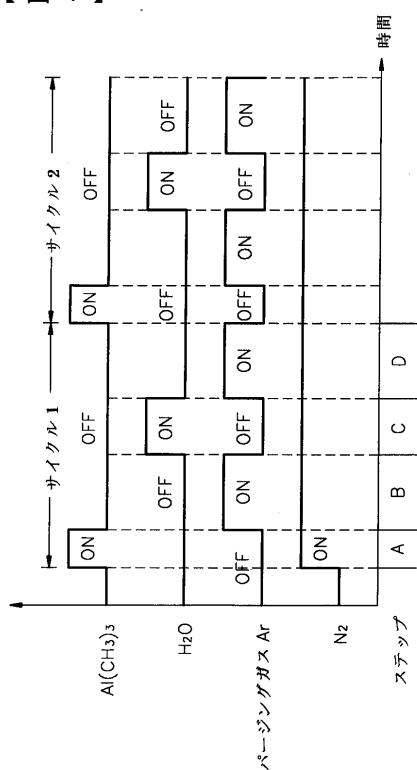

図1のAはALD方法によってキャパシタの誘電膜を形成する時多様なパージング時間に對して適用された工程サイクル数と得られた誘電膜の厚さとの関係を示したグラフである。

【0032】

具体的に説明すれば、ALD方法によって誘電膜、すなわちAl<sub>2</sub>O<sub>3</sub>膜を形成する時、まずAl(CH<sub>3</sub>)<sub>3</sub>ガスを下部電極上に供給して化学的吸着状態及び物理的吸着状態を誘導した後、パージング時間を各々0.2秒、0.3秒、0.5秒、0.7秒及び0.9秒とした時、誘電膜の形成のために適用する工程サイクル数を増加させながら形成されたAl<sub>2</sub>O<sub>3</sub>膜の厚さを測定した。

【0033】

図1のAの結果から、多様なパージング時間が適用された全ての場合において、Al<sub>2</sub>O<sub>3</sub>膜の厚さはALD工程時適用された工程サイクル数と線形的関係を有することが分かる。すなわち、パージング時間に關係なくALD工程サイクル数に比例してAl<sub>2</sub>O<sub>3</sub>膜が厚くなることが分かる。

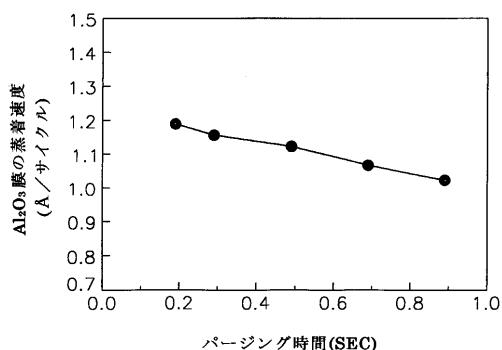

【0034】

図1のBは図1のAの結果に対してパージング時間と1回の工程サイクルの間に蒸着されるAl<sub>2</sub>O<sub>3</sub>膜の厚さ、すなわちAl<sub>2</sub>O<sub>3</sub>膜の蒸着速度との関係を示したグラフである。

【0035】

図1のBの結果から、Al<sub>2</sub>O<sub>3</sub>膜の蒸着速度はパージング時間が増加するほど減少されることが分かる。例えば、パージングを0.2秒間行なつた時には1工程サイクルの間1.21のAl<sub>2</sub>O<sub>3</sub>膜が蒸着され、パージングを0.9秒間行なつた時には1工程サイクルの間1.028のAl<sub>2</sub>O<sub>3</sub>膜が蒸着され、0.2秒のパージング時間では0.9秒のパージング時間より蒸着速度が17%増加した。

10

20

30

40

50

## 【0036】

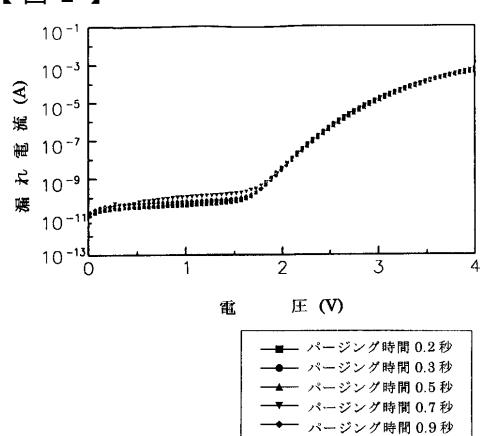

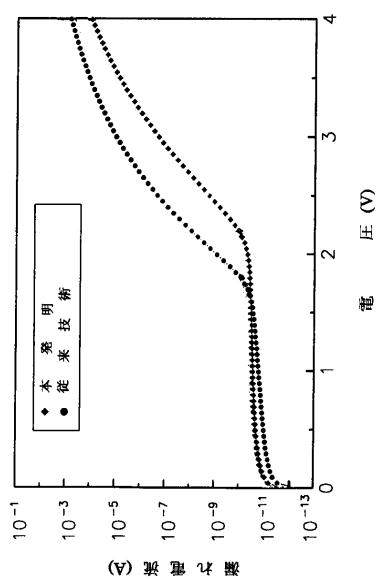

図2は多様なパージング時間を適用してALD方法によって形成されたAl<sub>2</sub>O<sub>3</sub>膜をキャパシタの誘電膜として適用した場合の各キャパシタの漏れ電流の特性を示したグラフである。

## 【0037】

図2はポリシリコンからなる下部電極と、70±1の厚さを有するAl<sub>2</sub>O<sub>3</sub>膜からなる誘電膜と、ポリシリコンからなる上部電極となされる単純なスタック型のキャパシタに対して前記それぞれのパージング時間を適用して誘電膜を形成したサンプルにおける漏れ電流を測定した結果である。すなわち、全てのサンプルは同一な厚さの誘電膜を有しているのですべて同一な等価酸化膜の厚さを持っており、漏れ電流の特性もほとんど類似していることがわかる。

## 【0038】

図2の結果から、パージング時間の変化による誘電膜の電気的特性はそれほど変化がないということが分かる。

## 【0039】

前記実験結果に基づき、本発明ではALD方法によって誘電膜を形成する時パージング時間を変化させる方法によって特定の部分における誘電膜を厚くする。すなわち、本発明では屈曲型結晶粒によって下部電極の表面に形成された曲率半径が小さな凹部のように下部電極の3次元形状に起因して電位が大きくなる部分で誘電膜を厚くすることによって前記電位の大きな部分で漏れ電流が増えることを防止しようとする。

## 【0040】

後述される本発明の具体的な実施例は多様な形態に変形でき、本発明が下記実施例に限定されることではない。本発明の実施例は当業界で通常の知識を有する者に本発明をより完全に理解できるようにするために提供されることである。添付した図面において、層または領域の厚さまたは大きさは明細書の明確性のために誇張して表現したものである。添付した図面において、同一な符号は同一な要素を指称することであり、ある層が他の層または基板の”上部”にあると記載された場合、前記ある層が前記他の層または基板の上部に直接存在することもあり、その間に第3の他の層が介在されることもある。

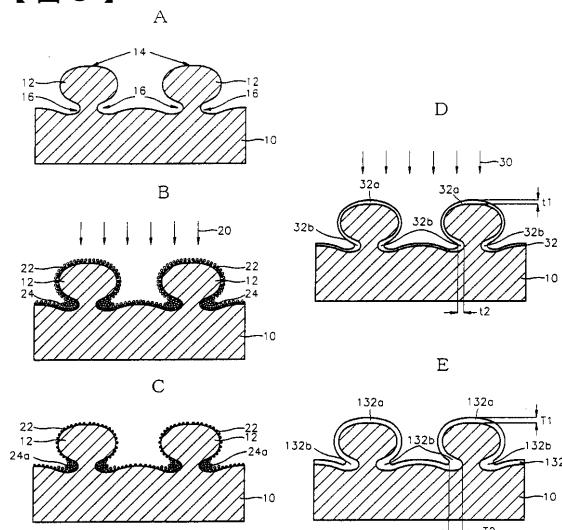

## 【0041】

図3のAないしE及び図4は本発明の好ましい実施例によるキャパシタの誘電膜の形成方法を説明するための図面であって、図3のAないしEは本発明の方法によって屈曲型結晶粒が形成された下部電極10の表面に誘電膜を形成する方法を段階別に示した下部電極10の一部断面図であり、図4は本発明に係る方法によって誘電膜を形成するためにALD方法によって周期的にガスをパルシングする方法を説明するためのタイミング図である。

## 【0042】

図3のAを参照すれば、半導体素子のキャパシタを形成するために、まず基板(図示せず)上にポリシリコンからなって屈曲型結晶粒が形成された表面(rugged surface)を有する下部電極10を形成する。前記下部電極10の表面には複数の屈曲型結晶粒12によって曲率半径が比較的大きな凸部14と曲率半径が比較的小さな凹部16が形成される。

## 【0043】

図3のBを参照すれば、第1反応物であるAl(CH<sub>3</sub>)<sub>3</sub>及び第2反応物であるH<sub>2</sub>Oガスを使用して前記下部電極10の表面にAl<sub>2</sub>O<sub>3</sub>膜からなる誘電膜をALD方法によって形成するために、まず工程温度を300に維持した状態で第1反応物であるAl(CH<sub>3</sub>)<sub>3</sub>ガス20を前記下部電極10の表面に供給する。この時、Al(CH<sub>3</sub>)<sub>3</sub>ガス20のキャリアガスとしてArを使用する。工程圧力は1ないし5Torrの範囲で適用可能である。

## 【0044】

この時、図4のステップAと同様に、雰囲気ガスとしてN<sub>2</sub>ガスを400sccmの流量で続けて供給しながらAl(CH<sub>3</sub>)<sub>3</sub>ガス20を0.3秒間200sccmの流量で供給する。ここで、前記雰囲気ガスとして使われるN<sub>2</sub>ガスは前記下部電極10の表面に供給

10

20

30

40

50

される  $\text{Al}(\text{CH}_3)_3$  ガス 20 を所望の濃度に稀釀させる役割をする。

【0045】

その結果、前記下部電極 10 の表面には  $\text{Al}(\text{CH}_3)_3$  ガス 20 から得られた  $\text{Al}$  原子からなる化学的吸着層 22 ( 黒色粒子 ) 及び前記化学的吸着層 22 上に比較的弱い物理的結合によって形成される物理的吸着層 24 ( 白色粒子 ) が形成される。

【0046】

図 3 の C を参照すれば、不活性ガスをバージングガスとして使用して図 3 の B の結果物に對してバージングを行なって前記物理的吸着層 24 の一部のみを取り除く。すなわち、前記曲率半径が小さな凹部 16 を除いた残り部分に形成された前記物理的吸着層 24 は除去し、前記凹部 16 に形成された化学的吸着層 22 上には物理的吸着層の残留層 24a を残存させる。

【0047】

これのために、図 4 のステップ B に示したように、バージングガスとして  $\text{Ar}$  ガスを 20 0 sccm の流量で 0.6 秒間供給する。この時、バージングガスの役割を強化させるために  $\text{N}_2$  ガスを 400 sccm の流量で共に供給する。

【0048】

ここで、通常の ALD 工程と同様に前記図 3 の B の結果物から物理的吸着層 24 をすべて除去するためには図 4 のステップ B で  $\text{Ar}$  ガスを利用したバージング工程を約 0.9 秒間行なうべきである。しかし、本発明に係る方法では前記物理的吸着層 24 が比較的遅く除去される前記凹部 16 にのみ前記物理的吸着層 24 が残るようになる時間までバージング工程を行なう。本実施例では 0.6 秒間のみバージング工程を行なって、前記凹部 16 に前記物理的吸着層の残留層 24a を残存させる。

【0049】

前記実施例では前記物理的吸着層 24 の一部を除去するための方法としてバージング工程を行なうと説明したが、前記物理的吸着層 24 の一部をポンピングによって除去することも可能である。

【0050】

図 3 の D を参照すれば、前記化学的吸着層 22 及び前記物理的吸着層の残留層 24a が形成された結果物上に工程温度を 300 に維持した状態で工程圧力を 1 ないし 5 torr にし、キャリアガスとして  $\text{Ar}$  を使用して第 2 反応物である  $\text{H}_2\text{O}$  ガス 30 を供給する。

【0051】

この時、図 4 のステップ C のように、雰囲気ガスとして  $\text{N}_2$  ガスを 400 sccm の流量で続けて供給しながら  $\text{H}_2\text{O}$  ガス 30 を 0.5 秒間 200 sccm の流量で供給する。ここで、前記雰囲気ガスとして使われる  $\text{N}_2$  ガスは  $\text{H}_2\text{O}$  ガス 30 を稀釀させる役割をする。

【0052】

その結果、 $\text{H}_2\text{O}$  ガス 30 を構成する酸素原子が前記化学的吸着層 22 及び前記物理的吸着層の残留層 24a と化学的に反応して下部電極 10 の表面には  $\text{Al}_2\text{O}_3$  からなる薄膜 32 が形成される。ここで、前記下部電極 10 の表面で曲率半径が比較的大きな前記凸部 14 上には前記化学的吸着層 22 のみ形成されているので前記凸部 14 上には純粋な  $\text{Al}_2\text{O}_3$  からなって比較的薄い ( t1 ) 薄膜 32a が形成される。反面、曲率半径が比較的小さな前記凹部 16 上には前記化学的吸着層 22 及び物理的吸着層の残留層 24a が形成されているので、これら化学的吸着層 22 及び物理的吸着層の残留層 24a がすべて薄膜 32 の形成に参与する。その結果、前記凹部 16 上には比較的厚い ( t2 ) 薄膜 32b が形成される。前記厚さ ( t2 ) を有する薄膜 32b 内には前記物理的吸着層の残留層 24a によって若干の不純物が含まれることもあるが、本発明に係る方法では図 3 の C におけるバージング時間を調節して前記薄膜 32b 内の不純物の含量が誘電膜の物性に影響を及ぼさないようにしうる。

【0053】

その後、不活性ガスをバージングガスとして使用して前記薄膜 32 が形成された結果物に對してバージングを行なって前記薄膜 32 を形成した後、残った反応副産物をすべて取り

10

20

20

30

40

50

除く。

【0054】

このため、図4のステップDに示したように、バージングガスとしてArガスを200sccmの流量で0.6秒間供給する。この時、バージングガスの役割を強化させるためにN<sub>2</sub>ガスを400sccmの流量と共に供給する。

【0055】

前記実施例では前記反応副産物を除去するための方法としてバージング工程を行なうと説明したが、前記反応副産物をポンピングによって除去することも可能である。

【0056】

これで、図4のステップAないしステップDからなる1サイクルの工程が完了する。

10

【0057】

図3のEを参照すれば、前記薄膜32が形成された結果物に対して図4に示したガスパルシングサイクルを複数回繰り返しながら図3のBないしDを参照して説明した工程を複数回繰り返してAl<sub>2</sub>O<sub>3</sub>からなる誘電膜132を所望の厚さ、例えば60の厚さに形成する。

【0058】

前記誘電膜132は曲率半径が比較的大きい前記凸部14上に形成された比較的薄い(t1)誘電膜132aと、曲率半径が比較的小さな前記凹部16上に形成された比較的厚い(t2)誘電膜132bを含む。したがって、前記凹部16上に蒸着された前記誘電膜132bのステップカバレージは100%を越えるようになる。

20

【0059】

図5は本発明の方法によって形成されたAl<sub>2</sub>O<sub>3</sub>誘電膜と従来の方法によって形成されたAl<sub>2</sub>O<sub>3</sub>誘電膜に対するそれぞれの漏れ電流の特性を示したグラフである。

【0060】

より具体的に説明すれば、屈曲型結晶粒が形成された下部電極上に本発明の方法によって曲率半径が比較的小さな凹部における誘電膜の厚さが曲率半径が比較的大きな凸部における誘電膜の厚さよりさらに厚くて100%以上のステップカバレージを有する誘電膜を形成した場合( )と、屈曲型結晶粒が形成された下部電極上に通常の方法によって全ての部分で100%のステップカバレージを有する誘電膜を形成した場合( )に、各々同一の等価酸化膜の厚さにおけるキャパシタの漏れ電流の特性を図5に示した。

30

【0061】

図5の結果から、本発明の方法によって誘電膜を形成した場合には従来の場合に比べて漏れ電流の特性が改善されたことを確認することができる。

【0062】

これは、本発明の方法によって前記曲率半径が小さな凹部における誘電膜の厚さをほかの部分より厚くすることにより、キャパシタの誘電膜の中ほかの部分より曲率半径が小さな部分でさらに大きく作用する電位によって漏れ電流が増加する現像が抑制されたことを示す。

【0063】

前記実施例ではキャパシタの誘電膜としてAl<sub>2</sub>O<sub>3</sub>膜を形成する場合のみを説明したが、本発明はこれに限らず、他の酸化物または窒化物を蒸着する場合にも同様に適用できる。例えば、TiO<sub>2</sub>、ZrO<sub>2</sub>、HfO<sub>2</sub>、Ta<sub>2</sub>O<sub>5</sub>、Nb<sub>2</sub>O<sub>5</sub>、CeO<sub>2</sub>、Y<sub>2</sub>O<sub>3</sub>、SiO<sub>2</sub>、In<sub>2</sub>O<sub>3</sub>、RuO<sub>2</sub>、IrO<sub>2</sub>などの単原子酸化物と、SrTiO<sub>3</sub>、PbTiO<sub>3</sub>、SrRuO<sub>3</sub>、CaRuO<sub>3</sub>、(Ba、Sr)TiO<sub>3</sub>、Pb(Zr、Ti)O<sub>3</sub>、(Pb、La)(Zr、Ti)O<sub>3</sub>、(Sr、Ca)RuO<sub>3</sub>、(Ba、Sr)RuO<sub>3</sub>、SnでドーピングされたIn<sub>2</sub>O<sub>3</sub>(ITO)、FでドーピングされたIn<sub>2</sub>O<sub>3</sub>、ZrでドーピングされたIn<sub>2</sub>O<sub>3</sub>等の複合酸化物と、SiN、NbN、ZrN、TiN、TaN、Y<sub>2</sub>N<sub>5</sub>、AlN、GaN、WN、BNなどの単原子窒化物と、WBN、WSiN、TiSiN、TaSiN、AlSiN、AlTiNなどの複合窒化物を形成するに本発明に係る方法を適用することも可能である。

40

50

## 【0064】

## 【発明の効果】

前述したように、本発明によればキャパシタの誘電膜を形成する時、ガスパルシング方法を利用した蒸着方法によって下部電極の表面中曲率半径が大きな凸部上には100%の優秀なステップカバレージを有する誘電膜を形成し、これと同時に曲率半径の小さな凹部上には他部より厚く誘電膜を形成して前記凹部における誘電膜のステップカバレージを100%以上にすることにより、素子動作に必要なセルキャパシタンスを十分に確保すると同時に曲率半径の小さな凹部で強く作用する電位による漏れ電流の増加現像を防止できる。

## 【0065】

以上、本発明を好ましい実施例を挙げて詳しく説明したが、本発明は前記実施例に限らず、本発明の技術的思想の範囲内で当分野で通常の知識を有する者によって多様な変形が可能である。

## 【図面の簡単な説明】

【図1】図1のAは、ALD方法による誘電膜の形成時、多様なパージング時間に対して適用された工程サイクル数と得られた誘電膜の厚さとの関係を示したグラフである。また、図1のBは、パージング時間と $\text{Al}_2\text{O}_3$ 膜の蒸着速度との関係を示したグラフである。

【図2】多様なパージング時間を適用してALD方法によってキャパシタの誘電膜を形成した場合に各キャパシタの漏れ電流の特性を示したグラフである。

【図3】図3のA, B, C, D, Eは、本発明の好ましい実施例によるキャパシタの誘電膜の形成方法を説明するための断面図である。

【図4】本発明の好ましい実施例によるキャパシタの誘電膜の形成方法に適用可能なガスパルシング方法を説明するためのタイミング図である。

【図5】本発明と従来の技術におけるそれぞれの漏れ電流の特性を比較したグラフである。

## 【符号の説明】

10 : 下部電極

12 : 屈曲型結晶粒

14 : 凸部

16 : 凹部

20 : 第1反応物

22 : 化学的吸着層

24 : 物理的吸着層

24a : 物理的吸着層の残留層

32 : 薄膜

32a :  $t_1$ を有する薄膜

32b :  $t_2$ を有する薄膜

$t_1$  : 薄厚

$t_2$  : 厚い厚さ

132 : 誘電膜

132a :  $t_1$ を有する誘電膜

132b :  $t_2$ を有する誘電膜

10

20

30

40

【図1】

A

【図2】

B

【図3】

【図4】

【図5】

---

フロントページの続き

(74)代理人 100111464

弁理士 斎藤 悅子

(72)発明者 金 榮 寛

大韓民国京畿道城南市盆唐區書 けん 洞8 7番地 韓信アパート112棟1501號

(72)発明者 李 相 忍

大韓民国京畿道城南市八達區梅灘2洞1211番地 韓國1次アパート104棟706號

(72)発明者 朴 昌 淳

大韓民国京畿道水原市八達區仁溪洞366番地 三星アパート101棟410號

(72)発明者 金 榮 善

大韓民国ソウル特別市麻浦區孔徳洞20 - 33番地

審査官 正山 旭

(56)参考文献 特開平06-069417 (JP, A)

特開平05-114712 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8242

C23C 16/40

H01L 21/822

H01L 27/04

H01L 27/108