등록특허 10-2433712

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2022년08월17일

(11) 등록번호 10-2433712

(24) 등록일자 2022년08월12일

- (51) 국제특허분류(Int. Cl.)

*B32B 37/02* (2006.01) *B32B 37/12* (2006.01)

*B32B 37/24* (2006.01) *B32B 7/14* (2019.01)

*G02B 7/00* (2021.01) *H01L 31/0232* (2014.01)

- (52) CPC특허분류

*B32B 37/02* (2013.01)

*B32B 37/1292* (2013.01)

- (21) 출원번호 10-2017-7012941

- (22) 출원일자(국제) 2015년10월14일

심사청구일자 2020년10월14일

- (85) 번역문제출일자 2017년05월12일

- (65) 공개번호 10-2017-0072255

- (43) 공개일자 2017년06월26일

- (86) 국제출원번호 PCT/SG2015/050387

- (87) 국제공개번호 WO 2016/060615

국제공개일자 2016년04월21일

(30) 우선권주장

62/063,532 2014년10월14일 미국(US)

(56) 선행기술조사문현

US08000041 B1\*

US20090321861 A1

US20130048208 A1

\*는 심사관에 의하여 인용된 문현

전체 청구항 수 : 총 10 항

심사관 : 정석환

(54) 발명의 명칭 광학 소자 스택 어셈블리들

**(57) 요 약**

본 개시 내용은 서로 적층된 복수의 기판들을 포함하는 광학 소자 스택 어셈블리들을 설명한다. 기판들 중 적어도 하나는 그 표면 상에 DOE와 같은 광학 소자를 포함한다. 스택 어셈블리는, 예를 들어, 웨이퍼 레벨 프로세스들에서 제조될 수 있다.

**대 표 도** - 도3

(52) CPC특허분류

*B32B 7/14* (2019.01)

*G02B 7/00* (2021.01)

*H01L 31/0232* (2013.01)

*B32B 2037/243* (2013.01)

*B32B 2307/412* (2013.01)

*B32B 2307/418* (2013.01)

*B32B 2551/00* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

복수의 스택 어셈블리들을 제조하는 웨이퍼 레벨 방법에 있어서,

제1 웨이퍼 및 제2 웨이퍼를 제공하는 단계 - 상기 제1 웨이퍼 또는 상기 제2 웨이퍼 중 적어도 하나는 자신의 표면 상에 복수의 광학 소자들을 가짐 - ;

상기 제2 웨이퍼에 관통 홀들을 형성하는 단계;

상기 제2 웨이퍼의 반대의 표면들(opposite surfaces) 상에 상부 스페이서 및 하부 스페이서를 형성하기 위해 단일 진공 주입 기술을 사용하는 단계 - 상기 진공 주입 기술은 상기 관통 홀들을 상기 상부 스페이서 및 상기 하부 스페이서를 형성하는 동일한 재료로 채움 - ;

웨이퍼 스택을 형성하기 위해 상기 제1 웨이퍼를 상기 제2 웨이퍼에 부착하는 단계 - 상기 제1 웨이퍼 및 상기 제2 웨이퍼는 각각의 광학 소자가 상기 제1 웨이퍼와 상기 제2 웨이퍼 사이에 배치되도록 부착됨 - ; 및

상기 웨이퍼 스택을 복수의 스택 어셈블리들로 분리하는 단계 - 상기 복수의 스택 어셈블리들 각각은 상기 광학 소자들 중 적어도 하나를 포함함 -

를 포함하는, 방법.

#### 청구항 2

제1항에 있어서,

상기 제1 웨이퍼 및 상기 제2 웨이퍼 각각은 자신의 표면 상에 복수의 광학 소자들을 갖고, 각각의 스택 어셈블리는 상기 광학 소자들 중 적어도 2개를 포함하는, 방법.

#### 청구항 3

제1항 또는 제2항에 있어서,

상기 제1 웨이퍼 및 상기 제2 웨이퍼를 부착하는 단계는,

상기 제1 웨이퍼 및 상기 제2 웨이퍼를 상기 광학 소자들의 바깥쪽 부분들과 상기 제2 웨이퍼 상의 상기 상부 스페이서들 사이에 배치된 접착제를 통해 서로 부착하는 단계를 포함하는, 방법.

#### 청구항 4

제1항 또는 제2항에 있어서,

상기 광학 소자들은 회절 광학 소자들인, 방법.

#### 청구항 5

제1항 또는 제2항에 있어서,

상기 광학 소자들은 복제된 광학 소자들인, 방법.

#### 청구항 6

스택 어셈블리로서,

제1 기판;

상기 제1 기판에 부착된 제2 기판;

적어도 상기 제1 기판 또는 상기 제2 기판 상의 광학 소자 - 적어도 하나의 광학 소자가 상기 제1 기판과 상기

제2 기판 사이에 배치됨 - ;

상기 제1 기판 또는 상기 제2 기판의 외측에 부착된 제1 스페이서; 및

상기 제1 기판과 상기 제2 기판 사이의 제2 스페이서 - 상기 제1 스페이서 및 제2 스페이서는 동일한 진공 주입 성형 단편(vacuum injection molded piece)의 일부임 -

를 포함하는 스택 어셈블리.

#### 청구항 7

제6항에 있어서,

상기 제1 기판 및 상기 제2 기판 각각은 자신의 표면 상에 각각의 광학 소자를 갖고, 상기 광학 소자들은 서로 마주 보는, 스택 어셈블리.

#### 청구항 8

제6항 또는 제7항에 있어서,

각각의 광학 소자는 회절 광학 소자인, 스택 어셈블리.

#### 청구항 9

제6항 또는 제7항에 있어서,

각각의 광학 소자는 복제된 광학 소자인, 스택 어셈블리.

#### 청구항 10

복수의 스택 어셈블리들을 제조하는 웨이퍼 레벨 방법으로서,

제1 웨이퍼 및 제2 웨이퍼를 제공하는 단계 - 상기 제1 웨이퍼 또는 상기 제2 웨이퍼 중 적어도 하나는 자신의 표면 상에 복수의 광학 소자들을 가짐 - ;

상기 제2 웨이퍼를 테이프에 부착하고 상기 제2 웨이퍼를 다수의 싱글레이션된 기판들로 분리하는 단계;

싱글레이션된 기판들의 반대의 표면들 상에 상부 스페이서 및 하부 스페이서를 형성하기 위하여 상기 싱글레이션된 기판들을 진공 주입 툴에 배치하는 단계;

각각의 광학 소자가 상기 제1 웨이퍼와 상기 싱글레이션된 기판들 중 하나 사이에 배치되도록 스택을 형성하기 위하여 상기 제1 웨이퍼를 상기 싱글레이션된 기판들에 부착하는 단계; 및

상기 스택을 복수의 스택 어셈블리들로 분리하는 단계 - 상기 스택 어셈블리들 각각은 상기 광학 소자들 중 적어도 하나를 포함함 -

를 포함하는, 방법.

#### 청구항 11

삭제

#### 청구항 12

삭제

#### 청구항 13

삭제

#### 청구항 14

삭제

#### 청구항 15

삭제

청구항 16

삭제

청구항 17

삭제

청구항 18

삭제

청구항 19

삭제

청구항 20

삭제

## 발명의 설명

### 기술 분야

[0001] 관련 출원(들)에 대한 상호 참조

[0002] 본 출원은 2014년 10월 14일자로 출원된 미국 가특허 출원 번호 62/063,532 의 우선권의 이익을 주장한다. 선 출원의 개시 내용은 그 전체가 본 명세서에 참조로 포함된다.

[0003] 기술분야

[0004] 본 개시 내용은 광학 소자 스택 어셈블리들에 관한 것이다.

### 배경 기술

[0005] 다양한 광전자 모듈이, 예를 들어, 3차원(3D) 이미징과 같은 이미징 어플리케이션들 또는 근접 센싱과 같은 거리 측정 어플리케이션들을 위해 사용된다. 일부 어플리케이션들에서, 광 방출기 어셈블리(optical emitter assembly)는 구조화된 광학 패턴을 방출하도록 작동되고, 이는 거리 감지 어플리케이션들 뿐만 아니라 이미징에도 유용할 수 있다. 구조화된 광은 물체 상에 투영되는 개별 피쳐들의 패턴(즉, 텍스처)을 야기할 수 있다. 물체에 의해 반사된 광은 이미지 센서 쪽으로 되돌아 갈 수 있고, 그 이미지 센서에 반사된 광이 감지될 수 있다. 감지된 신호들은 거리 계산들을 위해 사용될 수 있다. 일부 경우에는, 구조화된 광은 스테레오 이미징 어플리케이션들에서 픽셀들을 매칭시키기 위한 추가적인 텍스처를 제공한다.

[0006] 일부 모듈에서, 회절 광학 소자(diffractive optical element; DOE)와 같은 광학 소자는 수직 공동 반도체 방출 레이저(vertical cavity semiconductor emitting laser; VCSEL) 또는 VCSEL 어레이와 같은 광원에 의해 방출된 광의 경로에 도입된다. DOE는 구조화된 광 패턴을 생성하는 데 유용할 수 있다. 또한, DOE는 VCSEL 또는 다른 광원에 의해 생성된 구조화된 광 패턴의 증대를 용이하게 할 수 있다.

### 발명의 내용

[0007] 본 개시 내용은, 예를 들어, 웨이퍼 레벨 방법에 의해 제조될 수 있는 광학 소자 스택 어셈블리들을 설명한다.

[0008] 예를 들어, 일 양태에서, 스택 어셈블리들을 제조하는 웨이퍼 레벨 방법은, 웨이퍼 서브 스택(sub-stack)을 형성하기 위해 제1 웨이퍼를 제2 웨이퍼에 부착하는 단계를 포함한다. 제1 웨이퍼 또는 제2 웨이퍼 중 적어도 하나는 그 표면 상에 복수의 광학 소자들을 갖는다. 제1 웨이퍼 및 제2 웨이퍼는 각각의 광학 소자가 제1 웨이퍼 및 제2 웨이퍼 사이에 배치되도록 부착된다. 방법은 웨이퍼 스택을 형성하기 위해 스페이서 웨이퍼를 웨이퍼 서브 스택에 부착하는 단계와 웨이퍼 스택을 스택 어셈블리들로 분리하는 단계를 더 포함하며, 스택 어셈블리들 각각은 광학 소자들 중 적어도 하나를 포함한다.

- [0009] 다른 양태에서, 스택 어셈블리들을 제조하는 웨이퍼 레벨 방법은, 제1 웨이퍼 및 제2 웨이퍼를 제공하는 단계를 포함하며, 여기서 제1 웨이퍼 또는 제2 웨이퍼 중 적어도 하나는 그 표면 상에 광학 소자들을 가진다. 방법은 제2 웨이퍼의 반대의 표면들(opposite surfaces) 상에 상부 스페이서 및 하부 스페이서를 형성하기 위하여 단일 진공 주입 기술을 사용하는 단계를 포함한다. 방법은 웨이퍼 스택을 형성하기 위하여 제1 웨이퍼를 제2 웨이퍼에 부착하는 단계를 더 포함한다. 제1 웨이퍼 및 제2 웨이퍼는 각각의 광학 소자가 제1 웨이퍼와 제2 웨이퍼 사이에 배치되도록 부착될 수 있다. 그 다음에, 웨이퍼 스택은 스택 어셈블리들로 분리될 수 있으며, 스택 어셈블리들 각각은 광학 소자들 중 적어도 하나를 포함한다.

- [0010] 또 다른 양태에서, 스택 어셈블리들을 제조하는 웨이퍼 레벨 방법은, 제1 웨이퍼 및 제2 웨이퍼를 제공하는 단계를 포함하고, 여기서 제1 웨이퍼 또는 제2 웨이퍼 중 적어도 하나는 그 표면 상에 광학 소자들을 가진다. 방법은 제2 웨이퍼를 테이프에 부착하고 제2 웨이퍼를 싱글레이션된 기판들(singulated substrates)로 분리하는 단계를 포함한다. 싱글레이션된 기판들은 싱글레이션된 기판들의 반대의 표면들 상에 상부 스페이서 및 하부 스페이서를 형성하기 위하여 싱글레이션된 기판들을 진공 주입 툴에 배치된다. 제1 웨이퍼는 각각의 광학 소자가 제1 웨이퍼와 싱글레이션된 기판들 중 하나 사이에 배치되도록 스택을 형성하기 위하여 싱글레이션된 기판들에 부착된다. 그 다음에, 스택은 스택 어셈블리들로 분리되며, 스택 어셈블리들 각각은 광학 소자들 중 적어도 하나를 포함한다.

- [0011] 본 개시 내용은 또한 제1 기판, 제1 기판에 부착된 제2 기판, 및 적어도 제1 기판 또는 제2 기판 상의 광학 소자를 포함하는 스택 어셈블리를 설명하며, 여기서 적어도 하나의 광학 소자가 제1 기판과 제2 기판 사이에 배치된다. 스택 어셈블리는 제1 기판 또는 제2 기판의 외측(outer side)에 부착된 제1 스페이서를 포함한다. 일부 구현예에서, 스택 어셈블리는 제1 기판과 제2 기판 사이에 제2 스페이서를 더 포함하며, 여기서 제1 스페이서 및 제2 스페이서는 동일한 진공 주입 성형 단편(vacuum injection molded piece)의 일부이다. 또한, 일부 경우들에서, 진공 주입 성형 단편은 제2 기판의 측면 에지들을 측방향으로(laterally) 둘러싼다. 또한, 제1 기판 및 제2 기판은 광학 소자들 중 하나 이상의 바깥쪽 부분(lateral side portion) 상에서 접착제에 의해 서로 부착될 수 있다.

- [0012] 다양한 구현예들은 이하의 특징들 중 하나 이상을 포함한다. 예를 들어, 제1 웨이퍼 및 제2 웨이퍼 각각은 그 표면 상에 각각의 광학 소자를 가질 수 있고, 광학 소자들은 서로 마주 볼 수 있다. 일부 경우들에서, 광학 소자들은 회절 광학 소자들이다. 일부 구현예에서, 광학 소자들은 복제된 광학 소자들이다.

- [0013] 웨이퍼 레벨 방법들은 복수의 어셈블리들이 동시에 병렬로 제조되는 것을 허용한다. 또한, 기술들은 애플리케이션에 따라 제1 웨이퍼와 제2 웨이퍼 사이에 더 작은 거리 또는 더 큰 거리를 제공하기 위하여 유리하게 사용될 수 있다. 다양한 예들이 아래에서 더 상세하게 설명된다. 다른 양태들, 특징들 및 이점들은 이하의 상세한 설명, 첨부 도면들 및 청구 범위들로부터 쉽게 명백할 것이다.

- ### 도면의 간단한 설명

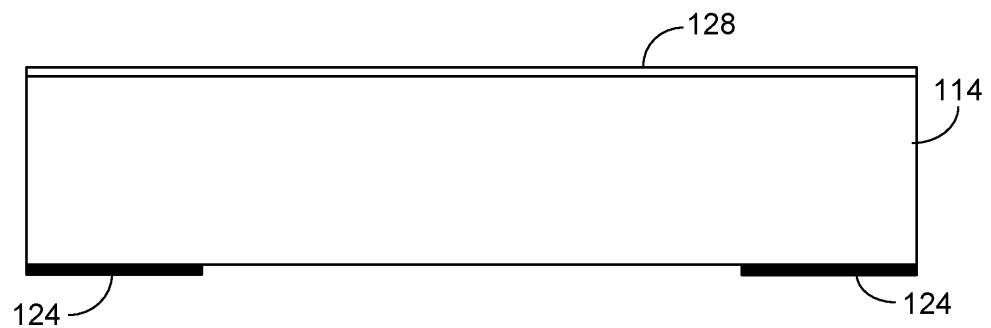

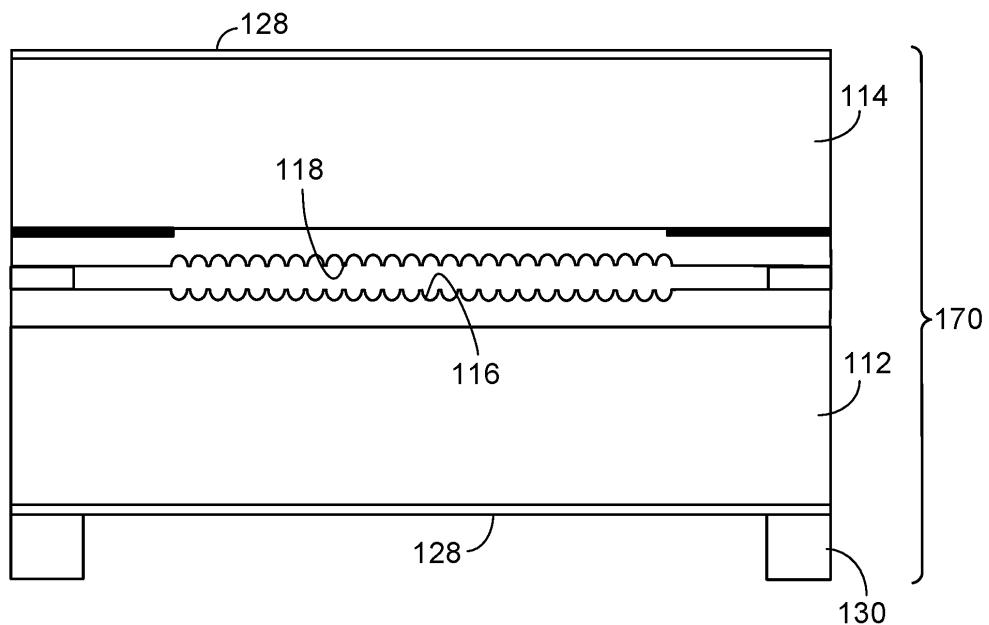

- [0014] 도 1은 광학 소자 스택 어셈블리의 제1 예를 도시한다.

- 도 2a 내지 도 2f는 도 1의 광학 소자 스택 어셈블리의 제조 단계들의 예시들을 도시한다.

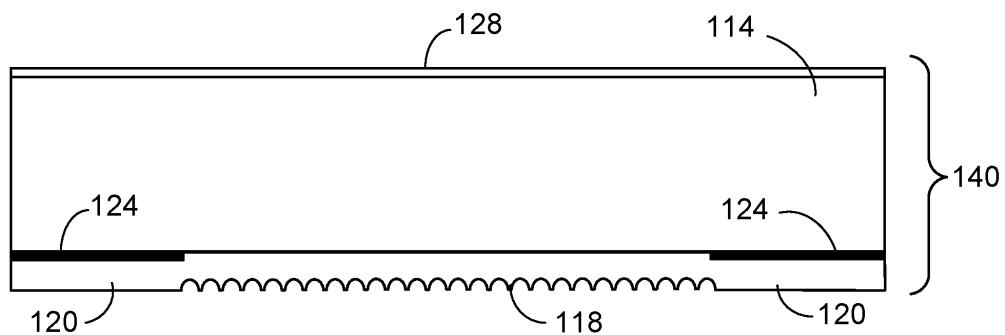

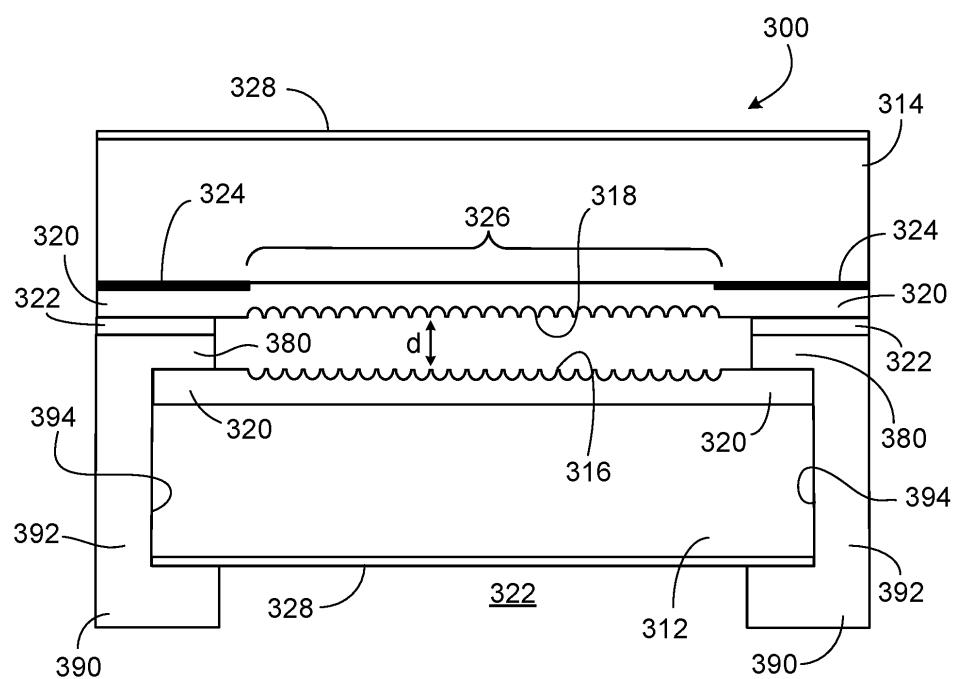

- 도 3은 광학 소자 스택 어셈블리의 제2 예를 도시한다.

- 도 4a 내지 도 4f는 도 3의 광학 소자 스택 어셈블리의 제조 단계들의 예시들을 도시한다.

- ### 발명을 실시하기 위한 구체적인 내용

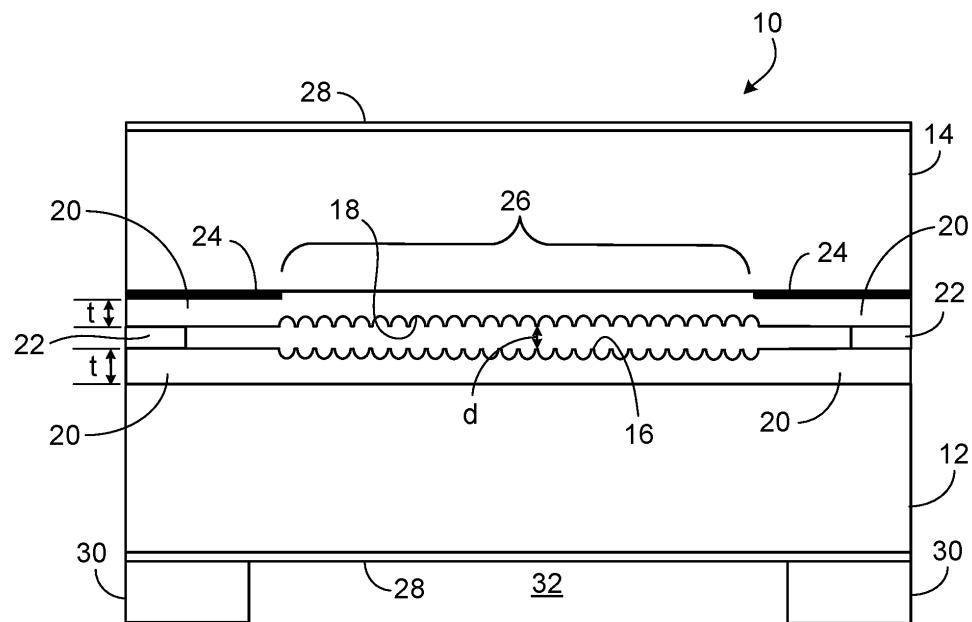

- [0015] 본 개시 내용은 서로 적층된 복수의 기판들을 포함하는 광학 소자 스택 어셈블리들을 설명한다. 기판들 중 적어도 하나는 그 표면 상에 DOE와 같은 광학 소자를 포함한다. 일부 경우에는, 모든 기판들이 기판 각각의 표면 상에 광학 소자를 갖는다. 기판들 및 광학 소자들은 스택을 통과하는 광학 신호가 기판들 및 광학 소자(들)를 통과하도록 정렬된다.

- [0016] 도 1에 나타난 바와 같이, 스택 어셈블리(10)는 서로 적층된 제1 기판 및 제2 기판(12, 14)을 포함한다. 각각의 기판(12, 14)은 예를 들어, 특정 과장 또는 과장 범위(예를 들어, 가시 광선, 적외선(IR) 및/또는 근적외선 부분들의 스펙트럼)에 투명한 유리, 중합체 또는 다른 재료로 구성될 수 있다. 도 1의 예에서, 기판들(12, 14)은 기판들의 대향하는 표면들(opposing surfaces) 상에 형성된 수동 광학 소자들(passive optical elements)(16, 18)을 갖는다. 도시된 예에서, 광학 소자들(16, 18)은 DOE들이다. 일부 구현예에서는 다른 유

형의 수동 광학 소자들(예를 들어, 굴절 또는 회절 렌즈, 또는 마이크로 렌즈 어레이와 같은 광학 소자들의 어레이)이 제공될 수 있다. 또한, 일부 경우에는, 하나의 기판(12)이 다른 기판(14) 상의 광학 소자의 유형과 상이한 광학 소자의 유형을 가질 수 있다. 일부 예에서는, 기판들(12, 14) 중 하나만이 그 표면 상에 광학 소자를 가질 수 있다.

[0017] 광학 소자들(16, 18)을 형성하는 재료의 바깥쪽 부분들(20)은 대향하는 광학 소자들(opposing optical elements)(16, 18) 사이에 잘 정의된 간격 'd'를 제공하는 스페이서들로서 역할을 할 수 있다. 바깥쪽 부분들(20)의 통상적인 두께 't'는  $50\mu\text{m}$  이하(예를 들어,  $25\text{--}50\mu\text{m}$ )이다. 도시된 예에서, 광학 소자들(16, 18)은 특정 파장 또는 파장 범위에 대해 투명한 에폭시 재료로 구성된다. 기판들(12, 14)은 바깥쪽 부분들(20) 상에 배치된 글루(glue) 또는 다른 접착제(22)의 얇은 층에 의해 함께 연결된다. 접착제(22)의 통상적인 두께는  $10\mu\text{m}$  미만(예를 들어,  $7\mu\text{m}$ )이다. 위에서 언급된 치수들은 일부 구현에서 상이할 수 있다.

[0018] 상단 기판(14)의 광학 소자 측 상의 얇은 불투명 코팅(24)은 광학 조리개(optical stop)(26)를 정의하며, 이는 특정 파장의 광 또는 특정 파장 범위의 광이 통과할 수 있는 투명한 창을 정의하는 역할을 한다. 각각의 기판(12, 14)의 외부 표면은 얇은 반사 방지 코팅(ARC)(28)으로 코팅될 수 있다. 하단 기판(12)의 ARC 측은 광학 소자들(16, 18)과, 어셈블리(10)가 장착되는 표면 사이에 잘 정의된 거리를 제공하는 스페이서(30)를 포함한다. 하부 기판(12)의 ARC 측에 접착제로 고정될 수 있는 스페이서(30)는 조리개(26) 아래에 개구(32)를 갖는다.

[0019] 도 2a 내지 도 2f는 도 1의 어셈블리(10)와 같은 광학 소자 스택 어셈블리들을 제조하기 위한 웨이퍼 레벨(wafer-level) 방법의 단계들을 도시한다. 웨이퍼 레벨 프로세스들은 다수의 어셈블리(10)가 동시에 제조되는 것을 허용한다. 일반적으로, 웨이퍼는 실질적으로 디스크- 또는 판-유사 형상의 아이템을 지칭하고, 그것의 일방향(z-방향 또는 수직 방향)에서의 연장범위는 다른 두 방향(x- 및 y- 또는 측 방향들)에서의 연장범위에 비해 더 작다. 일부 구현예에서, 웨이퍼의 직경은 5cm와 40cm의 사이이고, 예를 들어, 10cm와 31cm의 사이일 수 있다. 웨이퍼는, 예를 들어, 2, 4, 6, 8 또는 12인치의 직경을 갖는 원통형일 수 있고, 1인치는 대략 2.54cm이다. 웨이퍼 레벨 프로세스의 일부 구현예에서, 각각의 측 방향으로 적어도 10개의 모듈을 위한 제공들(provisions)이 있을 수 있고, 몇몇 경우에는 각각의 측 방향으로 적어도 30개 또는 심지어 50개 이상의 모듈을 위한 제공들이 있을 수 있다. 이해를 용이하게 하기 위해, 도 2a 내지 도 2f에는 단일 어셈블리(10)에 대응하는 각 웨이퍼의 일부분만이 도시된다.

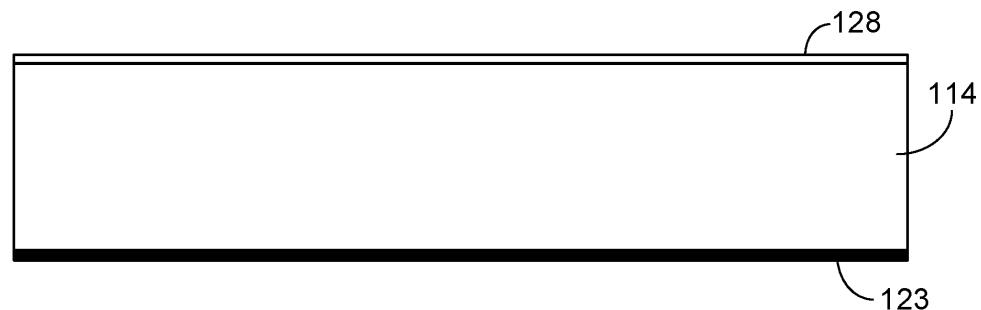

[0020] 도 2a에 도시된 바와 같이, 제1 투명 웨이퍼(114)가 제공되고, 제1 투명 웨이퍼는 제1 표면 상에 ARC(128)를 가지며 그 반대의 제2 표면 상에 불투명 층(예를 들어, 포토레지스트)(123)을 갖는다. 웨이퍼(114)는, 예를 들어, 특정 파장 또는 파장 범위에 투명한 유리, 중합체 또는 다른 재료로 구성될 수 있다. 도 2b에 나타난 바와 같이, 층(123)은 각 어셈블리(10)에 대한 불투명 코팅(24)을 정의하는 불투명 재료의 영역들(124)을 형성하도록 (예를 들어, 표준 포토리소그래피 기술들(standard photolithography techniques)을 사용하여) 패터닝 된다.

[0021] 다음으로, 도 2c에 나타난 바와 같이, 광학 소자들(118)(예를 들어, DOE들)이 기판(114)의 제2 표면 상에 형성된다. 그 중 하나가 도 1c에 나타나 있는 광학 소자들(118)은, 예를 들어, 웨이퍼 레벨 복제(wafer-level replication)에 의해 형성될 수 있다. 일반적으로, 복제란 주어진 틀(예를 들어, 광학 소자들의 네거티브(negative of the optical elements)를 포함하는 틀) 구조 또는 그것의 네거티브 포지티브(negative positive thereof)가, 예를 들어, 구조화된 표면(예를 들어, 광학 소자들의 포지티브)을 에칭, 앰보싱 또는 성형하는 것을 통해서 재생되도록 사용되는 기술을 지칭한다. 복제 프로세스의 특정 예에서, 구조화된 표면(예를 들어, 광학 소자 또는 다수의 광학 소자들을 정의함)은 틀을 사용하여 액체 재료, 점성 재료 또는 소성 변형 가능한(plastically deformable) 재료내에 프레스되고(pressed), 그 다음에, 재료는, 예를 들어, 자외선 복사 및/또는 가열을 사용한 큐어링에 의해 경화되며, 그리고 나서, 구조화된 표면 틀이 제거된다. 따라서, 구조화된 표면의 복제물이 획득된다. 복제에 적합한 재료는, 예를 들면, 경화 가능한(예를 들어, 큐어링 가능한) 중합체 재료들 또는 다른 복제 재료들, 즉 경화 단계 또는 응고(solidification) 단계(예를 들어, 큐어링 단계)에서 액체 상태, 점성 상태 또는 소성 변형 가능한 상태로부터 고체 상태로 변형이 가능한 물질들이다. 복제된 재료의 약드 부분들(yard portions)(120)의 두께는 통상적으로  $50\mu\text{m}$  이하(예를 들어, 25 내지  $50\mu\text{m}$ )이다. 도 2a 내지 2c에서의 프로세싱은 각각의 어셈블리(10)를 위한 상단 기판(14)을 제공하는 제1 웨이퍼 서브어셈블리(140)를 야기한다.

[0022] 제조 프로세스의 일부로서, 제2 투명 웨이퍼(112)가 제공되고, 제2 투명 웨이퍼는 그 제1 표면 상에 ARC(128)를 갖는다. 그 중 하나가 도 2d에 나타나 있는 광학 소자들(116)(예를 들어, DOE들)은, 웨이퍼(112)의 제2 표면

상에 형성된다. 또한, 광학 소자들(116)은, 예를 들어, 상술한 바와 같은 웨이퍼 레벨 복제에 의해 형성될 수 있다. 도 2d의 프로세싱은 각각의 어셈블리(10)를 위한 하단 기판(12)을 제공하는 제2 웨이퍼 서브어셈블리(150)를 야기한다.

[0023] 다음으로, 도 2e에 나타난 바와 같이, 제1 및 제2 웨이퍼 서브어셈블리들(140, 150)은 웨이퍼 서브 스택(160)을 형성하기 위해 서로 부착될 수 있다. 서브어셈블리들(140, 150)은, 예를 들어, 글루 또는 다른 접착제에 의해 (예를 들어, 글루 세팅(glue setting) 또는 스크린 프린팅(screen printing)에 의해) 서로 부착된다. 서브어셈블리들(140, 150)은 광학 소자들(116, 118)이 서로 마주 보도록 서로 부착될 수 있다. 또한, 도 2f에 나타난 바와 같이, 스페이서 웨이퍼(130)는 웨이퍼 스택(170)을 완성하기 위해 제2 웨이퍼 어셈블리(140)의 ARC측에 부착된다. 스페이서 웨이퍼(130)는, 예를 들어, 글루 또는 다른 접착제에 의해 부착될 수 있다. 일단 웨이퍼 레벨 스택(170)이 완성되면, 웨이퍼 레벨 스택은 복수의 개별 어셈블리들(10)을 형성하도록 (예를 들어, 다이싱(dicing)에 의해) 분리될 수 있다.

[0024] 도 2a 내지 도 2f의 예시적인 프로세스에서, 모든 웨이퍼들(112, 114)은 그들 각각의 표면 상에 복제된 광학 소자들(116, 118)을 갖는다. 그러나, 일부 구현예에서, 웨이퍼들 중 하나(제1 웨이퍼(114) 또는 제2 웨이퍼(112)중 어느 하나)만이 그 표면 상에 광학 소자들을 갖는다. 또한, 광학 소자들(116, 118)은 DOE들로서 나타내졌지만, 일부 예에서는 다른 유형의 광학 소자들이 사용될 수 있다.

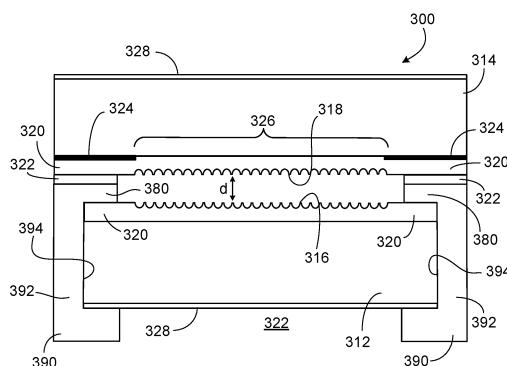

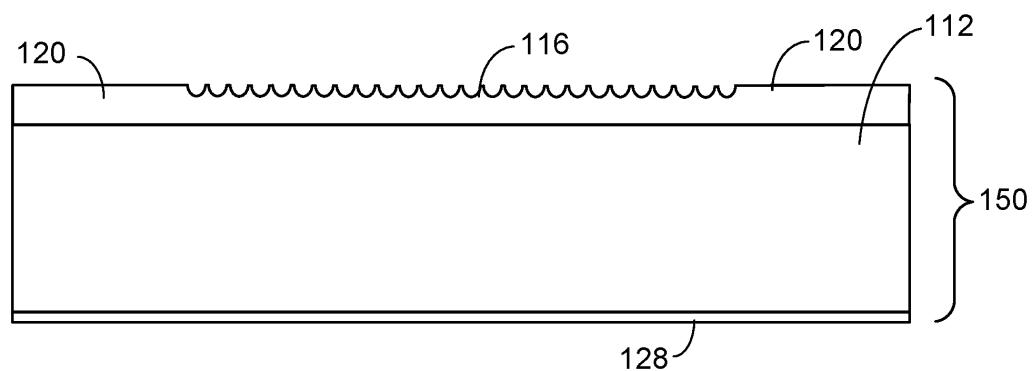

[0025] 도 3은 광학 소자 스택 어셈블리(300)의 제2 예를 도시한다. 스택 어셈블리(300)는 서로 적층된 제1 및 제2 기판들(312, 314)을 포함한다. 각각의 기판들(312, 314)은, 예를 들어, 특정 파장 또는 파장 범위(예를 들면, 가시광, 적외선(IR) 및/또는 근적외선 부분의 스펙트럼)에 대해 투명한 유리, 중합체 또는 다른 재료로 구성될 수 있다.

[0026] 도 3의 예에서, 기판들(312, 314)은 기판들의 대향 표면들(opposing surfaces) 상에 형성된 수동 광학 소자들(316, 318)을 갖는다. 도시된 예에서, 광학 소자들(316, 318)은 DOE들이다. 다른 유형의 수동 광학 소자들(예를 들어, 굴절 또는 회절 렌즈들)이 일부 구현예에서 제공될 수 있다. 또한, 일부 경우에, 하나의 기판(312)은 다른 기판(314) 상의 광학 소자의 유형과 상이한 유형의 광학 소자를 가질 수 있다. 일부 예에서, 기판들(312, 314) 중 하나만이 그 표면 상에 광학 소자를 가질 수 있다.

[0027] 상단 기판(314)의 광학 소자 측 상의 얇은 불투명 코팅(324)은 광학 조리개(326)를 정의하며, 이는 특정 파장의 광 또는 특정 파장 범위의 광이 통과할 수 있는 투명한 창으로서 역할을 한다. 각각의 기판들(312, 314)의 외부 표면은 얇은 반사 방지 코팅(ARC)(328)으로 코팅될 수 있다.

[0028] 대향하는 광학 소자들(opposing optical elements)(16, 18) 사이의 간격 'd'를 증가시키기 위하여, 진공 주입 성형된 스페이서(380)는 광학 소자들(316, 318)을 형성하는 재료의 바깥쪽 부분들(320)을 분리시킨다. 스페이서(380)는 하단 기판(312) 상의 광학 소자(316)의 바깥쪽 부분(320)에 직접 (접착제 없이) 고정될 수 있다. 스페이서(380)는 글루 또는 다른 접착제(322)에 의해 상단 기판(314) 상의 광학 소자(318)의 바깥쪽 부분(320)에 부착될 수 있다. 하단 기판(312)의 ARC측은 광학 소자들(316, 318)과, 어셈블리(300)가 장착되는 표면 사이에 잘 정의된 거리를 제공하는 스페이서(390)를 포함한다. 스페이서(390)는 진공 주입 성형된 스페이서일 수 있으며, 이는 하단 기판(312)의 ARC측에 직접 (즉, 접착제 없이) 고정될 수 있다. 스페이서(390)는 조리개(326) 아래에 개구(332)를 갖는다.

[0029] 도 3에 도시된 바와 같이, 스페이서들(380, 390)은 단일 진공 주입 성형 단편으로 형성될 수 있으며, 그 일부(392)는 하단 기판(312)의 바깥쪽 에지들(lateral side edges)(394)을 둘러싸고 있다.

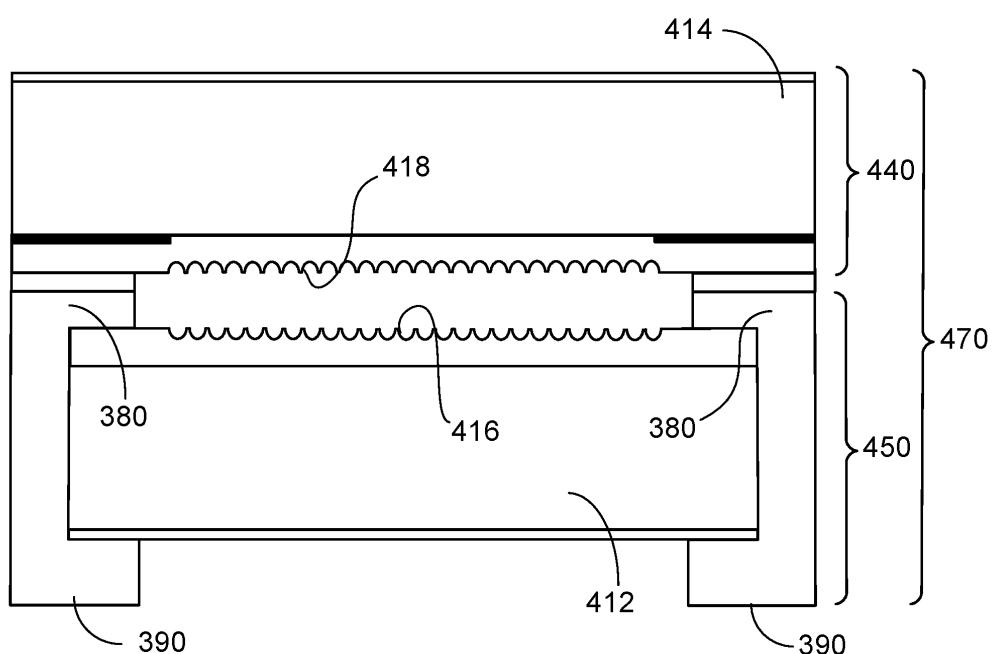

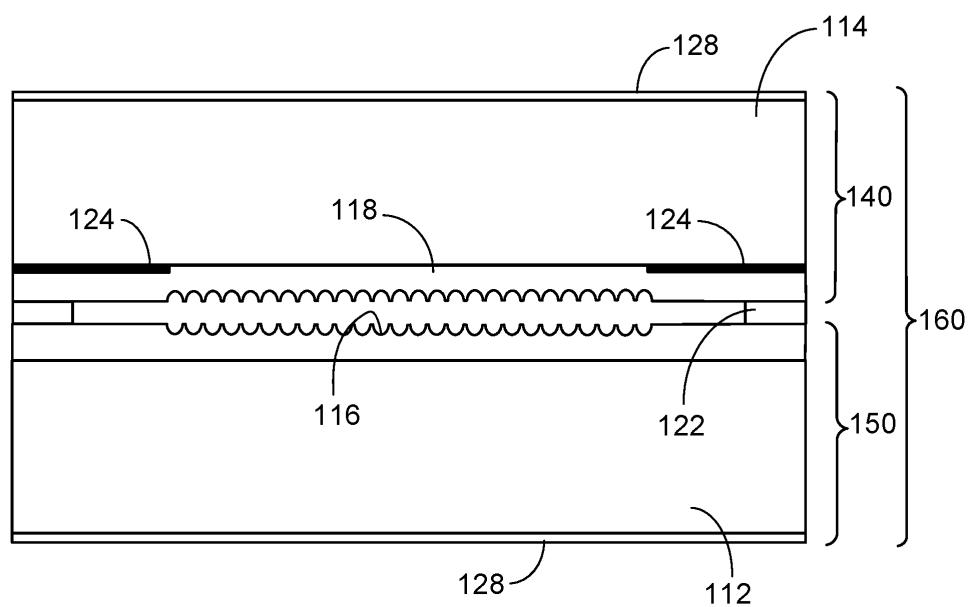

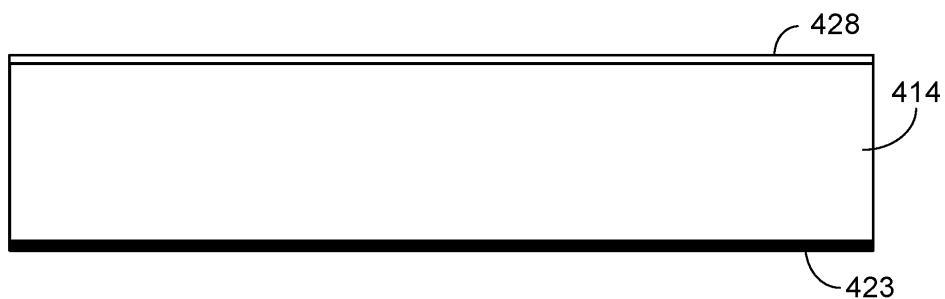

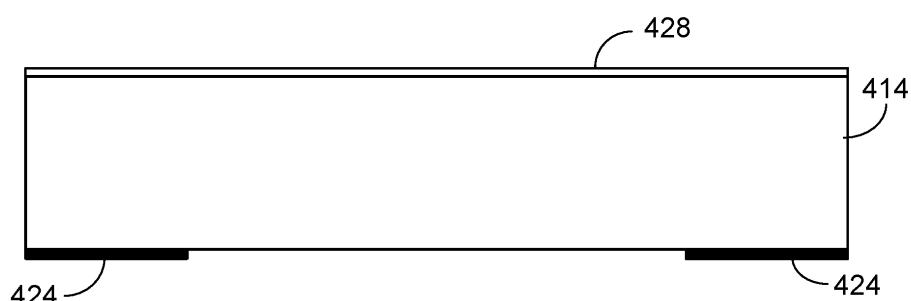

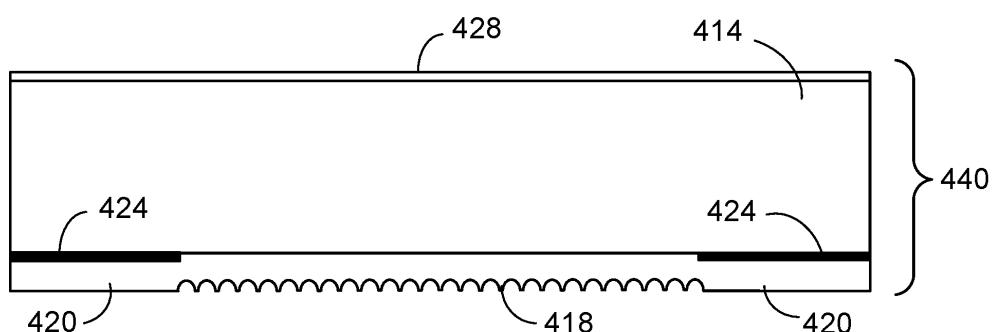

[0030] 도 4a 내지 도 4f는 도 3의 어셈블리(300)와 같은 광학 소자 스택 어셈블리들을 제조하기 위한 웨이퍼 레벨 방법의 단계들을 도시한다. 도 4a 내지 도 4c는 각각의 어셈블리(300)를 위한 상단 기판(314)을 제공하는 제1 웨이퍼 서브어셈블리(440)를 형성하는 프로세스를 나타낸다. 프로세스의 이러한 부분은 도 2a 내지 도 2c의 대응하는 단계들과 실질적으로 동일할 수 있다. 따라서, 도 4a에 나타난 바와 같이, 제1 투명 웨이퍼(414)가 제공되고, 제1 투명 웨이퍼는 제1 표면 상의 ARC(428) 및 그 반대의 제2 표면 상의 불투명 층(예를 들면, 포토레지스트)(423)을 갖는다. 웨이퍼(414)는, 예를 들어, 특정 파장 또는 파장 범위에 투명한 유리, 중합체 또는 다른 재료로 구성될 수 있다. 도 4b에 나타난 바와 같이, 층(423)은 각 어셈블리(300)를 위한 불투명 코팅(324)을 정의하는 불투명 재료의 영역들(424)을 형성하도록 (예를 들어, 표준 포토리소그래피 기술들을 사용하여) 패터닝 된다.

[0031] 다음으로, 도 4c에 나타난 바와 같이, 광학 소자들(418)(예를 들어, DOE들)은 기판(414)의 제2 표면 상에 형성

된다. 그 중 하나가 도 4c에 나타나 있는 광학 소자들(418)은, 예를 들어, 위에서 논의한 바와 같은 웨이퍼 레벨 복제에 의해 형성될 수 있다. 도 4a 내지 4c의 프로세싱은 각각의 어셈블리(300)를 위한 상단 기판(314)을 제공하는 제1 웨이퍼 서브어셈블리(440)를 야기한다.

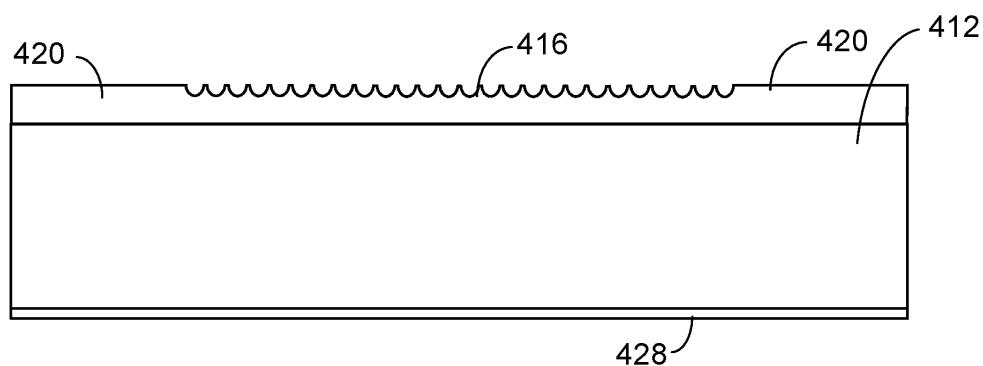

[0032] 제조 프로세스의 일부로서, 제2 투명 웨이퍼(412)가 또한 제공되고, 제2 투명 웨이퍼는 그것의 제1 표면 상에 ARC(428)를 갖는다(도 4d). 제2 웨이퍼(412)의 초기 준비 및 프로세싱은 도 2d의 웨이퍼(112)의 초기 준비 및 프로세싱과 유사할 수 있다. 따라서, 그 중 하나가 도 4d에 나타나 있는 광학 소자들(416)(예를 들어, DOE들)은, 웨이퍼(412)의 제2 표면 상에 형성된다. 광학 소자들(416)은 또한, 예를 들어, 상술한 바와 같은 웨이퍼 레벨 복제에 의해 형성될 수 있다.

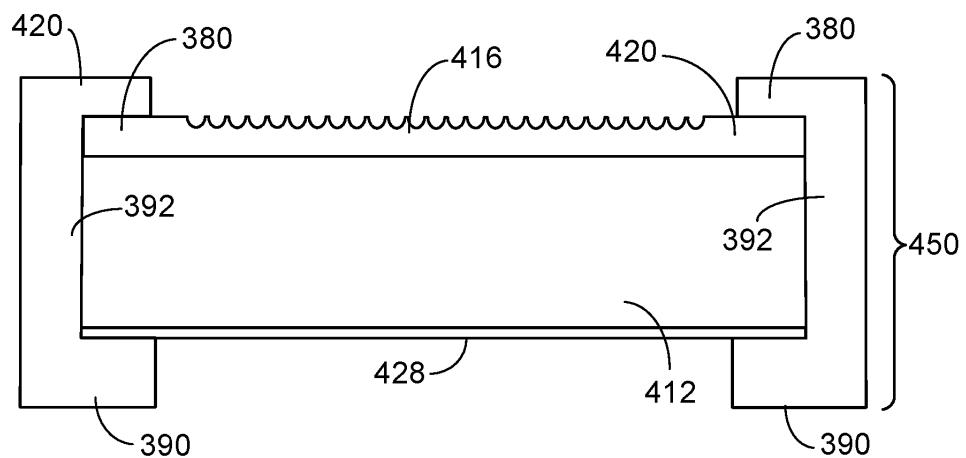

[0033] 다음으로, 도 4e에 도시된 바와 같이, 제2 웨이퍼 서브어셈블리(450)는 관통 홀들의 형성, 및 관통 홀들을 채우고 상단 및 하단 스페이서(380, 390)를 형성하는 진공 주입 성형 프로세스의 대상이다. 따라서, 스페이서들(380, 390)은 단일 진공 주입 성형 단편으로서 형성될 수 있고, 그 일부(392)는 제2 웨이퍼(412)의 관통 홀들을 채운다. 적합한 기술들은 미국 특허 번호 9,094,593 및 미국 공개 특허 출원 번호 2015-0034975에 설명되어 있다. 기술들은, 예를 들어, 다이싱(dicing), 마이크로머시닝(micromachining) 또는 레이저 커팅(laser cutting)에 의해 웨이퍼를 관통하는 관통 홀들을 형성하는 것을 포함한다. 그 다음에 웨이퍼 내의 개구들을 채우고 스페이서를 형성하기 위한 에폭시 또는 다른 적절한 재료를 제공하기 위해 진공 주입이 사용될 수 있다. 일부 경우에 있어서, 에폭시 또는 다른 재료는 차후에 (예를 들어, 열 및/또는 UV 처리들에의 노출을 통해) 큐어링된다. 전술한 미국 특허 문헌들의 개시 내용은 본 명세서에 참조로 포함된다. 도 4e의 프로세싱은 각각의 어셈블리(300)를 위한 하단 기판(412)을 제공하는 제2 웨이퍼 서브어셈블리(450)를 야기한다.

[0034] 다음으로, 도 4f에 나타난 바와 같이, 제1 및 제2 웨이퍼 서브어셈블리들(440, 450)은 웨이퍼 스택(470)을 형성하기 위해 서로 부착된다. 서브어셈블리들(440, 450)은, 예를 들어, 글루 또는 다른 접착제에 의해 (예를 들어, 글루 분사(glue jetting) 또는 스크린 프린팅에 의해) 서로 부착될 수 있고, 광학 소자들(416, 418)이 서로 마주 보도록 서로 부착될 수 있다. 그 다음에, 웨이퍼 레벨 스택(470)은 다수의 개별 어셈블리들(300)을 형성하기 위해 (예를 들어, 다이싱에 의해) 분리될 수 있다.

[0035] 일부 예에서, 도 4e에, 제2 웨이퍼 서브어셈블리(450)는, 예를 들어, UV 다이싱 테이프(UV dicing tape)에 부착될 수 있고, 이어서 복수의 싱글레이션된 기판들(singulated substrates)을 형성하기 위해 다이싱될 수 있다. 그 다음에, 싱글레이션된 기판들은 상부 및 하부의 스페이서들(380, 390)를 형성하기 위해 진공 주입 툴(vacuum injection tool)에 제공될 수 있다. 이 경우, 웨이퍼 레벨 방법은 각각의 광학 소자(416, 418)가 제1 웨이퍼(414)와 싱글레이션된 기판들 중 하나 사이에 배치되도록 스택을 형성하기 위해 제1 웨이퍼(414)를 싱글레이션된 기판들에 부착하는 것을 포함할 수 있다. 그 다음에, 스택은 복수의 스택 어셈블리들로 (예를 들어, 다이싱에 의해) 분리되고, 스택 어셈블리 각각은 광학 소자들 중 적어도 하나를 포함한다.

[0036] 스페이서들(380, 390)을 형성하기 위해 진공 주입 기술(vacuum injection technique)을 사용하는 것이 유리할 수 있다. 예를 들어, 상부 스페이서(380)의 추가는, 광학 소자들(316, 318)을 위한 복제된 재료의 바깥쪽 부분들(320)의 두께가 다소 제한되더라도 (예를 들어, 일부 경우에  $50 \mu\text{m}$  이하로 제한됨), 광학 소자들(316, 318) 사이의 거리 'd'가 증가되는 것을 허용한다.

[0037] 도 4a 내지 도 4f의 예시적인 프로세스에서, 모든 웨이퍼들(412, 414)은 그들 각각의 표면 상에 복제된 광학 소자들(416, 418)을 갖는다. 그러나, 일부 구현예에서, 웨이퍼들 중 하나(제1 웨이퍼(414) 또는 제2 웨이퍼(412) 중 어느 하나)만이 그 표면 상에 광학 소자들을 갖는다. 또한, 광학 소자들(416, 418)은 DOE들로서 나타내졌지만, 일부 예에서는 다른 유형의 광학 소자들이 사용될 수 있다.

[0038] 스택 어셈블리들(도 1의 10 및 도 3의 300)은 광범위한 광전자 모듈들에 통합되거나 광범위한 광전자 모듈들과 함께 사용될 수 있다. 이러한 모듈들은 광 방출기들(예를 들어, 발광 다이오드들(LED들), 적외선(IR) LED들, 유기 LED들(OLED들), 적외선(IR) 레이저들, 또는 수직 공동 표면 방출 레이저들(VCSEL들)) 및/또는 광 센서들(예를 들어, CCD 또는 CMOS 센서)과 같은 능동 광전자 구성요소들(active optoelectronic components)을 포함할 수 있다. 또한, 이러한 모듈들은 다양한 유형의 가전 제품들, 및 바이오 디바이스들, 모바일 로봇들 및 디지털 카메라들 등 뿐만 아니라 휴대 전화들, 스마트 폰들, 개인용 정보 단말기들(PDA들), 태블릿들 및 랩톱들과 같은 다른 디바이스들에 통합될 수 있다.

[0039] 다양한 변형들이 쉽게 명백할 것이고 본 발명의 사상 내에 있다. 따라서, 다른 구현예들이 청구항들의 범위 내에 있다.

도면

도면1

도면2a

도면2b

도면2c

도면2d

도면2e

## 도면2f

## 도면3

도면4a

도면4b

도면4c

도면4d

도면4e

도면4f