(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3998386号

(P3998386)

(45) 発行日 平成19年10月24日(2007.10.24)

(24) 登録日 平成19年8月17日(2007.8.17)

(51) Int.C1.

F 1

H01L 21/677 (2006.01)

G02F 1/13 (2006.01)H01L 21/68

G02F 1/13 101

A

請求項の数 12 (全 14 頁)

(21) 出願番号 特願2000-17223 (P2000-17223)

(22) 出願日 平成12年1月26日 (2000.1.26)

(65) 公開番号 特開2001-210693 (P2001-210693A)

(43) 公開日 平成13年8月3日 (2001.8.3)

審査請求日 平成16年5月7日 (2004.5.7)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100091409

弁理士 伊藤 英彦

(74) 代理人 100096781

弁理士 堀井 豊

最終頁に続く

(54) 【発明の名称】 液晶表示装置の製造装置および液晶表示装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

液晶表示装置の基板を洗浄する洗浄処理室と、

前記洗浄処理室で洗浄された前記基板に対して成膜処理を行う成膜処理室と、

前記洗浄処理室から前記成膜処理室へ前記基板を外気にさらすことなく移送する外気遮断移送手段とを備え、

前記外気遮断移送手段は、前記洗浄処理室で洗浄された前記基板を外気にさらすことなく、複数の前記基板が収容可能な力セッテ内に搬入する基板搬入手段と、前記成膜処理室において前記基板を前記力セッテ内から取り出す基板取り出し手段とを含み、

前記外気遮断移送手段は、前記洗浄処理室から前記成膜処理室まで前記基板が移送される通路であって外気が遮断された外気遮断通路を含み、

前記外気遮断移送手段は、前記力セッテを搬送可能に形成され、

前記外気遮断通路は、外気から概ね遮断される程度の緩密閉構造を有しており、前記外気遮断通路の内部では、前記基板に対して不活性の不活性ガスが外気に対して陽圧に保たれており、液晶表示装置の製造装置。

## 【請求項2】

前記洗浄処理室は、前記基板を薬液により洗浄する薬液洗浄処理室を含む、請求項1に記載の液晶表示装置の製造装置。

## 【請求項3】

前記力セッテは、外気と隔離可能な密封力セッテを含む、請求項1または2に記載の液

10

20

晶表示装置の製造装置。

## 【請求項 4】

力セットロード室と、搬送口ボットを有する搬送口ボット室とを備え、前記力セットロード室、前記洗浄処理室および前記成膜処理室は、いずれも、前記搬送口ボットの周囲に配置され、前記搬送口ボットによって前記基板の出し入れができるように前記搬送口ボット室と連絡している、請求項 1 から 3 のいずれかに記載の液晶表示装置の製造装置。

## 【請求項 5】

前記外気遮断通路と連絡し、外気と遮断された処理室であって、前記基板に対してアニール処理を施すアニール処理室をさらに備える、請求項 1 から 4 のいずれかに記載の液晶表示装置の製造装置。

10

## 【請求項 6】

前記アニール処理室において、前記基板に対してレーザアニール処理ができる光学アライメントユニットを備える、請求項 5 に記載の液晶表示装置の製造装置。

## 【請求項 7】

前記成膜処理室は、前記外気遮断通路と連絡する第 1 の成膜処理室と、前記外気遮断通路と連絡する第 2 の成膜処理室とを備える、請求項 1 から 6 のいずれかに記載の液晶表示装置の製造装置。

## 【請求項 8】

前記密封力セットは、外気から概ね遮断される程度の緩密閉構造を有しており、前記密封力セットの内部では、前記基板に対して不活性の不活性ガスが外気に対して陽圧に保たれている、請求項 3 に記載の液晶表示装置の製造装置。

20

## 【請求項 9】

ケミカルフィルタをさらに備え、該ケミカルフィルタを通して前記不活性ガスが前記外気遮断通路または密封力セットに導入されている、請求項 1 から 8 のいずれかに記載の液晶表示装置の製造装置。

## 【請求項 10】

ガラス基板の上に下地膜を有する基板を洗浄処理室に装入して、洗浄処理を行う工程と、

前記洗浄が行われた前記基板を、前記洗浄処理室から取り出し、外気にさらすことなく成膜処理室に装入する移送工程と、

30

前記成膜処理室において前記基板の上にアモルファスシリコン膜を成膜する工程とを備え、

前記移送工程は、複数の前記基板が収容可能な力セットに前記基板を挿入して搬送する工程を含み、

前記移送工程は、前記洗浄処理室で洗浄された前記基板を外気にさらすことなく、力セット内に搬入する工程と、前記成膜処理室において前記基板を前記力セット内から取り出す工程とを含み、

前記移送工程は、外気から概ね遮断される程度の緩密閉構造を有しており、内部では前記基板に対して不活性の不活性ガスが外気に対して陽圧に保たれている外気遮断通路を通して行なう、液晶表示装置の製造方法。

40

## 【請求項 11】

前記アモルファスシリコン膜を形成する工程の後に、引き続き外気にさらすことなく、前記アモルファスシリコン膜が成膜された基板を、アニールして多結晶体シリコン膜にする工程とを備える、請求項 10 に記載の液晶表示装置の製造方法。

## 【請求項 12】

前記多結晶体シリコン膜を形成する工程の後に、引き続き外気にさらすことなく別の成膜処理室に移送する工程と、その別の成膜処理室において、前記多結晶体シリコン膜の上にゲート絶縁膜を形成する工程とを備える、請求項 11 に記載の液晶表示装置の製造方法。

## 【発明の詳細な説明】

50

**【0001】****【発明の属する技术分野】**

本発明は、液晶表示装置の製造装置および液晶表示装置の製造方法に関し、特に駆動回路一体型液晶表示装置およびその駆動回路一体型液晶表示装置の製造方法に関する。

**【0002】****【従来の技术】**

薄膜トランジスタ(TFT:Thin Film Transistor)を用いた駆動回路一体型液晶表示装置において、画素領域のTFTは、画素電極への充電と電荷保持のスイッチの2つの役割を果たしているだけであった。このため、画素領域のTFTへの要求性能は、一般的の半導体装置に要求されるような、細かいしきい値電圧の制御は必要とされない。したがって、画素領域のTFTに用いられる薄膜半導体はアモルファスシリコンで十分用が足りていた。

10

**【0003】**

近年、アモルファスシリコンをレーザアニールすることによって形成された多結晶体シリコンTFTを用いる技術開発が行われ、この多結晶体シリコンTFTを用いた液晶表示装置が盛んに製造されている。この型の液晶表示装置は駆動回路領域と画素領域とを一体的に形成することによって、低コスト化や表示画素の高精細化が可能となる利点を有する。この多結晶体シリコンTFTは、駆動回路の素子に要求される特性を有する必要があるので、高精度のしきい値電圧を保持する必要がある。このため、新たな課題が発生してきている。

**【0004】**

20

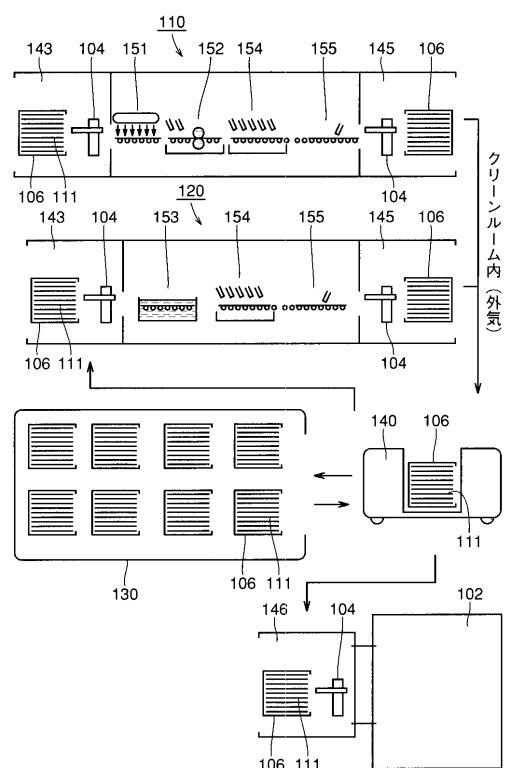

アモルファスシリコンを用いた従来の液晶表示装置の製造工程においては、通常、アモルファスシリコンの成膜処理の前工程で異物除去やアモルファスシリコン膜の密着力向上のために洗浄処理が行われてきた。図12は、従来の洗浄工程から成膜処理工程に至る経路の雰囲気環境を示す図である。洗浄処理には物理洗浄工程110と化学洗浄工程120とがある。カセット106に搭載された基板111は、自動搬送車(AGV:Automatic Guided Vehicle)140によってローダ143に搬入され、搬送ロボット104によって物理洗浄室に入れられ、物理洗浄処理を施される。ここで、「基板」というとき、石英基板等の基板そのものその他に処理が施された基板をも含むものとする。まず、UVランプ151によって紫外光を照射されて有機物を除去され、ついでブラシ洗浄やメガソニック洗浄等の物理洗浄ユニット152で洗浄され、水洗処理ユニット154および乾燥処理ユニット155を経て、アンローダ145に送り出される。また、化学洗浄工程120では、薬液による化学洗浄が施される化学洗浄ユニット153を備えるが、入口および出口の基板の取扱いは物理洗浄工程と同じである。これらの洗浄が済んだ基板は、クリーンルームの雰囲気開放のカセット106に収納され、AGVにより成膜処理室102のローダ/アンローダ146に搬送される。ここで、基板111は搬送ロボット104によりカセット106から取り出され、成膜処理室内でアモルファスシリコンの成膜処理が施される。次いで、再びクリーンルーム雰囲気にさらされて搬送され、レーザアニール処理室でアモルファスシリコンの結晶化を目的とするレーザアニール処理が行われる。これら基板は成膜処理装置の空き時間との関係で、保管庫130に保管され、下地膜が長時間にわたってクリーンルーム雰囲気にさらされる場合もある。これまで、この搬送や保管の間、パーティクルに関しては高レベルの付着防止管理がなされてきた。

30

**【0005】****【発明が解決しようとする課題】**

しかしながら、上記の基板がクリーンルーム雰囲気に対して開放されていたことから分かるように、基板表面の化学的汚染に関しては、十分な管理はなされていなかった。このような化学的汚染の影響は、画素領域にのみ用いられていたアモルファスシリコンTFTでは全く問題とならないレベルである。しかし、駆動回路を構成する多結晶体シリコンTFTでは、金属などの汚染によるドーピング効果や有機汚染による多結晶体シリコンの結晶粒成長等に及ぼす影響が生じる。このため、しきい値電圧が変動し、基板内ばらつきが発生し、駆動回路において誤動作等を生じ、歩留りの低下をきたしていた。

40

50

## 【0006】

そこで、本発明の目的は、クリーンルーム雰囲気と接することに起因する化学的汚染を防止し、しきい値電圧の変動等を生じないようにすることが可能な液晶表示装置の製造装置および液晶表示装置の製造方法を提供することにある。

## 【0007】

## 【課題を解決するための手段】

本発明の請求項1の液晶表示装置の製造装置は、液晶表示装置の基板を洗浄する洗浄処理室と、洗浄処理室で洗浄された基板に対して成膜処理を行う成膜処理室と、洗浄処理室から成膜処理室へ基板を外気にさらすことなく移送する外気遮断移送手段とを備える。外気遮断移送手段は、洗浄処理室で洗浄された基板を外気にさらすことなく、複数の基板が收容可能なカセット内に搬入する基板搬入手段と、成膜処理室において基板をカセット内から取り出す基板取出し手段とを含む。外気遮断移送手段は、洗浄処理室から成膜処理室まで基板が移送される通路であって外気が遮断された外気遮断通路を含む。外気遮断移送手段は、カセットを搬送可能に形成されている。外気遮断通路は、外気から概ね遮断される程度の緩密閉構造を有しており、外気遮断通路の内部では、基板に対して不活性の不活性ガスが外気に対して陽圧に保たれている。

10

## 【0008】

この構成により、洗浄後、クリーンルーム雰囲気にさらされることがないので、化学的汚染が防止される。このため、金属汚染によるドーピング効果や有機汚染による結晶粒度のばらつき発生等のために、しきい値電圧が変動することがなくなる。また、洗浄後のパーティクル付着を防止することができる。この結果、駆動回路の誤動作等によって製品歩留りが低下する事態を避けることができる。なお、上記の基板は、先に定義した基板をさす。

20

## 【0009】

請求項2の液晶表示装置の製造装置では、請求項1の装置において、洗浄処理室は、基板を薬液により洗浄する薬液洗浄処理室を含む。

## 【0010】

また、外気遮断通路内において基板を搬送する搬送機を備えることが好ましい。この構成により、基板を外気にさらすことなく自動的に搬送することが容易になる。また、自動化することによって、待ち時間や搬送時間を短縮することが容易になり、製造の高効率化が可能となる。

30

## 【0011】

請求項3の液晶表示装置の製造装置では、請求項1または2の装置において、カセットは、外気と隔離可能な密封カセットを含む。

## 【0012】

この構成により、基板が外気にさらされることなく密封カセット内に格納されたまま、洗浄処理室から成膜処理室に搬送されるので、化学的汚染および洗浄後のパーティクル付着を避けることができる。なお、洗浄処理室のアンロード部から成膜処理室のロード部への密封カセットの搬送はAGVのような搬送機によって行ってもよいし、手動で行ってもよい。

40

## 【0013】

請求項4の液晶表示装置の製造装置では、請求項1から3のいずれかの装置において、カセットロード室と、搬送口ボットを有する搬送口ボット室（ロードロック室）とを備え、カセットロード室、洗浄処理室および成膜処理室は、いずれも、搬送口ボットの周囲に配置され、搬送口ボットによって基板の出し入れができるように搬送口ボット室と連絡している。

## 【0014】

この構成により、カセットロード室から洗浄処理室を経て成膜処理室まで、搬送口ボットによって基板を外気にさらすことなく連続的に搬送することができる。この結果、化学的汚染や洗浄後のパーティクル付着を防止した上で、成膜処理の短時間化および高効率

50

化を実現することができる。また、上記の各室を組み込んだ装置を小型化してクリーンルーム内において省スペースを実現することができる。請求項1～4の装置においては、外気遮断通路または密封カセットの内部は、外気が $10^3$ Pa以下に減圧された雰囲気、窒素ガス雰囲気、またはドライエア雰囲気とされていることが望ましい。基板は上記の雰囲気の中で、化学的汚染や洗浄後のパーティクル付着を受けることがなく、また、これらの雰囲気は安価に実現することができるので、製造コストを高めることがなくなる。なお、窒素ガス、ドライエア等を不活性ガスと記す。

## 【0015】

請求項5の液晶表示装置の製造装置では、請求項1～4のいずれかの装置において、外気遮断通路と連絡し、外気と遮断された処理室であって、基板に対してアニール処理を施すアニール処理室をさらに備えている。10

## 【0016】

この構成により、成膜された膜を外気にさらすことなくアニール処理することができる。このため、成膜されたアモルファスシリコン膜の化学的汚染等を防止した状態でアニール処理して多結晶体シリコン膜とすることが可能となる。

## 【0017】

請求項6の液晶表示装置の製造装置では、請求項5の装置において、アニール処理室で基板に対してレーザアニール処理ができる光学アラインメントユニットを備えている。

## 【0018】

この構成により、アモルファスシリコン膜を低温で結晶粒径の大きい多結晶体シリコン膜とすることができます。このため、化学的汚染を防止したうえで、駆動回路に使用できる性能を有するTFTを製造することができる。20

## 【0019】

請求項7の液晶表示装置の製造装置では、請求項1～6のいずれかの装置において、成膜処理室は、外気遮断通路と連絡する第1の成膜処理室と、外気遮断通路と連絡する第2の成膜処理室とを備えている。

## 【0020】

この構成により、第1の成膜室で成膜される化学的汚染を嫌う膜、例えば多結晶体シリコンは、下地膜の側からも、また上側、すなわちゲート絶縁膜の側からも化学的汚染を防止することができる。この結果、安定したしきい値電圧を得ることができ、歩留り向上を果たすことができる。30

## 【0021】

請求項8の液晶表示装置の製造装置では、請求項3の装置において、密封カセットは、外気から概ね遮断される程度の緩密閉構造を有しており、密封カセットの内部では、基板に対して不活性の不活性ガスが外気に対して陽圧に保たれている。請求項9の液晶表示装置の製造装置では、請求項1から8のいずれか装置において、ケミカルフィルタをさらに備え、該ケミカルフィルタを通して窒素ガスまたはドライエアが外気遮断通路または密封カセットに導入されている。

## 【0022】

この構成は、厳密な密閉構造よりも安価に実現することができる。このため、安価に化学的汚染やパーティクル付着を防止することができ、歩留り向上の効果をより一層享受することが可能となる。40

## 【0023】

本発明の請求項10の液晶表示装置の製造方法は、ガラス基板の上に下地膜を有する基板を洗浄処理室に装入して洗浄処理を行う工程と、洗浄が行われた基板を、洗浄処理室から取り出し、外気にさらすことなく成膜処理室に装入する移送工程と、成膜処理室において基板の上にアモルファスシリコン膜を成膜する工程とを備える。移送工程は、複数の基板が収容可能なカセットに基板を挿入して搬送する工程を含む。移送工程は、洗浄処理室で洗浄された基板を外気にさらすことなく、カセット内に搬入する工程と、成膜処理室において基板をカセット内から取り出す工程とを含む。移送工程は、外気から概ね遮断され50

る程度の緩密閉構造を有しており、内部では基板に対して不活性の不活性ガスが外気に対して陽圧に保たれている外気遮断通路を通して行なう。

【0024】

この構成により、化学的汚染を嫌うアモルファスシリコン膜が下側から化学的汚染やパーティクル付着を受けることがないので、誤動作等を起こさず、高い歩留りを維持することが可能となる。

【0025】

請求項11の液晶表示装置の製造方法では、請求項10の製造方法において、アモルファスシリコン膜を形成する工程の後に、引き続き外気にさらすことなく、アモルファスシリコン膜が成膜された基板を、アニールして多結晶体シリコン膜にする工程とを備えている。

10

【0026】

この構成により、画素領域においては高精細化が可能となり、駆動回路領域の駆動トランジスタでは安価で安定した高精度しきい値電圧の確保が可能となる。また、画素領域と駆動回路領域とを一体的に形成することができ、液晶表示装置において重視される小型化を実現することができる。

【0027】

請求項12の液晶表示装置の製造方法では、請求項11の製造方法において、多結晶体シリコン膜を形成する工程の後に、引き続き外気にさらすことなく別の成膜処理室に移送する工程と、その別の成膜処理室において、多結晶体シリコン膜の上にゲート絶縁膜を形成する工程とを備えている。

20

【0028】

この構成により、多結晶体シリコンが下地膜の側からもゲート絶縁膜の側からも化学的汚染や洗浄後のパーティクル付着を受けることがなくなる。この結果、しきい値電圧の変動をより一層抑制することができ、歩留り低下をさらに確実に避けることが可能となる。

【0029】

【発明の実施の形態】

次ぎに、本発明の実施の形態について図を用いて説明する。

【0030】

(実施の形態1)

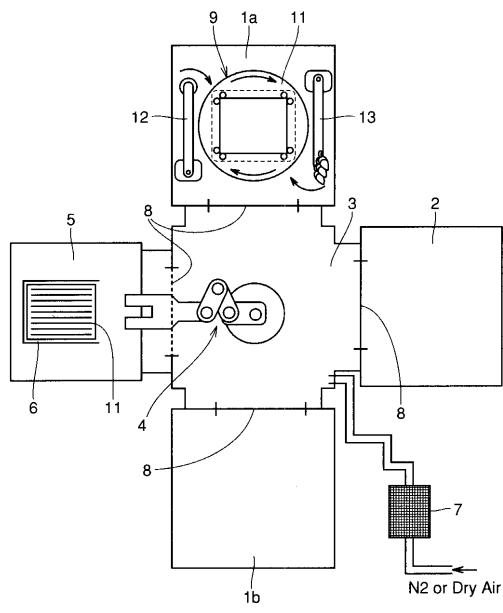

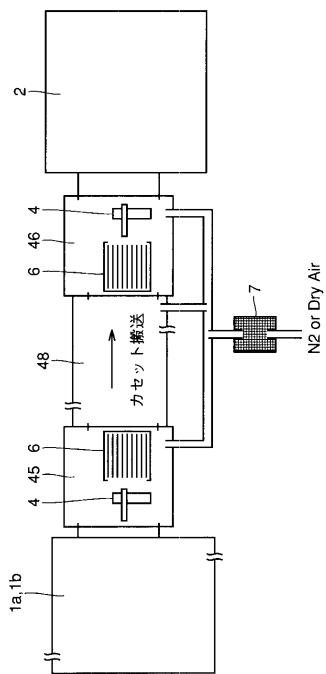

図1は本発明の洗浄処理室と成膜処理室とが一体化された装置を示す概略構成図である。本装置は、カセットローダ5、スピンドル式のウェット洗浄ユニット(以下、「洗浄ユニット」と記す)9が設置された洗浄ユニット室1a、UV照射ユニット室1bおよびCVD装置室2を有し、各室間の基板11の移動は、中央部のロードロック室(搬送口ボット室)3に設置された搬送口ボット4によって枚葉で行われる。ロードロック室3、UV照射ユニット室1b、洗浄ユニット室1a、CVD装置室2は、いずれも概ね密閉された緩密閉構造となっており、それぞれ配管(図示せず)によってガスを誘導できる構造を有し、ケミカルフィルタ7によって汚染物質が除去された窒素ガスまたはドライエアが導入される。各室内では、本装置外の雰囲気に対して陽圧となるように、誘導ガスの流量制御を行い、本装置外の雰囲気が混入しないようにしている。ロードロック室3に通じる各室の入口には開閉自在の扉8を設け、各室での基板処理中はロードロック室と雰囲気を分離できる構成となっている。カセットローダ5とロードロック室8との間に開閉自在の扉8を設け、基板の受け渡し時以外は閉じておく。特に、洗浄が完了した基板のCVD装置室2への搬送時には、ロードロック室3の雰囲気を制御する必要がある。成膜処理を行うCVD装置室内においては、当然、通常の真空装置と同様に、ポンプにより真空または減圧に引けるようにされている。

40

【0031】

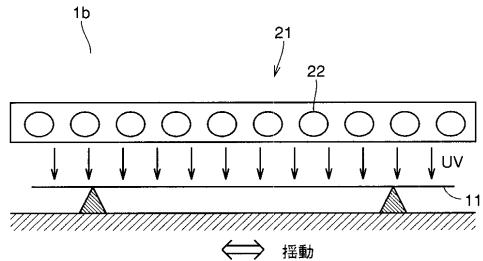

つぎに、各ユニット(装置)について説明する。図2は、UV照射ユニット室1bに設置されたUV照射ユニットの模式的断面図である。基板11のサイズに合わせたUV照射ユニット21は、150W程度の低出力型のUVランプ22が0.2本/cmの密度で備え

50

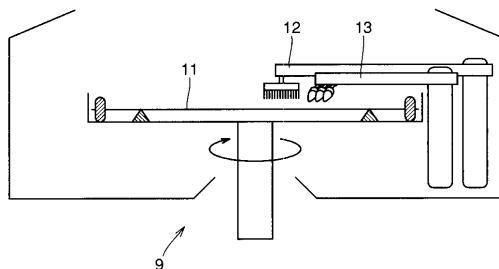

られている。また、ステージを可動構造にして、ランプピッチの半分の振幅で、基板 11 を揺動し UV 照射が均一に行われるようとする。この UV ランプの代わりに、波長 172 nm のエキシマ UV ランプ等を用いることにより、有機物の除去効率を高めることも可能である。図 3 は洗浄ユニット 9 の模式的断面図である。ここに備えられる洗浄処理装置は、液晶表示装置の製造に一般的に用いられるインライン写真製版装置の洗浄ユニットや現像ユニットと同等の性能のものでよい。この洗浄ユニット 9 は、基板の回転機構、アームによるブラシ洗浄機構 12、メガソニック洗浄機構などの物理洗浄と、薬液やリンス液を放出できるノズルによる化学洗浄との両方ができるアーム機構 13 を備える。洗浄に使用する薬液に応じて、基板支持ステージ台や薬液の飛散防止のカップの材質を耐薬液性とすることが望ましい。ここでは、薬液としてフッ酸系が使えるように、テフロンをコーティングしたステンレスを用いるのがよい。物理洗浄機構と薬液との組合せに不都合が生じる場合には、スピニ式の物理洗浄ユニットを別に設けてもよい。その場合には、酸化性の薬液などを用いることも可能である。

#### 【0032】

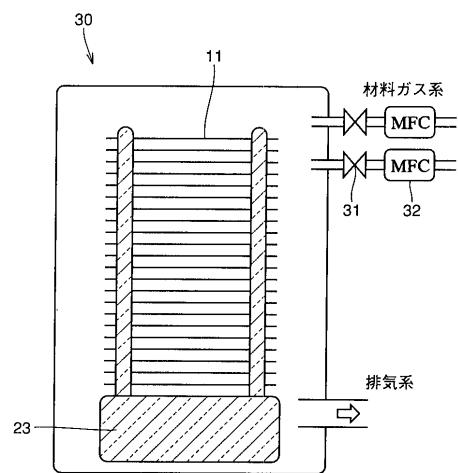

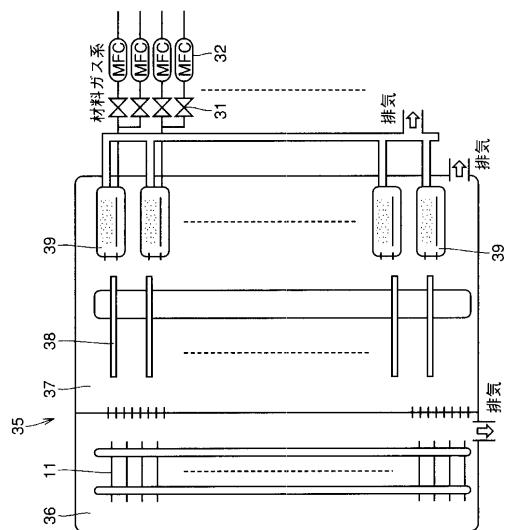

つぎに CVD 装置の例を示す。これらの CVD 装置は、どの種類の CVD 装置においても、一般的の液晶表示装置の製造に用いられる CVD 装置と同様のものでよい。図 4 は、減圧 CVD (LPCVD) ユニットの断面図である。この LPCVD 装置 30 は、チャンバ内に基板を支持する石英ポート 23、ポンプ（図示せず）等による減圧が可能な排気機構、および成膜ガスを導入するマスフローコントローラ (MFC) 32 やバルブ 31 を備えた配管系統を有している。また、図 5 に示すように、プラズマ CVD (PCVD) 装置では、プラズマ発生機構の付いた成膜処理室 39 には成膜ガスを導入する MFC 32 やバルブ 31 等を備えた配管が接続されている。また、基板 11 の予備加熱や冷却、さらに成膜処理室と低圧状態で基板の受け渡しが可能なように、ロードロック室 36 と、搬送ロボット 38 を設置した予備室 37 との二室を備えている。また、成膜処理室 39 はそれぞれ独立に、ポンプにより低圧に引ける排気機構を有している。この CVD 装置に付け加えて、同じ雰囲気内にアモルファスシリコンから多結晶体シリコンに結晶化するレーザアニール室を配置してもよい。レーザアニール装置としては、300 程度の低温で多結晶体シリコンを生成させる一般的な装置でよい。

#### 【0033】

上記の装置を用いて得られる作用はつぎのとおりである。洗浄処理から成膜処理、さらにレーザアニール処理に至る工程を外気に触れることなく、自動的に連続処理することができる。この結果、基板への化学汚染やパーティクル付着を低減することができる。また、このような緩密閉構造に雰囲気を制御したガスを導入することにより、さらに汚染付着を低減することができる。使用するガスとしては窒素ガスまたはドライエアのような安全で比較的安価なガスでよく、ケミカルフィルタを通して汚染物質を除去したものを導入することが望ましい。各室とも緩密閉構造を採用しているので、液晶表示装置用の大型ガラス基板を処理する場合、完全密閉構造とする場合に比較して装置コストの大きな低減をはかることができる。また、本装置は、成膜処理装置に LPCVD 装置を用いた場合に、とくに効果が高くなる。その理由は、LPCVD 法によって成膜したアモルファスシリコンを結晶化して多結晶体シリコンを形成する場合に、LPCVD による成膜速度がとくに遅く、下地の汚染の影響が大きく現れるからである。この汚染の影響により、多結晶体シリコンの結晶性が変動し易く、この結果、完成した TFT の特性は汚染の影響を強く受けれる。本実施の形態の装置を用いれば、上記の変動を抑制して安定した特性の TFT を作り込むことが可能となる。

#### 【0034】

さらに装置構成として、搬送ロボットを中心各ユニットを配置したことにより、装置が非常にコンパクトになり、装置の省スペース化が可能となる。また、本実施の形態では、UV 照射ユニットと他のウェット洗浄ユニットとの両方を用いたために、有機物および金属の汚染を確実に防止することができる。また、酸化性の処理液を用いると、有機物の除去効果がさらに向上する。しかし、とくに汚染を有機物に限定してよい場合には、洗浄ユ

10

20

30

40

50

ニットとしてUV照射ユニットのみでよい。この場合には、装置の大きさは、従来の成膜装置の搬送口ボットと成膜室との間にUV照射ユニットを取り付けただけの非常なコンパクトな装置とすることができます、省スペースの効果を上げることができる。

【0035】

(実施の形態2)

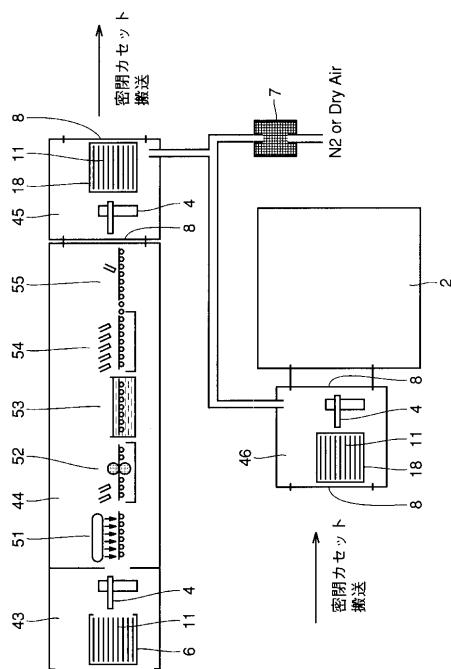

図6は、実施の形態2における製造装置の概略構成図である。洗浄装置は、液晶表示装置の製造に用いられてきた従来の洗浄装置でよく、UV照射ユニット51、ブラシ洗浄やメガソニック洗浄等の物理洗浄ユニット52、薬液による化学洗浄ユニット53、水洗ユニット54、乾燥ユニット55を備えている。成膜処理室2には、実施の形態1で説明したものと同等の性能のCVD装置が備えられる。洗浄処理室44のアンローダ43には、密閉可能なゴムパッキング付きの扉を備えたカセット18内に基板11を入れ、カセットの扉を閉じることによってカセット内に基板を密封封入する機構(図示せず)が備えられている。また、成膜処理室2のローダ46においては、密閉カセットの扉を開ける機構(図示せず)が備えられている。この密閉カセット18は洗浄処理室から成膜処理室まで、AGV等によって搬送してもよいし、洗浄処理室から成膜処理室までコンベアで自動搬送してもよい。

10

【0036】

さらに洗浄処理室のアンローダ45と成膜処理室のローダ46とは、入口と出口との両方に開閉自在の扉8を備え、扉を閉じた状態において概ね密閉構造となる緩密閉構造を有する。さらに、これらのアンローダ45およびローダ46には、ケミカルフィルタ7を通った窒素ガスやドライエアを誘導し、流量制御により装置外に対して陽圧を保ち、装置外の雰囲気が混入しない構造となっている。

20

【0037】

密閉カセット内の雰囲気としては、洗浄処理室のアンローダ45の雰囲気であるドライエアをそのまま封入してもよい。または、アンローダ45の雰囲気とは別に汚染物質を除去した窒素ガスまたはドライエアを直接カセット内に送り込んで封入してもよく、このほうがカセット内の雰囲気の管理を確実に実施できる。また、密閉後にカセット内を10<sup>3</sup>Pa以下程度に真空引きしても、雰囲気の汚染物質を1/100程度に低減できるので、基板に付着する汚染物質を十分に低くすることが可能である。

30

【0038】

別の方法として、図7に示すように、洗浄室のアンローダ45と成膜室のローダ46との間を概ね密閉構造の通路48として、この緩密閉構造の通路48に対して雰囲気制御を行うようにしてもよい。この構成によれば、上記の密閉カセット18における密閉機構および密閉カセットに対する開閉機構を省略することができる。この場合にも、実施の形態1において説明したように、液晶表示装置用の大型ガラス基板の処理において、完全に密閉する構造に比較して装置コストを大きく低減することができる。

【0039】

なお、実施の形態1および2ともに、成膜装置としてCVD装置を用いる場合を説明したが、洗浄後のパーティクル付着が歩留り低下につながるスパッタリング装置についても、本発明が適用できることは言うまでもない。

40

【0040】

(実施の形態3)

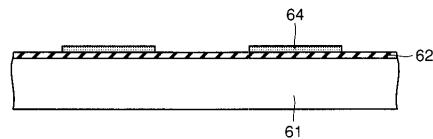

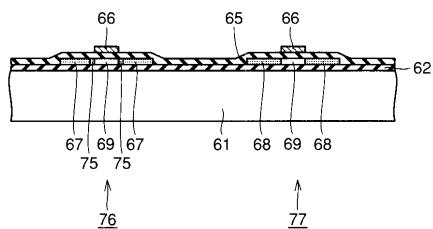

つぎに実施の形態1または2に示す製造装置にレーザアニール室を付け加えた本発明に係る装置を用いて、液晶表示装置の駆動回路部の多結晶シリコンTFTを製造する方法を説明する。まず、図8に示すように、ガラス基板11の表面に、例えば、PECVDによって下地膜としてシリコン窒化膜とシリコン酸化膜との2層膜62を連続形成する。つぎに、上記の洗浄・成膜・アニール一体型の装置を用いて、洗浄処理とLPCVD装置による成膜処理とレーザアニール処理とを連続して行う。洗浄処理としては、UV照射処理、ブラシ洗浄およびメガソニック洗浄を行い、その後、オゾン水またはHF系洗浄液を用いて薬液洗浄を行う。この後、基板を外気に触れないようにして成膜処理室に搬送して成膜

50

処理を行う。成膜処理としては、アモルファスシリコン膜を図4に示したLPCVD装置によって60nm程度形成する。さらに、外気にさらされることなく、上記装置に付け加えて設けたレーザアニール装置によってトランジスタのチャネル部のアモルファスシリコンをアニールして多結晶体シリコンとした後、図8に示すように、ドライエッ칭によりパターニングしてトランジスタ領域64を形成する。つぎに、図9に示すように、ゲート絶縁膜として、例えば、TEOS (Tetra Ethyl Ortho Silicate) PECVDによりシリコン酸化膜65を70nm程度形成する。この後、レジストを設けn型トランジスタ76のチャネル領域69の両端に燐イオンを低濃度に注入してn型不純物領域のLDD (Lightly Doped Domain) 75を形成する。次に、例えば、Cr膜を成膜し、パターニングしてゲート電極66を形成する。その後、燐イオン、ボロンイオンを順に注入してソース/ドレイン領域となるn+型不純物領域67およびp型不純物領域を形成し、それぞれn型トランジスタ76およびp型トランジスタ77を作り込む。燐イオンおよびボロンイオンの注入時には、n型トランジスタには燐イオンが、またp型トランジスタにはボロンイオンが注入されるようにする。

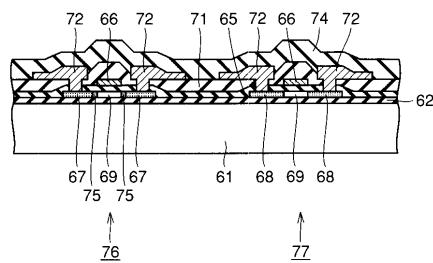

#### 【0041】

つぎに、図10に示すように、保護膜としてTEOS PECVDによりシリコン酸化膜71を形成した後、400で活性化アニールを行う。保護膜にコンタクトホールをドライエッ칭により開口し、Cr膜を100nm、またAl系合金膜を400nm、さらにCr膜を100nm連続してスパッタにより積層し、パターニングしてソース/ドレイン電極72を形成する。この後、水素プラズマ中でチャネル部を対象に多結晶体シリコンの水素化処理を行い、特性の向上や安定化をした後に、シリコン窒化膜等により絶縁膜74を形成する。このようなプロセスで作製したn型トランジスタ76およびp型トランジスタ77を組み合わせて、駆動回路に備えられるCMOS回路を構成する。

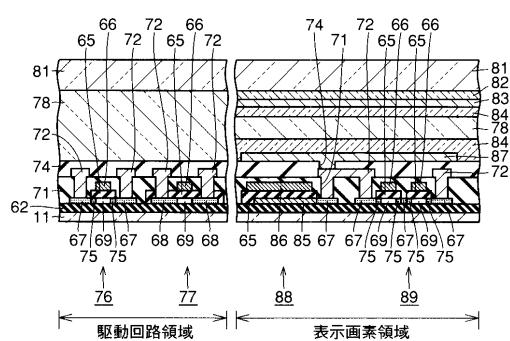

#### 【0042】

上記の駆動回路領域の作製中に、同じガラス基板に作製される表示画素領域についても同じ種類の層は駆動回路領域と同じタイミングで成膜処理がなされる。図11に示すように、表示画素領域に形成される素子部分は、画素用の2個のn型トランジスタからなる画素トランジスタ89、および上部電極86、下部電極85を有する容量88が形成される点を除いて、駆動回路領域の素子部分と変わることはない。表示画素領域における成膜手順は、駆動回路領域の成膜と平行して一体的に進行する。下部ガラス基板側において、絶縁膜74が形成された後、表示画素領域では画素電極87がコンタクトホールを介して表示画像領域のn型トランジスタに接続され、さらにその上に配向膜84が形成される。表示画素領域の上部ガラス基板81には、カラーフィルタ82、対向電極83が積層され、その上に配向膜84が形成される。この後、上記の処理がなされた上部および下部のガラス基板をギャップ間隔を保って貼り合わせ、そのギャップに液晶78を注入することによって液晶表示装置を完成する(図11)。

#### 【0043】

上記の方法で製造された液晶表示装置では、チャネル部の多結晶体シリコンの上層および下層からの有機物や金属による汚染を防止することができる。このため、レーザアニール後に多結晶体シリコン中へ金属不純物が混入することによるしきい値電圧Vthの変動や、下地の不純物の影響によって結晶化時の結晶成長が変動する等に起因するTFTの特性劣化が発生しなくなった。また、各成膜前のパーティクルの再付着も低減することができた。この結果、TFTのしきい値電圧のばらつき、容量絶縁膜の耐圧とも問題なく、製品の歩留り、耐久性、信頼性等のすべての面での向上が可能となった。本実施の形態では、とくに特性面での効果の高い、チャネル部のシリコンの成膜工程およびレーザアニール工程において、実施の形態1における装置にレーザアニール装置を付け加えた装置を導入した。しかし、洗浄後のパーティクル再付着の低減効果があるので、その他のスパッタ成膜等に応用することによってスパッタ成膜における歩留りを向上することが可能となる。

#### 【0044】

(実施の形態4)

10

20

30

40

50

実施の形態 3 に示した液晶表示装置について、実施の形態 2 における装置を用いることにより、薬液槽等で基板を洗浄処理することができる。強酸性の薬液や高温の薬液を温度制御して洗浄することができる。例えば、半導体装置の製造によく使用される R C A 洗浄液、すなわち  $H_2SO_4 + H_2O_2 + H_2O$  からなる洗浄液や、 $NH_3 + H_2O_2 + H_2O$ 、 $HC1 + H_2O_2 + H_2O$ 、 $HF + H_2O$  等の洗浄液を用いることができる。これらの洗浄液は、除去対象物やガラス基板表面へのダメージ具合等に応じて適宜組み合わせて、それぞれの処理を常温～100 度までの適当な温度で行う。これらの洗浄処理によって、汚染物質を除去し、その後、汚染物質を付着させずに成膜およびアニールすることが可能となる。上記の方法によって形成された液晶表示装置では、チャネル部の上層および下層において有機物や金属による汚染がなく、レーザアニール後の多結晶体シリコン中の金属不純物による  $V_{th}$  の変動や結晶化における結晶性への影響がないので、TFT の特性劣化が発生しなくなる。また、各成膜前のパーティクルの再付着も低減することができる。この結果、TFT のしきい値電圧  $V_{th}$  のばらつき、容量絶縁膜の耐圧とも問題なくなり、製品の歩留り、耐久性、信頼性のすべての面での向上を得ることができる。

#### 【0045】

上記において、本発明の実施の形態について説明を行ったが、上記に開示された本発明の実施の形態は、あくまで例示であって、本発明の範囲はこれら発明の実施の形態に限定されない。本発明の範囲は、特許請求の範囲の記載によって示され、さらに特許請求の範囲の記載と均等の意味および範囲内でのすべての変更を含む。

#### 【0046】

##### 【発明の効果】

本発明の液晶表示装置の製造装置を用いることにより、基板を洗浄後、化学的汚染やパーティクル等の再付着を受けずに液晶表示装置を製造することができる。この結果、しきい値電圧の変動等に起因する歩留り低下を生じることがなくなる。また、ロードロック室を中心に洗浄処理室および成膜処理室を配置することにより、本発明の装置は非常にコンパクトになり、液晶表示装置の製造現場の省スペースに寄与することが期待される。

##### 【図面の簡単な説明】

【図 1】 実施の形態 1 における洗浄・成膜処理一体型の液晶表示装置の製造装置の概略構成図である。

【図 2】 図 1 における UV 照射ユニットの模式的断面図である。

【図 3】 図 1 におけるスピン式ウェット洗浄ユニットの模式的断面図である。

【図 4】 実施の形態 1 における L P C V D 装置の概略構成図である。

【図 5】 実施の形態 1 における P C V D 装置の概略構成図である。

【図 6】 実施の形態 2 において洗浄処理室から成膜処理室に基板を搬送する機構を説明する図である。

【図 7】 実施の形態 2 において洗浄処理室から成膜処理室に基板を搬送する、もう一つの機構を説明する図である。

【図 8】 実施の形態 3 において、ガラス基板の上に下地膜を形成し、アモルファスシリコン膜を形成した後、アニールして結晶化し、トランジスタ部をパターニングした段階の断面図である。

【図 9】 ゲート絶縁膜を成膜し、ソース/ドレイン領域に不純物イオンを注入し、ゲート配線を形成した段階の断面図である。

【図 10】 層間絶縁膜、ソース/ゲート電極および保護絶縁膜を形成した段階の断面図である。

【図 11】 液晶表示装置の駆動回路領域および表示画素領域の断面図である。

【図 12】 洗浄処理工程から成膜処理工程に至る、従来の搬送工程の雰囲気を示す図である。

##### 【符号の説明】

1 a, 1 b 洗浄処理室、2 成膜処理室 (CVD 装置室)、3 ロードロック室、4 搬送ロボット、5 カセットロード/アンロード、6 カセット、7 ケミカルフィルタ、

10

20

40

50

8 扉、9 スピン式洗浄ユニット、11 基板（基板）、12 ブラシ洗浄機構、13 物理洗浄および薬液洗浄機構、18 密封カセット、21 UV照射ユニット、22 UVランプ、23 石英ポート、30 LPCVD、31 バルブ、32 MFC、35 P C V D、36 ロードロック室、37 予備室、38 搬送口ポット、39 成膜処理室、43 ローダ、44 洗浄処理室、45 アンローダ、46 ローダ/アンローダ、48 緩密閉通路、51 UV照射ユニット、52 物理洗浄ユニット（ブラシ洗浄、メガソニック洗浄）、53 薬液洗浄ユニット、54 水洗ユニット、55 乾燥ユニット、64 トランジスタ部、65 ゲート絶縁膜、66 ゲート配線、67 n+型不純物領域、68 p型不純物領域、69 チャネル領域、71 層間絶縁膜、72 金属配線、74 保護膜、75 n-型不純物領域、76 n型トランジスタ、77 p型トランジスタ、78 液晶、81 上部ガラス基板、82 カラーフィルタ、83 対向電極、84 配向層、85 容量下部電極、86 容量上部電極、87 画素電極、88 容量、89 画素トランジスタ。

10

【図1】

【図2】

【図3】

【 図 4 】

【 图 5 】

【 四 6 】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

---

フロントページの続き

(74)代理人 100096792

弁理士 森下 八郎

(72)発明者 久保田 健

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

(72)発明者 小松 紀和

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

審査官 田村 嘉章

(56)参考文献 特開平08-088367(JP, A)

国際公開第98/001896(WO, A1)

特開平09-148246(JP, A)

特開平04-210223(JP, A)

特開平07-245332(JP, A)

特開平01-272128(JP, A)

特開平11-214479(JP, A)

特開平07-283092(JP, A)

特開平11-220134(JP, A)

特開平09-018011(JP, A)

実開平05-022552(JP, U)

特開2000-068193(JP, A)

特開2000-260684(JP, A)

特開2000-357798(JP, A)

(58)調査した分野(Int.Cl., DB名)

G02F 1/13

H01L 21/67-21/687