(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3934236号

(P3934236)

(45) 発行日 平成19年6月20日(2007.6.20)

(24) 登録日 平成19年3月30日(2007.3.30)

(51) Int.C1.

F 1

G02F 1/1368 (2006.01)

G02F 1/1368

H01L 21/768 (2006.01)

H01L 21/90

A

H01L 29/786 (2006.01)

H01L 29/78 612C

請求項の数 19 (全 16 頁)

(21) 出願番号

特願平10-18050

(22) 出願日

平成10年1月14日(1998.1.14)

(65) 公開番号

特開平11-202368

(43) 公開日

平成11年7月30日(1999.7.30)

審査請求日

平成16年11月22日(2004.11.22)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 仲沢 美佐子

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 福島 浩司

最終頁に続く

(54) 【発明の名称】半導体装置およびその作製方法

## (57) 【特許請求の範囲】

## 【請求項1】

薄膜トランジスタと、

前記薄膜トランジスタ上に形成され、前記薄膜トランジスタのドレイン電極の一部を露呈する開孔部を有する層間絶縁膜と、

前記開孔部を埋め込むように形成された溶液塗布系導電膜と、

前記層間絶縁膜及び前記溶液塗布系導電膜上に接して形成された、アルミニウムを主成分とする材料、タンタル、タングステン又はモリブデンからなる画素電極とを有し、

前記層間絶縁膜の上面と前記溶液塗布系導電膜の上面は同一平面であり、

前記溶液塗布系導電膜は、カーボン系材料または顔料を含むITO膜であることを特徴とする半導体装置。 10

## 【請求項2】

薄膜トランジスタと、

前記薄膜トランジスタ上に形成された第1の層間絶縁膜と、

前記第1の層間絶縁膜上に形成されたドレイン電極と、

前記ドレイン電極を覆うように形成された窒化珪素膜と、

前記窒化珪素膜上に形成され、前記窒化珪素膜を誘電体として前記ドレイン電極との間で補助容量を形成する金属膜と、

前記金属膜上に形成された第2の層間絶縁膜と、

前記第2の層間絶縁膜上に形成された第3の層間絶縁膜と、

前記窒化珪素膜、前記第2の層間絶縁膜及び前記第3の層間絶縁膜に形成され、前記ドレイン電極の一部を露呈する開孔部と、

前記開孔部を埋め込むように形成された溶液塗布系導電膜と、

前記第3の層間絶縁膜及び前記溶液塗布系導電膜上に接して形成された、アルミニウムを主成分とする材料、タンタル、タングステン又はモリブデンからなる画素電極とを有し、

前記第3の層間絶縁膜の上面と前記溶液塗布系導電膜の上面は同一平面であり、

前記溶液塗布系導電膜は、カーボン系材料または顔料を含むITO膜であることを特徴とする半導体装置。

**【請求項3】**

10

薄膜トランジスタと、

前記薄膜トランジスタ上に形成され、前記薄膜トランジスタのドレイン電極の一部を露呈する開孔部を有する層間絶縁膜と、

前記開孔部を埋め込むとともに前記層間絶縁膜上に形成された溶液塗布系導電膜と、

前記溶液塗布系導電膜上に接して形成された、アルミニウムを主成分とする材料、タンタル、タングステン又はモリブデンからなる画素電極とを有し、

前記溶液塗布系導電膜は前記画素電極と同一形状であることを特徴とする半導体装置。

**【請求項4】**

薄膜トランジスタと、

前記薄膜トランジスタ上に形成された第1の層間絶縁膜と、

20

前記第1の層間絶縁膜上に形成されたドレイン電極と、

前記ドレイン電極を覆うように形成された窒化珪素膜と、

前記窒化珪素膜上に形成され、前記窒化珪素膜を誘電体として前記ドレイン電極との間で補助容量を形成する金属膜と、

前記金属膜上に形成された第2の層間絶縁膜と、

前記第2の層間絶縁膜上に形成された第3の層間絶縁膜と、

前記窒化珪素膜、前記第2の層間絶縁膜及び前記第3の層間絶縁膜に形成され、前記ドレイン電極の一部を露呈する開孔部と、

前記開孔部を埋め込むとともに前記第3の層間絶縁膜上に形成された溶液塗布系導電膜と、

30

前記溶液塗布系導電膜上に接して形成された、アルミニウムを主成分とする材料、タンタル、タングステン又はモリブデンからなる画素電極とを有し、

前記溶液塗布系導電膜は前記画素電極と同一形状であることを特徴とする半導体装置。

**【請求項5】**

請求項1において、前記層間絶縁膜は有機樹脂膜の単層又は積層であることを特徴とする半導体装置。

**【請求項6】**

請求項3または請求項4において、前記溶液塗布系導電膜は酸化物導電層でなることを特徴とする半導体装置。

**【請求項7】**

40

請求項3または請求項4において、前記溶液塗布系導電膜はITO膜であることを特徴とする半導体装置。

**【請求項8】**

請求項7において、前記ITO膜はカーボン系材料または顔料を含むことを特徴とする半導体装置。

**【請求項9】**

請求項1乃至請求項8のいずれか一項において、前記開孔部の断面形状はテーパー状であることを特徴とする半導体装置。

**【請求項10】**

請求項1乃至請求項9のいずれか一項において、前記半導体装置はアクティブマトリク

50

ス型液晶表示装置であることを特徴とする半導体装置。

【請求項 1 1】

請求項 1 乃至請求項 9 のいずれか一項において、前記半導体装置は E L 表示装置であることを特徴とする半導体装置。

【請求項 1 2】

請求項 1 乃至請求項 9 のいずれか一項において、前記半導体装置は、ビデオカメラ、スチルカメラ、リア型プロジェクター、フロント型プロジェクター、カーナビゲーション、パソコン用コンピュータまたは携帯情報端末であることを特徴とする半導体装置。

【請求項 1 3】

絶縁層、半導体層または導電層でなる下地膜上に第 1 の導電層を形成し、

前記第 1 の導電層を覆うように第 1 の絶縁層を形成し、

前記第 1 の絶縁層に前記第 1 の導電層の一部を露出する開孔部を形成し、

前記第 1 の絶縁層と前記開孔部を覆うようにスピンドルコート法により、カーボン系材料または顔料を含むITO膜を形成し、

前記 ITO 膜をエッチングすることにより、前記開孔部のみを前記 ITO 膜で充填し、

前記 ITO 膜及び前記第 1 の絶縁層上に接して第 2 の導電層を形成することを特徴とする半導体装置の作製方法。

【請求項 1 4】

薄膜トランジスタ上に第 1 の層間絶縁膜を形成し、

前記第 1 の層間絶縁膜上にドレイン電極を形成し、

前記ドレイン電極上に第 2 の層間絶縁膜を形成し、

前記第 2 の層間絶縁膜に、前記ドレイン電極の一部を露出する開孔部を形成し、

前記第 2 の層間絶縁膜と前記開孔部を覆うようにスピンドルコート法により、カーボン系材料または顔料を含むITO膜を形成し、

前記 ITO 膜をエッチングすることにより、前記開孔部のみを前記 ITO 膜で充填し、

前記 ITO 膜及び前記第 2 の層間絶縁膜上に接して画素電極を形成することを特徴とする半導体装置の作製方法。

【請求項 1 5】

薄膜トランジスタ上に第 1 の層間絶縁膜を形成し、

前記第 1 の層間絶縁膜上にドレイン電極を形成し、

前記ドレイン電極上に第 2 の層間絶縁膜を形成し、

前記第 2 の層間絶縁膜に、前記ドレイン電極の一部を露出する開孔部を形成し、

前記第 2 の層間絶縁膜と前記開孔部を覆うようにスピンドルコート法により、カーボン系材料または顔料を含むITO膜を形成し、

前記 ITO 膜を研磨することにより、前記開孔部のみを前記 ITO 膜で充填し、

前記 ITO 膜及び前記第 2 の層間絶縁膜上に接して画素電極を形成することを特徴とする半導体装置の作製方法。

【請求項 1 6】

薄膜トランジスタ上に第 1 の層間絶縁膜を形成し、

前記第 1 の層間絶縁膜上にドレイン電極を形成し、

前記ドレイン電極上に第 2 の層間絶縁膜を形成し、

前記第 2 の層間絶縁膜に前記ドレイン電極の一部を露出する開孔部を形成し、

前記第 2 の層間絶縁膜と前記開孔部を覆うようにスピンドルコート法により、カーボン系材料または顔料を含むITO膜を形成し、

前記 ITO 膜上に接して画素電極を形成し、

前記画素電極をマスクとして前記 ITO 膜をエッチングすることを特徴とする半導体装置の作製方法。

【請求項 1 7】

請求項 1 乃至請求項 9 のいずれか一項において、前記エッチングは、前記第 1 の絶縁層の上面と前記 ITO 膜の上面が同一平面になるよう行われることを特徴とする半導体装置の作製方法。

10

20

30

40

50

**【請求項 1 8】**

請求項1 4において、前記エッティングは、前記第2の層間絶縁膜の上面と前記ITO膜の上面が同一平面になるよう行われることを特徴とする半導体装置の作製方法。

**【請求項 1 9】**

請求項1 5において、前記研磨は、前記第2の層間絶縁膜の上面と前記ITO膜の上面が同一平面になるよう行われることを特徴とする半導体装置の作製方法。

**【発明の詳細な説明】****【0 0 0 1】****【発明が属する技術分野】**

本願発明は薄膜を用いた半導体装置において、導電性薄膜相互の電気的接続をとるための接続配線の構成に関する。 10

**【0 0 0 2】**

特に、アクティブマトリクス型液晶表示装置（以下、AMLCDと呼ぶ）の画素領域において、スイッチング素子と画素電極とを電気的に接続するための接続配線の構成に関する。

**【0 0 0 3】**

なお、本明細書中において、半導体装置とは半導体特性を利用して機能する全ての装置の総称であり、AMLCDに代表される電気光学装置やマイクロプロセッサ等の半導体回路も半導体装置の範疇に含む。さらに、その様な電気光学装置や半導体回路を構造に含む電子機器も半導体装置の範疇に含むものとする。 20

**【0 0 0 4】****【従来の技術】**

近年、安価なガラス基板上にTFTを作製する技術が急速に発達してきている。その理由は、AMLCD（Active Matrix Liquid Crystal Display）の需要が高まったことにある。

**【0 0 0 5】**

AMLCDはマトリクス状に配置された数十～数百万個もの各画素のそれぞれにスイッチング素子として薄膜トランジスタ（TFT）を配置し、各画素電極に出入りする電荷をTFTのスイッチング機能により制御するものである。

**【0 0 0 6】**

各画素電極と対向電極との間には液晶が挟み込まれ、一種のコンデンサを形成している。従って、TFTによりこのコンデンサへの電荷の出入りを制御することで液晶の電気光学特性を変化させ、液晶パネルを透過する光を制御して画像表示を行うことができる。 30

**【0 0 0 7】**

この様な液晶を用いた表示装置に特有の現象としてディスクリネーションと呼ばれる現象がある。液晶は画素電極と対向電極との間にある規則性をもった配向性をもって配列しているが、電極表面の凹凸に起因するラビング不良によって配向性が乱れる場合がある。この場合、その部分では正常な光シャッタとしての機能が失われ、光漏れなどの表示不良を起こす。

**【0 0 0 8】**

これまでディスクリネーションを防止するためにTFTを平坦化膜で覆う構成などの工夫が施されたが、現状では必ずしも抜本的な解決策とはなっていない。なぜならば、如何に平坦化膜を利用して最終的に形成される画素電極のコンタクト部の段差は平坦化が不可能だからである。 40

**【0 0 0 9】****【発明が解決しようとする課題】**

本願発明は上記問題点を鑑みてなされたものであり、完全に平坦な導電層を形成するためのコンタクト部の構成に関する技術を提供する。

**【0 0 1 0】**

特にAMLCDの画素電極を完全に平坦化し、コンタクト部の段差に起因するディスクリ 50

ネーションの発生を防止することを目的とする。そして、必要なブラックマスクの面積を低減することで有効画素面積を拡大し、高精細かつ高コントラストのAMLCDを実現する。

【0011】

【課題を解決するための手段】

本明細書で開示する発明の構成は、

異なる層に形成された二層の導電層と、当該二層の導電層に挟まれた絶縁層とを有する半導体装置であって、

前記二層の導電層は前記絶縁層に設けられた開孔部を埋め込む様に形成された酸化物導電層を介して互いに電気的に接続された構造を有していることを特徴とする。 10

【0012】

また、他の発明の構成は、

異なる層に形成された二層の導電層と、当該二層の導電層に挟まれた絶縁層とを有する半導体装置であって、

前記二層の導電層は前記絶縁層に設けられた開孔部を埋め込む様に形成された酸化物導電層を介して互いに電気的に接続された構造を有し、

前記開孔部の形状と当該開孔部に埋め込まれた前記酸化物導電層の形状とが概略一致していることを特徴とする。 20

【0013】

また、他の発明の構成は、

異なる層に形成された二層の導電層と、当該二層の導電層に挟まれた絶縁層とを有する半導体装置であって、

前記二層の導電層は前記絶縁層に設けられた開孔部を埋め込む様に形成された酸化物導電層を介して互いに電気的に接続された構造を有し、

前記酸化物導電層によって形成された平坦面上に前記二層の導電層の一方が形成されていることを特徴とする。 30

【0014】

また、他の発明の構成は、

第1の導電層を形成する工程と、

前記第1の導電層上に絶縁層を形成する工程と、

前記絶縁層に開孔部を形成し、当該開孔部の底部において前記第1の導電層を露呈させる工程と、 30

前記絶縁層及び開孔部を覆って酸化物導電層をスピンドルコート法により形成する工程と、

前記酸化物導電層をエッティング又は研磨し、前記開孔部のみが当該酸化物導電層で充填された状態とする工程と、

前記絶縁層及び前記酸化物導電層上に第2の導電層を形成する工程と、

を含むことを特徴とする。 40

【0015】

また、他の発明の構成は、

第1の導電層を形成する工程と、

前記第1の導電層上に絶縁層を形成する工程と、

前記絶縁層に開孔部を形成し、当該開孔部の底部において前記第1の導電層を露呈させる工程と、 40

前記絶縁層及び開孔部を覆って酸化物導電層をスピンドルコート法により形成する工程と、

前記酸化物導電層上に第2の導電層を形成する工程と、

前記第2の導電層を所望の形状にパターニングする工程と、

前記第2の導電層をマスクとして自己整合的に前記酸化物導電層をエッティングする工程と

、

を含むことを特徴とする。 50

【0016】

本願発明ではコンタクトホール内を導電層で埋め込むことでその上に形成される第2の導電層（特に画素マトリクス回路における画素電極）の平坦性を向上させることを目的とする。

【0017】

本発明者は微細なコンタクトホールを埋め込むために好適な材料として、溶液塗布系導電膜を選択し、その代表的な材料として溶液塗布系のITO（インジウム・ティン・オキサイド）膜に注目した。

【0018】

この様なITO膜としては、例えば旭電化工業株式会社製アデカITO塗布液を用いた薄膜などが挙げられる。このITO塗布液はキシレン溶媒中にインジウム・スズ有機化合物を溶解させたものであるが、溶媒・溶質を変えればその他の酸化物導電層を形成することも可能である。10

【0019】

これらの酸化物導電層は、凹凸部に集中的に形成されるので効率良く凹凸を埋め込み、平坦化するには好適な材料である。勿論、塗布回数は1度に限らず数度の重ね塗りを行って平坦性を高めると効果的である。

【0020】

【発明の実施の形態】

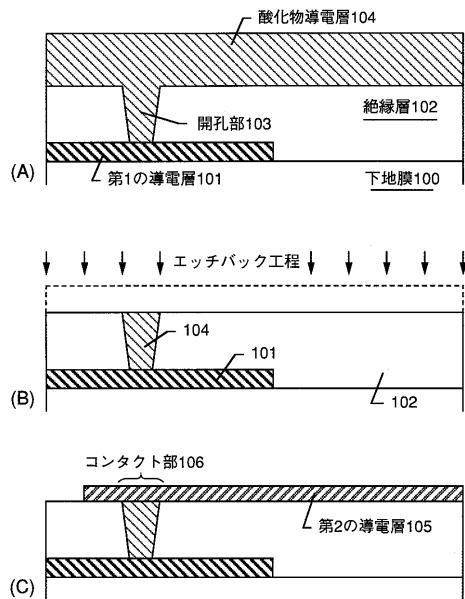

本願発明の実施形態について、図1を用いて説明する。図1(A)において、100は下地膜であり、絶縁層、半導体層又は導電層の如何なる場合もありうる。その上には第1の導電層101がパターン形成されている。20

【0021】

第1の導電層101は絶縁層（層間絶縁層）102によって覆われる。絶縁層102としては、酸化珪素、窒化珪素、酸化窒化珪素等の珪素を含む絶縁膜や有機樹脂膜を単層又は積層で用いる。

【0022】

絶縁層102を形成したら、エッチングにより開孔部（コンタクトホール）103を形成する。エッチングの方法はウェットエッチング法でもドライエッチング法でも良い。また、開孔部103の断面形状をテーパー状にすることで、次に成膜する薄膜のカバレッジを改善することも有効である。30

【0023】

こうして開孔部103を形成したら、酸化物導電層104を形成する。酸化物導電層104としては溶液塗布系のITO膜を用いる。この様な膜はキシレン等の有機溶媒中にインジウム・スズ有機化合物を溶かした溶液を絶縁層102上へ塗布し、スピンドライにより余分な溶液を飛ばして薄膜を形成する。この様な技術はスピントロート法とも呼ばれる。

【0024】

スピントロート法により酸化物導電層104を形成したら、150~170の乾燥工程と300以上の焼成工程を行い、その後必要に応じてアニール工程を施して膜質を向上させる。勿論、膜質を向上させるためのキュア工程はこの条件に限定されず、実施者が実験によって最適な条件を求めて良い。40

【0025】

この様な溶液塗布系の薄膜の利点は、成膜が非常に簡易であること、被覆性が高いこと、である。即ち、成膜段階では溶液であるため、微細な凹凸の被覆形状が非常に良好であり、コンタクトホール等の微細な開孔部の埋め込みには非常に適している。本願発明は、その様な溶液塗布系材料の被覆性の良さに着目した技術である。

【0026】

また、場合によっては溶液塗布系のITO膜の基となる溶液にカーボン系材料や顔料を分散させて黒色に着色することも可能である。こうすることでコンタクトホール内の遮光性を高めることができる。

【0027】

10

20

30

40

50

酸化物導電層 104 を形成したら、図 1 (A) の状態が得られる。この状態が得られたら、次に、ドライエッティング法により酸化物導電層 104 をエッチバック処理して開孔部 103 のみを充填する様な状態とする。(図 1 (B))

【0028】

なお、酸化物導電層として ITO 膜を用いる場合、このエッチバック工程におけるエッティング方法はウェット処理、ドライ処理のどちらの方法を用いることもできる。

【0029】

ウェット処理で行う場合には ITO 専用のエッチャントが市販されているのでそちらを用いれば良い。また、ドライ処理を行う場合にはエッティングガスとして HBr (臭化水素)、HI (ヨウ化水素)、CH<sub>4</sub> (メタン) を用いることができる。特に、HBr は加工性と汎用性の点で好ましい。10

【0030】

こうして図 1 (B) の状態を得たら、次に第 2 の導電層 105 をパターン形成する。この様にして、絶縁層 102 で絶縁分離された異なる二層の導電層 (第 1 の導電層 101 と第 2 の導電層 105) とが、酸化物導電層 104 を介して電気的に接続された状態を得る。この時、第 2 の導電層 105 はコンタクト部 106 においても完全に平坦性を維持することができる。

【0031】

以上の構成でなる本願発明について、以下に記載する実施例でもって詳細な説明を行なうこととする。20

【0032】

【実施例】

〔実施例 1〕

本実施例では、反射型モードで駆動するアクティブマトリクス型液晶表示装置 (AMLC)

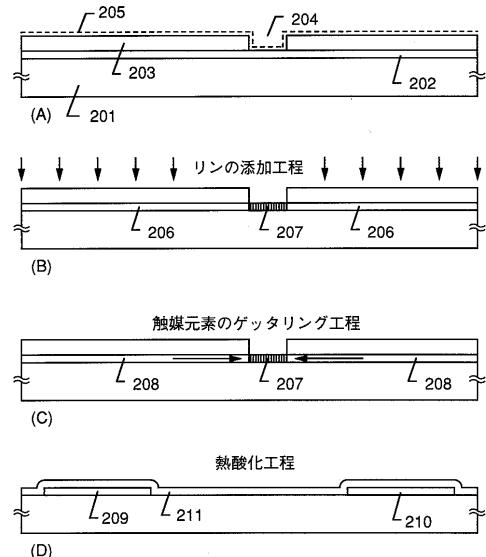

D の画素マトリクス回路を構成する単位画素 (単位絵素) の作製方法について図 2 を用いて説明する。

【0033】

まず、絶縁表面を有する基板として石英基板 201 を用意する。本実施例では後に 900 ~ 1100 の熱処理が行われるので耐熱性の高い材料を用いる必要がある。他にも下地膜を設けた結晶化ガラス (ガラスセラミクス) や熱酸化膜を設けたシリコン基板等を用いることもできる。30

【0034】

その上に 65nm 厚の非晶質珪素膜 202 を形成し、この非晶質珪素膜 202 を特開平 8 - 7

8329 号公報記載の技術を用いて結晶化する。同公報記載の技術は結晶化を助長する触媒元素を用いて選択的な結晶化を行う技術である。

【0035】

ここでは非晶質珪素膜 202 に対して選択的に触媒元素 (本実施例ではニッケル) を添加するためマスク絶縁膜 203 を形成する。また、マスク絶縁膜 203 には開口部 204 が設けられている。

【0036】

そして、重量換算で 10ppm のニッケルを含有したニッケル酢酸塩溶液をスピンドル法により塗布し、触媒元素含有層 205 を形成する。40

【0037】

こうして図 2 (A) の状態が得られたら、450 1 時間の水素出し工程の後、570 14 時間の加熱処理を窒素雰囲気中で施し、横成長領域 206 を得る。こうして結晶化工程が終了したら、マスク絶縁膜 203 をそのままマスクとしてリンの添加工程を行う。この工程によりリン添加領域 207 が形成される。

【0038】

こうして図 2 (B) の状態が得られたら、次に 600 12 時間の加熱処理を行い、横成長領域 206 に残留していたニッケルをリン添加領域 207 にゲッタリングさせる。こうして50

ニッケル濃度が  $5 \times 10^{17}$  atoms/cm<sup>3</sup> 以下にまで低減された領域（被ゲッタリング領域と呼ぶ）208が得られる。（図2（C））

#### 【0039】

次に、パターニングにより被ゲッタリング領域208のみで構成される活性層209、210を形成する。そして、120nm厚のゲイト絶縁膜211を形成する。ゲイト絶縁膜211としては、酸化珪素膜、窒化珪素膜、酸化窒化珪素膜或いはそれらの積層膜で構成される。

#### 【0040】

こうしてゲイト絶縁膜211を形成したら、酸素雰囲気中において950℃30分の加熱処理を行い、活性層／ゲイト絶縁膜界面に熱酸化膜を形成する。こうすることで界面特性を大幅に向上させることができる。

10

#### 【0041】

なお、熱酸化工程では活性層209、210が酸化されて薄膜化される。本実施例では最終的な活性層膜厚が50nmとなる様に調節する。即ち、出発膜（非晶質珪素膜）が65nmであったので、15nmの酸化が行われ、30nmの熱酸化膜が形成されることになる（ゲイト絶縁膜211はトータルで150nm厚となる）。

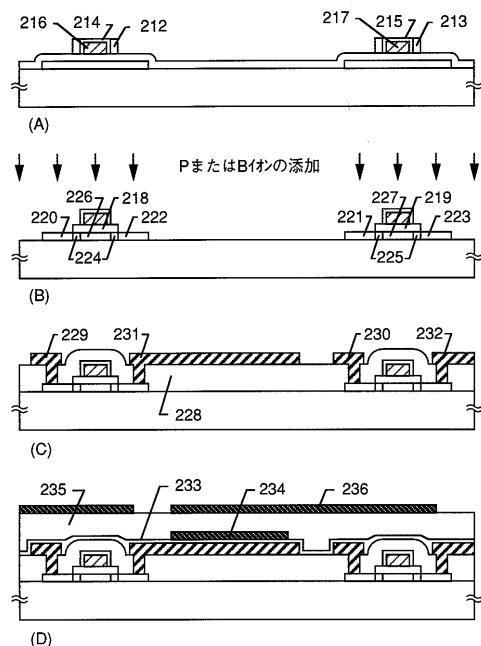

#### 【0042】

次に、0.2wt%のスカンジウムを含有させたアルミニウム膜（図示せず）を成膜し、パターニングによりゲイト電極の原型となる島状パターンを形成する。島状パターンを形成したら、特開平7-135318号公報に記載された技術を利用する。なお、詳細は同公報を参考にすると良い。

20

#### 【0043】

まず、上記島状パターン上にパターニングで使用したレジストマスクを残したまま、3%のシュウ酸水溶液中で陽極酸化を行う。この時、白金電極を陰極として2～3mVの化成電流を流し、到達電圧は8Vとする。こうして、多孔性陽極酸化膜212、213が形成される。

#### 【0044】

その後、レジストマスクを除去した後に3%の酒石酸のエチレングリコール溶液をアンモニア水で中和した溶液中で陽極酸化を行う。この時、化成電流は5～6mVとし、到達電圧は100Vとすれば良い。こうして、緻密な無孔性陽極酸化膜214、215が形成される。

30

#### 【0045】

そして、上記工程によってゲイト電極216、217が確定する。なお、画素マトリクス回路ではゲイト電極の形成と同時に1ライン毎に各ゲイト電極を接続するゲイト線も形成されている。（図3（A））

#### 【0046】

次に、ゲイト電極216、217をマスクとしてゲイト絶縁膜211をエッチングする。エッチングはCF<sub>4</sub>ガスを用いたドライエッチング法により行う。これにより218、219で示される様な形状のゲイト絶縁膜が形成される。

#### 【0047】

そして、この状態で一導電性を付与する不純物イオンをイオン注入法またはプラズマドーピング法により添加する。この場合、画素マトリクス回路をN型TFTで構成するならばP（リン）イオンを、P型TFTで構成するならばB（ボロン）イオンを添加すれば良い。

40

#### 【0048】

なお、上記不純物イオンの添加工程は2度に分けて行う。1度目は80keV程度の高加速電圧で行い、ゲイト絶縁膜218、219の端部（突出部）の下に不純物イオンのピークがくる様に調節する。そして、2度目は5keV程度の低加速電圧で行い、ゲイト絶縁膜218、219の端部（突出部）の下には不純物イオンが添加されない様に調節する。

#### 【0049】

50

こうしてTFTのソース領域220、221、ドレイン領域222、223、低濃度不純物領域(LDD領域とも呼ばれる)224、225、チャネル形成領域226、227が形成される。(図3(B))

#### 【0050】

この時、ソース／ドレイン領域は300～500 / のシート抵抗が得られる程度に不純物イオンを添加することが好ましい。また、低濃度不純物領域はTFTの性能に合わせて最適化を行う必要がある。また、不純物イオンの添加工程が終了したら熱処理を行い、不純物イオンの活性化を行う。

#### 【0051】

次に、第1の層間絶縁膜228として酸化珪素膜を400nmの厚さに形成し、その上にソース電極229、230、ドレイン電極231、232を形成する。なお、本実施例ではドレイン電極231、232を画素内に広げて形成する。

10

#### 【0052】

これは、ドレイン電極を補助容量の下部電極として用いるため、可能な限り大きい容量を確保するための工夫である。本実施例は反射型の例であるため、後に画素電極が配置される領域の下も開口率を気にせず自由に使える。

#### 【0053】

こうして図3(C)の状態が得られたら、ソース／ドレイン電極を覆って50nm厚の窒化珪素膜233を形成する。そして、その上に第1の金属膜(本実施例ではチタン)を形成する。本実施例では窒化珪素膜233を誘電体としてドレイン電極231と第1の金属膜234との間で補助容量を形成している。

20

#### 【0054】

その次に第2の層間絶縁膜235として1μm厚のポリイミド膜を形成する。勿論、ポリイミド以外にもアクリル等の有機性樹脂膜を用いても良い。そして、第2の層間絶縁膜235の上に第2の金属膜236を形成する。

#### 【0055】

第2の金属膜236はブラックマスクとしての機能も持っているが、主に電界遮蔽膜として役割を果たす。即ち、ソース／ドレイン配線から生じる電界が後に形成する画素電極に影響するのを防ぐ効果を持つ。

#### 【0056】

30

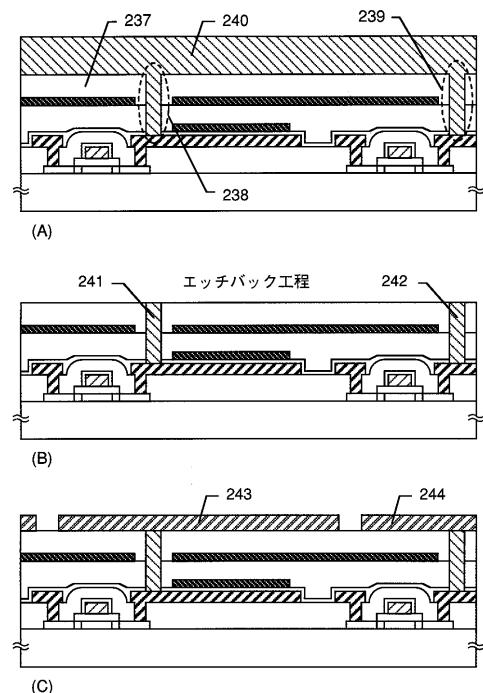

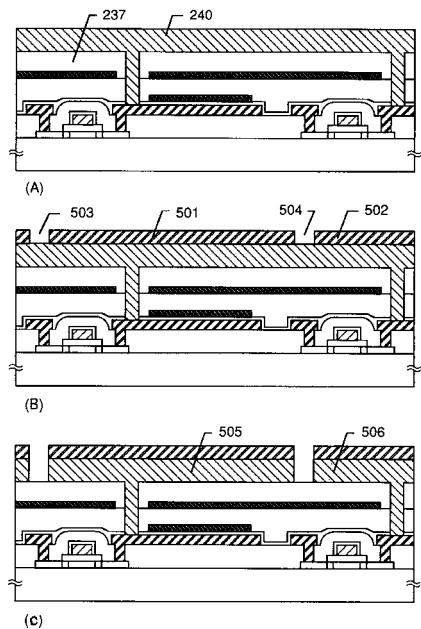

こうして図3(D)の状態が得られたら、第3の層間絶縁膜237として再び1μm厚のポリイミド膜を設け、それに対して開孔部238、239を形成する。そして、第3の層間絶縁膜237及び開孔部238、239を被覆する様にして酸化物導電層240を形成する。(図4(A))

#### 【0057】

本実施例では酸化物導電層240として粘度が10～30cPsの塗布系ITO膜(旭電化工業株式会社製)を用いる。溶液をスピンドル法により塗布したら窒素中で150～200 5～10分の乾燥工程、300～400 1～2時間の焼成工程を行い、膜質を向上させる。ただしこの膜質向上のための処理は本実施例に限定されるものではない。

#### 【0058】

40

また、上記焼成工程の後でさらに高温のアニールを行うことも有効である。ただし、電極材料等の耐熱性を考慮する必要があり、全体を高温アニールすることを避けるのであれば、ランプアニール等の手段を用いることが好ましい。

#### 【0059】

この様な膜質向上のための処理を施すことで酸化物導電層240の抵抗値は1k / 以下になる。ミクロンオーダー以下の電気的な接続をとるためならば、この程度の抵抗値で十分と考えられる。

#### 【0060】

また、形成される酸化物導電層240の膜厚は溶液の粘度、スピンドル時の回転数や回転時間等で制御することができる。コンタクトホールの径(開口面積)に応じて膜厚を変

50

化させる必要があるが、100～500nm（代表的には150～300nm）の範囲で調節すれば、コンタクトホール内を十分に埋め込むことが可能である。

#### 【0061】

次に、HBr、HI、CH<sub>4</sub>のいずれかのエッティングガスをAr（アルゴン）で希釈してドライエッティング法によるエッチバック工程を行う。本実施例では、HBrを用いる。こうして開孔部238、239が酸化物導電層241、242で充填された状態を実現する。（図4（B））

#### 【0062】

そして、酸化物導電層241、242によって完全に平坦化された第3の層間絶縁膜237上にアルミニウムを主成分とする材料でなる画素電極243、244を形成する。この時、コンタクトホール（開孔部）の内部は酸化物導電層241、242で充填されているので、段差を生じることなくドレイン電極との電気的な接続が実現される。

#### 【0063】

この後は、画素電極243、244上に配向膜（図示せず）を形成すれば液晶表示装置の一方の基板であるアクティブマトリクス基板が完成する。その後は公知の手段によって対向基板を用意し、セル組み工程を施してアクティブマトリクス型液晶表示装置が完成する。

#### 【0064】

##### 〔実施例2〕

実施例1では、酸化物導電層に対してエッチバック処理を行って開孔部の充填を行っているが、エッチバック処理の代わりに研磨処理を行うことも可能である。代表的にはCMP（ケミカルメカニカルポリッシング）と呼ばれる技術を採用することもできる。

#### 【0065】

この技術を用いる場合には発塵に注意する必要があるが、この技術を用いれば第3の層間絶縁膜と酸化物導電層が異なる材料で構成されている様な場合においても優れた平坦性を確保することができる。

#### 【0066】

##### 〔実施例3〕

実施例1では第2及び第3の層間絶縁膜としてポリイミド膜を用いていたが、酸化珪素膜や酸化窒化珪素膜を用いることも有効である。

#### 【0067】

ポリイミド等の有機樹脂膜は耐熱性が低いので、酸化物導電層の焼成温度やその後のアニール温度に制限がある。しかしながら、酸化珪素膜等で層間絶縁膜を形成しておけば、さらに高い温度でのアニールが可能となり、膜質の良い膜を得ることができる。

#### 【0068】

勿論、実施例1ではゲート電極やソース／ドレイン電極としてアルミニウムを主成分とする材料を用いているので、その耐熱性も考慮する必要がある。しかし、電極材料として耐熱性の高い材料を用いれば、500℃を超える様な高い温度でアニール処理も可能となる。

#### 【0069】

なお、実施例1において電極材料となりうる耐熱性の高い材料としては、タンタル、タンゲステン、モリブデン又は導電性を持たせたシリコン膜等を挙げることができる。

#### 【0070】

また、本実施例の構成と実施例2に示した構成とを組み合わせても良い。

#### 【0071】

##### 〔実施例4〕

本実施例では、実施例1とは異なる構成で反射型のAMLCDを作製する技術について図5を用いて説明する。

#### 【0072】

まず、実施例1の作製工程に従って図5（A）の状態を得る。図5（A）において、237は第3の層間絶縁膜、240は酸化物導電層である。

**【 0 0 7 3 】**

次に、酸化物導電層 240 上にアルミニウムを主成分とする材料でなる画素電極 501、502 を形成する。この時、画素電極 501、502 は開孔部 503、504 によって物理的に絶縁されている。（図 5（B））

**【 0 0 7 4 】**

次に、画素電極 501、502 をマスクとして酸化物導電層 240 をエッティングし、画素電極と同一形状にパターニングされた酸化物導電層 505、506 を形成する。これにより酸化物導電層 505、506 も物理的に絶縁されるので、画素電極の一部として機能することになる。

**【 0 0 7 5 】**

なお、本実施例の構成とすると、画素電極 501、502 を絶縁分離する開孔部（503、504 に相当）は  $1 \mu m$  以上の深さとなるが、この部分はソース電極（ソース配線）の上方であるので遮光され、問題とはならない。さらに、この部分はディスクリネーションを集中させるので、画素内の必要な領域にディスクリネーションが広がるのを防ぐ効果（ピン止め効果）も期待できる。

**【 0 0 7 6 】**

なお、本実施例は実施例 3 と組み合わせることも可能である。

**【 0 0 7 7 】****〔 実施例 5 〕**

実施例 1～4 ではトップゲイト構造（ここではプレーナ型）の TFT を例にとって説明したが、本願発明はボトムゲイト構造（代表的には逆スタガ型）の TFT に対しても容易に適用することができる。

**【 0 0 7 8 】**

また、本願発明は TFT に限らず、単結晶シリコンウェハ上に形成された MOSFET の配線接続にも活用することが可能である。

**【 0 0 7 9 】**

以上の様に、本願発明は異なる層に形成された配線同士を接続する必要性の生じる構造であれば、如何なる構造のデバイス素子に対しても適用することが可能である。

**【 0 0 8 0 】****〔 実施例 6 〕**

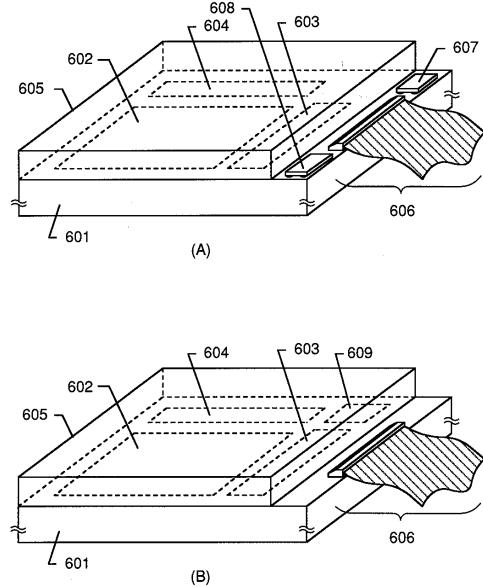

本実施例では実施例 1～5 に示した構成のアクティブマトリクス基板（素子形成側基板）を用いて AMLCD を構成した場合の例について説明する。ここで本実施例の AMLCD の外観を図 6 に示す。

**【 0 0 8 1 】**

図 6（A）において、601 はアクティブマトリクス基板であり、画素マトリクス回路 602、ソース側駆動回路 603、ゲート側駆動回路 604 が形成されている。駆動回路は N 型 TFT と P 型 TFT とを相補的に組み合わせた CMOS 回路で構成することが好ましい。また、605 は対向基板である。

**【 0 0 8 2 】**

図 6（A）に示す AMLCD はアクティブマトリクス基板 601 と対向基板 605 とが端面を揃えて貼り合わされている。ただし、ある一部だけは対向基板 605 を取り除き、露出したアクティブマトリクス基板に対して FPC（フレキシブル・プリント・サーキット）606 を接続してある。この FPC 606 によって外部信号を回路内部へと伝達する。

**【 0 0 8 3 】**

また、FPC 606 を取り付ける面を利用して IC チップ 607、608 が取り付けられている。これらの IC チップはビデオ信号の処理回路、タイミングパルス発生回路、補正回路、メモリ回路、演算回路など、様々な回路をシリコン基板上に形成して構成される。図 6（A）では 2 個取り付けられているが、1 個でも良いし、さらに複数個であっても良い。

**【 0 0 8 4 】**

10

20

30

40

50

また、図6(B)の様な構成もとりうる。図6(B)において図6(A)と同一の部分は同じ符号を付してある。ここでは図6(A)でI Cチップが行っていた信号処理を、同一基板上にTFTでもって形成されたロジック回路609によって行う例を示している。この場合、ロジック回路609も駆動回路603、604と同様にCMOS回路を基本として構成される。

【0085】

また、本実施例のAMLCDはブラックマスクをアクティブマトリクス基板に設ける構成(BM on TFT)を採用するが、それに加えて対向側にブラックマスクを設ける構成とすることも可能である。

【0086】

また、カラーフィルターを用いてカラー表示を行っても良いし、ECB(電界制御複屈折)モード、GH(ゲストホスト)モードなどで液晶を駆動し、カラーフィルターを用いない構成としても良い。

【0087】

また、特開昭8-15686号公報に記載された技術の様に、マイクロレンズアレイを用いる構成にしても良い。

【0088】

〔実施例7〕

本願発明の構成は、AMLCD以外にも他の様々な電気光学装置や半導体回路に適用することができる。

20

【0089】

AMLCD以外の電気光学装置としてはEL(エレクトロルミネッセンス)表示装置やイメージセンサ等を挙げることができる。

【0090】

また、半導体回路としては、I Cチップで構成されるマイクロプロセッサの様な演算処理回路、携帯機器の入出力信号を扱う高周波モジュール(MMICなど)が挙げられる。

【0091】

この様に本願発明は多層配線技術を必要とする全ての半導体装置に対して適用することができる。

【0092】

30

〔実施例8〕

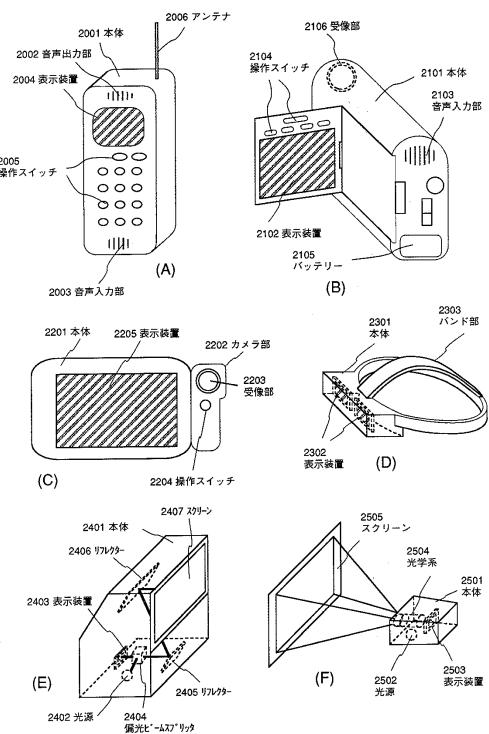

実施例6に示したAMLCDは、様々な電子機器のディスプレイとして利用される。なお、本実施例に挙げる電子機器とは、アクティブマトリクス型液晶表示装置を搭載した製品と定義する。

【0093】

その様な電子機器としては、ビデオカメラ、スチルカメラ、プロジェクター、プロジェクションTV、ヘッドマウントディスプレイ、カーナビゲーション、パーソナルコンピュータ(ノート型を含む)、携帯情報端末(モバイルコンピュータ、携帯電話等)などが挙げられる。それらの一例を図7に示す。

【0094】

40

図7(A)は携帯電話であり、本体2001、音声出力部2002、音声入力部2003、表示装置2004、操作スイッチ2005、アンテナ2006で構成される。本願発明は表示装置2004等に適用することができる。

【0095】

図7(B)はビデオカメラであり、本体2101、表示装置2102、音声入力部2103、操作スイッチ2104、バッテリー2105、受像部2106で構成される。本願発明は表示装置2102に適用することができる。

【0096】

図7(C)はモバイルコンピュータ(モービルコンピュータ)であり、本体2201、カメラ部2202、受像部2203、操作スイッチ2204、表示装置2205で構成され

50

る。本願発明は表示装置 2205 等に適用できる。

【0097】

図7(D)はヘッドマウントディスプレイであり、本体2301、表示装置2302、バンド部2303で構成される。本発明は表示装置2302に適用することができる。

【0098】

図7(E)はリア型プロジェクターであり、本体2401、光源2402、表示装置2403、偏光ビームスプリッタ2404、リフレクター2405、2406、スクリーン2407で構成される。本発明は表示装置2403に適用することができる。

【0099】

図7(F)はフロント型プロジェクターであり、本体2501、光源2502、表示装置2503、光学系2504、スクリーン2505で構成される。本発明は表示装置2503に適用することができる。

10

【0100】

以上の様に、本願発明の適用範囲は極めて広く、あらゆる分野の電子機器に適用することが可能である。また、他にも電光掲示盤、宣伝公告用ディスプレイなどにも活用することができます。

【0101】

【発明の効果】

本願発明はAMLCDの画素マトリクス回路を構成する各画素において、完全に平坦な画素電極を実現するための技術である。本願発明の構成は、特に画素電極全面が有効表示領域となる反射型AMLCDに対して有効である。

20

【0102】

本願発明を実施することで画素電極上に発生するディスクリネーションが効果的に防止され、有効表示領域が大幅に拡大する。従って、より高精細なLCDディスプレイにおいても高いコントラストを実現することが可能となる。

【図面の簡単な説明】

- 【図1】 配線の接続構造の構成を示す図。

- 【図2】 画素マトリクス回路の作製工程を示す図。

- 【図3】 画素マトリクス回路の作製工程を示す図。

- 【図4】 画素マトリクス回路の作製工程を示す図。

- 【図5】 画素マトリクス回路の作製工程を示す図。

- 【図6】 電気光学装置の構成を示す図。

- 【図7】 電子機器の構成を示す図。

- 30

【図1】

【図2】

201: 石英基板 202: 非晶質珪素膜 203: マスク絶縁膜

204: 開口部 205: 触媒元素含有層 206: 横成長領域

207: リン添加領域 208: 被ゲッタリング領域

209、210: 活性層 211: ゲイト絶縁膜

【図3】

212、213: 多孔性陽極酸化膜 214、215: 無孔性陽極酸化膜

216、217: ゲイト電極 218、219: ゲイト絶縁膜

220、221: ソース領域 222、223: ドレイン領域

224、225: LDD領域 226、227: チャネル形成領域

228: 第1の層間絶縁膜 229、230: ソース電極

231、232: ドレイン電極 233: 塗化珪素膜 234: 第1の金属膜

235: 第2の層間絶縁膜 236: 第2の金属膜

【図4】

237: 第3の層間絶縁膜 238、239: 開孔部

240~242: 酸化物導電層 243、244: 画素電極

【図5】

501、502：画素電極 503、504：開口部

505、506：酸化物導電層

【図6】

601：アクティブマトリクス基板 602：画素マトリクス回路

603：ソース側駆動回路 604：ゲート側駆動回路 605：対向基板

606：FPC 607、608：ICチップ 609：ロジック回路

【図7】

---

フロントページの続き

(56)参考文献 特開平08-340120(JP,A)

特開平05-335424(JP,A)

特開平09-080464(JP,A)

特開平07-098452(JP,A)

特開平08-101385(JP,A)

特開平04-220625(JP,A)

特開昭57-020778(JP,A)

特開平09-230806(JP,A)

特開平08-076145(JP,A)

特開平11-125831(JP,A)

特開平4-305627(JP,A)

(58)調査した分野(Int.Cl., DB名)

G02F 1/1368