(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-294564

(P2005-294564A)

(43) 公開日 平成17年10月20日(2005.10.20)

(51) Int.Cl.<sup>7</sup>

H01L 29/78

H01L 21/322

F 1

H01L 29/78

H01L 21/322

301G

Z

テーマコード(参考)

5F14O

審査請求 有 請求項の数 14 O L (全 20 頁)

(21) 出願番号

特願2004-108050 (P2004-108050)

(22) 出願日

平成16年3月31日 (2004.3.31)

(71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100109900

弁理士 堀口 浩

(72) 発明者 清水 達雄

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝研究開発センター内

(72) 発明者 山口 豪

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝横浜事業所内

(72) 発明者 西川 幸江

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝研究開発センター内

最終頁に続く

(54) 【発明の名称】半導体デバイスおよび半導体デバイスの製造方法

## (57) 【要約】

## 【課題】

Si基板上に高誘電体材料を成膜したとき、界面ダンギングボンドが多量に残留し、表面欠陥密度(Dit)の増大・移動度の低下・界面反応性の増大・低誘電率層の発生といった重大な問題が発生している。更に高誘電体をゲート絶縁膜に使うと、バンドオフセットが十分に取れない場合がある。

## 【解決手段】

Siを主成分とする半導体基板上に形成した非金属シリサイド薄膜を用いることで、反応性が低く、水素終端よりも安定な構造が得られる。そのため界面荒れが抑えられ、その結果、表面欠陥密度(Dit)の増大・移動度の低下・界面反応性の増大・低誘電率層の発生という問題が抑えられる。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

Siを主成分とする半導体基板上に形成された非金属シリサイド薄膜により前記半導体基板のSiのダングリングボンドが終端されていることを特徴とする半導体デバイス。

**【請求項 2】**

前記非金属シリサイド薄膜は、金属(M)対Siの比が1:2(MSi<sub>2</sub>)であり、Mは2価もしくは4価の金属であることを特徴とする請求項1記載の半導体デバイス。

**【請求項 3】**

前記金属(M)は、Mg、Ca、Sr、Ba、Co、Ni、Pd、Pt、Cu、Ag、Zn、Ti、Zr、Hf、Ce、Mo、W、Ru、Os、Irから選ばれた少なくとも一つの元素であることを特徴とする請求項2記載の半導体デバイス。10

**【請求項 4】**

前記半導体デバイスは、前記非金属シリサイド薄膜上に絶縁膜が形成され、さらにその上に電極が形成されたMIS型電界効果トランジスタであることを特徴とする請求項2記載の半導体デバイス。

**【請求項 5】**

前記非金属シリサイド薄膜上の絶縁膜は、酸化物、窒化物、酸窒化物の何れかであることを特徴とする請求項4記載の半導体デバイス。

**【請求項 6】**

前記非金属シリサイド薄膜は、金属(M)対Siの比が1:1(MSi)であり、Mは2価の金属であることを特徴とする請求項1記載の半導体デバイス。20

**【請求項 7】**

前記金属(M)は、Mg、Ca、Sr、Ba、Co、Ni、Pd、Pt、Cu、Ag、Znから選ばれた少なくとも一つの元素であることを特徴とする請求項6記載の半導体デバイス。

**【請求項 8】**

前記非金属シリサイド薄膜は、金属(M)対Siの比が1:1(MSi)であり、Mは4価の金属であることを特徴とする請求項1記載の半導体デバイス。

**【請求項 9】**

前記金属(M)は、Ti、Zr、Hf、Ce、Mo、W、Ru、Os、Irから選ばれた少なくとも一つの元素であることを特徴とする請求項8記載の半導体デバイス。30

**【請求項 10】**

前記半導体デバイスは、前記非金属シリサイド薄膜上に絶縁膜が形成され、さらにその上に電極が形成されたMIS型電界効果トランジスタであることを特徴とする請求項6または請求項8記載の半導体デバイス。

**【請求項 11】**

前記非金属シリサイド薄膜上の絶縁膜は、酸化物、窒化物、酸窒化物の何れかであることを特徴とする請求項10記載の半導体デバイス。

**【請求項 12】**

前記非金属シリサイド薄膜上にさらに高抵抗シリサイド膜が再構成構造を持つように形成されていることを特徴とする請求項1記載の半導体デバイス。40

**【請求項 13】**

請求項1記載の半導体デバイスの非金属シリサイド薄膜を、スパッタ、CVD、ALD、又はMBEのいずれかにより1モノレイヤ形成することを特徴とする半導体デバイスの形成方法。

**【請求項 14】**

前記非金属シリサイド薄膜上にさらに高抵抗シリサイド膜が再構成構造を持つように形成されていることを特徴とする請求項13に記載の半導体デバイスの形成方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体デバイス、例えば、金属・絶縁体・半導体(MIS)型電界効果トランジスタに係り、半導体基板上に形成された非金属薄膜シリサイドにより、半導体のダンギングボンドを終端させた構造の半導体デバイスおよび半導体デバイスの製造方法に関する。

### 【背景技術】

#### 【0002】

ULSI(Ultra Large Scale Integration)デバイスの微細化や低消費電力化のために、ゲート絶縁膜の薄膜化が要求されるようになってきている。従来、FET(Field Effect Transistor)のチャンネルに誘起される電荷量を確保するために、ゲート絶縁膜を薄膜化することによって容量を大きくする手法が採られてきた。その結果として、ゲート酸化膜である $\text{SiO}_2$ 膜の薄膜化が推し進められ、現在は10オングストローム(1nm)を大きく切る厚さにまで到達しようとしている。10

#### 【0003】

ここに至り、 $\text{SiO}_2$ 膜では、ゲート漏れ電流が大きくなり、待機電力の散逸から消費電力が押さえられないところまで来ている。例えば、膜厚8オングストローム(0.8nm)の $\text{SiO}_2$ 膜でもMOSFETは正常動作するものの、ゲート漏れ電流が1kA/cm<sup>2</sup>にまで達しており、消費電力の面での問題が極めて大きなものとなっている。

#### 【0004】

消費電力をいかに低下させるかという観点からは、実際の膜厚を厚くすることが有効である。このため、誘電率の高い物質(High-K dielectric)を用いることで、 $\text{SiO}_2$ 膜よりも厚膜で電荷量を確保しようとする試みが活発に検討されている。誘電率が高く安定な物質として多くの酸化物があり、絶縁膜としての開発が進められている。現在、特に有望視されている物質としては、HfSiONなどがあるが、これらの誘電率が高い酸化物をSi基板上に直接成膜すると、成膜の過程や後の高温過程において、界面に低誘電率層が発生してしまう。今後、 $\text{SiO}_2$ 膜厚に換算(換算膜厚)して0.5nm以下という要求もあり、低誘電率層の発生は致命的と言える。20

#### 【0005】

また界面に関して、その欠陥密度が非常に重要な意味を持っている。すなわち、界面に欠陥があると、電子や正孔の動きを邪魔することになり、移動度を著しく劣化させることになる。永年用いられてきた $\text{SiO}_2$ とSiの界面では、界面欠陥が非常に少ない構成にすることが可能である。この場合は、界面欠陥密度Ditは $10^9 \text{ cm}^{-2} \text{ eV}^{-1}$ のオーダーにまで低減可能である。その点から、 $\text{SiO}_2$ をベースにしたシリケート物質であれば、界面欠陥をある程度低くすることが可能と考えられ、盛んに開発が行われている。しかし、次の世代になれば、シリケートでは誘電率という意味で十分ではなく、将来のために、誘電率の高い酸化物を絶縁膜として開発していく必要がある。ところがここでまた大きな問題がある。誘電率の高い酸化物をSi基板上に直接成膜した場合、界面には非常に多くの界面欠陥が発生するという問題である。例えば、実際にSi(111)面上に $\text{CeO}_2$ をエピタキシャル成長させた場合、界面欠陥密度Ditは $5 \times 10^{13} \text{ cm}^{-2} \text{ eV}^{-1}$ に達している。そして、集積回路の高速動作に沿う形で考えれば、界面欠陥密度は $\text{SiO}_2 \cdot \text{Si}$ 界面並かそれ以下( $10^9 \text{ cm}^{-2} \text{ eV}^{-1}$ のオーダー以下)に抑えることが必須命題である。30

#### 【0006】

これに対して、絶縁性材料をSi基板上にエピタキシャル成長させる方法が提案されている(以下に挙げている多くの文献参照のこと)。低誘電率層発生抑制と界面欠陥密度の極小化という強い要請に鑑みると、これまでに提案されている、これらのエピタキシャル成長絶縁膜では、いずれも、低誘電率層が発生しないことと界面欠陥密度が $\text{SiO}_2 \cdot \text{Si}$ 界面程度に抑えることを両立させることは出来なかった。一方、Si上にアモルファスの酸化物を成長させる提案も数多くなされているが、やはり、低誘電率層発生抑制と界面欠陥密度の極小化という課題を解決し、両立させている開発はなかった。

#### 【0007】

10

20

30

40

50

更に、高誘電率酸化物を Si 上に直接エピタキシャル成長させた場合、電子障壁が十分に取れず、トンネル電流を抑えることが出来ないことが指摘されている（例えば下記の非特許文献 5 など）。

【特許文献 1】特開 2002-100766 公報

【非特許文献 1】Japanese Journal of Applied Physics 30 pL1415 (1991) (Ishiwara)

【非特許文献 2】Japanese Journal of Applied Physics 33 p1472 (1994) (Ishiwara)

【非特許文献 3】Journal of Vacuum Science & Technology B18 p2139 (2000) (Motorola)

【非特許文献 4】Applied Physics Letter 65 p3182 (1994) (Saeki)

【非特許文献 5】Science vol.293 p468 (2001) (McKee)

10

【非特許文献 6】2002 IEDM Technical Digest p955 (2002) (McKee)

【非特許文献 7】Journal of Vacuum Science & Technology B20 p257 (2002) (Norton)

【発明の開示】

【発明が解決しようとする課題】

【0008】

上記非特許文献 1、2 では、Si 基板上に SiO<sub>2</sub> が残存した形で、Sr あるいは Ti 金属などを厚く成膜している。この時、界面近傍には、低誘電率層が発生しており、ゲート絶縁膜として必要な 0.5 nm 以下の SiO<sub>2</sub> 換算膜厚を達成することは厳密には不可能である。

【0009】

たとえば、Ti 金属を成膜したものでは、界面では Ti シリケートが発生している。また、Ti に関しては、更に問題があり、この成膜過程で出来る誘電体 (TiO<sub>2</sub> や SrTiO<sub>3</sub>) の伝導帯のバンドオフセットが非常に低くなるため、もともとゲート絶縁膜には適していなかった。以下でも同様であり、一連の文献は Si 上への酸化物のエピタキシャル成長に主眼があり、電界効果トランジスタにおいてとても重要な界面特性やバンドオフセットに関する解決策とはならない。

【0010】

非特許文献 3 では、上記非特許文献 1、2 を拡張した開発であり、初期 SiO<sub>2</sub> 膜を薄くして、Sr 量を変え、SiO<sub>2</sub> 上に Sr を成膜して Sr シリケートを作成している。熱処理後は、界面が SiO<sub>2</sub> に近い状態にまで低誘電率化してしまう。このように、耐酸化性が非常に低いため、ゲート絶縁膜として必要な 0.5 nm 以下の SiO<sub>2</sub> 換算膜厚を達成することは不可能である。

30

【0011】

非特許文献 4 では水素終端を用いて SrO を直接成膜している。成膜中に水素は界面から抜けるが、Si 界面のダングリングボンドが SrO という極性の無い物質で終端することはほぼ不可能である。そのため、界面欠陥が多量に発生してしまうことになる。一般に、水素終端面を用いた場合、成膜中に終端が壊れてしまい、界面部分は活性になってしまふ。フォーミングガスアニール (FGA) を行っても、界面が出来た後での回復には限界があり、回復しきれない分だけ、界面の反応性が残ることになる。そのため、後処理温度によっては、界面酸化が進行し、低誘電率層が発生する。また、高誘電体材料をエピタキシャル成長させた場合でも、界面欠陥密度が大きなもの ( $D_{it} = 5 \times 10^{13} \text{ cm}^{-2} \text{ eV}^{-1}$ ) となってしまい、FGAを行っても、一桁程度の回復しかしない。また、酸素中でアニールを行うと、上記のように界面に低誘電率のシリケートが発生してしまうことが分っている。

40

【0012】

非特許文献 5、6 では、1 ML の SrSi<sub>2</sub> を成膜し、その上に余分な金属 Sr を更に成膜した後酸素を導入している。SrSi<sub>2</sub> 上に余分な Sr を導入すると、低温であってもシリサイド膜厚が厚くなってしまい、絶縁性が破壊され、終端構造がとれなくなってしまう。しかも十分に時間や Sr 量を制御していないため、シリサイド膜厚がランダムに分布することになり、界面はかなり荒れることになる。この荒れた金属的シリサイド上に Sr

50

Oが成膜された形となっている。通常シリサイドは金属的であり、その上にSrOを作成しても、バンドギャップは開かない。SrOが酸化物として、ボンドを余分に出さない物質だからである。また、金属的なシリサイドは、ダングリングボンドが余っているために耐酸化性が著しく低下する。また上記のように、ランダムな厚みの金属シリサイドを導入していることを反映して、界面には欠陥が多く、フォーミングガスアニールを行っても、欠陥密度Ditは $10^{11} \text{ cm}^{-2} \text{ eV}^{-1}$ のオーダーで残ってしまう。この文献で行われている開発では、主にSrTiO<sub>3</sub>などをSi上にエピタキシャル成長させるための下地としてBaSi<sub>2</sub>やSrSi<sub>2</sub>などのシリサイドを採用している点がポイントである。この場合、下地の格子情報を上部に成長させる酸化物などに引き継ぐことが最も大切なことであるため、界面の少数の欠陥は存在しても構わることになる。このシリサイド上にSrO、BaO、SrTiO<sub>3</sub>、BaTiO<sub>3</sub>といった酸化物をエピ成長させた場合の界面の欠陥は、成膜時には $10^{12} \text{ cm}^{-2}$ 程度である（成膜後のアニールによって一桁の改善はみられる）。この $10^{12} \text{ cm}^{-2}$ という値は、Si上エピタキシャル成長時に格子定数を引き継ぐための下地としては、非常に小さな値である。一方、これでSi上にゲート絶縁膜を形成し、電界効果トランジスタを形成する場合には、Si/絶縁膜界面の欠陥としては、あまりにも、大きな値である。

10

20

30

40

50

### 【0013】

非特許文献7には、非特許文献5、6と類似した開発に関して記されている。しかし、初期に作成するSiSr<sub>2</sub>シリサイドに膜厚分布があり、この膜厚分布のため、界面が非常に活性な状態にある。そのため、低温550℃、酸素中でのBa成膜時にシリケート構造が発生している。非特許文献5、6に比べ、本文献では、シリサイドに大きな膜厚分布があるため、より界面の活性度が高く、耐酸化性が低いことになる。

### 【0014】

電界効果トランジスタを作成する目的で、シリケートを含めた高誘電体膜をSi基板上に直接成膜した場合、界面低誘電率層が発生してしまい、SiO<sub>2</sub>換算膜厚にして1nmを大きく切るようなゲート絶縁膜（現在では0.5nm以下が目標であるが、将来は更に薄くなる可能性もある）を作成するのが困難である。例として、ZrO<sub>2</sub>ではZrシリケートが、SrTiO<sub>3</sub>ではSiO<sub>2</sub>が界面に発生する。耐酸化性を向上するための、新たな発明が求められている。また、Si基板上に直接成膜が出来、低誘電率層が出来ない場合でも、界面欠陥密度が大きいのでは意味がない。

### 【0015】

また、特許文献1には、Laシリサイド等、2モノレイヤ以下の厚さのシリサイドによりSi基板を終端させ、さらにその上に絶縁膜を形成した電界効果トランジスタが開示されている。しかしながら、この特許文献1のシリサイドは金属とされており、反応性が非常に強くなり薄膜化に向かない。これは、La等、3価の物質の場合、La側のボンドが余り、Siのダングリングボンドはうまく終端されないことに起因する。一旦、シリケートができると、シリケート自体が低い誘電率である上、シリケートで酸素をブロックすることはできないので基板Siの酸化がランダムに進行し上部薄膜との界面が荒れたものとなってしまう。これらはゲート絶縁膜としては問題となる。

### 【課題を解決するための手段】

### 【0016】

本発明は、かかる従来の課題の認識に基づいてなされたものであり、その目的は、Siを主成分とする半導体基板上に形成された非金属シリサイド薄膜により前記半導体基板のSiのダングリングボンドが終端されていることを特徴とする半導体デバイスおよび半導体デバイスの製造方法を提供することにある。

### 【0017】

本発明は、例えば、Si（シリコン）を主成分とする半導体基板上に直接接合してエピタキシャル成長させることによって人為的にバンドギャップを開き、耐酸化性を向上させた薄膜非金属シリサイド層を設け、さらに高誘電体酸化物を用いたゲート絶縁膜が形成された半導体デバイスを提供する。

## 【0018】

また、本発明の半導体デバイスの非金属シリサイド薄膜は、例えば、スパッタ、CVD、ALD、又はMBEのいずれかにより1モノレイヤ形成することを特徴とする半導体デバイスの製造方法を提供する。

## 【発明の効果】

## 【0019】

本発明は、耐酸化性に著しく優れ、低誘電率層が発生せず、かつ、界面欠陥密度が、極めて小さい半導体デバイスを提供することにある。更に、高抵抗シリサイドを導入して電子障壁を上昇させた半導体デバイスおよびその製造方法を提供する。

## 【発明を実施するための最良の形態】

## 【0020】

本発明の実施の形態を説明する前に、まず、本発明の概要について、以下説明する。

## 【0021】

半導体基板上に非金属薄膜シリサイド（この薄膜は、バンドギャップが十分開いた絶縁体である）を介して絶縁体薄膜を成膜すると、絶縁膜・半導体界面のダングリングボンドは、成膜過程・その後の高温過程を通して、非金属薄膜シリサイドにより終端が保たれる。その結果、界面の活性が低下し、耐酸化性が著しく向上する。同時に、界面のダングリングボンドが終端できているため、界面欠陥を一掃することが出来る。これは、Si・SiO<sub>2</sub>界面での界面欠陥よりも、より低密度の界面欠陥しか発生しないことを意味しており、ゲート絶縁膜の作成の下地として非常に有効である。

ここで、非金属シリサイド薄膜の形態としては以下の二つが考えられる。

## 【0022】

第一は、価数が+2あるいは+4である金属MをダイシリサイドMSi<sub>2</sub>という形で、1ML（モノレイヤ）成膜されたものである。つまり、Si（001）面の（2×1）構造上に1MLのシリサイドを高温（物質によって600～900）で形成すると、非常に安定な再構成構造が実現できる。この時、Si（001）面のダングリングボンドは電子を受け取り終端され、丁度1MLのシリサイドにより、ギャップが開いて最安定化することを今回発見した。ここで、金属は微量ずつ制御しながら成膜する必要があるが、金属量が多くなった場合は、高温で保つことで、再度離脱させることが可能である。何故なら、1ML着いた構造が非常に安定な構造であるのに対し、余分な金属が付着した構造はエネルギーの上昇をもたらすからである。上記の安定なシリサイドが1ML出来た上に余分の金属が存在する場合、高温では余分な金属を飛ばすことが可能である。但し、高温すぎれば内部への潜り込みもあり得るので注意が必要である。すなわち適温がある。高温側に条件を緩める方法としては、Si基板中にAsをドープする方法（チャンネルを作成する際に、ドープしたもの、カウンタードープしたものなどをそのまま使えばよい。）がある。すなわち、AsをドープすることでSi基板中に金属が潜り込むことを防ぐことができるため、より高温にして、余分な金属を飛ばすことが可能となる。このようにして、高温での1ML絶縁性薄膜ダイシリサイドの自己生成過程を使うと、高精度で1MLのMSi<sub>2</sub>構造を作成することが容易に出来る（後に示す実施例ではDitが8×10<sup>8</sup>cm<sup>-2</sup>eV<sup>-1</sup>まで出来ていることが分かるが、この値が限界というわけではない。理論的には、更に高精度化も可能である。）。金属Mは、+2価のものとしては、Mg、Ca、Sr、Ba、Co、Ni、Pd、Pt、Cu、Ag、Znから選ばれた少なくとも一つの元素が有効であり、+4価のものとしては、Ti、Zr、Hf、Mo、W、Ru、Os、Irから選ばれた少なくとも一つの元素が有効である。

## 【0023】

第二は、価数が+2である金属MをモノシリサイドMSiという形で、1ML成膜されたものである。

## 【0024】

つまり、Si（001）面の（2×1）構造上に1MLのシリサイドを高温で形成すると、非常に安定な再構成構造が実現できる。この時、Si（001）面のダングリングボ

10

20

30

40

50

ンドは電子を受け取り終端され、丁度 1 M L のシリサイドにより、ギャップが開いて最も安定化することを今回初めて見出した。

#### 【0025】

ここで、金属は微量ずつ制御しながら成膜する必要があるが、金属量が多くなった場合は、中高温（物質によって 400 ~ 700 ）で保つことで、再度離脱させることが可能である。何故なら、1 M L 着いた構造が非常に安定な構造であるのに対し、余分な金属が付着した構造はエネルギーの上昇をもたらすからである。このようにして、高温での過程を使うと、高精度で 1 M L の M S i 構造を作成することが容易に出来る。金属 M は、M g 、C a 、S r 、B a 、C o 、N i 、P d 、P t 、C u 、A g 、Z n から選ばれた少なくとも一つの元素である。

10

#### 【0026】

第三は、価数が +4 である金属 M をモノシリサイド M S i という形で、1 M L 成膜されたものである。

#### 【0027】

つまり、S i (001) 面の (1 × 1) 上に 1 M L のシリサイドを高温で形成すると、非常に安定な再構成構造が実現できる。この時、S i (001) 面のダングリングボンドは電子を受け取り終端され、丁度 1 M L のシリサイドにより、ギャップが開いて最も安定化することを今回発見した。ここで、金属は微量ずつ制御しながら成膜する必要があるが、金属量が多くなった場合は、中高温（物質によって 400 ~ 700 ）で保つことで、再度離脱させることが可能である。何故なら、1 M L 着いた構造が非常に安定な構造であるのに対し、余分な金属が付着した構造はエネルギーの上昇をもたらすからである。このようにして、高温での過程を使うと、高精度で 1 M L の M S i 構造を作成することが容易に出来る。金属 M は、T i 、Z r 、H f 、M o 、W 、R u 、O s 、I r から選ばれた少なくとも一つの元素が有効である。

20

#### 【0028】

また、上記非金属シリサイド上の誘電体膜にランダムに S r などの金属が余分にあると、ギャップ内部に金属的な表面状態（部分的に電子が詰まった状態）が発生して、D i t の悪化、界面反応性の増大などが起こる。しかし、上記シリサイド上に、更に安定な極薄膜高抵抗シリサイドを規則正しい再構成構造を持つように成膜すると、ギャップ内状態によるピニング効果を用いて、S i 基板と絶縁膜の伝導帯側のバンドオフセットを大きくできる。しかも、規則正しく並べることが出来ているので、移動度への影響はほとんどない。

30

#### 【0029】

例えば、高誘電率で知られているチタン酸化物などは伝導帯側のバンドオフセットが小さく問題視されているが、上記のピニング効果を用いることで、伝導帯側バンドオフセットを 1.0 e V 、価電子帯側バンドオフセット 1.1 e V にすることが可能である。ここで、高抵抗シリサイドとは、上記非金属シリサイド上に、シリサイド極薄膜を形成し、バンドギャップ中に局在状態が加わった状態を意味するものとする。

#### 【0030】

以上の非金属シリサイド界面構造を用いると、誘電体膜の初期膜として、アルカリ土類酸化物に限る必要はない。文献 5 ではアルカリ土類酸化物に制限しているが、S i 基板表面の終端が出来ていないために界面構造が不安定であるからである。例えば、単層 S r S i<sub>2</sub> (700 成膜) 成膜後、アモルファス H f O<sub>2</sub> (150 成膜、その後 500 anneal) 成膜が可能であり、単層シリサイド単独で (S r S i<sub>2</sub> / S r 0 という界面は必要ない) 非常に有効である。

40

#### 【0031】

ここで絶縁膜と下地の非金属薄膜シリサイドの関係について簡単にまとめておく。金属 M が構成要素となる、本発明の非金属薄膜シリサイドに関して考える。本発明による特殊なシリサイド薄膜は、通常のバルクシリサイドに比べて酸化・窒化に対し非常に安定である。そのため、通常であれば金属 M が酸化（窒化）されてしまう場合でも酸化（窒化）が

50

進まない。例えば、通常のシリサイド  $HfSi_2$  を  $Si$  上に作成した場合を考えてみる。

### 【0032】

この上に  $TiO_2$  を成膜した場合、シリサイド部分の酸化が進み、最終的には下地に低誘電率層が発生してしまう。それに対し、非金属シリサイドとして  $HfSi_2$  を作成した場合には、耐酸化性が非常に高まっている。そのため、上部に  $TiO_2$  を成膜しても、下地部分には低誘電率層が発生しない。このように、本発明による非金属薄膜シリサイドにより終端した基板に対し、ゲート絶縁膜として、酸化物 ( $SiO_2$ 、 $Al_2O_3$ 、 $Y_2O_3$ 、 $La_2O_3$ 、 $Gd_2O_3$ 、 $Ce_2O_3$ 、 $CeO_2$ 、 $Ta_2O_5$ 、 $HfO_2$ 、 $ZrO_2$ 、 $TiO_2$ 、 $LaAlO_3$ 、 $SrHfO_3$ 、 $SrZrO_3$ 、 $SrTiO_3$ 、 $HfSiO$ 、 $HfAlO$ 、 $AlSiO$ など) 10 、窒化物 ( $Si_3N_4$ 、 $AlN$ 、 $Hf_3N_4$ 、 $Zr_3N_4$ 、 $Ti_3N_4$ など)、酸窒化物 ( $SiON$ 、 $AlON$ 、 $YON$ 、 $LaON$ 、 $GdON$ 、 $CeON$ 、 $TaON$ 、 $HfON$ 、 $ZrON$ 、 $TiON$ 、 $LaAlON$ 、 $SrHfON$ 、 $SrZrON$ 、 $SrTiON$ 、 $HfSiON$ 、 $HfAlON$ 、 $AlSiON$ など)など様々な物質が使用できる。このように多くの絶縁膜が採用可能になったのは、界面シリサイドが基板表面を極めて良好に終端したためである。

### 【実施例】

#### 【0033】

##### (第1の実施例)

次に、本発明の第1の実施例として、 $Si$  基板上にアモルファス  $HfO_2$  誘電体膜を設けた MOSFET について説明する。 20

#### 【0034】

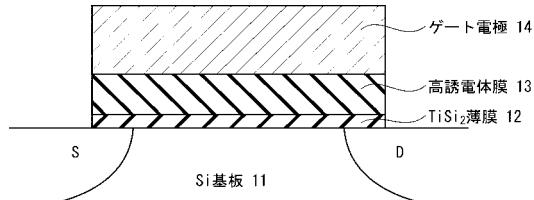

図1は、本発明による第1実施例であるMOSFETのゲート絶縁膜の部分を示す断面図である。すなわち、本実施例のFETは、シリコン基板11の表面部分に、ソース領域S、ドレイン領域Dが形成され、これらの間に形成されたチャネル領域の上に非金属シリサイド薄膜12、ゲート絶縁膜13を介してゲート電極14が設けられている。ここで、シリサイドは1ML (Mono Layer) の非金属薄膜  $TiSi_2$  シリサイドであり、 $Si$  基板のダングリングボンドを終端している。

#### 【0035】

これを製造工程に従って説明する。まず、正面が(001)面の $Si$  基板11の清浄表面を出現させた。この過程は通常用いられているHF(フッ酸)処理を行い、極薄酸化膜  $SiO_2$  を室温のオゾン酸化によって作成し、表面の保護を行った。この基板をMBE装置に搬送し、超高真空において、250にて最表面の不純物を飛ばして除去し、次いで880の高温にすることで表面の極薄酸化膜  $SiO_2$  を飛ばして除去した。この時は、清浄表面が出現して、2×1構造となっていることをRHEED (Reflection High Energy Electron Diffraction; 反射高速電子回折) により確認した。 30

#### 【0036】

次に、非金属シリサイド薄膜  $TiSi_2$  を作成した。K-セル(クヌーセンセル)から  $Ti$  を微量ずつ飛ばし(シャッター開閉)、RHEED信号を見ながらコントロールしている。基板温度は700の高温にして、シャッターの開閉に工夫している。 $Ti$  の必要量は  $TiSi_2$  が1MLとなるようになる量として計算が可能なので、(1)10%ずつ9回に分けて飛ばしRHEED信号強度が安定するまで10秒ずつ待ち時間を入れ、次いで(2)2%ずつ4回・待ち時間5秒にて成膜させ、最後に(3)0.5%の高精度にて4回・待ち時間5秒にて成膜を行っている。このプロセスは最後の(3)の過程ではRHEED信号強度の変化が極めて小さくなり最大強度を迎えていることがわかる。更に  $Ti$  成膜を続けた場合、RHEED信号強度が低下に向かうことが確認できる。この低下に向かったRHEED信号強度も更に高温の800にて待ち時間を10秒程度おくと、余分の  $Ti$  が飛び1MLの  $TiSi_2$  へと戻ることが確認できている。このようにして、1MLの  $TiSi_2$  が作成できる。ここでは、高温過程を700と800に分けている。初期段階で100程度低温にしているわけは、初期段階で高温すぎると、 $Ti$  の表面での 40

動きが大きくなり、Tiの定着率が悪くなるのと同時に、Tiの基板への潜り込みが問題になるからである。そこで1MLまでは700で行い、それ以上の余分なTiが仮にあった場合に備えて800に一度温度を上げる過程を導入するのがもっとも良いと考えられる。

#### 【0037】

この1MLのTiSi<sub>2</sub>を室温にてSTS(scanning tunneling spectroscopy)観察を行った結果、表面の絶縁性が実現しており、バンドギャップが開いているシリサイド(以下、非金属シリサイドと呼ぶ)であることが確認された。この表面は酸素に対して成膜温度(700)以下できわめて安定であり、界面酸化を避けた形での、酸素中で酸化物成膜が可能である。それに対し、成膜温度(700)以下であっても、絶縁性は余分な金属には弱く、余分なTiがあるとその分はシリサイド化が進み、界面は金属へと進んでいく。金属に変わってしまうと、酸素に対しては反応性があり、界面酸化が進むことになる。

#### 【0038】

たとえば、Tiを0.2ML作成してその上にアモルファスHfO<sub>2</sub>膜の作成を試みたところ、界面にTiシリケートとSiO<sub>2</sub>薄膜が出現し、厚い低誘電率層ができてしまった。

#### 【0039】

作成した1MLのTiSi<sub>2</sub>絶縁膜作成すみのSi基板をスパッタ装置に搬送する。まず超高真空にして、250にて表面の不純物を飛ばして除去する。その後、アモルファスHfO<sub>2</sub>を化合物モード(HfO<sub>2</sub>やHfOの形にて粒子が飛んでいる状態)で250の低温にてスパッタ成膜を行った。HfO<sub>2</sub>は4nmの膜厚とした。ここでは酸素分圧をスパッタ成膜初期から高めに設定することが可能であり、そうすることで(化合物モードで成膜している効果もあって)界面に金属状態のHfが付着することを完全に防ぐことが可能である。

#### 【0040】

上記でポイントとなるのは、酸素分圧を成膜初期から高くすることが出来ることと、スパッタの化合物モードを用いたことであるが、この片方だけでも、上記ほどではないにしても特性のよい成膜が可能である。つまり、酸素分圧を初期から高めにして成膜することで、様々な成膜方法が取れることになる。たとえばMBE法にて成膜初期から酸素を導入して成膜することが可能である。また、CVD法でも化合物が付着する形なので、非常によい誘電体膜が作成可能であると考えられる。その様子は次の実施例にて作成している。このような過程は、基板表面が酸素に対し強い構造を作成できたからこそ可能になった過程といえ、この非金属シリサイド薄膜は非常に大きな効果を持っていることがわかる。次に、電極14として、TiNをスパッタにより成膜した。

#### 【0041】

このようにして得られたn型のMISFETに関して調べた。絶縁膜はSiO<sub>2</sub>膜厚に換算した膜厚(EOT)が6.7オングストロームと小さいゲート絶縁膜であった。また、5MV/cmという大きな電界をかけた時のリーク電流を測定すると、0.1A/cm<sup>2</sup>という非常に小さな値が得られた。

#### 【0042】

比較例として、SiO<sub>2</sub>膜のみの絶縁膜において同じEOTにおける、5MV/cmでのリーク電流を外挿により求めると10<sup>5</sup>A/cm<sup>2</sup>であり、10<sup>6</sup>倍にも達していることから、リーク特性のよい絶縁膜が作成できていることがわかる。Si基板・誘電体界面や誘電体・電極界面に欠陥が発生していない、良好な構造が作成できていることになる。このとき、Si基板と誘電体の間の界面欠陥密度Ditを測定すると、およそ9×10<sup>8</sup>cm<sup>-2</sup>というSi基板上のSiO<sub>2</sub>薄膜界面の最適化した場合の値を凌駕する良好な値であった。このことは、シリサイド構造を作る過程・その上に高誘電体薄膜を作成する過程を絞り込んだ結果得られたものである。その結果、Si・SiO<sub>2</sub>界面での電子の移動度以上の高い移動度(550cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>)が得られており、この界面作成過程が非常に

有効であることが確認された。

#### 【0043】

次に、シリコン基板ではなく、ひずみシリコン基板でも同様の構造が可能であり、ひずみ基板にしたことによる移動度の向上が実現されることがわかった。1ML絶縁性シリサイドでは、1パーセント程度の基板格子定数の変化は吸収可能であり、全く同様の構造が作成可能であった。もちろん、その上部に誘電体をエピタキシャル成長させる場合、誘電体部分の格子定数と下地基板の格子定数がプラスマイナス1.5%程度を目途に一致している必要はある。アモルファス誘電体薄膜を用いる場合には、誘電体の格子定数に条件はつかない。

#### 【0044】

そこで1%ひずみシリコン基板の上で上記と同じ構造を作成した。ひずみシリコン基板と誘電体の間の界面欠陥密度D<sub>it</sub>を測定すると、およそ $1 \times 10^9 \text{ cm}^{-2}$ という値であり、上記Si基板上のアモルファスHfO<sub>2</sub>の場合とほぼ一致していた。移動度を測定した結果 $650 \text{ cm}^2 \text{ V}^{-1} \text{ s e c}^{-1}$ という高い値が得られ、ひずみシリコン基板上での絶縁性シリサイド薄膜の有効性が確認された。

#### 【0045】

また別の比較例として、Si基板を清浄化処理して、水素終端を行ない、その上に上記(HfO<sub>2</sub>のスパッタによる成膜)と同じ条件でHfO<sub>2</sub>薄膜を作成した。この時、界面にはHfシリケートの低誘電体層が発生しており、SiO<sub>2</sub>換算膜厚を押し下げてしまうことが確認された。同様に、多くの物質で、成膜段階、或いは高温過程を通る中で界面に低誘電率層が出現してしまうことが報告されている。これに対し、本発明の非金属シリサイド層がある場合には、耐酸化性が著しく向上しており、様々な誘電体膜をその上に成膜可能であることがわかった。

#### (第2の実施例)

次に、本発明の第2実施例として、Si基板上にアモルファスSrHfO<sub>3</sub>誘電体膜を設けたMOSFETについて説明する。

#### 【0046】

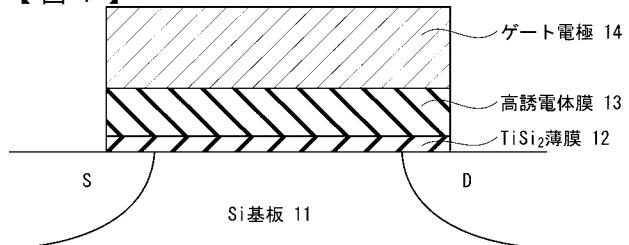

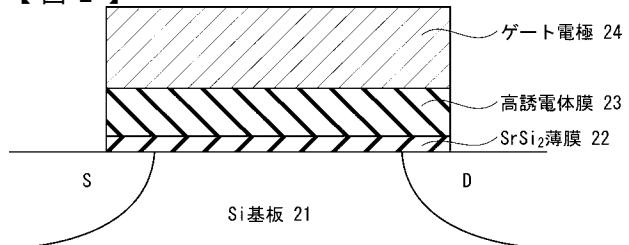

図2は、第2実施例であるMOSFETのゲート絶縁膜の部分を示す断面図である。すなわち、本実施例のFETは、シリコン基板21の表面部分に、ソース領域S、ドレイン領域Dが形成され、これらの間に形成されたチャネル領域の上に絶縁性シリサイド薄膜22、ゲート絶縁膜23を介してゲート電極24が設けられている。ここで、シリサイドは1ML(Mono Layer)の非金属薄膜SrSi<sub>2</sub>シリサイドであり、Si基板のダングリングボンドを終端している。

#### 【0047】

これを製造工程に従って説明する。まず、正面が(001)面のSi基板11の清浄表面を出現させた。この過程は実施例1で説明した通りである。

#### 【0048】

次に、非金属シリサイド薄膜SrSi<sub>2</sub>を作成した。k-セル(クヌーセンセル)からSrを微量ずつ飛ばし(シャッター開閉)、RHEED信号を見ながらコントロールしている。基板温度は600の高温にして、シャッターの開閉に工夫している。Srの必要量はSrSi<sub>2</sub>が1MLとなるようになる量として計算が可能なので、(1)10%ずつ9回に分けて飛ばしRHEED信号強度が安定するまで10秒ずつ待ち時間を入れ、次いで(2)2%ずつ4回・待ち時間5秒にて成膜し、最後に(3)0.5%の高精度にて4回・待ち時間5秒にて成膜を行っている。このプロセスは最後の(3)の過程ではRHEED信号強度の変化が極めて小さくなり最大強度を迎えてることがわかる。更にSr成膜を続けた場合、RHEED信号強度が低下に向かうことが確認できる。この低下に向かったRHEED信号強度も更に高温の700にて待ち時間を10秒程度おくと、余分のSrが飛び1MLのSrSi<sub>2</sub>へと戻ることが確認できている。このようにして、1MLのSrSi<sub>2</sub>が作成できる。ここでは、高温過程を600と700に分けている。初期段階で100程度低温にしているわけは、初期段階で高温すぎると、Srの表面での動き

が大きくなり、Srの定着率が悪くなるのと同時に、Srの基板への潜り込みが問題になるからである。そこで1MLまでは600で行い、それ以上の余分なSrが仮にあった場合に備えて700に一度温度を上げる過程を導入するのがもっとも良いと考えられる。

#### 【0049】

この点は実施例1でも同じであったが、Srの場合の方が100ずつ低温であった。シリサイドごとに最適な温度が決定されるが、ほとんどの物質(Mg、Ca、Ba、Co、Ni、Pd、Pt、Cu、Ag、Zn、Mo、W、Ru、Os, IrはSrと同じ過程で実行可能である。一部高温のTiと同じ過程が好ましいことがわかった。その一部とはCe、Hf、Zrである。

10

#### 【0050】

この1MLのSrSi<sub>2</sub>を室温にてSTS(scanning tunneling spectroscopy)観察を行うと、表面の絶縁性が実現しており、バンドギャップが開いているシリサイド(非金属シリサイド)であることが確認された。

#### 【0051】

この表面は酸素に対して成膜温度(600)以下できわめて安定であり、界面酸化を避けた形での、酸素中で酸化物成膜が可能である。それに対し、成膜温度(600)以下であっても、絶縁性は余分な金属には弱く、余分なSrがあるとその分はシリサイド化が進み、界面は金属へと進んでいく。金属に変わってしまうと、酸素に対しては反応性があり、界面酸化が進むことになる。たとえば、Srを0.2ML作成してその上にアモルファスHfO<sub>2</sub>膜の作成を試みたところ、界面にSrシリケートとSiO<sub>2</sub>薄膜が出現し、厚い低誘電率層ができてしまった。

20

#### 【0052】

作成した1MLのSrSi<sub>2</sub>絶縁膜作成までのSi基板をCVD装置に搬送する。まず超高真空にして、250にて表面の不純物を飛ばして除去する。その後、アモルファスSrHfO<sub>3</sub>を250の低温にて成膜した。SrHfO<sub>3</sub>は4nmの膜厚とした。ここでは酸素分圧を成膜初期から高めに設定することが可能であり、そうすることで界面に金属状態のHfやSrが付着することを完全に防ぐことが可能である。その後、550・5分間の酸素中アニールを行った。

30

#### 【0053】

このとき、Si基板と誘電体の間の界面欠陥密度Ditを測定すると、およそ $8 \times 10^8 \text{ cm}^{-2} \text{ eV}^{-1}$ という良好な値であった。このことは、シリサイド構造を作る過程・その上に高誘電体薄膜を作成する過程を絞り込んだ結果得られたものである。その結果、高い移動度( $560 \text{ cm}^2 \text{ V}^{-1} \text{ s e c}^{-1}$ )が得られており、この界面作成過程が非常に有効であることが確認された。

#### 【0054】

1%ひずみシリコン基板の上で上記と同じ構造を作成した。ひずみシリコン基板と誘電体の間の界面欠陥密度Ditを測定すると、およそ $9 \times 10^8 \text{ cm}^{-2} \text{ eV}^{-1}$ という値であり、上記Si基板上のアモルファスSrHfO<sub>3</sub>の場合とほぼ一致していた。移動度を測定した結果 $670 \text{ cm}^2 \text{ V}^{-1} \text{ s e c}^{-1}$ という高い値が得られ、ひずみシリコン基板での絶縁性シリサイド薄膜の有効性が確認された。

40

#### (第三の実施例)

次に、本発明による第3実施例として、Si基板上にアモルファスZrO<sub>2</sub>誘電体膜を設けたMOSFETについて説明する。

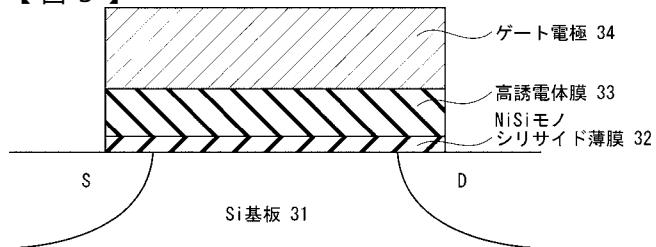

#### 【0055】

図3は、本発明による第3の実施例のMOSFETにおけるゲート絶縁膜の部分を示す断面図である。

#### 【0056】

すなわち、本実施例のFETでは、シリコン基板31の表面部分に、ソース領域S、ドレイン領域Dが形成され、これらの間に形成されたチャネル領域の上に非金属シリサイド

50

薄膜32、ゲート絶縁膜33を介してゲート電極34が設けられている。ここで、シリサイドは1ML(Mono Layer)の非金属の薄膜NiSiモノシリサイドであり、Si基板のダンギングボンドを終端している。

#### 【0057】

これを製造工程に従って説明する。まず、正面が(001)面のSi基板11の清浄表面を出現させた。この過程は実施例1で説明した通りである。

#### 【0058】

次に、非金属モノシリサイド薄膜NiSiを作成した。K-セル(クヌーセンセル)からNiを微量ずつ飛ばし(シャッター開閉)、RHEED信号を見ながらコントロールしている。基板温度は450の高温にして、シャッターの開閉に工夫している。

10

#### 【0059】

Niの必要量はNiSiが1MLとなるようになる量として計算が可能なので、(1)10%ずつ9回に分けて飛ばしRHEED信号強度が安定するまで10秒ずつ待ち時間を入れ、次いで(2)2%ずつ4回・待ち時間5秒にて成膜し、最後に(3)0.5%の高精度にて4回・待ち時間5秒にて成膜を行っている。このプロセスは最後の(3)の過程ではRHEED信号強度の変化が極めて小さくなり最大強度を迎えてることがわかる。

#### 【0060】

更にNi成膜を続けた場合、RHEED信号強度が低下に向かうことが確認できる。この低下に向かったRHEED信号強度も更に高温の550にて待ち時間を10秒程度おくと、余分のNiが飛び1MLのNiSiへと戻ることが確認できている。このようにして、1MLのNiSiが作成できる。ここでは、高温過程を450と550に分けている。初期段階で100程度低温にしているわけは、初期段階で高温すぎると、Niの表面での動きが大きくなり、Niの定着率が悪くなるのと同時に、Niの基板への潜り込みが問題になるからである。そこで1MLまでは450で行い、それ以上の余分なNiが仮にあった場合に備えて550に一度温度を上げる過程を導入するのがもっとも良いと考えられる。この点は実施例1や2でも同じであったが、NiSiの場合の方がかなり低温であった。モノシリサイドの生成温度が低いためであり、有効なすべての物質(Mg、Ca、Sr、Ba、Co、Ni、Pd、Pt、Cu、Ag、Zn)に対して、全く同様の過程で作成可能である。

20

30

#### 【0061】

この1MLのNiSiを室温にてSTS(scanning tunneling spectroscopy)観察を行うと、表面の絶縁性が実現しており、バンドギャップが開いているシリサイド(非金属シリサイド)であることが確認された。この表面は酸素に対して成膜温度(450)以下できわめて安定であり、界面酸化を避けた形での、酸素中で酸化物成膜が可能である。それに対し、成膜温度(450)以下であっても、絶縁性は余分な金属には弱く、余分なNiがあるとその分はシリサイド化が進み、界面は金属へと進んでいく。

40

#### 【0062】

金属に変わってしまうと、酸素に対しては反応性があり、界面酸化が進むことになる。たとえば、Niを0.2ML作成してその上にアモルファスHfO<sub>2</sub>膜の作成を試みたところ、界面にSiO<sub>2</sub>薄膜が出現し、厚い低誘電率層ができてしまった。

#### 【0063】

作成した1MLのNiSi絶縁膜作成すみのSi基板をCVD装置に搬送する。まず超高真空にして、250にて表面の不純物を飛ばして除去する。その後、アモルファスZrO<sub>2</sub>を250の低温にて成膜した。ZrO<sub>2</sub>は4nmの膜厚とした。ここでは酸素分圧を成膜初期から高めに設定することが可能であり、そうすることで界面に金属状態のZrが付着することを完全に防ぐことが可能である。その後550・5分間の酸素中アニールを行った。このとき、シリサイド膜の安定性が心配であるが、550・5分の酸素中アニールでは界面に変化は現れることはなかった。

#### 【0064】

50

更にここで、1050の数秒間のアニールを行った場合でも、界面構造そのものが非常に安定であることを反映して、界面低誘電率層が出現することはなかった。

#### 【0065】

このとき、Si基板と誘電体の間の界面欠陥密度Ditを測定すると、およそ $2 \times 10^9 \text{ cm}^{-2} \text{ eV}^{-1}$ という良好な値であった。このことは、シリサイド構造を作る過程・その上に高誘電体薄膜を作成する過程を絞り込んだ結果得られたものである。その結果、高い移動度( $500 \text{ cm}^2 \text{ V}^{-1} \text{ sec}^{-1}$ )が得られており、この界面作成過程が非常に有効であることが確認された。

#### 【0066】

1%ひずみシリコン基板の上で上記と同じ構造を作成した。ひずみシリコン基板と誘電体の間の界面欠陥密度Ditを測定すると、およそ $4 \times 10^9 \text{ cm}^{-2} \text{ eV}^{-1}$ という値であり、上記Si基板上のアモルファスZrO<sub>2</sub>の場合とほぼ一致していた。移動度を測定した結果 $600 \text{ cm}^2 \text{ V}^{-1} \text{ sec}^{-1}$ という高い値が得られ、ひずみシリコン基板での非金属シリサイド薄膜の有効性が確認された。10

#### (第4の実施例)

次に、本発明の第4実施例として、Si基板上にエピタキシャルCa(Zr、Ti)O<sub>3</sub>誘電体膜を設けたMOSFETについて説明する。

#### 【0067】

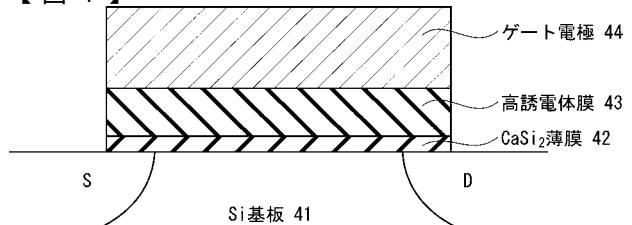

図4は、第4実施例によるMOSFETのゲート絶縁膜の部分を示す断面図である。20

すなわち、本実施例のFETは、シリコン基板41の表面部分に、ソース領域S、ドレイン領域Dが形成され、これらの間に形成されたチャネル領域の上に非金属シリサイド薄膜42、ゲート絶縁膜43を介してゲート電極44が設けられている。ここで、シリサイドは1ML(Mono Layer)の非金属シリサイド薄膜CaSi<sub>2</sub>シリサイドであり、Si基板のダングリングボンドを終端している。

#### 【0068】

これを製造工程に従って説明する。まず、主面が(001)面のSi基板41の清浄表面を出現させた。この過程は実施例1で説明した通りである。

#### 【0069】

次に、非金属シリサイド薄膜CaSi<sub>2</sub>を作成した。K-セル(クヌーセンセル)からCaを微量ずつ飛ばし(シャッター開閉)、RHEED信号を見ながらコントロールしている。基板温度は600の高温にして、シャッターの開閉に工夫している。Caの必要量はCaSi<sub>2</sub>が1MLとなるようになる量として計算が可能なので、(1)10%ずつ9回に分けて飛ばしRHEED信号強度が安定するまで10秒ずつ待ち時間を入れ、次いで(2)2%ずつ4回・待ち時間5秒にて成膜し、最後に(3)0.5%の高精度にて4回・待ち時間5秒にて成膜を行っている。このプロセスは最後の(3)の過程ではRHEED信号強度の変化が極めて小さくなり最大強度を迎えてることがわかる。更にCa成膜を続けた場合、RHEED信号強度が低下に向かうことが確認できる。この低下に向かったRHEED信号強度も更に高温の700にて待ち時間を10秒程度おくと、余分のCaが飛び1MLのCaSi<sub>2</sub>へと戻ることが確認できている。このようにして、1MLのCaSi<sub>2</sub>が作成できる。ここでは、高温過程を600と700に分けている。30

#### 【0070】

初期段階で100程度低温にしているわけは、初期段階で高温すぎると、Srの表面での動きが大きくなり、Caの定着率が悪くなるのと同時に、Caの基板への潜り込みが問題になるからである。そこで1MLまでは600で行い、それ以上の余分なCaが仮にあった場合に備えて700に一度温度を上げる過程を導入するのがもっとも良いと考えられる。この点は実施例1でも同じであったが、Caの場合の方が100ずつ低温であった。

#### 【0071】

この1MLのCaSi<sub>2</sub>を室温にてSTS(scanning tunneling spectroscopy)観察を行うと、表面の絶縁性が実現しており、バンドギャップが開いているシリサイド(非金属)40

50

シリサイド)であることが確認された。

#### 【0072】

この表面は酸素に対して成膜温度(600)以下できわめて安定であり、界面酸化を避けた形での、酸素中で酸化物成膜が可能である。それに対し、成膜温度(600)以下であっても、絶縁性は余分な金属には弱く、余分なCaがあるとその分はシリサイド化が進み、界面は金属へと進んでいく。金属に変わってしまうと、酸素に対しては反応性があり、界面酸化が進むことになる。たとえば、Caを0.2ML作成してその上にアモルファスHfO<sub>2</sub>膜の作成を試みたところ、界面にCaシリケートとSiO<sub>2</sub>薄膜が出現し、厚い低誘電率層ができてしまった。

#### 【0073】

作成した1MLのCaSi<sub>2</sub>絶縁膜作成すみのSi基板をそのままMBE装置の中に留め、絶縁膜の作成をした。CaO膜をまず1MLだけ成膜した。Caを、オゾンフラックス $1.5 \times 10^{12}$ 分子/秒cm<sup>2</sup>を流した状態で、圧力 $10^{-7}$ パスカル、基板温度は200という低温にて成長させている。次に(Zr、Ti)O<sub>2</sub>を1MLだけ成膜した。(Zr、Ti)固溶金属を、オゾンフラックス $1.5 \times 10^{12}$ 分子/秒cm<sup>2</sup>を流した状態で、圧力 $10^{-7}$ パスカル、基板温度は200という、CaOと同条件にて成長させている。あとはこれを繰り返すことによって、Ca(Zr、Ti)O<sub>3</sub>エピタキシャル成長膜を形成した。Ca(Zr、Ti)O<sub>3</sub>膜は4nmの膜厚とした。ここではオゾンフラックスを成膜初期から流すことが可能であり、そうすることで界面に金属状態のCaやZr、Tiなどが付着することを完全に防ぐことが可能である。その後550・5分間の酸素中アニールを行った。Ca(Ti、Zr)O<sub>3</sub>は格子定数がSiとほぼ一致しており、SrTiO<sub>3</sub>よりもSi上へのエピタキシャル成長に向いている。また、Siに対する伝導帯側のバンドオフセットも1eV以上ある物質なので、ゲート絶縁膜として有効である。

#### 【0074】

本発明の実施例によらなければ、Siと絶縁膜の界面に低誘電率膜が出来てしまうため、Ca(Ti、Zr)O<sub>3</sub>をゲート絶縁膜として使用することはなかったが、本発明の実施例によれば、極めて有効である。

#### (第5の実施例)

次に、本発明による第5実施例として、Si基板上にアモルファスSrTiO<sub>3</sub>誘電体膜を設けたMOSFETについて説明する。

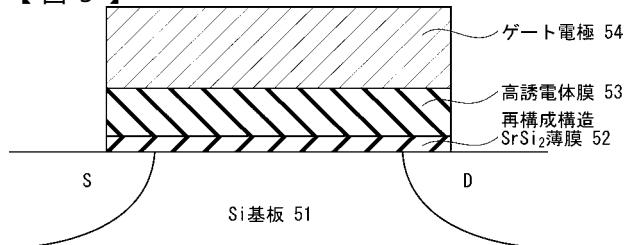

#### 【0075】

図5は、第5実施例によるMOSFETのゲート絶縁膜の部分を示す断面図である。すなわち、本実施例のFETは、シリコン基板51の表面部分に、ソース領域S、ドレイン領域Dが形成され、これらの間に形成されたチャネル領域の上に非金属シリサイド薄膜52、ゲート絶縁膜53を介してゲート電極54が設けられている。ここで、シリサイドは1ML(Mono Layer)の非金属薄膜SrSi<sub>2</sub>シリサイド上に再構成構造にして4倍の大きさになるようにシリサイド構造を再構成した高抵抗シリサイドであり、Si基板のダンギングボンドを終端している。

#### 【0076】

これを製造工程に従って説明する。まず、正面が(001)面のSi基板11の清浄表面を出現させた。この過程は実施例1で説明した通りである。

#### 【0077】

次に、非金属シリサイド薄膜SrSi<sub>2</sub>を作成した。この過程は実施例2と全く同様である。その後、基板温度600の高温にて、Srを0.0625MLに相当するだけKセル(クヌーセンセル)からSrを微量ずつ飛ばした。この時、RHEED信号を観察していると、一旦信号が消えるが十分に時間が経つと、当初の非金属シリサイド薄膜において示していた再構成構造の4倍の大きさの再構成構造が出現する。

#### 【0078】

このシリサイド構造を室温にてSTS(scanning tunneling spectroscopy)観察を行うと、表面は絶縁性を示しているが、バンドギャップ中に局在状態が出現しており、高抵

抗の半導体状態になっていることが判明した。この表面は酸素に対して成膜温度(600)以下できわめて安定であり、界面酸化を避けた形での、酸素中で酸化物成膜が可能であった。この高抵抗シリサイドも、これまでの実施例の非金属シリサイドとほぼ同等の耐酸化性があるが、成膜温度(600)以下であっても、高抵抗性は余分な金属には弱く、余分なSrがあるとその分はシリサイド化が進み、界面は金属へと進んでいく。金属に変わってしまうと、酸素に対しては反応性があり、界面酸化が進むことになる。たとえば、Srを0.2ML作成してその上にアモルファスHfO<sub>2</sub>膜の作成を試みたところ、界面にSrシリケートとSiO<sub>2</sub>薄膜が出現し、厚い低誘電率層ができてしまった。

#### 【0079】

次に、上記の高抵抗シリサイドSrSi<sub>2</sub>膜作成までのSi基板をCVD装置に搬送した。まず超高真空にして、250にて表面の不純物を飛ばして除去する。その後、アモルファスSrTiO<sub>3</sub>を250の低温にて成膜した。SrTiO<sub>3</sub>は20nmの膜厚とした。ここでは酸素分圧を成膜初期から高めに設定することが可能であり、そうすることで界面に金属状態のTiやSrが付着することを完全に防ぐことが可能である。その後50・5分間の酸素中アニールを行った。

#### 【0080】

このとき、Si基板と誘電体の間の界面欠陥密度Ditを測定すると、およそ $1 \times 10^9 \text{ cm}^{-2} \text{ eV}^{-1}$ という良好な値であった。このことは、シリサイド構造を作る過程・その上に高誘電体薄膜を作成する過程を絞り込んだ結果得られたものである。その結果、高い移動度( $540 \text{ cm}^2 \text{ V}^{-1} \text{ sec}^{-1}$ )が得られており、この界面作成過程が非常に有効であることが確認された。高抵抗シリサイド構造では、界面に局在状態が出来るが、上記のように、周期性をきちんと保った構造を形成しているため、ランダム性からくる散乱が排除されていることが分る。

#### 【0081】

次に、電極54として、TiNをスパッタにより成膜した。

#### 【0082】

このようにして得られたn型のMISFETに関して調べた。絶縁膜はSiO<sub>2</sub>膜厚に換算した膜厚(EOT)が2.6オングストロームと小さいゲート絶縁膜であった。また、5MV/cmという大きな電界をかけた時のリーク電流を測定すると、1A/cm<sup>2</sup>という非常に小さな値が得られた。通常SrTiO<sub>3</sub>では電子障壁が低いため、リーク電流が止まらず、この膜厚では測定不可である。それにも拘わらず、測定が出来ているのは、ゲート絶縁膜のバンドオフセットが、1.0eVに上昇しているためである。高抵抗シリサイドが持つバンドギャップ中の局在状態によりピニングが起こさせ、バンドオフセットを上昇させることに成功した。

#### 【0083】

比較例として、SiO<sub>2</sub>膜のみの絶縁膜において同じEOTにおける、5MV/cmでのリーク電流を外挿により求めると $10^8 \text{ A}/\text{cm}^2$ であり、 $10^8$ 倍にも達していることから、リーク特性のよい絶縁膜が作成できていることがわかる。Si基板・誘電体界面や誘電体・電極界面に欠陥が発生していない、良好な構造が作成できることになる。

#### (第六の実施例)

次に、本発明による第6実施例として、Si基板上にアモルファスLaAlO<sub>3</sub>誘電体膜を設けたMOSFETについて説明する。

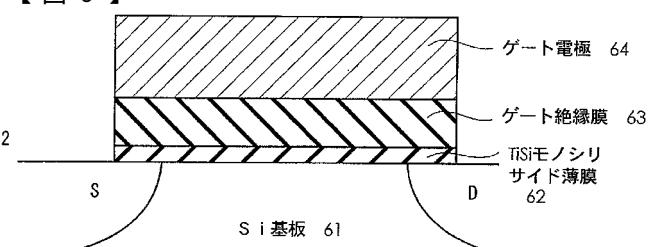

#### 【0084】

図6は、本発明による第6の実施例のMOSFETにおけるゲート絶縁膜の部分を示す断面図である。

#### 【0085】

すなわち、本実施例のFETでは、シリコン基板61の表面部分に、ソース領域S、ドレイン領域Dが形成され、これらの間に形成されたチャネル領域の上に非金属シリサイド薄膜62、ゲート絶縁膜63を介してゲート電極64が設けられている。ここで、シリサイドは1ML(Mono Layer)の非金属の薄膜TiSiモノシリサイドであり、Si基板の

10

20

30

40

50

ダングリングボンドを終端している。

#### 【0086】

これを製造工程に従って説明する。まず、正面が(001)面のSi基板11の清浄表面を出現させた。この過程は実施例1で説明した通りである。更にSi基板を高温(1050)にてアニールすることで、清浄化表面の構造を(1×1)構造にした。

#### 【0087】

次に、非金属モノシリサイド薄膜TiSiを作成した。K-セル(クヌーセンセル)からTiを微量ずつ飛ばし(シャッター開閉)、RHEED信号を見ながらコントロールしている。基板温度は550の高温にして、シャッターの開閉に工夫している。

#### 【0088】

Tiの必要量はTiSiが1MLとなるようになる量として計算が可能なので、(1)10%ずつ9回に分けて飛ばしRHEED信号強度が安定するまで10秒ずつ待ち時間を入れ、次いで(2)2%ずつ4回・待ち時間5秒にて成膜し、最後に(3)0.5%の高精度にて4回・待ち時間5秒にて成膜を行っている。このプロセスは最後の(3)の過程ではRHEED信号強度の変化が極めて小さくなり最大強度を迎えてることがわかる。

#### 【0089】

更にTi成膜を続けた場合、RHEED信号強度が低下に向かうことが確認できる。この低下に向かったRHEED信号強度も更に高温の650にて待ち時間を10秒程度おくと、余分のTiが飛び1MLのTiSiへと戻ることが確認できている。このようにして、1MLのTiSiが作成できる。ここでは、高温過程を550と650に分けている。初期段階で100程度低温にしているわけは、初期段階で高温すぎると、Tiの表面での動きが大きくなり、Tiの定着率が悪くなるのと同時に、Tiの基板への潜り込みが問題になるからである。そこで1MLまでは550で行い、それ以上の余分なTiが仮にあった場合に備えて650に一度温度を上げる過程を導入するのがもっとも良いと考えられる。この点は実施例1や2でも同じであったが、TiSiの場合の方がかなり低温であった。モノシリサイドの生成温度が低いためであり、有効なすべての物質(Ti、Zr、Hf、Ce、Mo、W、Ru、Os、Ir)に対して、全く同様の過程で作成可能である。

#### 【0090】

この1MLのTiSiを室温にてSTS(scanning tunneling spectroscopy)観察を行うと、表面の絶縁性が実現しており、バンドギャップが開いているシリサイド(非金属シリサイド)であることが確認された。この表面は酸素に対して成膜温度(550)以下できわめて安定であり、界面酸化を避けた形での、酸素中で酸化物成膜が可能である。それに対し、成膜温度(550)以下であっても、絶縁性は余分な金属には弱く、余分なTiがあるとその分はシリサイド化が進み、界面は金属へと進んでいく。

#### 【0091】

金属に変わってしまうと、酸素に対しては反応性があり、界面酸化が進むことになる。たとえば、Tiを0.2ML作成してその上にアモルファスHfO<sub>2</sub>膜の作成を試みたところ、界面にSiO<sub>2</sub>薄膜が出現し、厚い低誘電率層ができてしまった。

#### 【0092】

作成した1MLのTiSi絶縁膜作成すみのSi基板をCVD装置に搬送する。まず超高真空中にして、250にて表面の不純物を飛ばして除去する。その後、アモルファスLaAlO<sub>3</sub>を250の低温にて成膜した。LaAlO<sub>3</sub>は4nmの膜厚とした。ここでは酸素分圧を成膜初期から高めに設定することが可能であり、そうすることで界面に金属状態のLaやAlが付着することを完全に防ぐことが可能である。その後550・5分間の酸素中アニールを行った。このとき、シリサイド膜の安定性が心配であるが、550・5分の酸素中アニールでは界面に変化は現れることはなかった。

#### 【0093】

更にここで、1050の数秒間のアニールを行った場合でも、界面構造そのものが非

10

20

30

40

50

常に安定であることを反映して、界面低誘電率層が出現することはなかった。

#### 【0094】

このとき、Si基板と誘電体の間の界面欠陥密度D<sub>it</sub>を測定すると、およそ $1 \times 10^9 \text{ cm}^{-2} \text{ eV}^{-1}$ という良好な値であった。このことは、シリサイド構造を作る過程・その上に高誘電体薄膜を作成する過程を絞り込んだ結果得られたものである。その結果、高い移動度( $520 \text{ cm}^2 \text{ V}^{-1} \text{ sec}^{-1}$ )が得られており、この界面作成過程が非常に有効であることが確認された。

#### 【0095】

1%ひずみシリコン基板の上で上記と同じ構造を作成した。ひずみシリコン基板と誘電体の間の界面欠陥密度D<sub>it</sub>を測定すると、およそ $2 \times 10^9 \text{ cm}^{-2} \text{ eV}^{-1}$ という値であり、上記Si基板上のアモルファスLaAlO<sub>3</sub>の場合とほぼ一致していた。移動度を測定した結果 $630 \text{ cm}^2 \text{ V}^{-1} \text{ sec}^{-1}$ という高い値が得られ、ひずみシリコン基板上での非金属シリサイド薄膜の有効性が確認された。

#### 【0096】

本発明の半導体デバイスの例として、実施例ではMISFETについて説明を行ったが、本発明は、CMOS等のロジック回路や、SRAM、DRAM、フラッシュ、MRAM、FeRAM等のメモリ(特に周辺回路)への適用、さらにはこれらを組み合わせて混載したシステムLSIへの応用も考えられる。

#### 【0097】

以上、本発明の実施例で説明したように、Siを主成分とする半導体基板上に形成された非金属シリサイド薄膜により、半導体基板のSiのダンギングボンドが極めて良好に終端されているので、次のような効果が得られる。

#### 【0098】

(1)高温過程を通して、ダンギングボンドの終端が維持される。(2)基板・誘電体界面は耐酸化性に極めて優れ、反応性に乏しい界面になる。(3)基板・誘電体界面の欠陥は殆ど認められず、良好な界面を形成する。従って、この基板上にさらに誘電体薄膜、および電極を形成して電界効果トランジスタ等の半導体デバイスを構成した場合、上述した効果が得られた結果として、デバイスの移動度をSi/SiO<sub>2</sub>界面に比べて飛躍的に向上させることが可能となる。

#### 【0099】

この非金属シリサイド成膜過程で表面終端が完了しているため、表面は非常に安定で、耐酸化性も向上している。その上には、これまででは特性が十分發揮できなかつた様々な高誘電率材料の成膜も可能となる。例えば、通常であれば界面酸化性のために低誘電率層SiO<sub>2</sub>が出来てしまうような高誘電体膜(例えばアモルファスHfO<sub>2</sub>、アモルファスZrO<sub>2</sub>、アモルファスSrHfO<sub>3</sub>、エピタキシャルCa(Zr、Ti)O<sub>3</sub>など)を低誘電率層の発生なしで作成することが可能となる。また、LSI作成工程での高温過程にも強い界面である。

#### 【0100】

更に、この非金属シリサイドの上に規則正しくならんだ高抵抗シリサイドを作成することが可能である。この場合、バンドギャップ中に局在状態が発生しているが、金属ではなく、半導体的な振る舞いを示す。金属にまで達してしまうと、次第に耐酸化性が落ちてしまうので使用範囲に制限が大きくなってしまう。それに対し、局在状態を作成した段階までであれば、耐酸化性は非常に高い。この高抵抗シリサイドを用いて、フェルミエネルギーのピニングを起こさせることで、Si基板とゲート絶縁膜の間のバンドオフセットを伝導帯側と価電子帯側で同程度になるように制御することが可能になる。例えば、高誘電体でありながら、伝導帯バンドオフセットが殆ど取れないとされているSrTiO<sub>3</sub>やTiO<sub>2</sub>などでも、伝導帯バンドオフセットを $1.0 \text{ eV}$ にまで引き上げることが出来る。また、温度や成膜速度を最適化することで規則正しく並べることが出来るため、界面局在状態によるランダムな散乱は発生せず、キャリアの移動度が低下することはない。

10

20

30

40

50

**【図面の簡単な説明】****【0101】**

【図1】本発明の第1の実施例によるMOSFETのゲート絶縁膜部分を模式的に示す断面図。

【図2】本発明の第2の実施例によるMOSFETのゲート絶縁膜部分を模式的に示す断面図。

【図3】本発明の第3の実施例によるMOSFETのゲート絶縁膜部分を模式的に示す断面図。

【図4】本発明の第4の実施例によるMOSFETのゲート絶縁膜部分を模式的に示す断面図。

【図5】本発明の第5の実施例によるMOSFETのゲート絶縁膜部分を模式的に示す断面図。

【図6】本発明の第6の実施例によるMOSFETのゲート絶縁膜部分を模式的に示す断面図。

**【符号の説明】****【0102】**

11、21、31、41、51、61 . . . Si 基板

12 . . . 非金属 Ti<sub>2</sub> 薄膜

13 . . . HfO<sub>2</sub> 膜

14 . . . TiN ゲート電極

22 . . . 非金属 SrSi<sub>2</sub> 薄膜

23 . . . SrHfO<sub>3</sub> 高誘電体膜

24、34、44、54、64 . . . ゲート電極

32 . . . 非金属 NiSi モノシリサイド薄膜

33 . . . ZrO<sub>2</sub> 高誘電体膜

42 . . . 非金属 CaSi<sub>2</sub> 薄膜

43 . . . Ca(Ti、Zr)O<sub>3</sub> 高誘電体膜

52 . . . 非金属 SrSi<sub>2</sub> 薄膜

53 . . . SrTiO<sub>3</sub> 高誘電体膜

62 . . . 非金属 TiSi 薄膜

63 . . . LaAlO<sub>3</sub> 高誘電体膜

10

20

30

【図1】

【図4】

【図2】

【図5】

【図3】

【図6】

---

フロントページの続き

F ターム(参考) 5F140 AA00 AA01 AA24 AC28 BA01 BA20 BD01 BD04 BD11 BD13

BE01 BF01 BF10 BG30