(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2011년07월19일

(11) 등록번호 10-1050283

(24) 등록일자 2011년07월12일

(51) Int. Cl.

*H04B 1/40* (2006.01) *H04B 1/38* (2006.01)*H04M 1/00* (2006.01)

(21) 출원번호 10-2005-7003005

(22) 출원일자(국제출원일자) 2003년08월27일

심사청구일자 2008년07월31일

(85) 번역문제출일자 2005년02월22일

(65) 공개번호 10-2005-0058445

(43) 공개일자 2005년06월16일

(86) 국제출원번호 PCT/US2003/027182

(87) 국제공개번호 WO 2004/021684

국제공개일자 2004년03월11일

(30) 우선권주장

10/229,507 2002년08월27일 미국(US)

(56) 선행기술조사문헌

JP11215043 A\*

JP14032158 A\*

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

퀄콤 인코포레이티드

미국 캘리포니아 샌디에고 모어하우스

드라이브5775 (우 92121-1714)

(72) 발명자

크리쉬난, 란가나단

미국 92129 캘리포니아 샌디에고 #43 아주아가 스트리트 10311

로드원, 알버트 에스.

미국 92121 캘리포니아 샌디에고 오크뷰 웨이 11975

가드너, 윌리암 알.

미국 92130 캘리포니아 샌디에고 키우드 코트 4232

(74) 대리인

남상선

전체 청구항 수 : 총 9 항

심사관 : 장진환

(54) 다중 모드 장치들을 위한 저전력 이중 프로세서 구조

**(57) 요 약**

예컨대 무선 통신 및 개인 컴퓨팅과 같은 다중 모드들을 갖는 이동 계산 장치는 애플리케이션 프로세서 및 통신 프로세서를 구비한다. 계산 모드에서, 애플리케이션 프로세서는 마스터 프로세서이다. 통신 모드에서, 애플리케이션 프로세서는 배터리 전력을 보존하기 위해서 에너지 공급이 중단되고, 통신 프로세서는 상기 통신 프로세서의 메모리 인터페이스를 사용하여 장치의 주변 버스를 액세스함으로써 마스터 프로세서로서 기능한다.

**대 표 도 - 도2**

**특허청구의 범위**

청구항 1

삭제

청구항 2

삭제

청구항 3

삭제

청구항 4

삭제

청구항 5

삭제

청구항 6

삭제

청구항 7

삭제

청구항 8

삭제

청구항 9

삭제

청구항 10

삭제

청구항 11

삭제

청구항 12

삭제

청구항 13

삭제

청구항 14

삭제

청구항 15

삭제

청구항 16

삭제

청구항 17

삭제

청구항 18

삭제

청구항 19

삭제

청구항 20

삭제

청구항 21

삭제

청구항 22

삭제

청구항 23

삭제

청구항 24

삭제

청구항 25

삭제

청구항 26

삭제

청구항 27

삭제

청구항 28

삭제

청구항 29

삭제

청구항 30

삭제

청구항 31

통신 모드와 계산 모드 간에 스위칭하도록 구성된 다중 모드 이동 장치로서,

상기 다중 모드 이동 장치가 상기 통신 모드에 있는 경우에 무선 음성 및 데이터 통신을 용이하게 하도록 구성된 통신 프로세서;

상기 다중 모드 이동 장치가 상기 계산 모드에 있는 경우에 적어도 하나의 개인 계산 어플리케이션을 실행하도록 구성된 어플리케이션 프로세서;

전화 번호의 적어도 일부의 사용자 입력에 응답하여 상기 계산 모드로부터 상기 통신 모드로 상기 다중 모드 이동 장치를 스위칭하도록 구성된 구성 모듈을 포함하며,

상기 다중 모드 이동 장치가 상기 계산 모드에 있는 경우에 상기 어플리케이션 프로세서는 마스터 프로세서로서 기능하고 상기 통신 프로세서는 주변 프로세서로서 기능하며 상기 다중 모드 이동 장치가 상기 통신 모드에 있는 경우에 상기 통신 프로세서가 상기 마스터 프로세서로서 기능할 수 있도록 하기 위하여 상기 어플리케이션 프로세서가 전원공급차단되며(deenergized),

상기 어플리케이션 프로세서는 프로세서 로컬 버스(PLB)와 연관되며, 상기 다중 모드 이동 장치는, 상기 다중 모드 이동 장치가 상기 통신 모드에 있는 경우에 상기 통신 프로세서가 상기 마스터 프로세서로서 기능할 수 있고 상기 다중 모드 이동 장치가 상기 계산 모드에 있는 경우에 상기 통신 프로세서가 주변 프로세서로서 기능할 수 있도록 구성된 PLB 브리지 프로세서를 추가로 포함하며,

상기 통신 프로세서는 하나 이상의 메모리 장치들과 통신하는 메모리 버스와 관련되며, 상기 PLB 브리지 프로세서는 상기 메모리 버스를 상기 PLB로 연결하도록 구성되는, 다중 모드 이동 장치.

### 청구항 32

제 31 항에 있어서,

상기 PLB에 연결된 터치 패널 제어기 및 저장 인터페이스 중 적어도 하나를 더 포함하는, 다중 모드 이동 장치.

### 청구항 33

제 32 항에 있어서,

상기 다중 모드 이동 장치가 상기 통신 모드에 있는 경우에 상기 통신 프로세서는 상기 터치 패널 제어기 및 저장 인터페이스 중 적어도 하나에 액세스하도록 추가로 구성되는, 다중 모드 이동 장치.

### 청구항 34

삭제

### 청구항 35

통신 모드와 계산 모드에서 다중 모드 이동 장치를 동작시키기 위한 방법으로서,

상기 계산 모드에서 적어도 하나의 개인 계산 어플리케이션을 어플리케이션 프로세서에 의해 실행하는 단계;

전화 번호의 적어도 일부의 사용자 입력에 응답하여 상기 계산 모드로부터 상기 통신 모드로 스위칭하는 단계;

상기 통신 모드에서 통신 프로세서로 무선 음성 및 데이터 통신을 용이하게 하는 단계를 포함하며,

상기 다중 모드 이동 장치가 상기 계산 모드에 있는 경우에 상기 어플리케이션 프로세서는 마스터 프로세서로서 기능하고 상기 통신 프로세서는 주변 프로세서로서 기능하며 상기 다중 모드 이동 장치가 상기 통신 모드에 있는 경우에 상기 통신 프로세서가 상기 마스터 프로세서로서 기능할 수 있도록 하기 위하여 상기 어플리케이션 프로세서가 전원공급차단되며,

상기 어플리케이션 프로세서는 프로세서 로컬 버스(PLB)와 연관되며, 상기 방법은, 상기 다중 모드 이동 장치가 상기 계산 모드에 있는 경우에 상기 어플리케이션 프로세서가 상기 마스터 프로세서로서 기능할 수 있고 상기 통신 프로세서가 주변 프로세서로서 기능할 수 있도록 PLB 브리지 프로세서를 이용하는 단계를 추가로 포함하며,

상기 통신 프로세서는 하나 이상의 메모리 장치들과 통신하는 메모리 버스와 관련되며, 상기 방법은 상기 메모리 버스를 상기 PLB로 연결하도록 상기 PLB 브리지 프로세서를 이용하는 단계를 추가로 포함하는, 다중 모드 이동 장치를 동작시키기 위한 방법.

### 청구항 36

제 35 항에 있어서,

터치 패널 제어기 및 저장 인터페이스 중 적어도 하나가 상기 PLB에 연결되는, 다중 모드 이동 장치를 동작시키기 위한 방법.

### 청구항 37

제 36 항에 있어서,

상기 다중 모드 이동 장치가 상기 통신 모드에 있는 경우에 상기 터치 패널 제어기 및 저장 인터페이스 중 적어도 하나에 액세스하도록 상기 통신 프로세서를 이용하는 단계를 추가로 포함하는, 다중 모드 이동 장치를 동작시키기 위한 방법.

### 청구항 38

삭제

### 청구항 39

통신 모드와 계산 모드 간에 스위칭하도록 구성된 다중 모드 이동 장치로서,

상기 다중 모드 이동 장치가 상기 계산 모드에 있는 경우에 적어도 하나의 개인 계산 어플리케이션을 실행하기 위한 어플리케이션 프로세싱 수단;

상기 다중 모드 이동 장치가 상기 통신 모드에 있는 경우에 무선 음성 및 데이터 통신을 용이하게 하기 위한 통신 프로세싱 수단;

전화 번호의 적어도 일부의 사용자 입력에 응답하여 상기 계산 모드로부터 상기 통신 모드로 상기 다중 모드 이동 장치를 스위칭하기 위한 수단을 포함하며,

상기 다중 모드 이동 장치가 상기 계산 모드에 있는 경우에 상기 어플리케이션 프로세싱 수단은 마스터 프로세서로서 기능하고 상기 통신 프로세싱 수단은 주변 프로세서로서 기능하며 상기 다중 모드 이동 장치가 상기 통신 모드에 있는 경우에 상기 통신 프로세싱 수단이 상기 마스터 프로세서로서 기능할 수 있도록 하기 위하여 상기 어플리케이션 프로세싱 수단이 전원공급차단되며,

상기 어플리케이션 프로세싱 수단은 프로세서 로컬 버스(PLB)와 연관되며, 상기 다중 모드 이동 장치는, 상기 다중 모드 이동 장치가 상기 계산 모드에 있는 경우에 상기 어플리케이션 프로세싱 수단이 상기 마스터 프로세서로서 기능할 수 있고 상기 통신 프로세싱 수단이 주변 프로세서로서 기능할 수 있도록 하기 위한 PLB 브리지 프로세싱 수단을 추가로 포함하며,

상기 통신 프로세싱 수단은 하나 이상의 메모리 장치들과 통신하는 메모리 버스와 관련되며, 상기 PLB 브리지 프로세싱 수단은 상기 메모리 버스를 상기 PLB로 연결하기 위한 수단을 포함하는, 다중 모드 이동 장치.

### 청구항 40

제 39 항에 있어서,

상기 PLB에 연결된 터치 패널 제어기 및 저장 인터페이스 중 적어도 하나를 더 포함하는, 다중 모드 이동 장치.

### 청구항 41

제 40 항에 있어서,

상기 통신 프로세싱 수단은 상기 다중 모드 이동 장치가 상기 통신 모드에 있는 경우에 상기 터치 패널 제어기 및 저장 인터페이스 중 적어도 하나에 액세스하기 위한 수단을 포함하는, 다중 모드 이동 장치.

### 청구항 42

삭제

## 명세서

## 기술 분야

[0001]

본 발명은 일반적으로 보조 컴퓨터 기능들을 또한 수행하는 무선 전화기들과 같은 다중 모드 장치들에 관한 것이다.

## 배경 기술

[0002]

여러 성능들을 갖는 다중 모드 이동 컴퓨팅 장치들이 제안되어 왔다. 예컨대, 이동 전화기는 현재 노트북 컴퓨터들에 의해 수행되는 개인 컴퓨팅 작업들 외에도 그것들의 통신 기능들을 수행할 것으로 기대될 수 있다.

[0003]

본 명세서에서 인지되는 바와 같이, 다중 동작 모드들을 지원하기 위해서 다중 프로세서들이 필요할 수 있다. 본 명세서에서 또한 인지되는 바와 같이, 동작 모드에 상관없이 동일한 내부 동작을 사용하는 것은 메인 프로세서가 통상적으로 주변 장치들을 제어하면서 또한 다른 장치 프로세서들(예컨대, 전화 모뎀 프로세서)을 주변 장치들로서 처리하는 마스터 장치로서 가능하다는 것을 의미한다. 이러한 설계는 예컨대 메인 프로세서가 전화 모드에서 활성될 필요가 있는 것을 포함해서 메인 프로세서가 모든 모드들에서 활성되어야 하는 것을 필요로 하고, 여기서 모뎀 프로세서는 메인 프로세서에 의해서 제어되는 장치 하드웨어(예컨대, 데이터 디스플레이, 비휘발성 저장부, 오디오 입/출력부)로의 모뎀 프로세서 액세스를 간단히 제공하기 위해 활성된다. 즉, 메인 프로세서는 여기서 모뎀 프로세서를 대신해서 간단히 중재하고 있는데, 그 이유는 하드웨어 구조가 모뎀 프로세서로 하여금 장치의 하드웨어 자원들 중 일부에 직접 액세스하도록 허용하지 않기 때문이다.

[0004]

본 명세서에서 알 수 있는 바와 같이, (위의 예에서 메인 프로세서와 같은)하드웨어 중재기의 사용을 가능한 경우 최소로 함으로써 작업의 전력 효율적인 실행을 가능하게 하여 배터리를 보존하는 것이 유리할 것이다. 또한, 본 발명에서 설명되는 방법들을 사용함으로써, 장치의 배터리 수명을 더욱 연장시키는 이러한 중재자 역할을 제공할 필요가 없는 절차들의 전력을 차단하는 것이 가능할 수 있다. 게다가, 단일 메인 프로세서가 항상 장치 마스터로서 기능하는 것을 필요로 하는 것은 모뎀 프로세서에만 적용할 수 있는 소프트웨어 및 소프트웨어 변경들이 조정되어야 하거나 그렇지 않으면 또한 메인 프로세서와 통합되어야 함으로써 소프트웨어 관리를 복잡하게 한다는 것을 의미한다. 특히, 모뎀 프로세서 상에서 기능하는 셀룰러 전화기 타입 장치들을 위해 현재 이용가능한 소프트웨어의 큰 베이스는 메인 애플리케이션 프로세서에 대한 주변장치이다. 본 발명은 하드웨어를 설계함으로써 애플리케이션 소프트웨어의 이러한 큰 베이스 레거시(base legacy)의 재사용을 가능하게 할 수 있고, 그로 인해 레거시 소프트웨어가 현재의 단일 프로세서 장치 내에 있는 것으로 보인다.

## 발명의 상세한 설명

[0005]

다중 모드 이동 장치는 배터리를 포함하고 있는 하우징과, 상기 장치를 사용하여 무선 통신을 용이하도록 구성되는 모듈에 구현될 수 있는 통신 프로세서를 포함한다. 상기 통신 프로세서 모듈은 하우징 상에 제공되며 배터리에 의해서 전력이 제공된다. 모듈 내에 구현될 수 있는 애플리케이션 프로세서는 애플리케이션들을 실행하도록 구성되고, 하우징 상에 또한 제공되며 배터리에 의해 전력이 제공된다. 본 명세서에서의 모듈은 이산적인 성분들이 어셈블링되거나 또는 하드웨어 성분들의 조정된 사용을 통해 기능을 수행하는 집적 회로 패키지 내에 어셈블링되는 하드웨어의 컬렉션(collection)을 의미한다. 특히, 통신 프로세서 모듈은 통신 프로세서 코어 이외에도 그 통신 프로세서(예컨대, ARM 프로세서 코어가 현재 계획 중에 있는 통신 프로세서 모듈들(view communications processor module) 내에 있는 웰컴사의 MSM 3300, 5100, 5500)의 주변 장치들로서 기능하는 다른 하드웨어 자원들로 구성된다. 마찬가지로, 현재 계획 중에 있는 애플리케이션 프로세서 모듈은 보조용 하드웨어(예컨대, ARM 및 PowerPC를 갖는 웰컴사의 MSP1000 또는 IBM의 405GP는 애플리케이션 프로세서 모듈들의 일 예들임)와 함께 애플리케이션 프로세서 코어로 구성된다. 이러한 양상에 따르면, 장치는 통신 모드 및 계산 모드를 가지며, 장치가 통신 모드에 있을 때는, 애플리케이션 프로세서의 코어에 전력이 차단된다. 그러나, 애플리케이션 프로세서 코어는 장치가 통신 모드에 있을 때 전력이 공급된다.

[0006]

바람직하게, 통신 프로세서 모듈은 하나 이상의 메모리 장치들과 통신하는 메모리 버스와 연관되며, 애플리케이션 프로세서 모듈은 프로세서 로컬 버스(PLB)와 연관된다. 바람직한 메모리 버스는 통신 프로세서 모듈과 애플리케이션 프로세서 모듈사이의 하드웨어 인터페이스를 통해 PLB와 통신한다. 더 상세하게는, 바람직한 메모리 버스는 PLB 브릿지 프로세서와 통신함으로써, PLB의 마스터로서 통신 프로세서가 기능하는 것을 용이하게 한다. 그로 인해, 통신 프로세서는 PLB와 연관된 주변 하드웨어에 액세스할 수 있다.

[0007]

또 다른 양상에서는, 다중 모듈 이동 장치가 배터리를 포함하고 있는 하우징과, 상기 장치를 사용하여 무선 통신을 용이하게 하도록 구성되는 통신 프로세서를 포함한다. 통신 프로세서는 하우징 상에 제공되며, 배터리에

의해서 전력이 제공된다. 애플리케이션 프로세서는 애플리케이션을 실행하도록 구성되고, 하우징 상에 제공되며 배터리에 의해서 전력이 제공된다. 상기 장치는 적어도 통신 모드와 계산 모드를 가지며, 상기 장치가 통신 모드에 있을 때는, 통신 프로세서가 마스터 프로세서로서 기능한다.

[0008] 또 다른 양상에서는, 이동 계산을 실행하는 방법이 애플리케이션 프로세서와 통신 프로세서를 하우징 내에 제공하는 단계를 포함한다. 상기 방법은 또한 동작 모드에 기초하여 프로세서들 중 하나를 마스터 프로세서로서 선택적으로 설정하는 단계를 포함한다.

[0009] 본 발명의 상세한 설명은, 그 구조 및 동작 모두에 대해서, 첨부한 도면들을 참조함으로써 가장 잘 이해될 수 있고, 도면들에서는 동일한 번호가 동일한 부분을 나타낸다.

[0010] 비록 본 발명의 설명은 독특한 통신 및 애플리케이션 프로세서 모듈들과 관련하여 제공되지만, 이는 설명의 명확성을 위해서만 이루어졌다는 것을 알게 된다. 특히, 통신 및 애플리케이션 프로세서 모듈들이 동일한 접촉 회로 모듈 상에서 구현될 수 있다는 것이 상상되는데, 그것이 다중-칩-모듈 패키징 기술을 통해서 이루어지는지 또는 그 위에 (애플리케이션 및 통신) 프로세서 코어들 모두를 갖는 단일 칩으로서 전체 회로를 설계함으로써 이루어지는지에 상관없다.

### 실시예

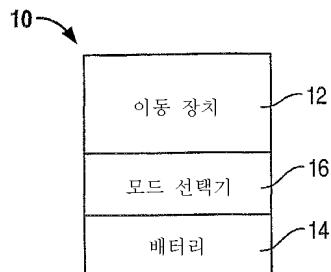

[0014] 처음으로 도 1을 참조하며, 이동 다중 모드 계산 유닛이 도시되어 있는데, 일반적으로 참조번호 10으로 지정되어 있다. 예시적인 비제한적 실시예에서는, 장치(10)는 무선 음성 및/또는 데이터 통신뿐만 아니라 워드 프로세싱(그러나 이것으로 제한되지는 않음)과 같은 개인용 계산 애플리케이션-기반 기능들을 수행하는데 사용될 수 있다. 여하튼, 장치(10)는 본 명세서에서 설명되는 성분들을 보유하면서 바람직하게는 무게가 가벼운 휴대용 하우징(12)을 구비한다. 배터리(14)는 하우징(12)과 연결됨으로써 아래에 설명되는 성분들에 전력 소스를 제공한다. 배터리(14)는 바람직하게 해당 분야에 공지되어 있는 휴대용 계산 원리에 따라 재충전가능하지만, 장치(10)가 전기적인 배출구에 접속되어 있지 않을 때는, 배터리(14)가 장치(10)의 성분들에 대해 유일한 전력 소스이다.

[0015] 모드 선택기(16)가 하우징(12) 상에 제공될 수 있다. 모드 선택기(16)는 예컨대 통신 또는 계산 모드와 같은 장치(10)의 동작 모드를 선택하기 위해서 사용자-조종가능한 입력 장치일 수 있다. 모드 선택기(16)는 여러 방식으로 구현될 수 있는데, 예컨대 그것은 스위치, 모드를 선택하기 위해 적절한 소프트웨어와 연계하여 사용되는 터치스크린 디스플레이의 일부, 또는 다른 등가의 입력 구조일 수 있다. 또는, 모드 선택기(16)는 사용자의 활성동작에 응하여 소프트웨어에 의해서 자동적으로 구현될 수 있는데, 예컨대 만약 사용자가 번호를 다이얼링하기 시작하면, 모드 선택기는 통신 모드에서 자동으로 장치(10)를 구성하는 소프트웨어일 수 있다.

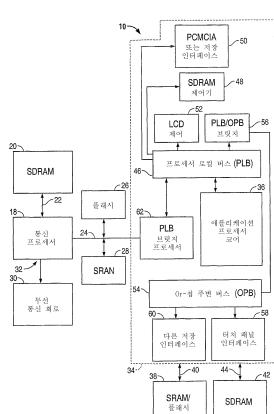

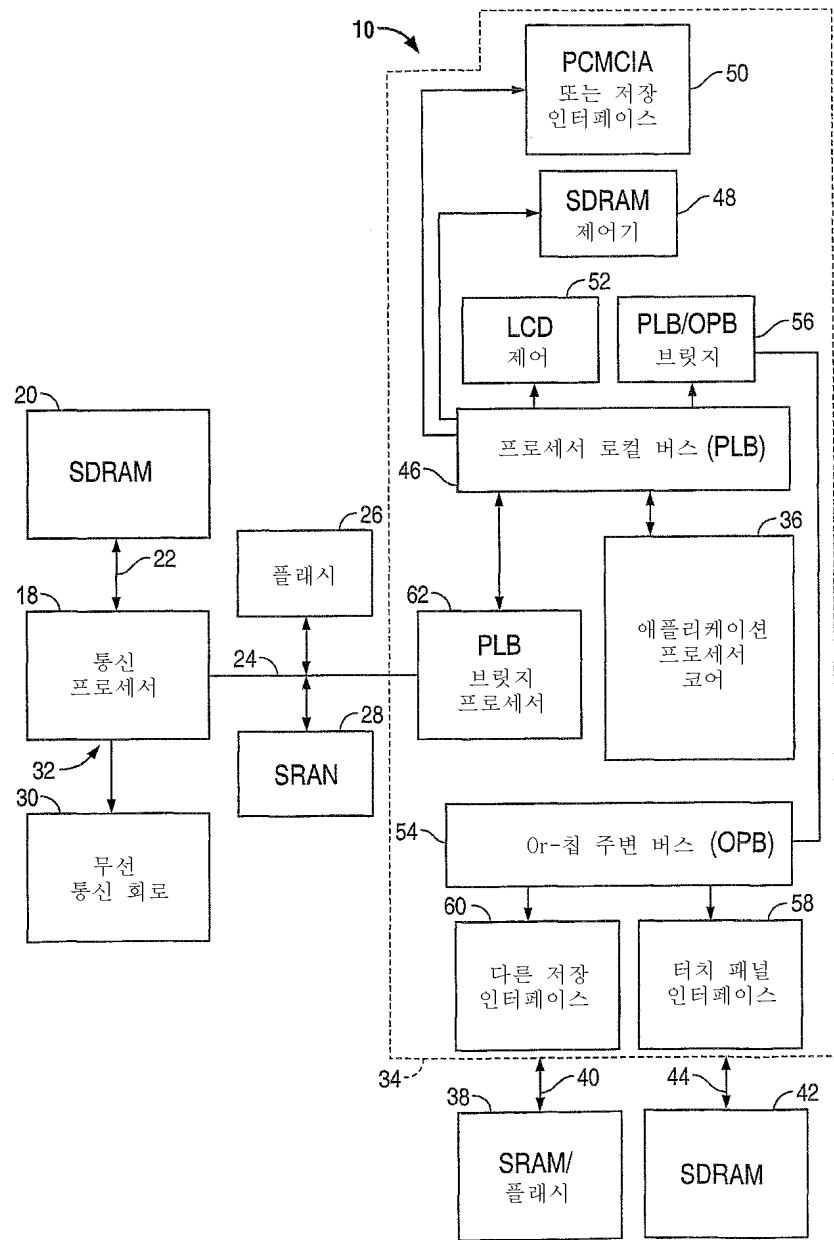

[0016] 이제 도 2를 참조하면, 장치(10)는 통신 프로세서(18), 바람직하게는 예컨대 16/32 비트 버스(22)를 통해 동기 다이내믹 랜덤 액세스 메모리(SDRAM)(20)에 접속할 수 있으며 통신 프로세서 모듈에서 구현될 수 있는 이동 시스템 모뎀(MSM)으로 지칭되는 타입의 프로세서를 구비한다. 또한, 통신 프로세서(18)는 예컨대 16 비트 메모리 인터페이스 버스(24), MSM 플래시 메모리(26) 및 MSM 정적 랜덤 액세스 메모리(SRAM)(28)를 사용하여 액세스할 수 있다. 본 발명의 양수인의 "BREW" 애플리케이션들과 같은 통신-관련 애플리케이션들은 통신 프로세서(18)에 의한 그것의 실행을 위해서 하나 이상의 메모리(20, 26, 28)에 저장될 수 있다.

[0017] 도 2에 또한 도시된 바와 같이, 통신 프로세서(18)는 해당 분야에 알려진 방법에 따라 무선 통신을 실행하기 위해서 무선 통신 회로(30)를 액세스한다. 즉, 메모리(20, 26, 및 28)와 연관된 통신 프로세서(18) 및 회로(30)가 통상 참조번호 32로 지정된 무선 음성 및/또는 데이터 통신 부분을 형성한다.

[0018] 비제한적인 일실시예에서, "이동국(MS)"으로도 지칭되는 통신부(32)는 Kyocera, Samsung, 또는 다른 제조사에서 만들어진 이동 전화 타입의 장치인데, 상기 장치는, 비록 본 발명이 임의의 무선 통신 장치에 대해 적용되더라도, 무선 인프라구조와 통신하기 위해 IS-95, IS-95B, WCDMA, IS-2000, 및 다른 것들(그러나 이러한 것들로 제한되지 않음)에서 정의된 것과 같은 코드 분할 다중 액세스(CDMA) 원리들 및 CDMA OTA(over-the-air) 통신 무선 인터페이스 프로토콜들을 사용한다.

[0019] 이를테면, 본 발명이 적용될 수 있는 무선 통신 시스템들은, 위에서 설명된 것 외에도, AMPS(Advanced Mobile Phone System) 및 다음의 디지털 시스템들과 같은 GSM, PCS(Personal Communications Service) 및 셀룰러 시스템들을 포함한다: CDMA, TDMA, 및 TDMA와 CDMA 기술들 모두를 사용하는 하이브리드 시스템들. CDMA 셀룰러 시스템은 TIA/EIA(Telecommunications Industry Association/Electronic Industries Association) 표준

IS-95에 설명되어 있다. 결합된 AMPS 및 CDMA 시스템들은 TIA/EIA 표준 IS-95에 설명되어 있다. 다른 통신 시스템들은 광대역 CDMA(WCDMA), cdma2000(예컨대, cdma2000 1x 또는 3x 표준) 또는 TD-SCDMA로 지정되는 것을 커버하는 International Mobile Telecommunication System 2000/Universal Mobile Telecommunication Systems(IMT-2000/UM) 표준에 설명되어 있다.

[0020] 도 2를 또한 참조하면, 모듈에 구현될 수 있는 메인 프로세서(34)는 애플리케이션 프로세서 코어(36)를 보유하는데, 상기 애플리케이션 프로세서 코어(36)는 비제한적인 일실시예에서 IBM 405 LP 프로세서이거나 그와 같은 것일 수 있다. 비록 도 2에서는 프로세서들(18, 36)이 서로 개별적인 칩들 상에 위치할 수 있지만, 그것들은 동일한 칩 상에도 배치될 수 있다는 것을 알 것이다.

[0021] 애플리케이션 프로세서 코어(36)는 애플리케이션들을 실행하기 위해서 여러 메모리에 저장될 수 있는 하나 이상의 소프트웨어 애플리케이션을 액세스한다. 예컨대, 애플리케이션 프로세서 코어(36)는 16-비트 메모리 버스(40)를 통해 SRAM/플래시 메모리(38)에 액세스할 수 있고, 그것은 또한 바람직하게 32-비트 버스(44)를 통해 SDRAM 메모리(42)(여기서 소프트웨어 애플리케이션들이 통상적으로 우선순위에 따라 저장될 것이다)에 액세스할 수 있다.

[0022] 도 2는 애플리케이션 프로세서 코어(36)가 프로세서 로컬 버스(PLB)(46)에 액세스하는 것을 또한 나타낸다. 비제한적인 일실시예에서, PLB 버스(46)는 64-비트 버스일 수 있다. 다양한 지원 장치들 및 주변 장치들이 해당 분야에 공지되어 있는 원리들에 따라 PLB(46)를 사용하여 애플리케이션 프로세서 코어(36)에 의해 접속된다. 예컨대, PLB(46)(그리고, 그에 따른 애플리케이션 프로세서 코어(36))가 SDRAM 메모리(42)를 제어하기 위한 SDRAM 제어기(48)에 접속될 수 있다. 또한, PLB(46)는 개인용 컴퓨터 메모리 카드 인터페이스 구조(PCMCIA) 인터페이스나 다른 저장 인터페이스(50)와 통신할 수 있다. 게다가, PLB(46)(그리고, 그에 따른 애플리케이션 프로세서 코어(36))가 액정 디스플레이(LCD) 제어기(52)에 접속될 수 있고, 상기 LCD 제어기(52)는 장치(10)의 하우징 상에 제공될 수 있는 LCD 디스플레이를 구동시킨다.

[0023] 위에서 설명된 성분들 외에도, 애플리케이션 프로세서 코어(36)를 포함하고 있는 애플리케이션 프로세서(34)가 비제한적인 일실시예에서 32 비트 버스일 수 있는 온-칩 주변 장치(OPB)(54)를 또한 구비할 수 있다. OPB(54)는 PLB/OPB 브릿지 장치(56)를 통해 PLB(46)에 접속된다. 브릿지 장치(56)는 32 비트 데이터를 64 비트 데이터로 변환하고 또한 그 반대로 변환할 수 있다. 여러 주변 장치들이 OPB(54)와 통신할 수 있다. 비제한적인 예들을 통해서, 터치 패널 인터페이스(58)는 OPB(54)에 접속될 수 있다. 또한, 다른 저장 인터페이스들(60)이 OPB(54)에 접속될 수 있다. OPB(54)에 접속될 수 있는 주변 장치들에 대한 비제한적인 예들로는 USB, UART, 인터럽트(UC), 및 AC97 장치가 있다.

[0024] 본 발명에 따르면, 통신 프로세서(18)는 또한 그것의 메모리 인터페이스(24)를 통해 PLB(46)와 통신할 수 있다. 특히, 도 2에 도시된 바와 같이, 예시적인 일실시예에서는, 통신 프로세서(18)의 메모리 인터페이스(24)가 PLB 브릿지 프로세서(62)에 의해서 PLB(46)에 접속된다. 한 구현에 있어서, PLB 브릿지 프로세서(62)는 예컨대 프로세서와 같은 논리 장치에 의해서 하드웨어로 구현된다. 이러한 방식으로, 통신 프로세서(18)는 PLB(46)에 연결된 장치에 액세스할 수 있다. 원한다면, PLB 브릿지 프로세서(62)의 기능들은 예컨대 통신 프로세서(18)의 전용 부분을 통해 구현될 수 있다.

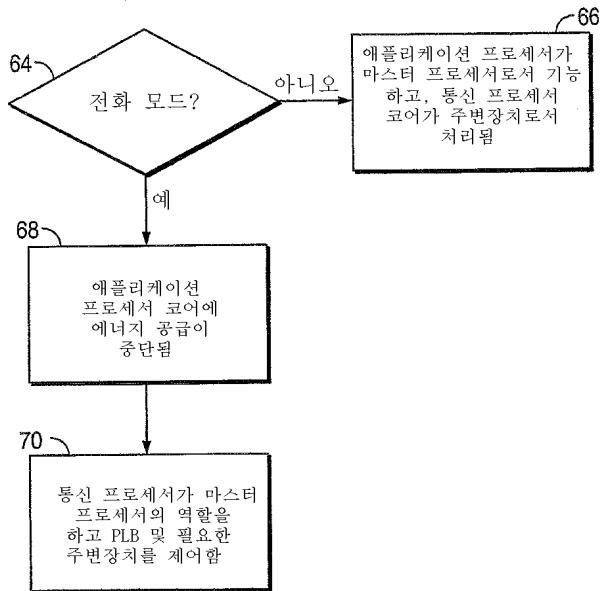

[0025] 도 3은 어떤 프로세서(18, 36)가 도 2에 도시된 주변 장치들을 제어하는지를 협상하기 위해서 PLB 브릿지 프로세서(62)에 의해서 실행되는 논리를 나타낸다. 결정 블록(64)에서는, 장치(10)가 예컨대 모드 선택기(16)나 위에서 설명된 사용자 활성 동작에 의해서 제시될 때 통신 모드 상태에 있는지 여부가 결정된다. 만약 그렇지 않고 장치(10)가 계산 모드 상태에 있다는 것을 나타내면, 논리는 블록(66)으로 진행하고, 상기 블록(66)에서는 PLB 브릿지 프로세서(62)가 PLB(46) 및 OPB(54)의 제어 하에서 애플리케이션 프로세서 코어(36)가 마스터 프로세서로 되도록 지정한다. 이러한 모드에서, 통신 프로세서(18)는 애플리케이션 프로세서 코어(36)에 의해서 주변 장치로서 취급된다.

[0026] 다른 한편으로, 만약 장치(10)가 통신 모드 상태에 있다면, 논리는 결정 블록(64)으로부터 블록(68)으로 이동하는데, 상기 블록(68)에서는 적어도 애플리케이션 프로세서(34)의 애플리케이션 프로세서 코어(36)에 에너지 공급이 중단된다. 즉, 통신 모드에서는, 본 발명의 원리들에 따라, 애플리케이션 프로세서(36)에 에너지 공급이 중단된다. 따라서, 통신 프로세서(18)는 블록(70)에서 마스터 프로세서의 역할이 할당되어(예컨대, PLB 브릿지 프로세서(62)에 의해), PLB(46) 및 OPB(54)에 연결된 주변 장치들을 제어한다.

[0027] 비록 본 명세서에서 제시되고 상세히 설명되어진 특정 LOW POWER DUAL PROCESSOR ARCHITECTURE FOR MULTI MODE

DEVICES가 본 발명의 상술된 목적들을 완전히 획득할 수 있지만, 그것은 본 발명의 현재 바람직한 실시예이며 따라서 본 발명에 의해 넓게 고려되는 요지를 나타내고, 본 발명의 범위가 당업자에게 자명해질 수 있는 다른 실시예들을 완전히 포함하며, 본 발명의 범위는 그에 따라서 첨부된 청구항들 이외의 어떤 것에 의해서도 제한되지 않을 것이며, 청구항들에서 단수로 표현된 엘리먼트의 참조가 단수라고 명확히 설명되지 않는 한 "꼭 하나"인 것을 의미하는 것으로 의도되지 않고 "하나 이상"인 것을 의미한다는 것을 알아야 한다. 당업자가 인지하고 있거나 나중에 인지하게 될 상술된 바람직한 실시예의 엘리먼트들과 구조 및 기능적으로 유사한 모든 엘리먼트들은 본 명세서에서 참조로서 명백히 포함되며 본 청구항들에 의해 포함되도록 의도된다. 게다가, 장치나 방법은 본 발명에 의해 해결될 각각의 그리고 모든 문제를 처리하는 것이 필요하지 않고, 그것은 본 청구항들에 의해 포함된다. 또한, 본 명세서의 어떠한 엘리먼트, 성분, 또는 방법의 단계도 상기 엘리먼트, 성분, 또는 방법의 단계가 청구항들에서 명백히 언급되는 것에 상관없이 공중에게 사용되도록 의도된다. 어떤 청구항의 엘리먼트도, 상기 엘리먼트가 "~하기 위한 수단"이란 어구를 사용하여 명백히 언급되거나 방법 청구항의 경우에 상기 엘리먼트가 "동작" 대신에 "단계"로 언급되지 않더라고, 35 U.S.C. '112, 제 6 패러그라프 하에서 해석되지 않을 것이다.

### 도면의 간단한 설명

[0011] 도 1은 바람직한 비-제한적인 다중 모드 이동 계산 장치의 개략도.

[0012] 도 2는 본 다중 모드 이동 장치 구조의 바람직한 비제한적인 구현의 블록도.

[0013] 도 3은 본 발명의 논리를 나타내는 흐름도.

### 도면

#### 도면1

## 도면2

## 도면3