(12)发明专利申请

(10)申请公布号 CN 110324019 A

(43)申请公布日 2019.10.11

(21)申请号 201910217433.5

(22)申请日 2019.03.21

(30)优先权数据

62/649,339 2018.03.28 US

16/287,277 2019.02.27 US

(71)申请人 QORVO美国公司

地址 美国北卡罗莱纳州

(72)发明人 苏珊·克罗伊策

(74)专利代理机构 北京康信知识产权代理有限公司

11240

代理人 王红艳

(51)Int.Cl.

H03H 9/02(2006.01)

权利要求书2页 说明书5页 附图7页

(54)发明名称

具有嵌入式边界环的耦合谐振器滤波器

(57)摘要

一种具有嵌入式边界环的耦合谐振器滤波器，包括第一谐振器、第二谐振器、一个或多个中间层、第一边界环和第二边界环。所述第一谐振器包括第一压电层和与所述第一压电层接触的第一电极。所述第二谐振器包括第二压电层和与所述第二压电层接触的第二电极。所述一个或多个中间层位于所述第一谐振器与所述第二谐振器之间并且以声学方式将所述第一谐振器与所述第二谐振器耦合。所述第一边界环位于所述第一电极上。所述第二边界环位于所述第二电极上。通过提供所述第一边界环和所述第二边界环两者可抑制所述耦合谐振器滤波器中的寄生模式，从而改善其性能。

1. 一种耦合谐振器滤波器(CRF),包括:

- 第一谐振器,所述第一谐振器包括第一压电层和与所述第一压电层接触的第一电极;

- 第二谐振器,所述第二谐振器包括第二压电层和与所述第二压电层接触的第二电极;

- 一个或多个中间层,所述中间层在所述第一谐振器与所述第二谐振器之间,所述一个或多个中间层以声学方式将所述第一谐振器与所述第二谐振器耦合;

- 第一边界环,所述第一边界环位于所述第一电极上;以及

- 第二边界环,所述第二边界环位于所述第二电极上。

2. 如权利要求1所述的CRF,其中所述第一谐振器和所述第二谐振器是体声波(BAW)谐振器。

3. 如权利要求2所述的CRF,其中所述第一电极形成所述CRF的顶部表面。

4. 如权利要求3所述的CRF,其中所述第二压电层位于所述第二电极与所述第一谐振器之间。

5. 如权利要求4所述的CRF,还包括位于所述第二谐振器与所述CRF的底部表面之间的一个或多个附加中间层。

6. 如权利要求3所述的CRF,其中所述第二电极位于所述第二压电层与所述第一谐振器之间。

7. 如权利要求1所述的CRF,还包括位于所述第一压电层上的第一附加电极,使得所述第一压电层位于所述第一电极与所述第一附加电极之间。

8. 如权利要求7所述的CRF,还包括在所述第二压电层上的第二附加电极,使得所述第二压电层位于所述第二电极与所述第二附加电极之间。

9. 如权利要求1所述的CRF,其中所述第二压电层位于所述第二电极与所述第一谐振器之间。

10. 如权利要求1所述的CRF,其中所述第二电极位于所述第二压电层与所述第一谐振器之间。

11. 如权利要求1所述的CRF,其中所述第一边界环沿着所述CRF的有效区域的外侧边缘设置。

12. 如权利要求11所述的CRF,其中所述第二边界环沿着所述CRF的所述有效区域的外侧边缘设置。

13. 一种耦合谐振器滤波器(CRF),包括:

- 第一谐振器,所述第一谐振器包括第一压电层和与所述第一压电层接触的第一电极;

- 第二谐振器,所述第二谐振器包括第二压电层和与所述第二压电层接触的第二电极;

- 一个或多个中间层,所述一个或多个中间层位于所述第一谐振器与所述第二谐振器之间,所述一个或多个中间层以声学方式将所述第一谐振器与所述第二谐振器耦合;

- 第一边界环,所述第一边界环位于所述第一电极上;以及

- 第二边界环,所述第二边界环位于所述一个或多个中间层中的第一个上。

14. 如权利要求13所述的CRF,其中所述第一谐振器和所述第二谐振器是体声波(BAW)谐振器。

15. 如权利要求14所述的CRF,其中所述第一电极形成所述CRF的顶部表面。

16. 如权利要求15所述的CRF,其中所述一个或多个中间层中的至少一个位于所述一个或多个中间层中的第一个与所述第一谐振器之间。

17. 如权利要求13所述的CRF,还包括位于所述第二谐振器与所述CRF的底部表面之间的一个或多个附加中间层。

18. 如权利要求13所述的CRF,其中所述一个或多个中间层中的第一个是金属层。

19. 如权利要求13所述的CRF,其中所述第一边界环沿着所述CRF的有效区域的外侧边缘设置。

20. 如权利要求19所述的CRF,其中所述第二边界环沿着所述CRF的所述有效区域的外侧边缘设置。

## 具有嵌入式边界环的耦合谐振器滤波器

[0001] 相关申请

[0002] 本申请要求2018年3月28日提交的临时专利申请序列号62/649,339的权益，所述申请的公开内容特此以引用的方式并入本文。

### 技术领域

[0003] 本公开涉及耦合谐振器滤波器，并且更具体地涉及包括嵌入式边界环的耦合谐振器滤波器。

### 背景技术

[0004] 声波滤波器广泛应用于现代无线通信设备中。随着无线通信标准的持续发展并且包括带宽更窄且频率更高的更多通信频带，因此设计出满足这些标准的严格要求的声波滤波器变得日益困难。近年来，已经出现了耦合谐振器滤波器，其提供常规的表面声波和体声波滤波器先前无法实现的滤波能力。耦合谐振器滤波器通常提供比常规的表面声波和体声波滤波器对应物高的选择率，并且还可在更高的频率下操作。因此，正如持续发展的标准所要求的那样，耦合谐振器滤波器在高频窄信号频带内滤波信号的能力方面具有前景。然而，常规的耦合谐振器滤波器面临许多问题，这些问题通常存在于常规的表面声波和体声波滤波器中。例如，耦合谐振器滤波器可能包括降低其性能的寄生模式。虽然已经对常规的表面声波和体声波滤波器进行了若干设计变化以尽力抑制寄生模式，但是耦合谐振器滤波器的不同操作特性通常意味着这些设计变化不具有相同的效果。因此，耦合谐振器滤波器持续面临降低其性能的寄生模式。鉴于上述情况，需要寄生模式减少，并且因此性能有所改善的耦合谐振器滤波器。

### 发明内容

[0005] 在一个实施方案中，一种耦合谐振器滤波器包括第一谐振器、第二谐振器、一个或多个中间层、第一边界环和第二边界环。所述第一谐振器包括第一压电层和与所述第一压电层接触的第一电极。所述第二谐振器包括第二压电层和与所述第二压电层接触的第二电极。所述一个或多个中间层位于所述第一谐振器与所述第二谐振器之间并且以声学方式将所述第一谐振器与所述第二谐振器耦合。所述第一边界环位于所述第一电极上。所述第二边界环位于所述第二电极上。通过提供所述第一边界环和所述第二边界环两者可抑制所述耦合谐振器滤波器中的寄生模式，从而改善其性能。

[0006] 在一个实施方案中，一种耦合谐振器滤波器包括第一谐振器、第二谐振器、一个或多个中间层、第一边界环和第二边界环。所述第一谐振器包括第一压电层和与所述第一压电层接触的第一电极。所述第二谐振器包括第二压电层和与所述第二压电层接触的第二电极。所述一个或多个中间层位于所述第一谐振器与所述第二谐振器之间并且以声学方式将所述第一谐振器与所述第二谐振器耦合。所述第一边界环位于所述第一电极上。所述第二边界环位于所述一个或多个中间层中的第一个上。通过提供所述第一边界环和所述第二边

界环两者可抑制所述耦合谐振器滤波器中的寄生模式,从而改善其性能。

[0007] 本领域技术人员在结合附图阅读以下对优选实施方案的详细描述之后,将了解本公开的范围并且意识到本公开的另外的方面。

## 附图说明

[0008] 并入本说明书且形成本说明书的一部分的附图示出本公开的若干方面,并且连同描述内容一起用来解释本公开的原理。

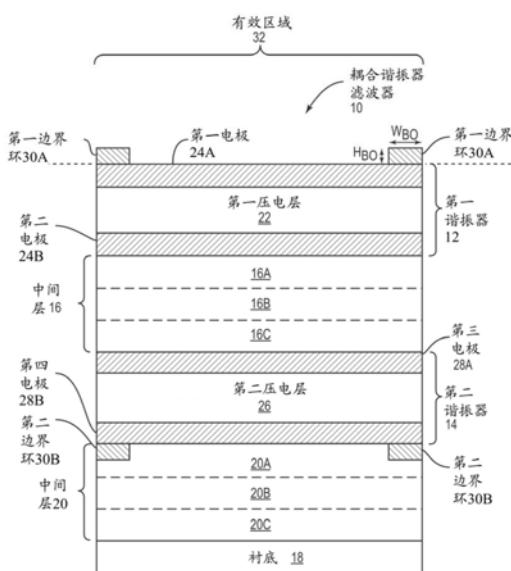

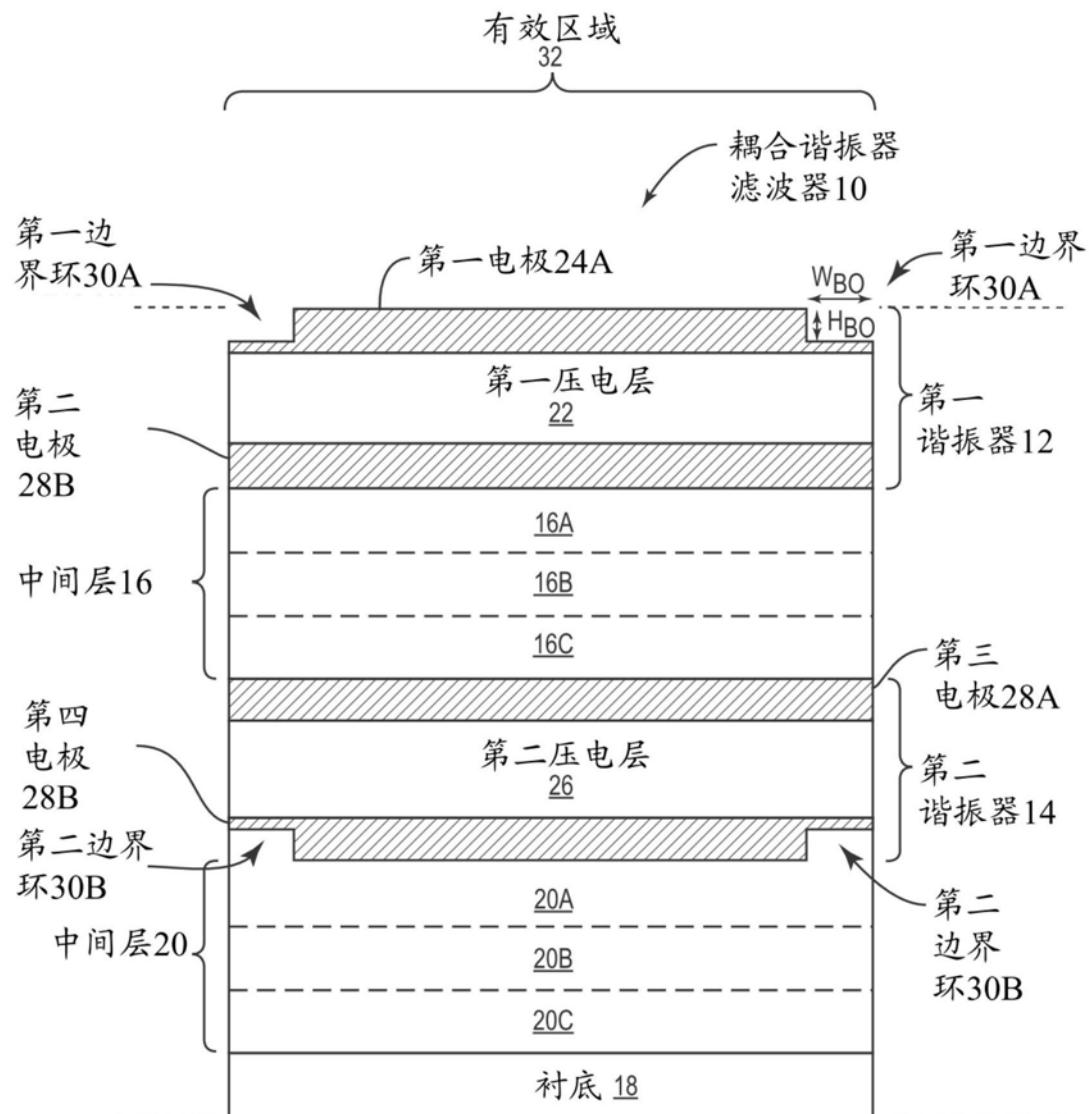

[0009] 图1示出根据本发明的一个实施方案的耦合谐振器滤波器的截面图。

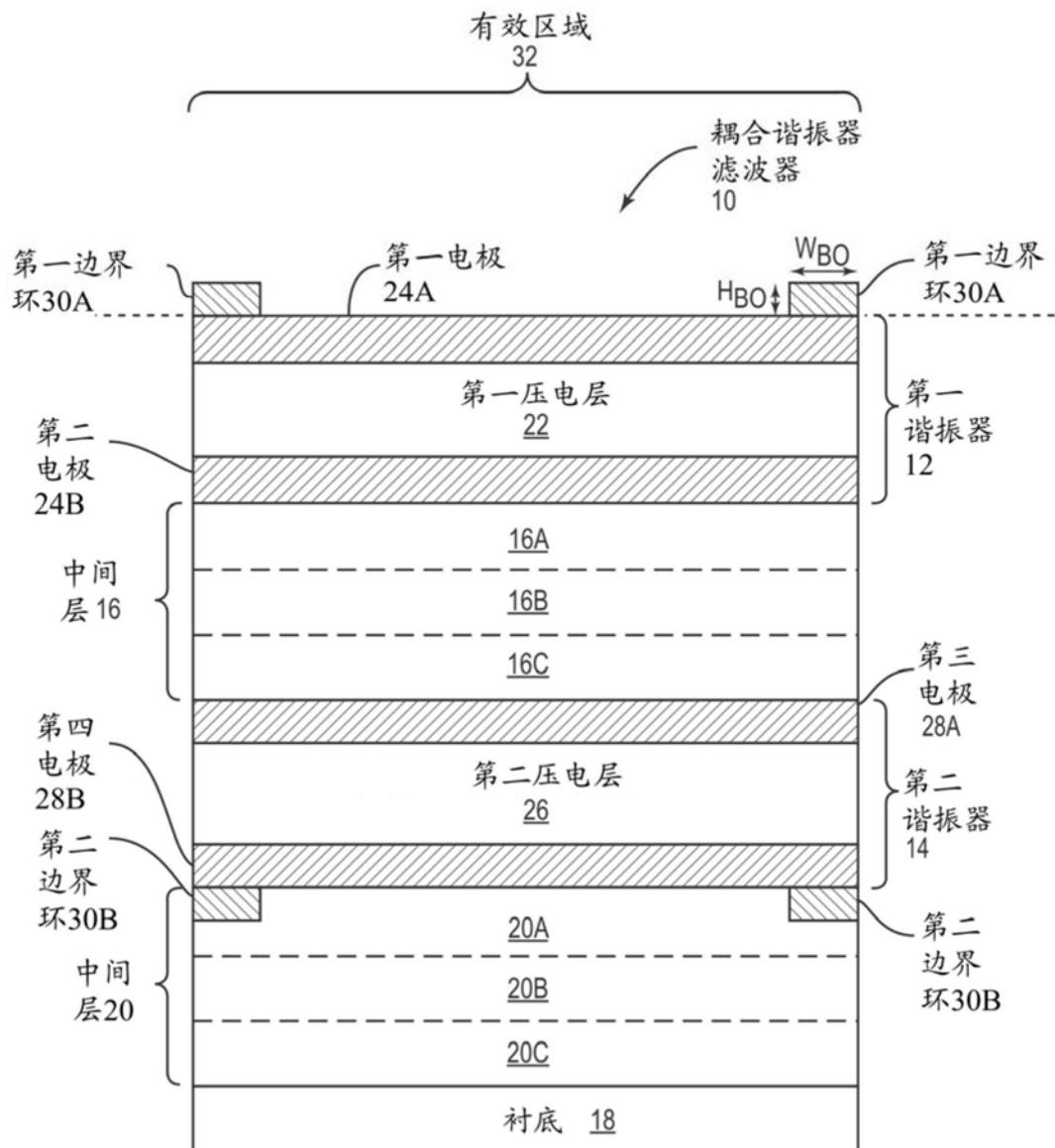

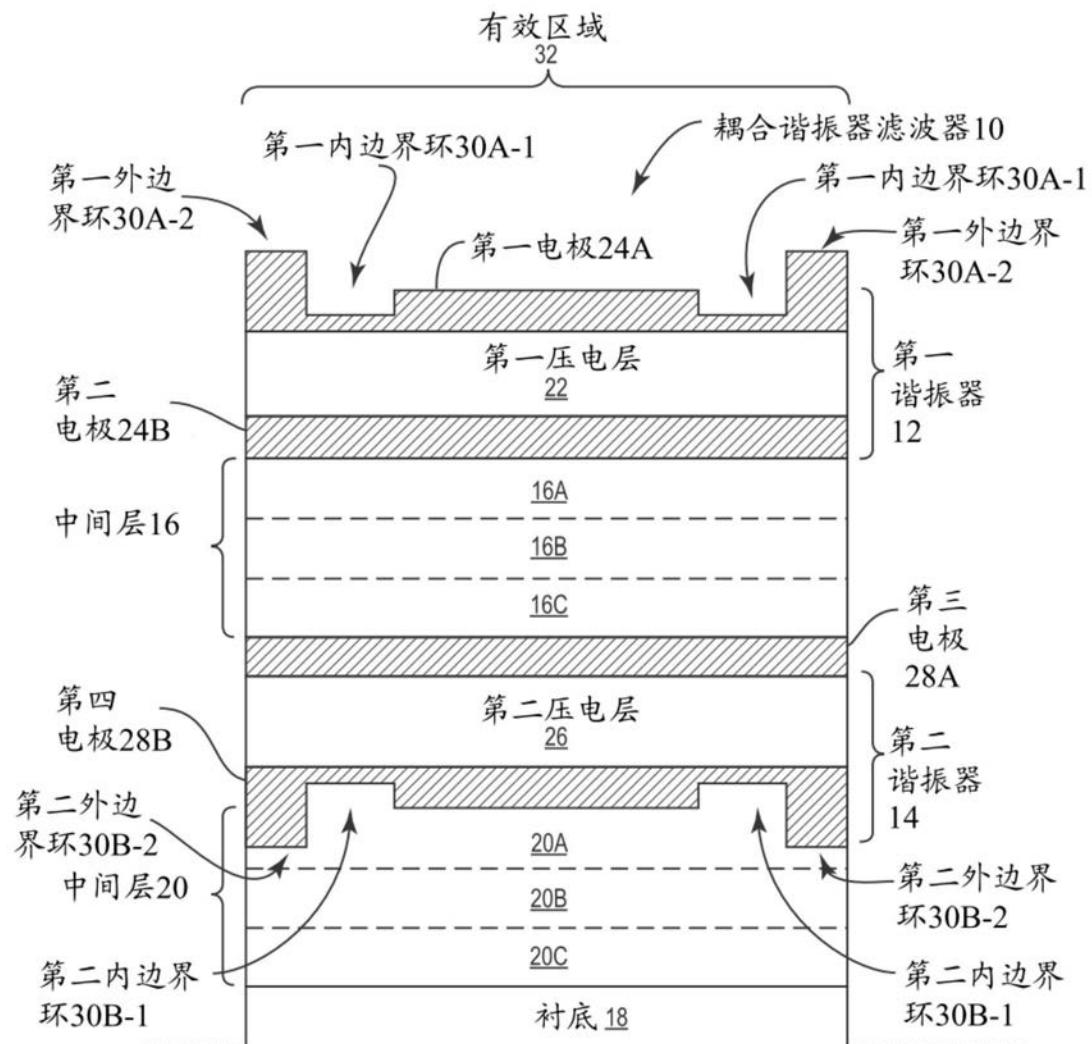

[0010] 图2示出根据本发明的一个实施方案的耦合谐振器滤波器的截面图。

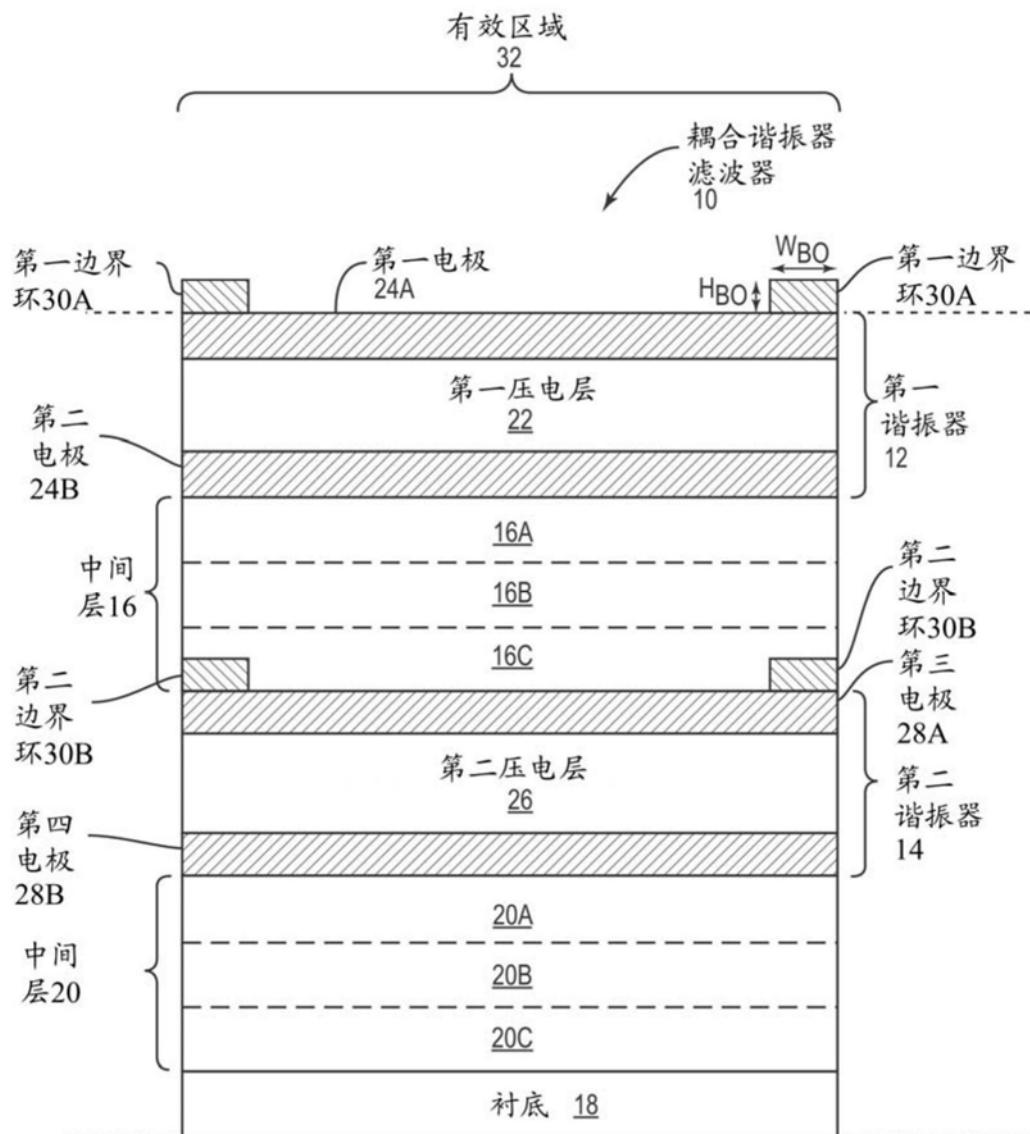

[0011] 图3示出根据本发明的一个实施方案的耦合谐振器滤波器的截面图。

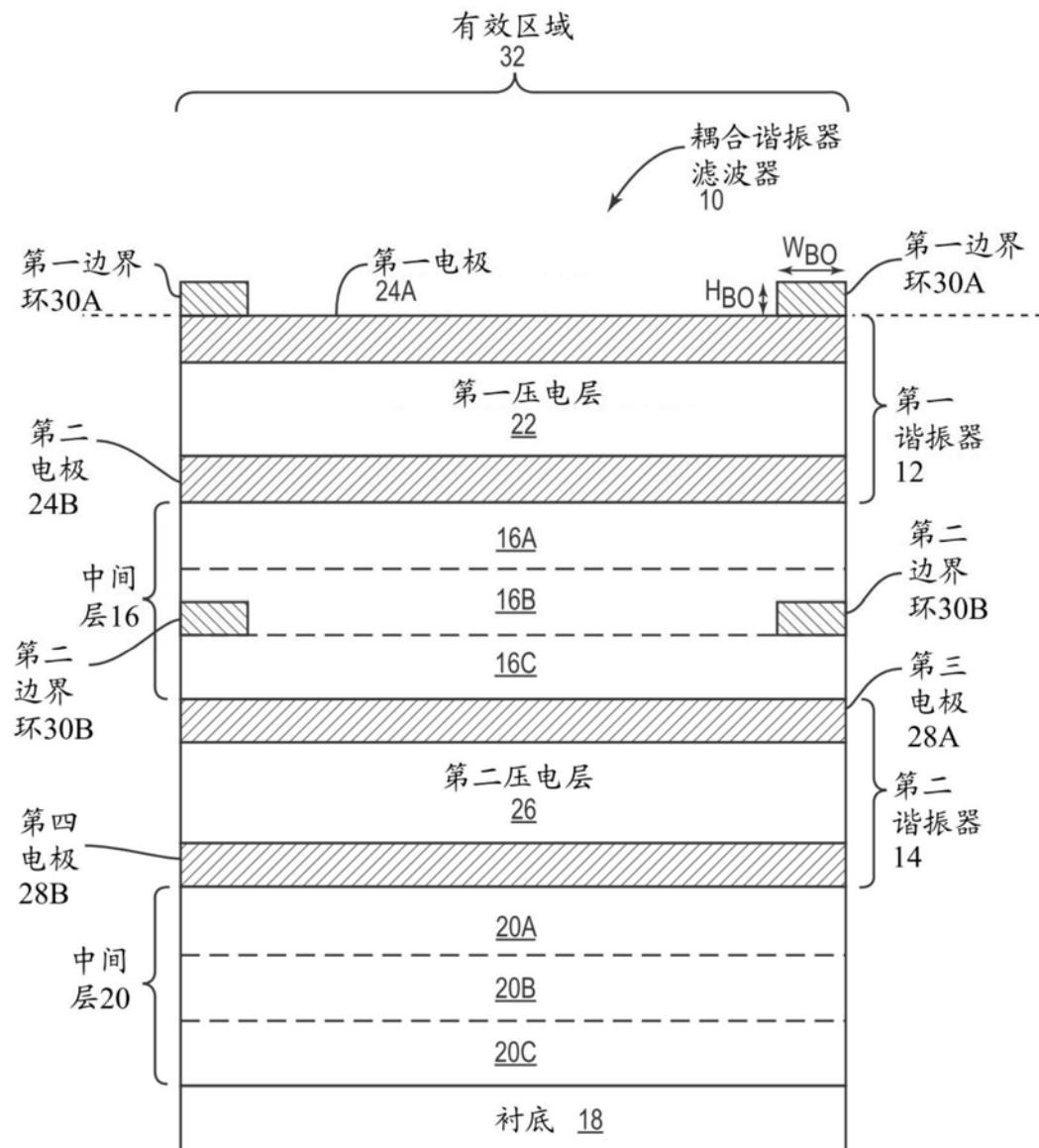

[0012] 图4示出根据本发明的一个实施方案的耦合谐振器滤波器的截面图。

[0013] 图5示出根据本发明的一个实施方案的耦合谐振器滤波器的截面图。

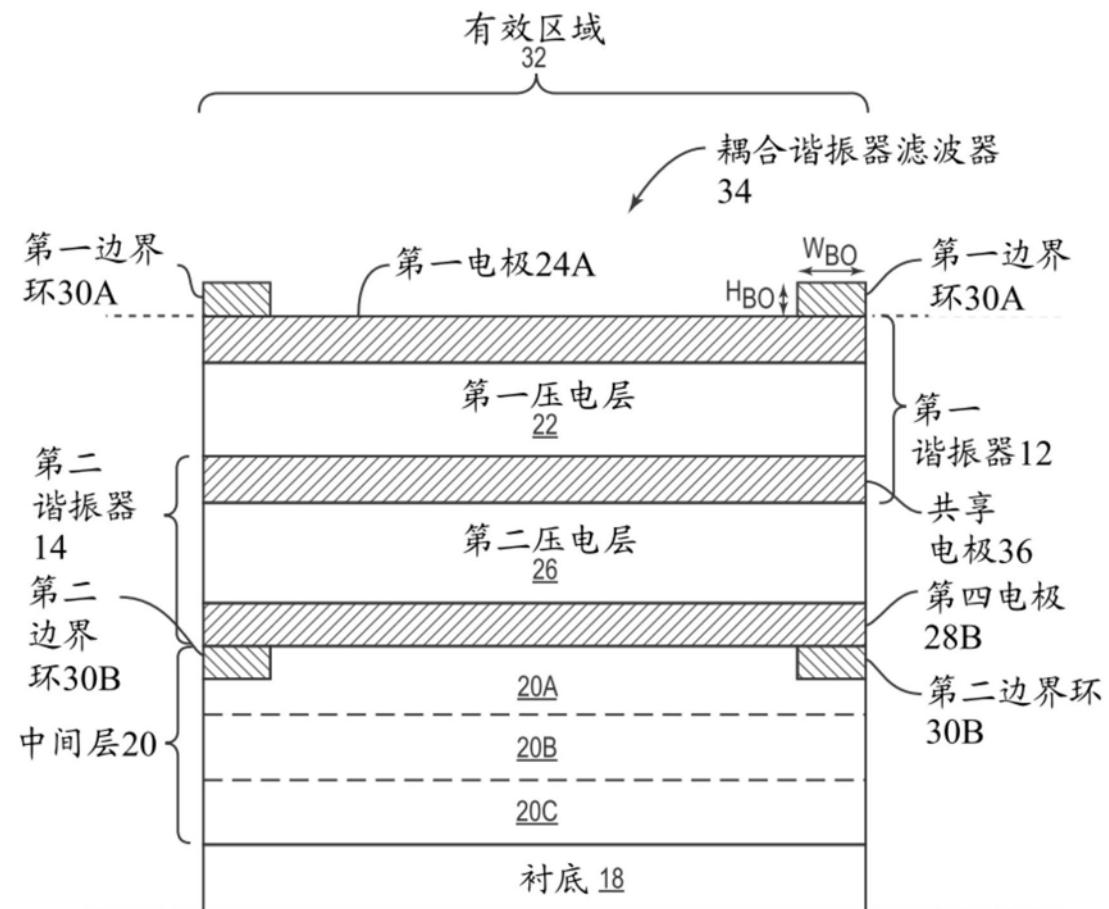

[0014] 图6示出根据本发明的一个实施方案的叠层式晶体滤波器的截面图。

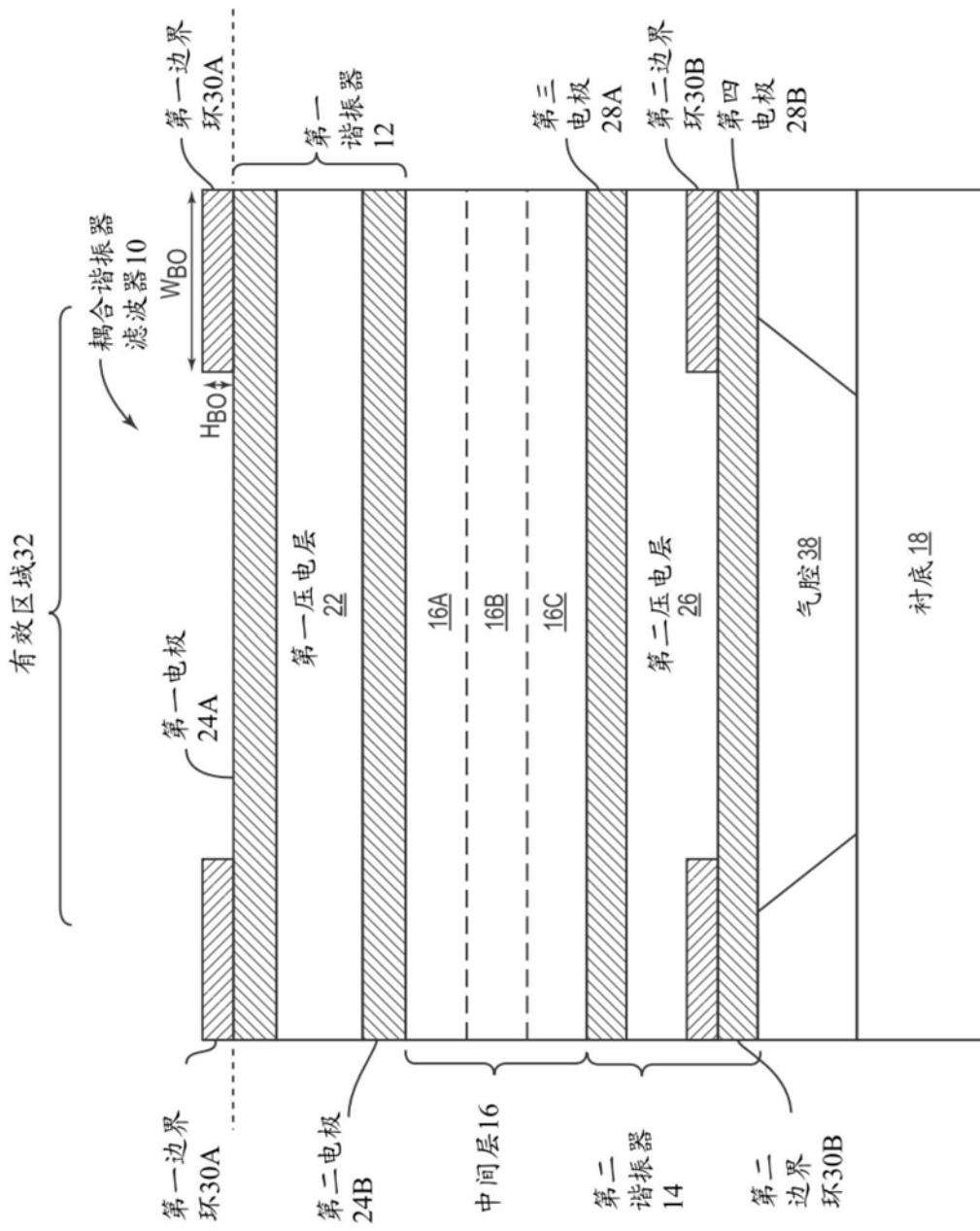

[0015] 图7示出根据本发明的一个实施方案的耦合谐振器滤波器的截面图。

## 具体实施方式

[0016] 下文陈述的实施方案代表使得本领域技术人员能够实践所述实施方案所必需的信息,并且示出实践所述实施方案的最佳模式。在根据附图来阅读以下描述之后,本领域技术人员将了解本公开的概念,并且将认识到本文中未具体提出的这些概念的应用。应当理解,这些概念和应用属于本公开和随附权利要求的范围内。

[0017] 应当理解,虽然术语第一、第二等可在本文中用于描述各种元件,但是这些元件不应受这些术语的限制。这些术语仅用于区分一个元件与另一个元件。例如,在不脱离本公开的范围的情况下,第一元件可称为第二元件,并且类似地,第二元件可称为第一元件。如本文所使用,术语“和/或”包括相关联的所列项目中的一个或多个的任何和所有组合。

[0018] 应当理解,当一个元件(诸如层、区域或衬底)被称为“在另一个元件上”或“延伸到另一个元件上”时,其可直接在另一个元件上或直接延伸到另一个元件上,或者也可存在中间元件。相反,当一个元件被称为“直接在另一个元件上”或“直接延伸到另一个元件上”时,不存在中间元件。同样,应当理解,当元件(诸如层、区域或衬底)被称为“在另一个元件之上”或“在另一个元件之上延伸”时,其可直接在另一个元件之上或直接在另一个元件之上延伸,或者也可存在中间元件。相反,当一个元件被称为“直接在另一个元件之上”或“直接在另一个元件之上延伸”时,不存在中间元件。还应当理解,当一个元件被称为“连接”或“耦合”到另一个元件时,其可直接连接或耦合到另一个元件,或者可存在中间元件。相反,当一个元件被称为“直接连接”或“直接耦合”到另一个元件时,不存在中间元件。

[0019] 诸如“在…下方”或“在…上方”或“上部”或“下部”或“水平”或“竖直”的相关术语在本文中可用来描述一个元件、层或区域与另一个元件、层或区域的关系,如图中所示出。应当理解,这些术语和上文所论述的那些术语意图涵盖设备的除附图中所描绘的取向之外的不同取向。

[0020] 本文中使用的术语仅用于描述特定实施方案的目的,而且并不意图限制本公开。如本文所使用,除非上下文明确地指出,否则单数形式“一个”(“a”、“an”)和“所述”意图同

样包括复数形式。还应当理解，当在本文中使用时，术语“包括”（“comprises”、“comprising”、“includes”和/或“including”）指明存在所述特征、整数、步骤、操作、元件和/或部件，但并不排除存在或者增添一个或多个其他特征、整数、步骤、操作、元件、部件和/或上述各项的组。

[0021] 除非另外定义，否则本文中使用的所有术语（包括技术术语和科学术语）的含义与本公开所属领域的普通技术人员通常理解的含义相同。还应当理解，本文所使用的术语应解释为含义与它们在本说明书和相关领域的情况下的一致，而不能以理想化或者过度正式的意义进行解释，除非本文中已明确这样定义。

[0022] 图1示出根据本发明的一个实施方案的耦合谐振器滤波器10的截面图。耦合谐振器滤波器10包括第一谐振器12、第二谐振器14、位于第一谐振器12与第二谐振器14之间的一个或多个中间层16、衬底18、以及第二谐振器14与衬底18之间的一个或多个附加中间层20。第一谐振器12位于第二谐振器14之上。第二谐振器14位于衬底18之上。第一谐振器12是体声波(BAW)谐振器，其包括夹置于第一电极24A与第二电极24B之间的第一压电层22。第二谐振器14也是BAW谐振器，其包括夹置于第三电极28A与第四电极28B之间的第二压电层26。中间层16位于第二电极24B与第三电极28A之间。附加中间层20位于第四电极28B与衬底18之间。

[0023] 中间层16和附加中间层20以声学方式（即，机械地）将第一谐振器12与第二谐振器14耦合到期望的程度。可调整第一谐振器12与第二谐振器14之间的声学耦合量以提供期望的滤波器响应。如上所述，耦合谐振器滤波器10可能面临降低其性能的寄生模式。因此，提供了第一边界环30A和第二边界环30B。在本实施方案中，第一边界环30A设置在第一电极24A上，并且第二边界环30B设置在第四电极28B上。具体地，第一边界环30A设置在第一电极24的形成耦合谐振器滤波器10的顶部的表面上。第二边界环30B设置在第四电极28B的与耦合谐振器滤波器10的顶部相反的表面上，使得第二谐振器14位于第二边界环30B与耦合谐振器滤波器10的顶部之间。如本文所论述的，边界环是在上面提供有边界环的层上的质量增加或减少区域。在本实施方案中，第一边界环30A和第二边界环30B被示出为分别在第一电极24A和第四电极28B上的附加金属层，因此分别增加了第一电极24A和第二电极28B的上面提供有所述金属层的区域之上的质量。第一边界环30A和第二边界环30B可设置为沿着耦合谐振器滤波器10的有效区域32的周边的框架状结构，其中有效区域32是第一谐振器12的电极24与第二谐振器14的电极28在其中重叠的区域。第一边界环30A和第二边界环30B的中间部分可以是空的。也就是说，第一边界环30A和第二边界环30B的中间部分可不改变上面分别设置有所述边界环的层的质量。第一边界环30A和第二边界环30B的宽度W<sub>B0</sub>和高度H<sub>B0</sub>可根据需要独立调整以提供期望的响应。此外，可选择第一边界环30A和第二边界环30B的材料以提供期望的响应。在一个实施方案中，第一边界环30A和第二边界环30B包括钨(W)。

[0024] 尽管边界环已经用于抑制常规体声波谐振器中的寄生模式达一段时间，但是它们通常仅应用于设备的顶部电极。以这种常规方式提供单个边界环可能降低耦合谐振器滤波器的性能，因为它可能并不抑制寄生模式并且还可能导致插入损耗的增加。此外，在耦合谐振器滤波器的顶部电极上使用单个边界环并不允许调整寄生模式抑制，因为这种常规边界环的厚度几乎不影响边界环区域中的分散。通过添加嵌入在耦合谐振器滤波器10中的第二边界环30B可抑制寄生模式。此外，耦合谐振器滤波器10的插入损耗没有显著增加。最后，添

加第二边界环30B使设备的边界环模式移动(通常被视为仅包括单个边界环的设备中的插入损耗的下降)到低于耦合谐振器滤波器10的通带。

[0025] 在一个实施方案中,中间层16和附加中间层20包括氧化硅(SiO<sub>2</sub>)和/或钨(W)。在各种实施方案中,中间层16和附加中间层20可以是具有不同材料的交替层。第一压电层22和第二压电层26包括例如氮化铝(AlN)。第一电极24A、第二电极24B、第三电极28A和第四电极28B包括金属叠层,所述金属叠层包括钨(W)和铝铜合金(AlCu)。衬底包括硅(Si)。本领域技术人员将容易了解的是,可将不同的材料用于上文列出的耦合谐振器滤波器10的各部分,所有材料这些都是涵盖在本文中的。

[0026] 图2示出根据本公开另一实施方案的耦合谐振器滤波器10。除了第二边界环30B在第三电极28A而不是第四电极28B上之外,图2中所示的耦合谐振器滤波器10基本上类似于图1中所示的耦合谐振器滤波器。具体地,第二边界环30B设置在第三电极28A的面向耦合谐振器滤波器10的顶部的表面上,使得第二边界环30B位于第二谐振器14与耦合谐振器滤波器10的顶部之间。在一些实施方案中,耦合谐振器滤波器10可包括多于两个的边界环30。例如,可组合关于图1和图2所描述的实施方案,使得第二边界环30B位于如图2所示的第三电极28A上,并且第二边界环30B位于如图1所示的第四电极28B上。

[0027] 图3示出根据本公开另一实施方案的耦合谐振器滤波器10。除了第二边界环30B位于中间层16中的一个上之外,并且具体地位于第三中间层16C上而不是位于第四电极28B上之外,图3中所示的耦合谐振器滤波器10基本上类似于图1中所示的耦合谐振器滤波器。值得注意的是,第二边界环30B可同样位于诸如第一中间层16A和第二中间层16B的中间层16中的任何一个上,并且进一步地可位于它们的任何表面上。在一些实施方案中,耦合谐振器滤波器10可包括多于两个的边界环30。例如,关于图1、图2和图3的实施方案可以与上文所论述的方式类似的方式组合。

[0028] 如上所述,边界环30可提供上面设置有所述边界环的层上的质量增加或质量减小。此外,边界环30可提供上面设置有所述边界环的层的一个区域中的质量增加,并且可提供上面设置有所述边界环的层的另一个区域中的质量减小。图4示出分别作为第一电极24A和第二电极24B上的质量减小区域的第一边界环30A和第二边界环30B。图5示出处于“阶梯”构型的第一边界环30A和第二边界环30B,所述构型使得边界环的一些部分减小质量而边界环的其他部分增加质量,或者边界环的不同部分改变不同量的质量。具体地,图5示出作为第一内边界环30A-1和第一外边界环30A-2的第一边界环30A,并且示出作为第二内边界环30B-1和第二外边界环30B-2的第二边界环30B。第一内边界环30A-1和第二内边界环30B-1分别是第一电极24A和第四电极28B上的质量减小区域。第一外边界环30A-2和第二外边界环30B-2分别是第一电极24A和第四电极28B上的质量增加区域。本领域技术人员将容易了解的是,虽然仅示出两个“阶梯”(质量减小区域和质量增加区域),但是第一边界环30A和第二边界环30B可包括任何数量的“阶梯”以实现期望的效果。

[0029] 本公开的原理同样适用于叠层式晶体滤波器34,其示例在图6中示出。除了中间层16被移除并且将第二电极24B与第三电极28A组合以提供共享电极36之外,叠层式晶体滤波器34基本上类似于耦合谐振器滤波器10。虽然图6中的叠层式晶体滤波器34仅示出第一边界环30A和第二边界环30B的单个构型,但是本领域技术人员将了解上文关于耦合谐振器滤波器10所论述的第一边界环30A和第二边界环30B的变型中的任一个同样适用于叠层式晶

体滤波器34。

[0030] 本公开的原理也同样适用于包括一个或多个薄膜体声波谐振器(FBAR)的耦合谐振器滤波器。这种耦合谐振器滤波器10在图7中示出。除了中间层20被移除并且第二谐振器14悬置在衬底18中的气腔38之上之外,图7中所示的耦合谐振器滤波器10基本上类似于上文关于图1至图5所论述的那些耦合谐振器滤波器。虽然出于说明的目的示出气腔38具有特定大小和形状,但是本领域技术人员将容易了解的是,气腔38可以任何数量的不同构型提供,所有这些构型都是涵盖在本文中的。此外,虽然图7中仅示出第一边界环30A和第二边界环30B的单个构型,但是本领域技术人员将了解,上文所论述的第一边界环30A和第二边界环30B的变型中的任一个同样适用于图7中所示的实施方案。

[0031] 本领域技术人员将认识到对本公开的优选实施方案的改进和修改。所有这种改进和修改都视为在本文所公开的概念和以下权利要求的范围内。

图1

图2

图3

图4

图5

图6

图7