**(19) 대한민국특허청(KR)**

**(12) 공개특허공보(A)**

(51) Int. Cl.<sup>5</sup>

G11C 11/41

(11) 공개번호 특 1994-0004647

(43) 공개일자 1994년 03월 15일

|            |                                                                                                                                                            |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 출원번호  | 특 1993-0014939                                                                                                                                             |

| (22) 출원일자  | 1993년 08월 02일                                                                                                                                              |

| (30) 우선권주장 | 92-229260 1992년 08월 05일 일본(JP)                                                                                                                             |

| (71) 출원인   | 카부시키가이샤 요오잔 타카토리 수나오                                                                                                                                       |

| (72) 발명자   | 일본국 토오쿄오토 세다가야쿠 기타자와 3-5-18<br>츄 코쿠료오<br>일본국 토오쿄오토 세다가야쿠 기타자와 3-5-18<br>타카토리 수나오<br>일본국 토오쿄오토 세다가야쿠 기타자와 3-5-18<br>야마모토 마코토<br>일본국 토오쿄오토 세다가야쿠 기타자와 3-5-18 |

| (74) 대리인   | 하상구, 하영욱                                                                                                                                                   |

**심사청구 : 없음****(54) 메모리장치****요약**

본 발명은, 리프레시가 불필요함과 아울러, 그 회로규모가 작은 메모리장치를 제공하는 것을 목적으로 한다. 본 발명의 메모리장치는, 베이스(B)에 입력전압이 접속되고 또 이미터(E)가 접지된 제1트랜지스터(TR1)와, 이 제1트랜지스터의 콜렉터(C)에 베이스(B)가 접속됨과 아울러 콜렉터(C)가 접지되며 또 이미터(E)에 전원(Vcc)이 접속된 제2트랜지스터(TR2)로 이루어지며, 이 제2트랜지스터(TR2)의 콜렉터(C)를 제1트랜지스터(TR1)의 베이스(B)에 접속해서 1기억단위를 구성하고 있다.

**대표도****도1****명세서**

[발명의 명칭]

메모리장치

[도면의 간단한 설명]

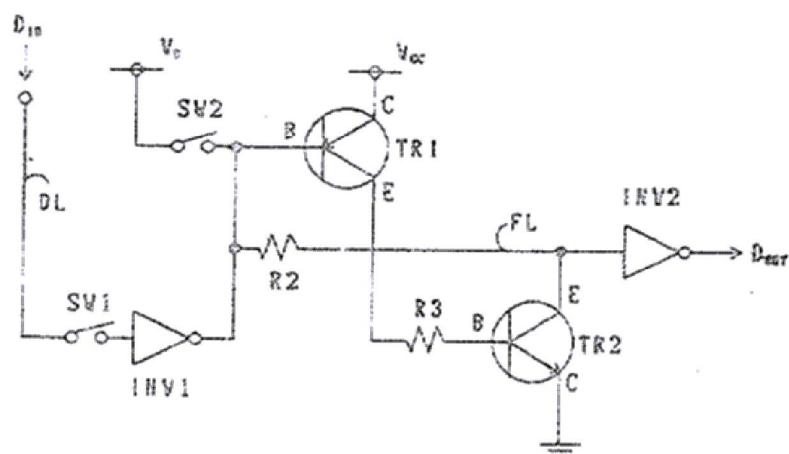

제1도는 본 발명의 제1실시예를 나타내는 회로도,

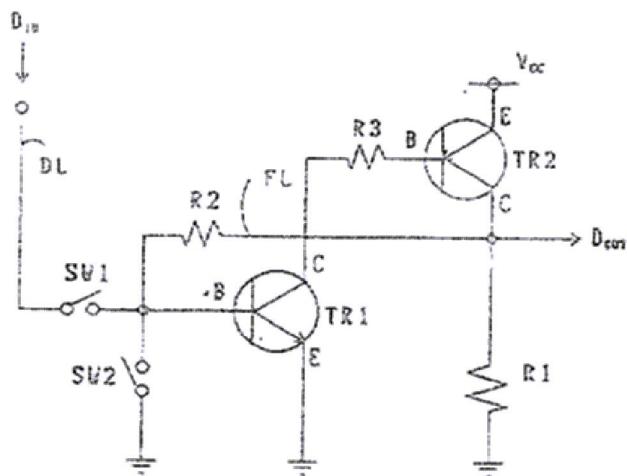

제2도는 본 발명의 제2실시예를 나타내는 회로도.

본 내용은 요부공개 건이므로 전문 내용을 수록하지 않았음

**(57) 청구의 범위****청구항 1**

베이스(B)에 입력전압이 접속되고 또 이미터(E)가 접지된 PNP형의 제1트랜지스터와(TR1)와 이 제1트랜지스터의 콜렉터에 베이스가 접속됨과 아울러 콜렉터가 접지되며 또 이미터에 전원(Vcc)이 접속된 NPN형의 제2트랜지스터(TR2)와, 이 제2트랜지스터의 콜렉터를 제1트랜지스터의 베이스에 접지하여서 1기억단위를 구성한 메모리장치.

**청구항 2**

제1항에 있어서, 제2트랜지스터의 콜렉터로부터 제1트랜지스터의 베이스에 이르는 도선(FL)에는 보호저항(R2)이 접속되어 있는 것을 특징으로 하는 메모리장치.

**청구항 3**

베이스(B)에 입력전압의 반전(反轉)출력이 접속되고 또 콜렉터(C)가 전원(Vcc)에 접속된 NPN형의 제1트랜지스터(TR1)와, 이 제1트랜지스터의 이미터에 베이스가 접속됨과 아울러 콜렉터가 접지되고 또 이미터가 제1트랜지스터의 베이스에 접속된 제2트랜지스터(TR2)에 의해 1기억단위를 구성하여 이루어지는 메모리장치.

#### 청구항 4

제3항에 있어서, 제2트랜지스터의 이미터로부터 제1트랜지스터의 베이스에 이르는 도선(FL)에는 보호저항(R2)이 접속되어 있는 것을 특징으로 하는 메모리장치.

※ 참고사항 : 최초출원 내용에 의하여 공개하는 것임.

#### 도면

##### 도면1

##### 도면2