(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4322810号

(P4322810)

(45) 発行日 平成21年9月2日(2009.9.2)

(24) 登録日 平成21年6月12日(2009.6.12)

|                         |                    |

|-------------------------|--------------------|

| (51) Int.Cl.            | F 1                |

| GO 1 R 19/165 (2006.01) | GO 1 R 19/165 M    |

| GO 6 F 1/28 (2006.01)   | GO 6 F 1/00 333 C  |

| GO 6 F 1/32 (2006.01)   | GO 6 F 1/00 332 Z  |

| GO 6 F 15/78 (2006.01)  | GO 6 F 15/78 510 G |

|                         | GO 6 F 15/78 510 P |

請求項の数 4 (全 12 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2004-551487 (P2004-551487)  |

| (86) (22) 出願日 | 平成15年9月30日 (2003.9.30)        |

| (65) 公表番号     | 特表2006-506617 (P2006-506617A) |

| (43) 公表日      | 平成18年2月23日 (2006.2.23)        |

| (86) 国際出願番号   | PCT/US2003/030864             |

| (87) 国際公開番号   | W02004/044719                 |

| (87) 国際公開日    | 平成16年5月27日 (2004.5.27)        |

| 審査請求日         | 平成18年9月15日 (2006.9.15)        |

| (31) 優先権主張番号  | 10/292,323                    |

| (32) 優先日      | 平成14年11月12日 (2002.11.12)      |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                            |

|-----------|------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 504199127<br>フリースケール セミコンダクター イン<br>コーポレイテッド<br>アメリカ合衆国 78735 テキサス州<br>オースティン ウィリアム キャノン<br>ドライブ ウエスト 6501 |

| (74) 代理人  | 100116322<br>弁理士 桑垣 衡                                                                                      |

| (72) 発明者  | エスピナー、ジョージ エル.<br>アメリカ合衆国 78727 テキサス州<br>オースティン ドーフィン コープ 1<br>902                                         |

最終頁に続く

(54) 【発明の名称】集積回路および低電圧検出システム

## (57) 【特許請求の範囲】

## 【請求項 1】

稼働モードまたは停止モードで動作する集積回路(102)であって、前記稼働モードの前記集積回路(102)は命令を実行することができ、前記停止モードの前記集積回路(102)は前記命令を実行することができず、前記集積回路(102)は、

電源からの電力を受取るための電力供給ピン(109)と；

前記電力供給ピン(109)の電圧としての供給ピン電圧(Vbatt)についての第1電圧レベル(LV1)を示す第1電圧検出信号(112)を供給するための出力を有する第1電圧検出回路(110)と；

前記供給ピン電圧(Vbatt)についての第2電圧レベル(LV2)を示す第2電圧検出信号(118)を供給するための出力を有する第2電圧検出回路(116)であって、前記第2電圧レベル(LV2)は前記第1電圧レベル(LV1)よりも低いこと；

前記電力供給ピン(109)を介して受取られる電力から電力供給されるように構成された中央処理装置(160)と；

前記中央処理装置(160)に動作可能に接続された割込ハンドラ(142)であって、前記割込ハンドラ(142)は少なくとも一つの割込に応答すること；

前記割込に対する前記割込ハンドラ(142)の応答性を制御する割込ハンドラ制御回路(138)と

を備え、

前記稼働モードにおいて前記供給ピン電圧(Vbatt)が前記第1電圧レベル(LV1)

10

20

以下の場合には、前記第2電圧検出回路(116)が常にイネーブルにされ；

前記停止モードにおいて前記供給ピン電圧(Vbatt)が前記第1電圧レベル以下の場合には、前記第2電圧検出回路(116)が周期的にイネーブルにされ；

前記稼働モードと前記停止モードの何れでも前記供給ピン電圧(Vbatt)が前記第2電圧レベル(LV2)以下の場合には、前記中央処理装置(160)が前記割込を了解することを禁止されるように構成されていることを特徴とする、集積回路(102)。

**【請求項2】**

請求項1記載の集積回路(102)は更に、前記第2電圧検出回路(116)を周期的にイネーブルにするための周期を決定する周期的立上げ回路(124)を備えることを特徴とする、集積回路(102)。

10

**【請求項3】**

請求項1に記載の集積回路(102)を含むシステム(100)であって、前記システム(100)は、

前記電力供給ピン(109)に前記電力を供給するために前記電力供給ピン(109)に接続された電池(106)と；

前記集積回路(102)に動作可能に接続された外部周辺装置(166)とを備えることを特徴とする、システム(100)。

**【請求項4】**

請求項1に記載の集積回路(102)は更に、安全ビットレジスタ(134)を備え、前記供給ピン電圧(Vbatt)が前記第1電圧レベルよりも高くなると、前記安全ビットレジスタ(134)はリセットされ、

20

前記割込ハンドラ制御回路(138)は、前記安全ビットレジスタ(134)がリセットされると、前記中央処理装置(160)が前記割込を了解することを許容するように構成されていることを特徴とする、集積回路(102)。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は一般に低電圧検出システムに関し、より詳しくは、複数の電圧検出レベルを有する低電圧検出システムに関する。

**【背景技術】**

30

**【0002】**

多くの電池駆動システム、例えば、携帯型電子機器市場における電池駆動システムにおいては、マイクロプロセッサやマイクロコントローラなどの論理装置は、主制御装置と電力管理装置またはそのいずれかの役目を担っている。この役目においては、電池が弱くなつたか、または電池が取り外されたときに、論理装置の内部論理状態と揮発性メモリ(RAM, 制御レジスタ、論理状態など)を保護することが重要である。例えば、今日入手可能なマイクロコントローラにおいては、低電圧検出(LVD)回路が、低電池電圧が発生したときを検出し、マイクロコントローラをリセットする。あるいは、いくつかのLVDシステムは、マイクロコントローラがリセットするのではなく、割り込みを受け取ることを可能にし、その場合、ソフトウェアは、電池電圧が回復するまでマイクロコントローラを停止モードにして電流消費を最少にすることができる。

40

**【0003】**

しかしながら、これらのシステムにおいては、停止モードにある間、割り込み(例えばキーボード入力からの割り込み)が受け付けられることにより、電池電圧が回復する前に、マイクロコントローラを再起動させて、電池を消耗するので、データが失われる。

**【0004】**

それ故、論理装置の内部論理状態と揮発性メモリを保護すると同時に、弱い電池状態または電池が取り外された状態からの安全な回復を可能にするLVDシステムを提供する必要性が存在する。また、コストを削減するために、論理装置の最低数のピンを用いたそのようなシステムを提供する必要性がある。

50

**【発明を実施するための最良の形態】****【0005】**

本発明は、例示によって説明されており、添付図面によって制限されるものではない。添付図面において、同様な参照符号は同様な要素を示している。

図面内の要素は簡略化と明確化のために示されたものであって、必ずしも一定の縮尺で描かれていないことは当業者にとって明らかである。例えば、図面内の要素のいくつかの寸法は、本発明の実施態様の理解を良くするために、他の要素に比べて誇張することができる。

**【0006】**

本書において使用されているように、用語「バス」は、一つまたはそれ以上のいろいろな種類の情報、例えば、データ、アドレス、制御、または状態、を転送するために使用することができる複数の信号線または導体を呼ぶために使用されている。本書において述べられたような導体は、単一導体、複数導体、単方向性導体、または双方向性導体であるものとして説明することができる。しかしながら、種々の実施態様は導体の態様を変更することができる。例えば、双方向性導体よりもむしろ別々の単方向性導体を使用することができ、その逆も可能である。また、複数の導体を、複数の信号をシリアルにまたは時分割多重化方法によって転送する単一導体で置き換えることができる。同様に、複数の信号を伝送する単一導体を、これらの信号のサブセットを伝送する種々の異なる導体に分けることができる。それ故、信号を転送するための多くのオプションが存在する。

**【0007】**

用語「アサート」および「ネゲート」(または「デアサート」)は、信号、状態ビット、または同様な機構を、それぞれ、その論理的真状態または論理的偽状態で表す場合に使用される。論理的真状態が論理レベル1である場合には、論理的偽状態は論理レベル0である。論理的真状態が論理レベル0である場合には、論理的偽状態は論理レベル1である。

**【0008】**

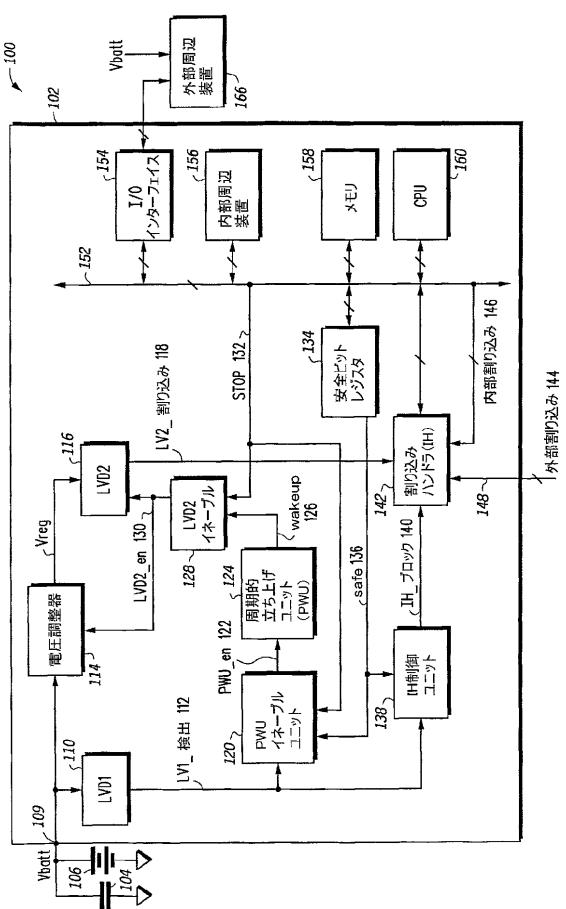

図1は、データ処理システム100の一実施形態のブロック図である。図1に示すように、データ処理システム100は、論理装置、例えばマイクロコントローラ(MCU)102と、外部回路とを含んでいる。別の実施態様においては、MCU102は、種々のマイクロプロセッサ、マイクロコントローラ、または他の種類の論理装置と置き換えることができる。一実施形態においては、MCU102(または他の種類の論理装置のうちのどれか)は単一集積回路上に設けられる。MCU102は、中央処理装置(CPU)160、メモリ158、内部周辺装置156、入出力(I/O)インターフェース154、安全ビットレジスタ134、および割り込みハンドラ(IH)142を含んでおり、これらはすべてバス152に双方向的に接続されている(本書において使用されるように、バス152はアドレス信号線、データ信号線、および制御信号線を含んでいることに注目されたい)。

**【0009】**

MCU102は更に、電圧V<sub>batt</sub>を供給する電池ノード109(即ち、電力供給ピン)に接続されたLVD1ユニット110を含んでいる。LVD1(110)は、V<sub>batt</sub>が第1電圧レベルLV1を下回るときを検出する。MCU102は更に、V<sub>batt</sub>が第2電圧レベルLV2を下回るときを検出するLVD2ユニット116を含んでおり、一般にLV1はLV2よりも大きい。MCU102は更に、LVD2(116)にV<sub>reg</sub>を供給するための、電池ノード109とLVD2(116)に接続された電圧調整器114を含んでいる。しかしながら、別の実施態様においては、電圧調整器114はなくてもよく、その場合には、LVD2(116)は電池ノード109に接続される。MCU102は更に、周期的立ち上げユニット(PWU)124、PWUイネーブルユニット120、LVD2イネーブルユニット128、および割り込みハンドラ(IH)制御ユニット138を含んでいる。バス152は、停止モード標識(インジケータ)のSTOP132をLVD2イネーブルユニット128とPWUイネーブルユニット120に供給する。PWUイネーブル

10

20

30

40

50

ユニット120は、信号PWU\_en122をPWU124に供給し、PWU124は、信号wake up126をLVD2イネーブルユニット128に供給する。LVD2イネーブルユニット128は、信号LVD2\_en130をLVD116と、もしあれば、電圧調整器114に供給する。安全ビットレジスタ134は、信号safe136をPWUイネーブルユニット120とIH制御ユニット138に供給する。割り込みハンドラ142は、信号L V 2\_割り込み118をLVD2(116)から、信号IH\_ブロック140をIH制御ユニット138から、内部割り込み146をバス152を介して、外部割り込み144を双方向性導体148を介して受け取る。

#### 【0010】

データ処理システム100の外部回路は、電池ノード109に接続可能な電池106と、充電要素104と、外部周辺装置166を含んでいる。充電要素104は、図1にコンデンサとして示されている（従って、コンデンサ104または電力貯蔵コンデンサ104と呼ぶことができる）ということに注目されたい。しかしながら、電池106は、充電回路によって再充電可能な充電式電池で置き換えることができる（従って、充電回路がコンデンサ104に置き換えられる）ことに注目されたい。また、電池106を何らかの適当な電源と置き換えることができる。図1に示すように、電池106の第1端子とコンデンサ104の第1端子は電池ノード109に接続されている。電池106の第2端子とコンデンサ104の第2端子は接地に接続されている。また、図1には示されていないが、MCU102内に示されたユニットのそれぞれは、電池ノード109か、電圧調整器114（もしあれば）の出力に接続されている。I/Oインターフェース154は、外部周辺装置166に双方向に接続されている。外部周辺装置166は、例えば、キーボード、ディスプレイ、他の処理装置などの種々の周辺装置を含むことができるということに注目されたい。

10

20

30

#### 【0011】

動作においては、コンデンサ104は電池ノード109からのノイズを除去し、電池106がノード109に接続されているとき、高周波はね返りに対しはね返り防止を行う。電池106が取り外された場合、コンデンサ104は、低電力状態の間、長時間にわたって、MCU102内のRAMメモリ、制御レジスタ、論理状態などを保持するのに十分な電圧を電池ノード109に供給する。図示された実施態様においては、以下に更に詳細に説明するように、MCU102に電力を供給するため、および弱くなった電池によってまたは電池を取り外したことによって生じる低電圧状態を検出するために、単一の電圧供給ピン（電池ノード109）が使用されるということに注目されたい。

30

#### 【0012】

I/Oインターフェース154、内部周辺装置156、メモリ158、およびCPU160は、この技術において周知のように動作し、本書において詳細に述べることはしない。即ち、本書において説明された低電圧検出システムに関するこれらのユニットのそれらの側面のみを述べる。MCU102の低電圧検出システム（LVD1(110)、LVD2(116)、オプションとしての電圧調整器114、PWUイネーブルユニット120、PWU124、LVD2イネーブルユニット128、安全ビットレジスタ134、IH制御ユニット138、割り込みハンドラ142、およびCPU160を含む）の動作を、図2～7を参照してより詳細に述べる。

40

#### 【0013】

一実施形態においては、MCU102は、VbattがMCU102の最低動作電圧Vminよりも高い間は、稼動モードまたは停止モードにおいて正常に動作することができる。稼動モードにおいては、MCU102は命令を実行することができるが、停止モードは低電力モードであり、その場合、MCU102は命令を実行することができない。MCU102は、停止命令の実行により稼動モードから停止モードに入ることができる。MCU102は、外部割り込み144または内部割り込み146を受けて、停止モードから抜けて、稼動モードに入ることができる。例えば、ユーザーがキーを押すことによってMCU102を立ち上げることができるように、外部割り込みはキーボード割り込みを含んでもよい

50

。しかしながら、 $V_{batt}$ が $V_{min}$ より低い間、MCU102が停止モードから稼動モードに移る場合、MCU102の動作は、MCU102がその最低動作電圧未満で稼動する、即ち、その規定動作範囲外で動作するので、不良となることがあり得る。それ故、一実施形態においては、 $V_{batt}$ が（弱くなった電池のためか、電池が取り外されたために） $V_{min}$ を下回ると、MCU102は、いかなる外部割り込みまたは内部割り込みを了解（acknowledged）することも禁止される安全状態に入る。 $V_{batt}$ が（弱くなった電池もしくは取り外された電池の交換によってか、または電池の再充電によって）安全動作電圧よりも高くなったときのみ安全状態から抜け出て、MCU102はもはや割り込みを了解することを禁止されることはない正常動作を再開することができる。この時点で、MCU102は安全に稼動モードに復帰することができる。

10

#### 【0014】

一実施形態においては、MCU102の低電圧検出システムは、第1低電圧検出ユニット（LVD1（110））を使って、 $V_{batt}$ がLV1（LV1はMCU102のための安全動作電圧に相当する）よりも低くなるときを検出する。この実施態様においては、MCU102は、第2電圧検出ユニット（LVD2（116））を使って、 $V_{batt}$ がLV2よりも低くなるときを検出する。このLV2は一般にLV1よりも低く、 $V_{min}$ よりも高い。上記で説明したように、一度 $V_{batt}$ がLV2より下がると、MCU102は安全状態に置かれ、MCU102はもはや再度稼動モードに入ることはできず、 $V_{batt}$ がLV1を超えるまで、いかなる外部割り込みまたは内部割り込みを了解することも禁止される。図示された実施態様においては、LVD1（110）は、稼動モードと停止モードの両方を含むMCU102のすべての正常モードにおいて動作する低電力消費型電圧検出回路である。しかしながら、LVD1（110）は、最小限の電力（その一例を以下に図6を参照して述べる）を消費するように設計されているので、MCU102が $V_{min}$ よりも高いままで最大電池寿命を保証するのを確実にするほど、LVD1（110）は十分精度が高くなない。LVD2（116）は、正確な低電圧表示を行うようになっているが、そうするためにLVD2（116）は更に電流を消費する。それ故、LVD1（110）は、 $V_{batt}$ が、（低電力消費によってもたらされる不正確さのために）ほぼLV1になったときに、標識を供給し（即ち、LV1\_検出112をアサートし）、LVD2（116）は、 $V_{batt}$ がLV2に達したときに、割り込みを供給する（即ち、LV2\_割り込み118をアサートする）。現在の実施態様においては、LVD2（116）は、稼動モードの間、常にイネーブルにされるということに注目されたい。しかしながら、LVD2（116）は多くの電力を消費するので、MCU102が停止モードにある間、LVD2（116）をイネーブルにすることは望ましくない。即ち、常にイネーブルにされるLVD1（110）とは異なり、LVD2（116）は、MCU102が停止モードにある間、必要に応じて、選択的にイネーブルにすることができる。

20

#### 【0015】

上の説明において、および、以下の説明において、LVD2（116）は、 $V_{batt}$ を監視して $V_{batt}$ がLV2より低くなるときを検出するということに注目されたい。このことは、オプションとしての電圧調整器114がMCU102の中にはない（即ち、LVD2（116）は $V_{reg}$ よりもむしろ $V_{batt}$ を直接受け取る）ことを仮定している。しかしながら、電圧調整器114が図示のようにMCU102の中にある場合、（電圧調整器114に接続された）LVD2（116）は $V_{reg}$ を受け取るので、実際は、 $V_{reg}$ がLV2よりも低くなるときを検出できることに注目されたい。それ故、この実施態様においては、LV2に対して使用される実際値は、電圧調整器114によって生じる電圧降下に基づいて調整することができる。しかし、 $V_{reg}$ または $V_{batt}$ が監視されるかどうかにかかわらず、LVD2（116）は、 $V_{batt}$ が第2閾値LV2を下回ったときに、LV2\_割り込み118を供給する。また、 $V_{batt}$ がLV2に近い電圧レベルに達したとき、電圧調整器114による電圧降下は減少し、 $V_{batt}$ は $V_{reg}$ とほぼ同じになることに注目されたい。それ故、本書における説明を容易にするために、以下の記述は、LVD2は $V_{reg}$ よりもむしろ $V_{batt}$ を監視することに言及しているが、 $V_{reg}$ を監視しても同じ結果が得られる

30

40

50

ことは当業者にとって明らかである。

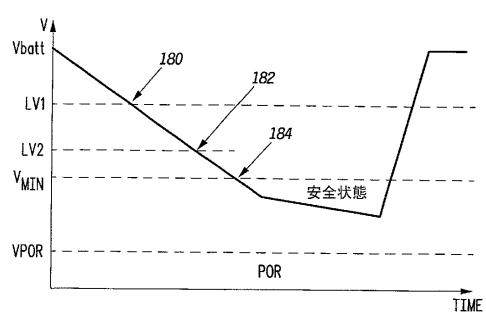

【0016】

図2は、本発明の一実施形態による、安全状態に入り安全状態から出る方法を示すグラフである。弱くなった電池のためか、または電池を取り外したために、Vbattが低下し始めると（Vbattはコンデンサ104によって供給されている）、LVD1（110）は、Vbattが、図2の中で点180によって示されたほぼLV1に達するときを検出する。点180に達したとき、MCU102が停止モードで動作している場合には、LVD2（116）は周期的にイネーブルにされて正確な低電圧検出を行う。

【0017】

例えば、再び図1において、PWUイネーブルユニット120が、LV1\_検出112、safe136、およびSTOP132に基づいて、PWU124をイネーブルにする。即ち、PWUイネーブルユニット120は、（PWU124をイネーブルにするために）PWU\_en122をアサートする。このとき、LV1\_検出112、safe136、およびSTOP132の値は図5の真理値表に示すようになっている。即ち、図5に見られるように、LV1\_検出112がアサートされ、STOP132がアサートされ、safe136がアサートされないときのみ、PWU\_en122はアサートされる。即ち、VbattがLV1を下回ったことをLVD1（110）が検出し（従ってLV1\_検出112をアサートしたとき）、MCU102は停止モードにあり（STOP132がアサートされ）、MCU102は安全モードにない（safe136がアサートされず）ときには、PWU124はイネーブルにされる。LV1\_検出112、safe136、およびSTOP132に対する値の他の組み合わせのすべてにおいては、PWU\_en122はアサートされないので、PWU124はイネーブルにされない。

【0018】

PWU124は、LVD2イネーブルユニット128にwake up126を供給する。一実施形態においては、wake up126は、LVD2イネーブル128を介してLVD2（116）を周期的にイネーブルにするために使用される周期性パルスである。即ち、LVD2イネーブルユニット128は、wake up126およびSTOP132を受け取り、LVD2\_en130をLVD2（116）に（もしあれば電圧調整器114にも）供給する。LVD2\_en130がアサートされたとき、LVD2（116）は、イネーブルにされ、Vbattを監視してVbattがLV2より高いかまたは低いかを判定する。（あるいは、上に述べたように、電圧調整器114がある場合は、LVD2（116）は、この時点でVbattとほぼ等しい可能性のあるVregを代わりに監視して、VbattがLV2より高いかまたは低いかを判定する）。LVD2イネーブルユニット128は、図4に示す真理値表に従って動作する。それ故、稼動モードにあるときは（STOP132がアサートされていないときは）、LVD2\_en130はアサートされ、LVD2（116）をイネーブルにする。しかしながら、停止モードにあるときは（STOP132がアサートされたときは）、wake up126がアサートされたときのみ、LVD2\_en130はアサートされる。このようにして、停止モードの間であって、VbattがLV1とLV2との間にある場合には、LVD2（116）は、最小の電力を消費するように、wake up126によって周期的にイネーブルにされる。

【0019】

再び図2のグラフにおいて、弱くなった電池のためか、電池が取り外されたために、Vbattが低下し続けると、LVD2（116）は、Vbattが、図2の中で点182によって示されたLV2に達するときを検出する。MCU102が停止モードで動作中であった場合、LVD2（116）は、wake up126によって決定される周期の一つの間にVbattがLV2に達するのを検出したことに注目されたい。しかしながら、MCU102が稼動モードで動作中である場合には、LVD2（116）は常にイネーブルにされて（即ち、STOP132がデアサートされたとき、wake up126にもかかわらず、LVD2\_en130が常にアサートされて）、VbattがLV2に達するのを検出する。上記で説明したように、LVD2（116）は、LVD1（110）がVbattがLV1に達す

るとき検出するよりも正確に、VbattがLV2に達するときを検出する。LV2に達したとき、LV D 2 (116)はLV2\_割り込み118をアサートする。一実施形態においては、LV2\_割り込み118が割り込みハンドラ142によってすぐに了解されることを保証するために、LV2\_割り込み118は最優先されることに注目されたい。それ故、この実施態様においては、LV2\_割り込み118をアサートしたとき、割り込みハンドラ142は、CPU160に待ち状態のLV D 2 (116)割り込みを処理させる。LV D 2 (116)割り込みを処理するための割り込み処理ルーチンは、MCU102が安全にシャットダウンするようにするための命令を含むことができる。例えば、割り込み処理ルーチンは、状態情報を含むすべての望ましい情報をメモリ158に保存したり、外部周辺装置に信号を送ったりすることができる。

10

#### 【0020】

MCU102はいまVmin付近で動作している（即ち、VbattがVminに近づきつつある）ので、MCU102は、Vminに達する前か達したときに安全状態に置かれるべきである。一実施形態においては、割り込み処理ルーチンは、安全状態に入ったことを示すために安全ビットレジスタ134を1に設定するための命令を含むことができる。安全ビットレジスタ134が設定されたとき、safe136は、割り込みハンドラ142が待ち状態の割り込みまたは将来の割り込みを了解するのを禁止するように、アサートされる。例えば、図1において、IH制御ユニット138は、外部割り込みと内部割り込みに対する割り込みハンドラ142の応答性を制御する。IH制御ユニット138は、LV1\_検出112とsafe136を受け取り、図3の真理値表によって示されるようにIH\_ブロック140を選択的にアサートする。例えば、IH制御ユニット138は、LV1\_検出112とsafe136の両方がアサートされたときのみIH\_ブロック140をアサートする。IH\_ブロック140がアサートされたとき、割り込みハンドラ142は、外部割り込み144または内部割り込み146からの割り込みを了解するのを禁止されるか阻止される。それ故、一実施形態においては、各割り込みは、外部割り込み144または内部割り込み146内に、対応する割り込み信号を有している。各割り込み信号とIH\_ブロック140をANDゲートへランセラることによって、各割り込み信号をIH\_ブロック140によって個々に禁止することができる。あるいは、他のイネーブル回路またはゲート回路を使用して、割り込みハンドラ142への入力を禁止することができる。別の実施態様においては、IH\_ブロック140を用いて、割り込みハンドラ142のすべてまたは一部分をディスエーブルして、割り込みの禁止または阻止を達成することができる。更にもう一実施形態においては、IH\_ブロック140を割り込みハンドラ142の出力と共にゲート制御して、割り込みの阻止または禁止を達成することができる。

20

#### 【0021】

別の実施態様においては、safe136を種々の方法で実行できることに注目されたい。例えば、Vbatt（いくつかの実施態様においてはVreg）がLV2に達したことをLV D 2 (116)が検出したときに、safe136を（割り込み処理ルーチンによるのではなく）自動的にアサートすることができる。安全ビットレジスタ134はMCU102内のどこに位置してもよいことに注目されたい。

30

#### 【0022】

再び図2において、MCU102は、Vbattが再びLV1より高くなるまで安全状態のままである。即ち、新しい電池が挿入されるか現在の電池が再充電されたとき、Vbattは再度、LV1より高くなり、その時点で安全状態から抜け出して、安全ビットレジスタ134が0にリセットされてsafe136をデアサートする。よって、MCU102は再び、割り込みを了解し、安全に停止モードを終了し、稼動モードに復帰することができる。別例においては、安全ビットレジスタ134は、VbattがLV1より高くなったときリセットされない。この実施態様においては、安全ビットレジスタは、ユーザーによって、あるいは、MCU102を立ち上げた後のある時点において、クリアされ得る。

40

#### 【0023】

本発明の一実施形態においては、LV D 1 (110)は、Vbattが、（図2に示すよう

50

な)  $V_{min}$  より小さいパワー・オン・リセット電圧 (V P O R) を下回るときを検出するために使用することもできる。V batt が V P O R に達すると、一般に、R A M と内部論理状態が、完全に、あるいは部分的に破壊される。電池を交換するかまたは電池を再充電する前に V batt が V P O R に達した場合には、データの破壊のために、電池の交換または再充電時に M C U 1 0 2 を初期化する必要がある。いくつかの実施態様においては、リセット割り込みまたはパワー・オン・リセット割り込みは、上記で説明された L V D 2 ( 1 1 6 ) 割り込みよりも高い優先度を有することができる。

#### 【 0 0 2 4 】

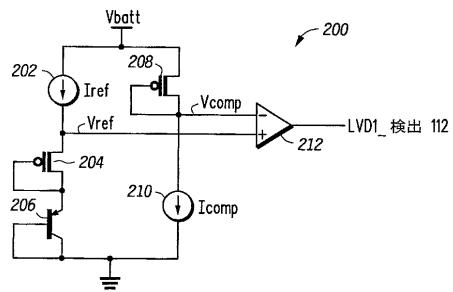

図 6 は、図 1 の L V D 1 ( 1 1 0 ) のために使用することができる L V D 回路 2 0 0 の一実施形態の概略図である。L V D 回路 2 0 0 は、比較回路 2 1 2 と、トランジスタ 2 0 8 , 2 0 4 , 2 0 6 と、電流源 2 0 2 , 2 1 0 を含んでいる。電流源 2 0 2 は、V batt に接続された第 1 端子と、比較回路 2 1 2 のプラス入力 (V ref) およびトランジスタ 2 0 4 の第 1 電流電極に接続された第 2 端子を有している。電流源 2 0 2 は、比較回路 2 1 2 のプラス入力とトランジスタ 2 0 4 の第 1 電流電極に電流  $I_{ref}$  を供給する。トランジスタ 2 0 4 の第 2 電流電極は、トランジスタ 2 0 4 の制御電極とトランジスタ 2 0 6 の第 1 電流電極に接続されている。トランジスタ 2 0 6 の制御電極とトランジスタ 2 0 6 の第 2 電流電極は、互いに接続されると共に、電流源 2 1 0 の第 2 端子と、接地ノードに接続されている。トランジスタ 2 0 8 の第 1 電流電極は V batt に接続されており、トランジスタ 2 0 8 の制御電極と第 2 制御電極は、比較回路 2 1 2 のマイナス入力 (V comp) および電流源の 2 1 0 の第 1 端子に接続されている。電流源 2 1 0 は電流  $I_{comp}$  を供給する。比較回路 2 1 2 の出力は L V D 1 \_ 検出 1 1 2 を供給する。図示の実施態様においては、トランジスタ 2 0 4 , 2 0 8 は p 型 M O S F E T トランジスタであり、トランジスタ 2 0 6 はバイポーラトランジスタであることに注目されたい。しかしながら、別の実施態様においては、他の形式のトランジスタを使用することができる。また、種々の回路構成を用いて L V D 1 \_ 検出 1 1 2 を供給することができる。

#### 【 0 0 2 5 】

動作においては、電流源 2 0 2 は、トランジスタ 2 0 6 , 2 0 4 にバイアスをかけて基準電圧  $V_{ref}$  を生成するために使用される。 $V_{ref}$  の値は、トランジスタ 2 0 6 のベース - エミッタ間電圧 ( $V_{be}$ ) とトランジスタ 2 0 4 の閾値電圧 ( $V_{tp}$ ) との和に等しい。電流源 2 1 0 は、トランジスタ 2 0 8 にバイアスをかけて、V batt からトランジスタ 2 0 8 の閾値電圧 ( $V_{tp}$ ) を引いた値に等しい  $V_{comp}$  を生成するために使用される。 $V_{comp}$  は、比較回路 2 1 2 によって  $V_{ref}$  と比較される。 $V_{comp}$  が  $V_{ref}$  より高い場合には、比較回路 2 1 2 の出力はローである (この実施態様においてはデアサートされる)。 $V_{comp}$  が  $V_{ref}$  以下となるのに十分なように V batt が低下した場合には、比較回路の出力はローからハイに切り替わり、低電圧状態の検出を示す。従って、この時点において、L V D 1 \_ 検出 1 1 2 はアサートされて、V batt が L V 1 に達したことを示す。

#### 【 0 0 2 6 】

L V D 回路 2 0 0 の中で使用される電流源 2 0 2 , 2 1 0 は、非常に低い電流値を有している。このため、L V D 回路 2 0 0 は、普通は低電圧検出機能のために望ましい雑音排除性を有していない。しかしながら、一実施形態においては、L V D 回路 2 0 0 の動作は、M C U 1 0 2 が低電力停止モードにあって、すべてのクロックがインアクティブであるときのみ重要である。L V D 回路 2 0 0 によって生成される基準電圧  $V_{ref}$  は、プロセスパラメータの変化および温度の変化のために、高精度ではない。しかしながら、この回路は M C U 1 0 2 への割り込みを生成してシステムをシャットダウンさせるためには使用されないので、上記で説明したように、高精度は要求されない。即ち、L V D 1 ( 1 1 0 ) は、適当な条件のもとでより正確な L V D 2 ( 1 1 6 ) を有効にするためと、十分な電圧が外部的に (V batt によって) 回復して M C U 1 0 2 が再び処理を開始できるようになるまで、M C U 1 0 2 を低電力安全状態に保持するためにのみ使用される。

#### 【 0 0 2 7 】

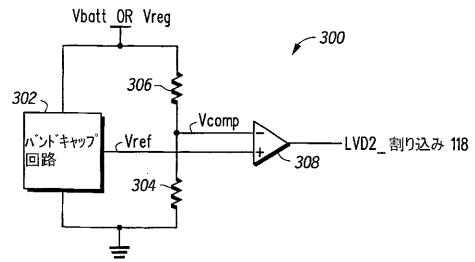

図 7 は、図 1 の L V D 2 ( 1 1 6 ) のために使用できる L V D 回路 3 0 0 の一実施形態

10

20

30

40

50

の概略図である。LVD回路300は、バンドギャップ回路302と、抵抗器306, 304と、比較回路308を含んでいる。Vbatt(電圧調整器114がない場合はVreg)は、バンドギャップ回路302の第1端子と抵抗器306の第1端子に接続されている。バンドギャップ回路302の第2端子は、比較回路308のプラス入力に接続されてVrefを供給し、バンドギャップ回路302の第3端子は、抵抗器304の第1端子と、接地ノードに接続されている。抵抗器306の第2端子は、抵抗器304の第2端子と比較回路308のマイナス入力に接続されている。比較回路308は、LVD2\_割り込み118を供給するための出力を有している。種々の実施態様は、種々の回路構成を使ってLVD2\_割り込み118を供給することができる。

## 【0028】

10

LVD回路300は、バンドギャップ基準回路(バンドギャップ回路302)を使って、正確な基準電圧Vrefを生成する。抵抗器306, 304は、Vregと基準値に対する比較のための電圧を生成するために使用される接地との間の分圧器を形成する。VcomがVrefよりも小さいか等しくなるのに十分なようにVbatt(またはVreg)が低下するたびに、比較回路308の出力はローからハイに切り替わり、低電圧状態の検出を示す(即ち、LVD2\_割り込み118をアサートする)。(バンドギャップ回路302は、この技術において公知の任意のバンドギャップ回路であってもよいことに注目されたい)。バンドギャップ回路302および抵抗器306, 304によって形成された分圧器は、いくつかの応用においては、停止モードに対して許容され得るよりも多くの電流を消費する。このため、(LVD回路300を使用する)LVD2(110)は、MCU102が低電力停止モードに入るとディスエーブルされる。よって、いかに様々な種類のLVD回路をLVD1(110)およびLVD2(116)に使用して、電流消費と精度とのバランスをとることができると明らかである。

20

## 【0029】

本発明を特定の伝導性タイプまたは電位極性に関して説明したが、伝導性タイプおよび電位極性を逆にできることは当業者にとって明らかである。

上記明細書において、本発明を特定の実施態様に関して説明した。しかしながら、特許請求の範囲に述べたような本発明の範囲から逸脱することなく、種々の変更を行うことができることは当業者にとって明らかである。例えば、ブロック図は、図示されたものとは異なるブロックを有することができ、更に多いまたは少ないブロックを有することができるか、異なるように配置することができる。また、いくつかのブロックを組み合わせることができる。例えば、別の実施態様は、高電力および低電力モードにおいて動作可能であると共に、VbattがLVD1より下がったときに標識を供給し、VbattがLVD2より下がったときに別の標識を供給することができる一つのLVDシステムに、LVD1(110)とLVD2(116)の機能を統合することができる。従って、本仕様書と図面は制限的というよりも説明的なものと見なされるべきものであって、すべてのそのような変更は、本発明の範囲内に含まれるものである。

30

## 【0030】

利点と問題に関する解決策とを特定の実施態様に関して上に説明した。しかしながら、利点と、問題に対する解決策と、すべての利点または解決策を生じさせるか一層明確にすることができるすべての要素は、いくつかのまたはすべての特許請求の範囲の重要な、必要な、または本質的な特徴または要素と解釈されるべきではない。本書で用いられたように、用語「備える」、「からなる」、またはそのすべての変形は、非排他的包含をカバーするものではないので、多くの要素からなる、プロセス、方法、物品、または装置は、それらの要素だけを含むものではなく、明確に列挙されていないか、そのようなプロセス、方法、物品、または装置に固有の他の要素を含むことができる。

40

## 【図面の簡単な説明】

## 【0031】

【図1】本発明の一実施形態によるデータ処理システムのブロック図。

【図2】本発明の一実施形態による安全状態に入り安全状態から出る方法を示すグラフ。

50

【図3】図1のデータ処理システム内の種々のユニットに対応する真理値の表。

【図4】図1のデータ処理システム内の種々のユニットに対応する真理値の表。

【図5】図1のデータ処理システム内の種々のユニットに対応する真理値の表。

【図6】図1のデータ処理システム内の低電圧検出ユニットの一実施形態の概略図。

【図7】図1のデータ処理システム内のもう一つの低電圧検出ユニットの一実施形態の概略図。

【図1】

【図2】

【図3】

| LV1_検出 112                | セーフ 136 | IH_ブロック 140 |

|---------------------------|---------|-------------|

| 0 ( $V_{BATT} > LV1$ )    | 0       | 0 (割り込み許可)  |

| 0                         | 1       | 0           |

| 1 ( $V_{BATT} \leq LV1$ ) | 0       | 0           |

| 1                         | 1       | 1 (割り込み阻止)  |

【図4】

| ウェーカップ 126 | STOP 132  | LVD2_en 130      |

|------------|-----------|------------------|

| 0          | 0 (ランモード) | 1 (LVD2 イネーブル)   |

| 0          | 1 (停止モード) | 0 (LVD2 ディスエーブル) |

| 1          | 0         | 1                |

| 1          | 1         | 1                |

【図5】

| LV1_検出 112 | セーフ 136 | STOP 132 | PWU_en 122      |

|------------|---------|----------|-----------------|

| 0          | 0       | 0        | 0 (PWU テ'イス'ブル) |

| 0          | 0       | 1        | 0               |

| 0          | 1       | 0        | 0               |

| 0          | 1       | 1        | 0               |

| 1          | 0       | 0        | 0               |

| 1          | 0       | 1        | 1 (PWU イネ'ブル)   |

| 1          | 1       | 0        | 0               |

| 1          | 1       | 1        | 0               |

【図7】

【図6】

---

フロントページの続き

(72)発明者 ルーカス、ウィリアム エル.

アメリカ合衆国 23111 バージニア州 メカニクスピル ビーティミル ドライブ 807

0

(72)発明者 ウッド、マイケル ジー.

アメリカ合衆国 78660 テキサス州 フルガービル パーククレスト コート 1000

審査官 藤原 伸二

(56)参考文献 特開平11-119871(JP, A)

特開平11-119872(JP, A)

特開平07-093066(JP, A)

特開平07-175785(JP, A)

特開昭63-103311(JP, A)

米国特許第05203000(US, A)

米国特許第05539910(US, A)

(58)調査した分野(Int.Cl., DB名)

G01R 19/00-19/32

G06F 1/00-1/32

G06F 15/76-15/78

G06F 15/02

H02J 7/00-7/36