(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-31471

(P2005-31471A)

(43) 公開日 平成17年2月3日(2005.2.3)

(51) Int.CI.<sup>7</sup>

G09C 1/00

F 1

G 09 C 1/00

テーマコード(参考)

5 J 1 O 4

審査請求 未請求 請求項の数 13 O L (全 21 頁)

|           |                              |           |                                           |

|-----------|------------------------------|-----------|-------------------------------------------|

| (21) 出願番号 | 特願2003-271525 (P2003-271525) | (71) 出願人  | 000002185<br>ソニー株式会社<br>東京都品川区北品川6丁目7番35号 |

| (22) 出願日  | 平成15年7月7日(2003.7.7)          | (74) 代理人  | 100093241<br>弁理士 宮田 正昭                    |

|           |                              | (74) 代理人  | 100101801<br>弁理士 山田 英治                    |

|           |                              | (74) 代理人  | 100086531<br>弁理士 澤田 俊夫                    |

|           |                              | (72) 発明者  | 阿部 譲司<br>東京都品川区北品川6丁目7番35号 ソニー株式会社内       |

|           |                              | (72) 発明者  | 金丸 昌司<br>東京都品川区北品川6丁目7番35号 ソニー株式会社内       |

|           |                              | F ターム(参考) | 5J104 AA18 AA47 JA13                      |

(54) 【発明の名称】暗号処理装置、および暗号処理方法

## (57) 【要約】

【課題】 消費電力の測定による暗号解析を困難としセキュリティレベルの高い暗号処理装置および方法を実現する。

【解決手段】 例えば複数段のラウンド関数部からなる共通鍵暗号処理を実行する暗号処理装置において、各段のF関数出力、すなわちSボックスから置換部を介した中間データ出力値を、第1データ格納部のRレジスタおよびL'レジスタにそのまま格納し、第2データ格納部のR'レジスタ、およびL'レジスタに出力値の反転データを格納する。本構成により、レジスタ格納処理におけるハミングウェイトの和を一定に保つことができる。その結果、デバイス消費電力の変化の観察に基づく鍵情報等、秘密情報に関するハミングウェイト情報の取得困難性が高まり、暗号解析困難性を高めることができる。

【選択図】 図6

**【特許請求の範囲】****【請求項 1】**

暗号処理装置であり、

入力データのデータ処理を実行するデータ処理部と、

前記データ処理部におけるデータ処理によって生成される中間データを構成するビットデータの反転データを生成する反転データ生成手段と、

前記中間データに対応する非反転ビットデータおよび反転ビットデータを各々格納する複数のデータ記憶部と、

を有することを特徴とする暗号処理装置。

**【請求項 2】**

前記暗号処理装置は、共通鍵暗号処理方式に従った暗号処理を実行する暗号処理装置であり、

前記データ処理部は、複数段のデータ変換部を構成し、

前記中間データは、前記データ変換部各段の出力データであることを特徴とする請求項1に記載の暗号処理装置。

**【請求項 3】**

前記複数のデータ記憶部は、

前記中間データを構成するビットデータを全く反転することなく格納する第1データ記憶部と、

前記中間データを構成するビットデータを全て反転して格納する第2データ記憶部とかなることを特徴とする請求項1に記載の暗号処理装置。

**【請求項 4】**

前記複数のデータ記憶部は、

前記中間データを構成するビットデータについて、ビット単位で反転または非反転したデータを格納する第1データ記憶部と、

前記中間データを構成するビットデータについて、前記第1データ記憶部に格納されるビットデータのビット単位の反転データを格納する第2データ記憶部とかなることを特徴とする請求項1に記載の暗号処理装置。

**【請求項 5】**

前記反転データ生成手段は、インバータであり、

前記複数のデータ記憶部中、一方のデータ記憶部はインバータを介して反転したデータを記憶する構成であることを特徴とする請求項1に記載の暗号処理装置。

**【請求項 6】**

前記暗号処理装置は、さらに、

前記複数のデータ記憶部中、前記データ処理部に対してデータを出力する中間データ記憶手段としてのデータ記憶部の出力段に出力データ反転処理手段を有し、

中間データ記憶手段としてのデータ記憶部に格納されたデータが、反転データである場合に、前記出力データ反転処理手段を介して再反転したデータを前記データ処理手段に出力する構成としたことを特徴とする請求項1に記載の暗号処理装置。

**【請求項 7】**

前記暗号処理装置は、

前記複数のデータ記憶部に対するデータ格納処理におけるハミングウェイトの和を一定に保持するように、前記中間データの非反転データおよび反転データ格納処理を実行する構成を有することを特徴とする請求項1に記載の暗号処理装置。

**【請求項 8】**

暗号処理方法であり、

入力データのデータ処理を実行するデータ処理ステップと、

前記データ処理ステップにおけるデータ処理によって生成される中間データを構成するビットデータの反転データを生成する反転データ生成ステップと、

前記中間データに対応する非反転ビットデータおよび反転ビットデータを、各々複数の

10

20

30

40

50

データ記憶部に格納するデータ記憶ステップと、

を有することを特徴とする暗号処理方法。

【請求項 9】

前記暗号処理方法は、共通鍵暗号処理方式に従った暗号処理を実行する暗号処理方法であり、

前記データ処理ステップは、複数段のデータ変換ステップを有し、

前記中間データは、前記データ変換ステップ各段の出力データであることを特徴とする請求項 8 に記載の暗号処理方法。

【請求項 10】

前記データ記憶ステップは、

前記中間データを構成するビットデータを全く反転することなく格納する第 1 データ記憶ステップと、

前記中間データを構成するビットデータを全て反転して格納する第 2 データ記憶ステップとからなることを特徴とする請求項 8 に記載の暗号処理方法。

【請求項 11】

前記データ記憶ステップは、

前記中間データを構成するビットデータについて、ビット単位で反転または非反転したデータを格納する第 1 データ記憶ステップと、

前記中間データを構成するビットデータについて、前記第 1 データ記憶ステップにおいて記憶部に格納されるビットデータのビット単位の反転データを格納する第 2 データ記憶ステップとからなることを特徴とする請求項 8 に記載の暗号処理方法。

【請求項 12】

前記暗号処理方法は、

データ記憶部の格納データが反転データであり、データ処理に適用すべきデータである場合に、格納データの再反転処理を行い、前記データ処理ステップは、該再反転データに対するデータ処理を実行することを特徴とする請求項 8 に記載の暗号処理方法。

【請求項 13】

前記暗号処理方法は、

前記複数のデータ記憶部に対するデータ格納処理におけるハミングウェイトの和を一定に保持するように、前記中間データの非反転データおよび反転データ格納処理を実行することを特徴とする請求項 8 に記載の暗号処理方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、暗号処理装置および暗号処理方法に関する。さらに詳細には、暗号処理を実行する例えば I C モジュール等の演算回路における電力解析に基づく暗号解析に対する耐性の高い暗号処理を実現する暗号処理装置および暗号処理方法に関する。

【背景技術】

【0002】

昨今、ネットワーク通信、電子商取引の発展に伴い、通信におけるセキュリティ確保が重要な問題となっている。セキュリティ確保の 1 つの方法が暗号技術であり、現在、様々な暗号化手法を用いた通信が実際に用いられている。

【0003】

例えば I C カード等の小型の装置中に暗号処理モジュールを埋め込み、I C カードと、データ読み取り書き込み装置としてのリーダライタとの間でデータ送受信を行ない、認証処理、あるいは送受信データの暗号化、復号化を行なうシステムが実用化されている。

【0004】

暗号処理モジュールにおいては、例えば、平文を入力し暗号文を出力するデータ暗号化処理、あるいは暗号文を入力し平文を出力する復号化処理が実行される。これらの暗号処理は、暗号処理モジュールを構成するハードウェア、例えば半導体による電気的な処理を

10

20

30

40

50

含む。従って、このような半導体モジュールにおいて暗号処理が実行される際の電力消費を解析することで、暗号処理の適用鍵や、アルゴリズムが解析されてしまうという恐れがある。

#### 【0005】

例えば、I C 等の演算処理装置に対する攻撃、すなわち暗号解読攻撃として、処理時間を解析することによる秘密情報を推定するタイミングアタック ( T A : T i m i n g a t t a c k ) 、暗号処理時の消費電力の観測により秘密情報を推定する単純電力解析 ( S P A : S i m p l e P o w e r A n a l y s i s ) 、さらに、大量のデータに対する暗号処理における消費電力を測定し、それらの測定データを統計的に解析することにより秘密情報を推定する電力差分解析 ( D P A : D i f f e r e n t i a l P o w e r A n a l y s i s ) 等がある。10

#### 【0006】

一般的な暗号処理装置は、データ入力部と記憶部と暗号処理部、およびデータ出力部とから構成されており、例えば入力データの暗号化を行う場合は、次のように動作する。すなわち、データ入力部から暗号処理部に平文が入力される。暗号処理部は、例えば D E S ( Data Encryption Standard ) などの暗号処理アルゴリズムを実行する処理部において一定の暗号処理アルゴリズムに従ったデータ処理がなされる。

#### 【0007】

暗号処理アルゴリズムの実行過程において生成される中間データを逐次、記憶部に格納し、また記憶部に格納した中間データを取得して予め定められた一定の処理順序に従って暗号化処理が実行される。暗号処理部において、予め定められた一連の暗号処理アルゴリズムが終了すると、生成暗号文が出力部を介して出力される。20

#### 【0008】

このような暗号処理装置において、暗号化処理の開始時から特定の暗号化中間処理手続きが開始されるまでに要する時間は、おおよそ一定になる。なお、暗号アルゴリズムの実装方法については、例えば非特許文献 1 に詳しく述べられている。

#### 【0009】

このような暗号処理装置は、前述した単純電力解析 ( シンプル・パワー・アナリシス ) や電力差分解析 ( ディファレンシャル・パワー・アナリシス ) と呼ばれる暗号解析法を適用することで、暗号処理に適用する鍵情報や、アルゴリズムが解析される恐れがある。30

#### 【0010】

単純電力解析および電力差分解析は、現在のメモリやレジスタ等の半導体デバイスにおいて、特定の時刻に、半導体デバイスの保持する値に変化が生じた場合と、保持する値に変化が生じなかつた場合とで、消費電力に差が発生するという特徴を利用して、暗号処理装置が暗号処理を実行している様々なタイミングにおいて消費電力を測定することにより、暗号処理装置が保持している暗号鍵等の秘密情報を特定する暗号解析法である。

#### 【0011】

単純電力解析や電力差分解析が有効に機能する条件としては、第 1 に消費電力を測定している各時点で行われている暗号処理手続きが特定できること、第 2 に各時刻で測定した消費電力の値が当該時刻において暗号化装置内で行われている暗号化処理の演算結果を顕著に反映していること、の 2 点が挙げられる。40

#### 【0012】

従来の暗号化装置、復号化装置および暗号化・復号装置等の暗号処理装置においては、上記の 2 点の条件が満たされてしまうために、単純電力解析や電力差分解析が有効に機能し、暗号の解読が可能になりうるという問題点が存在した。

#### 【0013】

この問題に対処するため、いくつかの方法が提案してきた。例えば特許文献 1 には差分解読や線形解読を防止することを目的としたデータの暗号化方法及び装置が記載されている。本文献には、データを複数ブロックに分割して、ブロックを順次、暗号化する構成において、暗号処理対象のブロックに適用する鍵を、前の処理ブロックの中間結果から導50

く構成とすることにより、ブロック毎に異なる鍵を適用した処理を行うものであり、結果として統計的な鍵推定を困難としたものである。

#### 【0014】

また、特許文献2には、暗号処理に適用する鍵情報の漏洩を防止した構成が示されている。本文献に記載の構成は、暗号化された鍵情報を不揮発性メモリに格納し、電源投入時に不揮発性メモリから暗号化された鍵情報を復号し、復号の結果としての鍵情報を揮発性メモリに格納して、これを暗号処理に適用するとともに、電源遮断時に揮発性メモリから鍵情報を能動的に消去することにより、鍵情報の漏洩を防止したものである。

#### 【0015】

また、特許文献3には、電力解析および電力差分解析等の消費電力の測定による暗号解析に対して耐性のある暗号化装置が示されている。本文献に記載の構成は、中間データ制御手段が、暗号処理において生成される中間データを乱数によって変化させ、この乱数によって変化した中間データに基づく暗号処理を実行する構成とし、さらに最終的な出力(暗号文)については、乱数に依存しないデータとすることを可能としたものである。本構成においては、暗号処理デバイスの状態変化は、乱数によって変化した中間データに基づく変化となり、その結果、電力解析および電力差分解析等、消費電力の測定による暗号解析の困難性が高まるというものである。

#### 【0016】

上述したように、暗号鍵あるいはアルゴリズムの漏洩に対する対策についての提案は様々存在するが、例えば特許文献1に記載の構成は、ブロック単位で、処理済みブロックから中間データを抽出し、新たな鍵を生成するといった複雑な処理が必要となり、演算処理効率の低下、処理遅延という問題を発生させる恐れがある。また、特許文献2に記載の構成は、鍵データそのものの漏洩を防止する効果は有するものの、暗号処理実行中の単純電力解析および電力差分解析等、消費電力の測定による暗号解析に対する対策とはなっていない。さらに、特許文献3に記載の乱数を利用した方法については、高階電力差分解析と呼ばれる暗号解析法によって攻撃が可能なことがMessagesによって既に示されている。例えば、[“Using Second-Order Power Analysis to Attack DPA Resistant Software”, T.S. Messges, CHES 2000]に説明が記述されている。

#### 【0017】

暗号処理を実行する例えばICモジュールは、例えば駅の改札などの様々なゲート、あるいはショッピングセンターなどで盛んに利用されるようになっており、小型化および処理の迅速化の要求が厳しくなってきている。従って、処理アルゴリズムを複雑化させることなく、かつ、電力差分解析や、高階電力差分解析に対する耐性のある構成が必要とされている。

#### 【特許文献1】特開平9-230786号公報

#### 【特許文献2】特開平8-504067号公報

#### 【特許文献3】特開2000-305453号公報

【非特許文献1】『Applied Cryptography』(Bruce Schneier著) John Wiley & Sons, Inc., 1996, ISBN 0-471-11709-9, pp. 623 - 673』

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0018】

本発明は、上記問題点に鑑みてなされたものであり、処理アルゴリズムを複雑化させることなく、暗号処理シーケンスの持つ規則的な処理に伴う消費電力変動の検出等に基づく単純電力解析、電力差分解析や高階電力差分解析による暗号解析の困難性を高めることを可能とした暗号処理装置および暗号処理方法を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0019】

10

20

30

40

50

本発明の第1の側面は、

暗号処理装置であり、

入力データのデータ処理を実行するデータ処理部と、

前記データ処理部におけるデータ処理によって生成される中間データを構成するビットデータの反転データを生成する反転データ生成手段と、

前記中間データに対応する非反転ビットデータおよび反転ビットデータを各々格納する複数のデータ記憶部と、

を有することを特徴とする暗号処理装置にある。

#### 【0020】

さらに、本発明の暗号処理装置の一実施態様において、前記暗号処理装置は、共通鍵暗号処理方式に従った暗号処理を実行する暗号処理装置であり、前記データ処理部は、複数段のデータ変換部を構成し、前記中間データは、前記データ変換部各段の出力データであることを特徴とする。 10

#### 【0021】

さらに、本発明の暗号処理装置の一実施態様において、前記複数のデータ記憶部は、前記中間データを構成するビットデータを全く反転することなく格納する第1データ記憶部と、前記中間データを構成するビットデータを全て反転して格納する第2データ記憶部とからなることを特徴とする。 20

#### 【0022】

さらに、本発明の暗号処理装置の一実施態様において、前記複数のデータ記憶部は、前記中間データを構成するビットデータについて、ビット単位で反転または非反転したデータを格納する第1データ記憶部と、前記中間データを構成するビットデータについて、前記第1データ記憶部に格納されるビットデータのビット単位の反転データを格納する第2データ記憶部とからなることを特徴とする。 20

#### 【0023】

さらに、本発明の暗号処理装置の一実施態様において、前記反転データ生成手段は、インバータであり、前記複数のデータ記憶部中、一方のデータ記憶部はインバータを介して反転したデータを記憶する構成であることを特徴とする。

#### 【0024】

さらに、本発明の暗号処理装置の一実施態様において、前記暗号処理装置は、さらに、前記複数のデータ記憶部中、前記データ処理部に対してデータを出力する中間データ記憶手段としてのデータ記憶部の出力段に出力データ反転処理手段を有し、中間データ記憶手段としてのデータ記憶部に格納されたデータが、反転データである場合に、前記出力データ反転処理手段を介して再反転したデータを前記データ処理手段に出力する構成としたことを特徴とする。 30

#### 【0025】

さらに、本発明の暗号処理装置の一実施態様において、前記暗号処理装置は、前記複数のデータ記憶部に対するデータ格納処理におけるハミングウェイトの和を一定に保持するように、前記中間データの非反転データおよび反転データ格納処理を実行する構成を有することを特徴とする。 40

#### 【0026】

さらに、本発明の第2の側面は、

暗号処理方法であり、

入力データのデータ処理を実行するデータ処理ステップと、

前記データ処理ステップにおけるデータ処理によって生成される中間データを構成するビットデータの反転データを生成する反転データ生成ステップと、

前記中間データに対応する非反転ビットデータおよび反転ビットデータを、各々複数のデータ記憶部に格納するデータ記憶ステップと、

を有することを特徴とする暗号処理方法にある。

#### 【0027】

10

20

30

40

50

さらに、本発明の暗号処理方法の一実施態様において、前記暗号処理方法は、共通鍵暗号処理方式に従った暗号処理を実行する暗号処理方法であり、前記データ処理ステップは、複数段のデータ変換ステップを有し、前記中間データは、前記データ変換ステップ各段の出力データであることを特徴とする。

#### 【0028】

さらに、本発明の暗号処理方法の一実施態様において、前記データ記憶ステップは、前記中間データを構成するビットデータを全く反転することなく格納する第1データ記憶ステップと、前記中間データを構成するビットデータを全て反転して格納する第2データ記憶ステップとからなることを特徴とする。

#### 【0029】

さらに、本発明の暗号処理方法の一実施態様において、前記データ記憶ステップは、前記中間データを構成するビットデータについて、ビット単位で反転または非反転したデータを格納する第1データ記憶ステップと、前記中間データを構成するビットデータについて、前記第1データ記憶ステップにおいて記憶部に格納されるビットデータのビット単位の反転データを格納する第2データ記憶ステップとからなることを特徴とする。

#### 【0030】

さらに、本発明の暗号処理方法の一実施態様において、前記暗号処理方法は、データ記憶部の格納データが反転データであり、データ処理に適用すべきデータである場合に、格納データの再反転処理を行い、前記データ処理ステップは、該再反転データに対するデータ処理を実行することを特徴とする。

#### 【0031】

さらに、本発明の暗号処理方法の一実施態様において、前記暗号処理方法は、前記複数のデータ記憶部に対するデータ格納処理におけるハミングウェイトの和を一定に保持するよう、前記中間データの非反転データおよび反転データ格納処理を実行することを特徴とする。

#### 【0032】

本発明のさらに他の目的、特徴や利点は、後述する本発明の実施例や添付する図面に基づくより詳細な説明によって明らかになるであろう。なお、本明細書においてシステムとは、複数の装置の論理的集合構成であり、各構成の装置が同一筐体内にあるものには限らない。

#### 【発明の効果】

#### 【0033】

本発明の構成によれば、処理アルゴリズムを複雑化することなく、様々な解析攻撃に対する耐性の高い暗号処理装置および暗号処理方法が実現される。

#### 【0034】

本発明の構成によれば、データの暗号化や復号を行う際に当該装置の消費電力を測定することによって暗号化鍵や復号鍵等の秘密情報を得る暗号解析法、すなわち、電力解析や電力差分解析等の消費電力の測定による暗号解析を困難とし、かつ、高階電力差分攻撃の適用についても困難とすることが可能となる。

#### 【0035】

本発明の構成によれば、例えば複数段のラウンド関数部からなる共通鍵暗号処理を実行する暗号処理装置において、各段のF関数出力、すなわちSボックスから置換部を介した中間データ出力値を、第1データ格納部のRレジスタおよびLレジスタにそのまま格納し、第2データ格納部のR'レジスタ、およびL'レジスタに出力値の反転データを格納する。本構成により、レジスタ格納処理におけるハミングウェイトの和を一定に保つことができる。その結果、デバイス消費電力の変化の観察に基づく鍵情報等、秘密情報に関するハミングウェイト情報の取得困難性が高まり、暗号解析困難性を高めることができる。

#### 【発明を実施するための最良の形態】

#### 【0036】

以下、本発明の暗号処理装置および暗号処理方法の詳細について説明する。

10

20

30

40

50

## 【実施例 1】

## 【0037】

暗号処理アルゴリズムには様々なものがあるが、大きく分類すると、暗号化鍵と復号化鍵を異なる鍵、例えば公開鍵と秘密鍵として設定する公開鍵暗号方式と、暗号化鍵と復号化鍵を共通の鍵として設定する共通鍵暗号方式とに分類される。

## 【0038】

共通鍵暗号方式の1つに共通鍵をベースとして複数の鍵を生成して、生成した複数の鍵を用いて暗号処理を繰り返し実行する方式がある。このような鍵生成方式を適用したアルゴリズムの代表的なものが共通鍵ブロック暗号方式である。

## 【0039】

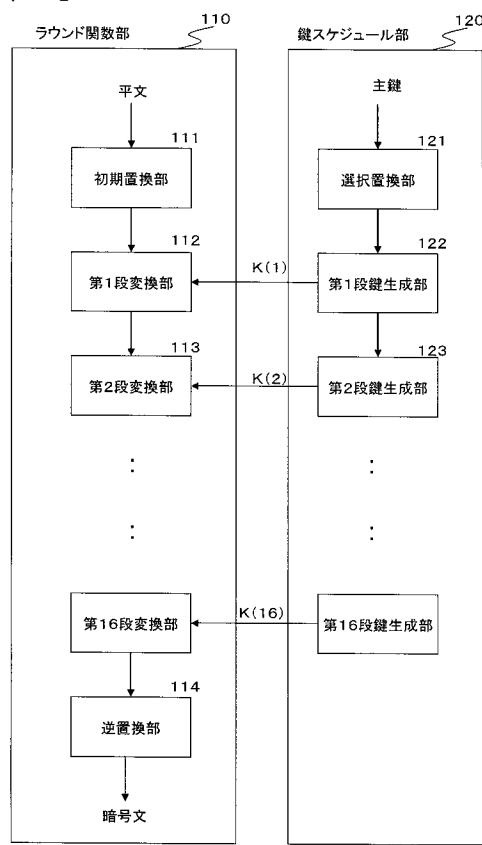

共通鍵ブロック暗号のアルゴリズムは、主として、入力データの変換を実行するラウンド関数部と、ラウンド関数部の各ラウンドで適用する鍵を生成する鍵スケジュール部とに分けることができる。ラウンド関数部の各ランウドで適用する鍵（副鍵）は、1つの主鍵に基づいて、鍵スケジュール部に入力されて生成され、各ラウンド関数部で適用される。この共通鍵暗号方式の代表的な方式に米国連邦標準暗号方式としてのDES（Data Encryption Standard）がある。

## 【0040】

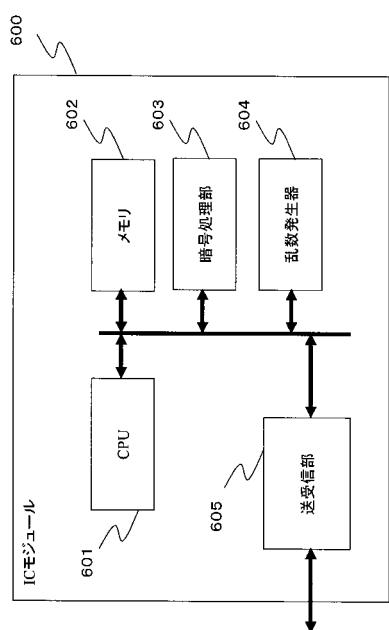

DES暗号処理の基本構造について、図を参照して説明する。DES暗号処理は、変換関数の単純な繰り返しにより、平文を暗号文に変換する構造を持つ。図1にDES暗号処理の基本構成を示す。入力データの変換を実行するラウンド関数部110と、ラウンド関数部の各ラウンドで適用する鍵を生成する鍵スケジュール部120とによって構成される。

## 【0041】

ラウンド関数部110において、平文（64ビット）は、まず、初期置換部111において、L, R各32ビットに分割され、分割されたL, R32ビットが、第1段変換部112に入力され、鍵スケジュール部120の第1段鍵生成部122から入力する鍵K（1）に基づいて変換処理がなされる。変換処理結果は、次段の第2段変換部113に入力される。

## 【0042】

鍵スケジュール部120においては、まず、選択置換部121により入力主鍵（64ビット）のパリティ8ビットが取り除かれ、残り56ビットの入れ替え処理が実行されて第1段鍵生成部122に入力される。第1段鍵生成部122では、入力ビット列のシフト処理およびパリティビットの除去等が実行され、48ビットの副鍵K（1）を生成し、生成した副鍵K（1）をラウンド関数部110の第1段変換部112に出力する。第1段鍵生成部122では、シフト処理による上位ビット列（28ビット）と下位ビット列（28ビット）とを下段の第2段鍵生成部123に出力する。

## 【0043】

ラウンド関数部は、16段の変換部を有し、それぞれ前段の変換部の出力を入力として鍵スケジュール部120から入力する鍵を適用した変換処理を実行し、変換結果を後段の変換部に出力する。16段の変換部で変換された出力が逆置換部114に入力され、初期置換部111の逆置換処理が実行されて、暗号文として出力される。

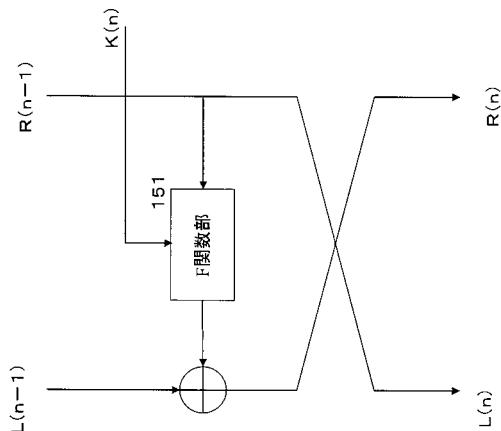

## 【0044】

ラウンド関数部110の各ラウンドを構成する変換部の構成を図2に示す。図2に示すように、変換部は、前段（n-1段）の変換部から2つの入力、L（n-1）、R（n-1）を入力し、鍵スケジュール部から鍵（k（n））を入力する。F関数部151において、鍵スケジュール部から入力する鍵（k（n））を用いて、前段変換部から入力するビット列（R（n-1））の変換処理がなされ、変換結果が、前段変換部から入力する残りのビット列（L（n-1））と排他論理和が実行されて、次段の変換部の出力R（n）が生成される。次段の変換部には、R（n-1）をL（n）としたビット列と、上述のF関数および排他論理和演算により生成されたR（n）が入力され同様の処理が繰り返される

10

20

30

40

50

。

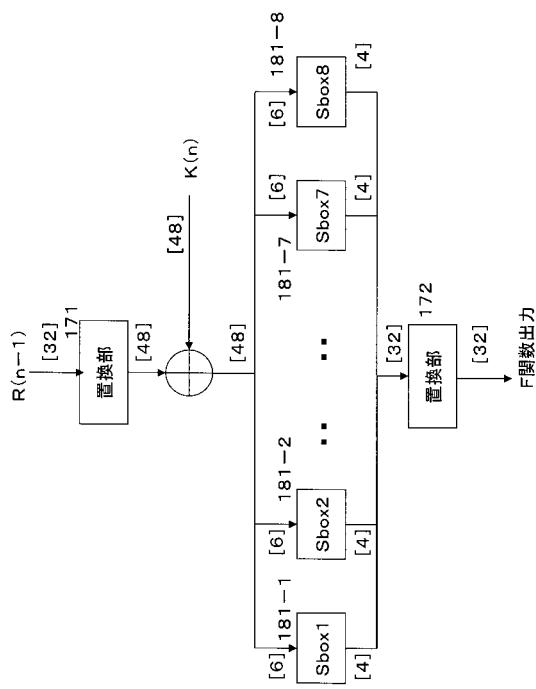

#### 【 0 0 4 5 】

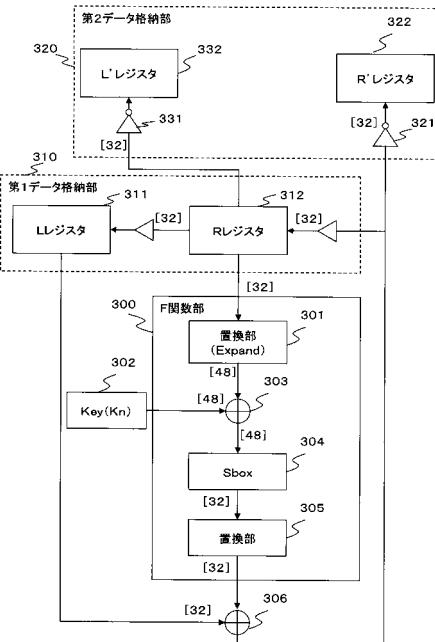

F 関数の構成を図 3 に示す。F 関数は、非線形処理を実行する複数の S ボックス (S box) を有する。ラウンド関数部の前段からの入力値 R (n - 1) は置換部 171 によって 48 ビットに拡大され、さらに鍵スケジュール部から入力する鍵 (48 ビット) と排他論理和が実行され、その出力が 6 ビットずつ非線形変換処理を実行する複数の S ボックス 181 - 1 ~ 8 に入力される。各 S ボックスでは、例えば変換テーブルを適用した 6 ビットから 4 ビットへの非線形変換処理が実行される。

#### 【 0 0 4 6 】

S ボックス 181 - 1 ~ 8 からの出力ビット  $4 \times 8 = 32$  ビットは、置換部 172 に入力されて、ビット位置の入れ替え処理がなされ、F 関数出力 32 ビットを生成して出力する。

#### 【 0 0 4 7 】

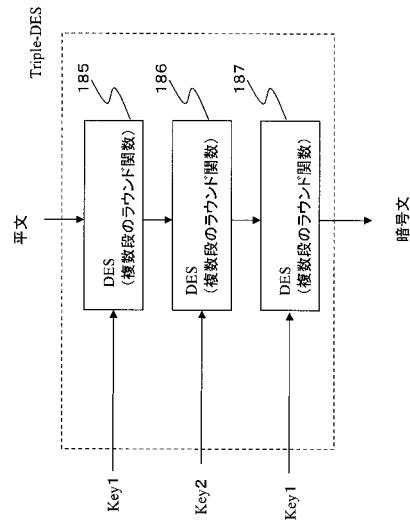

図 1 ~ 3 を参照して説明したように複数段 (16 段) の変換処理によって DES 暗号処理が実行される。この DES 暗号処理をさらに暗号強度を高めるため複数繰り返し実行する構成、例えば 3 回の DES 暗号処理を実行するトリプル DES 暗号処理が様々な分野、例えばインターネットを介したデータ通信機器間の相互認証処理や、I C カードとリーダライタ間の相互認証処理等に適用する暗号処理として多く採用されている。なお、トリプル DES 暗号処理と区別するため、1 回の DES 暗号処理をシングル DES 暗号処理と呼ぶ。

#### 【 0 0 4 8 】

トリプル DES (Triple DES) 暗号処理構成は、図 4 に示すように、図 1 ~ 3 を参照して説明した DES 暗号処理を 3 回繰り返して実行することにより、平文から暗号文を生成する。シングル DES 暗号処理部 185, 186, 187 のそれぞれが上述した 16 段のラウンド関数部を持ち、S ボックスを持つ F 関数による処理を 16 回繰り返す。

#### 【 0 0 4 9 】

通常、トリプル DES 暗号処理では、最初のシングル DES 暗号処理部 185 と、最後の DES 暗号処理部 187においては同じ主鍵 (K1) を適用し、中間の DES 暗号処理部 186 には異なる主鍵 (K2) を適用する。このように、DES 暗号処理を複数回繰り返し実行することで、暗号強度を向上させることができる。

#### 【 0 0 5 0 】

しかし、このような共通鍵暗号処理においては、暗号解析による鍵、あるいは暗号アルゴリズムの漏洩が問題となっている。暗号解析手法としては、複数の種類がある。まず、単純電力解析 (SPA : Simple Power Analysis) について説明する。スマートカードなどの耐タンパデバイスのほとんどはトランジスタで構成された論理回路からなり、ゲートに電圧が加えられたときに電流が流れ、電力が消費される。一般に回路の消費電力は、実行している演算と用いられているデータの値に関係する。例えば、乗法演算は 0 を書き込む場合よりも 1 を書き込む場合のほうが消費電力が大きくなり、乗法演算と平方演算ではそれぞれ異なる電力を消費する。

#### 【 0 0 5 1 】

このように演算やデータ値に応じて電力消費量が変動することから、秘密情報を用いた演算を行っているデバイスの消費電力の変化を観察することで、秘密情報に関してハミングウェイトなどの情報を得ることが可能となり、エントロピーを小さくすることができる。消費電力の変化を直接解析に用いる方法を単純電力解析と呼ぶ。

#### 【 0 0 5 2 】

デバイスの消費電力は、デバイスと電源または接地との間に抵抗を直列に挿入し、抵抗を流れる電流値から求めることができる。実際に共通鍵暗号の演算を行っているスマートカードに対して消費電力測定を行うと、測定波形より共通鍵暗号の各段の演算がはっきり確かめられる。さらに、消費電力波形を詳しく解析することにより鍵レジスタの交換等の

10

20

30

40

50

情報を得ることができる。

【0053】

次に、電力差分解析 (DPA : Differential Power Analysis) について説明する。耐タンパデバイスの消費電力は一般に演算内容と演算に用いられている秘密情報に依存する。しかしこれらの内容に依存した消費電力の変化は小さく、測定誤差やノイズなどから見分けることは一般に困難である。

【0054】

そこでKocherらは大量の測定値の平均をとって測定誤差やノイズなどの影響を小さくし、全データの平均値との差分を取ることで演算プロセスによる電力消費の影響を除いて、用いられる秘密情報による消費電力の変化のみを取り出す方法（電力差分解析）を提案した。10

【0055】

KocherらはDESに対する適用例を示している。まず、ラウンド関数部の第1段、または第16段に入る鍵の一部のビットについて予想し、第1段、または第16段の最後にメモリに書きこまれると予想されるデータの1ビットの値に注目して、その値に従って消費電力の観測データを分類する。次にそれぞれのグループについて測定値の平均をとり、それらの差分をとる。予想が正しい場合注目したビットが演算に用いられるとき消費電力の差分が大きくなる。予想が異なる場合目立った差分は確認されない。

【0056】

電力差分解析は、具体的には、以下の手順（ステップ1～ステップ7）に従った解析が行われる。20

（ステップ1）

$m$ 回暗号化プロセスを観測し、それぞれ第16段の消費電力の変化  $T_1, \dots, T_m$  を観測する。さらに、暗号文  $C_1, \dots, C_m$  を記録する。第16段の消費電力の変化を解析に用いる場合、平文の情報は必要ない。なお、 $m$  は1000程度で十分である。

【0057】

（ステップ2）

鍵に依存した分配関数  $D(K_s, C)$  を選択する。ただし、 $K_s$  は何らかの鍵情報、 $C$  は暗号文である。

例えば、最終段のSボックス1の出力の1ビット目の値に着目し、Sボックス1に供給される6ビットの部分鍵を推定する場合を考える。この場合、関数  $D$  は次式で与えられる。30

【0058】

【数1】

$$D(C_1, C_6, K_{16}) = C_1 \oplus SBOX_1(C_6 \oplus K_{16})$$

40

【0059】

ただし、

$K_{16}$  は、第16段にSボックス1に供給される6ビットの部分鍵の予想値、

$C_6$  は  $K_{16}$  と排他論理和 (XOR) される暗号文の6ビット、

$SBOX_1(x)$  はSボックス1に6ビット  $x$  が供給された場合の出力結果の1ビット目、

$C_1$  は  $SBOX_1$  の出力結果に排他論理和 (XOR) される暗号文の1ビットである。

【0060】

（ステップ3）

50

関数 D を用いて T<sub>1</sub>, …, T<sub>m</sub> を 2 つのグループに分ける。

$$S_0 = \{ T_i \mid D(\cdot, \cdot, \cdot) = 0 \}$$

$$S_1 = \{ T_i \mid D(\cdot, \cdot, \cdot) = 1 \}$$

【0061】

次に、それぞれのグループについて消費電力の平均値を取る。

【0062】

【数2】

$$A_0 = \frac{1}{|S_0|} \sum_{T_i \in S_0}$$

10

$$T_1 = \frac{1}{|S_1|} \sum_{T_i \in S_1} T_i$$

20

【0063】

ただし、|S<sub>0</sub>| + |S<sub>1</sub>| = m である。

【0064】

(ステップ4)

A<sub>0</sub> と A<sub>1</sub> の差分をとり、電力差分信号 D を得る。

$$D = A_0 - A_1$$

【0065】

(ステップ5)

部分鍵の予想値 K<sub>s</sub> が正しくない場合、D(·, ·, ·) は暗号文に対してほぼランダムに“0”と“1”を出力する。従って十分多くのサンプルを取ると、D の値は 0 に近づいていく。ただし、実際には正しい予想値 K<sub>s</sub> との相互作用のため、D の波形は完全にはフラットにならない。K<sub>s</sub> が正しい場合は、D(·, ·, ·) は注目したビットの実際の値と同じ値を取るため、m とすることで、D は注目したビットを用いるときに消費する電力に近づいていく。

30

【0066】

他のデータ値や測定誤差など D(·, ·, ·) に依存しないものは 0 に近づいていく。消費電力はデータのビット値に依存するため、D(·, ·, ·) の波形は注目したビットが用いられる領域でパルスを見せ、それ以外の領域では平坦になる。

40

【0067】

(ステップ6)

以上を繰り返し、S ボックス 1 に供給される部分鍵を推定する。反復の最大値は 2<sup>6</sup> = 64 回である。

【0068】

(ステップ7)

同様の作業を残り 7 つの S ボックスについて行い、秘密鍵について 48 ビットの情報を得る。残りの 8 ビットの鍵情報は全探索によって求める。これは、DES に関する例であるが、Camellia 等で利用されている 8 × 8 S box についても同様に適用が可能である。

50

## 【0069】

次に、高階電力差分解析について説明する。

上に述べた電力差分解析はサンプルの一つのイベントに基づいた情報に対して解析を行っているが、高次電力差分解析は複数のイベントに基づいた情報を関連付けて解析に用いる。分配関数Dはサンプルごとにそれぞれ異なる重み付けをしたり、2つ以上のグループ分けをしたりすることができる。そのような関数は多くの防御策を封じ、平文や暗号文の情報が不完全な場合でも解析が可能な場合がある。また、特徴的な統計的性質を持つサンプルに対しては、単純に平均をとるのではなく別の処理を行うことが有効である。

## 【0070】

図1～図4を参照して説明した複数段(16段)の変換処理によって暗号処理が実行される場合、各段の処理結果、すなわち中間データが、一旦、記憶部としてのレジスタに格納され、次の処理段での処理の開始時にレジスタから中間データが取り出されて次段の処理が実行される。すなわち、レジスタへの中間データの格納、およびレジスタからの中間データの取り出しが繰り返し実行されることになる。

## 【0071】

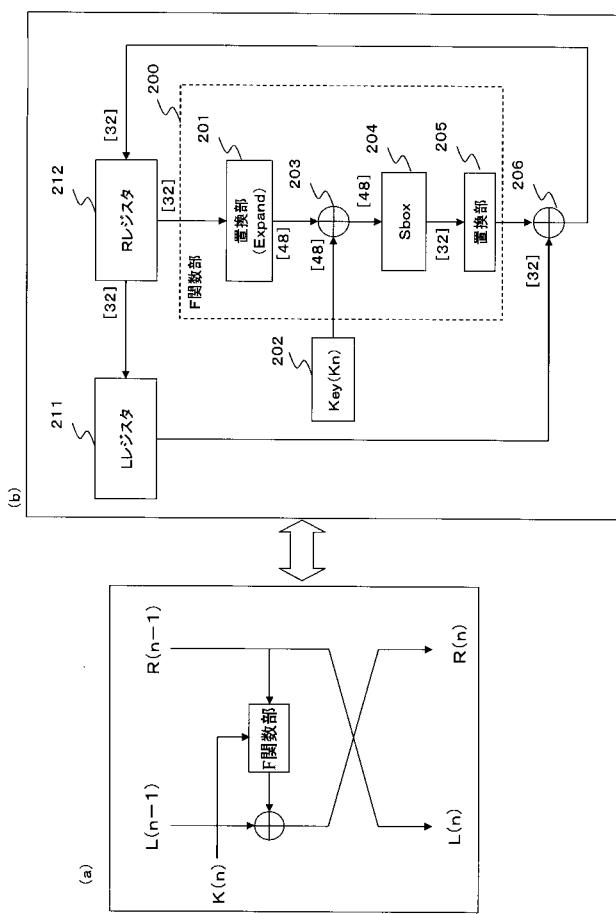

具体的な処理について、図5を参照して説明する。図5には、Sボックス(Sbox)204を持つF関数の構成および中間データ記憶部としてのレジスタ207, 208を持つ暗号処理デバイスの構成例である。

## 【0072】

図1～図4を参照して説明した複数段(16段)の変換処理を実行する場合、各処理段毎に生成する中間データがレジスタ207, 208に格納され、次の処理段では、レジスタ207およびレジスタ208から中間データが取り出されて処理が実行される。

## 【0073】

図5(a)は図2に示す変換処理部に相当し、その詳細および中間データ記憶部としてのレジスタを示したのが図5(b)である。前段(n-1段)の処理結果、すなわち、L(n-1)、R(n-1)は、それぞれLレジスタ211、Rレジスタ212に格納され、Rレジスタ212の32ビットデータがF関数部200に入力され、置換部201において、32ビットから48ビットに拡大置換される。置換部201は、図3の置換部171に相当する。

## 【0074】

さらに置換部201の出力に対して、鍵スケジュール部から鍵(k(n))202が適用されて、排他論理和(XOR)部203において排他論理和演算処理がなされ、処理結果がSボックス204に入力される。Sボックスにおいて非線形変換が実行され、Sボックス204出力が置換部205でビット入れ替え等の置換処理が実行された後、置換結果が、排他論理和(XOR)部206においてLレジスタ211の格納値と排他論理和演算処理がなされ、その結果が、Rレジスタ212、Lレジスタ211に格納される。これらの格納データがさらに次の段の処理において取り出されて同様の処理が繰り返されることになる。

## 【0075】

単純電力解析、電力差分解析、高階電力差分解析に対する対処を考慮しない、図5に示すような実装では、F関数部200の出力が直接レジスタに蓄えられ、後段の処理には、レジスタからのデータ取り出しを実行して取り出したデータに基づく処理が実行される。

## 【0076】

これらの処理を実行するデバイスは、トランジスタで構成された論理回路であり、前述したように、実行している演算と用いられているデータの値に関係する消費電力が発生する。例えば、レジスタに対するデータ書き込みにおいて、0を書き込む場合と1を書き込む場合とで異なる消費電力を示すことになる。従って、レジスタに対する中間データの書き込み、読み取りを繰り返し実行する演算を行っているデバイスの消費電力の変化を観察することで、秘密情報の解析を行うことが可能となる。

## 【0077】

10

20

30

40

50

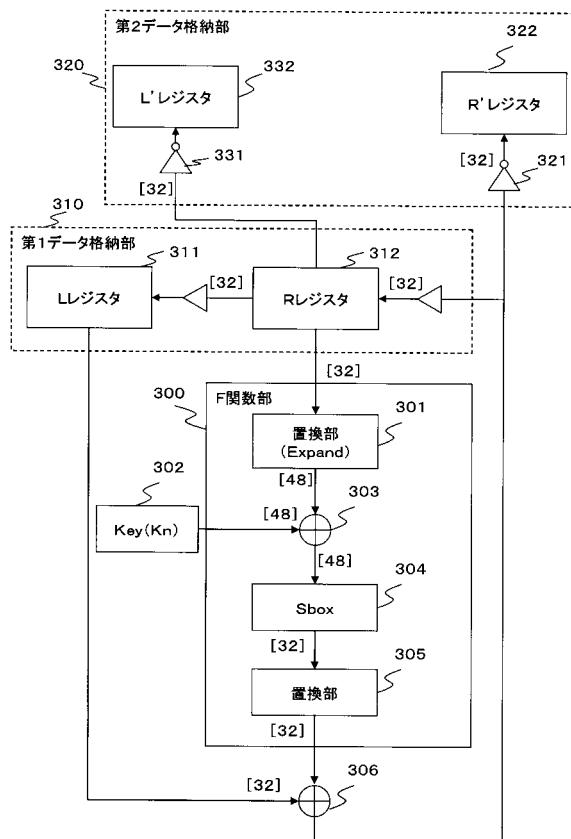

本発明に係る暗号処理装置のデータ処理部としての変換処理部およびデータ記憶部としてのレジスタに対するデータ記憶構成の具体的構成例を図6に示す。図6に示す本発明の暗号処理装置構成においては、上述した、単純電力解析、電力差分解析、高階電力差分解析に対応するため、Sボックス304の出力に基づくF関数部300からの出力は配線によって2つに分岐され、一方は、出力値を変更することなく、第1データ格納部310に入力されて、Rレジスタ312およびLレジスタ311に格納される。もう一方は第2データ格納部320に入力され、インバータ321, 322を介して出力値が反転された後、R'レジスタ322、およびL'レジスタ332に格納される。

#### 【0078】

レジスタにビット値を保存する際に消費される電力はSボックス304の出力のハミングウェイトに比例する（より厳密には相関が大きい）ので、このように出力値をそのまま格納する第1データ格納部310のRレジスタ312およびLレジスタ311と、出力値の反転データを格納する第2データ格納部320のR'レジスタ322、およびL'レジスタ332に分岐させてデータを格納することにより、双方のハミングウェイトの和を常に一定に保つことができ、上述したデバイスの消費電力の変化を観察することによる秘密情報に関するハミングウェイトの情報取得が困難となり、消費電力の変化に基づく解析の困難性を高めることができる。

#### 【0079】

なお、各レジスタに対する非反転データおよび反転データの格納タイミングは、ずれのないタイミングで並列に実行することが好ましい。このようなタイミング制御を行うことで、時間軸に沿ったデバイスの消費電力の変化に関するハミングウェイトの情報取得が困難となる。

#### 【0080】

図6に示す構成に基づく処理について説明する。図6の構成は、暗号処理を実行する複数段の変換処理を繰り返し実行するF関数を含む変換処理部および中間データ記憶部としてのレジスタを示す図である。

#### 【0081】

前段( $n - 1$ 段)の処理結果、すなわち、L( $n - 1$ )、R( $n - 1$ )は、それぞれ第1データ格納部310のLレジスタ311、Rレジスタ312に格納され、Rレジスタ312の32ビットデータがF関数部300に入力され、置換部301において、32ビットから48ビットに拡大置換される。置換部301は、図3の置換部171に相当する。

#### 【0082】

さらに置換部301の出力に対して、鍵スケジュール部から鍵( $k(n)$ )302が適用されて、排他論理和(XOR)部303において排他論理和演算処理がなされ、処理結果がSボックス304に入力される。Sボックス304において非線形変換が実行され、Sボックス304出力が置換部305でビット入れ替え等の置換処理が実行された後、置換結果が、排他論理和(XOR)部306において第1データ格納部310のLレジスタ311の格納値と排他論理和演算処理がなされる。

#### 【0083】

その結果は、第1データ格納部310のRレジスタ312、Lレジスタ311に格納され、これらの格納データがさらに次の段の処理において取り出されて同様の処理が繰り返される。さらに、本実施例の構成では、Sボックス304から置換部305を介した出力値が、インバータ321によってビットデータが反転され、第2データ格納部320のR'レジスタ322に格納される。R'レジスタ322に格納される値は、Rレジスタ312に格納される32ビットデータを反転した32ビットデータとなる。

#### 【0084】

さらに、第1データ格納部310のLレジスタ311に格納される32ビットデータに対応して、インバータ331によってビットデータが反転され、第2データ格納部320のL'レジスタ332に格納される。L'レジスタ332に格納される値は、Lレジスタ311に格納される32ビットデータを反転した32ビットデータとなる。

10

20

30

40

50

## 【0085】

第2データ格納部320のR'レジスタ322、およびL'レジスタ332に格納されたビットデータは、次の段の処理には利用されない。

## 【0086】

このように、本実施例の構成では、Sボックス304から置換部305を介した出力値が、第1データ格納部310のRレジスタ312およびLレジスタ311にそのまま格納されるとともに、第2データ格納部320のR'レジスタ322、およびL'レジスタ332に出力値の反転データを格納する構成としたので、レジスタ格納処理における双方のハミングウェイトの和を常に一定に保つことができる。その結果、デバイスの消費電力の変化の観察による秘密情報に関するハミングウェイト情報の取得困難性が高まり、結果として、消費電力の変化に基づく解析の困難性を高めることができる。10

## 【実施例2】

## 【0087】

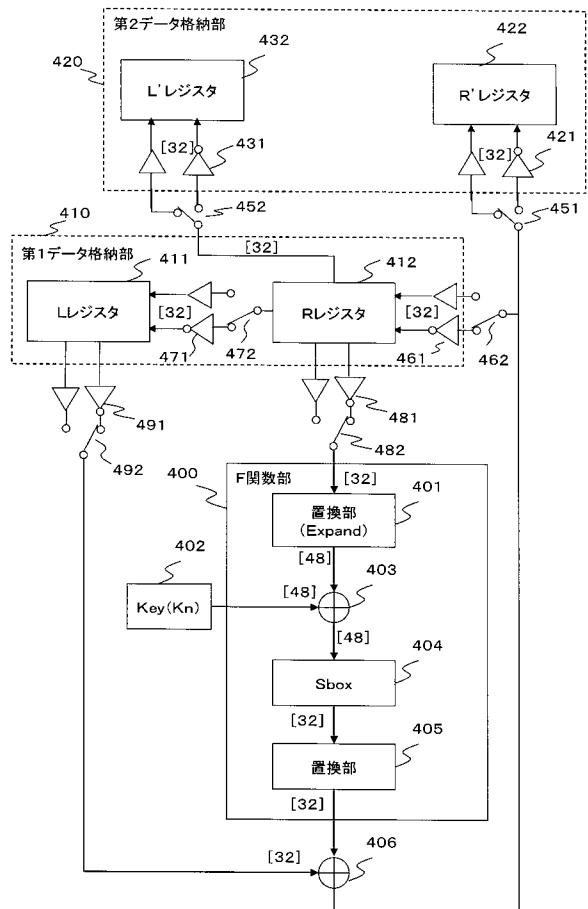

次に、本発明の実施例2の構成について説明する。本実施例に係る暗号処理装置の変換処理部およびレジスタに対するデータ記憶構成の具体的構成例を図7に示す。図7に示す本発明の暗号処理装置構成においては、上述した、単純電力解析、電力差分解析、高階電力差分解析に対応するため、実施例1と同様、Sボックス404の出力に基づくF関数部400からの出力を配線によって2つに分岐し、第1データ格納部410および第2データ格納部420に入力する。

## 【0088】

この実施例2においては、第1データ格納部410および第2データ格納部420に入力する値を反転データとするか非反転データとするかを選択可能としている。第1データ格納部410に入力する値を非反転データとした場合、第2データ格納部420に入力する値を反転データとする。また、第1データ格納部410に入力する値を反転データとした場合、第2データ格納部420に入力する値を非反転データとする。20

## 【0089】

なお、第1データ格納部410および第2データ格納部420の各レジスタ入力段にそれぞれスイッチ451、452、462、472を設け、レジスタ格納値をインバータ421、431、461、471を介して反転データとするか、あるいはインバータを介さずに非反転データとして格納するかを設定可能としている。30

## 【0090】

なお、第1データ格納部410および第2データ格納部420の各レジスタに入力するビットデータはそれぞれ32ビットデータとなるが、全ビットを反転ビットデータとするかあるいは非反転ビットデータとしてそれぞれのレジスタに入力する構成としてもよいが、32ビットデータの1ビット毎に反転、非反転ビットデータを生成して、それぞれのレジスタに入力する構成としてもよい。

## 【0091】

すなわち、例えば、F関数部401からの出力に基づいて排他論理和(XOR)部406から出力されるビット列が[01001011...]であるとき、全ビットの非反転データを第1データ格納部410のRレジスタ412に入力し、反転データを第2データ格納部420のR'レジスタ422に格納する場合は、第1データ格納部410のRレジスタ412に入力する値は、出力ビット列[01001011...]と同様の値となり、第2データ格納部420のR'レジスタ422に入力する値は、反転ビット列[10110100...]となる。40

## 【0092】

また、F関数部401からの出力に基づいて排他論理和(XOR)部406から出力されるビット列が[01001011...]であるとき、32ビット中1ビット毎に反転、非反転データを第1データ格納部410のRレジスタ412に入力し、そのRレジスタ412に入力されるビットデータと逆のパターンのビットデータを第2データ格納部420のR'レジスタ422に格納する場合は、第1データ格納部410のRレジスタ412に

10

20

30

40

50

入力する値、および第2データ格納部420のR'レジスタ422に入力する値は、下記のようになる。

出力ビット列 : [ 0 1 0 0 1 0 1 1 · · ]

Rレジスタ格納値 : [ 0 0 0 1 1 1 1 0 · · ]

R'レジスタ格納値 : [ 1 1 1 0 0 0 1 · · ]

#### 【0093】

上記、記述中、アンダーラインで示したデータが出力値の反転ビットデータである。

#### 【0094】

全ビットデータの反転データと非反転データの組み合わせでそれぞれ、第1データ格納部および第2データ格納部にビットデータを格納した場合でも、あるいは、上述のようにビット毎に反転データ、非反転データの組み合わせを生成して第1データ格納部および第2データ格納部に格納した場合でも、第1データ格納部および第2データ格納部には32ビットの各ビットについて、0と1、あるいは1と0のビット対が相互に格納されることになる。

#### 【0095】

第1データ格納部410のLレジスタ411と、第2データ格納部420のL'レジスタ432に格納される値もそれぞれ32ビットの各ビットについて、0と1、あるいは1と0のビット対が相互に格納されることになる。

#### 【0096】

前述したように、レジスタにビット値を保存する際に消費される電力はSボックスの出力のハミングウェイトに比例するので、第1データ格納部410のRレジスタ412およびLレジスタ411と、第2データ格納部420のR'レジスタ422、およびL'レジスタ432に分岐させて、0と1、あるいは1と0のビット対を格納することにより、双方のハミングウェイトの和を常に一定に保つことができ、デバイスの消費電力の変化観察によるハミングウェイトの情報取得が困難となり、消費電力の変化に基づく解析の困難性を高めることができる。

#### 【0097】

なお、本実施例の場合、第1データ格納部410の各レジスタ411、412に格納されるデータは、次段の処理に適用されることになる。従って、反転ビットデータをこれらのレジスタに格納した場合は、次の段の処理に適用するためのデータ出力の際に、再度、反転処理を実行することが必要であり、そのために、第1データ格納部410のRレジスタ412およびLレジスタ411の出力段に、インバータ481, 491およびスイッチ482, 492を設けてある。

#### 【0098】

第1データ格納部410のRレジスタ412およびLレジスタ411に格納されたビットデータが反転データである場合は、インバータ481, 491を介して再度反転したビットデータを次の段の処理に適用する値として出力する。この処理により、ビットデータの反転処理が行われない場合と全く同様の出力結果を得ることが可能となる。

#### 【0099】

図7に示す構成に基づく処理について説明する。図7の構成は、図6と同様、暗号処理を実行する複数段の変換処理を繰り返し実行するF関数を含む変換処理部および中間データ記憶部としてのレジスタを示す図である。

#### 【0100】

前段(n-1段)の処理結果に基づくビットデータは、それぞれ第1データ格納部410のLレジスタ411、Rレジスタ412に格納される。この値は、予め設定された制御プログラムに従って、反転ビット、あるいは非反転ビットとして格納されている。

#### 【0101】

Rレジスタ412の32ビットデータは、スイッチ482の制御により、格納ビットが反転ビットである場合には、インバータ481を介してF関数部400に入力され、格納ビットが非反転ビットである場合には、インバータ481を介さずにF関数部400に入

10

20

30

40

50

力される。

#### 【0102】

F 関数部 400 の置換部 401において、32 ビットから 48 ビットに拡大置換される。置換部 401 は、図 3 の置換部 171 に相当する。さらに置換部 401 の出力に対して、鍵スケジュール部から鍵 (k(n)) 402 が適用されて、排他論理和 (XOR) 部 403において排他論理和演算処理がなされ、処理結果が S ボックス 404 に入力される。S ボックス 404 において非線形変換が実行され、S ボックス 404 出力が置換部 405 でビット入れ替え等の置換処理が実行された後、置換結果が、排他論理和 (XOR) 部 406において第 1 データ格納部 410 の L レジスタ 411 の格納値と排他論理和演算処理がなされる。なお、L レジスタ 411 の 32 ビットデータは、スイッチ 492 の制御により、格納ビットが反転ビットである場合には、インバータ 491 を介して排他論理和 (XOR) 部 406 に入力され、格納ビットが非反転ビットである場合には、インバータ 491 を介さずに排他論理和 (XOR) 部 406 に入力される。

#### 【0103】

その結果は、第 1 データ格納部 410 の R レジスタ 412、L レジスタ 411 に、反転ビットあるいは非反転ビットとして格納され、その格納ビットパターンと逆のパターンを持つビットデータが、第 2 データ格納部 420 の R' レジスタ 422、L' レジスタ 432 に格納される。第 2 データ格納部 420 の R' レジスタ 422、および L' レジスタ 432 に格納されたビットデータは、次の段の処理には利用されない。

#### 【実施例 3】

#### 【0104】

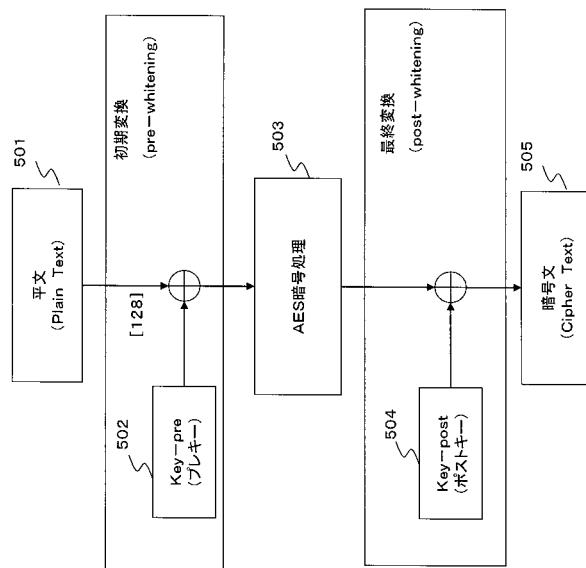

上述の実施例では DES 暗号処理アルゴリズムに適用する例を中心として説明したが、DES に代わる次世代の共通鍵暗号として知られる AES (Advanced Encryption Standard) 暗号においても本発明の適用は可能である。AES は、鍵長が 128、192、256 bit と、DES の 64 bit 鍵長に比較して長いビット長の鍵を適用した暗号処理であり、強固な安全性を持つものである。

#### 【0105】

AES では、鍵長、ブロック長とも 128、192、256 bit と、独立に異なるビット長とした処理が可能であり、上述した DES と同様、複数のラウンドの処理を繰り返し実行する。

#### 【0106】

また、AES 暗号処理では、図 8 に示すように、入力平文 501 に対してプレキー (K-pre) 502 を適用した初期変換 (Pre-whitening) を実行した後、複数ラウンドからなる AES 暗号処理部 503 において AES 暗号処理を実行し、さらに、最終的にポストキー (K-post) 504 を適用した最終変換 (Post-whitening) を実行して暗号文 505 を出力する構成を持つものであり、解読困難性の高い、すなわち安全性の高い暗号処理である。

#### 【0107】

この AES 暗号処理においても、AES 暗号処理の実行過程で発生する中間データの格納において、上述したと同様の反転データを生成してレジスタに格納する構成とすることで、レジスタ格納処理における双方のハミングウェイトの和を常に一定に保つことができる。その結果、デバイスの消費電力の変化の観察による秘密情報に関するハミングウェイト情報の取得困難性が高まり、結果として、消費電力の変化に基づく解析の困難性を高めることができる。

#### 【0108】

最後に、上述の暗号処理を実行するデバイスとしての IC モジュール 600 の構成例を図 9 に示す。上述の処理は、例えば PC、IC カード、リーダライタ、その他、様々な情報処理装置において実行可能であり、図 9 に示す IC モジュール 600 は、これら様々な機器に構成することが可能である。

#### 【0109】

10

20

30

40

50

図9に示すC P U (Central processing Unit) 6 0 1は、暗号処理の開始や、終了、データの送受信の制御、各構成部間のデータ転送制御、その他の各種プログラムを実行するプロセッサである。メモリ6 0 2は、C P U 6 0 1が実行するプログラム、あるいは演算パラメータとしての固定データを格納するR O M (Read-Only-Memory)、C P U 6 0 1の処理において実行されるプログラム、およびプログラム処理において適宜変化するパラメータの格納エリア、ワーク領域として使用されるR A M (RandomAccess Memory)等からなる。ここに上述した中間データの格納領域が形成される。また、メモリ6 0 2は暗号処理に必要な鍵データ等の格納領域として使用可能である。データ等の格納領域は、耐タンパ構造を持つメモリとして構成されることが好ましい。

## 【0 1 1 0】

暗号処理手部6 0 3は、例えば上述したD E S、A E Sに従った暗号処理、復号処理等を実行する。なお、ここでは、暗号処理手段を個別モジュールとした例を示したが、このような独立した暗号処理モジュールを設けず、例えば暗号処理プログラムをR O Mに格納し、C P U 6 0 1がR O M格納プログラムを読み出して実行するように構成してもよい。

## 【0 1 1 1】

乱数発生器6 0 4は、暗号処理に必要となる鍵の生成などにおいて必要となる乱数の発生処理を実行する。

## 【0 1 1 2】

送受信部6 0 5は、外部とのデータ通信を実行するデータ通信処理部であり、例えばリーダライタ等、I Cモジュールとのデータ通信を実行し、I Cモジュール内で生成した暗号文の出力、あるいは外部のリーダライタ等の機器からのデータ入力などを実行する。

## 【0 1 1 3】

以上、特定の実施例を参照しながら、本発明について詳解してきた。しかしながら、本発明の要旨を逸脱しない範囲で当業者が該実施例の修正や代用を成し得ることは自明である。すなわち、例示という形態で本発明を開示してきたのであり、限定的に解釈されるべきではない。本発明の要旨を判断するためには、冒頭に記載した特許請求の範囲の欄を参考すべきである。

## 【0 1 1 4】

なお、明細書中において説明した一連の処理はハードウェア、またはソフトウェア、あるいは両者の複合構成によって実行することが可能である。ソフトウェアによる処理を実行する場合は、処理シーケンスを記録したプログラムを、専用のハードウェアに組み込まれたコンピュータ内のメモリにインストールして実行させるか、あるいは、各種処理が実行可能な汎用コンピュータにプログラムをインストールして実行させることができる。

## 【0 1 1 5】

なお、明細書に記載された各種の処理は、記載に従って時系列に実行されるのみならず、処理を実行する装置の処理能力あるいは必要に応じて並列的あるいは個別に実行されてもよい。また、本明細書においてシステムとは、複数の装置の論理的集合構成であり、各構成の装置が同一筐体内にあるものには限らない。

## 【産業上の利用可能性】

## 【0 1 1 6】

本発明は、認証処理、暗号処理を実行するデバイス、例えば暗号処理モジュールを持つI Cカードあるいはその他の暗号処理装置に適用可能である。本発明の構成を適用することにより、電力解析によるI Cモジュール内の暗号処理鍵やアルゴリズムの漏洩が困難となるので、セキュリティレベルの高い暗号処理実行機能を持つデバイスあるいは装置が提供可能となる。

## 【図面の簡単な説明】

## 【0 1 1 7】

【図1】D E S暗号処理の基本構成を示す図である。

【図2】ラウンド関数部の各ラウンドを構成する変換部の構成を示す図である。

10

20

30

40

50

【図3】F関数の構成を示す図である。

【図4】トリプルDES(Triple DES)暗号処理構成を示す図である。

【図5】Sボックス(Sbox)を持つF関数の構成および中間データ記憶部としてのレジスタを持つ暗号処理デバイスの構成例について説明する図である。

【図6】本発明に係る暗号処理装置の変換処理部およびレジスタに対するデータ記憶構成の具体的構成例(実施例1)を示す図である。

【図7】本発明に係る暗号処理装置の変換処理部およびレジスタに対するデータ記憶構成の具体的構成例(実施例2)を示す図である。

【図8】AES暗号処理構成を示す図である。

【図9】本発明の構成が適用可能な暗号処理実行デバイスとしてのICモジュールの構成例を示す図である。 10

#### 【符号の説明】

##### 【0118】

|               |             |

|---------------|-------------|

| 110           | ラウンド関数部     |

| 111           | 初期置換部       |

| 112, 113      | 変換部         |

| 114           | 逆置換部        |

| 120           | 鍵スケジュール部    |

| 121           | 選択置換部       |

| 122, 123      | 鍵生成部        |

| 151           | F関数部        |

| 171, 172      | 置換部         |

| 181           | Sボックス       |

| 185, 186, 187 | DES暗号処理部    |

| 200           | F関数部        |

| 201           | 置換部         |

| 202           | 鍵           |

| 203           | 排他論理和(XOR)部 |

| 204           | Sボックス       |

| 205           | 置換部         |

| 206           | 排他論理和(XOR)部 |

| 211           | Lレジスタ       |

| 212           | Rレジスタ       |

| 300           | F関数部        |

| 301           | 置換部         |

| 302           | 鍵           |

| 303           | 排他論理和(XOR)部 |

| 304           | Sボックス       |

| 305           | 置換部         |

| 306           | 排他論理和(XOR)部 |

| 310           | 第1データ格納部    |

| 311           | Lレジスタ       |

| 312           | Rレジスタ       |

| 320           | 第2データ格納部    |

| 321, 331      | インバータ       |

| 322           | R'レジスタ      |

| 332           | L'レジスタ      |

| 400           | F関数部        |

| 401           | 置換部         |

| 402           | 鍵           |

10

20

30

40

50

|                                               |                                 |    |

|-----------------------------------------------|---------------------------------|----|

| 4 0 3                                         | 排他論理和 ( X O R ) 部               |    |

| 4 0 4                                         | S ボックス                          |    |

| 4 0 5                                         | 置換部                             |    |

| 4 0 6                                         | 排他論理和 ( X O R ) 部               |    |

| 4 1 0                                         | 第 1 データ格納部                      |    |

| 4 1 1                                         | L レジスタ                          |    |

| 4 1 2                                         | R レジスタ                          |    |

| 4 2 0                                         | 第 2 データ格納部                      |    |

| 4 2 1 , 4 3 1 , 4 6 1 , 4 7 1 , 4 8 1 , 4 9 1 | インバータ                           | 10 |

| 4 2 2                                         | R' レジスタ                         |    |

| 4 3 2                                         | L' レジスタ                         |    |

| 4 5 1 , 4 5 2 , 4 6 2 , 4 7 2 , 4 8 2 , 4 9 2 | スイッチ                            |    |

| 5 0 1                                         | 平文                              |    |

| 5 0 2                                         | ブレキー                            |    |

| 5 0 3                                         | A E S 暗号処理部                     |    |

| 5 0 4                                         | ポストキー                           |    |

| 5 0 5                                         | 暗号文                             |    |

| 6 0 0                                         | I C モジュール                       |    |

| 6 0 1                                         | C P U (Central processing Unit) |    |

| 6 0 2                                         | メモリ                             | 20 |

| 6 0 3                                         | 暗号処理部                           |    |

| 6 0 4                                         | 乱数発生器                           |    |

| 6 0 5                                         | 送受信部                            |    |

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】