(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5069449号

(P5069449)

(45) 発行日 平成24年11月7日(2012.11.7)

(24) 登録日 平成24年8月24日(2012.8.24)

|              |            |

|--------------|------------|

| (51) Int.Cl. | F 1        |

| H05K 1/02    | (2006.01)  |

| H01L 23/12   | (2006.01)  |

| H05K 3/18    | (2006.01)  |

| H05K 3/22    | (2006.01)  |

|              | HO5K 1/02  |

|              | HO1L 23/12 |

|              | HO5K 3/18  |

|              | HO5K 3/22  |

請求項の数 6 (全 13 頁)

(21) 出願番号 特願2006-308322 (P2006-308322)

(22) 出願日 平成18年11月14日 (2006.11.14)

(65) 公開番号 特開2008-124339 (P2008-124339A)

(43) 公開日 平成20年5月29日 (2008.5.29)

審査請求日 平成21年9月16日 (2009.9.16)

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100091672

弁理士 岡本 啓三

(72) 発明者 草間 泰彦

長野県長野市小島田町80番地 新光電氣

工業株式会社内

(72) 発明者 村松 茂次

長野県長野市小島田町80番地 新光電氣

工業株式会社内

(72) 発明者 経塚 正宏

長野県長野市小島田町80番地 新光電氣

工業株式会社内

最終頁に続く

(54) 【発明の名称】配線基板及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

ベース基材としての基板上に形成されたフリップチップ接続用のパッド部分を含む配線層と、前記パッド部分のみを露出させて前記基板及び前記配線層を覆うように形成された絶縁層とを備え、

前記配線層は、配線部分を構成する第1のめっき配線の一部領域上にのみ、前記パッド部分を構成する、前記第1のめっき配線と結晶配向が異なる第2のめっき配線が積み重ねられた構造を有し、前記パッド部分の上面が前記絶縁層の表面と同一面上に位置するように形成されていることを特徴とする配線基板。

## 【請求項 2】

少なくとも最表層に導体層が形成された基板の一方の面に、形成すべきフリップチップ接続用のパッド部分を含む所要の配線層の形状に従ってパターニングされた開口部を備えた第1のレジスト層を形成する工程と、

前記第1のレジスト層の開口部から露出している前記導体層を給電層として電解めっきを施し、当該開口部内を部分的に埋め込むように第1の配線層を形成する工程と、

電解めっきの条件を変えて前記第1の配線層に電解めっきを施し、当該開口部内の残りの部分を埋め込むように前記第1の配線層と結晶配向が異なる第2の配線層を形成する工程と、

前記第2の配線層のパッド部分に対応する領域にパターンが残るように、前記第1のレジスト層及び前記第2の配線層の上に第2のレジスト層を形成する工程と、

前記第2のレジスト層をマスクにして、前記第2の配線層の露出している部分のみをエッチングすることで、前記第1の配線層を露出させる工程と、

前記第2のレジスト層及び第1のレジスト層を除去した後、前記基板及び前記第1、第2の配線層を覆って全面に絶縁層を形成する工程と、

前記絶縁層を研磨して前記パッド部分の上面を露出させると共に、基板表面全体を平坦化する工程とを含むことを特徴とする配線基板の製造方法。

#### 【請求項3】

前記電解めっきの条件を変えて前記第2の配線層を形成する工程に代えて、

前記第1の配線層上にバリヤメタル層を形成し、さらに該バリヤメタル層に電解めっきを施し、当該開口部内の残りの部分を埋め込むように第2の配線層を形成する工程を含むことを特徴とする請求項2に記載の配線基板の製造方法。 10

#### 【請求項4】

前記第2のレジスト層及び前記第1のレジスト層の除去後に前記基板から露出している前記導体層を除去した後に、前記基板及び前記第1、第2の配線層を覆って全面に絶縁層を形成することを特徴とする請求項2又は3に記載の配線基板の製造方法。

#### 【請求項5】

前記バリヤメタル層は、前記第2の配線層の露出している部分のみをエッチングする際のストップ層として機能することを特徴とする請求項3に記載の配線基板の製造方法。 20

#### 【請求項6】

前記バリヤメタル層は、ニッケル層上に金層が積層された2層構造を有していることを特徴とする請求項3に記載の配線基板の製造方法。 20

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、配線基板を製造する技術に係り、より詳細には、半導体素子（チップ）を搭載する実装用基板として供され、その半導体素子をフリップチップ接続する際に使用されるパッドを備えた配線基板及びその製造方法に関する。

##### 【背景技術】

##### 【0002】

半導体素子（チップ）と実装用基板とを電気的に接続する方法としては、従来よりワイヤボンディングが一般的である。この方法を用いて半導体装置を構成する場合、基板上にチップの裏面（電極端子が形成されている側と反対側の面）を下にして接着剤等により固定化した後、当該チップの電極端子（以下、「チップパッド」ともいう）と基板上に形成されたパッド（以下、「基板パッド」ともいう）とをボンディングワイヤで接続し、さらにワイヤ及びチップを覆うように樹脂で封止している。この構造では、基板上でチップ搭載エリアの周囲に、基板パッドとワイヤボンディングするための余分なスペースを必要とする。 30

##### 【0003】

その一方で、近年、電子機器や装置の小型化の要求に伴い、それに用いられる半導体装置の小型化、高密度化が図られている。例えば、半導体装置の形状を個々の半導体チップの形状に極力近づけることで小型化及び高密度化を図るようにしたCSP（チップサイズパッケージ）等の半導体装置が開発され、実用化されている。かかる半導体装置では、ワイヤボンディング接続とは異なる形態のフリップチップ接続の技術を用いて半導体チップを基板に実装することで、より一層の小型化及び高密度化を図り、電気信号の高速処理を可能としている。 40

##### 【0004】

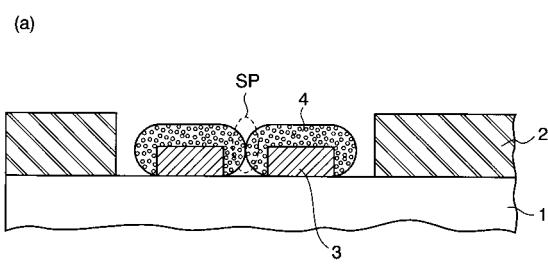

従来のフリップチップ実装用基板は、図1に概略的に示すように、搭載する半導体素子の接続部分（チップパッド）に対応する領域において、その表面が断面的に見て凹凸形状となっている。つまり、フリップチップ接続用の基板パッド3（基板1上に形成された配線パターンの一部分に画定される領域）の上面と基板1の表面（基板1上に形成されたソ 50

ルダレジスト等からなる絶縁層 2 の上面 )との間に段差があった。

#### 【 0 0 0 5 】

上記のフリップチップ接続に関する技術としては、例えば、特許文献 1 に記載されるように、配線基板の表面にフリップチップ接続用の接続パッドと共にワイヤボンディング接続用のボンディングパッドも併せて形成するようにしたものがある。この文献に記載された技術では、基板の表面に接続パッドとボンディングパッドをパターン形成した後、接続パッドを遮蔽してボンディングパッドの表面にボンディング用のめっきを施し、次にボンディングパッド形成領域にマスキング用テープを粘着してボンディングパッドを遮蔽した後、接続パッドの表面に粘着層を被着させてその表面にはんだ粉を付着させ、テープを剥離した後、リフローによりはんだ粉を溶融して接続パッドにはんだを被着させるようにしている。また、特許文献 2 に記載されるように、フリップチップ実装構造において半導体素子の各電極にそれぞれ形成したはんだバンプ間がショートするのを防止するようにしたものがある。このフリップチップ実装構造では、半導体素子側に形成した各はんだバンプに対応する実装用基板の当該部位に基板側電極を形成すると共に、各基板側電極の間の部位に溝を 2 条形成し、はんだバンプを加熱、溶融させて半導体素子の電極と実装用基板の電極とを接続した時に、余分なはんだが基板側電極上からはみ出して実装用基板の溝内に流れこむようにすることで、隣接するバンプ間のショートを防止している。また、特許文献 3 に記載されるように、絶縁層と配線導体とが交互に積層された配線基板において、最外層の絶縁層上に帯状配線導体を複数並べて配設するとともに、該帯状配線導体の一部に、半導体素子の電極端子がフリップチップ接続される導電突起を帯状配線導体の幅と一致する幅で形成し、さらに導電突起の少なくとも上面が露出するようにソルダレジスト層で被覆したものがある。

10

【特許文献 1】特開 2005 - 268353 号公報

【特許文献 2】特開 2001 - 53111 号公報

【特許文献 3】特開 2006 - 344664 号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【 0 0 0 6 】

上述したように従来のフリップチップ実装用基板では(図 1 参照)、フリップチップ接続用の基板パッド 3 の上面と基板表面(基板 1 上に形成された絶縁層 2 の上面)との間に段差があり、断面的に見て実装用基板の表面が凹凸形状となっていたため、この基板に半導体素子を搭載して半導体装置を構成する際に、以下の不都合があった。

30

#### 【 0 0 0 7 】

すなわち、基板パッドと半導体素子のチップパッドを接続するための手段としては、典型的にはんだバンプが用いられるが、その形成方法として、フォトプロセスを用いためっき法やメタルマスクを用いた蒸着法などが主流である一方、基板パッドが微細な間隔(ピッチ)で形成されている基板にあっては、基板パッドにはんだを被着させる際に、スーパージャフィット法と呼ばれる手法が用いられている。これは、Sn - Ag 系、Sn - Zn 系などの Pb フリー組成のはんだ合金で部品を実装するのに十分なはんだ量を供給しておき、粘着性フラックスで部品を仮付けし、大気雰囲気中で一括リフローする工法であり、上記の特許文献 1 にも記載されているように、基板パッドの表面に粘着層を形成してはんだ粉を基板パッド上に付着させ、そのはんだ粉を溶融させて基板パッドの表面にはんだを被着させる方法である。

40

#### 【 0 0 0 8 】

かかるスーパージャフィット法を用いてはんだ粉を基板パッドの表面に吸着させると、上述したように基板の表面には凹凸の段差があるため、微細ピッチになればなるほど(現状の技術では 20 μm ピッチのフリップチップ実装用基板も出現している)、図 1 (a) に例示するように、隣接する基板パッド 3 の対向する側面に吸着されたはんだ粉 4 同士がショート(短絡)もしくはブリッジ(橋絡)を起こしてしまい(図中、破線で囲んだ S P で示す部分)、不良発生要因の一つとなる。

50

## 【0009】

また、図1(b)に例示するように、半導体素子40(チップパッド41)をはんだパンプ5を介して実装用基板(基板パッド3)にフリップチップ接続した後に両者間にアンダーフィル樹脂6を充填する際に、基板表面には凹凸の段差があるため、アンダーフィル樹脂6の流動性が不均一となり、またピッチも狭くなっているため、樹脂6が内部に入りにくくなる。このため、図示のように注入した樹脂の一部にボイド(空洞部分)VDが発生したり、あるいは充填不足の要因となりうる。

## 【0010】

本発明は、かかる従来技術における課題に鑑み創作されたもので、半導体素子を搭載して半導体装置を構成する際に、隣接する基板パッド上に付着されるはんだ粉同士のショートを防止すると共に、アンダーフィル樹脂の充填の際の不良発生要因を実質的に無くすことができる配線基板及びその製造方法を提供することを目的とする。10

## 【課題を解決するための手段】

## 【0011】

上記の従来技術の課題を解決するため、本発明の一形態によれば、ベース基材としての基板上に形成されたフリップチップ接続用のパッド部分を含む配線層と、前記パッド部分のみを露出させて前記基板及び前記配線層を覆うように形成された絶縁層とを備え、前記配線層は、配線部分を構成する第1のめっき配線の一部領域上にのみ、前記パッド部分を構成する、前記第1のめっき配線と結晶配向が異なる第2のめっき配線が積み重ねられた構造を有し、前記パッド部分の上面が前記絶縁層の表面と同一面上に位置するように形成されていることを特徴とする配線基板が提供される。20

## 【0012】

この形態に係る配線基板の構成によれば、フリップチップ接続用のパッド部分(第2のめっき配線)が、これと結晶配向の異なる配線部分(第1のめっき配線)の一部領域上にのみ積み重ねられた構造となっており、そのパッド部分(基板パッド)の上面は絶縁層の表面(配線基板の表面)と同一面上に位置している。つまり、基板パッドの側面は外部に露出せず、その上面のみが露出する。これに対し、従来の技術(図1)では基板パッド3の側面も露出していた。

## 【0013】

従って、フリップチップ接続のためのはんだを基板パッドに被着させる際にはんだ粉を基板パッドの表面に吸着させると、本発明の配線基板では、基板パッドの上面にのみはんだ粉を吸着させることができる。これにより、従来の技術(図1(a))に見られたような隣接する基板パッド3(その対向する側面)上のはんだ粉4同士のショート等を防止することができる。30

## 【0014】

また、本発明の配線基板に半導体素子をフリップチップ接続した後に両者間にアンダーフィル樹脂を充填する際にも、基板パッドと基板表面は同一面にあるので、アンダーフィル樹脂を比較的スムーズに流動させることができ、樹脂が内部に入り易くなる。これにより、従来の技術(図1(b))に見られたようなボイドVDの発生や充填不足といった不良発生要因を実質的に無くすことができる。このことは、客先(本配線基板に半導体素子を搭載するメーカーなど)での歩留り改善に大いに寄与する。40

## 【0015】

また、本発明の他の形態によれば、上記の形態に係る配線基板を製造する方法が提供される。その一形態に係る配線基板の製造方法は、少なくとも最表層に導体層が形成された基板の一方の面に、形成すべきフリップチップ接続用のパッド部分を含む所要の配線層の形状に従ってパターニングされた開口部を備えた第1のレジスト層を形成する工程と、前記第1のレジスト層の開口部から露出している前記導体層を給電層として電解めっきを施し、当該開口部内を部分的に埋め込むように第1の配線層を形成する工程と、電解めっきの条件を変えて前記第1の配線層に電解めっきを施し、当該開口部内の残りの部分を埋め込むように前記第1の配線層と結晶配向が異なる第2の配線層を形成する工程と、前記第50

2の配線層のパッド部分に対応する領域にパターンが残るように、前記第1のレジスト層及び前記第2の配線層の上に第2のレジスト層を形成する工程と、前記第2のレジスト層をマスクにして、前記第2の配線層の露出している部分のみをエッチングすることで、前記第1の配線層を露出させる工程と、前記第2のレジスト層及び第1のレジスト層を除去した後、前記基板及び前記第1、第2の配線層を覆って全面に絶縁層を形成する工程と、前記絶縁層を研磨して前記パッド部分の上面を露出させると共に、基板表面全体を平坦化する工程とを含むことを特徴とする。

#### 【0016】

本発明に係る配線基板及びその製造方法の他の構成／プロセス上の特徴及びそれに基づく有利な利点等については、後述する発明の実施の形態を参考しながら説明する。 10

#### 【発明を実施するための最良の形態】

#### 【0017】

以下、本発明の好適な実施の形態について、添付の図面を参照しながら説明する。

#### 【0018】

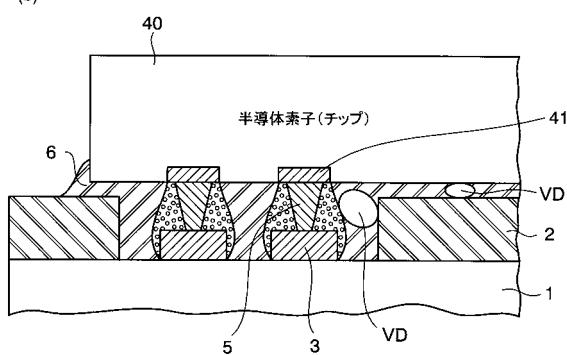

図2は本発明の一実施形態に係る配線基板（フリップチップ実装用基板）の構成を断面図の形態で示したものである。

#### 【0019】

図中、10は本実施形態に係る配線基板、12は配線基板10のベース基材としての樹脂基板、14は樹脂基板12上に形成された配線層、16は樹脂基板12上に形成された保護膜としての絶縁層を示す。配線層14は、図示のように上下に積み重ねられた2つの部分からなり、上側の部分は本発明を特徴付ける「基板パッド」部分14aを構成し、下側の部分は「下配線」部分14bを構成する。 20

#### 【0020】

樹脂基板12の形態としては、少なくとも最表層に導体層（図2には明示されていないが、「下配線」部分14bの一部として含まれている）が形成された基板であって、各導体層が基板内部を通して電気的に接続されている形態のものであれば十分である。樹脂基板12の内部には配線層が形成されていてもよいし、形成されていなくてもよい。本発明を特徴付ける部分ではないので特に図示はしないが、樹脂基板12の内部に配線層が形成されている形態の場合、基板内部で絶縁層を介在させて形成された各配線層及び各配線層間を相互に接続するピアホールを介して最表層の各導体層が電気的に接続されている。この形態の基板としては、例えば、ビルトアップ法を用いて形成され得る多層配線基板がある。一方、樹脂基板12の内部に配線層が形成されていない形態の場合、樹脂基板12の所要箇所に適宜形成されたスルーホールを介して最表層の各導体層が電気的に接続されている。この形態の基板としては、例えば、上記のビルトアップ法による多層配線基板のベース基材に相当するコア基板、すなわち、ガラス布にエポキシ樹脂、ポリイミド樹脂、ビスマレイミド・トリアジン（BT）樹脂、ポリフェニレンエーテル（PPE）樹脂等の絶縁性樹脂を含浸させたシートを所要枚数重ね、その両面もしくは片面に銅箔を被着させた基板（両面銅張積層板もしくは片面銅張積層板）がある。 30

#### 【0021】

本実施形態に係る配線基板10は、図2にも示されるように、配線層14の「基板パッド」部分14aの上面が基板10の表面（絶縁層16の表面）と同一面上に位置するように形成されていることを特徴とする。本実施形態の配線基板10を構成する各構成部材の材料や大きさ等については、後述するプロセスに関連させて具体的に説明する。 40

#### 【0022】

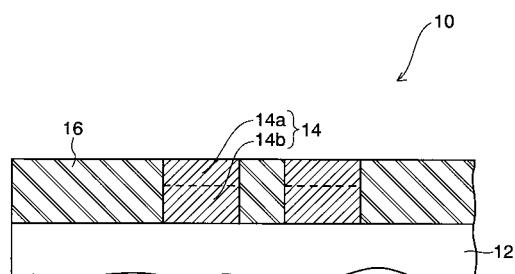

以下、本実施形態に係る配線基板10を製造する方法について、その製造工程を順に示す図3～図6を参照しながら説明する。なお、各図（断面図、上面図、斜視図）に示す構成では、図示の簡単化のため、本発明に関連する部分（「基板パッド」部分14aを含む配線層14及びその周辺部分）のみが示されている。

#### 【0023】

先ず最初の工程では（図3（a）参照）、通常のサブトラクティブ法、セミアディティ

50

ブ法などを用いて所要形態の樹脂基板12を用意する。この基板12の形態としては、上述したように少なくとも最表層に導体層が形成された基板であって、各導体層が基板内部を通して電気的に接続されている形態のものであれば十分である。図示の例では、本発明に関連する部分として、樹脂基板12の一方の最表層（半導体チップが搭載される側）に導体層13が形成された状態の断面構造が示されており、この導体層13は、後述するように電解めっきを行う際の給電層（シード層）として利用され、例えば、2～3μm程度の厚さに形成されている。導体層13の材料としては銅（Cu）が用いられ、樹脂基板12を構成する樹脂としては、熱硬化性のポリイミド樹脂、エポキシ樹脂、BT樹脂等が用いられる。

## 【0024】

10

次の工程では（図3（b）参照）、樹脂基板12の導体層13が形成されている側の面に、パターニング材料を使用してレジスト層21を形成し、このレジスト層21の所定の箇所に対応する部分を除去する（開口部OPの形成）。この開口部OPは、本発明を特徴付ける「基板パッド」部分を含む所要の配線層の形状に従ってパターン形成される。基板上での「基板パッド」部分の配置については、搭載する半導体チップの電極端子（チップパッド）の配列形態に応じて、当該チップの周辺部分に対応する領域にのみ配置した「ペリフェラル型」、当該チップに対応する全領域にマトリクス状に配置した「エリアアレイ型」のいずれであってもよい。

## 【0025】

20

また、パターニング材料としては、感光性のドライフィルム又は液状のフォトレジストを用いることができる。例えば、ドライフィルムを使用する場合には、典型的にレジスト材料をポリエステルのカバーシートとポリエチレンのセパレータシートの間に挟んだ構造となっているので、表面洗浄 ラミネーション前処理（セパレータシート剥離） 大気中のレジストラミネーション 露光 カバーシート剥離 現像の工程を経て、パターニングされたレジスト層21を形成する。具体的には、樹脂基板12（導体層13）上に、所定の厚さ（本実施形態では、25μm程度）の感光性ドライフィルムを熱圧着により貼り付けた後、そのドライフィルムに対し、所要の形状にパターニングされたマスク（図示せず）を用いて紫外線（UV）照射による露光を施して硬化させ、さらに所定の現像液（ネガ型のレジストの場合には有機溶剤を含む現像液、ポジ型のレジストの場合にはアルカリ系の現像液）を用いてエッティング除去を行うことで（開口部OPの形成）、所要の配線パターンの形状に応じたレジスト層21を形成する。同様に、液状のフォトレジストを用いた場合にも、表面洗浄 表面にレジスト塗布 乾燥 露光 現像の工程を経て、所要の形状にパターニングされたレジスト層21を形成することができる。

## 【0026】

30

次の工程では（図3（c）参照）、レジスト層21の開口部OPから露出しているシード層（Cu）13を給電層として電解銅（Cu）めっきを施し、開口部OPを埋め込むように「厚付け配線めっき」を行うことで配線層14を形成する。形成された配線層14の上面は、図示の例では平坦となっているが、必ずしも平坦とは限らない。このため、厚付け配線めっきを行った後、表面全体を平坦化（平滑化）する処理を施すのが望ましい。この平坦化処理は、次の工程で形成されるレジストとの密着性を高めることにも寄与する。なお、この工程で形成された配線層14は、特に図示はしないが、樹脂基板12の所要箇所に適宜形成されたスルーホールを介して、あるいは基板内部の所要箇所に適宜形成された各配線層及び各配線層間を相互に接続するビアホールを介して、基板の裏面側（半導体チップが搭載される側と反対側の面）の配線層に電気的に接続されている。

40

## 【0027】

次の工程では（図3（d）参照）、ドライフィルム等からなるレジスト層21をそのまま残した状態で、さらにレジスト層21及び配線層14の全面に、パターニング材料を使用してレジスト層22を形成する。このレジスト層22は、上記のレジスト層21と同じ材料で形成してもよいし、異なる材料で形成してもよい。

## 【0028】

50

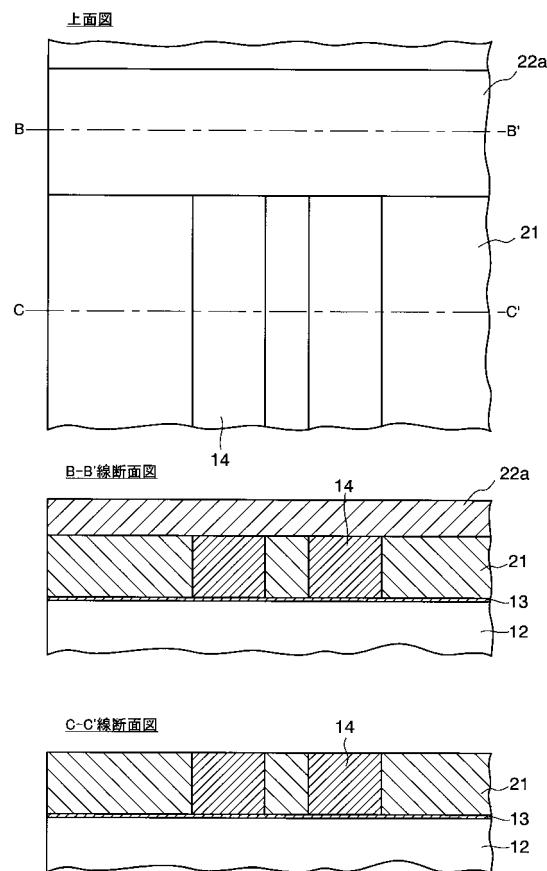

次の工程では(図4参照)、レジスト層21及び配線層14上に形成されたレジスト層22(図3(d))に対し、配線層14の「基板パッド」部分に対応する領域のみを残すようにパターニングを行う。このレジスト層22のパターニングは、図3(b)の工程で行ったレジスト層21のパターニングと同様にして行うことができる。図中、(a)はパターニングされた後のレジスト層22aを基板の上面から見たときの状態を概略的に示したものであり、(b)は(a)においてB-B'線(「基板パッド」部分を含む領域)に沿って断面的に見たときの構造、(c)は(a)においてC-C'線(「基板パッド」部分を含まない領域)に沿って断面的に見たときの構造をそれぞれ示している。

#### 【0029】

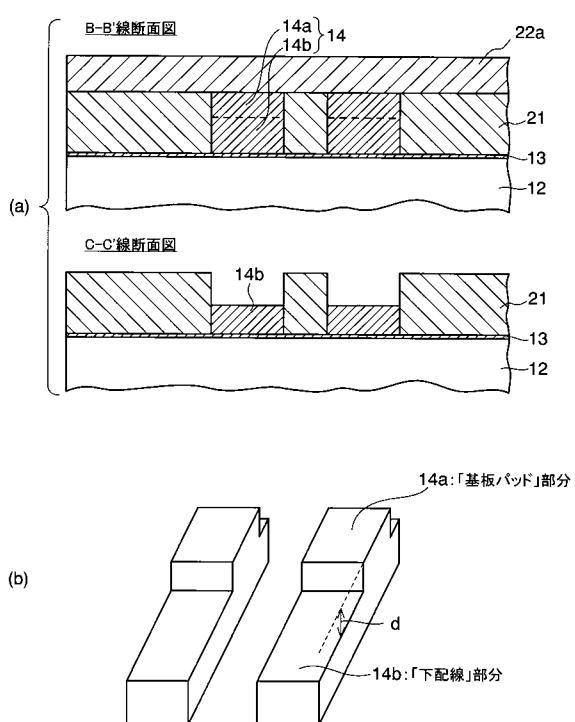

次の工程では(図5(a)参照)、パターニングされたレジスト層22aをマスクにして、例えば、銅(Cu)に対してのみ可溶性の薬液を用いたウエットエッチングにより、露出している部分の配線層(Cu)14を必要量のみエッチング除去する。このエッチングされた部分は配線層14の「下配線」部分14bを構成し(C-C'線断面図参照)、エッチングされずに残った部分は配線層14の「基板パッド」部分14aを構成する(B-B'線断面図参照)。つまり、配線層14は、「下配線」部分14bの上に「基板パッド」部分14aが積み重ねられた形状の構造体に加工される。

#### 【0030】

なお、この工程でエッチングすべき「必要量」とは、最終的に基板表面を研磨して平坦化したときに「基板パッド」部分14aの上面のみが露出し、「下配線」部分14bは露出せずに基板内に隠れている程度の厚さをいい、構成上は「基板パッド」部分14aの上面より1μmでも下の位置までエッチングされていれば十分である。しかし、実際には、研磨を行う前の「基板パッド」部分14aの上面(配線層14の上面)は必ずしも平坦でなく、それ故平坦化のために若干研磨する必要性があり、また、仮に「基板パッド」部分14aの上面が完全に平坦であったとしても研磨を所望の時点で正確に止めることは技術的に困難であるなどの事情を考慮して、本実施形態では、上記の「必要量」を10μm程度に選定している。従って、ここで形成される「基板パッド」部分14aは10μm程度の厚さとなり、「下配線」部分14bは15μm程度(=25μm程度(レジスト層21の厚さ)-10μm程度)の厚さとなる。

#### 【0031】

次の工程では(図5(b)参照)、レジスト層22a及びレジスト層21を、例えば、水酸化ナトリウムやモノエタノールアミン系などのアルカリ性の薬液を用いて除去する。これによって、配線層14が露出する。図示の例では、「下配線」部分14bの上に「基板パッド」部分14aが積み重ねられた形状の配線層14の構成のみが斜視図の形態で示されているが、実際には、この段階で、基板上で配線層14が形成されていない部分については樹脂基板12上の導体層13も露出している。

#### 【0032】

従って、このままでは各配線層14の「基板パッド」部分14aが導体層13を介して電気的に相互接続された状態となるので、次の工程の前処理として、この露出している導体層13を除去しておく必要がある。例えば、ウエットエッチングにより、導体層13を除去する。これによって、樹脂基板12の表面から配線層14のみが露出する。なお、導体層(Cu)13をエッチングするに際し、配線層14も同じ材料(Cu)で形成されているので、同時にその一部がエッチングされるが、導体層13の厚さ(2~3μm程度)に比べて配線層14の厚さは相当あるため、エッチングされてもその量は僅かであり、配線層14の各部分14a, 14bの実質的な厚さに重大な影響を及ぼすほどではない。

#### 【0033】

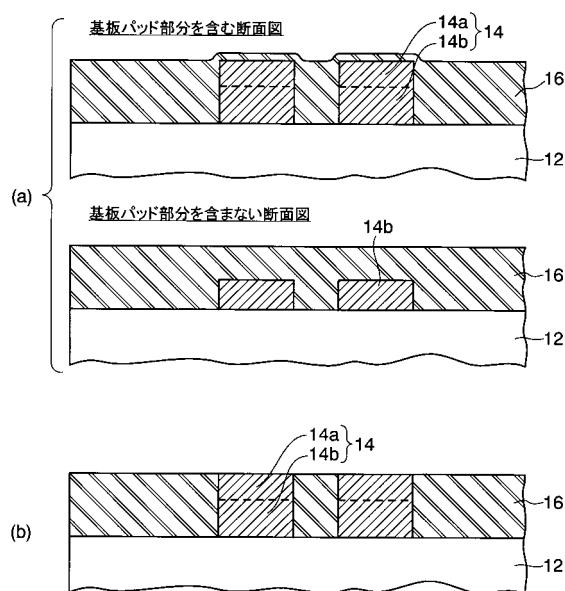

次の工程では(図6(a)参照)、樹脂基板12及び配線層14(「基板パッド」部分14a、「下配線」部分14b)の表面を覆って全面に保護膜として供される絶縁層16を形成する。この絶縁層16の材料としては、例えば、プリント配線板等において多く用いられているソルダレジスト(エポキシアクリレート樹脂やエポキシ樹脂の部分アクリル化樹脂など)を使用することができる。なお、図示の例では、樹脂基板12上に直接「下

10

20

30

40

50

配線」部分 14 b が形成されているが、実際には、「下配線」部分 14 b が形成されている部分については樹脂基板 12 上のシード層 13（図 5 (a) 参照）は残存しており、このシード層 13 については図示を省略している。この段階では、図 6 (a) の上側の断面図に示すように、基板パッド 14 a 上にも絶縁層 16 の一部分（樹脂）が若干堆積し、当該部分の断面が凸形状を呈するため、基板の表面は凹凸状態にある。

#### 【0034】

最後の工程では（図 6 (b) 参照）、絶縁層 16 を研磨して「基板パッド」部分 14 a の上面を露出させると共に、基板の表面全体を平坦化（平滑化）する。

#### 【0035】

ここでは、研磨の対象は金属ではなく樹脂（絶縁層 16）であるため、研磨方法としては、薬液を用いて行う化学研磨よりも、研磨紙や研磨材を含むバフやブラシ、振動などを利用して行う機械研磨の方が望ましい。例えば、バフ研磨の場合、研磨材を埋め込んだ円筒状のバフ及び研磨対象表面（絶縁層 16 の表面）を冷却水で湿潤させながら、バフを回転させて研磨対象表面に押し当てて研磨を行い、「基板パッド」部分 14 a の上面が露出した時点で研磨を止める。これにより、図示のように「基板パッド」部分 14 a の上面と基板の表面（絶縁層 16 の表面）が同一面上で平坦化される。バフ研磨以外にも、スクラップ研磨やサンドブラストなど、必要に応じて他の機械研磨を行ってもよい。

10

#### 【0036】

以上説明したように、本実施形態に係る配線基板 10（図 2）及びその製造方法（図 3～図 6）によれば、基板パッド 14 a の上面は配線基板 10 の表面（絶縁層 16 の表面）と同一面上に位置するので、基板パッド 14 a の側面は外部に露出せず、その上面のみが露出する。これに対し、従来の技術（図 1）では基板パッド 3 の側面も露出していた。

20

#### 【0037】

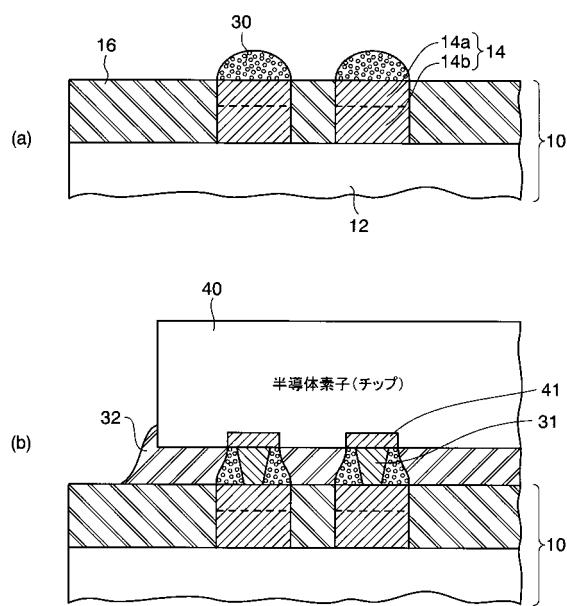

従って、フリップチップ接続のためのはんだを基板パッドに被着させる際にはんだ粉を基板パッドの表面に吸着させると、本配線基板 10 の表面には凹凸の段差がない（平坦化されている）ため、図 7 (a) に例示するように、基板パッド 14 a の上面にのみはんだ粉 30 を吸着させることができる。これにより、従来技術（図 1 (a)）に見られたような隣接する基板パッド 3（その対向する側面）上のはんだ粉 4 同士のショートもしくはブリッジの発生要因を実質的に無くすことができる。

#### 【0038】

30

また、本配線基板 10 に半導体チップをフリップチップ接続した後に両者間にアンダーフィル樹脂を充填する際にも、基板パッド 14 a と基板表面が同一面にあるので、基板パッド 14 a のピッチが狭くなっている場合でも、アンダーフィル樹脂を比較的スムーズに流動させることができ（流動性の均一化）、樹脂が内部に入り易くなる。これにより、従来技術（図 1 (b)）に見られたようなボイド VD の発生や充填不足といった不良発生要因を大いに減らす（実質的に無くす）ことができる。このことは、客先（本配線基板 10 にチップを搭載するメーカーなど）での歩留り改善に大いに寄与する。

#### 【0039】

図 7 (b) はフリップチップ実装後の半導体装置の一例を示したものであり、本配線基板 10（基板パッド 14 a）に半導体素子 40（チップパッド 41）をはんだバンプ 31 を介してフリップチップ接続した後、チップ 40 と配線基板 10 の間にアンダーフィル樹脂 32（例えば、エポキシ系樹脂やアクリル系樹脂等の熱硬化性樹脂）を充填した状態を示している。なお、図 7 (b) には示していないが、配線基板 10 の裏面（チップ搭載面側と反対側の面）にも、配線層のパッド部分を除いて全面（裏面）を覆うようにソルダレジスト等からなる絶縁層が形成されており、この絶縁層から露出するパッド部分に、半導体装置の外部接続端子として機能する金属ボールや金属ピン等がはんだを介して接合されている。

40

#### 【0040】

上述した実施形態では、図 3 (c) の工程において配線層 14 を「厚付け配線めっき」により一括して形成する場合を例にとって説明したが、配線層 14 の形成方法はこれに限

50

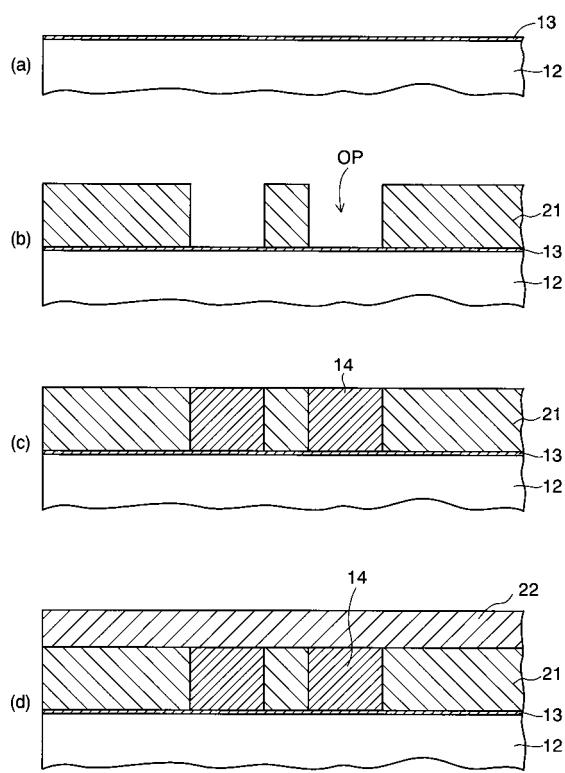

定されないことはもちろんである。例えば、後の工程（図5（a））で「基板パッド」部分14a以外の配線部分を「必要量」エッティングすることを考慮すると、この「必要量」をより確実に制御できるようにするために、「下配線」部分14bと「基板パッド」部分14aの2段に分けて配線層を形成するようにしてもよい。その場合の処理工程の一例を図8に示す。

#### 【0041】

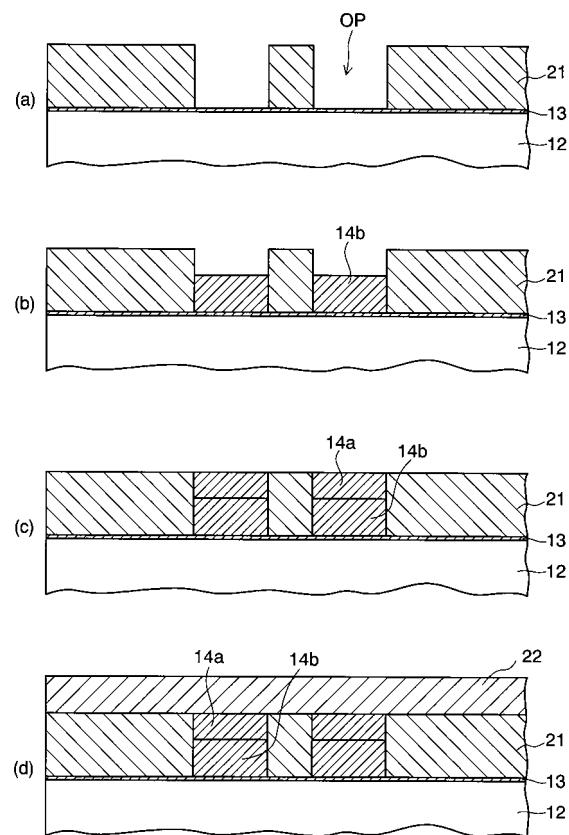

図8において、先ず、上述した図3（b）の工程で行った処理と同様にして、樹脂基板12（導体層13）上に所要の配線パターンの形状に応じたレジスト層21を25μm程度の厚さに形成し（図8（a）参照）、次に、レジスト層21の開口部OPから露出しているシード層（Cu）13を給電層として電解銅（Cu）めっきを施し、開口部OP内を15μm程度埋め込むようにして「下配線」部分14bを形成する（図8（b）参照）。さらに、「下配線」部分14bを形成した時の電解めっきの条件と異なる条件（例えば、めっき液を変えたり、印加する電源電圧を直流（DC）方式から交流（AC）方式あるいはパルス方式に変えるなど）の下に、「下配線」部分14bに電解銅（Cu）めっきを施し、開口部OP内の残りの部分（10μm程度）を埋め込むようにして「基板パッド」部分14aを形成する（図8（c）参照）。そして、図3（d）の工程で行った処理と同様にして、全面にレジスト層22を形成する（図8（d）参照）。

#### 【0042】

この実施形態によれば、上述した実施形態に係る製造方法と比べて、配線層を形成するための工程を2回に分けているため工程数が1つ増えるものの、「下配線」部分14bと「基板パッド」部分14aとで電解めっきの条件を変えているので、各部分のめっき配線の結晶配向を変えることができる（つまり、各部分のエッチングレートを異ならせることができる）。これにより、後の工程（図5（a））で「基板パッド」部分14a以外の配線部分を「必要量」エッティングする際に、各部分のめっき配線の結晶配向（エッチングレート）の違いにより、その「必要量」の厚さ、すなわち、「基板パッド」部分14aの厚さと「下配線」部分14bの厚さをより確実に制御することができる。

#### 【0043】

図8に示した実施形態では、「下配線」になる部分14bと「基板パッド」になる部分14aとに分けてそれぞれ銅（Cu）めっき配線の結晶配向を変えることで各部分のエッチングレートを異ならせるようにしたが、この方法以外にも、例えば、各部分のめっき配線間に中間金属層（バリヤメタル）を形成するようにしてもよい。この方法では、「下配線」になる部分14bの銅（Cu）めっき配線を形成した後、このめっき配線上に、例えば、ニッケル（Ni）めっき及び金（Au）めっきを施して2層構造（Ni/Au）のバリヤメタル層を形成し、更にこのバリヤメタル層上に、「基板パッド」になる部分14aの銅（Cu）めっき配線を形成する。

#### 【0044】

この実施形態では、バリヤメタル層とめっき配線のエッチングレートが異なるため、図5（a）の工程で「基板パッド」部分14a以外の配線部分を「必要量」エッティングする際に、バリヤメタル層はそのエッティングのストップ層として機能する。これにより、上記の実施形態の場合と同様に、「基板パッド」部分14aの厚さと「下配線」部分14bの厚さをより確実に制御することができる。

#### 【図面の簡単な説明】

#### 【0045】

【図1】従来のフリップチップ実装用基板の問題点を説明するための図である。

【図2】本発明の一実施形態に係る配線基板（フリップチップ実装用基板）の構成を示す断面図である。

【図3】図2の配線基板の製造方法の工程を示す断面図である。

【図4】図3の製造工程に続く工程を示す断面図（一部は上面図）である。

【図5】図4の製造工程に続く工程を示す断面図（一部は斜視図）である。

【図6】図5の製造工程に続く工程を示す断面図である。

10

20

30

40

50

【図7】図2の配線基板によって得られる効果を説明するための図である。

【図8】図3(c)の工程における配線層形成処理の他の実施形態に係る処理工程を示す断面図である。

【符号の説明】

【0046】

- 10 ... 配線基板(フリップチップ実装用基板)、

- 12 ... 樹脂基板、

- 13 ... シード層(導体層)、

- 14 ... 配線層、

- 14a ... 基板パッド(配線層の「基板パッド」部分)、

- 14b ... 下配線(配線層の「下配線」部分)、

- 16 ... ソルダレジスト層(絶縁層/保護膜)、

- 21, 22, 22a ... レジスト層、

- 30 ... はんだ粉、

- 31 ... はんだバンプ、

- 32 ... アンダーフィル樹脂、

- 40 ... 半導体素子(チップ)、

- 41 ... 電極端子(チップパッド)、

- SP ... 隣接する基板パッド(側面)上のはんだ粉同士がショートしている部分、

- VD ... ボイド(空洞部分)。

10

20

【図1】

(b)

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

審査官 中尾 麗

(56)参考文献 特開2004-095972(JP,A)

特開2005-166910(JP,A)

特開2003-008228(JP,A)

特開平03-253091(JP,A)

特開2002-299779(JP,A)

特表平09-500762(JP,A)

特開平11-126974(JP,A)

(58)調査した分野(Int.Cl., DB名)

H05K 1/02

H01L 23/12

H05K 3/18

H05K 3/22