(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7330605号

(P7330605)

(45)発行日 令和5年8月22日(2023.8.22)

(24)登録日 令和5年8月14日(2023.8.14)

(51)国際特許分類

|        |                  |        |        |         |

|--------|------------------|--------|--------|---------|

| H 01 L | 21/338 (2006.01) | H 01 L | 29/80  | H       |

| H 01 L | 29/778 (2006.01) | H 01 L | 29/78  | 3 0 1 B |

| H 01 L | 29/812 (2006.01) | H 01 L | 29/78  | 3 0 1 G |

| H 01 L | 21/336 (2006.01) | H 01 L | 21/316 | M       |

| H 01 L | 29/78 (2006.01)  | H 01 L | 21/318 | M       |

請求項の数 16 外国語出願 (全16頁) 最終頁に続く

(21)出願番号 特願2018-189353(P2018-189353)

(22)出願日 平成30年10月4日(2018.10.4)

(65)公開番号 特開2019-75558(P2019-75558A)

(43)公開日 令和1年5月16日(2019.5.16)

審査請求日 令和3年9月21日(2021.9.21)

(31)優先権主張番号 62/571,642

(32)優先日 平成29年10月12日(2017.10.12)

(33)優先権主張国・地域又は機関

米国(US)

前置審査

(73)特許権者 501315784

パワー・インテグレーションズ・インコ

ーポーレーテッド

アメリカ合衆国・95138・カリフォ

ルニア州・サンホゼ・ヘリヤー・アベニ

ュ・5245

(74)代理人 100125818

弁理士 立原 聰

(72)発明者 ジャマール ラムダニ

アメリカ合衆国 08530 ニュージャ

ージー州 ランパートヴィル、フェリス

ホイール ドライヴ 26

審査官 杉山 芳弘

最終頁に続く

(54)【発明の名称】 ヘテロ構造デバイスのためのゲートスタック

## (57)【特許請求の範囲】

## 【請求項1】

第1の活性層と、

前記第1の活性層上に位置する第2の活性層であって、二次元電子気体層が、前記第1の活性層と前記第2の活性層との間に形成される、前記第2の活性層と、

前記第2の活性層上に位置するサンドウィッチゲート誘電体層構造物であって、前記サンドウィッチゲート誘電体層構造物が、

a) 前記第2の活性層上に位置する第1のゲート誘電体層であって、前記第1のゲート誘電体層が、1~5ナノメートルの厚さの範囲内の第1の厚さをもち、および、窒化物ベースの化合物を含む、前記第1のゲート誘電体層と、

b) 前記第1のゲート誘電体層上に位置する第2のゲート誘電体層であって、前記第1のゲート誘電体層と前記第2のゲート誘電体層とが、同じ材料からなり、前記第2のゲート誘電体層が、20~60ナノメートルの範囲内の第2の厚さをもち、および、窒化物ベースの化合物を含み、前記第1の厚さと前記第2の厚さとの和が、30nm~60nmの範囲内である、前記第2のゲート誘電体層と、

c) 前記第2のゲート誘電体層上に位置する第3のゲート誘電体層であって、前記第3のゲート誘電体層が、10~20ナノメートルの範囲内の第3の厚さをもち、および、酸化アルミニウムを含み、前記第2の厚さが、前記第1の厚さおよび前記第3の厚さより大きい、前記第3のゲート誘電体層と、

を備える、前記サンドwichゲート誘電体層構造物と、

前記サンドウィッヂゲート誘電体層構造物の上方に位置するパッシベーション層と、前記パッシベーション層を通って前記サンドウィッヂゲート誘電体層構造物の上部まで延びたゲートと、

前記第2の活性層に電気的に接続する第1および第2のオーミック接点であって、前記第1のオーミック接点と前記第2のオーミック接点とが、横方向に離隔され、前記ゲートが、前記第1のオーミック接点と前記第2のオーミック接点との間に位置する、前記第1および第2のオーミック接点と、

を備える、ヘテロ構造半導体デバイス。

【請求項2】

前記第1のゲート誘電体層が、窒化ケイ素(SiN)を含む、

請求項1に記載のヘテロ構造半導体デバイス。

10

【請求項3】

前記第1のゲート誘電体層が、窒化炭素(CN)または窒化ホウ素(BN)を含む、

請求項1に記載のヘテロ構造半導体デバイス。

【請求項4】

前記第1のゲート誘電体層が、原子層堆積により形成された層である、

請求項1に記載のヘテロ構造半導体デバイス。

【請求項5】

前記ゲートを通る漏れ電流が前記ヘテロ構造半導体デバイスの通常動作中に温度に対して一定であるように、前記第1の厚さ、前記第2の厚さ、および前記第3の厚さが設定された、

20

請求項1に記載のヘテロ構造半導体デバイス。

【請求項6】

閾値電圧が前記ヘテロ構造半導体デバイスの通常動作中に温度に対して一定であるよう前記第1の厚さ、前記第2の厚さ、および前記第3の厚さが設定された、

請求項1に記載のヘテロ構造半導体デバイス。

30

【請求項7】

前記第1の活性層が、窒化ガリウム(GaN)を含み、

前記第2の活性層が、アルミニウムガリウム窒化物(AlGaN)を含む、

請求項1に記載のヘテロ構造半導体デバイス。

【請求項8】

前記ゲートが、ドレインのオーミック接点に向けて延びたゲートフィールドプレートを含む、

請求項1に記載のヘテロ構造半導体デバイス。

30

【請求項9】

前記パッシベーション層が、窒化ケイ素(SiN)を含む、

請求項1に記載のヘテロ構造半導体デバイス。

【請求項10】

基材上に第1の活性層を形成することと、

前記第1の活性層上に第2の活性層を形成することであって、

40

二次元電子気体層が前記第1の活性層と前記第2の活性層との間に形成されるよう前記第1の活性層と前記第2の活性層とが異なるバンドギャップをもつ、

前記第2の活性層を形成することと、

前記第2の活性層上に第1のゲート誘電体層を、前記第1の活性層および前記第2の活性層とインサイチュで形成することであって、

前記第1のゲート誘電体層が、1~5ナノメートルの範囲内の第1の厚さをもつ窒化物ベースの化合物を含む、

前記第1のゲート誘電体層を形成することと、

前記第1のゲート誘電体層上に第2のゲート誘電体層を、前記第1の活性層および前記第2の活性層とインサイチュで形成することであって、

50

前記第2のゲート誘電体層が、20～60ナノメートルの範囲内の第2の厚さをもつ窒化物ベースの化合物を含み、および、前記第1の厚さより厚く、前記第1の厚さと前記第2の厚さとの和が、30nm～60nmの範囲内である、

前記第2のゲート誘電体層を形成することと、

前記第2のゲート誘電体層上に第3のゲート誘電体層を形成することであって、

前記第3のゲート誘電体層が、酸化アルミニウムを含み、および、10～20ナノメートルの範囲内の第3の厚さをもち、および、前記第2の厚さより薄く、および、前記第1の厚さより厚い、

前記第3のゲート誘電体層を形成することと、

前記第3のゲート誘電体層と前記第2のゲート誘電体層と前記第1のゲート誘電体層とを通って縦方向に各々が伸びた第1および第2のオーミック接点を形成することであって、

前記第1のオーミック接点と前記第2のオーミック接点とが、横方向に離隔されて、前記第2の活性層に電気的に接続する、

前記第1および第2のオーミック接点を形成することと、

前記第1のオーミック接点と前記第2のオーミック接点との間の横方向位置において前記第3のゲート誘電体層に接触するゲートを形成することと、

を含む、ヘテロ構造半導体デバイスを製造する方法。

#### 【請求項11】

前記第1のオーミック接点と前記第2のオーミック接点とを形成する前に、前記第3のゲート誘電体層の上方にパッシベーション層を堆積および形成することをさらに含む、

請求項10に記載の方法。

#### 【請求項12】

前記第1のオーミック接点と前記第2のオーミック接点とをアニーリングすることをさらに含む、

請求項10に記載の方法。

#### 【請求項13】

前記ヘテロ構造半導体デバイスの正常動作中の温度にわたってゲート・ソース漏れ電流が一定に留まるように、前記第1の厚さ、前記第2の厚さ、および前記第3の厚さが選択される、

請求項10に記載の方法。

#### 【請求項14】

前記第1のゲート誘電体層と前記第2のゲート誘電体層とが、窒化ケイ素を含む、

請求項10に記載の方法。

#### 【請求項15】

前記第1のゲート誘電体層と前記第2のゲート誘電体層とが、有機金属化学気相成長法を使用して形成される、

請求項10に記載の方法。

#### 【請求項16】

前記第2のゲート誘電体層が、原子層堆積を使用して形成される、

請求項10に記載の方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、概して、高電圧電界効果トランジスタ(FET: field effect transistors)に関し、特に、高電子移動度トランジスタ(HEMT: high h-electron-mobility transistor)およびヘテロ構造電界効果トランジスタ(HFET: heterostructure field-effect transistor)、およびこのようなパワートランジスタデバイスを製造する方法に関する。

##### 【背景技術】

10

20

30

40

50

## 【0002】

高電圧FETのうちの一種がヘテロ構造FET(HFET)であり、高電子移動度トランジスタ(HEMT)とも呼ばれる。窒化ガリウム(GaN)、および、炭化ケイ素(SiC)などの他の広バンドギャップII族窒化物ベースの直接遷移半導体材料をベースとしたHFETが、それらの物理的性質を理由として特定の電子デバイスにおいて使用される。例えば、GaNおよびAlGaN/GaNトランジスタは、GaNベースの材料およびデバイス構造によりもたらされる高電子移動度、高い絶縁破壊電圧、および高飽和電子速度といった特性を理由として、高速スイッチングおよび高出力用途(例えば電力スイッチおよび電力コンバーター)において一般的に使用される。HFETの物理的性質に起因して、HFETは、同じ電圧において同じ電流を伝導する他の半導体スイッチより実質的に速く状態を変えることができ、広バンドギャップは、高温におけるHFETの性能を改善することができる。

10

## 【0003】

GaNベースのHFETデバイスは、典型的には、薄いゲート誘電体(例えば酸化物)材料の上方に形成されたゲート部材を含む。従来、ゲート酸化物と下方のGaN層との間における界面状態は、GaNベースのHFETの安定性および電気的信頼性における役割を果たす。ゲート安定性を改善することは、より高い電圧(例えば600V)の動作を達成することができる。典型的なHFETゲート構造はショットキーゲートを含み、ショットキーゲートは、ゲート酸化物を含まないか、または単一の薄いゲート酸化物層を含む。これらの構造物は、通常20~40Vの範囲内のクリティカル電圧による影響を受ける。クリティカル電圧V<sub>CRIT</sub>は、ゲート漏れ電流に比較的急峻な立ち上がりが存在するゲート対ソース電圧V<sub>GS</sub>として規定される。

20

## 【0004】

以下の図を参照しながら、本発明の非限定的かつ非網羅的な実施形態が説明され、異なる図の中の同様の参照符号は、別段の指定がない限り、同様の部分を示す。

## 【図面の簡単な説明】

## 【0005】

【図1】サンドウィッヂゲート誘電体構造物をもつ例示的な半導体デバイスの断面側面図である。

30

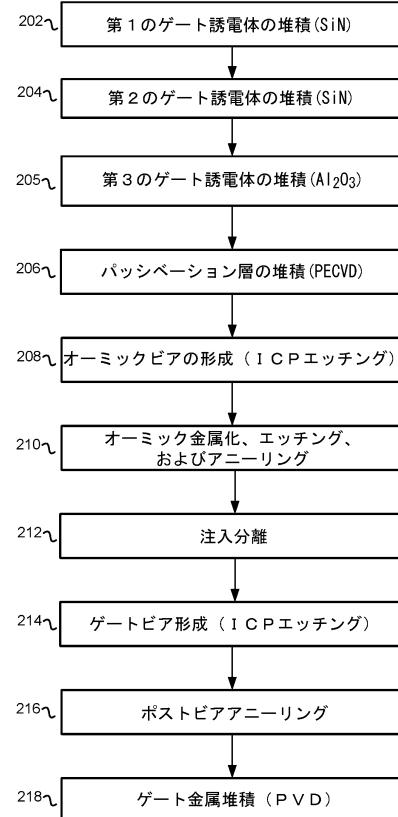

【図2】サンドウィッヂゲート誘電体構造物をもつ半導体デバイスを製造するための例示的な工程フローを示す図である。

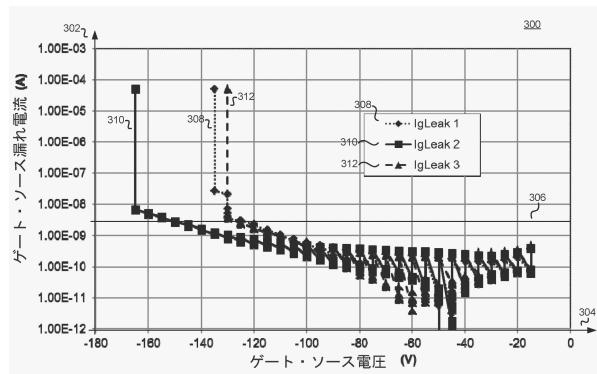

【図3】サンドウィッヂゲート誘電体構造物の印加されたステップストレスに対する例示的なゲート・ソース漏れを示すグラフである。

## 【発明を実施するための形態】

## 【0006】

図面中の複数の図にわたり、対応する参照符号が、対応する構成要素を示す。当業者は、図中の要素が簡潔かつ明確であるように描かれることと、一定の縮尺で描かれるとは限らないことを理解する。例えば、図中のいくつかの要素の寸法は、本発明の様々な実施形態をより理解しやすくするために、他の要素より誇張される場合があり得る。さらに、市販に適した実施形態において有用または必要な、一般的だがよく理解される要素は、多くの場合、本発明に係るこれらの様々な実施形態の図が見づらくなるのを防ぐために、描かれない。

40

## 【0007】

複数のゲート誘電体層を含むヘテロ構造トランジスタの例が本明細書において説明される。以下の説明では、本発明を十分に理解できるように、多くの特定の詳細事項が記載される。しかし、本発明を実施する際に特定の詳細事項が使用されるとは限らないことが、当業者には明らかとなる。他の例では、よく知られた材料または方法については、本発明が理解しにくくなるのを防ぐために、詳細には説明されない。

## 【0008】

本明細書中での、「一実施形態(one embodiment)」、「一実施形態(

50

an embodiment)」、「一例 (one example)」、または「一例 (an example)」についての言及は、実施形態または例との関連で説明される特定の特徴、構造、または特性が本発明の少なくとも 1 つの実施形態に含まれることを意味する。従って、本明細書中の様々な場所で使用する「一実施形態において (in one embodiment)」、「一実施形態において (in an embodiment)」、「一例 (one example)」または「例 (an example)」という語句は、すべてが同じ実施形態または例に関するとは限らない。さらに、特定の特徴、構造、または特性は、1 つまたは複数の実施形態または例において、任意の適切な組み合わせ、および / または部分的組み合わせで組み合わされ得る。特定の特徴、構造、または特性は、説明される機能を提供する集積回路、電子回路、結合論理回路、または他の適切な構成要素に含まれ得る。加えて、本明細書とともに提供される図が当業者への説明を目的としていることと、図面が一定の縮尺で描かれるとは限らないことが理解される。

#### 【0009】

本明細書において使用される場合、H F E T デバイスの「クリティカル電圧 (critical voltage)」または「クリティカルゲート電圧 (critical gate voltage)」は、ゲート漏れ電流に比較的急峻な立ち上がりが存在するゲート対ソース電圧として規定される。熱安定性は、温度に応じてデバイスのゲート漏れ電流がどの程度増加するかに関する。

#### 【0010】

上述のように、典型的な H F E T ゲート構造は、ゲート酸化物を含まないか、または単一の薄いゲート酸化物層を含むショットキーゲートを含む。これらの構造物は、通常 20 ~ 40 V の範囲内の低クリティカル電圧の影響を受ける。クリティカル電圧 V C R I T は、ゲート漏れ電流に比較的急峻な立ち上がりが存在するゲート対ソース電圧 V G S として規定される。より高い信頼性および高いゲート酸化物の完全性を達成するために、クリティカル電圧は、現在の範囲の 20 ~ 40 V から上げられることが必要である。さらに、単一の薄いゲート酸化物層を含むデバイスは、デバイスが高温 (摂氏 120 度など) で動作しているとき、室温における漏れ電流より 2 または 3 倍大きなゲート漏れ電流の増加を経験し得る。

#### 【0011】

ゲート誘電体の性質はまた、H F E T の他のパラメータおよび特性に影響を与える。例えば、ゲート誘電体層の厚さに下方の障壁層の厚さを加えたものが、高電圧 H F E T のゲート閾値電圧を部分的に決定する。より厚いゲート誘電体が、より高い温度またはより高い印加されるゲート電圧にともなうゲート漏れ電流を減らす一方で、ゲート誘電体の厚さは閾値電圧に寄与する。従って、H F E T デバイスのための一定の閾値電圧を提供する能力と、熱および電圧安定性との間にトレードオフが存在する。

#### 【0012】

本発明の実施形態によると、サンドウィッヂゲート誘電体構造物を含む G a N ベースの H F E T デバイス、およびそれを製造する方法が開示される。一実施形態において、H F E T デバイスは、第 1 の活性層と第 2 の活性層とを、その間に生じる二次元電子気体層とともに含む。サンドウィッヂゲート誘電体構造物は、第 2 の活性層上に位置し、第 1 のゲート誘電体層、第 2 のゲート誘電体層、および第 3 のゲート誘電体層を含む。第 1 のゲート誘電体層は、第 2 の活性層上に位置する。窒化ケイ素 (S i N)、窒化炭素 (C N)、窒化ホウ素 (B N)、または窒化アルミニウム (A l N) などの窒化物ベースの化合物が、第 1 のゲート誘電体層のために使用され得る。第 2 のゲート誘電体層は、第 1 のゲート誘電体層上に位置し、S i N、C N、B N、または A l N が、第 2 のゲート誘電体層のために使用され得る。第 3 のゲート誘電体層は、第 2 のゲート誘電体層上に位置する。一例において、酸化アルミニウム (A l 2 O 3) が、第 3 のゲート誘電体層のために使用され得る。ゲートは、第 3 のゲート誘電体層上に位置し、サンドウィッヂゲート誘電体構造物の上部まで延びている。デバイスのオーミック接点 (ソースおよびドレイン) は、サンドウィッヂゲート誘電体構造物を通って延びて、第 2 の活性層に接触する。

10

20

30

40

50

## 【0013】

様々な実施形態において、このサンドウィッチゲート誘電体構造物は、高クリティカル電圧動作（例えば、> 80V）をもたらし得る。さらに、サンドwichゲート誘電体構造物を使用するデバイスは、改善された熱安定性を経験し得る。デバイスは、摂氏200度まで上昇する温度においてデバイスが動作しているときに、漏れ電流の変化を実質的に経験しないものであり得る。より安定かつ堅牢なゲート誘電体構造物を製造することに加えて、他の利点は、より低いゲート漏れ、およびより均一なゲート閾値電圧をさらに含み得る。サンドwichゲート誘電体構造物は、H F E T デバイスがゲート漏れ電流を最小化しながら一定の閾値電圧を維持することをさらに可能にし得る。

## 【0014】

以下の説明において、例示的なH F E T が説明を目的として使用される。しかし、本発明の実施形態が、金属-酸化物-半導体F E T (M O S F E T : metal oxide semiconductor F E T ) または金属-絶縁体-半導体F E T (M I S F E T : metal insulator semiconductor F E T ) デバイスなどの、他の種類のF E T に使用され得ることが理解されなければならない。

10

## 【0015】

図1は、第1の活性層102、第2の活性層106、第1のゲート誘電体108、第2のゲート誘電体110、第3のゲート誘電体112、パッシベーション層114、オーミック接点118および120、ならびにゲート116を含む半導体デバイス100（例えば、G a N H F E T ）の断面側面図を示す。図1に、2つの層間のバンドギャップ差に起因して、第1の活性層102と第2の活性層106との間に生じ得る電荷層104がさらに示される。電荷層106は、第1の活性層102と第2の活性層106との間ににおけるバンドギャップ差によりもたらされる量子井戸に捕獲された電子が、二次元に自由に動くが第3の次元に強く閉じ込められるので、二次元電子気体（2 D E G : two-dimensional electron gas）層106とも呼ばれる横方向伝導チャネルを規定する。さらに、第1の活性層102がチャネル層またはバッファ層とも呼ばれるのに対し、第2の活性層106は障壁層またはドナー層とも呼ばれる。

20

## 【0016】

第2の活性層106は、第1の活性層102上に位置する。サンドwichゲート誘電体構造物113は、第2の活性層上に位置し、第1のゲート誘電体層108、第2のゲート誘電体層110、および第3のゲート誘電体層112を含む。第1のゲート誘電体層108は、第2の活性層106上に位置する。第2のゲート誘電体層110は、第1のゲート誘電体層108上に位置する。第3のゲート誘電体層112は、第2のゲート誘電体層110上に位置する。パッシベーション層114は、サンドwichゲート113誘電体構造物上に位置する。示されるように、パッシベーション層114は、第3のゲート誘電体層112上に位置する。ゲート116は、パッシベーション層114を通って第3のゲート誘電体層112まで縦方向に下方に延びる。ソースオーミック接点118およびドレインオーミック接点120のそれぞれが、パッシベーション層114、第3のゲート誘電体層112、第2のゲート誘電体層110、および第1のゲート誘電体層108を通って縦方向に下方に延びて、第2の活性層106に電気的に接続することが示される。言い換えると、オーミック接点118および120は、サンドwichゲート誘電体構造物113の底部まで延びる。示されるように、ゲート116がソースオーミック接点118とドレインオーミック接点120との間に位置する状態で、ソースオーミック接点118とドレインオーミック接点120とが横方向に離隔されている。

30

## 【0017】

第1の活性層102は典型的には、サファイア（A l 2 O 3 ）、シリコン（S i ）、G a N 、または炭化ケイ素（S i C ）などの、多くの異なる材料のうちの任意の1つにより形成された基材（図示されない）の上方に位置することが理解される。一実施形態において、第1の活性層102は、エピタキシャルG a N 層を備える。格子不整合および/または熱膨張係数の差にともなう想定される問題を避けるために、1つまたは複数の追加的な

40

50

層が、基材と第1の活性層102との間に配置され得る。例えば、任意選択的な薄い核形成層が、基材と第1の活性層102との間に形成され得る。他の例において、第1の活性層102は、他のIII族元素の窒化化合物を含有する異なる半導体材料を含み得る。第1の活性層102は、基材上に成長または堆積するようにされ得る。

【0018】

図1に示す例において、第2の活性層106は、アルミニウムガリウム窒化物(AlGaN)を含む。他の例において、アルミニウムインジウム窒化物(AlInN)およびアルミニウムインジウムガリウム窒化物(AlInGaN)などの異なるIII族窒化物半導体材料が、第2の活性層106のために使用され得る。他の実施形態において、第2の活性層106の材料は、不定比化合物であり得る。このような材料において、元素の比は通常の整数により簡単に表されない。例えば、第2の活性層106は、 $0 < X < 1$ としたときのAl<sub>X</sub>Ga<sub>1-X</sub>NなどのIII族窒化物半導体材料の不定比化合物であり得る。第2の活性層106は、第1の活性層102上に成長または堆積するようにされ得る。

【0019】

一実施形態において、第1のゲート誘電体層108は、窒化ケイ素(SiN)を含む。他の実施形態において、第1のゲート誘電体層108は、Si<sub>3</sub>N<sub>4</sub>を含み得る。さらに違う他の例において、窒化炭素(CN)、窒化ホウ素(BN)、または窒化アルミニウム(AlN)などの異なる窒化物ベースの化合物が、第1のゲート誘電体層108のために使用され得る。第1のゲート誘電体層108は、第2の活性層106と原子配列を保ち得る窒化物ベースの材料であり得る。さらに、第1のゲート誘電体層108は、絶縁性であり得、少なくとも3電子ボルト(eV)のバンドギャップをもち得る。一例において、第1のゲート誘電体層108の厚さは、実質的に1~5ナノメートル(nm)の間の厚さであり得る。第1のゲート誘電体層108が、第1の活性層102および第2の活性層106のそれぞれとインサイチュ(inline-situ、引き続き同様の環境で)堆積され得る。第1のゲート誘電体層108が、金属・有機化学気相デコンポジション(MOCVD)を使用して堆積され得る。別の一実施形態において、第1のゲート誘電体層108が、原子層堆積(ALD:atomic layer deposition)を通して第1の活性層102および第2の活性層106からイクサイチュ(ex-situ、同様ではない環境で)堆積され得る。

【0020】

示されるように、第2のゲート誘電体層110は、第1のゲート誘電体層108上に位置する。一例において、第2のゲート誘電体層110は、窒化ケイ素(SiN)を含む。他の実施形態において、第2のゲート誘電体層110は、Si<sub>3</sub>N<sub>4</sub>を含み得る。窒化炭素(CN)、窒化ホウ素(BN)、または窒化アルミニウム(AlN)などの異なる窒化物ベースの化合物が、第2のゲート誘電体層110のために使用され得る。第2のゲート誘電体層110は、約20~60nmの厚さの範囲内の厚さをもつ。一実施形態において、第2のゲート誘電体層110は、第1のゲート誘電体層108より厚い。さらに、第2のゲート誘電体層110と第1のゲート誘電体層108との両方のために使用される材料が同じであり得る。第1のゲート誘電体層108および第2のゲート誘電体層110の厚さの和は、30~60nmの範囲内であり得る。第2のゲート誘電体層110は、MOCVDなどの工程を通して第1の活性層102および第2の活性層106ならびに第1のゲート誘電体層108とインサイチュで堆積するようにされ得る。別の一例において、第2のゲート誘電体層110は、ALDなどの工程を通して、第1の活性層102および第2の活性層106ならびに第1のゲート誘電体層108からイクサイチュで堆積するようにされ得る。

【0021】

第3のゲート誘電体層112は、第2のゲート誘電体層110上に位置する。一例において、第3のゲート誘電体層112は、酸化アルミニウム(Al<sub>2</sub>O<sub>3</sub>)を備える。さらなる例において、ZrO、HfO、SiO<sub>2</sub>、およびGdOなどの他の酸化物材料が、第3のゲート誘電体層112のために使用され得る。第3のゲート誘電体層112は、10

10

20

30

40

50

~20nmの範囲内の厚さをもつ。一実施形態において、第2のゲート誘電体層110は、第1のゲート誘電体層108および第3のゲート誘電体層112より厚い。一例において、第3のゲート誘電体層112は、ALDを使用して第1の活性層102および第2の活性層106からイクサイチュで堆積される。

【0022】

上述のゲート誘電体構造物は、第2のゲート誘電体層110が第1のゲート誘電体層108と第3のゲート誘電体層110との間に挟まれているので、サンドウィッチゲート誘電体構造物と呼ばれ得る。後述のように、この種類のサンドウィッチ構造物は、デバイス100の全体的な安定性を高め得、漏れ電流を大幅に減らし得る。他の例において、第1のゲート誘電体層108と第3のゲート誘電体層112との間に複数の挟まれた層が存在し得る。

10

【0023】

パッシベーション層114は、第3のゲート誘電体層112上に位置し、およびオーミック接点118、120、およびゲート116を横方向から囲む。一実施形態において、パッシベーション層114は、窒化ケイ素(SiN)などの誘電体材料を含み得る。パッシベーション層114は、複数の材料層を備え得る。パッシベーション層114は、環境の電気的および化学的汚染物質からデバイスの表面を隔離することにより、デバイス100の電気的特性の安定性を提供する。パッシベーション層114は、低圧化学蒸着(LP CVD: low pressure chemical vapor deposition)またはプラズマエンハンスト化学蒸着(PECVD: plasma-enhanced chemical vapor deposition)などの化学蒸着を通して堆積するようにされ得る。

20

【0024】

第1のゲート誘電体層108、第2のゲート誘電体層110、および第3のゲート誘電体層112のサンドウィッチゲート誘電体構造物は、それぞれ、第2の活性層106からゲート116を分離する。示されるように、ゲート116は、パッシベーション層114を通って位置して、第3のゲート誘電体層112に接触する。一実施形態において、ゲート116は、チタン/窒化チタン/アルミニウム銅スタックを備える。別の一実施形態において、ゲート116は、チタン金(TiAu)合金またはモリブデン金MoAu合金を含む。他の例において、ゲート116は、ゲート電極およびゲートフィールドプレートを備え得る。動作時、ゲート116は、オーミックソース接点118とオーミックドレイン接点120との間における順伝導路を制御する。例示的な製造工程において、ゲート116は、パッシベーション層114において開口をエッチングすることと、続くゲート金属堆積とにより形成され得る。図1に示す例において、パッシベーション層114の上方にあり、オーミックドレイン接点120に向かって横方向に延びたゲート116の一部が、(オーミック接点120に最も近い)縁部における電界強度を軽減するように機能するゲートフィールドプレートとして機能する。

30

【0025】

オーミック接点118および120は、パッシベーション層114、第3のゲート誘電体層112、第2のゲート誘電体層110、および第1のゲート誘電体層108を通って位置して、第2の活性層106に接触する。オーミック接点118はソース接点の一例であり、オーミック接点120はドレイン接点の一例である。一実施形態において、オーミック接点118および120は、パッシベーション層114、第3のゲート誘電体層112、第2のゲート誘電体層110、および第1のゲート誘電体層108において開口をエッチングすることと、続く金属堆積およびアニーリングステップとにより形成され得る。

40

【0026】

示されるように、図1は、それぞれ、GaN HfETデバイス100のソース電極およびドレイン電極を備えるオーミック金属接点118および120の形成直後における製造工程の一時点におけるデバイス構造を示す。図1は、第2の活性層106上に直接形成されたオーミック金属接点118および120を示す。他の実施形態において、オーミック

50

ク金属接点 118 および 113 は、第 2 の活性層 106 内に縦方向に下向きに延びた窪み内に形成され得る。他の実施形態において、オーミック金属接点 118 および 120 は、第 2 の活性層 106 を通って縦方向に下向きに延びた窪み内に形成されて、第 1 の活性層 102 に接触し得る。

【0027】

H F E T デバイス 100 が電力スイッチとしての使用のために構成されるとき、ゲート 116 ならびにオーミック接点 118 および 120 は、典型的には端子を通して結合されて、外部回路までの電気接続部を形成する。動作時、2 D E G 層 104 における電荷は、オーミック接点 118 とオーミック接点 120 との間に横方向に流れて、外部回路における電流となる。電荷の流れ、および従って電流は、ゲート 116 とオーミック接点 118 との間に電気的に接続された外部回路から電圧により制御され得る。

10

【0028】

本開示において使用されるように、電気接続はオーミック接続である。オーミック接続は、電圧と電流との間の関係が実質的に線形であり、両方向の電流に関して対称なものである。例えば、金属のみを通して各々に接触する 2 つの金属パターンが、電気的に接続される。対照的に、(示されるように)オーミック接点 118 および 120 は、これらの 2 つの接点の間ににおけるどの接続も半導体材料内のチャネルを通り、この伝導経路がゲート 116 により制御されるので、H F E T デバイス 100 において互いに電気的に接続されない。同様に、第 1 のゲート誘電体層 108、第 2 のゲート誘電体層 110、および第 3 のゲート誘電体層 112 が下層の活性層からゲート 116 を絶縁するので、ゲート 116 は第 2 の活性層 106 に電気的に接続されない。

20

【0029】

上述の実施形態において、第 1 のゲート誘電体層 (108)、第 2 のゲート誘電体層 (110)、および第 3 のゲート誘電体層 (112) の厚さは、ゲート漏れ電流が H F E T デバイス 100 の通常動作中の温度にわたって実質的に一定に留まるようなものである。言い方をえれば、H F E T デバイス 100 は、デバイスが 120 で動作しているときに、ゲート漏れ電流の実質的な変化をまったく経験しないものであります。加えて、本発明の様々な実施形態は、ゲート漏れ電流に対する著しい変化をともなわずに最大 200 で動作し得る。

30

【0030】

さらに、本明細書において説明されるサンドウィッヂゲート誘電体層構造物は、H F E T デバイスの電圧安定性を改善し得る。例えば、H F E T デバイス 100 のクリティカル電圧は、約 100 ~ 170 V の範囲まで著しく高められる。

【0031】

図 2 は、図 1 に示される H F E T デバイス 100 などの半導体デバイスを製造するための例示的な工程フローを示す図 200 である。示される例において、第 1 の活性層と第 2 の活性層との両方が、基材上に堆積または成長するようにされた後、本工程が始まる。ブロック 202 から始まり、第 1 のゲート誘電体層がインサイチュで成長するようにされる。一実施形態において、第 1 のゲート誘電体層は、800 ~ 1050 の間の温度範囲において行われる M O C V D 技術を使用して堆積される。第 1 のゲート誘電体層は、約 1 ~ 5 nm の厚さに形成され、ウエハの表面の上方において連続的である。一実施形態において、ゲート誘電体層の厚さは約 4 nm である。別の一実施形態において、第 1 のゲート誘電体層は、第 1 の活性層および第 2 の活性層とインサイチュで形成される。例えば、第 1 の活性層と第 2 の活性層とを形成するために使用される同じ機械 (M O C V D) が、第 1 のゲート誘電体層を形成するためにも使用され得る。第 1 のゲート誘電体層は、S i N を含み得る。S i N の第 1 のゲート誘電体層を堆積させると、堆積のための S i 源は、S i の源としてのシランまたはジシランであり得る。他の実施形態において第 1 のゲート誘電体層は、第 1 の活性層と第 2 の活性層とからイクサイチュで堆積するようにされ得る。

40

【0032】

次に、ブロック 204 において、第 2 のゲート誘電体層は、第 1 のゲート誘電体層の上

50

に堆積するようにされる。一実施形態において、第2のゲート誘電体層は、MOCVDを使用して第1の活性層および第2の活性層ならびに第1のゲート誘電体層とインサイチュで堆積するようにされる。第2のゲート誘電体層は、約20~60nmの厚さに形成され、ウエハの表面の上方において連続的である。第1のゲート誘電体層は、SiNを含み得る。SiNの第1のゲート誘電体層を堆積させると、堆積のためのSi源は、Siの源としてのシランまたはジシランであり得る。別の一実施形態において、第2のゲート誘電体層は、第1のゲート誘電体層からイクサイチュで堆積するようにされ得、プラズマエンハンスト原子層堆積(PEALD: plasma-enhanced atomic layer deposition)、誘導結合プラズマ(ICP: inductive coupling plasma)、化学蒸着(CVD: chemical vapor deposition)、または原子層堆積(ALD)を使用して堆積するようにされ得る。ALDによりSiNの第2のゲート誘電体層を堆積させると、堆積のためのSi源は、アミノシランまたはSiの有機金属源であり得る。

#### 【0033】

ブロック205において、第3のゲート誘電体層は、PEALDを使用して300において第1のゲート誘電体層ならびに第1の活性層および第2の活性層からイクサイチュでウエハ表面上に堆積される。一実施形態において、第3のゲート誘電体層は、Al(CH<sub>3</sub>)<sub>3</sub>前駆体およびO<sub>2</sub>プラズマを使用してALDを使用して堆積するようにされる。第3のゲート誘電体層は、10~20nmの範囲内の厚さまで形成される。

#### 【0034】

プロセスはブロック206に進み、ブロック206において、パッシベーション層が第3のゲート誘電体層の上方に堆積するようにされる。一実施形態において、パッシベーション層は、PECVDを使用して堆積するようにされ得る。パッシベーション層は、典型的には約100~150nmの範囲内の厚さまで形成される。上述のように、パッシベーション層は、窒化ケイ素(SiN)または同様の性質をもつ他の材料を含み得る。

#### 【0035】

ブロック208において、オーミックビアが形成される。オーミックソース接点とオーミックドレイン接点とが、パッシベーション層およびサンドウィッヂゲート誘電体構造物を通して形成される。一例において、オーミックビアが、誘導結合プラズマ(ICP)エッチングを使用して形成される。

#### 【0036】

ブロック210において、オーミック金属化、エッチング、およびアニーリングが実施される。上述の層を通してオーミックビアが形成された後、金属または金属合金が堆積するようにされて、開口を充填する。1つの例示的な製造シーケンスにおいて、オーミック接点のために使用される金属は、スパッタリング技術または物理蒸着(PVD: physical vapor deposition)を使用して堆積するようにされる。例示的なオーミック接点金属は、チタン(Ti)、アルミニウム(Al)、チタン(Ti)、および窒化チタン(TiN)の層を含み得る。金属オーミック接点は、次に、約400~600の温度範囲においてRTAツールを使用するアニーリングされる。ブロック212において、デバイスを分離する注入分離が、窒素またはアルゴン注入を使用して実施され得る。

#### 【0037】

ゲートは、オーミック接点と同様の手法で形成され得る。ブロック214において、ゲートビアが、パッシベーション層を通して開口をエッチングして第3のゲート誘電体層を露出することにより形成され得る。一実施形態において、ICPエッチングが実施され得る。

#### 【0038】

エッチング工程が第3のゲート誘電体層を露出した後、ブロック216において、デバイスが高温アニーリングを経る。例示として、アニーリングステップは、約5~20分間にわたって450~650の温度範囲において炉の中で実施され得る。アニーリングは

10

20

30

40

50

、また、急速熱アニーリング( R T A : r a p i d t e m p e r a t u r e a n n e a l i n g )ツールなどの多くの異なるツールを使用して実施され得る。

【 0 0 3 9 】

ブロック 218において、ゲート金属または金属合金堆積が実施されてエッティングされた開口を充填する。金属は、スパッタリング技術または物理蒸着( P V D )を使用して堆積するようにされ得る。例示的なゲート金属は、チタン( T i )、窒化チタン( T i N )、アルミニウム銅( A l C u )、および窒化チタン( T i N )の層を含み得る。

【 0 0 4 0 】

半導体分野の当業者は、ウエハの表面上に金属( 例えは、パターン形成された線またはトレース )を形成すること、ウエハ裏面研磨( 裏面ラッピングまたはウエハ薄化とも呼ばれる )、ダイ分離、およびパッケージングを含む、他の標準的な製造後の、または最終段階の処理ステップが実施され得ることを理解する。

10

【 0 0 4 1 】

図 3 は、各々が図 1 に示すサンドウィッヂゲート誘電体構造物を含む様々な H F E T デバイスに対する、印加されたステップストレス電圧に対する例示的なゲート・ソース漏れ電流を描いたグラフである。示されるように、x 軸は絶対ゲート電圧 304 を表し、y 軸はゲート・ソース漏れ電流 302 である。グラフ 300 は、クリティカル閾値レベル 306 をさらに示す。クリティカル閾値 306 は、ゲート・ソース漏れ電流 302 がもはや許容可能ではなく、デバイスが絶縁破壊状態にあるとみなされる閾値として規定され得る。示される例において、クリティカル閾値 306 は、実質的に 5.00 E - 9 A または 5 nA である。加えて、クリティカル電圧は、特定のデバイスに対するゲート・ソース漏れ電流がクリティカル閾値 306 に達するゲート電圧を表す。

20

【 0 0 4 2 】

示されるように、グラフ 300 は、第 1 のデバイス 308 、第 2 のデバイス 310 、および第 3 のデバイス 312 の性能を示す。ゲート・ソース漏れ電流 302 が測定されながら、様々なデバイスの各々に対するゲート電圧が次第に増加する。第 1 のデバイス 308 の場合、クリティカル電圧は約 -135 V である。第 2 のデバイス 310 の場合、クリティカル電圧は約 -165 V である。第 3 のデバイス 312 の場合、クリティカル電圧は約 -130 V である。3 つのデバイス 308 、 310 、および 312 のすべてが、第 1 のゲート誘電体層、第 2 のゲート誘電体層、および第 3 のゲート誘電体層を含むサンドウィッヂゲート誘電体構造物を実装する。図 3 に示されるように、デバイス 308 、 310 、および 312 に対するクリティカル電圧の大きさは、 100 V より大きい。サンドウィッヂゲート誘電体構造物を使用しないデバイスは、 100 V よりはるかに小さなクリティカル電圧の大きさをもち得る。

30

【 0 0 4 3 】

本発明に関して示される例についての上述の説明は、要約で説明される事項を含め、網羅的であることも、開示される形態そのものへの限定であることも意図されない。本発明の特定の実施形態および例が、本明細書において例示を目的として説明されるが、本発明のより広い趣旨および範囲から逸脱することなく様々な同等な変更が可能である。実際、特定の例示的な電圧、厚さ、材料種などが説明のために提示されることと、本発明の教示に従った他の実施形態および例において他の値も使用し得ることが理解される。

40

【付記項 1】

第 1 の活性層と、

前記第 1 の活性層上に位置する第 2 の活性層であって、二次元電子気体層が、前記第 1 の活性層と前記第 2 の活性層との間に形成される、前記第 2 の活性層と、

前記第 2 の活性層上に位置するサンドウィッヂゲート誘電体層構造物と、

前記サンドウィッヂゲート誘電体層構造物の上方に位置するパッシベーション層と、

前記パッシベーション層を通じて前記サンドウィッヂゲート誘電体層構造物の上部まで延びたゲートと、

前記第 2 の活性層に電気的に接続する第 1 および第 2 のオーミック接点であって、前記

50

第1のオーミック接点と前記第2のオーミック接点とが、横方向に離隔され、前記ゲートが、前記第1のオーミック接点と前記第2のオーミック接点との間に位置する、前記第1および第2のオーミック接点と、

を備える、ヘテロ構造半導体デバイス。

[付記項2]

前記サンドウィッチゲート誘電体層構造物が、

前記第2の活性層上に位置する第1のゲート誘電体層と、

前記第1のゲート誘電体層上に位置する第2のゲート誘電体層と、

前記第2のゲート誘電体層上に位置する第3のゲート誘電体層と、

を備える、

付記項1に記載のヘテロ構造半導体デバイス。

[付記項3]

前記第3のゲート誘電体層が、酸化アルミニウム(Al<sub>2</sub>O<sub>3</sub>)を含む、

付記項2に記載のヘテロ構造半導体デバイス。

[付記項4]

前記第1のゲート誘電体層が、第1の厚さをもち、

前記第2のゲート誘電体層が、第2の厚さをもち、

前記第3のゲート誘電体層が、第3の厚さをもち、

前記第2の厚さが、前記第1の厚さおよび前記第3の厚さより大きい、

付記項2に記載のヘテロ構造半導体デバイス。

10

[付記項5]

前記第1のゲート誘電体層が、窒化物ベースの化合物を含む、

付記項2に記載のヘテロ構造半導体デバイス。

[付記項6]

前記第1のゲート誘電体層が、窒化ケイ素(SiN)を含む、

付記項2に記載のヘテロ構造半導体デバイス。

[付記項7]

前記第1のゲート誘電体層が、窒化炭素(CN)を含む、

付記項2に記載のヘテロ構造半導体デバイス。

20

[付記項8]

前記第1のゲート誘電体層が、窒化ホウ素(BN)を含む、

付記項2に記載のヘテロ構造半導体デバイス。

30

[付記項9]

前記第1のゲート誘電体層と前記第2のゲート誘電体層とが、同じ材料を含む、

付記項2に記載のヘテロ構造半導体デバイス。

[付記項10]

前記第1のゲート誘電体層が、約1～5ナノメートルの厚さの範囲内の第1の厚さをもち、

前記第2のゲート誘電体が、約20～60ナノメートルの範囲内の第2の厚さをもち、

前記第3のゲート誘電体が、10～20ナノメートルの範囲内の第3の厚さをもつ、

付記項2に記載のヘテロ構造半導体デバイス。

40

[付記項11]

前記ゲートを通る漏れ電流がヘテロ接合半導体デバイスの通常動作中に温度に対して実質的に一定であるように、前記第1の厚さ、前記第2の厚さ、および前記第3の厚さが設定された、

付記項9に記載のヘテロ構造半導体デバイス。

[付記項12]

閾値電圧がヘテロ接合半導体デバイスの通常動作中に温度に対して実質的に一定であるように、前記第1の厚さ、前記第2の厚さ、および前記第3の厚さが設定された、

付記項9に記載のヘテロ構造半導体デバイス。

50

## [付記項 1 3]

前記第1の活性層が、窒化ガリウム (GaN) を含み、

前記第2の活性層が、アルミニウムガリウム窒化物 (AlGaN) を含む、

付記項1に記載のヘテロ構造半導体デバイス。

## [付記項 1 4]

前記ゲート金属が、前記ドレインオーミック接点に向けて延びたゲートフィールドプレートを含む、

付記項1に記載のヘテロ構造半導体デバイス。

## [付記項 1 5]

前記パッシベーション層が、窒化ケイ素 (SiN) を含む、

付記項1に記載のヘテロ構造半導体デバイス。

## [付記項 1 6]

基材上に第1の活性層を形成することと、

前記第1の活性層上に第2の活性層を形成することであって、

二次元電子気体層が前記第1の活性層と前記第2の活性層との間に形成されるように、

前記第1の活性層と前記第2の活性層とが異なるバンドギャップをもつ、

前記第2の活性層を形成することと、

前記第2の活性層上に第1のゲート誘電体層を形成することであって、

前記第1のゲート誘電体層が、第1の厚さをもつ、

前記第1のゲート誘電体層を形成することと、

前記第1のゲート誘電体層上に第2のゲート誘電体層を形成することであって、

前記第2のゲート誘電体層が、前記第1の厚さより大きな第2の厚さをもつ、

前記第2のゲート誘電体層を形成することと、

前記第2のゲート誘電体層上に第3のゲート誘電体層を形成することであって、

前記第3のゲート誘電体層が、前記第2の厚さより小さく、前記第1の厚さより大きな第3の厚さをもつ、

前記第3のゲート誘電体層を形成することと、

前記第3のゲート誘電体層と前記第2のゲート誘電体層と前記第1のゲート誘電体層とを通って縦方向に各々が延びた第1および第2のオーミック接点を形成することであって、

前記第1のオーミック接点と前記第2のオーミック接点とが、横方向に離隔されて、前記第2の活性層に電気的に接続する、

前記第1および第2のオーミック接点を形成することと、

前記第1のオーミック接点と前記第2のオーミック接点との間の横方向位置において前記第3のゲート誘電体層に接触するゲートを形成することと、

を含む、ヘテロ構造半導体デバイスを製造する方法。

## [付記項 1 7]

前記第1のオーミック接点と前記第2のオーミック接点とを形成する前に、前記第3のゲート誘電体層の上方にパッシベーション層を堆積および形成することをさらに含む、

付記項1に記載の方法。

## [付記項 1 8]

前記第1のオーミック接点と前記第2のオーミック接点とをアニーリングすることをさらに含む、

付記項1に記載の方法。

## [付記項 1 9]

前記ヘテロ構造半導体デバイスの正常動作中の温度にわたってゲート・ソース漏れ電流が実質的に一定に留まるように、前記第1の厚さ、前記第2の厚さ、および前記第3の厚さが選択される、

付記項1に記載の方法。

## [付記項 2 0]

前記第1のゲート誘電体層と前記第2のゲート誘電体層とが、窒化ケイ素を含む、

10

20

30

40

50

付記項 1 6 に記載の方法。

[付記項 2 1]

前記第 2 のゲート誘電体層が、酸化アルミニウムを含む、

付記項 2 0 に記載の方法。

[付記項 2 2]

前記第 1 のゲート誘電体層と前記第 2 のゲート誘電体層とが、前記第 1 の活性層および前記第 2 の活性層とインサイチュで形成される、

付記項 1 6 に記載の方法。

[付記項 2 3]

前記第 1 のゲート誘電体層が、前記第 1 の活性層および前記第 2 の活性層とインサイチュで形成され、 10

前記第 2 のゲート誘電体層が、前記第 1 の活性層および前記第 2 の活性層とイクサイチュで形成される、

付記項 1 6 に記載の方法。

[付記項 2 4]

前記第 1 の厚さが、約 1 ~ 5 ナノメートルの範囲にある、

付記項 1 6 に記載の方法。

[付記項 2 5]

前記第 2 の厚さが、約 3 0 ~ 4 0 ナノメートルの範囲内にある、

付記項 2 4 に記載の方法。

20

[付記項 2 6]

前記第 3 の厚さが、1 0 ~ 2 0 ナノメートルの範囲内にある、

付記項 2 5 に記載の方法。

20

**【図面】**

**【図 1】**

**【図 2】**

200

30

40

40

50

【図 3】

10

20

30

40

50

## フロントページの続き

## (51)国際特許分類

F I

H 01 L 21/316 (2006.01)

H 01 L 21/318 (2006.01)

## (56)参考文献

特開2009-302435 (JP, A)

特開2013-118377 (JP, A)

米国特許出願公開第2014/0077266 (US, A1)

## (58)調査した分野 (Int.Cl., DB名)

H 01 L 29/778

H 01 L 29/812

H 01 L 21/338

H 01 L 21/336

H 01 L 21/316

H 01 L 21/318