(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4515043号

(P4515043)

(45) 発行日 平成22年7月28日(2010.7.28)

(24) 登録日 平成22年5月21日(2010.5.21)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 21/336 | (2006.01) | HO1L 29/78 | 616A |

| HO1L 29/786 | (2006.01) | HO1L 29/78 | 617K |

| HO1L 21/28  | (2006.01) | HO1L 29/78 | 617L |

| HO1L 29/423 | (2006.01) | HO1L 21/28 | E    |

| HO1L 29/49  | (2006.01) | HO1L 29/78 | 627C |

請求項の数 10 (全 28 頁) 最終頁に続く

(21) 出願番号

特願2003-135892 (P2003-135892)

(22) 出願日

平成15年5月14日 (2003.5.14)

(65) 公開番号

特開2004-47972 (P2004-47972A)

(43) 公開日

平成16年2月12日 (2004.2.12)

審査請求日

平成18年3月29日 (2006.3.29)

(31) 優先権主張番号

特願2002-143892 (P2002-143892)

(32) 優先日

平成14年5月17日 (2002.5.17)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 石川 明

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 川村 裕二

(56) 参考文献 特開平07-307477 (JP, A)

特開2001-345453 (JP, A)

)

特開平05-235028 (JP, A)

特開2001-308325 (JP, A)

)

最終頁に続く

(54) 【発明の名称】 半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体層上にゲート絶縁膜を介して導電膜を形成し、

前記導電膜上にハードマスク層を形成し、

前記ハードマスク層上にレジストマスクを形成し、

前記レジストマスクを用いて前記ハードマスク層をエッチングし、端部が前記レジストマスクの内側にあるハードマスクを形成し、

前記レジストマスクを用いて前記導電膜をエッチングして、第1の形状の導電層を形成し、

前記レジストマスクを除去し、

前記ハードマスクを用いて前記第1の形状の導電層の露出している部分を一部エッチングして、前記ハードマスクに覆われている部分よりも露出している部分の方が厚さが薄い第2の形状の導電層を形成し、

前記第2の形状の導電層をマスクとして前記半導体層に不純物を添加することにより、チャネル形成領域と、前記チャネル形成領域を挟んでいる第1の不純物領域と、前記第1の不純物領域と前記チャネル形成領域の間に設けられた、前記第1の不純物領域よりも不純物濃度が低い第2の不純物領域とを形成することを特徴とする半導体装置の作製方法。

## 【請求項 2】

半導体層上にゲート絶縁膜を介して第1の導電膜を形成し、

前記第1の導電膜上に第2の導電膜を形成し、

10

20

前記第2の導電膜上にハードマスク層を形成し、

前記ハードマスク層上にレジストマスクを形成し、

前記レジストマスクを用いて前記ハードマスク層をエッティングして、端部が前記レジストマスクの内側にあるハードマスクを形成し、

前記レジストマスクを用いて前記第1の導電膜及び前記第2の導電膜をエッティングして、

第1の形状の導電層を形成し、

前記レジストマスクを除去し、

前記ハードマスクを用いて前記第2の導電膜を選択的にエッティングして、前記第1の導電膜の端部が前記第2の導電膜の端部より外側に位置する第2の形状の導電層を形成し、

前記ハードマスクを除去し、

10

前記第2の形状の導電層をマスクとして前記半導体層に不純物を添加することにより、

チャネル形成領域と、前記チャネル形成領域を挟んでいる第1の不純物領域と、前記第1の不純物領域と前記チャネル形成領域の間に設けられた、前記第1の不純物領域よりも不純物濃度が低い第2の不純物領域とを形成することを特徴とする半導体装置の作製方法。

**【請求項3】**

請求項2において、前記第1の導電膜と前記第2の導電膜とは、互いに異なる材質であることを特徴とする半導体装置の作製方法。

**【請求項4】**

請求項2において、前記第1の導電膜として、高融点金属を用いることを特徴とする半導体装置の作製方法。

20

**【請求項5】**

請求項2において、前記第2の導電膜として、高融点金属を用いることを特徴とする半導体装置の作製方法。

**【請求項6】**

請求項1乃至5のいずれか一において、前記第2の不純物領域の長さは、0.25~0.5μmであることを特徴とする半導体装置の作製方法。

**【請求項7】**

基板上に下地膜を形成し、

前記下地膜上に第1及び第2の半導体層を形成し、

前記第1及び第2の半導体層上にゲート絶縁膜を介して第1の導電膜を形成し、

前記第1の導電膜上に第2の導電膜を形成し、

前記第2の導電膜上にハードマスク層を形成し、

前記ハードマスク層上に第1及び第2のレジストマスクを形成し、

前記第1及び第2のレジストマスクを用いて前記ハードマスク層をそれぞれ等方性エッティングして、端部が前記第1及び第2のレジストマスクの内側にある第1及び第2のハードマスクを形成し、

30

前記第1及び第2のレジストマスクを用いて前記第1の導電膜及び前記第2の導電膜をそれぞれ異方性エッティングして、第1の形状を有する第1のゲート電極及び第2の形状を有する第2のゲート電極を形成し、

前記第1及び第2のレジストマスクを除去し、

前記第1及び第2のハードマスクを用いて前記第1及び第2のゲート電極を形成する前記第2の導電膜をそれぞれエッティングして、前記第1の導電膜の端部が前記第2の導電膜の端部より外側に位置する第3の形状を有する第1のゲート電極及び第4の形状を有する第2のゲート電極を形成し、

40

前記第1及び第2のハードマスクを除去し、

前記第1及び第2のゲート電極をマスクとして前記第1及び第2の半導体層に第1の不純物をそれぞれ添加することにより、前記第1の導電膜と重なる第1の低濃度不純物領域を形成するとともに、前記第1の低濃度不純物領域の外側に第1の高濃度不純物領域を形成し、

前記第1の半導体層上を覆うように第3のレジストマスクを形成し、

50

前記第2のゲート電極及び前記第3のレジストマスクをマスクとして前記第2の半導体層に第2の不純物を添加することにより、前記第1の導電膜と重なる第2の低濃度不純物領域を形成するとともに、前記第2の低濃度不純物領域の外側に第2の高濃度不純物領域を形成することを特徴とする半導体装置の作製方法。

**【請求項8】**

請求項7において、前記第1の不純物はn型を付与する不純物元素であり、前記第2の不純物はp型を付与する不純物元素であることを特徴とする半導体装置の作製方法。

**【請求項9】**

請求項7において、前記第1の不純物はp型を付与する不純物元素であり、前記第2の不純物はn型を付与する不純物元素であることを特徴とする半導体装置の作製方法。 10

**【請求項10】**

請求項1乃至9のいずれか一において、前記ハードマスク層の材料として、Al、ITO、またはアモルファスシリコンを用いることを特徴とする半導体装置の作製方法。

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

本発明は、薄膜トランジスタ（以下、TFTと略記）で構成された回路を有する半導体装置の作製方法に係り、特に露光工程におけるマスク形成の方法と、該マスクを用いたエッチング方法に関する。

**【0002】**

**【従来の技術】**

近年、TFTを利用したアクティブマトリクス型の液晶ディスプレイが注目されている。アクティブマトリクス型の液晶ディスプレイは、各画素にスイッチング素子としてTFTが設けられている。

**【0003】**

一般的にTFTは、非晶質シリコン又は多結晶シリコンでチャネル形成領域が形成されている。特に600以下の温度（低温プロセスと呼ばれる）で作製される多結晶シリコンを用いたTFT（以下、多結晶シリコンTFTと呼ぶ）は、ガラス基板上に形成可能であるため、半導体装置の低価格化、大面積化が可能になる。また、多結晶シリコンは移動度が大きいため、画素部とドライバーをガラス基板上に一体形成した液晶ディスプレイの実現が可能になる。 30

**【0004】**

しかし多結晶シリコンTFTは連続駆動させると、移動度が変化したり、オン電流（TFTがオン状態の場合に流れる電流）が低下したり、また、オフ電流（TFTがオフ状態の場合に流れる電流）が増加したりすることがある。これは、ドレイン近傍の高電界により発生するホットキャリアに起因する劣化が原因ではないかと考えられる。

**【0005】**

ドレイン近傍の高電界を緩和し、ホットキャリアを抑えるには、ゲート線幅の設計ルール1.5μm以下のMOSトランジスタの場合、LDD（Lightly Doped Drainの略）構造を用いるのが有用である。 40

**【0006】**

例えば、NMOSトランジスタの場合、ゲート側壁のサイドウォールを利用してドレイン端部に低濃度n型領域（n<sup>-</sup>領域）を設けることでLDD構造を形成することができる。ドレイン接合の不純物濃度に傾斜を持たせるLDD構造により、ドレイン近傍の電界集中を緩和することができる。

**【0007】**

しかし、LDD構造はシングルドレイン構造に比べドレイン耐圧を向上させることができるが、n<sup>-</sup>領域の抵抗が大きい為にドレイン電流が減少するという難点がある。また、サイドウォールの真下に高電界領域が存在し、そこで衝突電離が最大になり、ホットエレクトロンがサイドウォールに注入される為、n<sup>-</sup>領域が空乏化して更に抵抗が増加し、TFT 50

Tが劣化されてしまう。

**【0008】**

特にチャネル長が縮小されるに従い、上記の問題が顕在化してくる。設計ルール0.5μm以下のMOSトランジスタで、この問題を克服するには、ゲート電極の端部にオーバーラップしてn<sup>-</sup>領域を形成するGate Overlap LDD構造が有用である。

**【0009】**

そして、MOSトランジスタだけではなく、多結晶シリコンTFTにおいても、ドレイン近傍の高電界を緩和する目的で、Gate Overlap LDD構造の採用が検討されている。Gate Overlap LDD構造の多結晶シリコンTFTは、多結晶シリコン層に、チャネル形成領域と、高濃度領域（n<sup>+</sup>領域）であるソース及びドレイン領域と、チャネル形成領域とソース及びドレイン領域の間に設けられた、ゲート電極とオーバーラップする低濃度領域（n<sup>-</sup>領域）とが形成される。10

**【0010】**

これらの構造を作製するための方法としては、特許文献1や特許文献2などの報告がある。

**【0011】**

**【特許文献1】**

特開2000-349297号公報

**【特許文献2】**

特開平07-202210号公報20

**【0012】**

**【発明が解決しようとする課題】**

Gate Overlap LDD構造を有するTFTの作製工程において、ゲート電極とオーバーラップする低濃度領域（n<sup>-</sup>領域）を形成するには、不純物元素の添加工程をゲート電極形成前に行うか、ゲート電極を貫通するように不純物元素を添加する必要がある。

**【0013】**

前者の方法の場合、不純物元素添加用のマスクとゲート電極形成用のマスクとを、個別の露光工程で用いる必要がある。このため、ゲート電極とn<sup>-</sup>領域を自己整合的に形成できず、マスク数を抑えることができない。

**【0014】**

一方、後者の方法の場合、チャネル領域には不純物が添加されないようにした上で、n<sup>-</sup>領域のみに不純物元素を添加する必要がある。したがって、ゲート電極そのものをマスクとしてチャネル領域への不純物添加を防ごうとする場合、チャネル領域上のみゲート電極を厚くするなど、ゲート電極の形状に工夫をこらす必要がある。30

**【0015】**

しかしながら、ゲート電極形状の工夫によりチャネル領域への不純物添加を防ぐ場合、一般的には露光工程が複数回必要となる。そのため、各露光工程におけるマスクずれにより、ゲート電極の形状を精密に制御するのが難しく、自己整合的にn<sup>-</sup>領域を形成できない。また、使用するレチクル数が増加し、製造工程が複雑になる。

**【0016】**

また、通常はレジストマスクの寸法が大きくなるほど、焦点深度やレジスト膜厚均一性などのパターニングに関する条件の制約が緩やかなので、パターニング工程のプロセスマージンは大きくなる。しかし従来の方法では、レジストマスクの寸法形状がパターンの設計寸法と同程度なので、微細化を進めるほどパターニング工程のプロセスマージンが減少し、TFTを作製することが困難となる。40

**【0017】**

例えば、特許文献1では、2層構造のゲート電極を用い、ゲート電極のエッチング工程を2回設け、ゲート電極の第1層目が、第2層目よりもチャネル長方向に長い、所謂ハットシェープゲートを形成する方法について開示されている。また、特許文献2には、ハットシェープゲートをセルフアラインで形成する方法の一例が記載されている。チタンあるいは

は窒化チタン膜からなるゲート電極の第1層目と、アルミニウムあるいはアルミニウム合金膜からなるゲート電極の第2層目とを、D Cスパッタ法により形成する。次いで、エッチング処理によりゲート電極の第1層目及び第2層目を共にエッチングした後、第2層目のゲート電極のみをサイドエッチングにより後退させて加工する方法が開示されている。

#### 【0018】

また、特許文献2に開示の技術では、耐熱性のよい多結晶シリコンなどのゲート電極と異なり、アルミニウムをゲート電極の第2層目に用いているため、高温での熱処理ではアルミニスパイクやマイグレーションによる不良が発生するので、プロセスの温度管理が非常に難しいという課題がある。従って、不純物の活性化をアルミニウムが変質しない温度において行う必要がある。しかし、イオン注入若しくはイオンドーピング後の活性化処理は、

550～800 の間で行われるため、それより低い温度で不純物の活性化処理を完全に行なうことには困難である。その他にも、アルミニウムは低温で再結晶化して表面が凹凸化してしまう、また軟らかい金属であるため機械的損傷を受けやすいといった問題がある。

10

#### 【0019】

以上の理由で、チャネル長1～2 μm程度、LDD領域のゲート電極とのオーバーラップ幅を0.5 μm以下とする設計ルールで、Gate Overlap LDD構造のTFTを作製することは難しかった。すなわち、従来のGate Overlap LDD構造の作製方法は、

1) 複数回のフォトリソグラフ工程を必要とする

2) 微細化を進めるほど、パターニング工程のプロセスマージンが減少し、作製が難しくなる

20

3) 特許文献2に記載の発明のように、1回のパターニングによりハットシェープゲート電極を作製する方法では、ゲート電極の第2層目がアルミニウム膜又はアルミニウム合金膜に限定され、好ましくない

等の各種問題を有している。

#### 【0020】

本発明は、上記問題を解決することを課題とする。具体的には、Gate Overlap LDD構造のTFTを作製工程において、ゲート電極の形成の際のフォトリソグラフ工程の数を抑え、デザインルールが微細化しても精度良く当該TFTを作製することができる技術の提供を課題とする。

#### 【0021】

##### 【課題を解決するための手段】

微細化が進んだプロセスにおいて、セルフアラインでGate Overlap LDD構造を形成することに伴う、複数回のフォトリソグラフ工程の必要性、パターニングのマージンの縮小、及びゲート材料の選択肢減少等の課題を解決する為の手段について記載する。

30

#### 【0022】

なお、本明細書においてはGate Overlap LDD構造等の製造方法を明確に説明するため、以下のような定義を設ける。LDD領域のうちゲート電極と重ならない領域を「LoFF領域」、LDD領域のうちゲート電極と重なる領域を「LoV領域」と定義する。LoFF領域の長さは「LoFF」、LoV領域の長さは「LoV」、チャネル領域の長さは「Li」と定義する。また、本明細書においては、特に明記しない限り、LoVの等しいLoV領域がチャネル領域の両側に存在するものとし、チャネル領域とLoV領域を合わせた領域の長さ、すなわち、活性層上におけるゲート電極全体の幅「L'」を「L'=Li + LoV × 2」で定義する。

40

#### 【0023】

また、LSIやTFTを製造する場合のエッチング工程やドーピング工程においては、通常、エッチング処理やドーピング処理をしない部分に保護膜を形成する前処理を行う。前記保護膜の形成方法は、パターニング、すなわち、フォトレジストを塗布した基板上にフォトマスクのパターンを投影して形成する方法が一般的である。したがって、以下の説明において、当該保護膜を「マスク」と定義し、フォトマスクを「レチクル」と定義する。なお、フォトレジスト以外の材料を用いてマスクを形成しても良い。また、フォトレジストを材料として形成したマスクを「レジストマスク」、フォトレジスト以外の材料を用い

50

て形成したマスクを「ハードマスク」と定義する。

【0024】

本発明は、上記課題を解決する手段として、2層構造のマスクパターンを形成し、これを利用することによりハットシェープゲート自体をセルフアラインで作製する。

【0025】

本発明の主要な構成は、マスクパターン形成工程とゲート形成工程であり、以下にマスク形成工程とゲート形成工程について詳細に説明する。ここで、各マスクを区別するために、以下のような定義を設ける。Gate Overlap LDD構造を形成する場合に用いる、チャネル形成領域とLov領域を合わせた領域を覆うマスクを「Gate Overlap LDDゲートマスク」と定義する。Lov領域上のゲート電極を薄膜化する際にチャネル領域を覆うマスクを「チャネルマスク」と定義する。チャネルマスクは、Loff領域を有するトランジスタのゲートを形成する場合にも用いる。また、Gate Overlap LDD構造を形成する場合、Gate Overlap LDDゲートマスクに覆われていない部分のゲート材料を完全に除去するエッチングと、チャネルマスクを用いてLov領域上のゲート電極を薄膜化するエッチングが必要となる。前者を「Gate Overlap LDDゲートエッティング」、後者を「Lov領域エッティング」と定義する。

10

【0026】

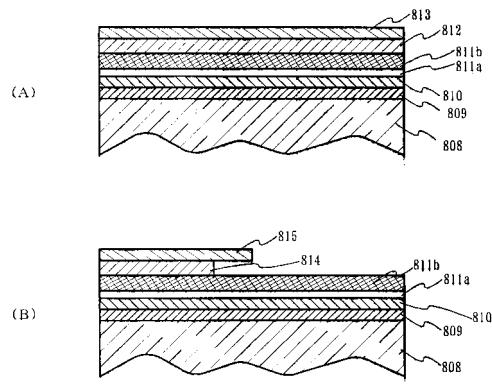

図8(A)にマスク形成工程を示す。基板808上に活性層809を形成し、ゲート絶縁膜810を介して第1層ゲート電極膜811a及び第2層目ゲート電極膜811bを形成する。次いで、マスク形成の準備としてマスクの材料となる層を形成する。通常のマスク形成工程は、パターニングでレジストマスクを形成するのみなのでレジストを塗布するだけであるが、図8においては、第2層目ゲート電極膜811bに接してハードマスク層812を形成し、次いでハードマスク層に接してレジスト813を塗布している。

20

【0027】

図8(B)は、レジストマスク815及びハードマスク814の形成プロセスを示しており、通常のパターニングによりレジストマスク815が形成された後、ウェットエッティングに代表される等方性エッティングによりハードマスク(A1)814が形成される様子を示している。図8(B)において、上層のレジストマスク815は、通常のパターニングによりGate Overlap LDDゲートマスクとして形成される。下層のハードマスク814は、上層のレジストマスクを利用したウェットエッティングに代表される等方性エッティングによりチャネルマスクとして形成される。また、等方性エッティングは、レジストマスクに対するハードマスクの後退量(サイドエッティング量)、すなわちLov、ハードマスク層の厚さで制御できる。Lovを大とする場合は、ハードマスク層を厚く形成し、Lovを小とする場合は、ハードマスク層を薄く形成すればよい。あるいは、ハードマスク層の厚さを一定とし、オーバーエッティング時間を制御する事により後退量を制御する事もできる。なお、ウェットエッティングで形成する場合は、ハードマスク形成時はコロージョンや膜残り欠陥などの問題を考える必要はない。

30

【0028】

このハードマスクの材料は、ゲート電極と選択比の高い等方性エッティングが可能であること、Lov領域エッティングの際にマスクとして使用できる程度に選択比が高いことの二つの条件を満たす材質を自由に選択できる。ハードマスクを用いたエッティング時にサイドエッティングが必須ならば、ハードマスク下に必ず空隙が形成され、後工程において不都合の原因となりうるため、エッティング後にハードマスクを除去することが必須となる。しかしながら、本発明においては、ゲート形成工程についての説明の際に後述するように、ハードマスクを用いたエッティング時のサイドエッティングが必須ではない。したがって、本発明においては、エッティング後にハードマスクを除去する工程は、必ずしも必須のものではない。また、エッティング後にハードマスクを除去するプロセスにおいて、ハードマスク除去時にゲート絶縁膜が剥き出しどなっている場合は、ハードマスク材質に関し「ゲート絶縁膜と選択比の高いエッティングが可能であること」という条件が加わる。本発明においては、ハードマスクを除去せずに残すプロセスが可能なので、ハードマスク材料の選択肢が広

40

50

がる。ハードマスクを除去せずに残すプロセスとは、例えば、ハードマスク材料として酸化シリコン膜を選択し、ハードマスクを層間絶縁膜の一部として残すプロセスが挙げられる。また、ハードマスク材料として高融点金属を選択した場合は、ハードマスクをゲート電極の一部として残す事も可能である。

#### 【0029】

このようにして、1回のフォトリソグラフ工程のみで第1層目のマスクパターン（ハードマスクのパターン）を、第2層目のマスクパターン（レジストマスクのパターン）に対し、セルフアラインで、かつ、相似形で寸法の異なるマスクパターンとして形成できる。活性層上における線幅を、第1層目のマスクパターンではLi、第2層目のマスクパターンではL'となるように設定する事は容易である。従来の方法ではレジストマスクでLiのパターンも作製しなければいけなかったが、本発明における方法を使用すれば、レジストマスクの活性層上の線幅はLi + Lov × 2となり、従来よりも大きく設定できるので、より微細化に対応することが可能となる。10

#### 【0030】

また、レジストマスクである第2層目のマスクパターンを剥離しても、ハードマスクである第1層目のマスクパターンは残る。したがって、第2層目のマスクパターンを用いた異方性エッチング、第1層目のマスクパターンを用いた異方性エッチングを順に行なうことができる。第1層目のマスクパターンと第2層目のマスクパターンは、相似形で、寸法の異なるマスクパターンとして形成されているから、これらのマスクパターンを用いたエッチングを順に行なう事により、ハットシェープゲートをセルフアラインで形成できる。このようにして、作製工程において使用するレチクル数を減少し、TFTの微細化に伴う作製方法の複雑化の問題を解決できる。20

#### 【0031】

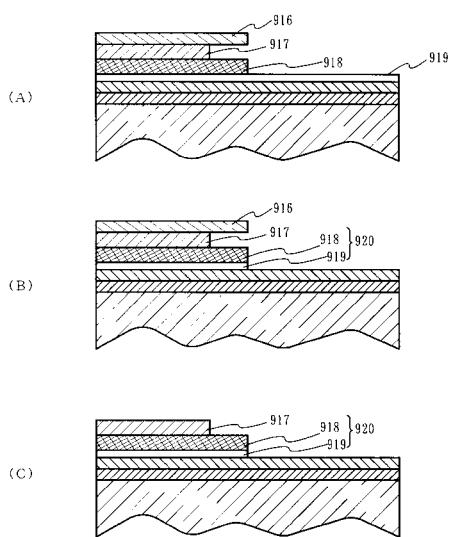

本発明の主要部の一つであるゲート形成工程について説明する。レジストマスク916とハードマスク917とからなる積層構造を有するマスクを用いたエッチングは、2段階に分けて行う（図9（A）及び図9（B）参照）。図9（A）は、第2層目ゲート電極膜918の異方性ドライエッチング処理の様子を示している。図9（B）は第1層ゲート電極膜919の異方性ドライエッチング処理の様子を示している。1段階目のエッチングでは、Gate Overlap LDDゲートマスクに相当するレジストマスク916を用いて、Gate Overlap LDDゲートエッチングを行う。Gate Overlap LDDゲートエッチングは、完全異方性エッチングである事が望ましい。すなわち、Gate Overlap LDDゲートマスクに覆われていない部分の第1層ゲート電極膜918と第2層目ゲート電極膜919が完全に除去される。その結果、第1の形状の導電層920を形成する。その後、レジストマスク916を剥離し、ハードマスク917を露出する（図9（C））。

#### 【0032】

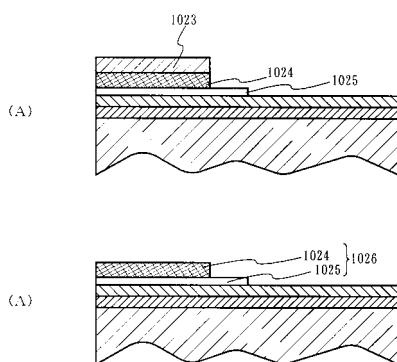

2段階目のエッチングは、チャネルマスクに相当するハードマスクを用いて、Lov領域上のゲート電極を薄膜化するエッチング（Lov領域エッチング）を行う。図10（A）は、ハードマスク1023をマスクとして第2層目ゲート電極膜1024のみを異方性ドライエッチング処理する様子を示している。その後、ウェットエッチングに代表される等方性エッチングによりハードマスク1023を除去する（図10（B）参照）。以上のように、ハットシェープゲートである第2の形状の導電層1026がセルフアラインで形成される。その後、ソース及びドレインへ不純物が高濃度で添加され、Lov領域に不純物が低濃度で添加される。40

#### 【0033】

このようにして、本発明の主要部として挙げたハードマスク上にレジストマスクを積層した構造のマスクを利用し、ハードマスクではLi、レジストマスクではL'となるように設定し、レジストマスクを用いた異方性エッチング、ハードマスクを用いた異方性エッチングを順に行なうことにより、ハットシェープゲートをセルフアラインで形成できる。従って、作製工程において使用するレチクル数を減少し、TFTの微細化に伴う作製方法の複雑化の問題を解決できる。50

## 【0034】

以上の説明では、ゲート電極となる導電膜を、異なる材質の2層構造とした。これにより、第1層目（下側の層）の導電膜を、第2層目（上側の層）の導電膜をエッティングする際のエッティングストッパーとすることが可能になる。この様にして、ゲート電極となる導電膜をエッティングする条件の選択の幅を拡大できる。その効果は、特にL<sub>o</sub>V領域エッティングの際に大であり、L<sub>o</sub>V領域上のゲート膜厚を精密制御する事を可能ならしめ、その結果、後工程においてL<sub>o</sub>V領域に添加される不純物の濃度の制御を容易ならしめる。

## 【0035】

また、本発明を適用すれば、ハットシェーブゲートを構成する第1の導電膜及び第2の導電膜の組み合わせを多数選択することができ、第2の導電膜はアルミニウム膜に限定されない。上記第1及び第2の導電膜はTa、W、Ti、Mo、Al、Cuから選ばれた元素、又は前記元素を主成分とする合金材料若しくは化合物材料で形成しても良い。また、リン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜を用いても良い。また、第1の導電膜をタンタル（Ta）膜で形成し、第2の導電膜をW膜とする組み合わせ、第1の導電膜を窒化タンタル（Ta<sub>N</sub>）膜で形成し、第2の導電膜をCu膜とする組み合わせとしても良い。ゲート材料として高融点金属を選ぶ事ができるので、不純物の活性化を、通常の熱処理により（550～800）行うことができる。

10

## 【0036】

しかしながら、ゲート電極膜を2層で構成する事は必須条件ではない。L<sub>o</sub>V領域エッティングの精密制御を行えば、ゲート電極膜を単層膜で構成する事も可能である。ゲート電極膜を単層膜で構成する場合であっても、本発明の適用によりハットシェーブゲート形成が可能となる。

20

## 【0037】

また、典型的な値は、Li=1.0～2.0μm、L<sub>o</sub>V=0.25～0.5μmである。但し、必ずしもこの範囲に限定されるわけではない。

## 【0038】

本発明の作製方法によれば、1回のフォトリソグラフ工程のみで第1層目のマスク（ハードマスク）を、第2層目のマスク（レジストマスク）に対して、セルファアラインで、かつ、相似形だが寸法の異なるマスクパターンとして形成できる。活性層上における線幅を、第1層目のマスクパターンではLi、第2層目のマスクパターンではLi+L<sub>off</sub>×2となるよう設定し、第2層目のマスクパターンを用いた異方性エッティング、第1層目のマスクパターンを用いた異方性エッティングを順に行うことにより、L<sub>off</sub>領域のみを持つTFTをセルファアラインで形成できる。従って、作製工程において使用するレチクル数を減少し、TFTの微細化に伴う作製方法の複雑化の問題を解決できる。また、ゲート電極の材料となる単層または積層された導電膜を、アルミニウムに限定されず多数選択することができる所以、不純物の活性化を、通常の熱処理により（550～800）行うことができる。

30

## 【0039】

また、典型的な値は、Li=1.0～2.0μm、L<sub>off</sub>=0.25～0.5μmである。但し、必ずしもこの範囲に限定されるわけではない。これにより、微細化が進んだL<sub>off</sub>領域のみを持つTFTの製造プロセスであってもレジストマスクの活性層上における線幅は微細化されず、パターニングマージンを拡大できる。

40

## 【0040】

また、ハードマスクはレジストマスクを利用したウェットエッティング処理により形成するとしても良い。これにより、微細化が進んだL<sub>off</sub>領域のみを持つTFTの製造プロセスにおいて膜厚のバラツキ、エッティングのムラの発生、コロージョン、及び膜残り欠陥等の問題を防止できる。

## 【0041】

なお、pチャネル型TFTをGate Overlap LDD構造としても良いし、nチャネル型TFTをGate Overlap LDD構造としても良い。またその両方をGate Overlap LDD構造としても良い。

50

## 【0042】

## 【発明の実施の形態】

## 〔実施の形態1〕

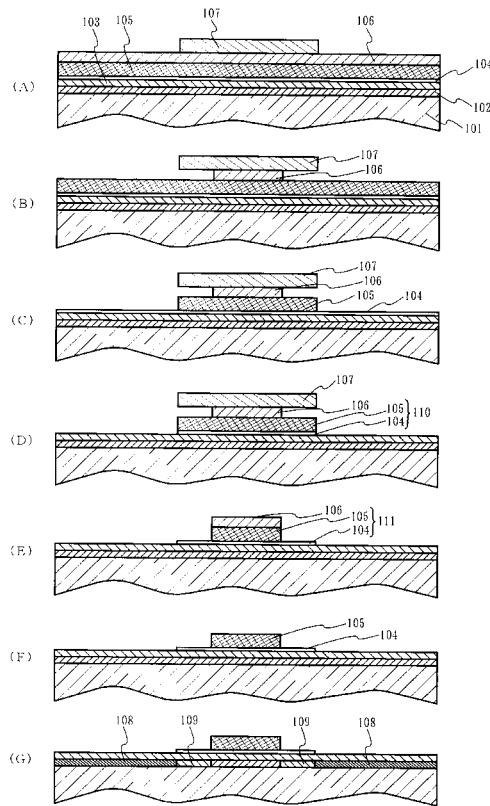

最初に、Gate Overlap LDD構造TFTの作製方法に関する図1の一実施の形態について説明する。基板101上にシリコン層102を形成し、その上にゲート絶縁膜103を堆積し、次に第1の導電膜及び第2の導電膜として第1層ゲート電極膜104及び第2層目ゲート電極膜105を積層する。その後、ハードマスク層106を形成する。次に、パターニングによりレジストマスク107を形成する(図1(A)参照)。そして、前記レジストマスク107を用いたウェットエッティングにより等方性エッティング処理を行い、ハードマスク106を形成する(図1(B)参照)。

10

## 【0043】

次に、前記レジストマスク107、すなわち、Gate Overlap LDDゲートマスクを用いて第2層目ゲート電極膜105のみを異方性ドライエッティングする(図1(C)参照)。

## 【0044】

次に、前記レジストマスク107及び前記第2層目ゲート電極膜105をマスクに、第1層ゲート電極膜104を異なる条件の異方性ドライエッティングし、第1の形状の導電層110を形成する(図1(D)参照)。そして、レジストマスク107を剥離し、ハードマスク106を露出させる。

## 【0045】

その後、ハードマスク106を用い、前記第1層ゲート電極膜104をエッティングストップとして前記第2層目ゲート電極膜105を異方性ドライエッティング処理して、Loff領域に前記第1層ゲート電極膜104のみを残す。こうして、第2の形状の導電層111を形成する(図1(E)参照)。

20

## 【0046】

次に、ウェットエッティングによりハードマスク106を除去する(図1(F)参照)。このようにして、ハットシェープゲートをセルファーラインで形成する。その後、高濃度不純物の添加を行い、第1の形状の導電層の外側にソース及びドレイン領域となる第1の不純物領域108を形成する。この後、低濃度不純物の添加を行うことにより、第2の形状の導電層と重なる第2の不純物領域109を形成する。第2の不純物領域109はLoff領域に相当する(図1(G)参照)。

30

## 【0047】

その後、層間絶縁膜形成工程、活性化工程、コンタクトホール形成工程、配線形成工程を経てTFTを完成させる。これらの工程は図示しない。

## 【0048】

なお、ソース及びドレイン領域となる第1の不純物領域108への不純物添加は、第1の形状の導電層110を形成した後(図1(D)または図1(D)よりレジストマスクを除去した状態)に行う事もできる。この場合は、第1層ゲート電極膜104及び第2層目ゲート電極膜105がLoff領域のマスクとなるので、第1の不純物領域108への不純物添加条件の制限が緩和される。

## 【0049】

40

## 〔実施の形態2〕

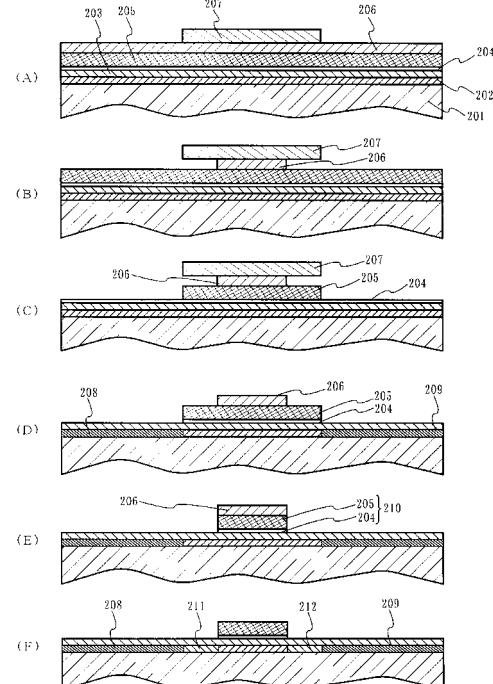

本実施の形態に記載の発明はLoff領域を有するTFTの形成において、ハードマスクとレジストマスクの積層構造マスクを、ウェットエッティングによりセルファーラインで形成することによってハードマスクの線幅をレジストマスクの線幅より小さく形成することができ、微細化が進んだプロセスにおけるパターニングマージンを拡大できることを特徴としている。本発明のLoff領域を有するTFTの作製方法に関する実施の形態について以下に記載する。

## 【0050】

実施の形態1において説明したセルファーラインでGate Overlap LDD構造を形成する方法に以下の3点の変更を加えることで、セルファーラインでLoff領域のみ持つTFT構造を

50

形成する方法に変更できる。

#### 【0051】

(変更1) Gate Overlap LDDゲートエッティングとLoff領域エッティングの間に、ソース及びドレインへの不純物添加工程を追加する。

(変更2) Loff領域エッティングの際に、ゲート上層(W)のみでなくゲート下層(TaN)まで異方性エッティングで除去するエッティング条件に変更する。

(変更3) Loff領域エッティングの後、もしくはハードマスク除去の後に、LDDへの不純物添加工程を追加する。

#### 【0052】

ここで、Loff領域を有するTFTの作製方法に関する図2の一実施の形態について記載する。基本的にレジストマスクパターン工程から第2層目ゲート電極膜のみエッティング工程までの図2(A)から図2(D)までの作製方法は図1の発明と同一であるので、此处では省略してレジストマスク剥離工程から記載する。そして、レジストマスク207を剥離し、ハードマスク206を露出させる。その後、不純物を添加する。本実施の形態においては、ソース及びドレイン領域に第1層ゲート電極膜204を残しているため、不純物を、第1層ゲート電極膜204とゲート絶縁膜203とを介して添加する。ゲートLoffマスクを用いたエッティングで第1層ゲート電極膜204まで除去した場合は、不純物をゲート絶縁膜203のみを貫通させて添加する。しかし、Loff領域は前記第1層ゲート電極膜204及び前記第2層目ゲート電極膜からなる第2の導電膜領域205によってマスクされているため、不純物は一切添加されない。これにより、ソース及びドレイン領域のみが高濃度不純物領域となり、第1の不純物領域208、209が形成される(図2(D)参照)。

10

#### 【0053】

その後、ハードマスク206を用い、前記第1層ゲート電極膜204をエッティングストップとして前記第2の導電膜領域205のみを異方性ドライエッティングし、さらに、前記第1層ゲート電極膜204のみを異方性ドライエッティングする。このようにしてLoff領域の前記第1層ゲート電極膜204及び前記第2の導電膜領域205を完全に除去する(図2(E)参照)。その結果、第1の形状の導電層210が形成される。

20

#### 【0054】

次に、ウェットエッティングによりハードマスク206を除去する(図2(F)参照)。その後、不純物をLoff領域及びソース及びドレイン領域に添加する。不純物はゲート絶縁膜を貫通させて添加する。このようにして、ソース及びドレイン領域が高濃度不純物領域である第1の不純物領域208、209となり、Loff領域が低濃度不純物領域である第2の不純物領域211、212となる(図2(F)参照)。その後、層間絶縁膜形成工程、活性化工程、コンタクトホール形成工程、配線形成工程を経てTFTを完成させる。このような工程を経てTFTを完成させる。これらの工程は図示しない。なお、ハードマスク除去はLoff領域の不純物添加の後でもよい。

30

#### 【0055】

##### 【実施例】

###### 【実施例1】

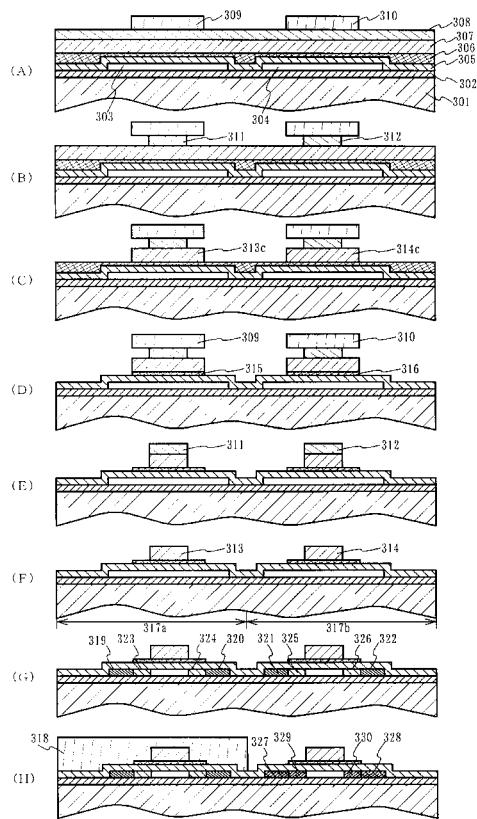

本発明の実施例である2つのGate Overlap LDD構造トランジスタを組み合わせた相補型の装置、いわゆるCMOS回路を用いた制御回路の作製方法について、図3を用いて説明する。

40

#### 【0056】

基板301は、ガラス基板、石英基板、セラミック基板等を用いることができる。また、シリコン基板、金属基板又はステンレス基板の表面に絶縁膜を形成したものを用いても良い。また、本実施例の処理温度に耐えうる耐熱性を有するプラスチック基板を用いても良い。

#### 【0057】

次いで、図3(A)に示す様に、基板301上に酸化シリコン膜、窒化シリコン膜又は酸

50

化窒化シリコン膜等の絶縁膜から成る下地膜302を形成する。本実施例では下地膜302として単層膜を用いるが、前記絶縁膜を2層以上積層させた構造を用いても良い。なお、前記下地膜302は、基板301からの不純物拡散を防止する為のものである(図3(A)参照)。

#### 【0058】

次いで、非晶質半導体膜を形成する。非晶質半導体膜は、公知の手段(スパッタ法、LPCVD法、又はプラズマCVD法等)により成膜を行う。この非晶質半導体膜の厚さは30~60nmの厚さで形成する。非晶質半導体膜の材料に限定はないが、好ましくはシリコン又はシリコンゲルマニウム(SiGe)合金等で形成すると良い(図3(A)参照)。なお、非晶質半導体膜に限定されず、多結晶半導体膜、及び微結晶半導体膜等を形成してもよい。10

#### 【0059】

その後に、非晶質半導体膜の脱水素化(500、1時間)を行い、次いでファーネスアニール炉による熱処理(550、4時間)を行う。必要であれば、この後にレーザーアニールを加えても良い。この様にして得られる結晶質半導体膜を図3(B)で示す様に、フォトリソグラフィ工程とエッチング工程により所望の形状にパターニングして結晶質半導体層303、304を形成する(図3(A)参照)。

#### 【0060】

次いで、半導体層303、304を覆うゲート絶縁膜305を形成する。ゲート絶縁膜305は、プラズマCVD法やスパッタ法で形成し、その厚さを40~150nmとしてシリコンを含む絶縁膜で形成する。ゲート絶縁膜は酸化窒化シリコン膜に限定されるものではなく、他のシリコンを含む絶縁膜を単層又は積層構造として用いても良い(図3(A)参照)。20

#### 【0061】

次いで、ゲート絶縁膜305上にゲート導電膜を形成する。本実施例では、膜厚20~100nmの第1の導電膜として第1層ゲート電極膜306(TaN)と、膜厚100~400nmの第2の導電膜として第2層目ゲート電極膜307(W)とを積層形成する。ゲート導電膜はTa、W、Ti、Mo、Al、Cuから選ばれた元素、又は前記元素を主成分とする合金材料若しくは化合物材料で形成しても良い。また、リン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜を用いても良い。また、第1層ゲート電極膜をタンタル(Ta)膜で形成し、第2層目ゲート電極膜をW膜とする組み合わせ、第1層ゲート電極膜を窒化タンタル(TaN)膜で形成し、第2層目ゲート電極膜をCu膜とする組み合わせとしても良い(図3(A)参照)。30

#### 【0062】

次いで、後述するゲート電極のエッチング工程においてエッチングマスクとなるハードマスク層308(Al)を形成する。本実施例ではハードマスクの材料をAlとしたが、ハードマスクの材料をAlのみに限定する必要はない。ハードマスクの材料は、「ゲート電極と選択比の高い等方性エッチングが可能であること」「Lox領域エッチングの際にマスクとして使用できる程度に選択比が高いこと」の2条件を満たす材質を自由に選択できる。例えば、ITO薄膜、アモルファスシリコン膜などを選択してもよい。ハードマスクの厚さについては後述する。40

#### 【0063】

次に、ハードマスク層308上にレジストマスク309、310を形成する。前記レジストマスクを用いたウェットエッチングによりハードマスク311、312を形成する(図3(B)参照)。エッチャントとして磷酸、酢酸、硝酸等の混酸などを使用する。また、塩酸系の水溶液を使用してもよい。なお、ドライエッチングでは条件によっては、レジストマスク層及びエッチング被膜の側壁にカーボン系の変質層が生成する可能性があり、この変質層と残留したCl<sub>2</sub>と空気中の水分とが反応することにより、コロージョンが生成し、表面状態は凹凸状態となることがあるため、注意が必要である。しかし本実施例では、ウェットエッチングであるためコロージョン等を考慮する必要はない。50

## 【0064】

後工程において、前記レジストマスク309、310はGate Overlap LDDゲートマスクとして使用され、前記レジストマスク309、310を用いて形成されたハードマスク311、312はチャネルマスクとして使用される。したがって、前記ハードマスクの縁は、前記レジストマスクの縁より、LoVだけ後退した位置に存在しなければならない。ハードマスクの厚さをLoV幅と同じに設定すれば、Gate Overlap LDDゲートエッチングが終了した時点で、前記ハードマスクの縁は、前記レジストマスクの縁より、LoVだけ後退した位置に存在することになる。また、ハードマスクの厚さをLoVより小さく設定した上でオーバーエッチングの時間を調節することによってもLoV幅の調節は可能である。

## 【0065】

次に、前記レジストマスク309、310、すなわち、Gate Overlap LDDゲートマスクを用いてGate Overlap LDDゲートエッチングを行い、第2層目ゲート電極膜307のみを異方性ドライエッチング（第1ステップのエッチング）する（図3（C）参照）。本実施例では、ゲート電極をタングステン（W）と窒化タンタル（TaN）の2層で構成しており、第1層ゲート電極膜（TaN）がW膜のエッチング時のエッチングストッパーとして機能するので、第2層目ゲート電極膜（W）と第1層ゲート電極膜（TaN）を異なる条件でエッチングする。

## 【0066】

本実施例では、エッチング用ガスにSF<sub>6</sub>とCl<sub>2</sub>とO<sub>2</sub>とを用い、各々のガス流量比を24/12/24（sccm）とし、2Paの圧力でコイル型の電極に700WのRF（13.56MHz）電力を投入してプラズマを生成してエッチングを行う。基板側（試料ステージ）には、10WのRF（13.56MHz）電力を投入し、第1のエッチング処理に比べ低い自己バイアス電圧を印加する。この条件のエッチングによりW膜を異方性エッチングして第1の形状の導電層313、314を形成する。この際、第2層目ゲート電極膜307（W膜）のみがエッチングされる為、第1層ゲート電極膜（TaN）306はエッチングされずに残る（図3（C）参照）。

## 【0067】

次に、第2のエッチング条件に変え、前記第2層目ゲート電極膜（W膜）313、314をマスクに、第1層ゲート電極膜306を異なる条件の異方性ドライエッチングする（図3（D）参照）。エッチング用ガスにCF<sub>4</sub>とCl<sub>2</sub>とを用い、各々のガス流量比を30/30（sccm）とし、1.5Paの圧力でコイル型の電極に500WのRF電力を投入してプラズマを生成してエッチングを行う。基板側（試料ステージ）にも10WのRF電力を投入し、実質的に負の自己バイアス電圧を印加する。その結果、前記第1層ゲート電極膜（TaN）315、316が形成される。

## 【0068】

なお、Gate Overlap LDDゲートエッチングは、完全異方性エッチングとなる条件で行う事が望ましい。完全等方性エッチングは、レジストマスクの下までゲート電極がエッチングされるので、望ましくない。完全異方性エッチングより多少等方性エッチングに寄った条件でGate Overlap LDDゲートエッチングを行う場合は、ゲート電極の仕上がり線幅がレジストマスクの線幅より目減りするが、公知の寸法補正技術により容易に制御できる。例えば、レチカル上のパターンまたはパターニング条件の修正により線幅目減り分だけレジストマスクの線幅を大きくし、併せて、ハードマスクの線幅が変わらないようにウェットエッチング時の後退量を補正すればよい。レジストマスクとの選択比が不足するため寸法補正が必要な場合なども同様に対処すればよい。

## 【0069】

そして、レジストマスク309、310を剥離し、ハードマスク311、312を露出させる。

## 【0070】

その後、ハードマスク311、312を用いたLoV領域エッチングを行う。前記第1層ゲート電極膜315、316をエッチングストッパーとして前記第2層目ゲート電極膜313

10

20

30

40

50

、314を異方性ドライエッチング処理して、Lov領域に前記第1層ゲート電極膜315、316のみを残す(図3(E)参照)。第2層目ゲート電極膜のみを異方性ドライエッチングによって除去する。また、寸法補正が必要な場合は、GATE OVERLAP LDDゲートエッチングの場合と同様に補正すればよい。

#### 【0071】

次に、ウェットエッチングによりハードマスク311、312を除去する(図3(F)参照)。このようにして、ハットシェーピングゲートをセルフアラインで形成する。なお、本実施例ではハードマスクを除去しているが、必ずしもハードマスクを除去する必要はない。例えば、ハードマスク材料として酸化シリコン膜を選択し、ハードマスクを層間絶縁膜の一部として残す事が可能である。別の例としては、ハードマスク材料としてMo等の高融点金属を選択し、ハードマスクをゲート電極の一部として残す事が可能である。ハードマスクを除去しない場合、Lov領域エッチングは完全異方性エッチングで行う事が望ましい。10

#### 【0072】

その後、ドーピング処理を行う。本実施例では、図3(G)の左側の半導体領域317a(第1の領域という)をnチャネル型TFT、右側の半導体領域317b(第2の領域という)をpチャネル型TFTとする場合について説明する。また、本実施例では、nチャネル型TFT、pチャネル型TFTの順にドーピング処理を行うが、この順番は逆でもかまわない。第1のドーピング処理を行い、半導体層にn型を付与する不純物元素を添加する。ドーピング処理はイオンドープ法、若しくはイオン注入法で行えば良い。例えば、イオンドープ法の条件はドーザ量を $1 \times 10^{13} \sim 5 \times 10^{15}$ atoms/cm<sup>2</sup>とし、加速電圧を60~100kVとして行う(5%PH<sub>3</sub> 40sccm 60kv 5μA 4.0E15)。n型を付与する不純物元素として15族に属する元素、典型的にはリン(P)又は砒素(As)を用いる。この場合、前記第1層ゲート電極膜315、316及び前記第2層目ゲート電極膜313、314がn型を付与する不純物元素に対するマスクとなり、エッチング処理により第1の不純物領域319~322が形成される。第1の不純物領域319~322には、 $1 \times 10^{20} \sim 1 \times 10^{21}$ atoms/cm<sup>3</sup>の濃度範囲でn型を付与する不純物元素を添加する。この領域は、n<sup>+</sup>領域とする(図3(G)参照)。20

#### 【0073】

この後、第2のドーピング処理を行う。この場合、第1のドーピング処理よりもドーザ量を下げる、高い加速電圧の条件としてn型を付与する不純物元素をドーピングする。例えば、加速電圧を70~120kV、本実施例では90kVの加速電圧とし、 $3.5 \times 10^{12}$ atoms/cm<sup>2</sup>のドーザ量で行い、第1のドーピング処理により形成した第1の不純物領域より内側の半導体層に新たな不純物領域を形成する。(5%PH<sub>3</sub> 30sccm 90kv 0.5μA 1.0E14)ドーピングは、前記第1層ゲート電極膜315、316及び前記第2層目ゲート電極膜313、314を不純物元素に対するマスクとして用い、第1層ゲート電極膜315、316の下部に於ける半導体層にも不純物元素が添加される様にドーピングする(図3(G)参照)。30

#### 【0074】

こうして、第1層ゲート電極膜315、316と重なる第2の不純物領域323~326と、第1の不純物領域319~322とを形成する。n型を付与する不純物元素は、第2の不純物領域で $1 \times 10^{17} \sim 1 \times 10^{19}$ atoms/cm<sup>3</sup>の濃度となる様にする。第2の不純物領域は、n<sup>-</sup>領域となる(図3(G)参照)。以上のようにして、Gate Overlap LDD構造を有するnチャネル型TFTを形成する。なお、第1のドーピング処理は、レジストマスク除去後、Lov領域エッチングの前に行っても良い。この場合、第1のドーピング処理の際にLov領域に不純物添加される心配がないので、第1のドーピング処理の条件を設定できる範囲を広げる事ができる。40

#### 【0075】

次に、左側の半導体領域317aを、フォトレジスト318で覆い、その状態で、右側半導体領域317bにp型の不純物をドーピングする。上記nチャネル型TFTを形成するための処理と同様の方法によりドーピング処理を行う。すなわち、第3のドーピング処理50

により高濃度の不純物を添加し、第3の不純物領域327、328を形成し、また、より低濃度の不純物が添加された第4の不純物領域329、330を形成する。

#### 【0076】

このようにして、第3の不純物領域はp+領域となり、第4の不純物領域はp-領域となる。本実施例では、不純物領域はジボラン( $B_2H_6$ )を用いたイオンドープ法で形成する(5% $B_2H_6$  80sccm 80kv 5μA 2.0E16)。第3のドーピング処理の際には、nチャネル型TFTを形成する半導体領域317aはフォトレジスト318で覆われている。第1のドーピング処理及び第2のドーピング処理によって、不純物領域327～330には各々異なる濃度でリンが添加されているが、その何れの領域においても、p型を付与する不純物元素の濃度を $2 \times 10^{20} \sim 2 \times 10^{21}$ atoms/cm<sup>3</sup>となる様にドーピング処理することにより、pチャネル型TFTのソース領域およびドレイン領域として機能する為に何ら問題は生じない(図3(H)参照)。10

#### 【0077】

以上のようにして、Gate Overlap LDD構造を有するnチャネル型TFTを形成する。なお、nチャネル型TFTとpチャネル型TFTのいずれか一方をレジストマスクで覆い、n型不純物又はp型不純物を添加し、次に他の方をレジストマスクで覆い、n型不純物又はp型不純物を添加する方法によって、nチャネル型TFTとpチャネル型TFTを作製する方法をとってもよい。

#### 【0078】

その後、プラズマCVD法又はスパッタ法を用い、層間絶縁膜を形成する。例えば、窒化シリコン膜その他の絶縁膜を単層又は積層構造として用いても良い。そして、各々の半導体層に添加された不純物元素を活性化処理する工程を行う。この活性化工程はファーネスアニール炉を用いた熱処理により行う。熱処理の温度は400～700、代表的には500～550で行えれば良い。尚、熱アニール法の他に、レーザーアニール法、又はラビットドサーマルアニール法(RTA法)を適用することができる。この熱処理により、層間絶縁膜が含有する水素が放出され、半導体層を水素化することができる。20

#### 【0079】

その後、ソース配線に達するコンタクトホールと各不純物領域に達するコンタクトホールを形成する為のパターニングを行う。そして、各不純物領域と各々電気的に接続する配線を形成する。なお、これらの配線としてはTi膜、その他の合金膜の単層又は積層膜をパターニングして形成する。このような工程を経てTFTを完成させる。これらの工程は図示しない。以上のようにして、同一基板内に2つのGate Overlap LDD構造トランジスタを組み合わせたCMOS回路を作製することができる。30

#### 【0080】

##### [実施例2]

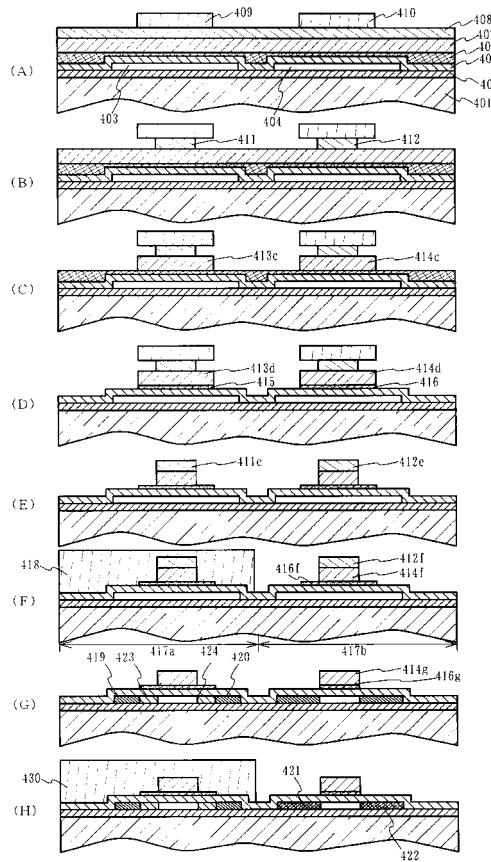

実施例1はいわゆるCMOS回路を用いた制御回路の作製方法について述べたものであるが、本実施例においてはGate Overlap LDD構造TFTとシングルドレイン構造TFTを混在させて作製する作製方法について説明する。実施例1の作製方法にパターニング工程を1回追加した作製方法である。作製プロセス内で前記パターニング工程を追加する順序によってゲート電極の活性層上における幅が異なる2種類のシングルドレイン構造を作製できる。従って、Gate Overlap LDD構造のTFTとシングルドレイン構造TFTを混在させて作製する作製方法は2通り存在する。以下、第1の作製方法について詳細に説明する。40

#### 【0081】

最初に、本発明の実施例であるGate Overlap LDD構造TFTとシングルドレイン構造TFTを混在させて作製する第1の方法について、図4を用いて説明する。本実施例は実施例1で述べた2つ以上のGate Overlap LDD構造TFTを同一基板内に作製する方法の応用である。従って、基本的に実施例1において説明した図3(A)から図3(E)までの工程は図4(A)から図4(E)までの工程と重複するため、説明を省略し、以下、Nチャネル型TFTの領域417aを覆うレジストマスクをパターニングによって形成する50

工程図4(F)から説明する。

**【0082】**

公知のパターニング方法によってNチャネル型TFTの領域417aを覆うようにレジストマスク418を形成する(図4(F)参照)。次に、pチャネル型TFTの領域417bに対して、TaN膜の異方性エッチング処理を行う。前記第2層目ゲート電極膜(W膜)414fをマスクに、第1層ゲート電極膜416fを異方性ドライエッチングする。その結果、第1層ゲート電極膜(TaN膜)416gが形成される(図4(G)参照)。なお、TaN膜のエッチングは完全異方性エッチングとなる条件で行う事が好ましい。このとき、Nチャネル型TFTはレジストマスク418で覆われているためエッチングされない。pチャネル型TFTは、ハードマスク412fで覆われているチャネル領域はエッチングされないが、剥き出しとなるLoV領域にあるTaN膜はエッチングされる。10

**【0083】**

次に、レジストマスク418を剥離し、さらに、ハードマスク412fを剥離する。この様にして、Nチャネル型TFT417a領域のゲート電極は2層構造のハットシェーブゲートの形状となり、pチャネル型TFTのゲート電極は通常の形状となる。

**【0084】**

さらに、実施例1において説明した図3(G)、図3(H)と同じ工程を経て、nチャネル型TFTのソース及びドレイン領域、LoV領域、pチャネル型のソース及びドレイン領域に所定の条件の不純物添加を行う。このようにして、nチャネル型TFTにおいて高濃度不純物領域である第1の不純物領域419、420及び低濃度不純物領域である第2の不純物領域423、424を形成し、pチャネル型TFTにおいてソース及びドレイン領域に通常の高濃度不純物領域421、422を形成する。その後、層間絶縁膜を形成するそして、各々の半導体層に添加された不純物元素を活性化処理する工程を行う。20

**【0085】**

その後、ソース配線に達するコンタクトホールと各不純物領域に達するコンタクトホールを形成する為のパターニングを行う。そして、各不純物領域と各々電気的に接続する配線を形成する。このような工程を経てTFTを完成させる。これらの工程は図示しない。以上のようにして、同一基板内にNチャネル型Gate Overlap LDD構造TFTとpチャネル型シングルドレイン構造TFTを混在させて作製することができる。

**【0086】**

**[実施例3]**

次に、本発明の実施例であるGate Overlap LDD構造TFTとシングルドレイン構造TFTを混在させて作製する第2の方法について、図5を用いて説明する。本実施例は実施例1で述べた2つ以上のGate Overlap LDD構造TFTを同一基板内に作製する方法の応用である。従って、基本的に実施例1において説明した図3(A)から図3(D)までの工程は図5(A)から図5(D)の工程と重複するため、説明を省略し、以下、Pチャネル型TFTの領域517bを覆うレジストマスクをパターニングによって形成する工程(図5(E))から説明する。

**【0087】**

公知のパターニング方法によってPチャネル型TFTの領域517bを覆うようにレジストマスク518を形成する(図5(E)参照)。40

**【0088】**

次に、チャネルマスクを用いたLoV領域エッチングを行う。第1層ゲート電極膜515eをエッチングストッパーとして第2層目ゲート電極膜513dを異方性ドライエッチング処理して、LoV領域に第1層ゲート電極膜515eのみを残す(図5(E)参照)。Gate Overlap LDDゲートエッチング際の第2層目ゲート電極膜507のみを異方性ドライエッチングしたときと同様の方法によってエッチングする。また、寸法補正が必要な場合は、Gate Overlap LDDゲートエッチングの場合と同様に補正すればよい。このとき、pチャネル型TFTはレジストマスク518で覆われているためエッチングされない。nチャネル型TFTにおいては、ハードマスク511eで覆われているチャネル領域はエッチングされないが、剥き出しとなるLoV領域にあるTaN膜はエッチングされる。50

グされないが、剥き出しとなるLov領域にある第2層目ゲート電極膜(W)はエッチングされる。

#### 【0089】

次に、レジストマスク518を剥離し、さらに、ハードマスク511f、511gを剥離する。この様にして、nチャネル型TFTのゲート電極はハットシェーブゲートの形状となり、nチャネル型TFTのゲート電極は通常の形状となる。

#### 【0090】

さらに、実施例1において説明した図3(G)、図3(H)と同じ工程を経て、nチャネル型TFTのソース及びドレイン領域、Lov領域、pチャネル型のソース及びドレイン領域に所定の条件の不純物添加を行う。このようにして、nチャネル型TFTにおいて高濃度不純物領域である第1の不純物領域519、520及び低濃度不純物領域である第2の不純物領域523、524を形成し、pチャネル型TFTにおいてソース及びドレイン領域に通常の高濃度不純物領域521、522を形成する(図5(F)参照)。その後、層間絶縁膜形成工程、活性化工程、コンタクトホール形成工程、及び配線形成工程を経てTFTを完成させる。これらの工程は図示しない。以上のようにして、同一基板内にnチャネル型Gate Overlap LDD構造TFTとpチャネル型シングルドレイン構造TFTを混在させて作製することができる。

#### 【0091】

##### 〔実施例4〕

本実施例においてはLovの異なるGate Overlap LDD構造TFTを混在させて作製する作製方法について説明する。基本的には実施例1と同様に作製されるが、次の点で相違する。Lov狙い値、すなわち、LDD領域のうちゲート電極と重なる領域の長さの種類毎に、マスクの形成を行う。そして、Gate Overlap LDDゲートエッチングを別々に行う。また、ハードマスクの厚さをLovの最小値より小さな値とし、ウェットエッチング時のオーバーエッチング量を制御する事で、ハードマスクの寸法を制御する方法を採用する。

#### 【0092】

本発明の実施例であるLovの異なるGate Overlap LDD構造TFTを混在させて作製する方法について、以下説明する。本実施例は実施例1で述べた2つ以上のGate Overlap LDD構造TFTを同一基板内に作製する方法の応用である。従って、実施例1において説明と共に通する説明は省略し、変更点について詳細に説明する。本実施例では、 $Lov = 0.3 \mu m$ のTFTと $Lov = 0.5 \mu m$ のTFTを同一基板内に形成する方法を、図6を用いて説明する。

#### 【0093】

まず、図6(A)に示すように、基板601上に下地膜602、活性層603、ゲート絶縁膜604、第1の導電膜として第1層ゲート電極膜605、第2の導電膜として第2層目ゲート電極膜606、ハードマスク層607の成膜までを行う。ハードマスク層607の厚さは、目的とするLovの値である $0.3 \mu m$ 以下でなければならない。

#### 【0094】

次に、レジストマスクを形成する。Lovの値を $0.3 \mu m$ としたTFTの領域はレジストマスク608を形成し、Gate Overlap LDDゲートマスクとする。Lovの値を $0.5 \mu m$ のTFTの領域は全体を覆うようにレジストマスク609を形成する。この様なレジストマスクは、実施例1で使用したパターニング用のレチクル上のパターンを設計変更することにより容易に形成できる。

#### 【0095】

そして、Lov狙い値 $0.3 \mu m$ のTFTのみ、実施例1における図3(A)から図3(D)までと同様の工程によりGate Overlap LDDゲートエッチングを行う。その後、レジストマスク608、609を剥離する。

#### 【0096】

なお、ハードマスク607の寸法は、ウェットエッチング時のオーバーエッチング量を制御する事で制御し、レジストマスク608との寸法差を片側 $0.3 \mu m$ とする。

10

20

30

40

50

**【 0 0 9 7 】**

ここまで進めた状態では、 $Lov$ 狙い値  $0.3\ \mu m$  の TFT の領域は図 6 ( E ) の状態になつていて、ゲート電極パターンの縁からハードマスクの縁までの長さは  $0.3\ \mu m$  で目的とする  $Lov$  の値に等しい。一方、目的とする  $Lov$  の値  $0.5\ \mu m$  の TFT の領域はハードマスク層 607 全体がエッティングされずに残り図 6 ( A ) の状態になっている。

**【 0 0 9 8 】**

次に、レジストマスクを形成する。 $Lov$  の値を  $0.5\ \mu m$  とした TFT の領域はレジストマスク 611 をパターニングにより形成する。これが、Gate Overlap LDD ゲートマスクとなる。このとき、同時に、 $Lov$  の値を  $0.3\ \mu m$  の TFT の領域全体を覆うようにレジストマスク 610 を形成する。この様なレジストマスクは、実施例 1 で使用したパターニング用のレチクル上のパターンを設計変更することにより容易に形成できる。さらに、レジストマスク 610 及び 611 を用いたウェットエッティングによりハードマスクを形成する。ハードマスク 607g の寸法は、ウェットエッティング時のオーバーエッティング量を制御する事で制御し、レジストマスク 611 との寸法差を片側  $0.5\ \mu m$  とする。

10

**【 0 0 9 9 】**

そして、目的とする  $Lov$  値が  $0.5\ \mu m$  の TFT 領域のみに対して、上述した Gate Overlap LDD ゲートエッティングを行う。これは、実施例 1 における図 3 ( A ) から図 3 ( D ) までと同様の工程により行う。その後、レジストマスク 610、611 を剥離する。

**【 0 1 0 0 】**

ここまで進めた状態では、目的とする  $Lov$  値  $0.5\ \mu m$  の TFT の領域は図 6 ( F ) の状態になつていて、ゲート電極パターンの縁からハードマスクの縁までの長さは、 $0.5\ \mu m$  で目的とする  $Lov$  の値に等しい。一方、目的とする  $Lov$  の値  $0.3\ \mu m$  の TFT の領域は、 $Lov$  値  $0.5\ \mu m$  の TFT の領域の Gate Overlap LDD ゲートエッティングの際に、レジストマスク 610 で全体が覆われていたためエッティングされずに前工程の状態から変化していない。すなわち、図 6 ( E ) の状態のままであり、ゲート電極パターンの縁からハードマスクの縁までの長さは、 $0.3\ \mu m$  で目的とする  $Lov$  の値と等しい。

20

**【 0 1 0 1 】**

次に、チャネルマスクであるハードマスク 607f、607g を用いて、目的とする  $Lov$  値が  $0.3\ \mu m$  及び  $0.5\ \mu m$  の 2 つの TFT 領域に対して、 $Lov$  領域エッティングを行う。実施例 1 における図 3 ( E ) と同様の工程により、第 2 層目ゲート電極膜のみを異方性ドライエッティング処理する。その後、ハードマスク 607f、607g を剥離する。

30

**【 0 1 0 2 】**

このようにして、 $Lov$  は、目的とする  $Lov$  値  $0.5\ \mu m$  の TFT の領域では  $0.3\ \mu m$ 、目的とする  $Lov$  値  $0.5\ \mu m$  の TFT の領域では  $0.5\ \mu m$  となる。ともに目的とする  $Lov$  を獲得する。この様にして、狙い通りの  $Lov$  を持つハットシェープゲートを形成でき、 $Lov=0.3\ \mu m$  の Gate Overlap LDD 構造の TFT と  $Lov=0.5\ \mu m$  の Gate Overlap LDD 構造の TFT を同一基板内に混在させて形成できる。

**【 0 1 0 3 】**

さらに、実施例 1 において説明した図 3 ( G ) から図 3 ( H ) までの工程と同じ工程を経て、n チャネル型 TFT のソース及びドレイン領域、及び  $Lov$  領域、p チャネル型のソース及びドレイン領域、及び  $Lov$  領域に所定の条件の不純物添加を行う。このようにして、N チャネル型 TFT 及び P チャネル型 TFT において高濃度不純物領域である第 1 の不純物領域 619 ~ 622 及び低濃度不純物領域である第 2 の不純物領域 623 ~ 626 を形成する。

40

**【 0 1 0 4 】**

その後、層間絶縁膜を形成する。そして、各々の半導体層に添加された不純物元素を活性化処理する工程を行う。

**【 0 1 0 5 】**

ソース配線に達するコンタクトホールと各不純物領域に達するコンタクトホールを形成する為のパターニングを行う。そして、各不純物領域と各々電気的に接続する配線を形成す

50

る。このような工程を経て TFT を完成させる。これらの工程は図示しない。以上のようにして、同一基板内に Loff 領域の異なる n チャネル型 Gate Overlap LDD 構造 TFT と p チャネル型 Gate Overlap LDD 構造 TFT を混在させて作製することができる。

#### 【 0106 】

##### 〔 実施例 5 〕

次に、実施例 1 の Gate Overlap LDD 構造トランジスタの作製方法を変更することで、Loff 領域のみを持つ TFT 構造の作製方法を示す。

#### 【 0107 】

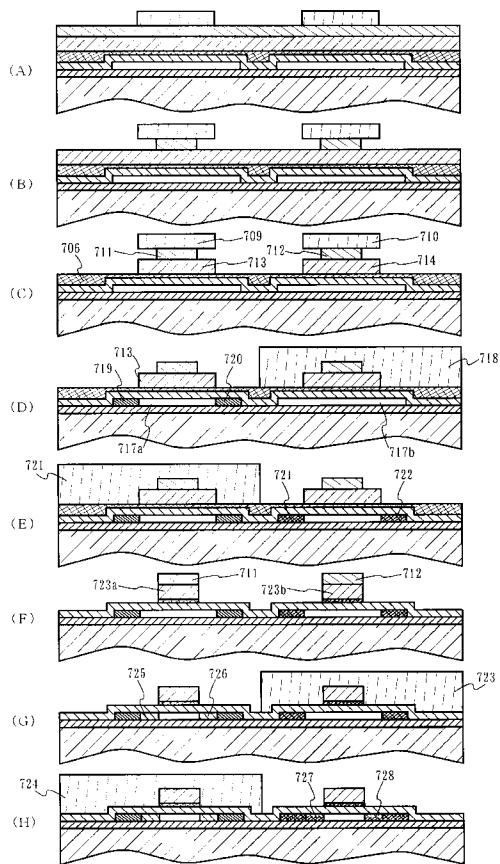

本実施例では、Loff 領域を有する TFT の作製方法について、図 7 を用いて説明する。基本的にレジストマスクパターン工程から第 2 層目ゲート電極膜のみエッチング工程までの図 3 ( A ) から図 3 ( C ) までの作製方法は実施例 1 の発明と同一であるので、此処では省略する。図 3 ( C ) に示したエッチング条件により、第 2 層目ゲート電極膜 ( W 膜 ) 713、714 のみがエッチングされる為、第 1 層ゲート電極膜 ( TaN ) 706 はエッチングされずに残る。第 1 層ゲート電極膜 ( TaN ) を残す理由は、後述するチャネルエッチングの際に、ソース及びドレイン領域のゲート絶縁膜や活性層を消失させないためである。しかし、このことを考慮する必要がないエッチング条件により、第 2 層目ゲート電極膜 ( W 膜 ) をエッチングする場合は、第 1 層ゲート電極膜を残さずエッチングしてもよい。

10

#### 【 0108 】

なお、このエッチングは、完全異方性エッチングとなる条件で行う事が望ましい。完全等方性エッチングは、レジストマスクの下まで第 2 層目ゲート電極膜 ( W 膜 ) がエッチングされるので、望ましくない。完全異方性エッチングよりも、多少等方性エッチングに寄った条件で行う場合は、実施例 1 で述べた要領で寸法補正を行えばよい。

20

#### 【 0109 】

次に、レジストマスク 709、710 を剥離し、ハードマスク 711、712 を露出させる。この工程は図示しない。そして、公知のパターニング方法によって p チャネル型 TFT の領域 717b を覆うようにレジストマスク 718 を形成する ( 図 7 ( D ) 参照 ) 。その後、n チャネル型 TFT のソース及びドレイン領域に n 型の高濃度不純物を添加する。本実施例においては、ソース及びドレイン領域に第 1 層ゲート電極膜を残しているため、高濃度不純物を、第 1 層ゲート電極膜とゲート絶縁膜とを貫通させて添加する。ゲート Loff マスクを用いたエッチングで第 1 層ゲート電極膜まで除去した場合は、高濃度不純物をゲート絶縁膜のみを貫通させて添加する。しかし、Loff 領域は第 1 層ゲート電極膜及び第 2 層目ゲート電極膜によってマスクされているため、不純物は一切添加されない。これにより、ソース及びドレイン領域のみが高濃度不純物領域となり、第 1 の不純物領域 719、720 が形成される ( 図 7 ( D ) 参照 ) 。

30

#### 【 0110 】

その後、レジストマスク 718 を剥離する。次に、公知のパターニング方法によって n チャネル型 TFT の領域 717a を覆うようにレジストマスク 721 を形成する ( 図 7 ( E ) 参照 ) 。その後、p チャネル型 TFT のソース及びドレイン領域に p 型の高濃度不純物を添加する。不純物添加の条件は、n チャネル型 TFT の場合に準じ、ここでは省略する。これにより、ソース及びドレイン領域のみが高濃度不純物領域となり、第 1 の不純物領域 721、722 が形成される ( 図 7 ( E ) 参照 ) 。

40

#### 【 0111 】

次に、不純物添加後にレジストマスク 721 を剥離し、ハードマスク 711 を露出させる。そして、ハードマスク 711、712、すなわち、チャネルマスクを用いたチャネルエッチングを行う。本実施例では、第 1 層ゲート電極膜 ( TaN ) をエッチングストッパーとして残しているので、Loff 領域の第 2 層目ゲート電極膜 ( W ) をエッチングした後、第 1 層ゲート電極膜 ( TaN ) をエッチングする。なお、エッチングの条件等は実施例 1 に準ずる。ゲート Loff マスク ( チャネル領域と Loff 領域を合わせた領域を覆うマスク ) を用いたエッチングで第 1 層ゲート電極膜 ( TaN ) を残さずに除去した場合は、Loff 領域に

50

おける第2層目ゲート電極膜(W)及び第1層ゲート電極膜(TaN)を除去する。このようにして、第1の形状の導電層723が形成される(図7(F))。なお、このエッチングも完全異方性エッティングとなる条件で行う事が望ましい。必要があれば寸法補正を行う。

#### 【0112】

次に、ウェットエッティングによりハードマスク711、712を除去する。そして、公知のパターニング方法によってpチャネル型TFTの領域717bを覆うようにレジストマスク723を形成する(図7(G)参照)。その後、nチャネル型TFTのLoff領域にN型の低濃度不純物を添加する。不純物はゲート絶縁膜を貫通させて添加する。なお、Loff領域への不純物添加は、Loff領域における第1層ゲート電極膜(TaN)を除去する前に、第1層ゲート電極膜とゲート絶縁膜とを貫通させて添加しても良い。

10

#### 【0113】

その後、レジストマスク723を剥離する。次に、公知のパターニング方法によってnチャネル型TFTの領域717aを覆うようにレジストマスク724を形成する(図7(H)参照)。その後、pチャネル型TFTのソース及びドレイン領域にp型の低濃度不純物を添加する。不純物添加の条件は、nチャネル型TFTの場合に準じ、ここでは省略する。これにより、ソース及びドレイン領域が高濃度不純物領域となり、また、Loff領域が低濃度不純物領域となり、第1の不純物領域719～722、第2の不純物領域725～728が形成される(図7(H)参照)。

20

#### 【0114】

その後、層間絶縁膜を形成する。そして、各々の半導体層に添加された不純物元素を活性化処理する工程を行う。

#### 【0115】

ソース配線に達するコンタクトホールと各不純物領域に達するコンタクトホールを形成する為のパターニングを行う。そして、各不純物領域と各々電気的に接続する配線を形成する。このような工程を経てTFTを完成させる。これらの工程は図示しない。以上のようにして、同一基板内にNチャネル型及びPチャネル型のLoff領域のみを持つTFTを混在させて作製することができる。

#### 【0116】

本実施例では、同一基板内における2つのTFTのLoffの値は全て一定としているが、積層マスクの形成とゲートLoffエッティングをLoffの値毎に行うことにより、Loffの値の異なるTFTや、シングルドレイン構造(Loff=0)のTFTを同一基板上に混在させる半導体装置の作製方法としてもよい。

30

#### 【0117】

##### [実施例6]

本実施例では、Gate Overlap LDD構造のTFTを用いた透過型の液晶表示装置の作製方法について述べる。尚、基本的に実施例1に記載した作製方法と同一の方法で作製するため、重複する説明は省略する。

#### 【0118】

最初に、液晶表示装置の構成要素の一つであるTFTアレイ基板の作製方法について述べる。

40

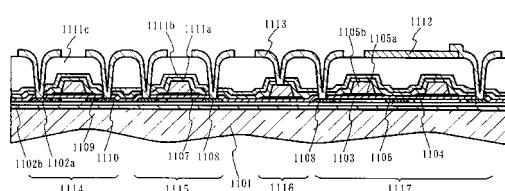

#### 【0119】

図11において、TFT作製用の基板1101を用意する。次に、基板1101に基板からの不純物拡散を防止するための下地絶縁膜1102(1102a、1102b)を形成する。下地絶縁膜1102には、酸化シリコン膜や窒化シリコン膜などの絶縁性を有するものを用いる。

#### 【0120】

下地絶縁膜1102の上に半導体層1103を形成する。半導体層1103は、非晶質シリコン膜を成膜後、前記非晶質シリコン膜を結晶化して得られた結晶質シリコン膜をフォトリソおよびエッティングにより所望の形状にして形成する。半導体層1103には、素子

50

の閾値電圧を制御するための不純物添加を添加する。前記不純物としては、リンあるいはボロンなどを用いる。前記不純物の添加は、前記非晶質シリコン膜を成膜後、あるいは前記非晶質シリコン膜を結晶化後や半導体層1103を形成後にドーピングによって行う。また、成膜時に前記不純物を添加した非晶質シリコン膜を用いてもよい。

#### 【0121】

次いで、半導体層1103の上にゲート絶縁膜1104を形成する。絶縁膜1104は厚さ100nm～120nmのシリコン酸化膜を成膜して形成している。ゲート絶縁膜1104の厚さは、必要に応じて100nm以下でも、120nm以上でも構わない。前記シリコン酸化物以外にも、窒化シリコン膜などの絶縁膜を用いても構わない。

#### 【0122】

ゲート絶縁膜1104上にゲート電極1105(1105a、1105b)を形成する。ゲート絶縁膜1104の上に厚さ20～100nmの導電成膜1105aと厚さ100～400nmの導電成膜1105bを積層成膜し、フォトリソグラフィおよびエッティングにより所望の形状のゲート電極1105を形成する。本実施例では、導電性膜1105aにTaN、導電性膜1105bにWを用いている。

10

#### 【0123】

n<sup>-</sup>領域1106を形成する。n<sup>-</sup>領域1106は、半導体層全面に燐をドーピングして形成する。本実施例では、燐を用いているが、n型不純物元素であればAs等を用いても構わない。またイオンドーピング以外に、イオン注入などの方法を用いても構わない。

#### 【0124】

n<sup>-</sup>領域1107、n<sup>+</sup>領域1108を形成する。n<sup>-</sup>領域1107およびn<sup>+</sup>領域1108以外の領域にn型不純物が添加されないようにレジストマスクした後、燐をドーピングしてn<sup>-</sup>領域およびn<sup>+</sup>領域を形成する。n<sup>-</sup>領域1107にはゲート電極1105aを突き抜けて燐がドープされる。またn<sup>-</sup>領域には半導体層1103上に残っている絶縁膜を突き抜けてドープされる。本実施例では、n<sup>-</sup>領域1107を形成するためのドープとn<sup>+</sup>領域1108を形成するためのドープを同時に行っているが、n<sup>-</sup>領域形成用とn<sup>+</sup>領域形成用とにドーピング条件を変えて行ってもよい。また燐以外にAsなどのn型不純物を用いてもよく、添加方法もイオンドーピング以外にイオン注入などの方法を用いても構わない。

20

#### 【0125】

p<sup>-</sup>領域1109、p<sup>+</sup>領域1110を形成する。p<sup>-</sup>領域1109およびp<sup>+</sup>領域1110以外の領域にp型不純物が添加されないようにレジストマスクした後、燐をドーピングしてp<sup>-</sup>領域およびp<sup>+</sup>領域を形成する。p<sup>-</sup>領域1109にはゲート電極1105aを突き抜けて燐がドープされる。またp<sup>-</sup>領域には半導体層1103上に残っている絶縁膜を突き抜けてドープされる。本実施例では、p<sup>-</sup>領域1109を形成するためのドープとp<sup>+</sup>領域1110を形成するためのドープを同時に行っているが、p<sup>-</sup>領域1109形成用とp<sup>+</sup>領域1110形成用とにドーピング条件を変えて行ってもよい。また燐以外にAsなどのp型不純物を用いてもよく、添加方法もイオンドーピング以外にイオン注入などの方法を用いても構わない。

30

#### 【0126】

層間絶縁膜1111(1111a、1111b、1111c)を形成する。層間絶縁膜1111は無機膜である第一の層間絶縁膜1111aと第2の層間絶縁膜1111b、および有機膜である第3の層間絶縁膜1111cから形成される。

40

#### 【0127】

第一の層間絶縁膜1111aには厚さ50～100nmの酸化シリコン膜を用いる。第一の層間絶縁膜1111aを形成した後、熱により半導体層に添加した不純物を活性化する。前記活性化はファーネスにより窒素ガス雰囲気中で550～1～12時間行う。本実施例では活性化をファーネスを用いて行っているが、RTAやレーザーを用いて行っても構わない。前記活性化の雰囲気、温度、時間は上記に限定されない。低酸素雰囲気中でファーネスやRTAによる活性化を行うなど、ゲート電極1105が酸化されない雰囲気で活性化するのであれば、層間絶縁膜1111aは無くてもよい。さらにレーザーにより活性

50

化を行う場合も、層間絶縁膜 1111a は無くてもよい。また前記酸化シリコン膜以外に、活性化温度に耐性があり、活性化中のゲート電極 1105 の酸化を防止でき、さらに光透過性のよいものであれば、前記酸化シリコン膜以外の材料を用いてもよい。

#### 【0128】

第2の層間絶縁膜 1111b には厚さ 50 ~ 100 nm の窒化シリコン膜を用いる。第2の層間絶縁膜 1111b を形成した後、窒素雰囲気中で 350 ~ 420 の熱処理を1時間行う。本実例では、窒素雰囲気中で熱処理を行っているが、3 ~ 100 % の水素雰囲気中で行ってもよい。また熱処理時間は1時間に限定されない。第一の層間絶縁膜 1111a 形成後の活性化処理後に 3 ~ 100 % の水素雰囲気中で1時間の熱処理を行うのであれば、第2の層間絶縁膜 1111b を形成後の前記熱処理はなくてもよい。

10

#### 【0129】

第3の層間絶縁膜 1111c には厚さ 0.6 ~ 1.6 μm のアクリルを用いる。アクリル以外に絶縁性を有するポリイミドなどの材料を用いてもよい。また絶縁性を有する無機膜を用いてもよい。無機膜の厚さは前記無機膜の比誘電率によっても異なるが、通常 1 ~ 3 μm である。

#### 【0130】

第三の層間絶縁膜 1111c の上に画素電極 1112 を形成する。画素電極 1112 は ITO (Indium Tin Oxide) を成膜した後、フォトリソおよびエッチングによって形成する。透明導電膜であれば ITO 以外に酸化錫などを用いてもよい。

20

#### 【0131】

画素電極 1112 を形成後、高不純物濃度領域 (1108, 1110) と配線 1113 を接続するためのコンタクトホールをフォトリソおよびエッチングによって形成する。

#### 【0132】

コンタクトホールを形成後、配線 1113 を形成する。配線 1113 は厚さが約 60 nm の第一の Ti 膜を成膜後、厚さが約 40 nm の TiN 膜を積層成膜し、さらに厚さが 350 nm の Al-Si (2 wt% の Si を含有した Al) 膜を積層成膜して、最後に第2の Ti 膜を成膜した積層膜にフォトリソおよびエッチングをして形成する。第1の Ti 膜により Al-Si 膜中の Al が半導体層に拡散するのを防ぎ、第2の Ti 膜により、Al-Si 膜のヒロックを防止している。本実施例では TiN 膜を成膜しているが、前記 Al の拡散防止効果を高めるためであり、成膜しなくてもよい。また Al-Si 以外に Al-Ti (Ti を含有した Al) など、他の低抵抗性導電性膜を用いても構わない。

30

#### 【0133】

本実施例では、画素電極 1112 を配線 1113 を積層した領域を設け、コンタクトホール形成を行うことなく、画素電極 1112 と配線 1113 との電気的な接続をしている。

#### 【0134】

以上のような工程を得て、Gate Overlap LDD 構造の n チャネル型 TFT および Gate Overlap LDD 構造の p チャネル型 TFT を有する駆動回路と画素 TFT および保持容量、画素電極を有する画素部を同一基板上有する TFT アレイ基板を作製する。

#### 【0135】

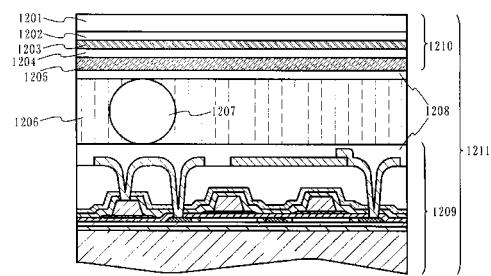

次に対向基板の作製方法について述べる。図 12 に示すように、基板 1201 上に遮光膜 1202 を形成する。遮光膜 1202 は、金属クロムを成膜し、光露光およびエッチングにより形成する。

40

#### 【0136】

遮光層 1202 の上に画素電極 1205 を形成する。画素電極 1205 は透明導電膜である ITO を成膜し、フォトリソおよびエッチングにより形成する。

#### 【0137】

遮光膜 1206 と画素電極 1205 の間にカラーフィルター 1203 を設ける場合は、遮光層 1202 の上に目的の色の着色樹脂をスピンコート法により塗布し、露光および現像して形成する。赤、青、緑の三色のカラーフィルター 1203a ~ 1203c (図示しない)、各々に対して前記カラーフィルター形成工程を繰り返す。

50

## 【0138】

カラーフィルター1203と遮光層1202の段差を埋めて平坦化する目的の保護膜1204を形成する。保護膜1204はカラーフィルターの上からアクリルを塗布して形成する。アクリルの他に平坦化可能な材料を用いてもよい。カラーフィルターを設けない場合は保護膜1204は無くてもよい。以上のような工程を経て対向基板を作製する。

## 【0139】

TFTアレイ基板1209と対向基板1210を作製したら、これらの基板を用いて液晶パネル1211を作製する。

## 【0140】

TFTアレイ基板1209のTFTを形成した側と、対向基板1210の画素電極を形成した側にそれぞれ配向膜1208を形成する。10 配向膜1208の形成はオフセット印刷法を用いる。配向膜1208の材料にはポリイミド樹脂用いるが、この他、ポリアミック系樹脂などを用いてもよい。

## 【0141】

配向膜1208を形成したTFT基板と対向基板の配向膜を形成した側にラビング処理をして液晶分子がある一定のプレチルト角をもって配向するようとする。ラビング処理後、ラビング処理によって発生したゴミやラビング布の抜け毛を除去するためにTFTアレイ基板1209と対向基板1210を洗浄する。

## 【0142】

対向基板側にシール剤(図示しない)を塗布した後、対向基板1210をオーブンで加熱し前記シール剤を仮硬化させる。20 仮硬化後、対向基板の画素電極を形成した側にプラスチック球のスペーサーを散布する。

## 【0143】

TFTアレイ基板1209のTFTを形成している側と対向基板1210の画素電極1205を形成している側とが向き合うようにして、両基板を精度よく張り合わせ液晶パネル1211を作製する。シール剤中にはフィラー(図示しない)が混入されており、フィラーとスペーサーにより両基板を均一な間隔をもって張り合わすことができる。

## 【0144】

張り合わせた基板のうち不要な部分をせん断して、所望のサイズの液晶パネル1211基板にする。30 液晶パネル1211の内部に液晶材料1206を注入する。パネル内部全体に液晶材料1206を満たした後、封止剤(図示しない)によって完全に封止する。

## 【0145】

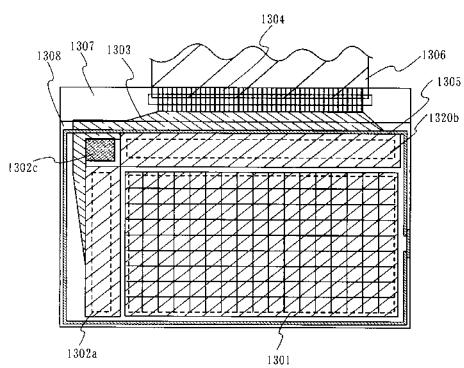

図13は液晶パネル1211の上面図である。画素部1301の周辺に走査信号駆動回路1302aと画像信号駆動回路1302bが設けられている。この他、CPUやメモリなどの信号処理回路1302cを設けてもよい。駆動回路は接続配線群1303によって外部入出力端子群1304と接続されている。

## 【0146】

画素部1301では走査信号駆動回路1302aから延在するゲート配線群と画像信号駆動回路1302bから延在するデータ配線群がマトリクス状に交差して画素を形成し、各画素にはそれぞれ画素TFTと保持容量、画素電極が設けられている。40

## 【0147】

シール剤1305は、TFTアレイ基板1307上の画素部1301および走査信号駆動回路1302a、画像信号駆動回路1302b、信号処理回路1302bの外側であり、且つ外部入力端子1304よりも内側の部分に形成する。

## 【0148】

液晶パネル1211の外側では、フレキシブルプリント配線板(FPC: Flexible Printed Circuit)1306が外部入出力端子1304に接続しており、接続配線群1303によりそれぞれの駆動回路に接続している。外部入出力端子1304はデータ配線群と同じ導電性膜から形成される。フレキシブルプリント配線板1306はポリイミドなどの有機樹脂フィルムに銅配線が形成されており、異方性導電性接着剤で外部入出力端子1304と50

接続する。

#### 【0149】

液晶パネル1211の対向基板側に、対向基板に最も近い液晶層の液晶分子のディレクタ方向と同じ方向の直線偏光が入射するように偏光板と位相差板を取り付ける。またパネルのTFT基板側に、TFT基板に最も近い液晶層の液晶分子のディレクタ方向と同じ方向の光が出射するように偏光板と位相差板を取り付ける。以上のような方法で、本発明の液晶ディスプレイを完成させることができる。

#### 【0150】

##### 【発明の効果】

本発明の作製方法によれば、1回のフォトリソグラフ工程のみで、第1層目のマスクパターンを、第2層目のマスクパターンに対しセルファーラインで、かつ、相似形で寸法の異なるマスクパターンとして形成できる。活性層上における線幅を、第1層目のマスクパターンではLi、第2層目のマスクパターンではL'となるように設定し、第2層目のマスクパターンを用いた異方性エッチング、第1層目のマスクパターンを用いた異方性エッチングを順に行うことにより、ハットシェープゲートをセルファーラインで形成できる。従って、作製工程において使用するレチクル数を減少し、Gate Overlap LDD構造、及びLooff領域のみを持つTFTの微細化に伴う作製方法の複雑化の問題を解決できる。10

#### 【0151】

また、ゲート電極膜を単層膜で構成する場合であっても、2層目のマスクパターンを利用した異方性エッチングにおいてLooff領域上のゲート膜厚を精密制御することにより、ハットシェープゲートを形成できる。20

#### 【0152】

さらに、本発明の作製方法によれば、導電膜を異なる材質の2層構造とすることにより、第1層目の導電膜を、第2層目の導電膜をエッチングする際のエッチングストッパーとすることができるため、導電膜をエッチングする条件の選択の幅を拡大できる。そのため、ハットシェープゲートを構成する第1の導電膜及び第2の導電膜の組み合わせをTa、W、Ti、Mo、Al、Cuから選ばれた元素、又は前記元素を主成分とする合金材料等の中から任意に選択することができる。

#### 【0153】

このように、本発明では、第2層目ゲート電極はアルミニウム膜又はアルミニウム合金膜に限定されない点で従来の技術にない優れた効果を奏でることができる。30

#### 【0154】

本発明によれば、タンクステン(W)等の高融点金属をゲート材料として選択できるため、不純物の活性化を、通常の熱処理により(550~800)行うことができる。このため、活性化工程はイオン注入法に限定されず、熱処理又はイオン注入法の後に熱処理を行うこともできる。また、高融点金属を用いることにより、熱処理によって電気的に活性な領域の特性が劣化することを防止できる。

#### 【0155】

本発明によれば、抵抗値の低い金属膜や複合材料膜をゲート材料として利用でき、さらにセルファーラインプロセスによりこれらの材料の微細化を実現できるため、微細な領域のTFTであっても回路動作速度を高め、近年の超LSIの進展に伴う高速化に対応できる。40

#### 【0156】

また、本発明の半導体装置の作製方法によれば、ハードマスク(第1層目マスクパターン)の寸法よりレジストマスク(第2層目マスクパターン)の寸法を大きく設定できるため、レジストマスクの活性層上における線幅がL'となり、Liよりも大きくできるため、微細化が進んだGate Overlap LDD構造、及びLooff領域のみを持つTFTのプロセスであっても、レジストマスクの活性層上における線幅は微細化されず、パターニングマージンを拡大できる。パターニングマージンの拡大は、基板の歪みの影響が無視できない大型基板を用いる場合に、大きな利点となる。

#### 【0157】

50

さらに、ハードマスクはレジストマスクを利用したウェットエッチング処理により形成されることにより、微細化が進んだTFTのプロセスにおいて膜厚のバラツキ、エッティングのムラの発生、コロージョン、及び膜残り欠陥等を防止できる。

### 【0158】

#### 【図面の簡単な説明】

- 【図1】 本発明によるGate Overlap LDD構造TFTの作製方法を示す。

- 【図2】 本発明によってLooff領域のみを持つTFTの作製方法を示す。

- 【図3】 本発明によるCMOS回路の作製方法を示す。

- 【図4】 本発明によるGate Overlap LDD構造TFTとシングルドレイン構造TFTを混在させて作製する第1の方法を示す。 10

- 【図5】 本発明によってGate Overlap LDD構造TFTとシングルドレイン構造TFTを混在させて作製する第2の方法を示す。

- 【図6】 本発明によるLoVの異なるGATE OVERLAP LDD構造TFTを混在させて作製する作製方法を示す。

- 【図7】 本実施例によるLooff領域のみを持つTFTの作製方法を示す。

- 【図8】 マスク形成工程を示す図。

- 【図9】 ゲート形成工程について示す図。

- 【図10】 ハードマスクをマスクとして第2層目ゲート電極膜のみを異方性ドライエッティング処理する様子を示す図。

- 【図11】 TFTアレイ基板の作製方法を示す図。 20

- 【図12】 TFTアレイ基板と対向基板とが重なり合っている様子を示す図。

- 【図13】 液晶パネルの上面図を示す図。

【図1】

【図2】

【図3】

【図4】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

---

フロントページの続き

(51)Int.Cl. F I

**G 02 F 1/1368 (2006.01)** H 01 L 29/58 G

G 02 F 1/1368

(58)調査した分野(Int.Cl., DB名)

H01L 21/336

H01L 29/78

H01L 29/786