(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

**(19) World Intellectual Property Organization**

International Bureau

A standard linear barcode is located at the bottom of the page, spanning most of the width. It is used for tracking and identification of the document.

**(43) International Publication Date

5 October 2006 (05.10.2006)**

PCT

(10) International Publication Number

**WO 2006/104562 A2**

**(51) International Patent Classification:**

(74) **Agents:** KING, Robert, L. et al.; 7700 W. Parmer Lane, MD: PL02, Austin, Texas 78729 (US).

(21) International Application Number:

PCT/US2006/003528

(81) **Designated States** (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, LY, MA, MD, MG, MK, MN, MW, MX, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SM, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

**(22) International Filing Date:** 1 February 2006 (01.02.2006)

**(25) Filing Language:** English

**(26) Publication Language:** English

(30) Priority Data: 11/092,289 29 March 2005 (29.03.2005) US

(71) Applicant (for all designated States except US):

**FREESCALE SEMICONDUCTOR, INC. [US/US];**

6501 William Cannon Drive West, Austin, Texas 78729

(US).

(72) Inventors; and

(75) Inventors/Applicants (*for US only*): MATHEW, Leo [IN/US]; 15844 Garrison Circle, Austin, Texas 78717 (US). KOLAGUNTA, Venkat, R. [IN/US]; 11915 Sky West Drive, Austin, Texas 78758 (US). SING, David, C. [US/US]; 1505 Summit Street, Austin, Texas 78741 (US).

(84) **Designated States** (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

### Published:

— without international search report and to be republished upon receipt of that report

[Continued on next page]

**(54) Title: METHOD OF FORMING A SEMICONDUCTOR DEVICE HAVING ASYMMETRIC DIELECTRIC REGIONS AND STRUCTURE THEREOF**

10

WO 2006/104562 A2

**(57) Abstract:** A method for forming a semiconductor device (10) including forming a semiconductor substrate (12); forming a gate electrode (16) over the semiconductor substrate having a first side and a second side, and forming a gate dielectric under the gate electrode. The gate dielectric has a first area (42) under the gate electrode and adjacent the first side of the gate electrode, a second area (44) under the gate electrode and adjacent the second side of the gate electrode, and a third area (14) under the gate electrode that is between the first area and the second area, wherein the first area is thinner than the second area, and the third area is thinner than the first area and is thinner than the second area.

*For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.*

**METHOD OF FORMING A SEMICONDUCTOR DEVICE HAVING ASYMMETRIC DIELECTRIC REGIONS AND STRUCTURE THEREOF**

**Field of the Invention**

5 [0001] This invention relates generally to semiconductor devices, and more specifically, to semiconductor devices having asymmetric dielectric regions.

**Background**

[0002] Semiconductor devices, such as MOSFETs (metal oxide semiconductor field effect transistors), may have asymmetrically doped source and drain regions to increase drive currents and reduce parities. In the prior art, the asymmetrical source and drain doped regions may have different dopants or different numbers of implanted regions. In addition, to form the different dopant regions, spacers on either side of a gate electrode may be different shapes or sizes. While these prior art techniques allow for increased drive current, to form these asymmetrically doped semiconductor devices additional process steps are used that undesirably increase cycle time. Therefore, a need exists for obtaining the advantages of asymmetrically doped source and drain regions without dramatically increasing cycle time.

**Brief Description of the Drawings**

[0003] The present invention is illustrated by way of example and is not limited by the accompanying figures, in which like references indicate similar elements.

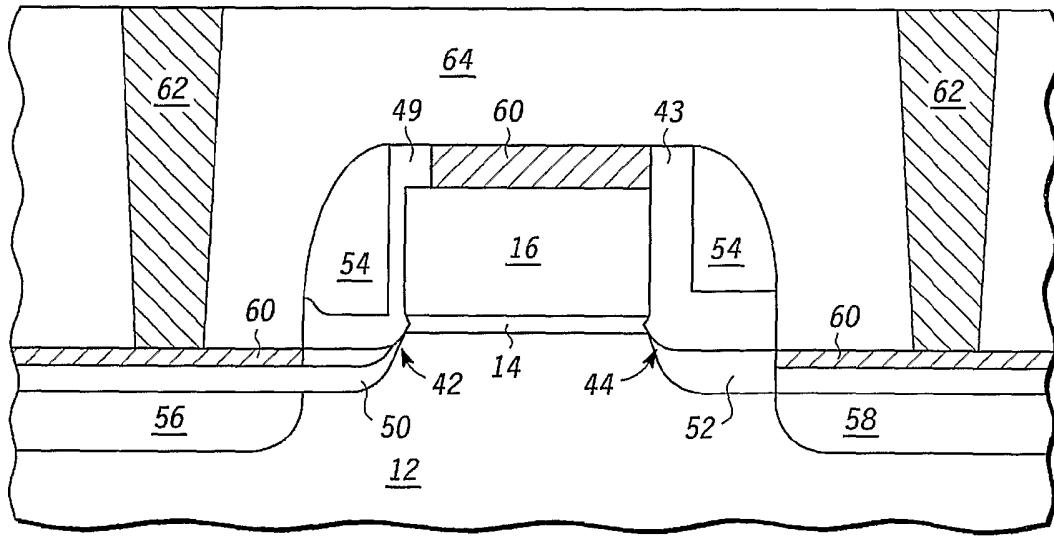

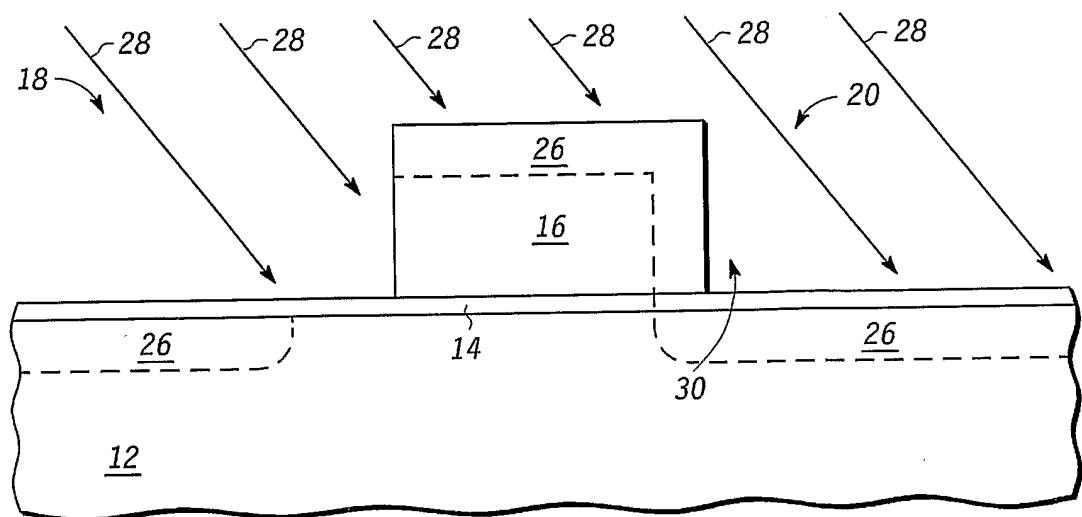

20 [0004] FIG. 1 illustrates a cross-sectional view of a portion of a workpiece while implanting an oxidation enhancing species in accordance with an embodiment of the present invention;

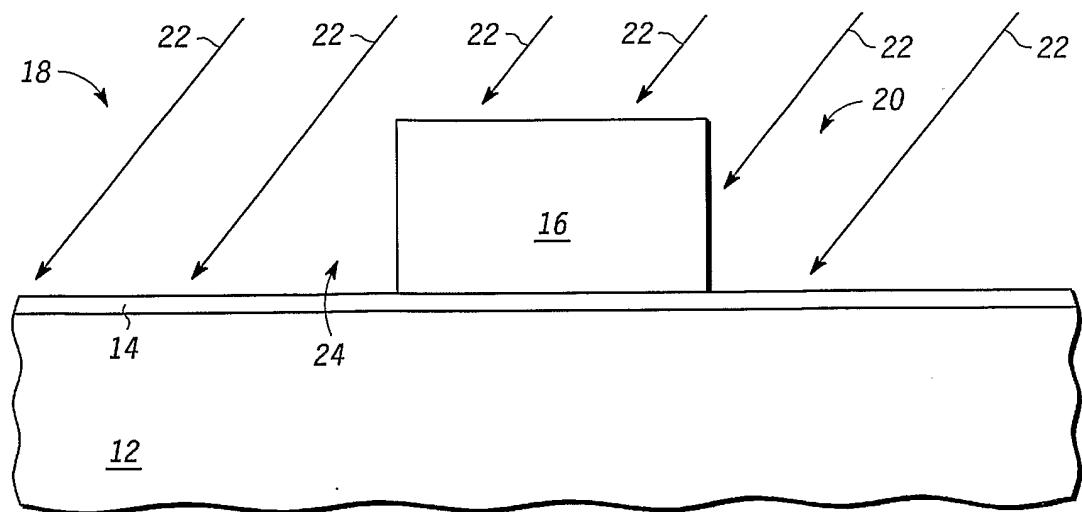

[0005] FIG. 2 illustrates the workpiece of FIG. 1 after implanting the oxidation enhancing species in accordance with an embodiment of the present invention;

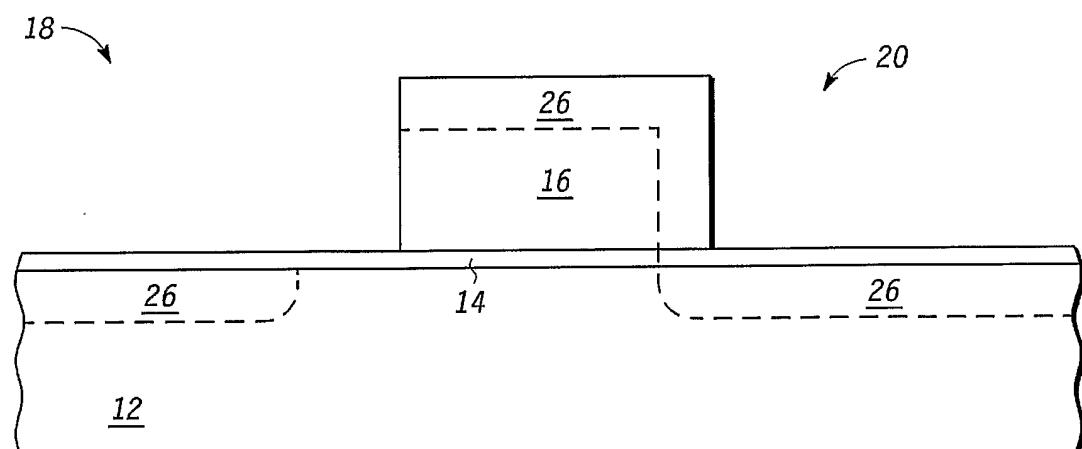

25 [0006] FIG. 3 illustrates the workpiece of FIG. 2 after forming a dielectric layer in accordance with an embodiment of the present invention;

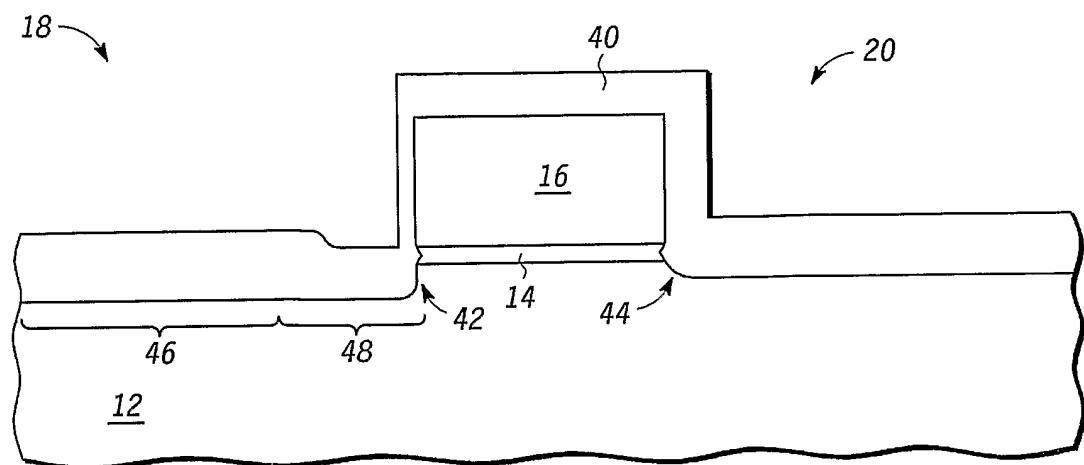

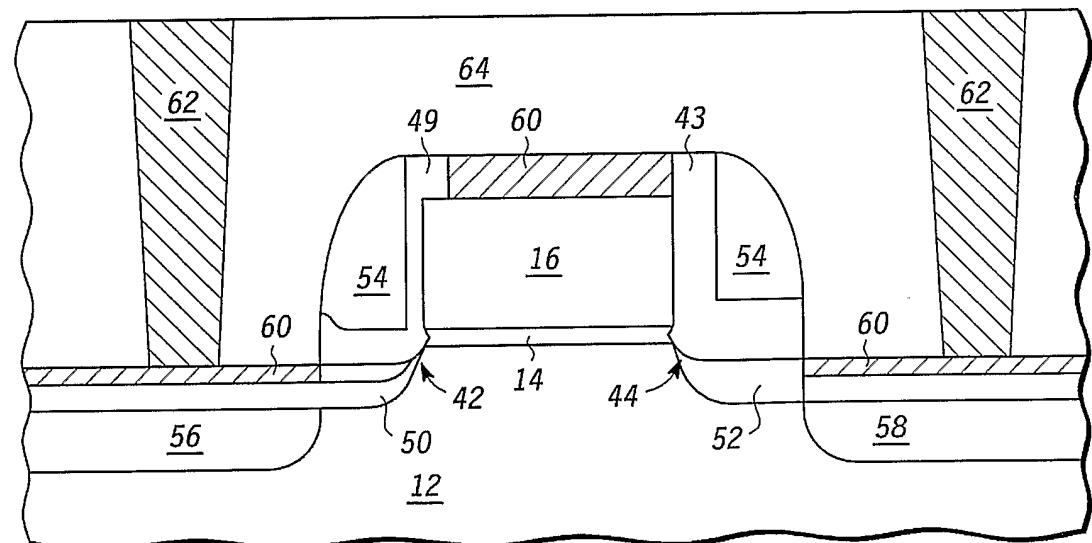

[0007] FIG. 4 illustrates the workpiece of FIG. 3 after additional processing to form a semiconductor device in accordance with an embodiment of the present invention;

**[0006]** FIG. 3 illustrates the workpiece of FIG. 2 after forming a dielectric layer in accordance with an embodiment of the present invention;

**[0007]** FIG. 4 illustrates the workpiece of FIG. 3 after additional processing to form a semiconductor device in accordance with an embodiment of the present invention;

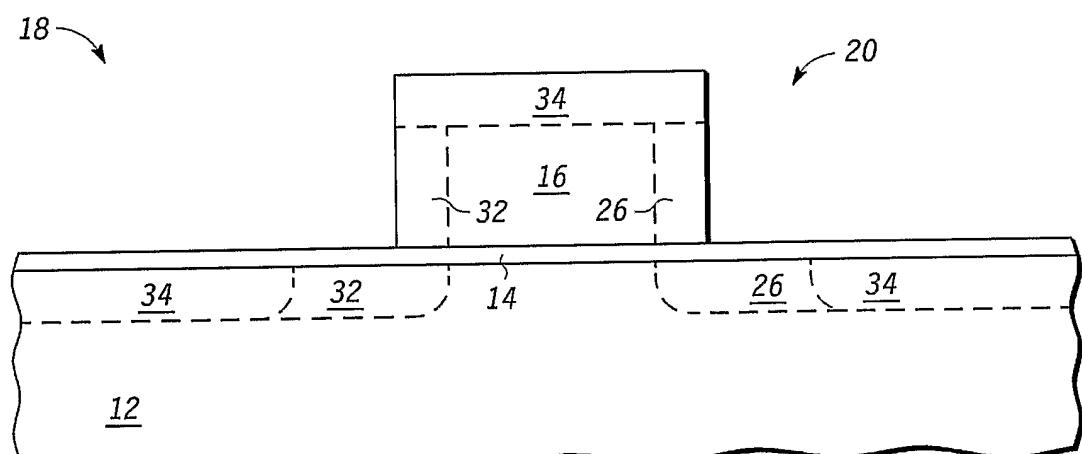

5 **[0008]** FIG. 5 illustrates the workpiece of FIG. 2 while implanting an oxidation reduction species in accordance with an embodiment of the present invention; and

**[0009]** FIG. 6. illustrates the workpiece of FIG. 5 after implanting the oxidation reduction species in accordance with an embodiment of the present invention.

10 **[0010]** Skilled artisans appreciate that elements in the figures are illustrated for simplicity and clarity and have not necessarily been drawn to scale. For example, the dimensions of some of the elements in the figures may be exaggerated relative to other elements to help improve the understanding of the embodiments of the present invention.

Detailed Description of the Drawings

**[0011]** FIG. 1 illustrates a cross-sectional view of a portion of a workpiece 10 having a semiconductor substrate 12, a first dielectric layer 14, a gate electrode 16, a source region 18, and a drain region 20, while an implantation is being performed. The workpiece 10 is a portion of a semiconductor wafer and will undergo various processing to form a semiconductor device. The semiconductor substrate 12 can be any semiconductor material or combinations of materials, such as gallium arsenide, silicon germanium, silicon-on-insulator (SOI) (e.g., fully depleted SOI (FDSOI)), silicon, monocrystalline silicon, the like, and combinations of the above. The first dielectric layer 14 may be silicon dioxide, a high dielectric constant (hi-k) dielectric (such as hafnium oxide or zirconium oxide), the like, or a combination the above. In one embodiment, the first dielectric layer 14 is hafnium oxide with an underlying layer of silicon dioxide, which may be a native silicon dioxide. Although as shown in FIG. 1 the first dielectric layer 14 is not patterned, it may be patterned. For example, portions of the first dielectric layer 14 that are not under the gate electrode 16 may be removed while patterning a gate electrode layer to form the gate electrode 16. The gate electrode 16 may be any suitable material, such as polysilicon (which subsequently may be doped), a metal gate, the like, or combinations of the above. The first dielectric layer 14 and the gate electrode 16 are formed by any suitable processes such as thermal oxidation, chemical vapor deposition (CVD), physical vapor deposition (PVD), the like, and combinations of the above. A skilled artisan should recognize that the source region 18 and the drain region 20 may be switched so that the source region 18 is to the right of the gate electrode 16 and the drain region 20 is to the left of the gate electrode 16. In one embodiment, at this point in the processing there has been no doping to form source and drain regions in the source region 18 or the drain region 20. In other words, no extensions or halo implants have occurred.

**[0012]** The workpiece 10 in FIG. 1 is being implanted with an oxidation enhancing species 22. As will be better understood after further explanation, the oxidation enhancing species 22 is being implanted into portions of the semiconductor substrate 12 and the gate electrode 16 so that oxidation growth will be increased in these regions. Although not shown, a mask, such as a photoresist, may be formed over the workpiece 10 (and over the semiconductor substrate 12) and be patterned to expose the areas where the oxidation enhancing species 22 are to be located within the workpiece 10. If a mask is used, the

implantation may occur perpendicular to the workpiece 10 or at a tilt so that the angle between the semiconductor substrate 12 and the implantation is less than ninety degrees. If a mask is not used or if the mask is patterned to expose both the source region 18 and the drain region 20, a tilt is preferred so that a shadow region 24 can be formed in one of the regions, 5 which in a preferred embodiment is the source region 18. The shadow region 24 is a region where none of the oxidation enhancing species 22 will travel so that areas around the shadow region 24 will not be implanted with the oxidation enhancing species 22. In the embodiment illustrated in FIG. 1, the shadow region 24 prevents oxidation enhancing species 22 from being implanted into portions of the first dielectric layer 14, the gate electrode 16, and the 10 semiconductor substrate 12, as will be better understood after discussing FIG. 2. In one embodiment, the tilt is approximately 5 to 30 degrees. However, the most desirable tilt will depend on the height and density of the gate electrode 16. The taller and more dense the gate electrode 16, it is desirable to use a lower tilt angle.

[0013] The oxidation enhancing species 22 may be oxygen, germanium, fluorine, 15 chlorine, the like or combinations of the above. The energy used is desirably low enough so that the oxidation enhancing species 22 reaches the desired depth in the semiconductor substrate 12 and the gate electrode 16. In one embodiment, the desired depth is approximately 5 to 10 nm. In one embodiment, the energy is between approximately 2 and 8 keV. The actual energy chosen depends on the desired depth, which can vary based on the 20 dimensions of the features, other processing that may occur, and the species used. Furthermore, any dose can be used. In one embodiment, a dose of  $1E15/cm^2$  is used. In a preferred embodiment, germanium is used as the oxidation enhancing species 22 at a 5 keV and a dosage of  $1E15/cm^2$ . In one embodiment, it is desirable to use fluorine for an N-type semiconductor device and germanium for a P-type semiconductor device.

[0014] Figure 2 shows the resulting implanted oxidation enhanced regions 26 after 25 performing an implantation of an oxidation enhancing species 22 at a tilt, in accordance with the embodiment illustrated in FIG. 1. The oxidation enhanced regions 26 are present in the drain region 20, the top surface of the gate electrode 16, and a first side of the gate electrode 16. The oxidation enhanced regions 26 are also present in a first portion of the source region 30 18 and a first portion of a second side of the gate electrode 16. The absence of the oxidation enhanced region 26 in a second portion of the source region 18 and a second portion of the second side of the gate electrode 16 is due to the shadow region. Thus, the area that is under

and adjacent the second side of the gate electrode and a portion of the area of the gate electrode that is adjacent the second side of the gate electrode do not include the oxidation enhanced region 26. In contrast, the portion of the area under and adjacent the first side of the gate electrode and a portion of the area of the gate electrode that is adjacent the first side of the gate electrode does include the oxidation enhanced region 26.

5 [0015] As shown in FIG. 3, After forming the oxidation enhanced region 26, portions of the semiconductor substrate 12, and optionally portions of the gate electrode 16, are converted to a second dielectric layer 40. Portions of the gate electrode 16 may not be converted if the material chosen for the gate electrode 16 does not oxidize when exposed to 10 the environment used to oxidize portions of the semiconductor substrate 12. Hence, the resulting dielectric material depends on the material used for the gate electrode 16 and the semiconductor substrate 12. In an embodiment, where the gate electrode 16 and the semiconductor substrate 12 include silicon, the second dielectric layer 40 is silicon dioxide. 15 The second dielectric layer 40 may or may not be the same material used for the first dielectric layer 14.

20 [0016] In one embodiment, the conversion occurs by annealing the workpiece 10. For example, the conversion can occur by thermal oxidation in a dry oxygen environment at a temperature between approximately 700 and 1,000 degrees Celsius. An ambient of nitrogen and possibly oxygen may be used. The time for the thermal oxidation will vary based on the 25 temperature used. For example, the duration of the thermal oxidation may be between 10 minutes to 2 hours. However, if the temperature of the thermal oxidation is approximately 1,000 degrees Celsius the duration of the thermal oxidation can be short, such as 10 minutes. As the temperature decreases, the duration will increase. However, the second dielectric layer 40 can be formed by any suitable method, such as other oxidation processes besides thermal oxidation.

30 [0017] As illustrated in FIG. 3 the portions of the second dielectric layer 40 that are formed in the oxidation enhanced region 26 of the gate electrode 16 and the semiconductor substrate 12 have a thickness greater than that of the rest of the second dielectric layer 40. If portions of the gate electrode 16 are converted to the second dielectric layer 40, the thickness of the second dielectric layer 40 on the second side of the gate electrode 16 is thinner than that of the second dielectric layer 40 on the first side of the gate electrode 16 due to the presence of the oxidation enhancement region 26 on the first side of the gate electrode 16 and

the lack of the oxidation enhancement region 26 in areas adjacent the second side of the gate electrode 16.

**[0018]** Due to the oxidation enhanced regions 26, region 46 in the source region 18 is thicker than region 48 in the drain region 20. At the intersection of the gate electrode 16,

5 the first dielectric layer 14, and the semiconductor substrate 12 that is adjacent the first side of the gate electrode 16 is a first dielectric area 44. At the intersection of the gate electrode 16, the first dielectric layer 14, and the semiconductor substrate 12 that is adjacent the second side of the gate electrode 16 is a second dielectric area 42. The first dielectric area 44 and the second dielectric area 42 both form bird's beaks, which is a name given to dielectric areas

10 that have a bird beak shape, such as the bird's beaks that are created during LOCOS (local oxidation) processing to form isolation regions. Due to the absence of the oxidation enhancement region 26 in and near the second dielectric area 42, the second dielectric area 42 is smaller than the first dielectric area 44. In one embodiment, the thickness of the second dielectric area 42 is approximately  $\frac{1}{2}$  that of the first dielectric area 44. In one embodiment,

15 the thickness of the second dielectric area 42 is approximately 2 nm and the thickness of the first dielectric area 44 is approximately 4 nm. As shown in FIG. 3, a third dielectric area lies between the first dielectric area 44 and the second dielectric area 42. The third dielectric area is thinner than both the first dielectric area 44 and the second dielectric area 42 because it was not substantially oxidized during the conversion processing. The third dielectric area is a

20 portion of the first dielectric layer 14. Thus, the gate dielectric, which is the dielectric under the gate electrode 16, includes the first dielectric area 44, the second dielectric area 42, and a portion of the first dielectric layer 14. Thus, the gate dielectric is a dielectric with asymmetric bird beak's or dielectric regions, where the dielectric region at one end is thicker than the dielectric region at the other end. The first dielectric layer 14 may be the same

25 material as the second dielectric layer 40. Alternatively, different materials may be used. In one embodiment, the gate dielectric is made of two dielectrics where the ends are the same material and the area between the ends is a different material; in addition, the ends are asymmetric dielectric regions, where the dielectric region at one end is thicker than the dielectric region at the other end.

30 **[0019]** The presence of the first dielectric area 44 and the second dielectric area 42 as part of the gate dielectric reduces delay and reduced capacitance in the semiconductor device without degradation in current. As the width of the first dielectric area 44 and the second

dielectric area 42 increase, the drive current degrades. Since the thickness of the first dielectric area 44 is greater than that of the first dielectric layer 14 that forms the gate dielectric, the inversion layer that is formed during the functioning of the semiconductor device is pinched-off near the drain the saturation region making the saturation drain current 5 insensitive to gate-drain overlap. The gate-drain overlap capacitance improves when the thickness of the first dielectric area 44 increases. The maximum steep improvement that may be able to be obtained is approximately 3.4%.

[0020] The first dielectric area 44 and the second dielectric area 42 may be entirely under the gate electrode or the gate electrode 16 and the second dielectric layer 40 10 surrounding the gate electrode 16, but some of these areas may extend outside the areas covered by the gate electrode 16 and the second dielectric layer 40. Regardless, at least part of the first dielectric area 44 and the second dielectric area 42 will be under the gate electrode 16.

[0021] After forming the second dielectric layer 40, conventional processing is continued 15 to form a semiconductor device, as shown in FIG. 4. First, a source extension 50 and a drain extension 52 are formed in the source region 18 and the drain region 20, respectively. After forming the source extension 50 and the drain extension 52, a third dielectric layer, such as silicon nitride, is formed, for example by CVD, and patterned to form spacers 54. Next, a deep source region 56 is formed in the source region 18 and a deep drain region 58 is formed 20 in the drain region 20. Portions of the second dielectric layer 40 may be removed to form the fourth dielectric 49 and the fifth dielectric 43 either when the spacers 54 are formed or after forming the deep source region 56 and the deep drain region 58. The fourth dielectric 49 is thinner than the fifth dielectric 43 because more oxidation enhancing species was present in the area that was converted into the fifth dielectric 43 than in the area that was converted into 25 the fourth dielectric 49.

[0022] Next, silicide 60 is formed over the deep source region 56 and the deep drain region 58. In addition, if the gate electrode 16 includes silicon, silicide may be formed over the gate electrode 16. Next, an interlevel dielectric layer 64 is formed over the workpiece 10 and patterned to form openings, which are later filled with conductive material(s) to form 30 contacts 62. In the cross-section shown in FIG. 4, the contacts 62 are formed in the source region 18 and the drain region 20. In addition, a contact (not shown) is formed and coupled to the gate electrode 16.

[0023] In the embodiment illustrated in FIGs. 1-4, an oxidation enhancing species was implanted. Alternatively, an oxidation reduction species is implanted. In another embodiment, the oxidation reduction species may be implanted in addition to the oxidation enhancing species, as illustrated in FIGs. 5 and 6. In other words, co-implantation of an oxidation enhancing species and an oxidation reduction species is performed in one embodiment.

[0024] As shown in FIG. 5 an oxidation reduction species 28, such as nitrogen, is implanted into the workpiece 10 after forming oxidation enhancement region 26. The oxidation reduction species 28 is implanted into portions of the semiconductor substrate 12 and the gate electrode 16 so that oxidation growth will be inhibited in these regions. Although not shown, a mask, such as photoresist, may be formed over the workpiece 10 (and over the semiconductor substrate 12) and be patterned to expose the areas where the oxidation reduction species 28 are to be implanted. If a mask is used, the implantation may occur perpendicular to the workpiece 10 or at a tilt so that the angle between the semiconductor substrate 12 and the implantation is less than ninety degrees. If a mask is not used or if the mask is patterned to expose both the source region 18 and the drain region 20, a tilt is preferred so that a shadow region 30 can be formed in one of the regions, which in a preferred embodiment is the drain region 20. The shadow region 30 is similar to the shadow region 24 of FIG. 1, because it is a region where none of the oxidation reduction species 28 will travel so that areas around the shadow region 30 will not be implanted with the oxidation reduction species 28. In the embodiment illustrated in FIG. 5 the shadow region 30 prevents oxidation reduction species 28 from being implanted into portions of the first dielectric layer 14, the gate electrode 16, and the semiconductor substrate 12, as will be better understood after discussing FIG. 6. In one embodiment, the tilt is approximately 5 to 30 degrees. However, the most desirable tilt will depend on the height and density of the gate electrode 16. The taller and more dense the gate electrode 16, it is desirable to use a lower tilt angle.

[0025] In one embodiment, the oxidation reduction species 28 is nitrogen. The energy used is desirably low enough so that the oxidation reduction species 28 reaches the desired depth in the semiconductor substrate 12 and the gate electrode 16. In one embodiment, the desired depth is between approximately 5 and 10 nm. In one embodiment, the energy is between approximately 1 and 3 keV. The energy chosen depends on the desired thickness, which can vary based on the dimensions of the features, other processing that may occur, and

the species used. Furthermore, any dose can be used. In one embodiment, a dose of 1E15/cm<sup>2</sup> is used.

[0026] FIG. 6 shows the resulting implanted oxidation enhancement regions 26, oxidation reducing regions 32, and the combined regions 34 that include both the oxidation reducing and enhancing species after performing an implantation of an oxidation reduction species 28 and the oxidation enhancing species 22 at a tilt. The oxidation enhanced regions 26 are present in the areas that were exposed to the oxidation enhancing species and were near the shadow region 30. The oxidation enhanced regions 26 are near the first side of the gate electrode 16. The oxidation reducing regions 32 are area that were exposed to the oxidation reducing species and were near the shadow region 24. The oxidation reducing regions are near the first side of the gate electrode 16. The combined regions 34 are in the drain region 20 at a distance separated from the are underlying the gate electrode 16, in the source region 18 at a distance separated from the are underlying the gate electrode 16, and in the top most area of the gate electrode 16.

[0027] After forming the oxidation reducing regions 32, portions of the semiconductor substrate 12, and optionally portions of the gate electrode 16, are converted to dielectric layer, using any process discussed in regards with FIG. 3. The oxidation reducing regions 32 will inhibit the growth of a dielectric and the oxidation enhanced region 26 will increase dielectric growth. The effect of the combined regions 34 on oxide growth will depend on the relative amounts of the oxidation reducing species and the oxidation enhancing species. The combined regions 34 may inhibit or increase dielectric growth. Instead, the effect of the oxidation reducing species and the oxidation enhancing species may cancel each other and therefore, the combined regions 34 will behave the same as the material would without any of oxidation reducing species and the oxidation enhancing species. Hence, the presence of the combined regions 34 may not affect the dielectric growth. After forming the dielectric layer, additional processing discussed with respect to FIG. 4 is performed.

[0028] In one embodiment, method for forming a semiconductor device includes forming a semiconductor substrate, forming a gate electrode over the semiconductor substrate having a first side and a second side, forming a gate dielectric under the gate electrode, wherein the gate dielectric has a first area under the gate electrode and adjacent the first side of the gate electrode, a second area under the gate electrode and adjacent the second side of the gate electrode, and a third area under the gate electrode that is between the first area and

the second area, wherein the first area is thinner than the second area, and the third area is thinner than the first area and is thinner than the second area. In one embodiment, forming the gate dielectric under the gate electrode further includes forming a first dielectric layer, implanting an oxidation enhancing species into the semiconductor substrate to form oxidation enhancement regions, and oxidizing the oxidation enhancement regions; in one embodiment, implanting the oxidation enhancing species further includes implanting the oxidation enhancing species into the gate electrode to form oxidation enhancement regions; and in one embodiment, the implanting is performed at a tilt. In one embodiment, forming the gate dielectric under the gate electrode further includes forming a first dielectric layer, implanting an oxidation reduction species into the semiconductor substrate to form oxidation reducing regions, and oxidizing the semiconductor substrate. In one embodiment, implanting the oxidation enhancing species further includes implanting the oxidation reduction species into the gate electrode to form oxidation reducing regions, and in one embodiment, implanting is performed at a tilt. In one embodiment, forming the gate dielectric under the gate electrode further includes forming a first dielectric layer, implanting an oxidation enhancing species into the semiconductor substrate to form oxidation enhancement regions, implanting an oxidation reduction species into the semiconductor substrate to form oxidation reducing regions, and oxidizing the semiconductor substrate, wherein oxidizing includes forming a dielectric in the oxidation enhancement regions. In one embodiment, the method also includes forming a source extension region and a drain extension region after the forming the gate dielectric, wherein the source extension region is deeper than the drain extension region. In one embodiment, the method also includes forming a first spacer adjacent the first side of the gate electrode and a second spacer adjacent the second side of the gate electrode after the forming the gate dielectric

[0029] In one embodiment, a method for forming a semiconductor device includes providing semiconductor substrate, forming a dielectric layer over the semiconductor substrate, forming a gate electrode over the dielectric layer, wherein the gate electrode has a first side and a second side opposite the first side, implanting an oxidation enhancing species into the first side of the gate electrode and a first area of the semiconductor substrate, wherein the first area is under the gate electrode and adjacent the first side of the gate electrode, converting the first area to a first dielectric and a second area of the semiconductor substrate, wherein the second area is under the gate electrode and adjacent the second side of the gate electrode, to a second dielectric, wherein the thickness of the first dielectric is greater than the

thickness of the second dielectric. In one embodiment, converting includes annealing the semiconductor substrate. In one embodiment, implanting includes implanting at least a species selected from the group consisting of germanium, oxygen, fluorine, and chlorine. In one embodiment, the method also includes implanting an oxidation reduction species into the 5 second area. In one embodiment, the implanting the oxidation reduction species includes implanting nitrogen. In one embodiment, the method also includes forming a source extension region and a drain extension region after the converting, the first area and the second area, wherein the source extension region is deeper than the drain extension region. In one embodiment, the method also includes forming a first spacer adjacent the first side of 10 the gate electrode and a second spacer adjacent the second side of the gate electrode after the converting. In one embodiment, implanting is performed at a tilt.

**[0030]** In one embodiment, semiconductor device includes a semiconductor substrate, a gate electrode over the semiconductor substrate having a first side and a second side, and a gate dielectric under the gate electrode, wherein the gate dielectric has a first area under the 15 gate electrode and adjacent the first side of the gate electrode, a second area under the gate electrode and adjacent the second side of the gate electrode, and a third area under the gate electrode that is between the first area and the second area, wherein the first area is thinner than the second area, and the third are is thinner than the first area and is thinner than the second area. In one embodiment, the first side of the gate electrode includes a first dielectric 20 and second side includes a second dielectric, wherein the second dielectric is thicker than the first dielectric. In one embodiment, the first area is at least approximately 2 times the thickness of the second area. In one embodiment, the semiconductor device also includes extension regions wherein region under first area is deeper than region under the second area. In one embodiment, the first area is the source region and the second area is the drain region. 25 In one embodiment, the first area is the drain region and the second area is the source region.

**[0031]** By now it should be appreciated that there has been provided a structure in which a bird's beak dielectric is formed thicker on one side of a gate dielectric, such as the drain side of a semiconductor device. Alternatively, the thicker dielectric can be on the source side. In addition, a method to make such as structure is taught by performing an oxidation 30 enhancing implant, an oxidation reducing implant, or both. In one embodiment, angled implants that allow shadow on one side and oxidation enhancing or reducing species on the other are used. This method is cost effective to implement since a maskless implant

procedure or a process using only one additional mask is used. The resulting structure offers enhanced performance, such as reduced delay and reduced capacitance (both  $C_{gd}$  and Miller capacitance) without degradation in current. In addition, having a thick oxide at the point of the highest field (e.g., the drain region next to the gate electrode) will reduce leakage and

5 improve reliability.

**[0032]** In the foregoing specification, the invention has been described with reference to specific embodiments. However, one of ordinary skill in the art appreciates that various modifications and changes can be made without departing from the scope of the present invention as set forth in the claims below. For example, a different semiconductor device

10 than that shown in the figures may be used. For example, the semiconductor device can be a FinFET or a nonvolatile memory (NVM) device.

**[0033]** Accordingly, the specification and figures are to be regarded in an illustrative rather than a restrictive sense, and all such modifications are intended to be included within the scope of the present invention.

**[0034]** Moreover, the terms “front”, “back”, “top”, “bottom”, “over”, “under” and the like in the description and in the claims, if any, are used for descriptive purposes and not necessarily for describing permanent relative positions. It is understood that the terms so used are interchangeable under appropriate circumstances such that the embodiments of the invention described herein are, for example, capable of operation in other orientations than

20 those illustrated or otherwise described herein.

**[0035]** Benefits, other advantages, and solutions to problems have been described above with regard to specific embodiments. However, the benefits, advantages, solutions to problems, and any element(s) that may cause any benefit, advantage, or solution to occur or become more pronounced are not to be construed as a critical, required, or essential feature or

25 element of any or all the claims. As used herein, the terms “comprises,” “comprising,” or any other variation thereof, are intended to cover a non-exclusive inclusion, such that a process, method, article, or apparatus that comprises a list of elements does not include only those elements but may include other elements not expressly listed or inherent to such process, method, article, or apparatus. The terms “a” or “an”, as used herein, are defined as one or

30 more than one.

CLAIMS

What is claimed is:

1. A method for forming a semiconductor device, the method comprising:

- 5 forming a semiconductor substrate;

- forming a gate electrode over the semiconductor substrate having a first side and a second side; and

- 10 forming a gate dielectric under the gate electrode, wherein the gate dielectric has a first area under the gate electrode and adjacent the first side of the gate electrode; a second area under the gate electrode and adjacent the second side of the gate electrode; and a third area under the gate electrode that is between the first area and the second area; wherein the first area is thinner than the second area, and the third area is thinner than the first area and is thinner than the second area.

2. The method of claim 1 wherein the forming the gate dielectric under the gate electrode further comprises:

- 15 forming a first dielectric layer;

- implanting an oxidation enhancing species into the semiconductor substrate to form oxidation enhancement regions; and

- 20 oxidizing the oxidation enhancement regions.

3. The method of claim 2, wherein the implanting the oxidation enhancing species further comprises implanting the oxidation enhancing species into the gate electrode to form oxidation enhancement regions.

- 25 4. The method of claim 2, wherein the implanting is performed at a tilt.

5. The method of claim 1 wherein the forming the gate dielectric under the gate electrode further comprises:

- 20 forming a first dielectric layer;

- 30 implanting an oxidation reduction species into the semiconductor substrate to form oxidation reducing regions; and

- oxidizing the semiconductor substrate.

6. The method of claim 5, wherein the implanting the oxidation enhancing species further comprises implanting the oxidation reduction species into the gate electrode to form oxidation reducing regions.

5

7. The method of claim 5, wherein the implanting is performed at a tilt.

8. The method of claim 1 wherein the forming the gate dielectric under the gate electrode further comprises:

10 forming a first dielectric layer;

implanting an oxidation enhancing species into the semiconductor substrate to form oxidation enhancement regions;

implanting an oxidation reduction species into the semiconductor substrate to form oxidation reducing regions; and

15 oxidizing the semiconductor substrate, wherein oxidizing comprises forming a dielectric in the oxidation enhancement regions.

9. The method of claim 1, further comprising:

20 forming a source extension region and a drain extension region after the forming the gate dielectric, wherein the source extension region is deeper than the drain extension region.

10. The method of claim 1, further comprising:

forming a first spacer adjacent the first side of the gate electrode and a second spacer adjacent the second side of the gate electrode after the forming the gate dielectric

25

11. A method for forming a semiconductor device, the method comprising:

providing a semiconductor substrate;

forming a dielectric layer over the semiconductor substrate;

forming a gate electrode over the dielectric layer, wherein the gate electrode has a first

30 side and a second side opposite the first side;

implanting an oxidation enhancing species into the first side of the gate electrode and a first area of the semiconductor substrate, wherein the first area is under the gate electrode and adjacent the first side of the gate electrode; and

converting the first area to a first dielectric and a second area of the semiconductor substrate, wherein the second area is under the gate electrode and adjacent the second side of the gate electrode, to a second dielectric, wherein the thickness of the first dielectric is greater than the thickness of the second dielectric.

5

12. The method of claim 11, wherein the converting comprises annealing the semiconductor substrate.

13. The method of claim 11, wherein the implanting comprises implanting at least a species 10 selected from the group consisting of germanium, oxygen, fluorine, and chlorine.

14. The method of claim 11, further comprises implanting an oxidation reduction species into the second area.

15. The method of claim 14, wherein the implanting the oxidation reduction species comprises implanting nitrogen.

16. The method of claim 11, further comprising:

20 forming a source extension region and a drain extension region after the converting, the first area and the second area, wherein the source extension region is deeper than the drain extension region.

17. The method of claim 11, further comprising:

25 forming a first spacer adjacent the first side of the gate electrode and a second spacer adjacent the second side of the gate electrode after the converting.

18. The method of claim 11, wherein the implanting is performed at a tilt.

19. A semiconductor device comprising:

30 a semiconductor substrate;

a gate electrode over the semiconductor substrate having a first side and a second side; and

a gate dielectric under the gate electrode, wherein the gate dielectric has a first area under the gate electrode and adjacent the first side of the gate electrode; a second area under

the gate electrode and adjacent the second side of the gate electrode; and a third area under the gate electrode that is between the first area and the second area; wherein the first area is thinner than the second area, and the third area is thinner than the first area and is thinner than the second area.

5

20. The semiconductor device of claim 19, wherein the first side of the gate electrode comprises a first dielectric and second side comprises a second dielectric, wherein the second dielectric is thicker than the first dielectric.

1/3

*FIG. 1* <sup>10</sup>

*FIG. 2* <sup>10</sup>

2/3

*FIG. 3* <sup>10</sup>

*FIG. 4* <sup>10</sup>

3/3

*FIG. 5*  $\frac{10}{10}$

*FIG. 6*  $\frac{10}{10}$