RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication :

2 517 494

(A n'utiliser que pour les

commandes de reproduction).

A1

**DEMANDE

DE BREVET D'INVENTION**

(21)

**N° 81 22273**

(54) Dispositif de correction automatique d'intermodulation produite par un amplificateur de signaux haute fréquence dans un émetteur à bande latérale unique.

(51) Classification internationale (Int. Cl. 3). H 03 F 3/189; H 03 G 1/00.

(22) Date de dépôt..... 27 novembre 1981.

(33) (32) (31) Priorité revendiquée :

(41) Date de la mise à la disposition du public de la demande ..... B.O.P.I. — « Listes » n° 22 du 3-6-1983.

(71) Déposant : THOMSON-CSF, société anonyme. — FR.

(72) Invention de : Daniel Gaudin et Jacques Viaud.

(73) Titulaire : *Idem* (71)

(74) Mandataire : P. Guilguet, Thomson-CSF, SCPI,

173, bd Haussmann, 75360 Paris Cedex 08.

DISPOSITIF DE CORRECTION AUTOMATIQUE D'INTERMODULATION

PRODUITE PAR UN AMPLIFICATEUR DE SIGNAUX HAUTE

FREQUENCE DANS UN EMETTEUR A BANDE LATERALE UNIQUE

La présente invention concerne un dispositif de correction automatique d'intermodulation produite par un amplificateur de signaux haute fréquence dans un émetteur à bande latérale unique (BLU) régulé en niveau crête et présentant des non linéarités d'amplitudes.

La non linéarité d'un amplificateur provoque, lorsqu'il est excité simultanément par plusieurs signaux de fréquences différentes, des signaux parasites appelés produits d'intermodulation.

Lorsque les signaux haute fréquence à amplifier sont des signaux modulés, le phénomène d'intermodulation se traduit alors, en dehors de la bande de modulation, par une perturbation des communications utilisant des canaux voisins, et dans la bande de modulation, par une distorsion phonique et surtout par un accroissement du taux d'erreur en cas de transmission numérique multiporteuse.

On a depuis longtemps essayé de minimiser les conséquences du phénomène de non linéarité. Ainsi, on a pensé à disposer en amont de l'amplificateur, un précorrecteur ayant une fonction de transfert complémentaire de celle de l'amplificateur. Mais, étant données les évolutions des non linéarités d'un amplificateur suivant ses conditions d'utilisation (fréquence, puissance et vieillissement de ses composants) il s'avère nécessaire de recaler fréquemment le précorrecteur associé à cet amplificateur.

On a alors pensé à automatiser ces réglages en recourant notamment à un microprocesseur qui en fonction de l'analyse qu'il fait du signal amplifié, décide d'agir de telle ou telle manière sur le réglage du précorrecteur.

Un tel système est décrit dans la demande de brevet français n° 78 36 488 déposée au nom de la demanderesse. Toutefois, dans ce système, le précorrecteur est du type décrit précédemment c'est-à-dire ayant une fonction de transfert complémentaire de celle de l'amplificateur à corriger, c'est-à-dire encore permettant de remédier globalement au phéno-

mène de non linéarité. Or ce précorrecteur présente une grande complexité de réalisation et de mise au point, qui se traduit également par une grande complexité des algorithmes de fonctionnement du microprocesseur. Cette complexité est jugée injustifiée lorsqu'on vise 5 seulement, comme cela est le cas dans la présente demande de brevet, à corriger les produits d'intermodulation, et plus particulièrement les produits d'intermodulation d'ordres impairs, seuls générateurs des produits d'intermodulation au voisinage des fréquences d'émission.

Dans cette optique, un précorrecteur de produits d'intermodulation 10 d'ordres impairs, présentant une réalisation et une mise au point très simplifiées, a fait l'objet de la demande de brevet français n° 81 10 451 déposée au nom de la demanderesse.

La présente invention vise à automatiser les réglages d'un tel précorrecteur de produits d'intermodulation en recourant à l'analyse par 15 un microprocesseur, de l'amplitude des raies d'intermodulation d'ordres impairs mesurée par un dispositif de mesure d'intermodulation.

Selon l'invention, le dispositif de correction automatique d'intermodulation produite par un amplificateur de signaux haute fréquence dans un émetteur à bande latérale unique régulé en niveau crête et 20 présentant des non linéarités d'amplitude comporte premièrement, en amont de l'amplificateur, un précorrecteur d'intermodulation apte à élaborer, à partir du signal à amplifier, des signaux de correction, d'amplitude réglable, aux fréquences des produits d'intermodulation d'ordres impairs, ce précorrecteur fournissant le signal d'entrée de 25 l'amplificateur, le produit des fonctions de transfert du précorrecteur d'intermodulation et de l'amplificateur ne donnant pas nécessairement une fonction de transfert linéaire, deuxièmement, en aval de l'amplificateur, un dispositif de mesure de l'amplitude des produits d'intermodulation d'ordres impairs produits par l'amplificateur, troisièmement un micro- 30 processeur apte à analyser l'amplitude des produits d'intermodulation d'ordres impairs mesurée par le dispositif de mesure d'intermodulation et à commander en conséquence le précorrecteur d'intermodulation de manière à réduire l'amplitude des produits d'intermodulation d'ordres impairs, et quatrièmement des moyens pour alimenter l'amplificateur soit

au moyen d'un signal de test constitué de la somme de deux tons haute fréquence, soit au moyen du signal haute fréquence à amplifier, suivant que l'on est ou non dans une phase de correction de l'intermodulation.

D'autres objets et caractéristiques de l'invention apparaîtront plus 5 clairement à la lecture de la description suivante d'exemples de réalisation, ladite description étant faite en relation avec les dessins ci-annexés dans lesquels :

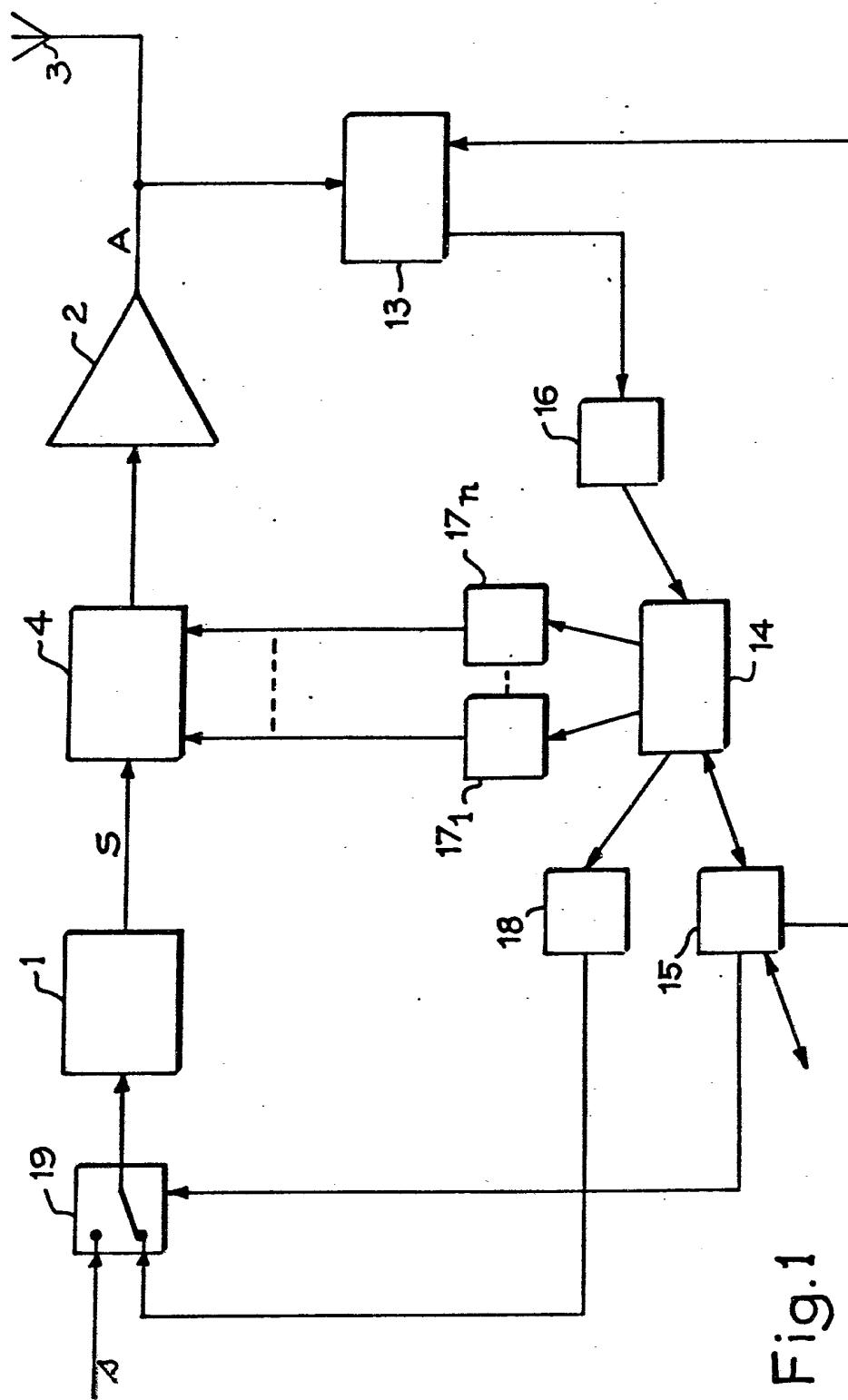

- la figure 1 est un schéma d'un dispositif de correction automatique d'intermodulation conforme à l'invention ;

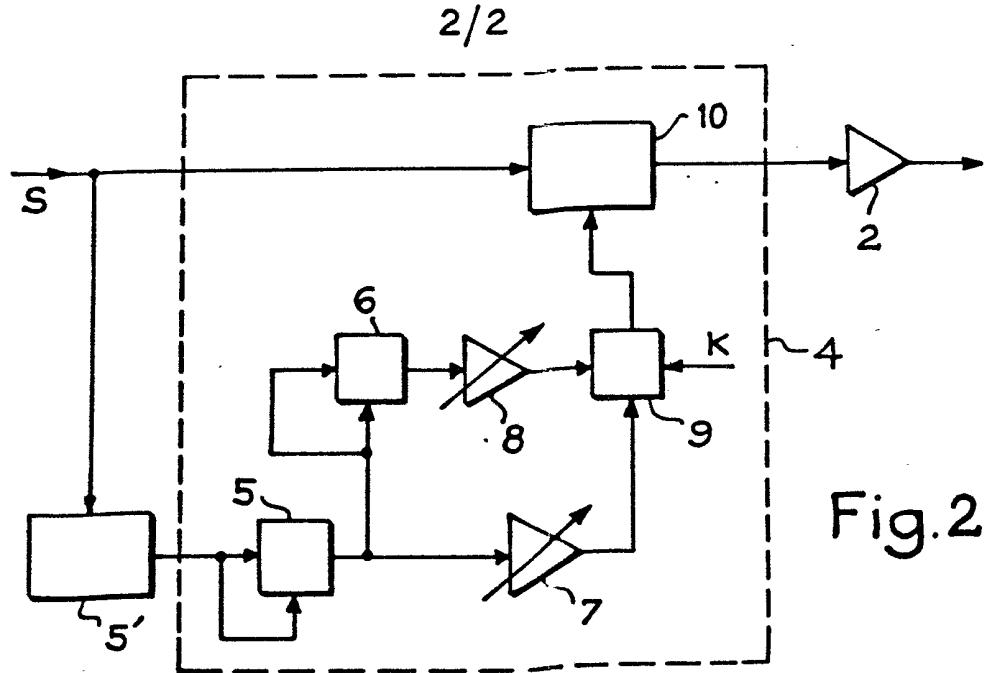

- 10 - la figure 2 est un schéma d'une première variante de réalisation du précorrecteur d'intermodulation entrant dans un dispositif de correction automatique d'intermodulation conforme à l'invention ;

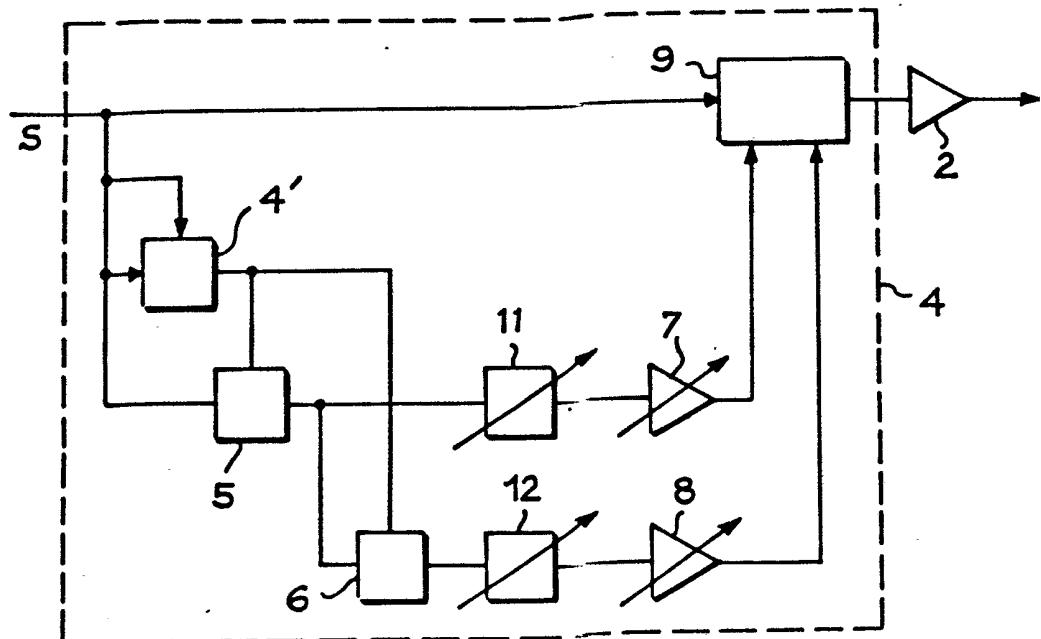

- la figure 3 est un schéma d'une deuxième variante de réalisation du précorrecteur d'intermodulation entrant dans un dispositif de correction 15 automatique d'intermodulation conforme à l'invention ;

Des éléments identiques représentés sur des figures différentes portent des références identiques.

Sur la figure 1 on a représenté une chaîne d'émission haute fréquence dans laquelle s'insère un amplificateur de signaux haute 20 fréquence destiné à être corrigé par un dispositif de correction automatique d'intermodulation conforme à l'invention.

Cette chaîne d'émission haute fréquence comporte un modulateur 25 1 apte à transformer un signal basse fréquence  $s$  en un signal haute fréquence  $S$  modulé suivant une modulation du type à bande latérale unique, un amplificateur haute fréquence 2 apte à assurer l'amplification du signal haute fréquence  $S$ , et une antenne d'émission 3 apte à assurer l'émission du signal haute fréquence amplifié A. Les éléments 1, 2 et 3 ne constituent pas l'objet de la présente invention et ne seront donc pas décrits de manière plus détaillée.

Entre le modulateur 1 et l'amplificateur 2 est interposé un précorrecteur d'intermodulation 4 apte à élaborer, à partir du signal à amplifier, des signaux de correction, d'amplitude réglable, aux fréquences des produits d'intermodulation d'ordres impairs. Lorsque le signal à amplifier comporte deux tons de fréquences  $f_1$  et  $f_2$ , on entend par produits

d'intermodulation d'ordres impairs les raies du spectre du signal amplifié qui se situent aux fréquences  $nf_1 - (n-1)f_2$  et  $(n-1)f_1 - nf_2$ , où  $n$  est un nombre entier.

Une première variante de réalisation du précorrecteur d'intermodulation, dans laquelle le précorrecteur opère à partir de l'enveloppe du signal haute fréquence  $S$ , est représentée à la figure 2. A titre d'exemple, il s'agit d'un précorrecteur des produits d'intermodulation d'ordres 3 et 5, c'est-à-dire issus des termes de puissances égales à 3 et 5 de la fonction de transfert de l'amplificateur 2.

Le précorrecteur 4 comporte un premier multiplicateur 5 muni de deux entrées reliées à la sortie d'un détecteur 5' de l'enveloppe du signal haute fréquence  $S$ , et un second multiplicateur 6 muni de deux entrées reliées à la sortie du premier multiplicateur 5. Le précorrecteur 4 comporte également un premier amplificateur à gain réglable 7, muni d'une entrée reliée à la sortie du premier multiplicateur 5, et un second amplificateur à gain réglable 8, muni d'une entrée reliée à la sortie du second multiplicateur 6. Les amplificateurs 7 et 8 sont des amplificateurs linéaires, par exemple des amplificateurs opérationnels bouclés à l'aide d'une résistance.

Le précorrecteur 4 comporte également un circuit sommateur 9 muni d'une première entrée reliée à la sortie de l'amplificateur 7, d'une deuxième entrée reliée à la sortie de l'amplificateur 8 et d'une troisième entrée destinée à recevoir une valeur constante  $K$  déterminée par l'opérateur en fonction du point de fonctionnement désiré. Le circuit sommateur 9 est destiné à effectuer des additions ou des soustractions entre les valeurs disponibles sur chacune de ses entrées, le choix entre addition et soustraction relativement à chacune de ces valeurs étant déterminé par l'opérateur.

Plus généralement, pour la précorrection de produits d'intermodulation d'ordres impairs quelconques, le précorrecteur 4 comporte  $N$  multiplicateurs dont le premier est muni de deux entrées reliées à la sortie du détecteur d'enveloppe, dont le deuxième est muni de deux entrées reliées à la sortie du premier et dont le  $n^{\text{ième}}$  ( $n$  étant un entier compris entre 3 et  $N$ ) est muni de deux entrées reliées respectivement à la sortie du premier et du  $(n-1)^{\text{ième}}$ ,  $N$  amplificateurs linéaires à gain réglable munis

chacun d'une entrée reliée à la sortie de l'un des N multiplieurs, et un circuit sommateur à N+1 entrées, dont N sont reliées aux sorties des amplificateurs linéaires à gain réglable, et dont la (N+1)<sup>ème</sup> est destinée à recevoir la valeur constante K.

5 Le précorrecteur 4 comporte également un mélangeur 10 muni d'une première entrée qui reçoit le signal haute fréquence S, d'une seconde entrée reliée à la sortie du circuit sommateur 9, et d'une sortie qui constitue la sortie du précorrecteur 4 et qui est reliée à l'entrée de l'amplificateur 2. Le mélangeur 10 est destiné à effectuer le produit des 10 signaux présents sur ses deux entrées.

Une seconde variante de réalisation du précorrecteur, dans laquelle le précorrecteur opère directement à partir du signal haute fréquence S est représentée à la figure 3.

A titre d'exemple il s'agit également d'un précorrecteur de produits 15 d'intermodulation d'ordres 3 et 5.

Le précorrecteur 4 comporte un premier multiplicateur 4<sup>1</sup> muni de deux entrées qui reçoivent le signal haute fréquence S, un deuxième multiplicateur 5 muni d'une entrée reliée à la sortie du premier multiplicateur 4<sup>1</sup> et d'une entrée destinée à recevoir le signal S, et un troisième multiplicateur 6 20 muni de deux entrées reliées respectivement à la sortie du premier et du deuxième multiplicateur. Le précorrecteur 4 comporte également deux amplificateurs à gain réglable 7 et 8 connectés respectivement aux sorties des multiplicateurs 5 et 6. Le précorrecteur 4 comporte également un circuit sommateur 9 muni d'une première entrée destinée à recevoir le signal 25 haute fréquence à amplifier, d'une deuxième entrée reliée à la sortie de l'amplificateur 7, et d'une troisième entrée reliée à la sortie de l'amplificateur 8. Le circuit sommateur 9 est également destiné à effectuer des additions ou des soustractions entre les valeurs disponibles sur chacune de ses entrées, le choix entre addition et soustraction relativement à 30 chacune de ces valeurs étant déterminé par l'opérateur. Le précorrecteur 4 comporte enfin deux déphasateurs variables 11 et 12 interposés respectivement entre le multiplicateur 5 et l'amplificateur 7, et entre le multiplicateur 6 et l'amplificateur 8.

Plus généralement, pour la précorrection de produits d'intermodu-

lation d'ordres impairs quelconques le précorrecteur 4 comporte premièrement N multiplicateurs, dont le premier est muni de deux entrées destinées à recevoir le signal haute fréquence à amplifier, dont le deuxième est muni d'une entrée destinée à recevoir le signal haute fréquence à amplifier et d'une entrée reliée à la sortie du premier, et dont le n<sup>ième</sup> (n étant un entier compris entre 3 et N) est muni d'une entrée reliée à la sortie du premier et du (n-1)<sup>ième</sup>, deuxièmement N-1 amplificateurs linéaires à gain réglable munis chacun d'une entrée reliée à la sortie de l'un des multiplicateurs de rang n supérieur à 1, troisièmement un circuit sommateur 9 muni de N entrées dont N-1 sont reliées aux sorties des amplificateurs linéaires à gain réglable et dont la N<sup>ième</sup> est destinée à recevoir le signal haute fréquence à amplifier, et quatrièmement N-1 déphasateurs variables interposés entre les sorties des N-1 multiplicateurs de rang n supérieur à 1 et les entrées des amplificateurs à gain réglable correspondants.

Le mode opératoire du précorrecteur d'intermodulation représenté à la figure 2 est le suivant. En agissant sur le réglage du gain des amplificateurs 7 et 8 et sur le réglage des signes à affecter aux signaux d'entrée du circuit sommateur 9, on contrôle l'amplitude et le signe de chacune des composantes de sortie du circuit sommateur 9. Le réglage se fait dans l'ordre décroissant des raies d'intermodulation à éliminer en observant à chaque étape du réglage l'évolution du signal de sortie de l'amplificateur 2. Il consiste d'abord à minimiser l'amplitude des raies d'intermodulation d'ordre 5 par action sur l'amplificateur linéaire à gain réglable 8, ce qui modifie également l'amplitude des raies d'intermodulation d'ordre 3. Il consiste ensuite à minimiser les nouvelles raies d'intermodulation d'ordre 3 par action sur l'amplificateur linéaire à gain réglable 7, ce qui joue un peu sur le niveau des fréquences du signal S, mais ceci n'est pas gênant. A la fin du réglage, le spectre du signal de sortie de l'amplificateur 2 comporte des raies d'intermodulation très affaiblies.

Le mode opératoire du précorrecteur d'intermodulation représenté à la figure 3 est semblable à celui du précorrecteur d'intermodulation représenté à la figure 2, à ceci près que l'on obtient directement en sortie

des différents multiplicateurs des raies correspondant aux différents produits d'intermodulation à corriger, contrairement au cas où le précorrecteur opère à partir de l'enveloppe, auquel cas on doit recourir à un mélangeur.

Par ailleurs, du fait que le précorrecteur d'intermodulation représenté à la figure 3 opère directement sur le signal haute fréquence, il est nécessaire d'insérer des déphasateurs variables, réglables par l'opérateur, entre les multiplicateurs et les amplificateurs à gain réglable, de manière à compenser les retards de phase que subit le signal dans les différents multiplicateurs et à établir ainsi un synchronisme des différents signaux d'entrée du circuit sommateur. Ce réglage se fait une fois pour toutes indépendamment de l'opération de correction de l'intermodulation.

On se reporte maintenant à la figure 1. Un dispositif 13 de mesure de l'amplitude des raies d'intermodulation d'ordres impairs est connecté en sortie de l'amplificateur 2. Cette mesure d'intermodulation peut être effectuée de manière connue, par exemple par retransposition en fréquence intermédiaire suivie d'un filtrage.

Un microprocesseur 14 est prévu entre le dispositif 13 de mesure d'intermodulation et le précorrecteur 4 d'intermodulation, de manière à automatiser les réglages du précorrecteur 4.

Le microprocesseur 14 est muni de premières entrées reliées à des premières sorties d'une interface logique avec l'extérieur 15 et de secondes entrées reliées aux sorties du dispositif de mesure d'intermodulation 13 via un convertisseur analogique numérique 16. Le dispositif de mesure d'intermodulation 13 est par ailleurs muni d'une entrée de commande destinée à sélectionner la raie d'intermodulation à mesurer. Cette entrée de commande est reliée à une seconde sortie de l'interface logique 15.

Le microprocesseur 14 est muni de premières sorties reliées à l'entrée de réglage d'un premier amplificateur à gain réglable du précorrecteur 4 via un convertisseur numérique analogique 17<sub>1</sub> --- etc, de n<sup>ièmes</sup> sorties reliées à l'entrée de réglage d'un n<sup>ième</sup> amplificateur à gain réglage du précorrecteur 4 via un convertisseur numérique analogique 17<sub>n</sub>.

Le microprocesseur 14 est également muni de sorties reliées aux

entrées d'un convertisseur numérique analogique 18 muni lui-même d'une sortie reliée à une première entrée de signal d'une porte analogique 19. La porte analogique 19 est par ailleurs munie d'une deuxième entrée de signal qui reçoit le signal basse fréquence, d'une sortie reliée à l'entrée du 5 modulateur 1 et d'une entrée de commande reliée à une troisième sortie de l'interface logique 15.

Le microprocesseur 14 est également muni de sorties reliées à des entrées de l'interface logique 15, l'interface logique 15 étant par ailleurs munie d'entrées et de sorties permettant un dialogue avec l'opérateur.

10 Le dispositif de correction automatique d'intermodulation représenté à la figure 1 fonctionne de la façon suivante.

Une opération de réglage du précorrecteur est déclenchée par décision de l'opérateur, et cette décision est transmise au microprocesseur 14 par l'intermédiaire de l'interface logique 15. Cet évènement 15 lance l'exécution d'un programme contenu dans la mémoire morte du microprocesseur, qui se traduit par les opérations suivantes. La porte analogique 19 est positionnée de telle sorte que la chaîne d'émission soit alimentée par un signal de test, généré par le microprocesseur 14, appliqué sur la première entrée de signal de la porte analogique 19, et 20 constitué de la somme de deux tons basse fréquence.

Ce microprocesseur sélectionne en sortie du dispositif de mesure d'intermodulation 13, par l'intermédiaire de l'interface logique 15, la raie d'intermodulation d'ordre le plus élevé, puis le signal appliqué sur l'entrée de réglage du précorrecteur correspondant à cet ordre est modifié jusqu'à 25 ce que l'amplitude de cette raie d'intermodulation soit inférieure à un seuil.

Le microprocesseur procéde de la même façon pour les autres raies d'intermodulation en les traitant par ordre décroissant.

Le réglage étant terminé, le microprocesseur 14 positionne la porte analogique 19 de telle sorte que la chaîne d'émission soit alimentée par le signal basse fréquence s, et maintient sur le précorrecteur 4 les coefficients de réglage trouvés et transmis par les convertisseurs 17<sub>1</sub> à 17<sub>n</sub>.

L'opérateur est averti du commencement et de la fin du réglage, de

même que de tout incident intervenant en cours de réglage, par l'intermédiaire de l'interface logique 15.

Par un choix judicieux des coefficients de réglage du précorrecteur utilisés à l'initialisation, c'est-à-dire avant toute mesure d'intermodulation, on peut réduire la durée de la phase de réglage. Pour cela il suffit de mémoriser les coefficients de réglage trouvés pour chaque état, et de démarrer le réglage avec les coefficients trouvés pour un état comparable.

REVENDICATIONS

1. Dispositif de correction automatique d'intermodulation produite par un amplificateur (2) de signaux haute fréquence dans un émetteur à bande latérale unique réglé en niveau crête et présentant des non linéarités d'amplitude, caractérisé en ce qu'il comporte premièrement, en 5 amont de l'amplificateur (2), un précorrecteur d'intermodulation (4) apte à élaborer, à partir du signal à amplifier, des signaux de correction, d'amplitude réglable, aux fréquences des produits d'intermodulation d'ordres impairs, ce précorrecteur (4) fournissant le signal d'entrée de l'amplificateur (1), le produit des fonctions de transfert du précorrecteur 10 d'intermodulation (4) et de l'amplificateur (2) ne donnant pas nécessairement une fonction de transfert linéaire, deuxièmement, en aval de l'amplificateur (2), un dispositif (13) de mesure de l'amplitude des produits d'intermodulation d'ordres impairs produits par l'amplificateur (2), troisièmement un microprocesseur (14) apte à analyser l'amplitude des produits 15 d'intermodulation d'ordres impairs mesurée par le dispositif de mesure d'intermodulation (13) et à commander en conséquence le précorrecteur d'intermodulation (4) de manière à réduire l'amplitude des produits d'intermodulation d'ordres impairs et quatrièmement des moyens (19) pour alimenter l'amplificateur (2) soit au moyen d'un signal de test constitué de 20 la somme de deux tons haute fréquence, soit au moyen du signal haute fréquence à amplifier, suivant que l'on est ou non dans une phase de correction de l'intermodulation.

2. Dispositif selon la revendication 1, caractérisé en ce que le précorrecteur d'intermodulation (4) comporte premièrement un détecteur 25 d'enveloppe (5) du signal à amplifier, deuxièmement N multiplicateurs (5,6), dont le premier est muni de deux entrées reliées à la sortie du détecteur d'enveloppe (5), dont le deuxième est muni de deux entrées reliées à la sortie du premier et dont le  $N^{\text{ième}}$  ( $n$  étant compris entre 3 et  $N$ ) est muni de deux entrées reliées respectivement à la sortie du premier et du 30  $(N-1)^{\text{ième}}$ , troisièmement  $N$  amplificateurs linéaires à gain réglable (7,8) munis chacun d'une entrée reliée à la sortie de l'un des  $N$  multiplicateurs, quatrièmement un circuit sommateur (9) muni de  $N+1$  entrées dont  $N$  sont

5 reliées aux sorties des amplificateurs linéaires à gain réglable, et dont la  $(N+1)^{\text{ième}}$  est destinée à recevoir une valeur constante réglable, et d'une sortie qui constitue la sortie du précorrecteur (4), le circuit sommateur (9) étant apte à fonctionner en additionneur ou en soustracteur relativement à chacune de ses entrées, et cinquièmement un mélangeur (10) muni d'une première entrée destinée à recevoir le signal d'entrée, d'une deuxième entrée reliée à la sortie du circuit sommateur (9), et d'une sortie reliée à l'entrée de l'amplificateur (2).

10 3. Dispositif selon la revendication 1, caractérisé en ce que le précorrecteur d'intermodulation (4) comporte premièrement N multiplicateurs (4', 5, 6), dont le premier est muni de deux entrées destinées à recevoir le signal à amplifier, dont le deuxième est muni d'une entrée destinée à recevoir le signal à amplifier et d'une entrée reliée à la sortie du premier, et dont le  $n^{\text{ième}}$  ( $n$  étant un entier compris entre 3 et  $N$ ) est muni de deux 15 entrées reliées respectivement à la sortie du premier et du  $(n-1)^{\text{ième}}$ , deuxièmement  $(N-1)$  amplificateurs linéaires à gain réglable munis chacun d'une entrée reliée à la sortie de l'un des multiplicateurs de rang  $n$  supérieur à 1, et troisièmement un circuit sommateur (9) muni de  $n$  entrées dont  $n-1$  sont reliées aux sorties des amplificateurs linéaires à gain réglable et dont 20 la  $N^{\text{ième}}$  est destinée à recevoir le signal haute fréquence à amplifier, et d'une sortie reliée à l'entrée de l'amplificateur (2).

1/2

Fig. 1

Fig. 2

Fig. 3