(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5532568号

(P5532568)

(45) 発行日 平成26年6月25日(2014.6.25)

(24) 登録日 平成26年5月9日(2014.5.9)

|                       |                 |

|-----------------------|-----------------|

| (51) Int.Cl.          | F 1             |

| G09F 9/30 (2006.01)   | GO9F 9/30 338   |

| G02F 1/1368 (2006.01) | GO2F 1/1368     |

| H01L 29/786 (2006.01) | H01L 29/78 616T |

| H01L 21/336 (2006.01) | H01L 29/78 619B |

|                       | H01L 29/78 616A |

請求項の数 3 (全 19 頁)

(21) 出願番号 特願2008-248539 (P2008-248539)

(22) 出願日 平成20年9月26日 (2008.9.26)

(65) 公開番号 特開2010-79038 (P2010-79038A)

(43) 公開日 平成22年4月8日 (2010.4.8)

審査請求日 平成23年8月4日 (2011.8.4)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100095728

弁理士 上柳 雅善

(74) 代理人 100107261

弁理士 須澤 修

(74) 代理人 100127661

弁理士 宮坂 一彦

(72) 発明者 茂筑 寛士

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

審査官 請園 信博

最終頁に続く

(54) 【発明の名称】電気光学装置及び電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

データ線と、

チャネル領域と、前記データ線に電気的に接続された第1のソースドレイン領域と、画素電極に電気的に接続された第2のソースドレイン領域と、前記第1のソースドレイン領域と前記チャネル領域との間に形成された第1の接合領域と、前記第2のソースドレイン領域と前記チャネル領域との間に形成された第2の接合領域とを有する半導体膜を含むトランジスタと、

前記半導体膜の延在する第1の方向と交差する第2の方向に沿って延在し、前記チャネル領域と重なる本体部と、該本体部から前記第1の方向に沿って延設され且つ前記半導体膜の第1の接合領域と重なる第1の延設部と、前記本体部から前記第1の方向とは反対側の第3の方向に沿って延設され且つ前記半導体膜の第2の接合領域と重なる第2の延設部とを有する遮光膜とを備え、

前記遮光膜の第1の延設部は、前記遮光膜の第2の延設部よりも幅が狭くなるように形成されており、

前記チャネル領域及び前記第2の接合領域は、それぞれ同一幅となるように形成されており、前記第1の接合領域は、前記遮光膜の第1の延設部と重なる領域において、前記チャネル領域側よりも前記第1のソースドレイン領域側が幅広に形成され、前記第1の接合領域の前記第1のソースドレイン領域側が、前記チャネル領域及び第2の接合領域よりも幅広に形成されている

ことを特徴とする電気光学装置。

【請求項 2】

前記遮光膜は、前記チャネル領域と重なるように設けられたゲート電極と電気的に接続されることを特徴とする請求項 1 に記載の電気光学装置。

【請求項 3】

請求項 1 又は 2 に記載の電気光学装置を具備してなることを特徴とする電子機器。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、例えば液晶装置等の電気光学装置、及び該電気光学装置を具備してなる電子機器、並びにトランジスタの技術分野に関する。 10

【背景技術】

【0002】

この種の電気光学装置は、基板上の画像表示領域にデータ線及び走査線が互いに交差して配線され、両配線の交差に対応して画素電極がマトリクス状に設けられると共に、画素電極は画素毎にスイッチング制御される。各画素には、画素電極をスイッチング制御する画素スイッチング素子として、例えば LDD (Lightly Doped Drain) 構造を有するトランジスタが設けられる。LDD 構造では、トランジスタの半導体膜に低濃度の不純物が注入されて低濃度不純物領域が形成されると共に高濃度の不純物が注入されて高濃度不純物領域が形成される。低濃度不純物領域及び高濃度不純物領域の相互間の不純物の濃度勾配に基づく電解緩和効果により、トランジスタの非動作時におけるリーク電流（即ちオフリーケ電流）を低減する。 20

【0003】

例えば特許文献 1 では、半導体膜に低濃度不純物領域を形成した後、サイドウォールを形成し高濃度の不純物を注入して高濃度不純物領域を形成する技術が開示されている。特許文献 1 によれば、サイドウォールの存在に起因する半導体膜（シリコン基板）の低濃度不純物領域の結晶欠陥に起因するトランジスタのリーク電流低減のため、サイドウォールを三日月形状或いは凹形状に加工する。

【0004】

【特許文献 1】特開平 5 - 3209 号公報

30

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら特許文献 1 によれば、サイドウォールの加工によりトランジスタの製造プロセスは煩雑となるおそれがある。従って、このような煩雑な加工により製造プロセスの歩留まりも低下する不具合が生じ得る。

【0006】

本発明は上記問題点等に鑑みてなされたものであり、LDD 構造を有するトランジスタにおけるリーク電流をより有効に低減できると共に比較的容易に製造可能な電気光学装置、及びこのような電気光学装置を具備してなる電子機器、並びにトランジスタを提供することを課題とする。 40

【課題を解決するための手段】

【0007】

本発明の電気光学装置は上記課題を解決するために、データ線と、チャネル領域と、前記データ線に電気的に接続された第 1 のソースドレイン領域と、画素電極に電気的に接続された第 2 のソースドレイン領域と、前記第 1 のソースドレイン領域と前記チャネル領域との間に形成された第 1 の接合領域と、前記第 2 のソースドレイン領域と前記チャネル領域との間に形成された第 2 の接合領域とを有する半導体膜を含むトランジスタと、前記半導体膜の延在する第 1 の方向と交差する第 2 の方向に沿って延在し、前記チャネル領域と重なる本体部と、該本体部から前記第 1 の方向に沿って延設され且つ前記半導体膜の第 1 50

の接合領域と重なる第1の延設部と、前記本体部から前記第1の方向とは反対側の第3の方向に沿って延設され且つ前記半導体膜の第2の接合領域と重なる第2の延設部とを有する遮光膜とを備え、前記遮光膜の第1の延設部は、前記遮光膜の第2の延設部よりも幅が狭くなるように形成されており、前記チャネル領域及び前記第2の接合領域は、それぞれ同一幅となるように形成されており、前記第1の接合領域は、前記遮光膜の第1の延設部と重なる領域において、前記チャネル領域側よりも前記第1のソースドレイン領域側が幅広に形成され、前記第1の接合領域の前記第1のソースドレイン領域側が、前記チャネル領域及び第2の接合領域よりも幅広に形成されている。

また、前記遮光膜は、前記チャネル領域と重なるように設けられたゲート電極と電気的に接続される。

10

#### 【0008】

本発明の電気光学装置によれば、例えば、基板上の表示領域に、複数の画素電極が例えばマトリクス状に設けられ、その動作時には、データ線から画素電極への画像信号の供給が制御され、所謂アクティブマトリクス方式による画像表示が可能となる。画像信号は、データ線及び画素電極間に電気的に接続されたスイッチング素子であるトランジスタが、例えば走査線から供給される走査信号に基づいてオンオフされることによって、所定のタイミングでデータ線からトランジスタを介して画素電極に供給される。

#### 【0009】

トランジスタは、チャネル領域、第1及び第2のソースドレイン領域を有する半導体膜と、チャネル領域に重なるゲート電極とを含む。

20

#### 【0010】

チャネル領域は、基板上における一の方向に沿ったチャネル長を有する。本発明に係る「一の方向」とは、例えば基板上でマトリクス状に規定された複数の画素の行方向、即ち複数のデータ線が配列される配列方向、言い換えれば複数の走査線の各々が延びる方向（即ちX方向）、又は例えば基板上でマトリクス状に規定された複数の画素の列方向、即ち複数の走査線が配列される配列方向、言い換えれば複数のデータ線の各々が延びる方向（即ちY方向）を意味する。

#### 【0011】

第1及び第2のソースドレイン領域のうち一の領域はデータ線と互いに電気的に接続され、他の領域は画素電極と互いに電気的に接続される。更に、第1及び第2のソースドレイン領域の各々について、半導体膜のチャネル領域との間に第1及び第2の接合領域の各々が形成される。即ち、チャネル領域と第1のソースドレイン領域との間に第1の接合領域が形成され、チャネル領域と第2のソースドレイン領域との間に第2の接合領域が形成される。第1及び第2の接合領域は、例えば、トランジスタがLDD構造を有する場合におけるLDD領域（即ち、例えばイオンインプランテーション法等の不純物打ち込みによって半導体膜にソースドレイン領域よりも少量の不純物を打ち込んでなる領域）を意味する。この場合、第1及び第2のソースドレイン領域は夫々、LDD領域よりも高濃度の不純物領域として形成される。

30

#### 【0012】

本発明では特に、第1及び第2の接合領域のうち少なくとも一方は、少なくとも部分的に、チャネル領域よりも幅広に形成される。例えば、第1及び第2の接合領域の少なくとも一方は、その対応するソースドレイン領域側の幅が、チャネル領域側の幅よりも広くなるように（典型的には、チャネル領域側から対応するソースドレイン領域側に向かって徐々に幅が広くなるように）形成される。

40

#### 【0013】

ここで、少なくとも一方の接合領域は、前述のようなLDD構造によれば少なくも一方のソースドレイン領域よりも不純物濃度が低くなるように形成される。この場合、少なくとも一方の接合領域の対応するソースドレイン領域への境目（即ち、少なくとも一方の接合領域と該接合領域に対応するソースドレイン領域との境目）においては、不純物濃度は低い値から高い値に変化する。例えばこのような不純物濃度の変化に応じて、本発明では

50

少なくとも一方の接合領域は、少なくとも部分的に、チャネル領域よりも幅広に形成される。より具体的には、少なくとも一方の接合領域において、対応するソースドレイン領域への境目がチャネル領域への境目（即ち、少なくとも一方の接合領域とチャネル領域との境目）よりも幅広となるように形成され、不純物濃度の変化（低い、即ち小さい値から、高い、即ち大きい値への変化）に反して幅が狭くならないように形成される。従って、少なくとも一方の接合領域について、上述したようなソースドレイン領域への境目における不純物濃度の変化に基づく濃度勾配を、その幅広形状によって補足的に維持することが可能となる。これにより、少なくとも一方の接合領域及びソースドレイン領域間の濃度勾配に基づく電解緩和効果を良好に維持し、リーク電流を低減することができる。また、本発明ではトランジスタの設計時において少なくとも一方の接合領域の幅を調整すれば、特許文献1と比較して製造プロセスにおける新たな加工を行わなくても容易にトランジスタを製造することができる。10

#### 【0014】

以上説明したような本発明の電気光学装置では、各画素でトランジスタのリーク電流を抑制し表示品位を向上させることができると共に、より簡易な製造プロセスにより製造することができる。

#### 【0015】

更に本発明では、前記第1及び第2のソースドレイン領域のうち少なくとも一方は、前記一方の接合領域よりも幅広に形成される。

#### 【0016】

よって、少なくとも一方の接合領域から対応する少なくとも一方のソースドレイン領域へ、その境目を挟んで半導体膜の幅が広く変化するように形成することができる。従って、より確実に不純物濃度の変化に反して、少なくとも一方の接合領域の対応するソースドレイン領域への境目で幅が狭くならないように形成することができる。これにより、より確実に、少なくとも一方の接合領域から少なくとも一方のソースドレイン領域への濃度勾配を維持し、電解緩和効果を向上させることができる。20

#### 【0017】

本発明の一態様では、前記半導体膜は、前記一方の接合領域から前記一方のソースドレイン領域にかけて連続的に幅が変化するように形成される。

#### 【0018】

この場合には、半導体膜の幅の寸法変化を緩やかに行う、言い換えれば幅の寸法変化に基づく寸法勾配をより小さくすることができる。よって、少なくとも一方の接合領域から少なくとも一方のソースドレイン領域への不純物の濃度勾配に基づく電流密度に与える影響を小さくし、電解緩和効果をより向上させることが可能となる。30

#### 【0019】

本発明の電気光学装置の他の態様では、前記チャネルの延在方向と交差する方向に沿って延在する本体部と、該本体部からチャネルの延在方向に沿って延設され且つ前記半導体膜と少なくとも部分的に重なる延設部とを有する遮光膜を備え、前記チャネル領域は、前記本体部と前記延設部とが交差する部分に重なるように配置される。

#### 【0020】

この態様によれば、遮光膜はトランジスタの半導体膜に対して基板の側から進行していく光を遮光可能なように形成される。遮光膜の延設部は、半導体膜に沿って半導体膜と少なくとも部分的に重なって形成されるため、半導体膜に対して進行する光を延設部において少なくとも部分的に遮光することができる。40

#### 【0021】

この態様では、半導体膜においてチャネル領域は、本体部と延設部との交差する部分に重なって配置される。ここに、本体部の延在方向に沿う「他の方向」とは、上述した「一の方向」に交差するX方向又はY方向を意味する。本体部及び延在部の各々で遮光可能な進行方向を有する光を、本体部と延設部との交差する部分で遮光することができる。よって、チャネル領域に対して進行する光をより確実に遮光することができ、トランジスタに50

おける光リーク電流を抑制することが可能となる。その結果、電気光学装置においてより高品位な表示を行うことができる。

#### 【0022】

この、遮光膜を備える態様では、前記遮光膜は、前記延設部における前記第2の接合領域と重なる部分が、前記延設部における前記第1の接合領域と重なる部分よりも幅広になるように形成されており、前記第1の接合領域は、少なくとも部分的に、前記チャネル領域よりも幅広に形成されてもよい。

#### 【0023】

この場合には、第1の接合領域よりも第2の接合領域を基板上のより広い領域で遮光膜の延設部によって遮光することができる。ここに、後述するように半導体膜において、第1の接合領域がデータ線と電気的に接続され且つ第2の接合領域が特に画素電極と電気的に接続される場合は、第2の接合領域は第1の接合領域と比較して、相対的に光リーク電流が発生し易い傾向にある。従って、この場合に、本態様の構成を適用すれば第2の接合領域に対する遮光性を延設部によってより向上させることができ、より確実に光リーク電流を低減することが可能となる。

10

#### 【0024】

これに対して、遮光膜の延設部による遮光で第2の接合領域よりも第1の接合領域について遮光性が低下しても、第1の接合領域の第1のソースドレイン領域への境目における不純物の濃度勾配を、その幅広形状によって補足的に維持することができる。その結果、第1の接合領域においても、第1のソースドレイン領域への境目における不純物の濃度勾配に基づく電解緩和効果により、光リーク電流の発生を抑制することが可能となる。

20

#### 【0025】

ここに、遮光膜の延設部において、より幅狭く形成された第1の接合領域と重なる一部について、延在部の延在方向と交差する方向で生じる段差形状に基づいて、第1の接合領域では、第1のソースドレイン領域への境目で幅が局所的に狭くなることによりくびれ形状が生じるおそれがある。この態様では、第1の接合領域の幅が、第1のソースドレイン領域への境目で狭くならないように形成することができ、上述したようなくびれ形状が生じるのを防止することが可能となる。

#### 【0026】

この、第1の接合領域が、少なくとも部分的に、チャネル領域よりも幅広に形成される態様では、前記トランジスタに対応して設けられた画素電極を備え、前記第1のソースドレイン領域は前記データ線に電気的に接続されると共に、前記第2のソースドレイン領域は前記画素電極に電気的に接続されるように構成してもよい。

30

#### 【0027】

この場合には、第1の接合領域がデータ線と電気的に接続され且つ第2の接合領域が画素電極と電気的に接続される。従って、第2の接合領域に対する遮光性を遮光膜における延設部によってより向上させることができ、より確実に光リーク電流を低減することが可能となる。

#### 【0028】

本発明の電子機器は上記課題を解決するために、上述した本発明の電気光学装置（但し、その各種態様も含む）を具備してなる。

40

#### 【0029】

本発明の電子機器によれば、上述した本発明の電気光学装置を具備してなるので、高品位な表示を行い且つより簡易な製造プロセスにより製造することができる、投射型表示装置、携帯電話、電子手帳、ワードプロセッサ、ビューファインダ型又はモニタ直視型のビデオテープレコーダ、ワークステーション、テレビ電話、POS端末、タッチパネルなどの各種電子機器を実現できる。

#### 【0030】

本件の参考発明に係るトランジスタは上記課題を解決するために、チャネル領域と、該チャネル領域を挟んで夫々形成された第1及び第2のソースドレイン領域と、前記第1及

50

び第2のソースドレイン領域と前記チャネル領域との間に夫々形成された第1及び第2の接合領域とを有する半導体膜と、前記チャネル領域に重なるゲート電極とを備え、前記第1及び第2の接合領域のうち少なくとも一方は、少なくとも部分的に、前記チャネル領域よりも幅広に形成されており、前記第1及び第2のソースドレイン領域のうち少なくとも一方は、前記一方の接合領域よりも幅広に形成される。

#### 【0031】

本件の参考発明に係るトランジスタによれば、上述した本発明の電気光学装置と同様に、リーク電流を低減し且つ比較的容易に製造することができる。

#### 【0032】

本発明のこののような作用及び他の利得は次に説明する実施するための最良の形態から明らかにされる。 10

#### 【発明を実施するための最良の形態】

#### 【0033】

以下図面を参照しながら、本発明に係る電気光学装置、並びに電子機器の各実施形態を説明する。尚、本実施形態では、電気光学装置の一例として、駆動回路内蔵型のTFTアクティブマトリクス駆動方式の液晶装置を例に挙げる。

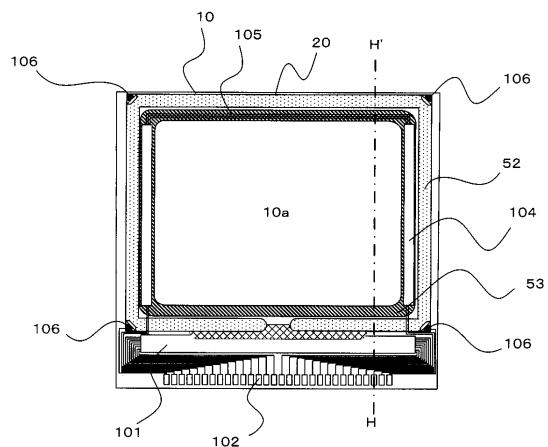

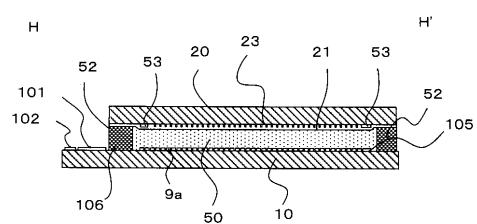

#### 【0034】

先ず、本実施形態に係る液晶装置の全体構成について、図1及び図2を参照して説明する。 20

#### 【0035】

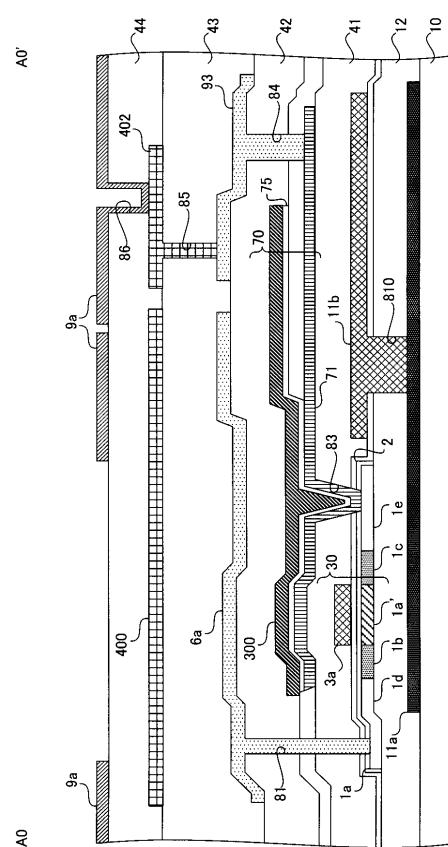

図1は、TFTアレイ基板をその上に形成された各構成要素と共に対向基板の側から見た液晶装置の平面図であり、図2は、図1のH-H'線断面図である。

#### 【0036】

図1及び図2において、本実施形態に係る液晶装置では、TFTアレイ基板10と対向基板20とが対向配置されている。TFTアレイ基板10は例えば石英基板、ガラス基板等の透明基板、又はシリコン基板である。対向基板20も好ましくはTFTアレイ基板10と同様に透明基板である。TFTアレイ基板10と対向基板20との間に液晶層50が封入されている。TFTアレイ基板10と対向基板20とは、画像表示領域10aの周囲に位置するシール領域に設けられたシール材52により相互に接着されている。 30

#### 【0037】

シール材52は、両基板を貼り合わせるための、例えば紫外線硬化樹脂、熱硬化樹脂等からなり、製造プロセスにおいてTFTアレイ基板10上に塗布された後、紫外線照射、加熱等により硬化させられたものである。シール材52中には、TFTアレイ基板10と対向基板20との間隔（即ち、基板間ギャップ）を所定値とするためのグラスファイバあるいはガラスピーブ等のギャップ材が散布されている。本実施形態に係る液晶装置は、プロジェクタのライトバルブ用として小型で拡大表示を行うのに適している。

#### 【0038】

シール材52が配置されたシール領域の内側に並行して、画像表示領域10aの額縁領域を規定する遮光性の額縁遮光膜53が、対向基板20側に設けられている。但し、このような額縁遮光膜53の一部又は全部は、TFTアレイ基板10側に内蔵遮光膜として設けられてもよい。 40

#### 【0039】

周辺領域のうち、シール材52が配置されたシール領域の外側に位置する領域には、データ線駆動回路101及び外部回路接続端子102がTFTアレイ基板10の一辺に沿って設けられている。走査線駆動回路104は、この一辺に隣接する2辺に沿い、且つ、額縁遮光膜53に覆われるようにして設けられている。更に、このように画像表示領域10aの両側に設けられた二つの走査線駆動回路104間をつなぐため、TFTアレイ基板10の残る一辺に沿い、且つ、額縫遮光膜53に覆われるようにして複数の配線105が設けられている。

#### 【0040】

10

20

30

40

50

対向基板 20 の 4 つのコーナー部に対して、両基板間において上下導通材 106 が配置されている。他方、TFT アレイ基板 10 にはこれらのコーナー部に対向する領域において上下導通端子が設けられている。これらにより、TFT アレイ基板 10 と対向基板 20 との間で電気的な導通をとることができる。

#### 【0041】

図 2において、TFT アレイ基板 10 上には、駆動素子である画素スイッチング用の TFT や走査線、データ線等の配線が作り込まれた積層構造が形成されている。画像表示領域 10a には、画素スイッチング用 TFT や走査線、データ線等の配線の上層に画素電極 9a がマトリクス状に設けられている。画素電極 9a 上には、配向膜（図 2 中、図示省略）が形成されている。他方、対向基板 20 における TFT アレイ基板 10 との対向面上に、遮光膜 23 が形成されている。遮光膜 23 は、例えば遮光性金属膜等から形成されており、対向基板 20 上の画像表示領域 10a 内で、例えば格子状等にパターニングされている。そして、遮光膜 23 上（図 2 中、遮光膜 23 より下側）に、ITO（Indium Tin Oxide）等の透明材料からなる対向電極 21 が複数の画素電極 9a と対向してベタ状に形成されている。対向電極 21 上（図 2 中、対向電極 21 より下側）には配向膜が形成されている（図 2 中、図示省略）。また、液晶層 50 は、例えば一種又は数種類のネマティック液晶を混合した液晶からなり、これら一対の配向膜間で、所定の配向状態をとる。

#### 【0042】

尚、図 1 及び図 2 に示した TFT アレイ基板 10 上には、これらのデータ線駆動回路 101、走査線駆動回路 104 等の駆動回路に加えて、画像信号線上の画像信号をサンプリングしてデータ線に供給するサンプリング回路、複数のデータ線に所定電圧レベルのプリチャージ信号を画像信号に先行して各々供給するプリチャージ回路、製造途中や出荷時の当該電気光学装置の品質、欠陥等を検査するための検査回路等を形成してもよい。

#### 【0043】

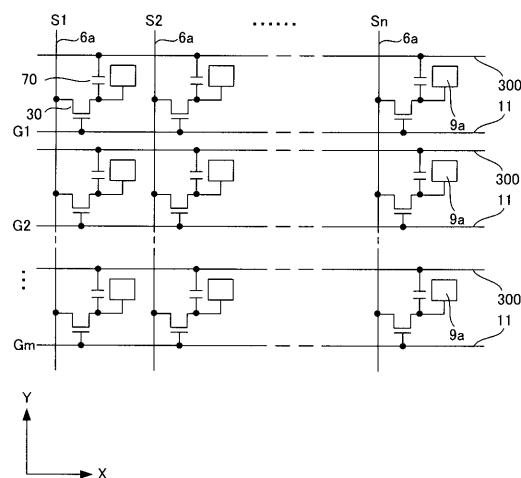

次に、本実施形態に係る液晶装置の画素部の電気的な構成について、図 3 を参照して説明する。

#### 【0044】

図 3 は、本実施形態に係る液晶装置の画像表示領域を構成するマトリクス状に形成された複数の画素における各種素子、配線等の等価回路図である。

#### 【0045】

図 3において、画像表示領域 10a を構成するマトリクス状に形成された複数の画素の夫々には、画素電極 9a 及び本発明に係る「トランジスタ」の一例としての TFT30 が形成されている。TFT30 は、画素電極 9a に電気的に接続されており、液晶装置の動作時に画素電極 9a をスイッチング制御する。画像信号が供給されるデータ線 6a は、TFT30 のソースに電気的に接続されている。データ線 6a に書き込む画像信号 S1、S2、…、Sn は、この順に線順次に供給しても構わないし、相隣接する複数のデータ線 6a 同士に対して、グループ毎に供給するようにしてもよい。

#### 【0046】

TFT30 のゲートに走査線 11 が電気的に接続されており、本実施形態に係る液晶装置は、所定のタイミングで、走査線 11 にパルス的に走査信号 G1、G2、…、Gm を、この順に線順次で印加するように構成されている。画素電極 9a は、TFT30 のドレインに電気的に接続されており、スイッチング素子である TFT30 を一定期間だけそのスイッチを閉じることにより、データ線 6a から供給される画像信号 S1、S2、…、Sn が所定のタイミングで書き込まれる。画素電極 9a を介して電気光学物質の一例としての液晶に書き込まれた所定レベルの画像信号 S1、S2、…、Sn は、対向基板に形成された対向電極との間で一定期間保持される。

#### 【0047】

液晶層 50（図 2 参照）を構成する液晶は、印加される電圧レベルにより分子集合の配向や秩序が変化することにより、光を変調し、階調表示を可能とする。ノーマリー・ホワイトモードであれば、各画素の単位で印加された電圧に応じて入射光に対する透過率が減少

10

20

30

40

50

し、ノーマリーブラックモードであれば、各画素の単位で印加された電圧に応じて入射光に対する透過率が増加され、全体として液晶装置からは画像信号に応じたコントラストをもつ光が出射される。

#### 【0048】

ここで保持された画像信号がリークすることを防ぐために、画素電極9aと対向電極21(図2参照)との間に形成される液晶容量と並列に蓄積容量70が付加されている。蓄積容量70は、画像信号の供給に応じて各画素電極9aの電位を一時的に保持する保持容量として機能する容量素子である。蓄積容量70の一方の電極は、画素電極9aと並列してTFT30のドレインに接続され、他方の電極は、定電位となるように、電位固定の容量線300に接続されている。蓄積容量70によれば、画素電極9aにおける電位保持特性が向上し、コントラスト向上やフリッカの低減といった表示特性の向上が可能となる。尚、蓄積容量70は、後述するように、TFT30へ入射する光を遮る内蔵遮光膜としても機能する。

#### 【0049】

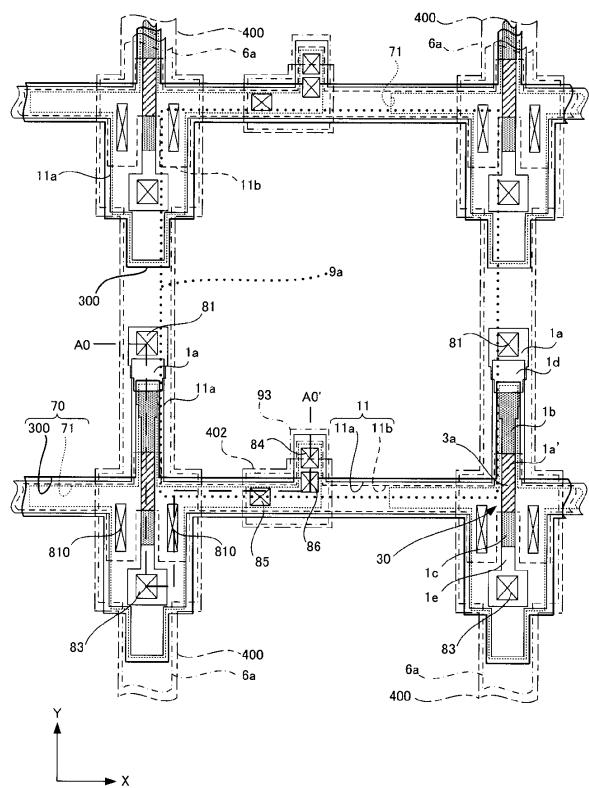

次に、上述の動作を実現する画素部の具体的な構成について、図4及び図5を参照して説明する。

#### 【0050】

図4は、相隣接する複数の画素部の平面図であり、図5は、図4のA0-A0'線断面図である。図4及び図5では、各層・各部材を図面上で認識可能な程度の大きさとするため、該各層・各部材ごとに縮尺を異ならしめてある。この点については、後述する各図についても同様である。図4及び図5では、説明の便宜上、画素電極9aより上側に位置する部分の図示を省略している。

#### 【0051】

図4において、画素電極9aは、TFTアレイ基板10上に、マトリクス状に複数設かれている。なお、図4中には、任意の一画素に着目して、かかる画素における画素電極9aの構成を概略的に図示してある。画素電極9aの縦横の境界にそれぞれ沿って、データ線6a及び走査線11が設けられている。即ち、走査線11は、X方向に沿って延びており、データ線6aは、走査線11と交差するように、Y方向に沿って延びている。なお、走査線11は、下側遮光膜を兼ねる第1の走査線11aと、ゲート電極3aと一体的に形成された第2の走査線11bとを含み、X方向に沿って二重配線されてなる。走査線11及びデータ線6aが互いに交差する個所の各々には画素スイッチング用のTFT30が設けられている。このように、第1の走査線11a及び第2の走査線11bが二重配線されるため、走査線11の電気的な抵抗を全体的に低くすることが可能となる。また、第1の走査線11a及び第2の走査線11bの一方に断線等の不具合が生じても、他方を冗長的に機能させることができるために、液晶装置の信頼性を向上させることができる。

#### 【0052】

走査線11、データ線6a、蓄積容量70、TFT30、シールド層400及び中継層93及び402等は、TFTアレイ基板10上で平面的に見て、画素電極9aに対応する各画素の開口領域(即ち、各画素において、表示に実際に寄与する光が透過又は反射される領域)を囲む非開口領域内に配置されている。即ち、これらの走査線11、データ線6a、蓄積容量70、TFT30、シールド層400及び中継層93及び402等は、表示の妨げとならないように、各画素の開口領域ではなく、非開口領域内に配置されている。

#### 【0053】

以下、TFTアレイ基板10上の画素部の積層構造について第1層から順に、説明する。

#### 【0054】

第1層には、導電性ポリシリコン、高融点金属、高融点金属シリサイド等により、例えば200nmの膜厚で第1の走査線11aが設けられている。第1の走査線11aは、図4に示すようにX方向に沿って延びる部分と共に、該部分からTFT30のチャネル領域1a'に重なるようにY方向に沿って延在する部分を有している。

10

20

30

40

50

## 【0055】

第1の走査線11aは、図4に示すように、TFT30のチャネル領域1a'、データ線側LDD領域1b及び画素電極側LDD領域1c、並びにデータ線側ソースドレイン領域1d及び画素電極側ソースドレイン領域1eに対向する領域を含むように、好ましくは形成される。よって、第1の走査線11aによって、TFTアレイ基板10における裏面反射や、複板式のプロジェクタ等で他の液晶装置から発せられ合成光学系を突き抜けてくる光などの、戻り光に対してTFT30のチャネル領域1a'を殆ど或いは完全に遮光できる。即ち、第1の走査線11aは、走査信号を供給する配線として機能すると共に戻り光に対するTFT30の下側遮光膜として機能することが可能である。

## 【0056】

10

図5において、第1層の走査線11a及び第2層のTFT30間は、下地絶縁膜12によって絶縁されている。下地絶縁膜12は、第1の走査線11aからTFT30を絶縁する機能の他、TFTアレイ基板10の全面に形成されることにより、TFTアレイ基板10の表面の研磨時における荒れや、洗浄後に残る汚れ等で画素スイッチング用のTFT30の特性の劣化を防止する機能を有する。なお、下地絶縁膜12は、例えばTEOS(珪酸エチル)膜を膜厚300nm及びHTO(High Temperature Oxide)膜を膜厚50nmで積層してなる2層構造を有する。

## 【0057】

第2層には、半導体膜1a及びゲート電極3aを含むTFT30が設けられている。

## 【0058】

20

図4及び図5に示すように、半導体膜1aは、例えばポリシリコンから膜厚が55nmとして形成され、Y方向に沿ったチャネル長を有するチャネル領域1a'、データ線側LDD領域1b及び画素電極側LDD領域1c、並びにデータ線側ソースドレイン領域1d及び画素電極側ソースドレイン領域1eからなる。即ち、TFT30はLDD構造を有している。尚、データ線側LDD領域1bは、本発明に係る「第1の接合領域」の一例であり、画素電極側LDD領域1cは、本発明に係る「第2の接合領域」の一例である。データ線側ソースドレイン領域1dは、本発明に係る「第1のソースドレイン領域」の一例であり、画素電極側ソースドレイン領域1eは、本発明に係る「第2のソースドレイン領域」の一例である。

## 【0059】

30

データ線側ソースドレイン領域1d及び画素電極側ソースドレイン領域1eは、チャネル領域1a'を基準として、Y方向に沿ってほぼミラー対称に形成されている。データ線側LDD領域1bは、チャネル領域1a'及びデータ線側ソースドレイン領域1d間に形成されている。画素電極側LDD領域1cは、チャネル領域1a'及び画素電極側ソースドレイン領域1e間に形成されている。データ線側LDD領域1b、画素電極側LDD領域1c、データ線側ソースドレイン領域1d及び画素電極側ソースドレイン領域1eは、例えばイオンプランテーション法等の不純物打ち込みによって半導体膜1aに不純物を打ち込んでなる不純物領域である。データ線側LDD領域1b及び画素電極側LDD領域1cはそれぞれ、データ線側ソースドレイン領域1d及び画素電極側ソースドレイン領域1eよりも不純物の少ない低濃度な不純物領域として形成される。このような不純物領域によれば、TFT30の非動作時において、データ線側ソースドレイン領域1d及び画素電極側ソースドレイン領域1eに流れるオフ電流を低減し、且つTFT30の動作時に流れるオン電流の低下を抑制できる。尚、TFT30は、LDD構造を有することが好ましいが、データ線側LDD領域1b、画素電極側LDD領域1cに不純物打ち込みを行わないオフセット構造であってもよい。

40

## 【0060】

図4及び図5において、ゲート電極3aと一体的に第2の走査線11bが、例えば導電性ポリシリコンとタンゲステンシリサイド(WSi)とを夫々膜厚が60nmとして積層することにより形成される。第2の走査線11bは、図4に示すように、平面的に見てチャネル領域1a'に重なってY方向に沿って延在する部分がゲート電極3aとして機能す

50

ると共に、Y方向に沿って延在する部分から第1の走査線11aに並走してX方向に延在する部分を有している。

#### 【0061】

第2の走査線11bにおいて、これと一体的に形成されたゲート電極3aは半導体膜1aとゲート絶縁膜2によって絶縁されている。本実施形態では、図4及び図5に示すように、下地絶縁膜12において、半導体膜1aの脇にはコンタクトホール810が開口される。ゲート電極3aは、コンタクトホール810内にまで連続的に形成されて第1の走査線11aと電気的に接続される。

#### 【0062】

図5において、TFT30より上層側には、第2層及び第3層間を層間絶縁する、層間絶縁膜41が設けられる。10 層間絶縁膜41は、例えば膜厚300nmのTEOS膜により形成される。層間絶縁膜41には、画素電極側ソースドレイン領域1eと蓄積容量70の下部容量電極71とを電気的に接続するためのコンタクトホール83が開口される。また、データ線側ソースドレイン領域1dとデータ線6aとを電気的に接続するためのコンタクトホール81も、開口される。

#### 【0063】

層間絶縁膜41より上層側の第3層には、下部容量電極71、及び誘電体膜75を介して下部容量電極71と対向する上部容量電極300を有する蓄積容量70が形成される。

#### 【0064】

上部容量電極は、容量線300と一体的に形成される。容量線300は、例えば、膜厚が50nm及び100nmの各々の窒化チタン(TiN)膜に、膜厚が150nmのアルミニウム(Al)膜を挟持してなる3層構造を有する。容量線300は、その詳細な構成については図示を省略してあるが、画素電極9aが配置された画像表示領域10aからその周囲に延設され、定電位源と電気的に接続され、固定電位に維持される。容量線300は、図4において、半導体膜1a上において、データ線側LDD領域1b及び画素電極側LDD領域1cと、画素電極側ソースドレイン領域1eとに重なるように、Y方向に沿って延在する部分と、該部分からX方向に沿って延在する部分を有する。容量線300において、Y方向に沿って延在する部分と、下部容量電極71と重なる、X方向に沿って延在する一部が上部容量電極として機能する。よって、上部容量電極は固定電位に維持される、固定電位側容量電極として機能する。2030

#### 【0065】

下部容量電極71は、例えば膜厚が100nmとして導電性ポリシリコンより形成される。下部容量電極71は、図4において、Y方向及びX方向の各々に、上部容量電極300と重なるように延在する部分を有する。そして、Y方向に延在する部分において、画素電極側ソースドレイン領域1eと重なると共に、コンタクトホール83を介して電気的に接続される。また、X方向に延在する部分において、容量線300の配置を避けて露出する部分において、コンタクトホール84を介して第4層目の中継層93と電気的に接続される。中継層93はコンタクトホール85を介して第5層目の中継層402と電気的に接続される。更に、中継層402は、コンタクトホール86を介して画素電極9aと電気的に接続される。従って、下部容量電極71は、画素電位に維持される、画素電位側容量電極として機能する。40

#### 【0066】

誘電体膜75は、例えば膜厚が4nmのHTO膜及び膜厚が15nm窒化シリコン(SiN)膜を積層してなる2層構造を有している。

#### 【0067】

図5において、蓄積容量70より上層側には、第3層及び第4層間を層間絶縁する層間絶縁膜42が、例えば膜厚が400nmのTEOS膜により形成される。コンタクトホール84は層間絶縁膜42を貫通して、下部容量電極71の表面に達するように開口され、コンタクトホール81は、層間絶縁膜42及び41、更にはゲート絶縁膜2を貫通して開口され、半導体膜1aの表面に達する。50

## 【0068】

図4及び図5において、第4層には、データ線6a及び中継層93が設けられる。図5において、データ線6aは、コンタクトホール81を介して、半導体膜1aのデータ線側ソースドレイン領域1dと電気的に接続される。また、中継層93は、コンタクトホール84を介して下部容量電極71と電気的に接続される。データ線6a及び中継層93は、例えば金属膜等の導電材料で構成される薄膜を層間絶縁膜42上に薄膜形成法を用いて形成しておき、当該薄膜を部分的に除去、即ちパターニングすることによって相互に離間させた状態で形成される。従って、データ線6a及び中継層93を同一工程で形成できるため、装置の製造プロセスを簡便にできる。なお、例えばデータ線6a及び中継層93は夫々、膜厚が20nmのチタン(Ti)膜、膜厚が50nmのTiN膜、膜厚が350nmのAl膜、膜厚が150nmのTiN膜をこの順に積層してなる4層構造を有する。

## 【0069】

図5において、データ線6a及び中継層93より上層側には、第4層及び第5層間を層間絶縁する層間絶縁膜43が、例えば膜厚が600nmのTEOS膜により形成される。コンタクトホール85は、層間絶縁膜43を貫通して開口され、中継層93の表面に達する。なお、好ましくは、層間絶縁膜43の表面に対して、例えばCMP(化学的機械研磨)法等による平坦化処理が行われる。

## 【0070】

第5層には、シールド層400及び中継層402が設けられる。図4において、シールド層400は、データ線6aと同方向即ちY方向に沿って延設される。半導体膜1aにおいてチャネル領域1a'、データ線側LDD領域1b及び画素電極側LDD領域1c、並びにデータ線側ソースドレイン領域1d及び画素電極側ソースドレイン領域1eに対向する領域に、データ線6a及びシールド層400が配線されている。よって、半導体膜1aにおける、これらの各領域に対して上層側から進行する光を、データ線6a及びシールド層400によって遮光することが可能となる。

## 【0071】

また、図5において、中継層402は好ましくはシールド層400と同一膜により形成される。中継層402は、既に説明したように、画素電極9aと電気的に接続され、画素電極9a及び中継層93間の電気的接続を中継する。なお、シールド層400及び中継層402は夫々、例えば、膜厚が350nmのAl膜及び膜厚が150nmのTiN膜を積層してなる2層構造を有する。

## 【0072】

図5において、シールド層400及び中継層402より上層側には、第5層及び第6層間を層間絶縁する層間絶縁膜44が、例えば膜厚が600nmのTEOS膜及び膜厚が75nmのBSG(ボロンシリケートガラス)膜よりなる2層構造により、形成される。コンタクトホール86は、層間絶縁膜44を貫通して開口され、中継層402の表面に達する。なお、好ましくは、層間絶縁膜44の表面に対して平坦化処理が行われる。

## 【0073】

図4及び図5において、第6層には、画素電極9aが形成される。図5に示すように、画素電極9aは、中継層402及び93と、下部容量電極71とによって、コンタクトホール86、85、84及び83を介して中継されつつ、半導体膜1aの画素電極側ソースドレイン領域1eに電気的に接続されている。図2を参照して既に説明したように、画素電極9aの上側表面には、ラビング処理等の所定の配向処理が施された配向膜が設けられている。

## 【0074】

以上に説明した画素部の構成は、図4に示すように、各画素部に共通である。画像表示領域10a(図1参照)には、かかる画素部が周期的に形成されている。

## 【0075】

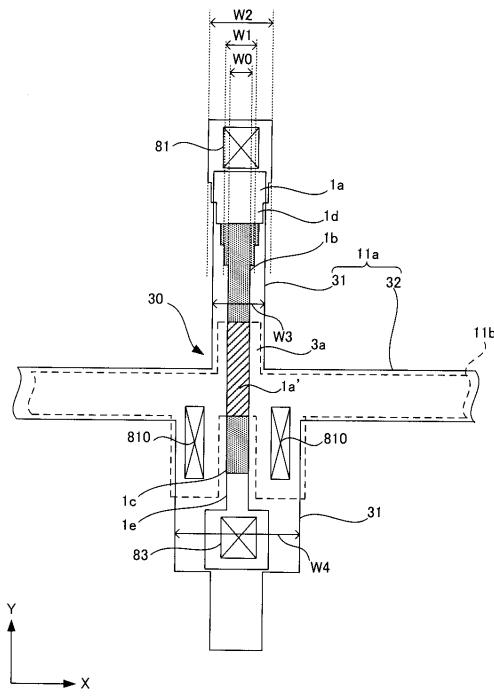

次に、本実施形態において特徴的なTFT30の構成について、図6を参照してより詳細に説明する。

10

20

30

40

50

**【 0 0 7 6 】**

図6は、第1層及び第2層の各層について、TFTに対する第1及び第2の走査線の配置関係に係る主要な構成を示す平面図である。

**【 0 0 7 7 】**

TFT30は上述したようにLDD構造を有し、半導体膜1aにおいて、データ線側LDD領域1b及び画素電極側LDD領域1cは夫々低濃度不純物領域として形成され、データ線側ソースドレイン領域1d及び画素電極側ソースドレイン領域1eは夫々高濃度不純物領域として形成される。本実施形態では、データ線側LDD領域1b及び画素電極側LDD領域1cのうち少なくとも一方は、データ線側ソースドレイン領域1d及び画素電極側ソースドレイン領域1eのうち、対応する少なくとも一方への不純物濃度の変化に応じて幅が以下のように調整されて形成されている。10

**【 0 0 7 8 】**

ここに、図4及び図5を参照して説明したように、TFT30より下層側の第1層には第1の走査線11aが下側遮光膜を兼ねて形成される。この下側遮光膜11aは、半導体膜1aの延在方向(Y方向)に沿って延設し、半導体膜1aと少なくとも部分的に重なる延設部31及び、延設部31の延在方向と交差する方向(X方向)に沿って延在する本体部32を有する。本体部32は、第2の走査線11bと共にX方向に沿って二重配線され走査線11の一部を構成する。

**【 0 0 7 9 】**

既に説明したように延設部31は、半導体膜1aのデータ線側LDD領域1b及び画素電極側LDD領域1c、並びにデータ線側ソースドレイン領域1d及び画素電極側ソースドレイン領域1eと少なくとも部分的に重なり、TFTアレイ基板10の側から進行していく戻り光等からこれらの領域を少なくとも部分的に遮光することが可能である。半導体膜1aのチャネル領域1a'が延設部31及び本体部32の交差する部分に重なるように配置される。よって、延設部31及び本体部32の各々で遮光可能な進行方向を有する光を、延設部31と本体部32との交差する部分で遮光することができる。よって、チャネル領域1a'に対して進行する光をより確実に遮光することができ、光リーク電流を抑制することが可能となる。20

**【 0 0 8 0 】**

また、図6において、延設部31はデータ線側LDD領域1bと重なる部分の幅W3に対して、少なくとも画素電極側LDD領域1cと重なる部分の幅W4が広くなるように形成される。よって、データ線側LDD領域1bよりも画素電極側LDD領域1cをTFTアレイ基板10上により広い領域で延設部31によって遮光することができる。ここに、画素電極側LDD領域1cはデータ線側LDD領域1bと比較して、相対的に光リーク電流が発生し易い傾向にある。従って、画素電極側LDD領域1cに対する遮光性を延設部31によってより向上させることができ、より確実に光リーク電流を低減することが可能となる。30

**【 0 0 8 1 】**

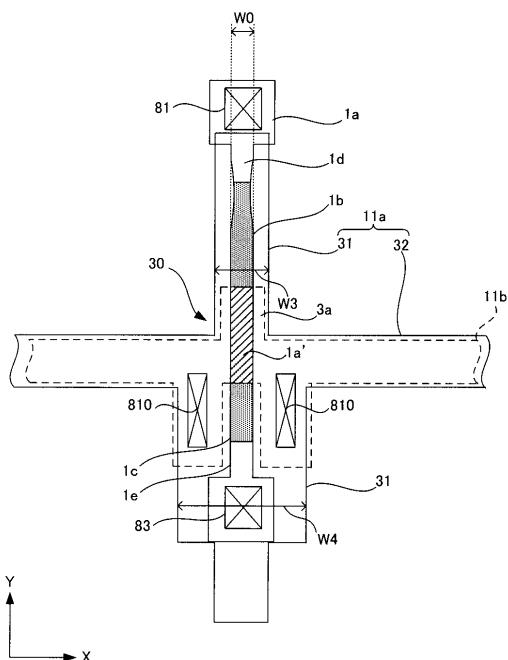

ここに、本実施形態の比較例について図7を参照して、本実施形態と異なる構成にのみ着目して説明する。40

**【 0 0 8 2 】**

図7は、比較例において、図6に対応する各種構成要素の配置関係に係る主要な構成を示す平面図である。

**【 0 0 8 3 】**

比較例において図7では、設計上で第1の接合領域1bはチャネル領域1a'と同程度の幅W0を有する点が本実施形態と異なっている。延設部31において、画素電極側LDD領域1cと重なる部分に対してより幅狭く(W3 < W4)形成された、データ線側LDD領域1bと重なる部分について、延在部31の延在方向(Y方向)と交差する方向で延在部31の膜厚に起因する段差形状が生じ、この段差形状に応じて図5に示す半導体膜1aの下地となる下地絶縁膜12の表面に段差が生じる。このような下地絶縁膜12の表面50

における段差形状に基づいて、データ線側 LDD 領域 1b ではデータ線側ソースドレイン領域 1d への境目で幅が、局所的にチャネル領域 1a' と同程度の設計上の幅 W0 より狭くなりくびれ形状が生じるおそれがある。

#### 【0084】

また、図 6 を参照して説明したように幅狭く形成されたデータ線側 LDD 領域 1b と重なる延設部 31 の一部では戻り光等の光に対する遮光性が低下するおそれがある。加えて図 7 に示すようなくびれ形状が半導体膜 1a において生じることにより、データ線側 LDD 領域 1b のデータ線側ソースドレイン領域 1d への境目でこれらの領域間の濃度勾配に基づく電解緩和効果が乱され、リーク電流が生じ易くなるおそれがある。よって、結果として光リーク電流が増加する問題点が生じ得る。

10

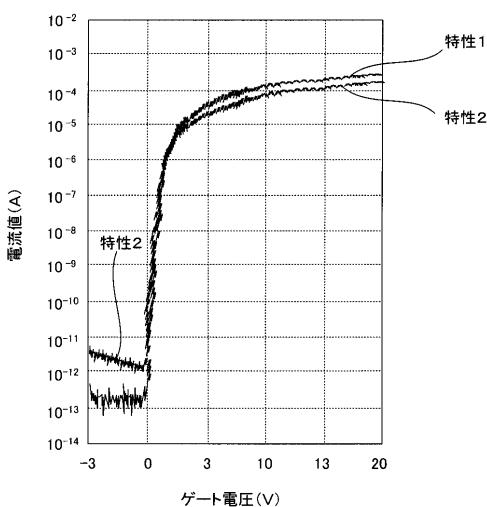

#### 【0085】

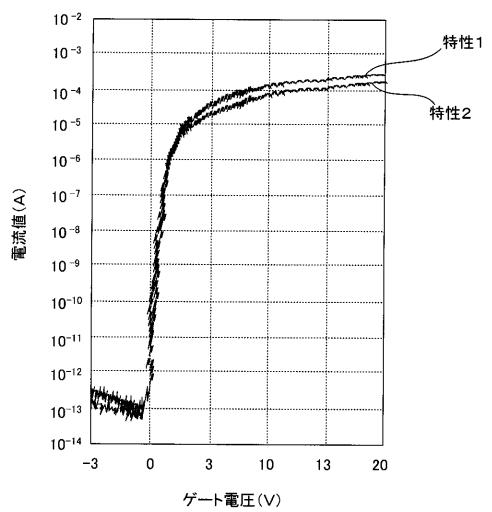

ここに、図 8 には図 7 に示す比較例における TFT の電気特性を示してある。図 8 においては、横軸にゲート電圧 (V) 及び縦軸に電流値 (A) をとり、特性 1 及び特性 2 について示してある。特性 1 は、TFT30 の良好な電気特性を示し、特性 2 は図 7 に示す比較例における TFT30 の電気特性を示している。図 8 において、TFT30 のゲート電圧の 0V 付近の閾値以下で、特性 1 によればオフ電流は殆ど或いは理想的には全く生じないが、特性 2 によればオフ電流の値、即ちリーク電流が高くなっている。

#### 【0086】

再び図 6において、本実施形態では特に、TFT30 の半導体膜 1a においてデータ線側 LDD 領域 1b 及び画素電極側 LDD 領域 1c のうち少なくとも一方は、少なくとも部分的に、チャネル領域 1a' よりも幅広に形成される（即ち、チャネル領域 1a' よりも少なくとも部分的に幅が広くなるように形成される）。より具体的には、好ましくは半導体膜 1a においてデータ線側 LDD 領域 1b は、データ線側ソースドレイン領域 1d への不純物濃度の変化に応じて、チャネル領域 1a' の幅 W0 よりも幅広となるように形成される。データ線側 LDD 領域 1b のデータ線側ソースドレイン領域 1d への境目においては、不純物濃度は低い値から高い値に変化する。このような不純物濃度の変化に応じて、データ線側 LDD 領域 1b はチャネル領域 1a' の幅 W0 よりも少なくとも部分的に幅広となるように形成される。即ち、不純物濃度の変化が維持されるようにデータ線側 LDD 領域 1b において、データ線側ソースドレイン領域 1d への境目がチャネル領域 1a' よりも広い幅 W1 となるように形成され、不純物濃度の変化（低い、即ち小さい値から、高い、即ち大きい値への変化）に反して幅が狭くならないように形成される。従って、データ線側 LDD 領域 1b について、データ線側ソースドレイン領域 1d への境目における不純物濃度の変化に基づく濃度勾配を、その幅広形状によって補足的に維持することができる。これにより、データ線側 LDD 領域 1b 及びデータ線側ソースドレイン領域 1d 間の濃度勾配に基づく電解緩和効果を良好に維持し、リーク電流を低減することができる。また、設計時において上述したように少なくともデータ線側 LDD 領域 1b の幅を調整すれば、特許文献 1 と比較して製造プロセスにおける新たな加工を行わなくても容易に TFT30 を製造することができる。

20

#### 【0087】

また、好ましくはデータ線側ソースドレイン領域 1d は、少なくとも部分的に、データ線側 LDD 領域 1b よりも幅広に形成される（即ち、データ線側 LDD 領域 1b に対して、データ線側ソースドレイン領域 1d の幅が少なくとも部分的に広くなるように形成される）。よって、データ線側 LDD 領域 1b からデータ線側ソースドレイン領域 1d へ、その境目を挟んで半導体膜 1a の幅が広く変化するように形成することができる。従って、より確実にデータ線側 LDD 領域 1b において、データ線側ソースドレイン領域 1d への境目で幅が狭くならないように形成することが可能となる。この場合には図 6 に示すように、半導体膜 1a において、データ線側 LDD 領域 1b からデータ線側ソースドレイン領域 1d にかけて、幅 W0 から最終的に幅 W2 となるように、2 以上の段階を経て且つ連続的に幅が変化するように形成するのが好ましい。よって、このような幅の寸法変化を緩やかに行う、言い換えれば幅の寸法変化に基づく寸法勾配をより小さくすることができ、デ

30

40

50

ータ線側 L D D 領域 1 b からデータ線側ソースドレイン領域 1 d への不純物の濃度勾配に基づく電流密度に与える影響を小さくし、電解緩和効果をより向上させることが可能となる。

#### 【 0 0 8 8 】

従って、データ線側 L D D 領域 1 b の幅が、データ線側ソースドレイン 1 d への境目で狭くならないように形成することができ、半導体膜 1 a にくびれ形状が生じるのを防止することが可能となる。加えて、延設部 3 1 のより幅狭く形成された一部による遮光で画素電極側 L D D 領域 1 c よりもデータ線側 L D D 領域 1 b について遮光性が低下しても、上述したようなデータ線側 L D D 領域 1 b において、データ線側ソースドレイン領域 1 d への境目における不純物の濃度勾配に基づく電解緩和効果を良好に維持することができ、光リーキ電流の発生を抑制することが可能となる。10

#### 【 0 0 8 9 】

ここに、図 9 には本実施形態における T F T の電気特性を示してある。図 9 においては、図 8 と同様に横軸にゲート電圧 (V) 及び縦軸に電流値 (A) をとり、特性 1 及び特性 2 について示してある。特性 1 は、T F T 3 0 の良好な電気特性を示し、特性 2 は本実施形態における T F T 3 0 の電気特性を示している。図 9 においては、図 8 に示す比較例の電気特性と比較して、T F T 3 0 のゲート電圧の 0 V 付近の閾値以下で、特性 2 は特性 1 とリーキ電流は同程度にまで、比較例の特性 2 に対して 2 极程度低下させることができとなる。20

#### 【 0 0 9 0 】

以上説明したようなデータ線側 L D D 領域 1 b 及びデータ線側ソースドレイン領域 1 d の構成は、これらの領域の側に加えて若しくは代えて半導体膜 1 a における画素電極側 L D D 領域 1 c 及び画素電極側ソースドレイン領域 1 e に対して同様に適用するようにしてもよい。

#### 【 0 0 9 1 】

従って、以上説明したような本実施形態では、各画素部で T F T 3 0 のリーキ電流を抑制し表示品位を向上させることができると共に、より簡易な製造プロセスにより製造することが可能となる。

#### 【 0 0 9 2 】

次に、上述した電気光学装置である液晶装置を各種の電子機器に適用する場合について説明する。30

#### 【 0 0 9 3 】

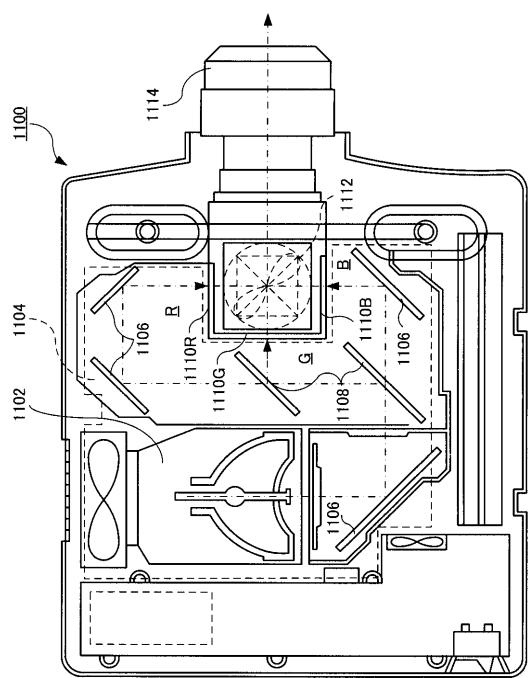

図 10 は、プロジェクタの構成例を示す平面図である。以下では、この液晶装置をライトバルブとして用いたプロジェクタについて説明する。

#### 【 0 0 9 4 】

図 10 に示されるように、プロジェクタ 1 1 0 0 内部には、ハロゲンランプ等の白色光源からなるランプユニット 1 1 0 2 が設けられている。このランプユニット 1 1 0 2 から射出された投射光は、ライトガイド 1 1 0 4 内に配置された 4 枚のミラー 1 1 0 6 及び 2 枚のダイクロイックミラー 1 1 0 8 によって R G B の 3 原色に分離され、各原色に対応するライトバルブとしての液晶パネル 1 1 1 0 R、1 1 1 0 B 及び 1 1 1 0 G に入射される。40

#### 【 0 0 9 5 】

液晶パネル 1 1 1 0 R、1 1 1 0 B 及び 1 1 1 0 G の構成は、上述した液晶装置と同等であり、画像信号処理回路から供給される R、G、B の原色信号でそれぞれ駆動されるものである。そして、これらの液晶パネルによって変調された光は、ダイクロイックプリズム 1 1 1 2 に 3 方向から入射される。このダイクロイックプリズム 1 1 1 2 においては、R 及び B の光が 90 度に屈折する一方、G の光が直進する。従って、各色の画像が合成される結果、投射レンズ 1 1 1 4 を介して、スクリーン等にカラー画像が投写されることとなる。

#### 【 0 0 9 6 】

10

20

30

40

50

尚、図10を参照して説明した電子機器の他にも、モバイル型のパーソナルコンピュータや、携帯電話、液晶テレビ、ビューファインダ型、モニタ直視型のビデオテープレコーダ、カーナビゲーション装置、ページャ、電子手帳、電卓、ワードプロセッサ、ワークステーション、テレビ電話、POS端末、タッチパネルを備えた装置等が挙げられる。そして、これらの各種電子機器に適用可能なのは言うまでもない。

#### 【0097】

また、本発明は上述の各実施形態で説明した液晶装置以外にも反射型液晶装置（LCD）等にも適用可能である。

#### 【0098】

本発明は、上述した実施形態に限られるものではなく、請求の範囲及び明細書全体から読み取れる発明の要旨或いは思想に反しない範囲で適宜変更可能であり、そのような変更を伴う電気光学装置、及び該電気光学装置を備えた電子機器、並びにトランジスタもまた本発明の技術的範囲に含まれるものである。

#### 【図面の簡単な説明】

#### 【0099】

【図1】液晶装置の概略的な平面図である。

【図2】図1のH-H'線断面図である。

【図3】本実施形態に係る液晶装置の画像表示領域を構成するマトリクス状に形成された複数の画素における各種素子、配線等の等価回路図である。

【図4】相隣接する複数の画素部の平面図である。

【図5】図4のA0-A0'線断面図である。

【図6】第1層及び第2層の各層について、TFTに対する第1及び第2の走査線の配置関係に係る主要な構成を示す平面図である。

【図7】比較例において、図6に対応する各種構成要素の配置関係に係る主要な構成を示す平面図である。

【図8】図7に示す比較例におけるTFTの電気特性を示す図である。

【図9】本実施形態におけるTFTの電気特性を示す図である。

【図10】液晶装置を適用した電子機器の一例たるプロジェクタの構成を示す平面図である。

#### 【符号の説明】

#### 【0100】

1a...半導体膜、1a'...チャネル領域、1b...データ線側LDD領域、1c...画素電極側LDD領域、1d...データ線側ソースドレイン領域、1e...画素電極側ソースドレイン領域、3a...ゲート電極、6a...データ線、10...TFTアレイ基板、10a...画像表示領域、11...走査線、30...TFT

10

20

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(56)参考文献 特開2004-340981(JP,A)

特開平07-147411(JP,A)

特開2008-191200(JP,A)

特開2002-122889(JP,A)

特開2005-197618(JP,A)

特開2005-086024(JP,A)

特開平06-252405(JP,A)

(58)調査した分野(Int.Cl., DB名)

|        |             |   |             |

|--------|-------------|---|-------------|

| G 09 F | 9 / 0 0     | - | 9 / 3 0     |

|        | 9 / 3 0 7   | - | 9 / 4 6     |

| H 01 L | 2 7 / 3 2   |   |             |

| G 02 F | 1 / 1 3 4 3 | - | 1 / 1 3 4 5 |

|        | 1 / 1 3 5   | - | 1 / 1 3 6 8 |

| H 01 L | 2 1 / 3 3 6 |   |             |

|        | 2 9 / 7 8 6 |   |             |