(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4493779号

(P4493779)

(45) 発行日 平成22年6月30日(2010.6.30)

(24) 登録日 平成22年4月16日(2010.4.16)

(51) Int.Cl.

F 1

H01L 29/786 (2006.01)

H01L 29/78

626C

H01L 21/31 (2006.01)

H01L 21/31

C

H01L 21/318 (2006.01)

H01L 21/318

B

請求項の数 16 (全 24 頁)

(21) 出願番号 特願2000-22022 (P2000-22022)

(22) 出願日 平成12年1月31日 (2000.1.31)

(65) 公開番号 特開2001-217422 (P2001-217422A)

(43) 公開日 平成13年8月10日 (2001.8.10)

審査請求日 平成18年9月27日 (2006.9.27)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(73) 特許権者 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(72) 発明者 坂間 光範

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 石丸 典子

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 三輪 昌彦

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置およびその作製方法

## (57) 【特許請求の範囲】

## 【請求項1】

薄膜トランジスタを有する半導体装置であって、

基板に接して絶縁膜と、

前記絶縁膜上に接して半導体膜とを有し、

前記絶縁膜は、少なくとも前記基板と接する第1の層と前記半導体膜と接する第2の層とを有し、

前記第1の層は、水素濃度が $2 \sim 3$  atomic %で、窒素濃度が $7 \sim 10$  atomic %で、酸素濃度が $52 \sim 55$  atomic %の酸化窒化シリコン膜であり、

前記第2の層は、水素濃度が $0.5 \sim 2$  atomic %で、窒素濃度が $1 \sim 2$  atomic %で、酸素濃度が $62 \sim 65$  atomic %の酸化窒化シリコン膜であることを特徴とする半導体装置。 10

## 【請求項2】

薄膜トランジスタを有する半導体装置であって、

基板に接して絶縁膜と、

前記絶縁膜上に接して半導体膜とを有し、

前記絶縁膜は、前記基板と接する領域から前記半導体膜と接する領域にかけて連続的に組成が変化し、

前記基板と接する領域は、水素濃度が $2 \sim 3$  atomic %で、窒素濃度が $7 \sim 10$  atomic %で、酸素濃度が $52 \sim 55$  atomic %の酸化窒化シリコン膜であり、

10

20

前記半導体膜と接する領域は、水素濃度が 0.5 ~ 2 atomic % で、窒素濃度が 1 ~ 2 atomic % で、酸素濃度が 62 ~ 65 atomic % の酸化窒化シリコン膜であることを特徴とする半導体装置。

【請求項 3】

薄膜トランジスタを有する半導体装置であって、

基板に接して絶縁膜と、

前記絶縁膜上に接して半導体膜とを有し、

前記絶縁膜は、少なくとも前記基板と接する第 1 の層と前記半導体膜と接する第 2 の層とを有し、

前記第 1 の層は、シリコンに対する酸素の組成比が 1.4 ~ 1.8 で、シリコンに対する窒素の組成比が 0.05 ~ 0.5 の酸化窒化シリコン膜であり、

前記第 2 の層は、シリコンに対する酸素の組成比が 1.7 ~ 2 で、シリコンに対する窒素の組成比が 0.02 ~ 0.06 の酸化窒化シリコン膜であることを特徴とする半導体装置。

【請求項 4】

薄膜トランジスタを有する半導体装置であって、

基板に接して絶縁膜と、

前記絶縁膜上に接して半導体膜とを有し、

前記絶縁膜は、前記基板と接する領域から前記半導体膜と接する領域にかけて連続的に組成が変化し、

前記基板と接する領域は、シリコンに対する酸素の組成比が 1.4 ~ 1.8 で、シリコンに対する窒素の組成比が 0.05 ~ 0.5 の酸化窒化シリコン膜であり、

前記半導体膜と接する領域は、シリコンに対する酸素の組成比が 1.7 ~ 2 で、シリコンに対する窒素の組成比が 0.02 ~ 0.06 の酸化窒化シリコン膜であることを特徴とする半導体装置。

【請求項 5】

請求項 1 乃至 4 のいずれか一項において、前記酸化窒化シリコン膜中の窒素濃度は、前記半導体膜側の界面に向かって連続的に減少することを特徴とする半導体装置。

【請求項 6】

請求項 1 乃至 4 のいずれか一項において、前記酸化窒化シリコン膜中の酸素濃度は、前記半導体膜側の界面に向かって連続的に増加することを特徴とする半導体装置。

【請求項 7】

請求項 1 乃至 6 のいずれか一項において、前記半導体装置は、ビデオカメラ、デジタルカメラ、プロジェクター、ゴーグル型ディスプレイ、カーナビゲーション、カーステレオ、パーソナルコンピュータ、または携帯情報端末から選ばれた一つであることを特徴とする半導体装置。

【請求項 8】

半導体膜を形成する工程と、前記半導体膜と基板との間の絶縁膜を形成する工程とを有し、

前記絶縁膜を形成する工程は、少なくとも前記基板と界面を形成する第 1 の層を形成する工程と、前記半導体膜と界面を形成する第 2 の層を形成する工程とを有し、

前記第 1 の層を形成する工程は、 $SiH_4$ 、 $N_2O$ 、 $H_2$  のガス流量比が  $X_h = 0.5 ~ 5$  ( $X_h = H_2 / SiH_4 + N_2O$ )、 $X_g = 0.94 ~ 0.97$  ( $X_g = N_2O / SiH_4 + N_2O$ ) の範囲で酸化窒化シリコン膜を形成し、

前記第 2 の層を形成する工程は、 $SiH_4$ 、 $N_2O$ 、 $H_2$  のガス流量比が  $X_h = 0$  ( $X_h = H_2 / SiH_4 + N_2O$ )、 $X_g = 0.97 ~ 0.99$  ( $X_g = N_2O / SiH_4 + N_2O$ ) 範囲で酸化窒化シリコン膜を形成することを特徴とする半導体装置の作製方法。

【請求項 9】

請求項 8 において、前記絶縁膜の第 1 の層と第 2 の層とを形成する工程は、プラズマ CVD 装置の同一の成膜室で行われることを特徴とする半導体装置の作製方法。

10

20

30

40

50

## 【請求項 10】

半導体膜を形成する工程と、前記半導体膜と基板との間の絶縁膜を形成する工程とを有し、

前記絶縁膜を形成する工程は、前記基板と接する領域から前記半導体膜と接する領域にかけて、 $\text{SiH}_4$ 、 $\text{N}_2\text{O}$ 、 $\text{H}_2$ のガス流量比が $Xh = 0.5 \sim 5$  ( $Xh = \text{H}_2 / \text{SiH}_4 + \text{N}_2\text{O}$ )、 $Xg = 0.94 \sim 0.97$  ( $Xg = \text{N}_2\text{O} / \text{SiH}_4 + \text{N}_2\text{O}$ )の範囲から、 $Xh = 0$  ( $Xh = \text{H}_2 / \text{SiH}_4 + \text{N}_2\text{O}$ )、 $Xg = 0.97 \sim 0.99$  ( $Xg = \text{N}_2\text{O} / \text{SiH}_4 + \text{N}_2\text{O}$ )の範囲に変化させて酸化窒化シリコン膜を形成することを特徴とする半導体装置の作製方法。

## 【請求項 11】

10

同一成膜室で、

水素濃度が $2 \sim 3$  atomic %で、窒素濃度が $7 \sim 10$  atomic %で、酸素濃度が $52 \sim 55$  atomic %の基板と接する第1の酸化窒化シリコン膜と、

水素濃度が $0.5 \sim 2$  atomic %で、窒素濃度が $1 \sim 2$  atomic %で、酸素濃度が $62 \sim 65$  atomic %の半導体膜と接する第2の酸化窒化シリコン膜と、

前記半導体膜とを連続的に成膜することを特徴とする半導体装置の作製方法。

## 【請求項 12】

同一成膜室で、

基板と接する領域は、水素濃度が $2 \sim 3$  atomic %で、窒素濃度が $7 \sim 10$  atomic %で、酸素濃度が $52 \sim 55$  atomic %、

20

半導体膜と接する領域は、水素濃度が $0.5 \sim 2$  atomic %で、窒素濃度が $1 \sim 2$  atomic %で、酸素濃度が $62 \sim 65$  atomic %と連続的に組成が変化する酸化窒化シリコン膜と、

前記半導体膜とを連続的に成膜することを特徴とする半導体装置の作製方法。

## 【請求項 13】

同一成膜室で、

シリコンに対する酸素の組成比が $1.4 \sim 1.8$ で、シリコンに対する窒素の組成比が $0.05 \sim 0.5$ の基板と接する第1の酸化窒化シリコン膜と、

シリコンに対する酸素の組成比が $1.7 \sim 2$ で、シリコンに対する窒素の組成比が $0.02 \sim 0.06$ の半導体膜と接する第2の酸化窒化シリコン膜と、

30

前記半導体膜とを連続的に成膜することを特徴とする半導体装置の作製方法。

## 【請求項 14】

同一成膜室で、

基板と接する領域は、シリコンに対する酸素の組成比が $1.4 \sim 1.8$ で、シリコンに対する窒素の組成比が $0.05 \sim 0.5$ 、

半導体膜と接する領域は、シリコンに対する酸素の組成比が $1.7 \sim 2$ で、シリコンに対する窒素の組成比が $0.02 \sim 0.06$ と連続的に組成が変化する酸化窒化シリコン膜と、

前記半導体膜とを連続的に成膜することを特徴とする半導体装置の作製方法。

## 【請求項 15】

40

請求項 8 乃至 14 のいずれか一項において、前記酸化窒化シリコン膜中の窒素濃度は、前記半導体膜側の界面に向かって連続的に減少させることを特徴とする半導体装置の作製方法。

## 【請求項 16】

請求項 8 乃至 14 のいずれか一項において、前記酸化窒化シリコン膜中の酸素濃度は、前記半導体膜側の界面に向かって連続的に増加させることを特徴とする半導体装置の作製方法。

## 【発明の詳細な説明】

## 【0001】

## 【発明の属する技術分野】

50

本願発明は薄膜トランジスタ（以下TFTという）で構成された回路を有する半導体装置およびその作製方法に関する。例えば、画素部と駆動回路を同一の基板に設けたアクティブマトリクス型の液晶表示装置に代表される電気光学装置およびその様な電気光学装置を部品として搭載した電子機器に関する。

#### 【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、薄膜トランジスタを用いて形成されるアクティブマトリクス型の液晶表示装置に代表される電気光学装置、そのような電気光学装置を部品として搭載した電子機器、半導体回路は全て半導体装置である。

#### 【0003】

10

#### 【従来の技術】

ガラスなどの絶縁基板上に形成された半導体薄膜を用いた薄膜トランジスタ（TFT）が開発されている。半導体薄膜材料には、非晶質シリコン膜、非晶質シリコン膜をレーザーアニール法や熱アニール法などで結晶化させた結晶質シリコン膜などが用いられている。中でも、結晶質シリコン膜を活性層に用いたTFTはその高い電界移動度から電流駆動能力が高く、そのため微細加工が可能となり画素部の高開口率化が図れるようになった。

#### 【0004】

このようなTFTはICや電気光学装置のような電子デバイスに広く応用され、例えば画素のスイッチング素子や駆動回路に適用したアクティブマトリクス型の表示装置に用いられている。TFT基板にはバリウムホウケイ酸ガラスやアルミノホウケイ酸などのガラス基板が代表的に用いられている。ガラス基板は石英基板と比較して耐熱性には劣るもののが安価で大面積基板を容易に製造できる利点があるため、大画面かつ安価な表示装置の実現が可能となる。

20

#### 【0005】

ガラス基板中、例えば、バリウムホウケイ酸ガラスやアルミノホウケイ酸ガラス中にはナトリウム（Na）などアルカリ金属元素などの不純物が微量ながら含まれており、ガラス基板から活性層へ不純物イオンが侵入することによりTFTの電気特性が変動する。この電気特性の変動を防ぐため、TFTを形成するガラス基板表面に酸化シリコン膜や窒化シリコン膜あるいは酸化窒化シリコン膜などからなる下地層（ブロッキング層）を形成していた。

#### 【0006】

30

また、下地膜として窒化シリコン膜を基板側、酸化シリコン膜を活性層側に設けた積層膜を用いると、TFT特性の安定性向上に効果があることが知られている。

#### 【0007】

トップゲート型TFTの場合、チャネル形成領域が下地膜に接しているためTFT特性は下地膜の膜質により大きく影響される。

#### 【0008】

40

#### 【発明が解決しようとする課題】

TFTのゲート電極に電圧を印加すると活性層に電界が形成され、ガラス基板中の不純物イオンは活性層側へと引き寄せられる。そのため、下地膜の膜質によっては不純物イオンが下地膜を通して活性層やゲート絶縁膜に侵入し、それに伴いTFTの電気特性の変動が生じ信頼性の低下につながる問題が生じる。

#### 【0009】

下地膜としての窒化シリコン膜は不純物イオンのブロッキング効果が高いという長所があるがTFT特性に影響を与えるトラップ準位が多いという短所があり、さらに、内部応力が大きいので活性層と界面を形成すると歪みを与え $V_{th}$ （閾値電圧）のネガティブシフトや $S$ 値（サブスレッショルド定数）の増大といったTFT特性の低下を引き起こす。また、下地膜としての酸化シリコン膜は窒化シリコン膜よりもバンドギャップが広い、絶縁性が高い、トラップ準位が低いという長所があるが、水分が吸着しやすい、不純物イオンのブロッキング効果が低いという短所がある。酸化窒化シリコン膜の場合、膜中の窒素濃度及び酸素濃度によってその性質は異なり、不純物イオンのブロッキング効果を高めるには膜中の

50

窒素濃度を増加させ膜を緻密化させる必要がある。しかし、酸化窒化シリコン膜中の窒素濃度を増加させると窒化シリコン膜と同様の欠点が生じる。

【0010】

さらに、下地膜として固定電荷を多量に含む膜を活性層に接触させた場合、この下地膜と活性層の界面でトラップ準位が形成されTFT特性の低下を招いてしまう。一般的に、膜中の窒素濃度が高くなると固定電荷が多くなる。

【0011】

また、窒化シリコン膜と酸化シリコン膜を積層する場合、それぞれ構成元素が異なるためそれぞれ専用の成膜室が必要であった。この場合、基板搬送時に基板が冷えることにより成膜室の温度が低下してしまうため、基板温度を低下させないための予備加熱が必要となる。この予備加熱時間が処理時間の増大につながっていた。

10

【0012】

本発明は上記問題点を解決するための技術であり、TFT特性の安定性および信頼性向上、生産性に優れた下地膜、およびその作製方法を提供することを目的とする。

【0013】

【課題を解決するための手段】

上記問題点を解決するために本発明は、プラズマCVD法でSiH<sub>4</sub>、N<sub>2</sub>O、H<sub>2</sub>を用いて酸化窒化シリコン膜を作製し、この膜をTFTの下地に適用する。作製される酸化窒化シリコン膜の特性は、主にN<sub>2</sub>OとH<sub>2</sub>の流量を変化させて制御する。H<sub>2</sub>の流量の増加により膜中の水素濃度と窒素濃度を上記範囲内において増加させることができる。また、N<sub>2</sub>Oの流量の増加により膜中の水素濃度と窒素濃度が減少し酸素濃度を高くすることができる。一方、H<sub>2</sub>とN<sub>2</sub>Oのガス流量比のみを変化させてもシリコンの濃度は殆ど変化しない。これにより、窒化シリコン膜の長所が現れる膜質を示す組成の酸化窒化シリコン膜を基板側に、酸化シリコン膜の長所が現れる膜質を示す組成の酸化窒化シリコン膜を活性層側に、連続的に組成を変化させて形成することができ、窒化シリコン膜及び酸化シリコン膜の両者の長所を活かした良質の下地膜が作製できる。また、前記膜質を示す酸化窒化シリコン膜はガス流量比を変えるのみで成膜法が同じであるため、同一成膜室での成膜が可能となりそれにより生産性が向上する。

20

【0014】

具体的には、SiH<sub>4</sub>、N<sub>2</sub>O、H<sub>2</sub>の流量比がXh=0.5~5 (Xh=H<sub>2</sub>/SiH<sub>4</sub>+N<sub>2</sub>O) Xg=0.94~0.97 (Xg=N<sub>2</sub>O/SiH<sub>4</sub>+N<sub>2</sub>O) の範囲で形成する酸化窒化シリコン膜と、Xh=0 (Xh=H<sub>2</sub>/SiH<sub>4</sub>+N<sub>2</sub>O) 、Xg=0.97~0.99 (Xg=N<sub>2</sub>O/SiH<sub>4</sub>+N<sub>2</sub>O) の範囲で形成する酸化窒化シリコン膜とを形成し、それらの酸化窒化シリコン膜を使い分ける。

30

【0015】

プラズマCVD法で酸化窒化シリコン膜を作製する時に、SiH<sub>4</sub>とN<sub>2</sub>Oの混合ガスにH<sub>2</sub>を添加することで、SiH<sub>4</sub>から分解して生成されたラジカルが気相中（反応空間中）でポリマー化をするのを防ぎ、パーティクルの生成を無くすことができる。また、膜の成長表面において、水素ラジカルによる表面吸着水素の引き抜き反応により過剰な水素が膜中へ取り込まれるのを防止することができる。このような作用は膜堆積時の基板温度と密接な相関があり、基板温度を300~400℃、好ましくは400℃にすることによりその作用を得ることができる。その結果、欠陥密度の少ない緻密な膜を形成することを可能とし、膜中に含まれる微量の水素は格子歪みを緩和する作用として有効に働く。水素を分解して水素ラジカルの発生密度を高めるには、グロー放電を発生させるための高周波電源周波数13.56~120MHz、好ましくは27~60MHzの範囲とし、放電電力密度0.1~1W/cm<sup>2</sup>とする。

40

【0016】

上記の作製条件を採用することにより、本発明に適用される酸化窒化シリコン膜の組成は、窒素濃度が0.5atomic%以上10atomic%未満、水素濃度が0.5atomic%以上5atomic%未満、酸素濃度が50atomic%以上70atomic%未満となるようにする。

【0017】

本発明の特徴は、酸化窒化シリコン膜でTFTの下地膜を形成する場合において、少なく

50

とも、下地膜の基板側と活性層側とでその組成を異ならせ、相対的に前者の方が膜中窒素濃度及び水素濃度が高く酸素濃度が低くなるようにする。

【0018】

例えば、下地膜の基板と接する第1層目を窒素濃度7~10atomic%、水素濃度が2~3atomic%、酸素濃度が52~55atomic%の酸化窒化シリコン膜で形成し、活性層接する第2層目を窒素濃度1~2atomic%、水素濃度0.5~2atomic%、酸素濃度が62~65atomic%の酸化窒化シリコン膜で形成し、階段状の濃度勾配を設ける。或いは、上記のように第1層目と第2層目との明確な区別を無くし、組成を連続的に変化させても良い。

【0019】

酸化窒化シリコン膜の作製にはプラズマ装置の構成は容量結合型の平行平板方式のものを用いる。その他にも誘導結合型の方式や電子サイクロトロン共鳴など磁場のエネルギーを援用したプラズマCVD装置を用いても良い。酸化窒化シリコン膜はSiH<sub>4</sub>、N<sub>2</sub>Oガスを用い、さらにH<sub>2</sub>を添加して組成を変化させることができる。プラズマ形成時の圧力は10~133Pa(好ましくは20~40Pa)、高周波電力密度0.2~1W/cm<sup>2</sup>(好ましくは0.3~0.5 W/cm<sup>2</sup>)、基板温度200~450(好ましくは300~400)、高周波電源の発振周波数は10~120MHz(好ましくは27~60MHz)で形成する。

【0020】

表1には3種類の作製条件が記載されている。条件 #210はSiH<sub>4</sub>とN<sub>2</sub>Oから作製する酸化窒化シリコン膜の作製条件である。一方、#211と#212はSiH<sub>4</sub>とN<sub>2</sub>OにH<sub>2</sub>を添加したときの作製条件であり、添加するH<sub>2</sub>流量を変化させたものである。本明細書ではSiH<sub>4</sub>とN<sub>2</sub>Oから作製する酸化窒化シリコン膜を酸化窒化シリコン膜(A)と表記し、SiH<sub>4</sub>とN<sub>2</sub>OにH<sub>2</sub>から作製する酸化窒化シリコン膜を酸化窒化シリコン膜(B)と表記する。酸化窒化シリコン膜(A)はSiH<sub>4</sub>、N<sub>2</sub>O、H<sub>2</sub>の流量比がXh=0(Xh=H<sub>2</sub>/SiH<sub>4</sub>+N<sub>2</sub>O)、Xg=0.97~0.99(Xg=N<sub>2</sub>O/SiH<sub>4</sub>+N<sub>2</sub>O)の範囲で形成し、酸化窒化シリコン膜(B)はSiH<sub>4</sub>、N<sub>2</sub>O、H<sub>2</sub>の流量比がXh=0.5~5(Xh=H<sub>2</sub>/SiH<sub>4</sub>+N<sub>2</sub>O)、Xg=0.94~0.97(Xg=N<sub>2</sub>O/SiH<sub>4</sub>+N<sub>2</sub>O)の範囲で形成する。

【0021】

また、表1には酸化窒化シリコン膜の成膜前に実施する前処理条件について記載されている。この前処理は必須なものではないが、酸化窒化シリコン膜特性の再現性やTFTに応用した場合におけるその特性の再現性を高めるために有用である。

【0022】

【表1】

| 条件/サンプルNo. |            | #210             | #211 | #212 |

|------------|------------|------------------|------|------|

| プラズマクリーニング | ガス [sccm]  | H <sub>2</sub>   | 100  | 200  |

|            |            | O <sub>2</sub>   | 100  | 0    |

|            | 圧力 [Pa]    |                  | 20   | 20   |

|            | 高周波電力      |                  | 0.2  | 0.2  |

|            | 処理時間 [min] |                  | 2    | 2    |

|            |            |                  |      |      |

| 成膜         | ガス [sccm]  | SiH <sub>4</sub> | 4    | 5    |

|            |            | N <sub>2</sub> O | 400  | 120  |

|            |            | H <sub>2</sub>   | 0    | 500  |

|            | 圧力 [Pa]    |                  | 20   | 20   |

|            | 高周波電力      |                  | 0.4  | 0.4  |

|            | 基板温度 [°C]  |                  | 400  | 400  |

【0023】

表1を参照すると前処理条件は水素を200SCCM導入し、圧力20Pa、高周波電力0.2W/cm<sup>2</sup>でプラズマを生成して2分間処理する。また、水素を100SCCMと酸素を100SCCM導入して同様にプラズマを生成して処理しても良い。また、表には記載しないがN<sub>2</sub>Oと水素を導入して圧力10~70Pa、高周波電力密度0.1~0.5 W/cm<sup>2</sup>で数分間処理しても良い。このような前処理のとき基板温度は300~450、好ましくは400とすれば良い。前処理の効果は基板上の

10

20

30

40

50

被堆積表面をクリーニングする作用や、被堆積表面に水素を吸着させ一時的に不活性化させることで、その後堆積される酸化窒化水素化シリコン膜の界面特性を安定化させる作用がある。また、酸素やN<sub>2</sub>Oを同時に導入することにより被堆積表面の最表面およびその近傍を酸化させ、界面準位密度を低減させるなどの好ましい作用がある。

【0024】

具体的には、酸化窒化シリコン膜(B)の成膜条件は、#211の条件でSiH<sub>4</sub>を5SCCM、N<sub>2</sub>Oを120SCCM、水素を500SCCM、高周波電力密度0.4W/cm<sup>2</sup>とし、基板温度400 で作製した。高周波電源周波数は10~120MHz、好ましくは27~60 MHzが適用され得るが、ここでは60 MHzとした。また、#212の条件では、#211の条件に対して水素の流量を125SCCMとして作製した。それぞれのガスの流量は、その絶対値を限定するものではなく流量比に意味を持つている。 $X_h = [H_2] / ([SiH_4] + [N_2O])$  とすると、X<sub>h</sub>は0.1~7の範囲とすれば良い。また、前述のように、 $X_g = [N_2O] / ([SiH_4] + [N_2O])$  とすると、X<sub>g</sub>は0.90~0.99の範囲とすれば良い。また、酸化窒化シリコン膜(A)の成膜条件は#210の条件である。

【0025】

このような条件で作製した酸化窒化シリコン膜の代表的な特性を表2に示す。表2には、ラザフォード・バックスキャッタリング・スペクトロメトリー (Rutherford Backscattering Spectrometry: 以下、RBSと省略して記す。使用装置 システム; 3S - R10、加速器; NE C3SDH pelletron エンドステーション; CE & A RBS - 400) から求めた水素(H)、窒素(N)、酸素(O)、シリコン(Si)の組成と密度を示す。

【0026】

【表2】

| サンプルNo.                      |      | #210                  | #211                  | #212                  |

|------------------------------|------|-----------------------|-----------------------|-----------------------|

| 組成<br>(atomic%)              | H    | 1.6±0.5               | 3.0±0.5               | 2.0±0.5               |

|                              | N    | 1.5±4                 | 9.6±4                 | 7.9±4                 |

|                              | O    | 63.5±2                | 53.8±2                | 56.4±2                |

|                              | Si   | 33.4±2                | 33.6±2                | 33.7±2                |

| 組成比                          | O/Si | 1.9                   | 1.6                   | 1.67                  |

|                              | N/Si | 0.04                  | 0.18                  | 0.14                  |

| 密度 (atomic/cm <sup>3</sup> ) |      | 6.53×10 <sup>22</sup> | 7.16×10 <sup>22</sup> | 7.11×10 <sup>22</sup> |

【0027】

表2の結果では、成膜時にH<sub>2</sub>を添加することで膜中に含まれる水素の濃度が増加している。これに伴い酸素や窒素の含有量も変化している。酸化窒化シリコン膜(A)ではSiに対するOの比が1.9(許容範囲として1.7~2)であり、Siに対するNの比が0.04(許容範囲として0.02~0.06)である。これに対し酸化窒化シリコン膜(B)の組成は、成膜時に添加するH<sub>2</sub>の流量で変化するものの、Siに対するOの比が1.6(許容範囲として1.4~1.8)程度であり、Siに対するNの比が0.14~0.18(許容範囲として0.05~0.5)であり、Siに対するOの割合が低下し、窒素の割合が増加している。

【0028】

窒素含有量の増加は膜の密度の増加と対応しており、酸化窒化シリコン膜(A)の6.5atom s/cm<sup>3</sup>から、酸化窒化シリコン膜(B)では7.1atoms/cm<sup>3</sup>に増加し緻密化している。このような密度の変化はフッ化水素アンモニウム(NH<sub>4</sub>HF<sub>2</sub>)を7.13%とフッ化アンモニウム(NH<sub>4</sub>F)を15.4%含む混合溶液(ステラケミファ社製、商品名LAL500)の20 におけるエッティング速度からも、酸化窒化シリコン膜(A)で120nm/minであるのに対し、酸化窒化シリコン膜(B)では63~105nm/minであることから、窒素含有量の増加とともに膜が緻密化していくといえる。このことは、緻密で硬い膜は基板からの不純物のプロッキング性が高いことから酸化窒化シリコン膜(B)を基板側に設けることは有効であるということを示している。

10

20

30

40

50

## 【0029】

さらに、内部応力で比較すると、酸化窒化シリコン膜(A)は $-4.26 \times 10^8 \text{ Pa}$ の圧縮応力であるものが熱処理(500、1時間+550、4時間:結晶化の工程における処理条件と同等なもの)ですが $-7.29 \times 10^6 \text{ Pa}$ に大きく変化する。一方、酸化窒化シリコン膜(B)は $2.31 \times 10^8 \text{ Pa}$ の引張り応力であり熱処理を施しても殆ど変化しない。熱処理により内部応力が変化する現象は膜の構造変化や組成変化と関連付けて考慮することができ、酸化窒化シリコン膜(B)の熱的安定性が良いといえる。

## 【0030】

以上のように、酸化窒化シリコン膜の特性について代表的な例を示した。勿論、本発明に適用し得る絶縁膜としての酸化窒化シリコン膜は表1、2で示したものに限定されるものではない。酸化窒化シリコン膜(A)の組成は、TFTに代表される半導体装置に適した下地膜として適した絶縁膜の組成は、窒素濃度1~2atomic%、水素濃度0.5~2atomic%、酸素濃度62~65atomic%とする。酸化窒化シリコン膜(B)の組成は、窒素濃度7~10atomic%、水素濃度2~3atomic%、酸素濃度52~55atomic%とする。さらに、酸化窒化シリコン膜(A)の密度は $6 \times 10^{22}$ 以上 $7 \times 10^{22} \text{ atoms/cm}^3$ 未満とし、酸化窒化シリコン膜(B)の密度は $7 \times 10^{22}$ 以上 $8 \times 10^{22} \text{ atoms/cm}^3$ 未満とする。上述のフッ化水素アンモニウム( $\text{NH}_4\text{HF}_2$ )をとフッ化アンモニウム( $\text{NH}_4\text{F}$ )を含む混合溶液によるエッチング速度は、酸化窒化シリコン膜(A)で110~130nm/minとし、酸化窒化シリコン膜(B)で60~110nm/minとする。

## 【0031】

## 【発明の実施の形態】

本実施形態でTFTに代表される半導体装置に適した下地膜の作製方法について説明する。

## 【0032】

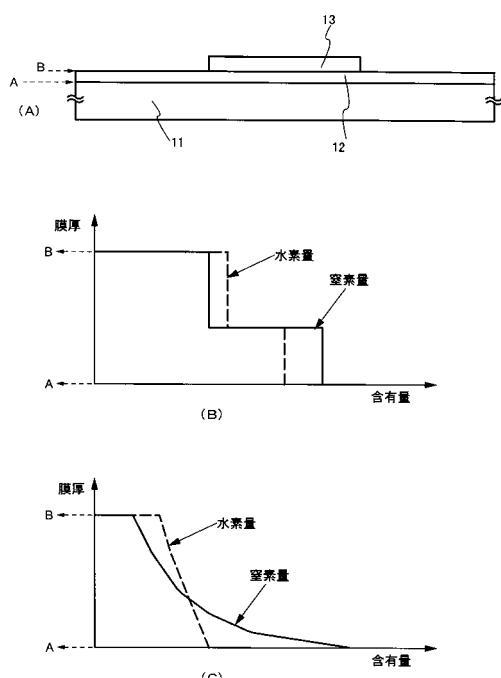

酸化窒化シリコン膜(A)と酸化窒化シリコン膜(B)をTFTの下地膜に適用する例を示す。図1(A)はトップゲート型のTFTの構成について示したものである。基板11上に下地膜(または、ブロッキング層ともいう)12が形成され、その上に島状半導体層13が形成されている。島状半導体層は非晶質半導体、結晶質半導体いずれの材料であっても良い。下地膜12は島状半導体層13の下面に接して形成されることになる。

## 【0033】

下地膜12は、膜厚方向に対して酸化窒化シリコン膜(A)から酸化窒化シリコン膜(B)に連続的または階段状に組成が変化する構成とする。図1(B)、(C)は酸化窒化シリコン膜の水素と窒素の組成を示すグラフである。上記構成の一例として、図1(B)に示すように酸化窒化シリコン膜(B)を島状半導体層に接して形成し、その上に酸化窒化シリコン膜(A)を形成する。または、図1(C)に示すように島状半導体層側から酸化窒化シリコン膜(B)から酸化窒化シリコン膜(A)に連続的に組成を変化させても良い。

## 【0034】

上記のように酸化窒化シリコン膜(A)と酸化窒化シリコン膜(B)を積層または連続的に組成を変化させることで、TFTの特性を安定化させることができる。具体的にはV<sub>th</sub>のシフトを防ぎ、熱的安定性による変動を防ぐことができる。

## 【0035】

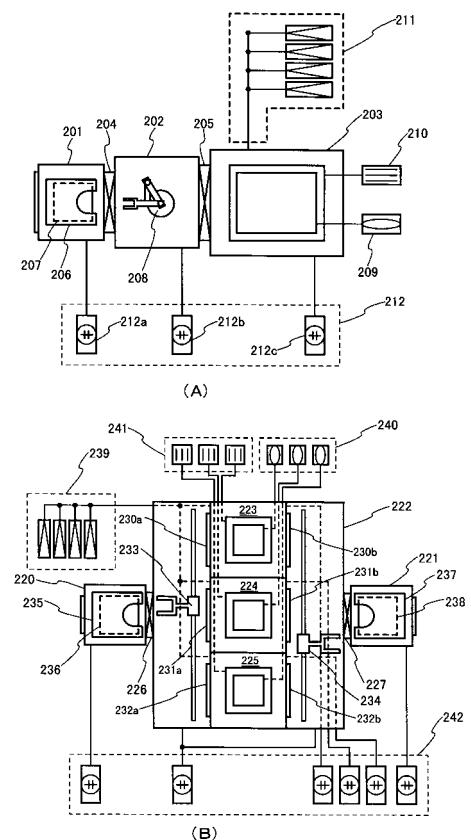

図2は酸化窒化シリコン膜(A)と(B)を形成して、本発明の構成を得るのに適した装置の一例を示している。図2(A)に示すプラズマCVD装置は、ロード/アンロード室201、搬送室202、成膜室203を備えた装置である。各部屋は仕切弁204、205で分離されている。各部屋には真空ポンプなどを備えた減圧手段212a~212cがそれぞれ接続している。ロード/アンロード室201には基板207と該基板を保持するカセット206があり、搬送室202に設けた搬送手段208により反応室203へ移送される。反応室203にはプラズマ発生手段209、基板加熱手段210、ガス供給手段211が備えられ、この部屋でグロー放電プラズマを利用した膜の形成が行われる。ガス供給手段211はSiH<sub>4</sub>、N<sub>2</sub>O、H<sub>2</sub>、O<sub>2</sub>などのガスが流量を制御して供給できるようになっている。

## 【0036】

10

20

30

40

50

反応室は1室のみの構成であるが、酸化窒化シリコン膜(A)と(B)はSiH<sub>4</sub>、N<sub>2</sub>O、H<sub>2</sub>の供給量や、高周波電力、反応圧力の制御ができるので同じ反応室で連続して形成することができる。むしろ、基板のサイズが大型化した場合には設置する床面積を小さくすることができるとなり省スペース化に寄与する。

【0037】

図2(B)に示す装置の構成は、ロード室220、アンロード室221、共通室222があり、共通室222の中に反応室223～225が設けられた構成である。ロード室220、アンロード室221はそれぞれ基板236、238とそれを保持するカセット235、237が備えられ、仕切弁226、227で共通室と分離されている。ロード室220から搬送手段233により搬出された基板は反応室223～225のいずれの部屋にもセットすることが可能である。 10

【0038】

反応室223～225にはプラズマ発生手段240、基板加熱手段241、ガス供給手段239が備えられ、この部屋でグロー放電プラズマを利用した膜の形成が行われる。それぞれの反応室には仕切弁230a～232a、230b～232bが設けられ、真空ポンプなどを備えた減圧手段342により個別に圧力が制御できる。従って、成膜条件をそれぞれ個別に制御して膜の堆積をすることが可能である。または、それぞれの反応室で同時に、或いは並列して膜を形成することも可能であり生産性の向上を図ることもできる。

【0039】

酸化窒化シリコン膜(A)と(B)はSiH<sub>4</sub>、N<sub>2</sub>O、H<sub>2</sub>の供給量や、高周波電力、反応圧力の制御ができるので同じ反応室で連続して形成することができ、上記膜の2層構造としても良いし、ガスの供給量を成膜時間と共に変化させて組成を連続的に変化させても良い。いずれにしても、図2(B)の装置の構成は生産性の向上に寄与する。 20

【0040】

【実施例】

[実施例1]

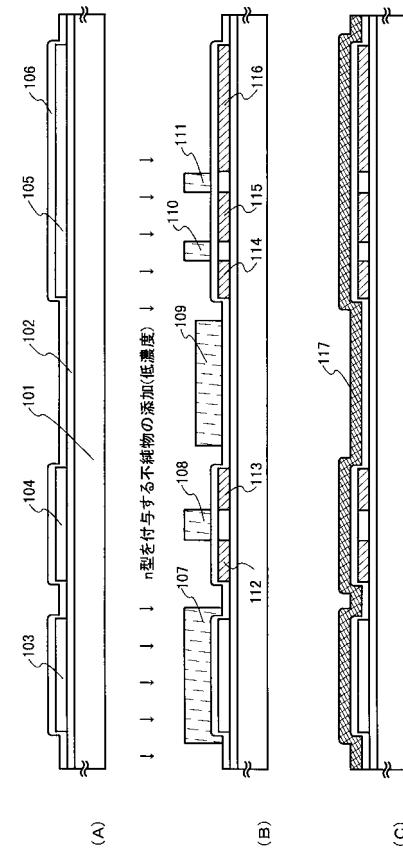

本発明を利用した酸化窒化シリコン膜と半導体膜(本実施例では結晶質シリコン膜)とを作製する工程について説明する。以下、図3を用いて本実施例を示す。

【0041】

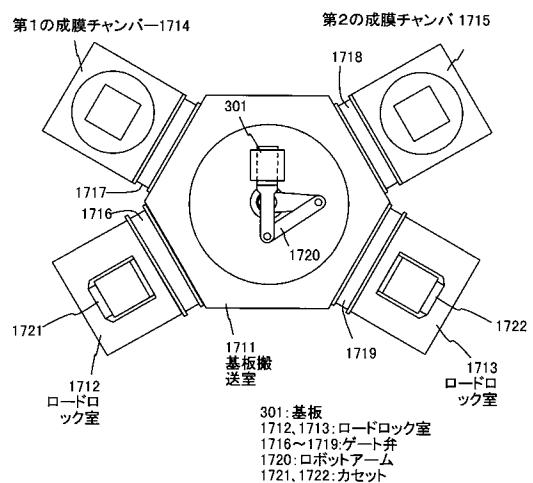

本実施例では、図17に示す枚葉式のプラズマCVD装置(基板搬送室1711、ロードロック室1712、1713、第1の成膜チャンバー1714、第2の成膜チャンバー1715、ゲート弁1716～1719等を備えた)を用いた。 30

【0042】

まず、ロードロック室1712のカセット1721に基板301をセットする。基板301にはコーニング社の7059ガラス基板や#1737ガラス基板に代表されるバリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどを用いる。このようなガラス基板には微量ではあるが、ナトリウムなどのアルカリ金属元素などが含まれている。

【0043】

次いで、基板301を第1成膜チャンバー1714に搬入し、加熱して基板温度を約400にする。第1成膜チャンバー1714に搬入する前に、予熱室等を用いて基板を加熱してもよい。 40

【0044】

そして、図3に示すように基板301からのアルカリ金属元素やその他の不純物の汚染を防ぐためのブロッキング層として下地膜302を形成する。表1に記載された作製条件を基に、基板側との界面を酸化窒化シリコン膜(B)で形成し、その組成から酸化窒化シリコン膜(A)の組成へ連続的に組成が変化するようにSiH<sub>4</sub>、N<sub>2</sub>O、H<sub>2</sub>のガス流量をマスフローコントローラーで制御する。窒素含有量の多い酸化窒化シリコン膜(B)を基板側に設けることによって基板から活性層への不純物拡散を防止でき窒素含有量の少ない酸化窒化シリコン膜(A)を活性層側に設けることによって活性層と良好な界面状態を保つことができる。図3では組成が丁度中間の値を示すところを点線で示す。その部分は膜厚の中央 50

部であっても良いし、半導体層寄り或いはゲート電極寄りであっても良い。具体的には、最初SiH<sub>4</sub>を5SCCM、N<sub>2</sub>Oを120SCCM、H<sub>2</sub>を125SCCM流し、Xh=1でXg=0.96とし、20Paに圧力を制御して27MHzで0.4mW/cm<sup>2</sup>の高周波電力を投入して成膜を開始し、その後成膜速度を考慮して随時N<sub>2</sub>O流量を成膜終了時に500SCCMとなるように増加させ、H<sub>2</sub>流量を0SCCMとして、Xh=0でXg=0.99となるように減少させる制御を行う。SiH<sub>4</sub>の流量は5SCCMから4SCCMへの制御なので、図3で示す点線のところで切り替えた。このようにして150nmの厚さで下地膜を形成した。勿論、下地膜の厚さはこれに限定されるものではなく、50～300nm（好ましくは、80～150nm）の厚さで形成し、前述のように酸化窒化シリコン膜（A）と（B）を積層する構造としても良い。尚、ここで示す成膜条件は一例であり、表2で示した組成が得られるならば成膜条件に何ら限定される事項はない。

10

#### 【0045】

下地膜の成膜前に行うプラズマクリーニング処理は効果的である。また、プラズマクリーニング処理は、水素を200SCCM導入し、圧力20Pa、高周波電力0.2W/cm<sup>2</sup>でプラズマを生成して2分間処理する。或いは、H<sub>2</sub>を100SCCMと酸素を100SCCM導入して、圧力40Paで同様にプラズマ処理しても良い。また、N<sub>2</sub>Oと水素を導入して圧力10～70Pa、高周波電力密度0.1～0.5W/cm<sup>2</sup>で数分間処理してもよい。基板温度は300～450、好ましくは400とする。この段階で、基板301の表面をプラズマクリーニング処理することで、吸着しているボロンやリン、その他の有機物などの汚染物質を取り除くことができる。

#### 【0046】

こうして、膜中におけるN、O、Hの組成比が連続的に変化している酸化窒化シリコン膜12が得られる。この酸化窒化シリコン膜12は膜中において組成勾配を有しており、基板側の界面に向かって連続的に窒素及び水素が増加している。

20

#### 【0047】

次いで、第1成膜チャンバー1714内のガスを真空引き、あるいはN<sub>2</sub>等の不活性ガスで置換した後、基板搬送室を経由して第2成膜チャンバー1715に基板を搬送する。

#### 【0048】

次いで、酸化窒化シリコン膜302上に接して半導体膜303、ここでは非晶質シリコン膜を第2の成膜チャンバー1715で成膜した。

#### 【0049】

ここでは、酸化窒化シリコン膜302と半導体膜とは、同じ成膜法で形成することが可能であるので両者を同一チャンバーで連続形成しても良い。連続成膜することによって、酸化窒化シリコン膜302の形成後、一旦搬送時の酸化窒化シリコン膜表面の汚染を防ぐことが可能となり、作製されるTFTの特性バラツキや閾値電圧の変動を低減させることができる。また、処理時間の短縮も図れ生産性が向上する。

30

#### 【0050】

次いで、非晶質珪素膜が成膜された基板は、基板搬送室1711を経由してロードロック室1712に搬送され、カセット1722にセットされる。

#### 【0051】

次いで、酸化窒化シリコン膜302と非晶質半導体膜とが積層形成された基板を公知の結晶化技術により結晶質半導体膜を形成した。

40

#### 【0052】

以降の工程は、公知の技術を用いてTFTを形成すればよい。

#### 【0053】

#### [実施例2]

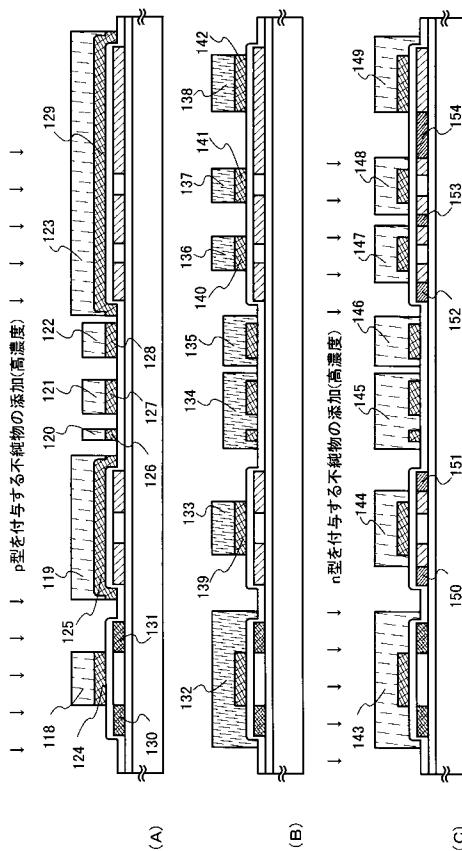

以下、本発明の一実施例として同一基板上に画素マトリクス回路とドライバ回路を一体化したアクティブマトリクス型の液晶表示装置に適用した場合について、図4～図10を用いて説明する。

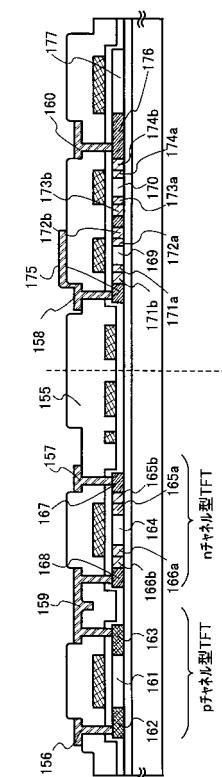

#### 【0054】

図4(A)は断面図であり、101は絶縁性基板であり、例えばコーニング社の1737ガラス基板である。このガラス基板上には、基板からの不純物拡散防止のための下地膜とし

50

てN、O、Hの組成比が連続的に変化している酸化窒化シリコン膜102と非晶質半導体膜103との積層膜を形成する。この積層膜の形成方法としてここでは、実施例1に示した方法を用い、膜厚150nmの下地膜と、膜厚50nmの非晶質シリコン膜とをそれぞれ形成した。

#### 【0055】

次いで、非晶質シリコン膜は含有水素量にもよるが、好ましくは400～550で数時間加熱して脱水素処理を行い、含有水素量を5atomic%以下として、結晶化の工程を行う。これにより、膜表面の荒れを防ぐことができる。プラズマCVD法にて非晶質シリコン膜を形成する場合、反応ガスにSiH<sub>4</sub>とArを用いて成膜時の基板温度を300～400で形成すると、非晶質シリコン膜の含有水素濃度を5atomic%以下にすることもできる。このような場合には脱水素処理は不要となる。

#### 【0056】

非晶質シリコン膜を結晶化する工程は、公知のレーザーアニール法または熱アニール法を用いれば良い。結晶化をレーザーアニール法で行う場合には、パルス発振型または連続発光型のエキシマレーザーやアルゴンレーザーをその光源とする。パルス発振型のエキシマレーザーを用いる場合にはレーザー光を線状に加工してレーザーアニールを行う。レーザーアニール条件は実施者が適宜選択するが、例えばレーザーパルス発振周波数30Hzとし、レーザーエネルギー密度を100～500mJ/cm<sup>2</sup>（代表的には300～400mJ/cm<sup>2</sup>）とする。そして、線状ビームを基板全面に渡って照射し、この時の線状ビームの重ね合わせ率（オーバーラップ率）を80～90%として行う。このようにして、結晶質半導体層を形成することができる。また、別な方法としてパルス発振型のYAGレーザーを使用する方法がある。第2高調波（532nm）～第3高調波を使用し、例えばレーザーパルス発振周波数1～20000Hz（好ましくは10～10000Hz）、レーザーエネルギー密度を200～600mJ/cm<sup>2</sup>（代表的には300～500mJ/cm<sup>2</sup>）とする。そして、線状ビームを基板全面に渡って照射し、この時の線状ビームの重ね合わせ率（オーバーラップ率）を80～90%として行う。第2高調波を使うと、半導体層の内部にも均一に熱が伝わり、照射エネルギー範囲が多少ばらついても結晶化が可能となる。それにより、加工マージンがとれるため結晶化のばらつきが少なくなる。また、パルス周波数が高いのでスループットが向上する。熱アニール法による場合にはファーネスアニール炉を用い、窒素雰囲気で600～660程度の温度でアニールを行う。いずれにしても非晶質半導体層を結晶化させると原子の再配列が起こり緻密化するので作製される結晶質半導体層の厚さは当初の非晶質半導体層の厚さよりも1～15%程度減少する。本実施例では、パルス発振型のKrFエキシマレーザー光を線状に集光して非晶質シリコン膜に照射して結晶質シリコン膜を形成した。

#### 【0057】

こうして形成された結晶質シリコン膜を第1のフォトマスクを使用して島状にパターニングし、ドライエッチングによりドライバ回路のpチャネルTFTの活性層103、nチャネルTFTの活性層104、画素TFTの活性層105を形成した。

#### 【0058】

尚、本実施例では島状の半導体層を非晶質シリコン膜から結晶質シリコン膜を形成したが、微結晶シリコン膜を用いても構わないし、直接結晶質シリコン膜を成膜しても良い。

#### 【0059】

次に、島状の半導体層103、104、105を覆って、酸化シリコンまたは窒化シリコンを主成分とするゲート絶縁膜106を形成した。ゲート絶縁膜106は、プラズマCVD法でN<sub>2</sub>OとSiH<sub>4</sub>を原料とした酸化窒化シリコン膜を10～200nm、好ましくは50～150nmの厚さで形成すれば良い。ここでは100nmの厚さに形成した。（図4(A)）

#### 【0060】

そして、第2のフォトマスクにより、半導体層103と、半導体層104、105のチャネル形成領域を覆うレジストマスク107、108、109、110、111を形成した。このとき、配線を形成する領域にもレジストマスク109を形成しておいても良い。

#### 【0061】

10

20

30

40

50

そして、n型を付与する不純物元素を添加して第2の不純物領域を形成する工程を行った。ここでは、リンを用い、フォスフィン( $\text{PH}_3$ )を用いたイオンドープ法で行った。この工程では、ゲート絶縁膜106を通してその下の半導体層にリンを添加するために、加速電圧は80keVに設定した。半導体層に添加されるリンの濃度は、 $1 \times 10^{16} \sim 1 \times 10^{19} \text{ atoms/cm}^3$ の範囲にするのが好ましく、ここでは $1 \times 10^{18} \text{ atoms/cm}^3$ とした。そして、半導体層にリンが添加された領域112、113、114、115、116が形成された。ここで、リンが添加された領域の一部は、LDD領域として機能する第2の不純物領域とされるものである。(図4(B))

#### 【0062】

その後、レジストマスクを除去して、第1の導電層117を全面に形成した。第1の導電層117は、Ta、Ti、Mo、W、Cr、Alから選ばれた元素を主成分とする導電性材料やリンを含有するシリコンやシリサイドなどの単層膜あるいは積層膜から成る。例えば、 $\text{WMo}$ 、 $\text{TaN}$ 、 $\text{MoTa}$ 、 $\text{Wsix}$  ( $2.4 > x > 2.7$ )などの化合物を用いることができる。そして、第1の導電層417の厚さは100~1000nm、好ましくは150~400nmで形成しておけば良い。ここではTaをスパッタ法で形成した。(図4(C))

#### 【0063】

次に、第3のフォトマスクによりレジストマスク118、119、120、121、122、123を形成した。第3のフォトマスクは、pチャネル型TFTのゲート電極と、CMOS回路および画素部のゲート配線、ゲートバスラインを形成するためのものである。nチャネル型TFTのゲート電極は後の工程で形成するため、第1の導電層117が半導体層104、105上の全面で残るようにレジストマスク119、123を形成した。(図5(A))

#### 【0064】

第1の導電層はドライエッチング法により不要な部分を除去した。Taのエッチングは $\text{CF}_4$ と $\text{O}_2$ の混合ガスにより行われた。そして、ゲート電極124と、ゲート配線126、128と、ゲートバスライン127が形成された。

#### 【0065】

そして、レジストマスク118、119、120、121、122、123をそのまま残して、pチャネル型TFTが形成される半導体層103の一部に、p型を付与する第3の不純物元素を添加するの工程を行った。ここではボロンをその不純物元素として、ジボラン( $\text{B}_2\text{H}_6$ )を用いてイオンドープ法で添加した。ここでも加速電圧を80keVとして、 $2 \times 10^{20} \text{ atoms/cm}^3$ の濃度にボロンを添加した。そして、図5(A)に示すようにボロンが高濃度に添加された第3の不純物領域130、131が形成された。

#### 【0066】

図5(A)で設けられたレジストマスクを除去した後、新たに第4のフォトマスクによりレジストマスク132、133、134、135、136、137、138を形成した。第4のフォトマスクはnチャネル型TFTのゲート電極を形成するためのものであり、ドライエッチング法によりゲート電極139、140、141及び容量電極142が形成された。このときゲート電極139、140、141は第2の不純物領域112、113、114、115、116の一部と重なるように形成された。(図5(B))

#### 【0067】

そして、レジストマスクを除去した後、新たなレジストマスク143、144、145、146、147、148、149を形成した。レジストマスク144、147、148はnチャネル型TFTのゲート電極139、140、141と、第2の不純物領域の一部を覆う形で形成されるものであった。ここで、レジストマスク144、147、148は、LDD領域のオフセット量を決めるものであった。

#### 【0068】

そして、n型を付与する不純物元素を添加して第1の不純物領域を形成する工程を行った。そして、ソース領域となる第1の不純物領域151、152とドレイン領域となる第1の不純物領域150、153、154が形成された。ここでは、フォスフィン( $\text{PH}_3$ )を用いたイオンドープ法で行った。この工程でも、ゲート絶縁膜106を通してその下の半導

10

20

30

40

50

体層にリンを添加するために、加速電圧は80keVに設定した。この領域のリンの濃度はn型を付与する第1の不純物元素を添加する工程と比較して高濃度であり、 $1 \times 10^{19} \sim 1 \times 10^{21}$  atoms/cm<sup>3</sup>とするのが好ましく、ここでは $1 \times 10^{20}$  atoms/cm<sup>3</sup>とした。（図5（C））

#### 【0069】

図5（C）までの工程が終了したら、図6に示すように、ゲート電極およびゲート絶縁膜上に第1の層間絶縁膜155を形成する工程を行った。第1の層間絶縁膜は酸化シリコン膜、酸化窒化シリコン膜、窒化シリコン膜、またはこれらを組み合わせた積層膜で形成すれば良い。いずれにしても第1の層間絶縁膜155は無機絶縁物材料から形成する。第1の層間絶縁膜155の膜厚は100～200nmとする。ここで、酸化シリコン膜を用いる場合には、プラズマCVD法でTEOSとO<sub>2</sub>とを混合し、反応圧力40Pa、基板温度300～400 とし、高周波（13.56MHz）電力密度0.5～0.8W/cm<sup>2</sup>で放電させて形成することができる。また、酸化窒化シリコン膜を用いる場合には、プラズマCVD法でSiH<sub>4</sub>、N<sub>2</sub>O、NH<sub>3</sub>から作製される酸化窒化シリコン膜、またはSiH<sub>4</sub>、N<sub>2</sub>Oから作製される酸化窒化シリコン膜で形成すれば良い。この場合の作製条件は反応圧力20～200Pa、基板温度300～400 とし、高周波（60MHz）電力密度0.1～1.0W/cm<sup>2</sup>で形成することができる。また、SiH<sub>4</sub>、N<sub>2</sub>O、H<sub>2</sub>から作製される酸化窒化水素化シリコン膜を適用しても良い。窒化シリコン膜も同様にプラズマCVD法でSiH<sub>4</sub>、NH<sub>3</sub>から作製することが可能である。

10

#### 【0070】

そして、熱処理の工程を行った。熱処理の工程は、それぞれの濃度で添加されたn型またはp型を付与する不純物元素を活性化するために行う必要があった。第1の層間絶縁膜が積層である場合、下層となる絶縁膜を成膜した後、熱処理工程を行うと良い。この工程は、電気加熱炉を用いた熱アニール法や、前述のエキシマレーザーを用いたレーザーアニール法や、ハロゲンランプを用いたラピットサーマルアニール法（RTA法）で行えれば良い。ここでは熱アニール法で活性化の工程を行った。加熱処理は、酸素濃度が1ppm以下好ましくは0.1ppm以下の窒素雰囲気中において400～700 、好ましくは500～600 、ここでは500 、4時間の処理を行った。

20

#### 【0071】

熱活性化工程の後、さらに、3～100%の水素を含む雰囲気中300～450 で1～12時間の熱処理を行い、島状半導体層を水素化する工程を行った。この工程は熱的に励起された水素により半導体層のダングリングボンドを終端する工程である。水素化の他の手段としてプラズマ水素化（プラズマにより励起された水素を用いる）を行っても良い。いずれにしても、半導体層中の欠陥密度を10<sup>16</sup>/cm<sup>3</sup>以下とすることが望ましく、そのため、水素を0.01～0.1atomic%程度付与すれば良い。

30

#### 【0072】

第1の層間絶縁膜155はその後、パターニングでそれぞれのTFTのソース領域と、ドレイン領域に達するコンタクトホールが形成された。そして、ソース電極156、157、158とドレイン電極159、160を形成した。図示していないが、本実施例ではこの電極を、Ti膜を100nm、Tiを含むAl膜300nm、Ti膜150nmをスパッタ法で連続して成膜し、この3層膜をパターニングして電極として用いた。

40

#### 【0073】

以上の工程で、CMOS回路のnチャネル型TFTにはチャネル形成領域164、第1の不純物領域167、168、第2の不純物領域165、166が形成された。ここで、第2の不純物領域は、ゲート電極と重なる領域（GOLD領域）165a、166a、ゲート電極と重ならない領域（LDD領域）165b、166bがそれぞれ形成された。そして、第1の不純物領域167はソース領域として、第1の不純物領域168はドレイン領域となった。

#### 【0074】

pチャネル型TFTは、チャネル形成領域161、第3の不純物領域162、163が形成された。そして、第3の不純物領域162はソース領域として、第3の不純物領域163はドレイン領域となった。

#### 【0075】

50

また、画素部のnチャネル型TFTはマルチゲート構造であり、チャネル形成領域169、170と第1の不純物領域175、176と第2の不純物領域171、172、173、174が形成された。ここで第2の不純物領域は、ゲート電極と重なる領域171a、172a、173a、174aと重ならない領域171b、172b、173b、174bとが形成された。

【0076】

こうして図6に示すように、基板101上にCMOS回路と、画素部が形成されたアクティブマトリクス基板が作製された。また、画素部のnチャネル型TFTのドレイン側には、第2の不純物領域と同じ濃度でn型を付与する不純物元素が添加された低濃度不純物領域177と、ゲート絶縁膜106と、容量電極142とにより保持容量が同時に形成された。

10

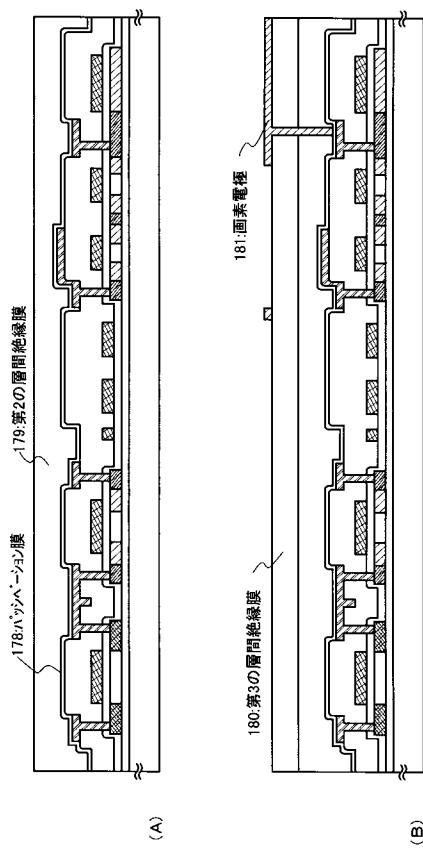

【0077】

次いで、アクティブマトリクス基板から、アクティブマトリクス型液晶表示装置を作製する工程を説明する。

【0078】

図6の状態のアクティブマトリクス基板に対して、パッシベーション膜178を形成した。パッシベーション膜178は、窒化シリコン膜で300nmの厚さで形成した。また、パッシベーション膜成膜後に水素化処理を行うとTFT特性向上に対して好ましい結果が得られている。例えば、3~100%の水素を含む雰囲気中300~450で1~12時間の熱処理を行うと良く、あるいはプラズマ水素化法を用いても同様の効果が得られた。

20

【0079】

さらに、有機樹脂からなる第2の層間絶縁膜179を約1000nmの厚さに形成した。有機樹脂膜としては、ポリイミド、アクリル、ポリイミドアミド等を使用することができる。有機樹脂膜を用いることの利点は、成膜方法が簡単である点や、比誘電率が低いので、寄生容量を低減できる点、平坦性に優れる点などが上げられる。なお上述した以外の有機樹脂膜を用いることもできる。ここでは、基板に塗布後、熱重合するタイプのポリイミドを用い、300で焼成して形成した。(図7(A))

【0080】

さらに第3の層間絶縁膜180を形成した。第3の層間絶縁膜180は、ポリイミドなどの有機樹脂膜で形成した。そして、第3の層間絶縁膜180、第2の層間絶縁膜179、及びパッシベーション膜178を選択的に除去してドレイン電極160に達するコンタクトホールを形成し、画素電極181を形成した。画素電極181は、透過型液晶表示装置とする場合には透明導電膜を用い、反射型の液晶表示装置とする場合には金属膜を用いれば良い。ここでは透過型の液晶表示装置とするために、酸化インジウム・スズ(ITO)膜を100nmの厚さにスパッタ法で形成した後、パターニングして画素電極181を形成した。(図7(B))

30

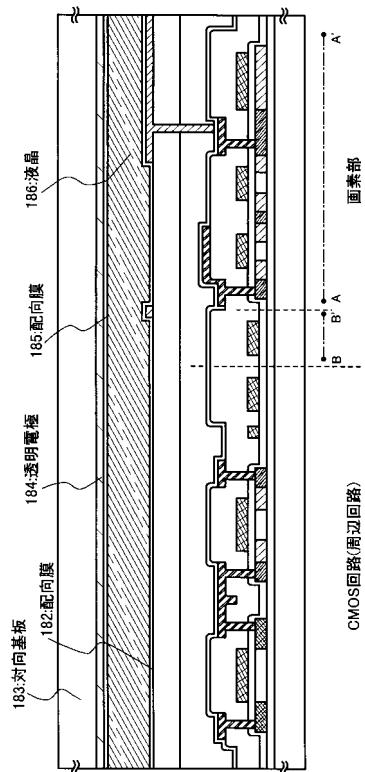

【0081】

次に、図8に示すように、配向膜182を第3の層間絶縁膜180と画素電極181とに接して形成する。通常液晶表示素子の配向膜にはポリイミド樹脂が多く用いられている。対向側の基板183には、透明導電膜184と、配向膜185とを形成した。配向膜は形成された後、ラビング処理を施して液晶分子がある一定のプレチルト角を持って平行配向するようにした。

40

【0082】

上記の工程を経て、画素部と、CMOS回路が形成されたアクティブマトリクス基板と対向基板とを、公知のセル組み工程によってシール材やスペーサ(共に図示せず)などを介して貼りあわせる。その後、両基板の間に液晶材料186を注入し、封止剤(図示せず)によって完全に封止した。こうして図8に示すアクティブマトリクス型液晶表示装置が完成了。

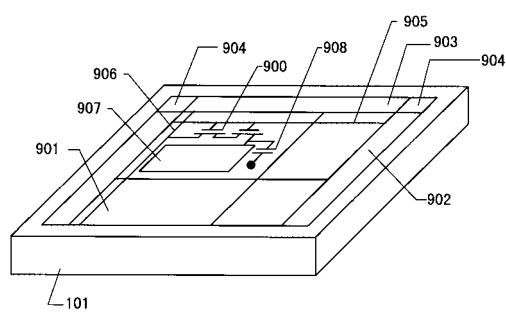

【0083】

次に本実施例のアクティブマトリクス型液晶表示装置の構成を、図9と図10を用いて説明する。図9は本実施例のアクティブマトリクス基板の斜視図である。アクティブマトリク

50

ス基板は、ガラス基板101上に形成された、画素部901と、走査(ゲート)線駆動回路902と、信号(ソース)線駆動回路903と、ロジック回路904とで構成される。画素部の画素TFT900はnチャネル型TFTであり、周辺に設けられる駆動回路はCMOS回路を基本として構成されている。走査(ゲート)線駆動回路902と、信号(ソース)線駆動回路903はそれぞれゲート配線905とソース配線906で画素部901に接続されている。画素部901は画素TFT900と、画素電極907と、保持容量908とで形成される。

【0084】

本実施例では、画素TFT900をダブルゲートの構造としているが、シングルゲートの構造でも良いし、トリプルゲートとしたマルチゲート構造にしても構わない。本実施例のアクティブマトリクス基板の構造は、本実施例の構造に限定されるものではない。本願発明の構造は、下地膜の構成に特徴があるので、それ以外の構成については実施者が適宣決定すれば良い。

【0085】

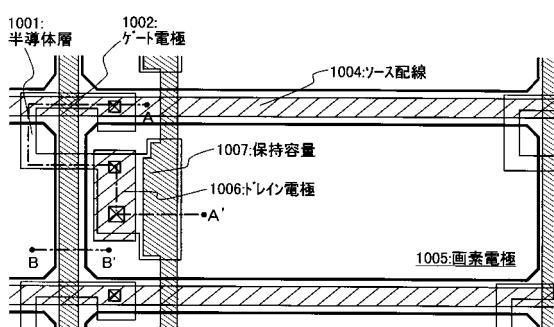

図10は画素部901の上面図の一部であり、ほぼ1画素の上面図である。画素部にはnチャネル型TFTが設けられている。ゲート電極1002は、図示されていないゲート絶縁膜を介してその下の半導体層1001と交差している。図示はしていないが、半導体層には、ソース領域、ドレイン領域、第1の不純物領域が形成されている。また、画素TFTのドレン側には、半導体層と、ゲート絶縁膜と、ゲート電極と同じ材料で形成された電極とから、保持容量1007が形成されている。また、図10で示すA-A'、およびB-B'に沿った断面構造は、図8に示す画素部の断面図に対応している。

【0086】

[実施例3]

本実施例では、実施例2において半導体層として用いる結晶質半導体膜を、触媒元素を用いた熱結晶化法により形成する例を示す。触媒元素を用いる場合、特開平7-130652号公報、特開平8-78329号公報で開示された技術を用いることが望ましい。

【0087】

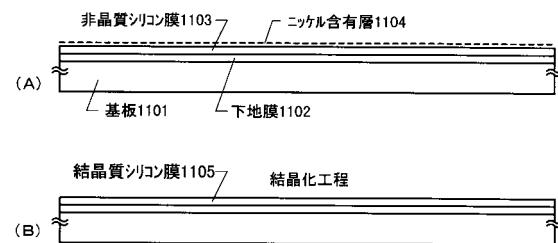

ここで、特開平7-130652号公報に開示されている技術を本願発明に適用する場合の例を図11に示す。まず基板1101上下地膜としてN、O、Hの組成が連続的に変化している酸化窒化シリコン膜1102を設け、その上に非晶質シリコン膜1103を形成した。この積層膜の形成方法としてここでは、実施例1に示した方法を用い、膜厚200nmの下地膜と、膜厚50nmの非晶質シリコン膜とをそれぞれ形成した。

【0088】

次いで、図11(A)にあるように重量換算で10ppmの触媒元素であるニッケルを含む酢酸ニッケル塩溶液をスピンドルコーターで塗布した。これにより、結晶化を助長する元素であるニッケルが非晶質シリコン膜に添加され、ニッケル含有層1104が形成された。

【0089】

次に、500、1時間の脱水素工程により水素含有量を5atomic%以下にした後、500~650で4~12時間、例えば550、8時間の熱処理を行い、結晶質シリコン膜1105を形成した。こうして得られた結晶質シリコン膜1105は非常に優れた結晶性を示した。(図11(B))

【0090】

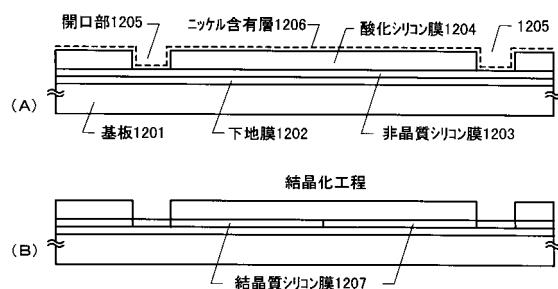

また、特開平8-78329号公報で開示された技術は、触媒元素を選択的に添加することによって、非晶質半導体膜の選択的な結晶化を可能としたものである。同技術を本願発明に適用した場合について、図12で説明する。

【0091】

まず、ガラス基板1201上にNまたはOの組成が連続的に変化している酸化窒化シリコン膜を含む下地膜1202を設け、その上に非晶質シリコン膜1203、酸化シリコン膜1204を連続的に形成した。この時、酸化シリコン膜1204の厚さは150nmとした。この下地膜1202の形成方法としてここでは、実施例1に示した方法を用いた下地膜を形

10

20

30

40

50

成した。

【0092】

次に酸化シリコン膜1204をパターニングして、選択的に開孔部1205を形成し、その後、重量換算で10ppmのニッケルを含む酢酸ニッケル塩溶液を塗布した。これにより、ニッケル含有層1206が形成され、ニッケル含有層1206は開孔部1205の底部のみで非晶質シリコン膜1203と接触した。(図12(A))

【0093】

次に、500～650で4～24時間、例えば570、14時間の熱処理を行い、結晶質シリコン膜1207を形成した。この結晶化の過程では、ニッケルが接した非晶質シリコン膜の部分が最初に結晶化し、そこから横方向へと結晶化が進行する。こうして形成された結晶質シリコン膜1207は棒状または針状の結晶が集合して成り、その各々の結晶は巨視的に見ればある特定の方向性をもって成長しているため、結晶性が揃っているという利点がある。(図12(B))

【0094】

尚、上記2つの技術において使用可能な触媒元素は、ニッケル(Ni)の以外にも、ゲルマニウム(Ge)、鉄(Fe)、パラジウム(Pd)、スズ(Sn)、鉛(Pb)、コバルト(Co)、白金(Pt)、銅(Cu)、金(Au)、といった元素を用いても良い。

【0095】

以上のような技術を用いて結晶質半導体膜(結晶質シリコン膜や結晶質シリコンゲルマニウム膜などを含む)を形成し、パターニングを行えば、結晶質TFTの半導体層を形成することができる。本実施例の技術を用いて、結晶質半導体膜から作製されたTFTは、優れた特性が得られるが、そのため高い信頼性を要求されていた。しかしながら、本願発明のTFT構造を採用することで、本実施例の技術を最大限に生かしたTFTを作製することが可能となった。

【0096】

[実施例4]

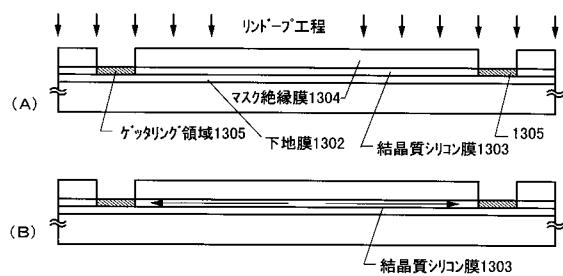

本実施例は、実施例3で用いられる半導体層を形成する方法として、非晶質半導体膜を初期膜として前記触媒元素を用いて結晶質半導体膜を形成した後で、その触媒元素を結晶質半導体膜から除去する工程を行った例を示す。本実施例ではその方法として、特開平10-135468号公報または特開平10-135469号公報に記載された技術を用いた。

【0097】

同公報に記載された技術は、非晶質半導体膜の結晶化に用いた触媒元素を結晶化後にリンのゲッタリング作用を用いて除去する技術である。同技術を用いることで、結晶質半導体膜中の触媒元素の濃度を $1 \times 10^{17}$ atms/cm<sup>3</sup>以下、好ましくは $1 \times 10^{16}$ atms/cm<sup>3</sup>にまで低減することができる。

【0098】

本実施例の構成について図13を用いて説明する。ここではコーニング社の1737基板に代表される無アルカリガラス基板を用いた。図13(A)では、実施例3で示した結晶化の技術を用いて、基板1301上に下地膜1302、結晶質シリコン膜1303が形成された状態を示している。この下地膜1302の形成方法としてここでは、実施例1に示した方法を用いる。そして、結晶質シリコン膜1303の表面にマスク用の酸化シリコン膜1304が150nmの厚さに形成され、パターニングにより開孔部が設けられ、結晶質シリコン膜を露出させた領域を設けてある。そして、リンを添加する工程を実施して、結晶質シリコン膜にリンが添加された領域1305が設けられた。

【0099】

この状態で、窒素雰囲気中で550～800、5～24時間、例えば600、12時間の熱処理を行うと、結晶質シリコン膜にリンが添加された領域1305がゲッタリングサイトとして働き、結晶質シリコン膜1303に残存していた触媒元素はリンが添加された領域1305に偏析させることができた。

10

20

30

40

50

## 【0100】

そして、マスク用の酸化シリコン膜1304と、リンが添加された領域1305とをエッチングして除去することにより、結晶化の工程で使用した触媒元素の濃度を $1 \times 10^{17}$ atms/cm<sup>3</sup>以下にまで低減された結晶質シリコン膜を得ることができた。この結晶質シリコン膜はそのまま実施例2で示した本願発明のTFTの半導体層として使用することができ、このようにして作製したTFTはオフ電流値が下がり結晶性が良いことから高い電界効果移動度が得られ、良好な特性が得られる。

## 【0101】

## [実施例5]

本願発明を実施して形成されたTFTは様々な電気光学装置（代表的にはアクティブマトリクス型液晶ディスプレイ等）に用いることができる。即ち、それら電気光学装置や半導体回路を部品として組み込んだ電子機器全てに本願発明を実施できる。

10

## 【0102】

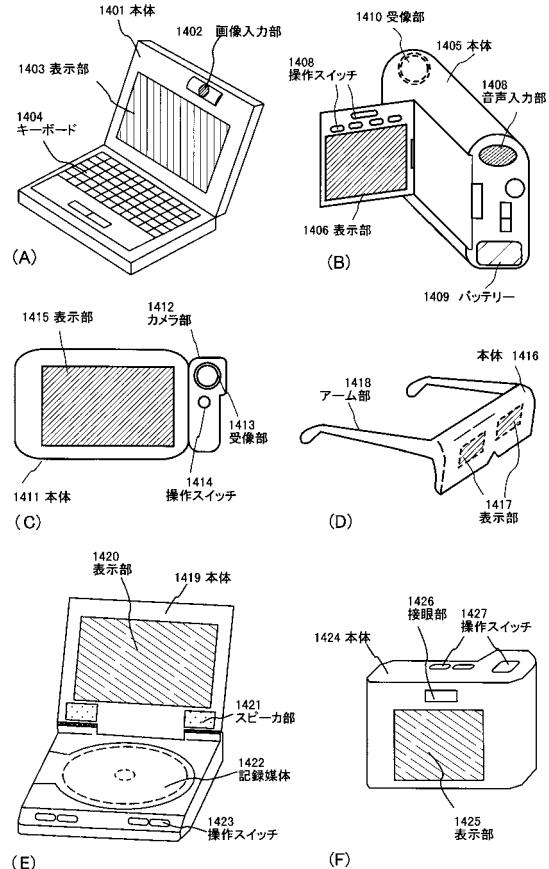

その様な電子機器としては、ビデオカメラ、デジタルカメラ、プロジェクター（リア型またはフロント型）、ヘッドマウントディスプレイ（ゴーグル型ディスプレイ）、カーナビゲーション、カーステレオ、パーソナルコンピュータ、携帯情報端末（モバイルコンピュータ、携帯電話または電子書籍等）などが挙げられる。それらの一例を図14、図15及び図16に示す。

## 【0103】

図14（A）はパーソナルコンピュータであり、本体1401、画像入力部1402、表示部1403、キーボード1404等を含む。本発明を画像入力部1402、表示部1403やその他の信号制御回路に適用することができる。

20

## 【0104】

図14（B）はビデオカメラであり、本体1405、表示部1406、音声入力部1407、操作スイッチ1408、バッテリー1409、受像部1410等を含む。本発明を表示部1406やその他の信号制御回路に適用することができる。

## 【0105】

図14（C）はモバイルコンピュータ（モービルコンピュータ）であり、本体1411、カメラ部1412、受像部1413、操作スイッチ1414、表示部1415等を含む。本発明は表示部1415やその他の信号制御回路に適用できる。

30

## 【0106】

図14（D）はゴーグル型ディスプレイであり、本体1416、表示部1417、アーム部1418等を含む。本発明は表示部1417やその他の信号制御回路に適用することができる。

## 【0107】

図14（E）はプログラムを記録した記録媒体（以下、記録媒体と呼ぶ）を用いるプレーヤーであり、本体1419、表示部1420、スピーカ部1421、記録媒体1422、操作スイッチ1423等を含む。なお、このプレーヤーは記録媒体としてDVD（Digital Versatile Disc）、CD等を用い、音楽鑑賞や映画鑑賞やゲームやインターネットを行うことができる。本発明は表示部1420やその他の信号制御回路に適用することができる。

40

## 【0108】

図14（F）はデジタルカメラであり、本体1424、表示部1425、接眼部1426、操作スイッチ1427、受像部（図示しない）等を含む。本願発明を表示部1425やその他の信号制御回路に適用することができる。

## 【0109】

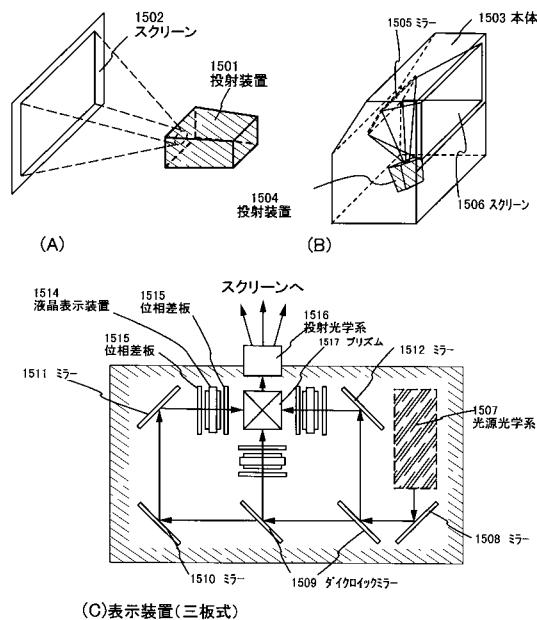

図15（A）はフロント型プロジェクターであり、投射装置1501、スクリーン1502等を含む。本発明は投射装置1501の一部を構成する液晶表示装置1514やその他の信号制御回路に適用することができる。

## 【0110】

50

図15(B)はリア型プロジェクターであり、本体1503、投射装置1504、ミラー1505、スクリーン1506等を含む。本発明は投射装置1504の一部を構成する液晶表示装置1514やその他の信号制御回路に適用することができる。

【0111】

なお、図15(C)は、図15(A)及び図15(B)中における投射装置1501、1504の構造の一例を示した図である。投射装置1501、1504は、光源光学系1507、ミラー1508、1510～1512、ダイクロイックミラー1509、プリズム1513、液晶表示装置1514、位相差板1515、投射光学系1516で構成される。投射光学系1516は、投射レンズを含む光学系で構成される。本実施例は三板式の例を示したが、特に限定されず、例えば単板式であってもよい。また、図15(C)中において矢印で示した光路に実施者が適宜、光学レンズや、偏光機能を有するフィルムや、位相差を調節するためのフィルム、IRフィルム等の光学系を設けてもよい。

【0112】

また、図15(D)は、図15(C)中における光源光学系1507の構造の一例を示した図である。本実施例では、光源光学系1507は、リフレクター1518、光源1519、レンズアレイ1520、1521、偏光変換素子1522、集光レンズ1523で構成される。なお、図15(D)に示した光源光学系は一例であって特に限定されない。例えば、光源光学系に実施者が適宜、光学レンズや、偏光機能を有するフィルムや、位相差を調節するフィルム、IRフィルム等の光学系を設けてもよい。

【0113】

ただし、図15に示したプロジェクターにおいては、透過型の電気光学装置を用いた場合を示しており、反射型の電気光学装置の適用例は図示していない。

【0114】

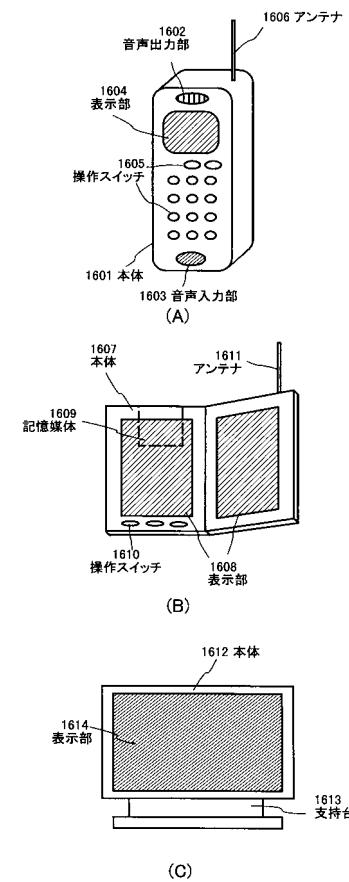

図16(A)は携帯電話であり、本体1601、音声出力部1602、音声入力部1603、表示部1604、操作スイッチ1605、アンテナ1606等を含む。本願発明を音声出力部1602、音声入力部1603、表示部1604やその他の信号制御回路に適用することができる。

【0115】

図16(B)は携帯書籍(電子書籍)であり、本体1607、表示部1608、記憶媒体1609、操作スイッチ1610、アンテナ1611等を含む。本発明は表示部1608、1609やその他の信号回路に適用することができる。

【0116】

図16(C)はディスプレイであり、本体1612、支持台1613、表示部1614等を含む。本発明は表示部1614に適用することができる。本発明のディスプレイは特に大画面化した場合において有利であり、対角10インチ以上(特に30インチ以上)のディスプレイには有利である。

【0117】

以上の様に、本願発明の適用範囲は極めて広く、あらゆる分野の電子機器に適用することができる。また、本実施例の電子機器は実施例1～4のどのような組み合わせからなる構成を用いても実現することができる。

【0118】

【発明の効果】

こうして得られた本発明によるSiH<sub>4</sub>、N<sub>2</sub>O、H<sub>2</sub>を原料ガスとしてプラズマCVD法で作製される酸化窒化シリコン膜は、原料ガスの流量比を変化させるだけで作製することができ、それにより、膜中N、O、Hの組成の連続変化が制御された良質な下地膜として使用できる。本発明を下地膜として使用した場合、ブロッキング効果による基板からの不純物拡散の防止のみならず活性層と良好な界面を形成でき、TFT特性の劣化を防ぐことができる。また、同一チャンバーで成膜するため処理時間の短縮化が図れ、TFT特性の安定性向上並びに生産性向上にも寄与する。

【図面の簡単な説明】

10

20

30

40

50

- 【図1】 本発明の下地膜の構成を説明する図。

- 【図2】 本発明に適用するプラズマCVD装置の構成の一例を説明する図。

- 【図3】 本発明の作製工程を示す図。(実施例1)

- 【図4】 AM-LCDの作製工程を示す図。(実施例2)

- 【図5】 AM-LCDの作製工程を示す図。(実施例2)

- 【図6】 AM-LCDの作製工程を示す図。(実施例2)

- 【図7】 AM-LCDの作製工程を示す図。(実施例2)

- 【図8】 アクティブマトリクス型液晶表示装置の断面構造図。(実施例2)

- 【図9】 AM-LCDの外観を示す図。(実施例2)

- 【図10】 画素部上面図の一部を示す図。(実施例2) 10

- 【図11】 AM-LCDの作製工程を示す図。(実施例3)

- 【図12】 AM-LCDの作製工程を示す図。(実施例3)

- 【図13】 AM-LCDの作製工程を示す図。(実施例4)

- 【図14】 電子機器の一例を示す図。(実施例5)

- 【図15】 電子機器の一例を示す図。(実施例5)

- 【図16】 電子機器の一例を示す図。(実施例5)

- 【図17】 製造装置の一例を示す図。(実施例1)

【図1】

【図2】

【図3】

301:基板

302:酸化シリコン膜(組成勾配)

303:半導体膜

【図4】

101:基板、102:下地膜、103～105:半導体層、107～111:シストラップ

【図5】

118～123:レジストマスク、124,139～141:ゲート電極、143～149:シストラップ、132～138:レジストマスク、142:容量電極、126:ゲート配線、127,128:ゲートストラップ

【図6】

CMOS回路

nチャネル型FET

pチャネル型FET

孤立部

155:第1の骨間絶縁、156～158:ゲート電極、159,160:ゲート電極、161,164,169,170:チャネル形成領域、162,第3の不純物領域(レジスト)、163:第2の不純物領域(レジスト)、165,166,171～14:第1の不純物領域(レジスト)、167,171:第1の不純物領域(レジスト)、168,176:第1の不純物領域(レジスト)、177:低濃度不純物領域

(A)

(B)

(C)

【図7】

【図8】

【図9】

101:基板

900:画素TFT、901:画素部、902:走査(ゲート)線駆動回路、

903:信号(ソース)線駆動回路、904:ドシック回路

905:ゲート配線、906:ソース配線、907:画素電極、908:保持容量

【図10】

画素部上面図

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

301: 基板

1712, 1713: ロードロック室

1716~1719: ゲート弁

1720: ロボットアーム

1721, 1722: カセット

---

フロントページの続き

(72)発明者 岩井 道記

大阪府大阪市阿倍野区長池町22番22号 シャープ株式会社内

審査官 河本 充雄

(56)参考文献 特開2000-269510 (JP, A)

特開2001-015764 (JP, A)

特開2001-177101 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/786

H01L 21/336

H01L 21/31

H01L 21/318