(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6649806号

(P6649806)

(45) 発行日 令和2年2月19日(2020.2.19)

(24) 登録日 令和2年1月21日(2020.1.21)

|              |                |

|--------------|----------------|

| (51) Int.Cl. | F 1            |

| HO4N 5/378   | (2011.01)      |

| HO4N 5/357   | (2011.01)      |

| HO4N 5/232   | (2006.01)      |

| HO3M 1/56    | (2006.01)      |

|              | HO4N 5/378     |

|              | HO4N 5/357     |

|              | HO4N 5/232 190 |

|              | HO3M 1/56      |

請求項の数 16 (全 16 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2016-40440 (P2016-40440)    |

| (22) 出願日  | 平成28年3月2日(2016.3.2)           |

| (65) 公開番号 | 特開2017-158061 (P2017-158061A) |

| (43) 公開日  | 平成29年9月7日(2017.9.7)           |

| 審査請求日     | 平成31年3月1日(2019.3.1)           |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 100076428<br>弁理士 大塚 康徳                     |

| (74) 代理人  | 100115071<br>弁理士 大塚 康弘                     |

| (74) 代理人  | 100112508<br>弁理士 高柳 司郎                     |

| (74) 代理人  | 100116894<br>弁理士 木村 秀二                     |

| (74) 代理人  | 100130409<br>弁理士 下山 治                      |

| (74) 代理人  | 100134175<br>弁理士 永川 行光                     |

最終頁に続く

(54) 【発明の名称】信号処理装置、撮像装置及び制御装置、信号処理方法及び制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

互いに異なる傾きを有する複数の参照信号を用いて、撮像素子の画素部から出力されるアナログ信号をデジタル信号に変換するアナログデジタル変換手段と、

前記変換されたデジタル信号の分布に基づいて、前記複数の参照信号を切り替える信号レベルを決定する決定手段と、を有し、

前記アナログデジタル変換手段は、前記アナログ信号が前記信号レベル以上の場合に、小さい場合よりも、より大きい傾きを有する参照信号を用いて変換を行うことを特徴とする信号処理装置。

## 【請求項 2】

前記決定手段は、前記撮像素子の画素部の全体に対応する前記デジタル信号の分布に基づいて、前記信号レベルを決定することを特徴とする請求項 1 に記載の信号処理装置。

## 【請求項 3】

前記画素部のうちの一部の領域を設定する設定手段を更に有し、

前記決定手段は、前記一部の領域に対応する前記デジタル信号の分布に基づいて、前記信号レベルを決定することを特徴とする請求項 1 に記載の信号処理装置。

## 【請求項 4】

前記撮像素子の画素部の全体から得られたデジタル信号から、主被写体を検出する検出手段を更に有し、

前記一部の領域は、前記主被写体の領域であることを特徴とする請求項 3 に記載の信号

10

20

処理装置。

【請求項 5】

前記一部の領域を指示するための指示手段を更に有することを特徴とする請求項 3 に記載の信号処理装置。

【請求項 6】

前記撮像素子は、予め決められた周期で、1 フレーム分のアナログ信号を出力し、

前記決定手段は、静止画の記録が指示された場合に、当該指示の直前に出力された 1 フレーム分のアナログ信号を変換したデジタル信号の分布を分析して、前記信号レベルを決定することを特徴とする請求項 1 乃至 5 のいずれか 1 項に記載の信号処理装置。

【請求項 7】

前記撮像素子は、予め決められた周期で、1 フレーム分のアナログ信号を出力し、

前記決定手段は、前記予め決められた周期で、デジタル信号の分布を分析し、当該分析結果に応じて前記信号レベルが変わった場合に、前記アナログデジタル変換手段に変更した後の前記信号レベルを通知することを特徴とする請求項 1 乃至 5 のいずれか 1 項に記載の信号処理装置。

【請求項 8】

予め決められた複数の異なる出力レベルのアナログ信号を前記アナログデジタル変換手段に供給する電圧供給手段と、

前記複数の異なる出力レベルのアナログ信号を前記複数の参照信号によりそれぞれ変換して得られた複数のデジタル信号に基づいて、前記デジタル信号を補正するための補正值を算出する算出手段と

を更に有することを特徴とする請求項 1 乃至 7 のいずれか 1 項に記載の信号処理装置。

【請求項 9】

前記補正值は、前記複数の参照信号の傾きの比と、オフセット量とを含むことを特徴とする請求項 8 に記載の信号処理装置。

【請求項 10】

前記複数の参照信号を出力する参照信号出力手段を更に有し、

前記複数の参照信号は、第一の参照信号と、該第一の参照信号よりも傾きの大きい第二の参照信号とを含み、前記参照信号出力手段は、前記デジタル信号の分布に応じて、前記第一の参照信号の傾きをえることを特徴とする請求項 1 乃至 9 のいずれか 1 項に記載の信号処理装置。

【請求項 11】

前記撮像素子と、

請求項 1 乃至 10 のいずれか 1 項に記載の信号処理装置と

を有することを特徴とする撮像装置。

【請求項 12】

互いに異なる傾きを有する複数の参照信号を用いて、撮像素子の画素部から出力されるアナログ信号をデジタル信号に変換するアナログデジタル変換手段を制御するための制御装置であって、

前記変換されたデジタル信号の分布に基づいて、前記複数の参照信号を切り替える信号レベルを決定する決定手段と、

前記決定した信号レベルを前記アナログデジタル変換手段に通知する通知手段と、を有し、

前記アナログデジタル変換手段は、前記アナログ信号が前記信号レベル以上の場合に、小さい場合よりも、より大きい傾きを有する参照信号を用いて変換を行うことを特徴とする制御装置。

【請求項 13】

アナログデジタル変換手段が、互いに異なる傾きを有する複数の参照信号を用いて、撮像素子の画素部から出力されるアナログ信号をデジタル信号に変換するアナログデジタル変換工程と、

10

20

30

40

50

決定手段が、前記変換されたデジタル信号の分布に基づいて、前記複数の参照信号を切り替える信号レベルを決定する決定工程と、を有し、

前記アナログデジタル変換工程では、前記アナログ信号が前記信号レベル以上の場合に、小さい場合よりも、より大きい傾きを有する参照信号を用いて変換を行うことを特徴とする信号処理方法。

【請求項 1 4】

互いに異なる傾きを有する複数の参照信号を用いて、撮像素子の画素部から出力されるアナログ信号をデジタル信号に変換するアナログデジタル変換手段を制御するための制御方法であって、

決定手段が、前記変換されたデジタル信号の分布に基づいて、前記複数の参照信号を切り替える信号レベルを決定する決定工程と、

通知手段が、前記決定した信号レベルを前記アナログデジタル変換手段に通知する通知工程と、を有し、

前記アナログデジタル変換手段は、前記アナログ信号が前記信号レベル以上の場合に、小さい場合よりも、より大きい傾きを有する参照信号を用いて変換を行うことを特徴とする制御方法。

【請求項 1 5】

コンピュータに、請求項 1 4 に記載の制御方法の各工程を実行させるためのプログラム。

【請求項 1 6】

請求項 1 5 に記載のプログラムを記憶したコンピュータが読み取り可能な記憶媒体。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、信号処理装置、撮像装置及び制御装置、並びに信号処理方法及び制御方法に関し、特に、アナログデジタル変換を行う信号処理装置、撮像装置及び制御装置、並びに信号処理方法及び制御方法に関する。

【背景技術】

【0 0 0 2】

近年、テレビジョンの規格は、フルハイビジョンと呼ばれる水平 1920 画素、垂直 1080 画素（以下、「1920 × 1080 画素」のように記す。）の画素数から、4k 2k と呼ばれる 3840 × 2160 画素の HD の 4 倍の画素数に変わってきている。また、4k 2k よりもさらに次の世代として、8k 4k、もしくはスーパーハイビジョンと呼ばれる規格もあり、この規格では、7680 × 4320 画素となっている。また、画素数と合わせて、フレームレートも増加の一途を辿っている。

【0 0 0 3】

このようなテレビジョン規格の変化に伴い、テレビジョン映像を撮影する撮像装置においても、記録できる映像の高画素化及び高フレームレート化が要求されている。こういった要求を満足するためには、光を電気信号に変換する撮像素子においても、映像の読み出し時間を高速化することは重要な課題の一つであり、特に撮像素子が有する A/D 変換器の高速化が求められている。

【0 0 0 4】

特許文献 1 では、画素の信号と比較レベルとを比較して、傾きの異なるランプ信号を用いてアナログデジタル変換を行うことが開示されている。具体的には、画素の信号が比較レベルよりも大きい場合は、第一の傾きのランプ信号と比較してアナログデジタル変換を行い、比較レベル以下の場合には、第一のランプ信号より傾きの小さい第二の傾きのランプ信号で比較してアナログデジタル変換を行う。こうすることによって、A/D 変換にかかる時間を短縮している。

【先行技術文献】

【特許文献】

10

20

30

40

50

**【0005】**

【特許文献1】特開2011-211535号公報

**【発明の概要】****【発明が解決しようとする課題】****【0006】**

しかしながら、特許文献1のように傾きの異なる複数のランプ信号を用いてアナログデジタル変換した信号は、同じゲインレベルになるようビットシフトする必要がある。この際に、傾きの差によっては、画素信号の比較レベル付近の切り替わり目で、ビットシフトによるビット飛びが映像に見えてしまうことがある。これを回避するために、比較レベル付近の画素信号に、撮像装置の画像処理部でランダムノイズを重畠（ディザ）することで、切り替わり目での違和感を軽減する手法が考えられる。10

**【0007】**

しかしながら、この手法では、映像の画素信号が比較レベル付近に集まっている場合、ランダムノイズが重畠される画素信号が多くなり、通常よりもノイズが目立つ映像となってしまう。

**【0008】**

本発明は上記問題点を鑑みてなされたものであり、傾きの異なる複数のランプ信号を用いてアナログデジタル変換する場合に、ランプ信号の切り替わり目での違和感を軽減することを目的とする。

**【課題を解決するための手段】**

20

**【0009】**

上記目的を達成するために、本発明の信号処理装置は、互いに異なる傾きを有する複数の参照信号を用いて、撮像素子の画素部から出力されるアナログ信号をデジタル信号に変換するアナログデジタル変換手段と、前記変換されたデジタル信号の分布に基づいて、前記複数の参照信号を切り替える信号レベルを決定する決定手段と、を有し、前記アナログデジタル変換手段は、前記アナログ信号が前記信号レベル以上の場合に、小さい場合よりも、より大きい傾きを有する参照信号を用いて変換を行う。

**【発明の効果】****【0010】**

本発明によれば、傾きの異なる複数のランプ信号を用いてアナログデジタル変換する場合に、ランプ信号の切り替わり目での違和感を軽減することができる。30

**【図面の簡単な説明】****【0011】**

【図1】本発明の実施形態における撮像装置で用いられる撮像素子の概略構成を示すプロック図。

【図2】撮像素子の列アンプ群の概略構成及び動作タイミングを示す図。

【図3】第1の実施形態におけるA/D変換の動作を説明するためのタイミング図。

【図4】信号レベルに応じて傾きの異なるランプ信号を用いる場合の、出力レベルとA/D変換結果との関係を示す図。

【図5】第1の実施形態におけるヒストグラムとA/D変換値との関係を示す図。

40

【図6】第1の実施形態における明部の信号レベルの画素が比較的多い場合のヒストグラムとA/D変換値との関係を示す図。

【図7】第1の実施形態における暗部の信号レベルの画素が比較的多い場合のヒストグラムとA/D変換値との関係を示す図。

【図8】第1及び第2の実施形態における判定レベルの変更タイミングを示す図。

【図9】第1の実施形態における撮像素子の画素部の構成例を示す図。

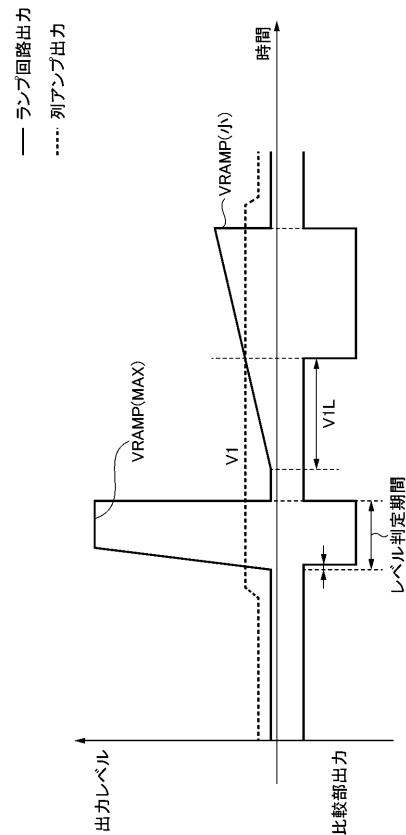

【図10A】第1の実施形態のダミー画素の読み出し期間における固定電圧V1を第一のランプ信号VRAMP（小）でA/D変換処理する場合のタイミング図。

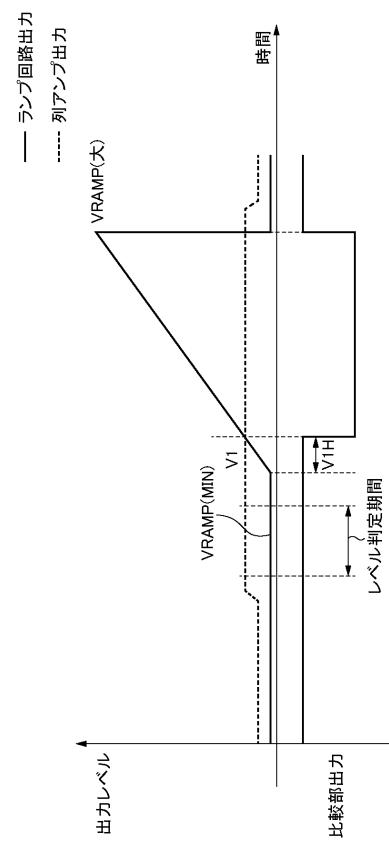

【図10B】第1の実施形態のダミー画素の読み出し期間における固定電圧V1を第二のランプ信号VRAMP（大）でA/D変換処理する場合のタイミング図。50

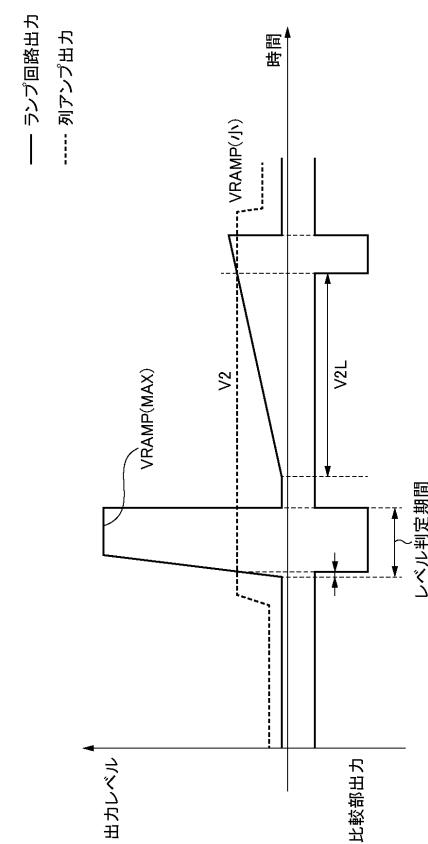

【図10C】第1の実施形態のダミー画素の読み出し期間における固定電圧V2を第一のランプ信号VRAMP(小)でAD変換処理する場合のタイミング図。

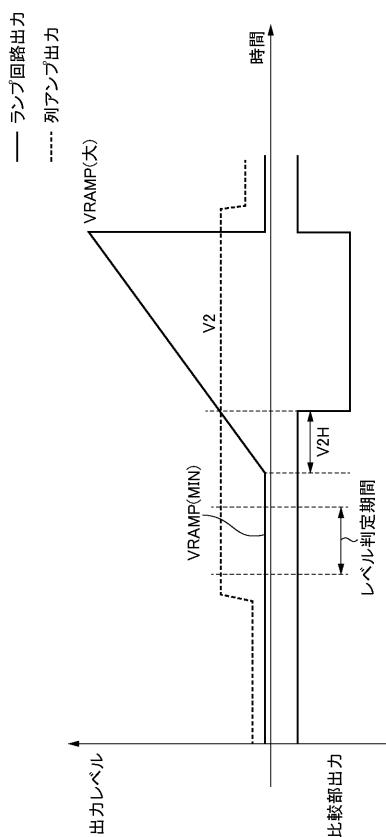

【図10D】第1の実施形態のダミー画素の読み出し期間における固定電圧V2を第二のランプ信号VRAMP(大)でAD変換処理する場合のタイミング図。

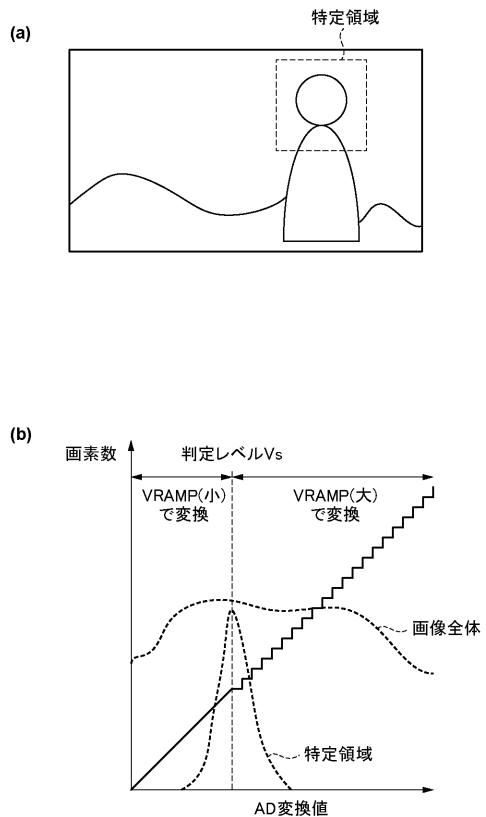

【図11】第3の実施形態における画像例と、ヒストグラムとAD変換値との関係を示す図。

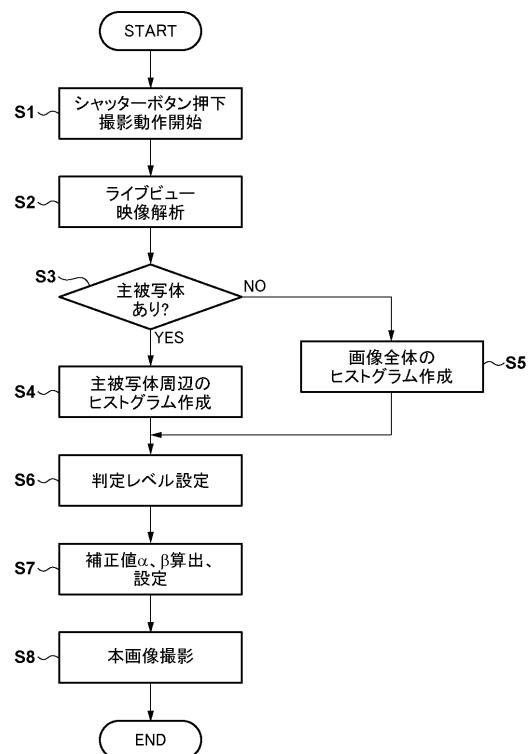

【図12】第3の実施形態における撮像処理のフローチャート。

**【発明を実施するための形態】**

**【0012】**

以下、添付図面を参照して本発明を実施するための形態を詳細に説明する。 10

**【0013】**

**<第1の実施形態>**

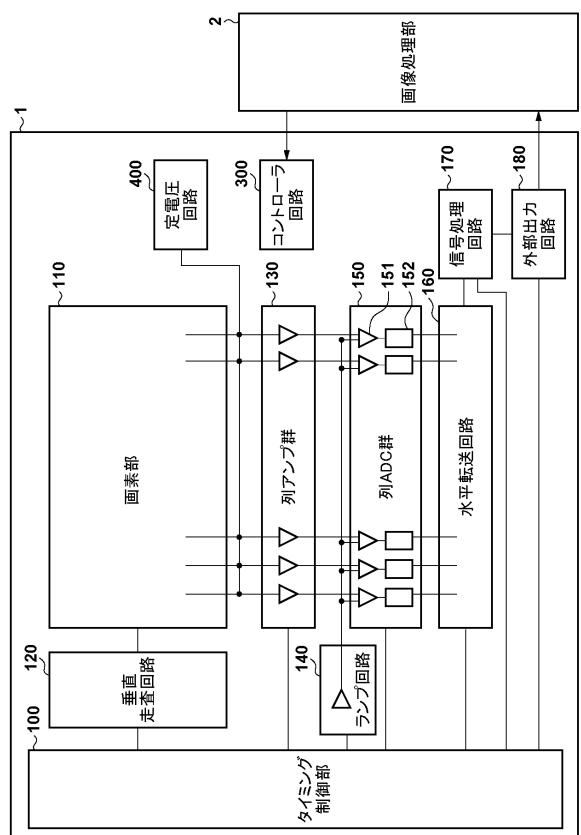

図1は、本発明の第1の実施形態における撮像装置で用いられる撮像素子1の構成を示すブロック図であり、撮像素子1と、撮像素子1により得られた画像データの出力先である画像処理部2とを示している。第1の実施形態における撮像素子1は、並列型AD変換器を実装したCMOSイメージセンサである。画像処理部2は、撮像素子1が出力する画像データに対し、ホワイトバランス処理や、ガンマ処理などの現像処理を行い、最終的に記録媒体に記録する。また、画像処理部2はCPUを内蔵しており、このCPUにより、撮像装置の動作モードに応じて撮像素子1と通信（例えばシリアル通信）し、制御を行う。 20

**【0014】**

撮像素子1において、タイミング制御部100は撮像素子1の各ブロックに対して動作クロック信号及びタイミング信号を供給し、動作を制御する。

**【0015】**

画素部110は、2次元に配置された複数の画素を含み、各画素の光電変換素子において入射光量に応じて光電変換して得られた電荷を、電圧に変換して出力する。各々の画素には、カラーフィルタとマイクロレンズが実装されている。なお、カラーフィルタとして、R(赤)、G(緑)、B(青)の3色の、いわゆるRGB原色カラーフィルタによるベイヤー配列の周期構造をとっているのが一般的であるが、必ずしもこの限りではない。

**【0016】**

垂直走査回路120は、画素部110の各画素により得られた画素信号を1フレーム期間内に順次読み出すためのタイミング制御を行う。一般的に読み出しあは、1フレーム中の上部の行から下部の行にかけて、行単位で順次行われる。 30

**【0017】**

列アンプ群130は、各列にそれぞれ設けられた複数の列アンプから成り、画素部110から読みだされた画素信号を電気的に増幅するために用いられる。列アンプ群130で画素信号を増幅することにより、後段のランプ回路140や列アナログデジタル変換器群（列ADC群）150が出すノイズとのS/N比を改善させる。ただし、画素部110の出すノイズに対し、ランプ回路140や列ADC群150が出すノイズが十分小さい回路構造においては、列アンプ群130は必ずしも必須ではない。 40

**【0018】**

定電圧回路400は、画素部110と列アンプ群130とを繋ぐ信号線に、固定の電圧を供給する電圧供給手段として動作する。なお、第1の実施形態では定電圧回路400を用いるが、ある一定の電圧で信号をクリップするようなクリップ回路などに応用できる回路を用いても良い。

**【0019】**

ランプ回路140（参照信号出力手段）は、時間方向に一定のスロープ（傾き）を持つランプ形状の電圧信号（ランプ信号）を発生する信号発生器である。列ADC群150は、列毎に比較部151とカウンタ・ラッチ回路152とからなる列ADCを有する。比較部151は、列アンプ群130により増幅された画素信号（アナログ信号）と、ランプ回

10

20

30

40

50

路 140 からのランプ信号とを比較して、信号の大小関係を示す信号を出力する。そしてカウンタ・ラッチ回路 152 が、比較部 151 からの信号に応じてカウンタ値をラッチすることで、アナログ - デジタル変換が行われる。なお、比較部 151 とカウンタ・ラッチ回路 152 の詳細な動作は後述する。カウンタ・ラッチ回路 152 に保持された 1 行分のデジタル画像データ（デジタル信号）は、水平転送回路 160 により端の行から順に読みだされる。

#### 【 0020 】

水平転送回路 160 により読み出された画像データは信号処理回路 170 に入力される。信号処理回路 170 はデジタル的に信号処理を行う回路であり、デジタル処理で一定量のオフセット値を加える他に、シフト演算や乗算を行うことで、簡易にゲイン演算を行うことができる。また、画素部 110 に、遮光した画素領域（OB 画素部）を形成し、OB 画素部の画素から得られる信号を利用したデジタルの黒レベルクランプ動作を行っても良い。更に、入力された画像データに基づいて、後述するように、ランプ回路 140 から出力されるランプ信号を、タイミング制御部 100 を介して制御する。

10

#### 【 0021 】

信号処理回路 170 により処理された画像データは、外部出力回路 180 に渡される。外部出力回路 180 は、シリアルライザ機能を有し、信号処理回路 170 からの多ビットの入力パラレル信号をシリアル信号に変換する。また、このシリアル信号を、例えば LVDS 信号等に変換し、画像処理部 2 に出力する。

20

#### 【 0022 】

コントローラ回路 300 は、画像処理部 2 との I/F 部であり、シリアル通信回路などを用いて、画像処理部 2 の CPU から撮像素子 1 への制御を受ける。

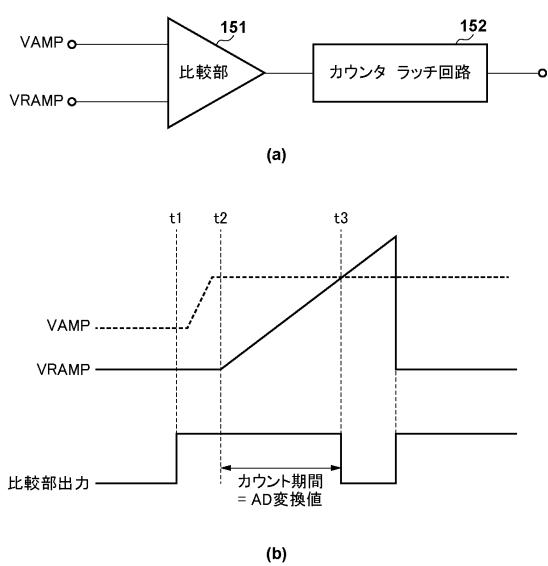

#### 【 0023 】

次に、撮像素子 1 の列 ADC 群 150 を用いた基本的な A/D 変換の原理について、図 2 を用いて説明する。列 ADC 群 150 は、上述したように、列毎に比較部 151 とカウンタ・ラッチ回路 152 を有している。また、図 2 (a) に示すように、比較部 151 は、列アンプ群 130 から出力される画素信号 VAMP と、ランプ回路 140 から出力されるランプ信号 VRAMP とを比較し、その結果を出力する。

#### 【 0024 】

図 2 (b) に示すように、画素部 110 からの画素信号 VAMP の読み出し開始に先立つて比較部 151 の動作を開始する（時刻 t1）。列アンプ群 130 の各列アンプの動作が安定すると、時刻 t2 において、カウンタ・ラッチ回路 152 のカウント値をリセットする。このカウンタ・ラッチ回路 152 のカウントリセットタイミングと同期して、ランプ回路 140 から出力されるランプ信号 VRAMP の信号レベルは、時刻 t2 から時間の経過とともに増加する。比較部 151 の出力は、列アンプ群 130 から出力される画素信号 VAMP の信号レベルをランプ回路 140 から出力されるランプ信号 VRAMP の信号レベルが超えた時に反転する（時刻 t3）。カウンタ・ラッチ回路 152 は、カウント値をリセットしてから、比較部 151 の出力が反転するまでの期間（時刻 t2 ~ 時刻 t3）、カウント動作を行う。この動作により、列アンプ群 130 により增幅された画素信号の出力レベルに比例したカウント値が得られるため、こうして得られたカウント値が A/D 変換結果となる。なお、ここで説明した画素信号とランプ信号の比較方法、カウンタ・ラッチ回路によるカウント方法などはあくまで一例であり、カウント値をリセットしてから比較部 151 の出力が反転するまでの期間を検出できれば、他の方法で実施しても構わない。

30

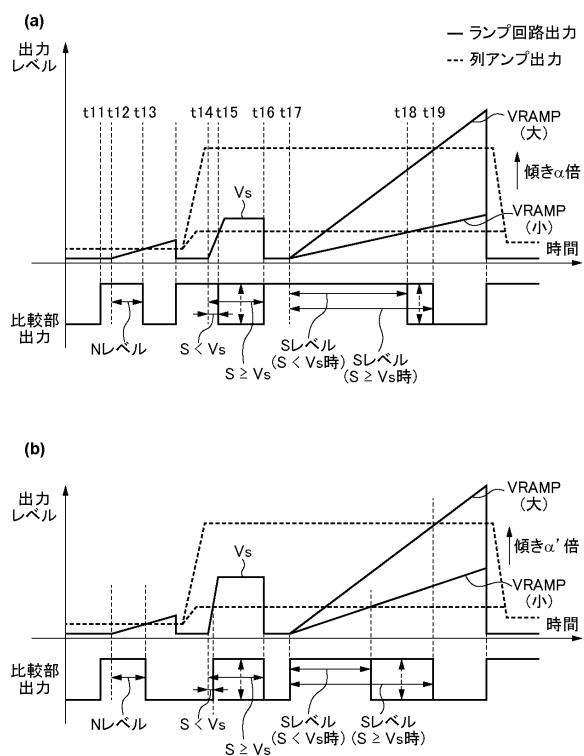

#### 【 0025 】

図 3 は、第 1 の実施形態におけるランプ回路 140 及び列 ADC 群 150 の動作を説明する図である。図 3 において、横軸は時間、グラフ上部の縦軸は出力レベル、グラフ下部は、比較部 151 の出力を示している。先ず、図 3 (a) を参照して、列アンプ群 130 の出力信号 VAMP の信号レベルに応じて、ランプ回路 140 から出力されるランプ信号 VRAMP のスロープを変える例について説明する。

40

50

**【 0 0 2 6 】**

一般的に、単位画素からの信号の読み出し処理においては、まずN信号（ノイズレベル）の読み出し及びA/D変換を行い、その後にS信号（ノイズレベル+信号レベル）の読み出し及びA/D変換を行う。そして、信号処理回路170で変換されたS信号とN信号との差分をとることでノイズ成分を打ち消すことで、S/Nの良い信号を得る。

**【 0 0 2 7 】**

まず、N信号のA/D変換を行うために、時刻t11で比較部151の動作を開始し、時刻t12でカウンタ・ラッチ回路152のカウントをリセットと共に、ランプ回路140から出力されるランプ信号VRAMPの信号レベルを変化させる。ここで、ノイズレベルであるN信号の信号レベルは小さいため、N信号のA/D変換には、傾きが小さい第一のランプ信号VRAMP（小）（第一の参照信号）を用いる。そして、カウンタ・ラッチ回路152のカウントをリセットしてから、比較部151の出力が反転するまでの期間（時刻t12～時刻t13）、カウント動作を行うことで、N信号をA/D変換する。10

**【 0 0 2 8 】**

次に、画素部110に蓄積された電荷に応じた信号を読み出して列アンプ群130により増幅された出力信号であるS信号に対し、レベル判定期間に、ランプ回路140はある一定の判定レベルVsを最大レベルとする判定用ランプ信号を比較部151に出力する。そして、S信号との比較を行う。ここでは、時刻t14においてカウンタ・ラッチ回路152のカウント値をリセットと共に、ランプ回路140は所定の判定レベルVsを最大レベルに持つ判定用ランプ信号の出力を開始する。S信号の信号レベルが判定レベルVs以上（信号レベル以上）であれば（S > Vs）、比較部151の出力は反転しないため、時刻t16でレベル判定期間が終了するまでカウント値が増え続ける。これに対し、S信号の信号レベルが判定レベルVsより小さければ（S < Vs）、例えば時刻t15で比較部151の出力が反転するため、カウント値の増加が終了する。このように、カウンタ・ラッチ回路152のカウント値により、信号処理回路170では、S信号の信号レベルが判定レベルVsよりも大きいか小さいかを判断することができる。なお、カウンタ・ラッチ回路152のカウント値をリセットするタイミングを、ランプ回路140の出力が判定レベルVsに安定した時点とし、S信号の信号レベルが判定レベルVsより小さい（S < Vs）場合に、カウント値が0となるように制御してもよい。20

**【 0 0 2 9 】**

S信号の信号レベルが判定レベルVsよりも小さい場合は、時刻t17から、N信号と同じ第一のランプ信号VRAMP（小）を用いてS信号のA/D変換を行う。これにより、図3（a）に示す例では、時刻t17から時刻t18の間のカウント値が得られる。一方、S信号の信号レベルが判定レベルVs以上である場合は、第一のランプ信号VRAMP（小）よりもスロープが倍の第二のランプ信号VRAMP（大）（第二の参照信号）を用いて、S信号のA/D変換を行う。これにより、図3（a）に示す例では、時刻t17から時刻t19の間のカウント値が得られる。30

**【 0 0 3 0 】**

図4は、出力レベルに応じて傾きの異なるランプ信号を用いる場合の、出力信号の信号レベルとA/D変換結果との関係を示す図である。図4の横軸は列アンプ群130の出力信号レベルを示し、縦軸はS信号のA/D変換後のデジタル値を示している。実線は、比較部151及びカウンタ・ラッチ回路152でA/D変換され、水平転送回路160を経て、信号処理回路170に入力されるデジタル値（A/D変換値）を表している。上述したように、判定レベルVsより信号レベルが小さいS信号は第一のランプ信号VRAMP（小）を用いて、また、判定レベルVs以上の信号レベルを持つS信号は第二のランプ信号VRAMP（大）を用いてA/D変換される。そのため、図4（a）に示すように、判定レベルVsの前後で、A/D変換後のS信号の整合が取れていことになる。40

**【 0 0 3 1 】**

そのため、信号レベルが判定レベルVs以上のS信号のA/D変換値に対しては、まず、信号処理回路170にて、第一のランプ信号VRAMP（小）と第二のランプ信号VRAMP（大）を用いてA/D変換される。50

M P (大)の傾きの比 を乗算する。更に、判定レベルV s で段差が無くなるようにオフセット量 を加算することで、入射光量に応じた画素信号の信号レベルとA D 変換値が一次的な関係になるように補正を行う。

#### 【0032】

上述した補正を行わない状態で、有効画素の映像を出力すると、ある輝度で段差が残ったような違和感のある映像となってしまう。この補正に用いる補正值は、撮像素子の温度、撮像素子の駆動タイミング（列アンプ群130のゲインや動作状態等）、駆動設定（電源設定等）によって変化が生じるため、画像取得直前か、または定期的な補正值の取得が必要である。なお、補正值の取得方法については後述する。

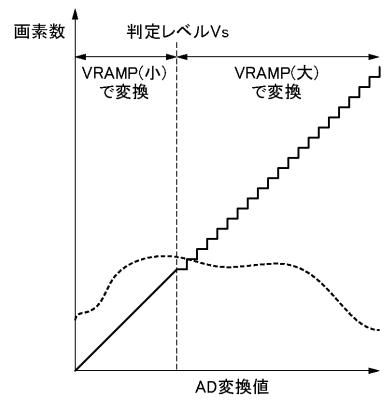

#### 【0033】

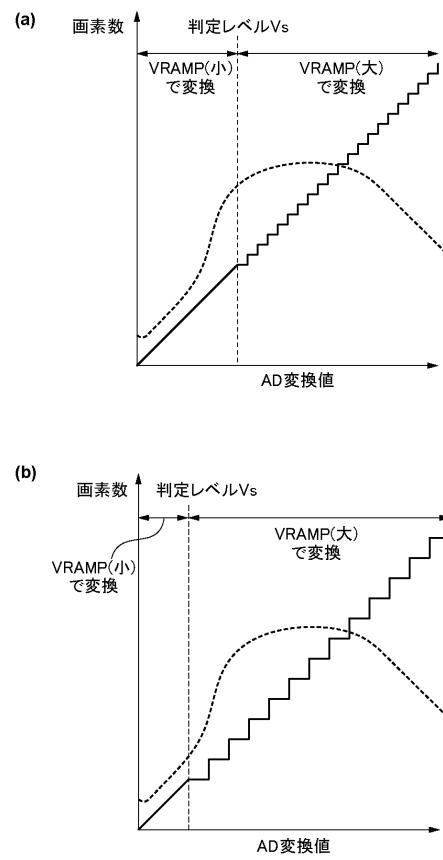

次に、第1の実施形態における判定レベルV s の設定方法について、図5～図7を参照して説明する。第1の実施形態では、画像処理部2において、取得した画像のA D 変換値の分布を示すヒストグラムを生成し、その形状を分析する。図5において、横軸はA D 変換値、縦軸は各A D 変換値を有する画素の画素数を示し、点線は生成したヒストグラムを示す。

10

#### 【0034】

ヒストグラムの形状は、撮影している被写体により大きく変わるが、図5に示すヒストグラムはA D 変換値の小さい部分（暗部）から大きい部分（明部）まで存在しており、コントラストの高い画像と言える。この場合、第一のランプ信号V R A M P（小）と第二のランプ信号V R A M P（大）とを切り替える判定レベルV s 近辺のA D 変換値を有する画素の画素数は多くない。

20

#### 【0035】

一方、図6(a)は、明部の信号レベルの画素が比較的多く、一般的にハイキーと呼ばれる画像である。この場合、図6(b)に示すように判定レベルV s を暗部側に変更することで、判定レベルV s 付近で変換される画素数を減らすことができる。

#### 【0036】

逆に、図7(a)は、暗部の信号レベルの画素が多く、一般的に低照度画像と呼ばれる画像である。これは後段の画像処理でデジタルゲインをかける場合や、ノイズを少なく撮影するためにわざと暗めに撮影するような場合である。この場合、図7(b)に示すように判定レベルV s を明部側に変更することで、判定レベルV s 付近で変換される画素数を減らすことができる。

30

#### 【0037】

このように、画像処理部2は、A D 変換値のヒストグラムを生成し、生成したヒストグラムを分析して、明部または暗部に偏っているかどうかを判断し、偏っている場合には、判定レベルV s を予め決められたレベル分、ヒストグラムの度数が少ない方にシフトする。このように、画像の特徴に合わせて判定レベルV s を変更する。

#### 【0038】

なお、上述したように判定レベルV s を変更すると同時に、第一のランプ信号V R A M P（小）の傾きを変更してもよい。図3(b)は、ランプ回路140から出力される第一のランプ信号V R A M P（小）の傾きを変えたときの図であり、図3(a)と比較して、判定レベルV s を大きくすると同時に、第一のランプ信号V R A M P（小）の傾きを大きくしている。そのため、第一のランプ信号V R A M P（小）で変換したA D 変換値は、図3(a)に示す第一のランプ信号V R A M P（小）で変換した変換結果よりも小さくなる。また、傾きの比が(a)の 倍から' 倍に変わるために、補正值' とそれに対応したを算出する必要がある。

40

#### 【0039】

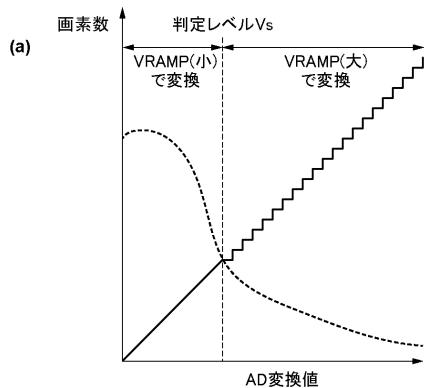

次に図8(a)のタイミング図を用いて、本撮像装置の動作について説明する。ここでは、デジタル一眼レフカメラ及びデジタルカメラなどの静止画撮像装置について記載する。図8では、横軸に時間、縦軸に撮像素子1の垂直方向ラインでの読み出しタイミングを表している。

50

## 【0040】

近年のデジタル一眼レフカメラ及びデジタルカメラには、ライブビュー機能が搭載されているものがある。ライブビュー機能は、ミラーアップして撮像素子1に常に光を入射させ、予め決められた周期で1フレーム分のアナログ信号を出力し、得られた画像信号に基づく画像を液晶モニタなどに表示するもので、ユーザは表示された画像を観察することができる。図8(a)の期間 $t_{81}$ ,  $t_{82}$ ,  $t_{83}$ はそのライブビュー画像を読み出している時間である。そして、撮像装置は、静止画(本画像)を取得するタイミングで、先幕シャッタ及び後幕シャッタを駆動する。このシャッタはメカシャッターではなく、撮像素子1内で行う電子シャッタでも良い。

## 【0041】

本画像の撮影に先立って、先幕シャッタを切る直前までに取得したライブビュー画像から、本画像を撮影する際の露出条件、例えばレンズの絞り値、先幕シャッタ駆動から後幕シャッタ駆動までの時間(シャッタスピード)などを決定する。そして、 $t_{84}$ のタイミングで撮像素子1と通信を行い、決定した露光条件を反映する。また、先幕シャッタの駆動直前の期間 $t_{83}$ で読み出したライブビュー画像を用いて、画像処理部2でヒストグラムの生成を行う。そして、生成したライブビュー画像のヒストグラムに基づいて、判定レベル $V_s$ を決定して撮像素子1に通知し、これも $t_{84}$ のタイミングで変更を反映する。このとき、図3(b)で説明したように、第一のランプ信号VRAMP(小)の傾きを制御してもよい。

## 【0042】

期間 $t_{85}$ では、後述するように、撮像素子1に含まれるダミー画素領域を利用して、AD変換時の傾きの比と加算するオフセット量を算出する。その後、先幕シャッタ及び後幕シャッタを駆動してから本画像の読み出しを行い、本画像を読み出す(期間 $t_{86}$ )。

## 【0043】

次に、ヒストグラムの分析結果から判定レベル $V_s$ 及びランプ信号の傾きを制御した後の、傾きの比と加算するオフセット量を算出する方法について説明する。なお、補正值を算出する動作を、以降、補正值取得動作と記載する。

## 【0044】

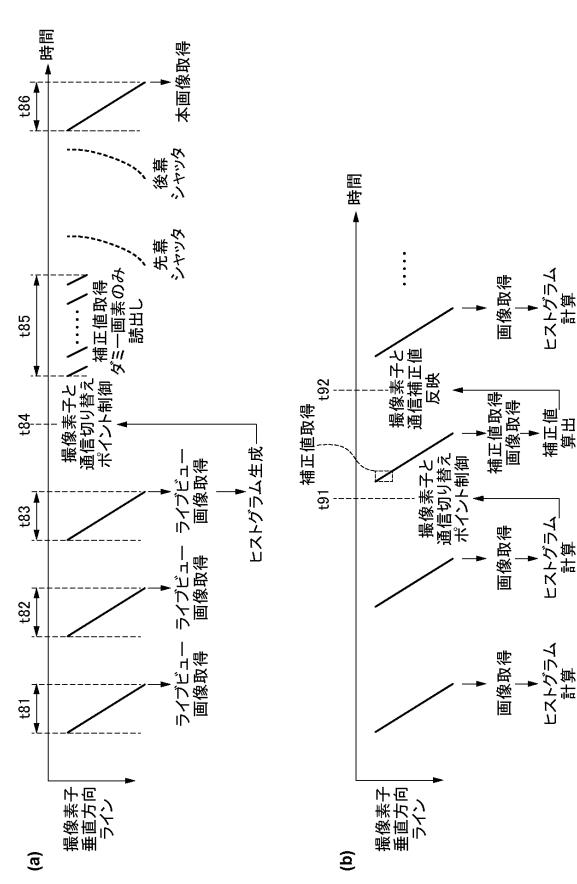

図9は、画素部110の構成例を示している。画素構成として、最も上部にフォトダイオードを持たないダミー画素領域を配置し、順に、遮光されたオプティカルブラック(OB)画素領域、光電変換して得られた信号を出力する有効画素領域を配している。第1の実施形態では、ダミー画素の画素信号読み出し期間を、傾きの比とオフセット量を算出するために使用する。ここでは、ダミー画素の画素信号読み出し期間に、定電圧回路400から固定電圧を入力し、列アンプ群130から比較部151に入力される電圧がある固定電圧になるように制御する。なお、第1の実施形態においては、固定電圧として、判定レベル $V_s$ より小さい電圧 $V_1$ 及び $V_2$ を用いる。

## 【0045】

ダミー画素の読み出し期間におけるAD変換処理について、図10A～図10Dを参照して説明する。図10Aでは、固定電圧 $V_1$ をAD変換する。なお、図3で説明した処理とは異なり、N信号をAD変換するための期間は設ける必要がない。まず、図10Aに示すように、レベル判定期間のランプ回路140から出力されるランプ信号VRAMPを最大値VRAMP(MAX)まで上げることで、傾きが小さい第一のランプ信号VRAMP(小)で固定電圧 $V_1$ のAD変換を行う。AD変換した結果を $V_{1L}$ とする。

## 【0046】

続いて図10Bに示すように、レベル判定期間のランプ回路140から出力されるランプ信号VRAMPを最小値VRAMP(MIN)とすることで、傾きが大きい第二のランプ信号VRAMP(大)で固定電圧 $V_1$ をAD変換する。AD変換した結果を $V_{1H}$ とする。

## 【0047】

10

20

30

40

50

その後、図10C及び図10Dに示すように、固定電圧を電圧V1よりも大きい電圧V2に変え、図10A及び図10Bと同様にAD変換を行う。この結果をそれぞれV2L、V2Hとする。

#### 【0048】

これらは、横軸を出力レベル、縦軸をAD変換値とすると、図4(b)のように表される。図4(b)は、図4(a)の出力信号レベルが判定レベルVsよりも小さい部分を拡大したものである。これら4点の座標から、傾きの比とオフセット量を求めることができる。例えば、傾きの比は、次の式(1)で求められる。

$$= (V2L - V1L) / (V2H - V1H) \dots (1)$$

傾きの比を求めた上で、2本の直線が判定レベルVsで交わるように、オフセット量を次の式(2)で求めることができる。10

$$\begin{aligned} &= (V2L - V1L) / (V2H - V1H) \times Vs \\ &- (V2H - V1H) / (V2 - V1) \times Vs \dots (2) \end{aligned}$$

#### 【0049】

上記補正值、の算出は、撮像素子1の内部で行っても良いし、画像処理部2で行っても良い。

#### 【0050】

上記の通り第1の実施形態によれば、AD変換値の分布(ヒストグラム)から、AD変換に使用するランプ信号を決定するための判定レベルを変更することで、判定レベル付近でAD変換される画素数を低減させることができる。これにより、ランプ信号の切り替わり目での違和感を軽減することができる。20

#### 【0051】

##### <第2の実施形態>

上述した第1の実施形態では、本画像取得前のライブビュー画像から、ヒストグラムの生成と補正值の取得とを行ったが、ビデオカメラのような、ライブビューと本画像の区別が無く画像を取得する場合は、図8(b)のような動作を行う。

#### 【0052】

ビデオカメラのような撮像装置では、一定のフレームレートで毎フレーム画像取得を行う。画像取得し、画像処理部2でフレーム毎にヒストグラムを生成し、例えば、図6や図7に示すような、判定レベルVsを変更する分布になった場合は、撮像素子1の判定レベルVsを決定し、t91のタイミングで変更を反映する。このとき、図3(b)で説明したように、第一のランプ信号VRAMP(小)の傾きを制御してもよい。30

#### 【0053】

ここで、上記変更を反映したフレームでは、そのランプ信号の傾きの比とオフセットが算出されておらず、段差の残った映像が出力される。この出力フレームで、ランプ信号の傾きの比とオフセットを求め、t92のタイミングで補正值を反映させる。

#### 【0054】

補正值を反映させた次フレームから正常な画像を取得することになるが、ビデオカメラではフレームレートが速い(近年であれば60P、120Pなど)ので、1フレームの映像の段差はあまり見た目に影響しない。40

#### 【0055】

上記の通り本第2の実施形態によれば、ビデオカメラなどの連続的に画像を読み出す撮像装置においても、判定レベル付近でAD変換される画素数を低減させることができる。

#### 【0056】

##### <第3の実施形態>

第1及び第2の実施形態では、ヒストグラムの生成を、出力された画像全体に対して実施しているが、画像の一部の注目する領域について生成しても良い。注目する領域とは、主な被写体を意味し、例えば、フォーカスの合焦領域、人物の顔を検出した領域、液晶表示モニタにタッチパネルで指示した領域、などが挙げられる。

#### 【0057】

10

20

30

40

50

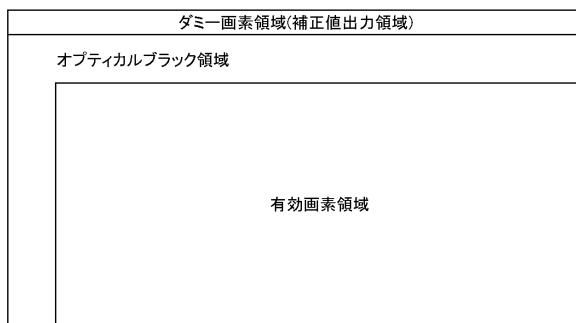

図11(a)は、撮像装置からの出力画像を示している。図11(b)は図11(a)の画像のヒストグラムである。画像全体はコントラストが高く、これだけ見ると判定レベルVsを変更する必要はない。しかしながら、図11(a)のある特定領域(人物の顔)のヒストグラムが、図11(b)に示すように判定レベルVs近辺の信号レベルを有する画素数が多い場合、判定レベルVsを第1の実施形態で上述したように変更する。

#### 【0058】

図12は、本第3の実施形態における撮影処理のフローチャートを示す。S1で撮像装置の使用者がシャッタボタンを押下すると、撮影動作を開始する。

#### 【0059】

S2で、先幕および後幕シャッタを切る前のライブビュー画像を取得する。そして、このライブビュー画像を画像処理部2で解析し、主被写体が存在するかどうか判定する。なお、主被写体とは、前述したように、例えば、フォーカスの合焦領域、人物の顔を検出した領域、液晶表示モニタにタッチパネルで指示した領域などである。

#### 【0060】

S3で主被写体が存在すると判断された場合には、S4において、画像処理部2で主被写体周辺のヒストグラムを生成する。主被写体が存在しない場合には、S5において、画像全体のヒストグラムを生成する。そして、生成したヒストグラムから、判定レベルVs及び、変更可能な場合には第一のランプ信号VRAMP(小)の傾きを決定し、撮像素子1を制御する(S6)。

#### 【0061】

次に、S7では、S6で反映した判定レベルVs及びランプ信号の傾きに対して、補正值の傾きの比とオフセットを求めるために、補正值取得処理を行い、補正值を取得した上で、本画像を撮影する(S8)。

#### 【0062】

上記の通り本第3の実施形態によれば、ヒストグラムの生成領域を、画像のある注目領域に限定し、注目領域に適した判定レベルに変更することで、注目領域について、判定レベル付近でAD変換される画素数を低減させることができる。これにより、注目領域におけるランプ信号の切り替わり目での違和感を軽減することができる。

#### 【0063】

なお、上述した第1～第3の実施形態では、1つの判定レベルVsに応じて、第一のランプ信号VRAMP(小)または第二のランプ信号VRAMP(大)のいずれかを選択するものとして説明した。しかしながら、本発明はこれに限るものではなく、複数の判定レベルを設定して、3種類以上のランプ信号から選択できるようにしてもよい。

#### 【0064】

##### <他の実施形態>

また、本発明は、上述の実施形態の1以上の機能を実現するプログラムを、ネットワーク又は記憶媒体を介してシステム又は装置に供給し、そのシステム又は装置のコンピュータにおける1つ以上のプロセッサーがプログラムを読み出し実行する処理でも実現可能である。また、1以上の機能を実現する回路(例えば、ASIC)によっても実現可能である。

#### 【符号の説明】

#### 【0065】

1：撮像素子、2：画像処理部、140：ランプ回路、150：列アナログデジタル変換器群、151：比較部、152：カウンタ・ラッチ回路、170：信号処理回路、300：コントローラ回路、400：定電圧回路

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【 四 6 】

【 四 7 】

Graph (b) illustrates the relationship between the number of pixels (画素数) on the vertical axis and the AD conversion value (AD変換値) on the horizontal axis. The graph shows two curves: a solid line representing the transformation with VRAMP (大) and a dashed line representing the transformation with VRAMP (小). A vertical dashed line at the AD conversion value  $V_s$  indicates the decision level. The solid line starts at the origin and increases linearly. The dashed line starts at a higher value on the y-axis, decreases to a minimum, and then increases linearly, eventually meeting the solid line at the decision level  $V_s$ .

【 図 8 】

【図9】

【図10A】

【図10B】

【図10C】

【図10D】

【図11】

【図12】

---

フロントページの続き

(72)発明者 小布施 武範

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 鈴木 明

(56)参考文献 特開2011-244249(JP,A)

特開2012-095218(JP,A)

特開2010-219624(JP,A)

特開2001-078097(JP,A)

特開2013-229852(JP,A)

特開2013-251677(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378

H04N 5/222 - 5/257

H03M 1/56