(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第5203727号

(P5203727)

(45) 発行日 平成25年6月5日(2013.6.5)

(24) 登録日 平成25年2月22日(2013.2.22)

(51) Int.Cl.

F 1

|             |           |            |   |

|-------------|-----------|------------|---|

| HO1L 21/338 | (2006.01) | HO1L 29/80 | F |

| HO1L 29/812 | (2006.01) | HO1L 29/80 | H |

| HO1L 29/778 | (2006.01) | HO1L 29/80 | Q |

| HO1L 21/337 | (2006.01) | HO1L 29/80 | V |

| HO1L 29/808 | (2006.01) | HO1L 29/48 | F |

請求項の数 13 外国語出願 (全 13 頁) 最終頁に続く

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2008-13133 (P2008-13133)    |

| (22) 出願日     | 平成20年1月23日 (2008.1.23)        |

| (65) 公開番号    | 特開2008-244433 (P2008-244433A) |

| (43) 公開日     | 平成20年10月9日 (2008.10.9)        |

| 審査請求日        | 平成20年6月2日 (2008.6.2)          |

| (31) 優先権主張番号 | 11/726, 975                   |

| (32) 優先日     | 平成19年3月23日 (2007.3.23)        |

| (33) 優先権主張国  | 米国 (US)                       |

|           |                                                                                                    |

|-----------|----------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 592054856<br>クリー インコーポレイテッド<br>C R E E I N C.<br>アメリカ合衆国 ノースカロライナ州 2<br>7703 ダラム シリコン ドライブ<br>4600 |

| (74) 代理人  | 110000578<br>名古屋国際特許業務法人                                                                           |

| (72) 発明者  | ステン ヘイクマン<br>アメリカ合衆国 93117 カリフォルニア州 ゴレタ ローレル ウォーク 7<br>87 アパートメント ケイ                               |

最終頁に続く

(54) 【発明の名称】窒化ガリウム系トランジスタデバイス

## (57) 【特許請求の範囲】

## 【請求項 1】

窒化ガリウム系トランジスタデバイスであって、炭化ケイ素、サファイア、スピネット、ZnO、シリコン、窒化ガリウム、及び、窒化アルミニウムからなる群から選択された材料により製造された基板と、前記基板の上方に形成された複数の活性半導体層を備える活性領域と、前記活性領域に接触して形成されたソース電極と、前記活性領域に接触して形成されたドレイン電極と、

前記活性領域上で前記ソース電極と前記ドレイン電極との間に形成されたゲート電極であって、高ショットキー障壁を有し、かつ高動作温度において低劣化を呈する材料から製作されたコンタクト部分を備え、前記コンタクト部分は、前記活性領域に接触するように配設されるゲート電極と、

10

前記活性領域の表面の少なくとも一部分上で、前記ソース電極と前記ドレイン電極との間に配設された第1のスペーサ層と、

前記コンタクト部分が拡散障壁と前記活性領域との間に置かれるように、前記コンタクト部分上に配設された拡散障壁と、

を備え、

前記コンタクト部分は、ニッケル - クロム合金部分 (NiCr) を含むトランジスタデバイス。

## 【請求項 2】

前記ニッケル - クロム合金部分は、重量で 0 パーセントより多く、重量で 90 パーセント以下のクロムを含む請求項 1 に記載の窒化ガリウム系トランジスタデバイス。

【請求項 3】

前記ニッケル - クロム合金部分は、重量で 80 パーセントのニッケルと、重量で 20 パーセントのクロムとを含む請求項 1 に記載の窒化ガリウム系トランジスタデバイス。

【請求項 4】

前記ニッケル - クロム合金部分は、重量で 50 パーセントのニッケルと、重量で 50 パーセントのクロムとを含む請求項 1 に記載の窒化ガリウム系トランジスタデバイス。

【請求項 5】

前記ニッケル - クロム合金部分は、5 nm 以上 100 nm 以下の厚さを有する請求項 1 から 4 のいずれか一項に記載の窒化ガリウム系トランジスタデバイス。 10

【請求項 6】

前記ニッケル - クロム合金部分は、20 nm の厚さを有する請求項 1 から 4 のいずれか一項に記載の窒化ガリウム系トランジスタデバイス。

【請求項 7】

前記ゲート電極は、

前記拡散障壁上に配設された側方導電層と、

前記側方導電層上に配設された保護層と、

をさらに有する請求項 1 から 6 のいずれか一項に記載の窒化ガリウム系トランジスタデバイス。 20

【請求項 8】

前記ゲート電極は、

上面が凹んだ中央領域を含む乱平面構造 (split-level structure) を有し、

前記側方導電層は、前記中央領域を挟んで非対称に形成され、前記中央領域から前記ドレイン電極の方向へより伸長している

請求項 7 に記載の窒化ガリウム系トランジスタデバイス。

【請求項 9】

窒化ガリウム (GaN) ベースの高電子移動度トランジスタ (HEMT) を含む請求項 1 から 8 のいずれか一項に記載の窒化ガリウム系トランジスタデバイス。 30

【請求項 10】

前記第 1 のスペーサ層は、絶縁窒化ケイ素 (SiN) 層を有する請求項 1 から 9 のいずれか一項に記載の窒化ガリウム系トランジスタデバイス。

【請求項 11】

前記コンタクト部分は、プラチナ (Pt)、タンクステン (W)、モリブデン (Mo)、クロム (Cr)、ニッケル - クロム合金 (NiCr)、および多結晶窒化インジウム (InN) からなる群から選択された材料を含む請求項 1 から 10 のいずれか一項に記載の窒化ガリウム系トランジスタデバイス。

【請求項 12】

前記ゲート電極、および前記第 1 のスペーサ層の少なくとも一部分を覆う第 2 のスペーサ層と。 40

前記第 2 のスペーサ層上に配設されたフィールドプレートと

をさらに備える請求項 1 から 11 のいずれか一項に記載の窒化ガリウム系トランジスタデバイス。

【請求項 13】

前記コンタクト部分及び前記拡散障壁の厚さの合計は、前記第 1 のスペーサ層の厚さより薄い、請求項 1 から 12 のいずれか一項に記載の窒化ガリウム系トランジスタデバイス。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は一般に、トランジスタに関し、より詳細には、高温において効率的に動作するように設計されたトランジスタに関する。

【背景技術】

【0002】

A1GaN/GaN半導体材料の製造面での改良が、高周波数、高温、および高電力応用分野向けの、高電子移動度トランジスタ(HEMT)などのA1GaN/GaNトランジスタの開発を進展させる助けとなってきた。A1GaN/GaNは、大きなバンドギャップ、高いピーク電子速度値および飽和電子速度値を有する(例えば、非特許文献1参照)。A1GaN/GaN HEMTは、 $10^{13} \text{ cm}^{-2}$ を超える2DEGシート密度、および比較的高い電子移動度(最大 $2019 \text{ cm}^2/\text{Vs}$ )を有することもできる(例えば、非特許文献2参照)。これらの特性により、A1GaN/GaN HEMTが、無線周波、マイクロ波、およびミリメートル波周波数において非常に高い電圧および高い電力動作を実現することが可能になる。10

【0003】

バッファおよび基板上に成長させたGaN/A1GaNベースのHEMTが開示されている(例えば、Khan等の特許文献1参照)。その他のA1GaN/GaN HEMTおよび電界効果トランジスタ(FET)も、開示されている(例えば、非特許文献3および非特許文献4参照)。これらのデバイスのいくつかは、100ギガヘルツもの高い利得-帯域幅積(fT)を示し(例えば、非特許文献5参照)、X帯において最大 $10 \text{ W/m}$ の高電力密度を示している(例えば、非特許文献6参照)。20

【0004】

【特許文献1】米国特許第5,192,987号明細書

【特許文献2】米国特許第6,586,781号明細書

【特許文献3】米国再発行特許第34,861号明細書

【特許文献4】米国特許第4,946,547号明細書

【特許文献5】米国特許第5,200,022号明細書

【非特許文献1】B. Gelmont, K. Kim and M. Shur, Monte Carlo Simulation of Electron Transport in Gallium Nitride, J.Appl.Phys. 74, (1993), pp. 1818-1821

【非特許文献2】R. Gaska, et al., Electron Transport in AlGaN-GaN Heterostructures Grown on 6H-SiC Substrates, Appl.Phys.Lett. 72, (1998), pp. 707-70930

【非特許文献3】Gaska et al., High-Temperature Performance of AlGaN/GaN HFET's on SiC Substrates, IEEE Electron Device Letters, 18, (1997), pp. 492-494

【非特許文献4】Wu et al. "High Al-content AlGaN/GaN HEMTs With Very High Performance", IEDM-1999 Digest, pp. 925-927, Washington DC, Dec. 1999

【非特許文献5】Lu et al. "AlGaN/GaN HEMTs on SiC With Over 100 GHz ft and Low Microwave Noise", IEEE Transactions on Electron Devices, Vol. 48, No. 3, March 2001, pp. 581-585

【非特許文献6】Wu et al., "Bias-dependent Performance of High-Power AlGaN/GaN HEMTs", IEDM-2001, Washington DC, Dec. 2-6, 2001

【非特許文献7】S Kamalkar and U.K. Mishra, Very High Voltage AlGaN/GaN High Electron Mobility Transistors Using a Field Plate Deposited on a Stepped Insulator, Solid State Electronics 45, (2001), pp. 1645-166240

【非特許文献8】Wu et al., 30 W/mm GaN HEMTs by field plate optimization, IEEE Electron Device Letters, Vol. 25, No.3, March 2004

【発明の開示】

【発明が解決しようとする課題】

【0005】

電子トラッピング、およびその結果生ずる直流特性と無線周波特性との差異が、これらのデバイスの性能を制限する要因となってきた。窒化ケイ素(SiN)パッシベーション(passivation)が、このトラッピングの問題を軽減するために成功裏に使用され、50

その結果、10 GHzにおいて電力密度が10 W / mmを超える高性能デバイスがもたらされている。GaNベーストランジスタ内のトラッピング効果を低減させるための方法および構造が開示されている（例えば、特許文献2参照）。しかし、その構造内に存在する高電界のため、電荷トラッピングは依然として問題である。

#### 【0006】

フィールドプレートが、GaNベースのHEMTの性能を高めるために使用されてきた（例えば、非特許文献7）。最近では、マイクロ波周波数での動作に合せてフィールドプレートを最適化することによって、4および8 GHzにおいて30 W / mmを超える電力密度の劇的な改善がもたらされている（例えば、非特許文献8参照）。しかし、これらのデバイスの信頼性は、特に高動作温度において依然として問題である。

10

#### 【課題を解決するための手段】

#### 【0007】

本発明は、高温において効率的に動作し、経時的に劣化を呈するトランジスタを提供する。本発明によるトランジスタデバイスの一実施形態では、炭化ケイ素、サファイア、スピネット、ZnO、シリコン、窒化ガリウム、及び、窒化アルミニウムからなる群から選択された材料により製造された基板と、基板の上方に形成された複数の活性半導体層を備える活性領域と、活性領域に接触して形成されたソース電極と、活性領域に接触して形成されたドレイン電極と、活性領域上でソース電極とドレイン電極との間に形成されたゲート電極であって、高ショットキー障壁を有し、かつ高動作温度において劣化を呈する材料から製作されたコンタクト部分を備え、コンタクト部分は、活性領域に接触するよう配設されるゲート電極と、活性領域の表面の少なくとも一部分上で、ソース電極とドレイン電極との間に配設された第1のスペーサ層と、コンタクト部分が拡散障壁と活性領域との間に置かれるように、コンタクト部分上に配設された拡散障壁とを備え、コンタクト部分は、ニッケル・クロム合金部分（NiCr）を含む窒化ガリウム系トランジスタデバイスが提供される。

20

#### 【0008】

本発明による電界効果トランジスタ（FET）の一実施形態は、複数の半導体層を備える活性領域を備える。ドレイン電極およびソース電極が、活性領域に接触して形成される。ゲート電極が、活性領域上でソース電極とドレイン電極の間に形成される。ゲートは、高ショットキー障壁を有し、かつ高動作温度において劣化を呈する材料から製作されるコンタクト部分を備える。コンタクト部分は、活性領域に接触するよう配設される。第1および第2のスペーサ層が形成される。第1のスペーサ層は、活性領域の表面の少なくとも一部分を覆う。第2のスペーサ層は、ゲート電極、および第1のスペーサ層の少なくとも一部分を覆う。第2のスペーサ層上に、フィールドプレートが配設される。

30

#### 【0009】

本発明によるIII族窒化物トランジスタデバイスの一実施形態は、複数の活性半導体層を備える活性領域を備える。ソース電極が、活性領域に接触して形成される。ドレイン電極が、活性領域に接触して形成される。ゲート電極が、活性領域上でソース電極とドレイン電極との間に形成される。ゲートは、プラチナ（Pt）、タンゲステン（W）、モリブデン（Mo）、クロム（Cr）、およびニッケル・クロム合金（NiCr）からなる群から選択された材料から製作されたコンタクト部分を備える。活性領域の表面の少なくとも一部分上でソース電極とドレイン電極との間に、少なくとも1層のスペーサ層が配設される。

40

#### 【0010】

本発明によるIII族窒化物トランジスタデバイスの別の実施形態は、複数の活性半導体層を備える活性領域を備える。ソース電極が、活性領域に接触して形成される。ドレイン電極が、活性領域に接触して形成される。ゲート電極が、活性領域上でソース電極とドレイン電極との間に形成される。ゲートは、多結晶窒化インジウム（InN）から製作されたコンタクト部分を備える。活性領域の表面の少なくとも一部分上でソース電極とドレイン電極との間に、少なくとも1層のスペーサ層が配設される。

50

**【発明を実施するための最良の形態】****【0011】**

本発明によるトランジスタゲートの構造および組成は、高電子移動度トランジスタ（H E M T）など、さまざまなトランジスタ構造で使用することができる。トランジスタは一般に、複数の半導体層を有する活性領域を含み、そのうち1層がチャネル層である。金属のソース電極およびドレイン電極が、活性領域に接触して形成され、活性領域内の電界を調節するために、ゲートが活性領域上でソース電極とドレイン電極との間に形成される。一実施形態では、活性領域の上に、ソースとドレインとの間で活性領域の表面の少なくとも一部分を覆って、第1の非導電性スペーサ層が形成される。別の実施形態では、第1のスペーサ層の少なくとも一部分、およびゲート電極を覆って、第2の非導電性スペーサ層が形成され、第2のスペーサ層上にフィールドプレートが配設される。これらのスペーサ層は、誘電体層、または複数の誘電体層の組合せを備えることができ、いくつかの実施形態では、エピタキシャル成長させた層など、その他の材料を備えることもできる。

10

**【0012】**

一実施形態では、第2のスペーサ層上に導電性フィールドプレートが形成され、そのスペーサ層が、フィールドプレートと下方の活性領域との間を分離する。フィールドプレートは、スペーサ層上でゲートの縁部からドレイン電極に向かってある距離だけ延び、スペーサ層上でソース電極に向かってある距離だけ延びることができる。フィールドプレートを、ソース電極またはゲートに電気的に接続することができる。このフィールドプレート構成により、デバイス内のピーク電界を低減させ、その結果、破壊電圧の増大およびトラッピングの低減をもたらすことができる。電界の低減は、漏れ電流の低減や信頼性の強化など、その他の利点を生み出すこともできる。スペーサ層とフィールドプレートとの追加の対を含むこともできる。

20

**【0013】**

ゲート電極は、特定の半導体系（例えば、GaNまたはAlGaN）に対応する高ショットキー障壁を有し、かつ高動作温度において低劣化を呈するいくつかの材料で製作することができる。GaN半導体系では、高ショットキー障壁は、0.4eVを上回る任意の障壁高さであると考えられており、好ましい障壁高さは0.45eVを上回る。高動作温度における低劣化とは、デバイスの無線周波出力電力が、デバイスが350で100時間作動された後に多くとも0.5dBまでしか劣化しないことを意味する。さまざまな材料が、ある特定の半導体系で使用される場合にこれらの特性を有する。例えば、ある特定のニッケル-クロム合金（NiCr）をゲートコンタクト金属として有するゲート電極は、高動作温度において改善された耐久性を呈する。その他の材料は、以下に説明するように、類似の結果を呈している。

30

**【0014】**

要素または層が、別の要素または層「上に」ある、別の要素または層「に接続される」、別の要素または層「に結合される」、あるいは別の要素または層「に接触する」と記載される場合、それは、他の要素または層の直接上にあっても、他の要素または層に直接接続または結合されても、他の要素または層に接触してもよく、あるいは、介在する要素または層が存在してもよいことが理解されよう。それとは対照的に、要素が別の要素または層の「直接上に」ある、別の要素または層「に直接接続される」、別の要素または層「に直接結合される」、あるいは別の要素または層「に直接接触する」と記載される場合、介在する要素または層は存在しない。同様に、第1の要素または層が、第2の要素または層「に電気的に接觸する」あるいは第2の要素または層「に電気的に結合する」と記載される場合、第1の要素または層と第2の要素または層との間の電流の流れを可能にする電気経路がある。電気経路は、コンデンサ、結合インダクタ、および／または導電性要素間に直接的な接觸がなくても電流の流れを可能にする他の要素を含むことができる。

40

**【0015】**

本発明の諸実施形態は、本明細書において、本発明の理想化された諸実施形態の概略図である断面図を参照して説明される。したがって、例えば製造技法および／または公差の

50

結果として、図面の形状との違いが予想される。本発明の諸実施形態は、本明細書に示される領域の特定の形状に限定されるものと解釈すべきではなく、例えば製造によって生ずる形状のそれを含むべきである。正方形または長方形として図示または説明される領域は一般に、標準的な製造上の公差のため、丸いまたは曲線状のフィーチャ(feature)を有する。したがって、図中に示される領域は、実際は概略であり、その形状は、デバイスの領域の正確な形状を示すものではなく、本発明の範囲を限定するものではない。

#### 【0016】

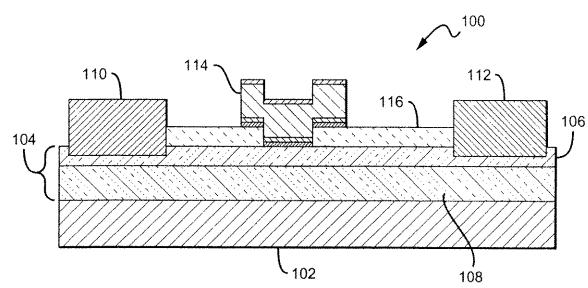

図1は、好ましくはIII族窒化物ベースであるが、他の材料系を使用することもできる、本発明によるトランジスタデバイス100の一実施形態を示す。III族窒化物とは、窒素と周期表のIII族の元素、一般にアルミニウム(Al)、ガリウム(Ga)、およびインジウム(In)との間で形成された半導体化合物を指す。この語は、AlGaNやAlInGaNなどの、三元化合物および四元化合物も指す。

10

#### 【0017】

トランジスタデバイス100は、基板102を備えることができ、基板102は、炭化ケイ素、サファイア、スピネット(spinet)、ZnO、シリコン、窒化ガリウム、窒化アルミニウム、あるいはIII族窒化物材料の成長を支えることができる任意の他の材料または材料の組合せから製作することができる。いくつかの実施形態では、基板は、完成後のトランジスタデバイスから除去される。

#### 【0018】

基板102は、さまざまな材料で製作することができ、適切な基板は、4Hポリタイプの炭化ケイ素であるが、3C、6Hおよび15Rポリタイプを含む、他の炭化ケイ素ポリタイプを使用することもできる。炭化ケイ素は、非常に高い熱伝導性を有し、その結果、炭化ケイ素上にあるIII族窒化物デバイスの全出力電力は、基板の熱放散による制限を受けない(サファイア上に形成された一部のデバイスの場合も、この制限を受けないことがある)。また、炭化ケイ素基板が利用できることから、デバイスを分離し、寄生容量を低減させる能力もたらされ、そのことが商用デバイスを可能にしている。SiC基板は、ノースカロライナ州ダラム在の本件特許出願人から入手可能であり、その製造方法は、科学文献ならびに文献(例えば、特許文献3、特許文献4、および特許文献5参照)に記載されている。

20

#### 【0019】

トランジスタデバイス100は、活性領域104を備える。活性領域104は、障壁層106および複数の半導体層108を備える。複数の半導体層108は、基板102とトランジスタデバイス100内の次の層との間の格子不整合を低減するために、基板102上に形成された核形成層(明示的に図示せず)を含むことができる。核形成層は、約1000オングストローム(㎚)の厚さであるべきだが、他の厚さを使用することもできる。核形成層は、さまざまな材料を含むことができ、適切な材料は $Al_zGa_{1-z}N$ ( $0 < z \leq 1$ )であり、また核形成層を、有機金属化学気相成長(MOCVD)、ハイドライド気相エピタキシ(HVPE)、または分子線エピタキシ(MBE)など、周知の半導体成長技法を使用して、基板102上に形成することができる。

30

#### 【0020】

複数の半導体層108は、核形成層上に形成された高抵抗バッファ層(明示的に図示せず)を備えることもできる。バッファ層は、約 $2\mu m$ 厚さのGaNで製作することができ、バッファ層の一部分は、鉄(Fe)でドープされる。III族窒化物材料のドープ層または非ドープ層など、他の材料をバッファ層に使用することもでき、好ましいバッファ層は、 $Al_xGa_yIn_{(1-x-y)}N$ ( $0 < x < 1$ 、 $0 < y < 1$ 、 $x + y \leq 1$ )などのIII族窒化物材料で製作される。

40

#### 【0021】

障壁層106は、活性領域104の上層として形成することができる。障壁層106は、III族窒化物材料のドープ層または非ドープ層を備えることができる。障壁層は、1層または複数層の $Al_xGa_{1-x}N$ で製作することができ、ただし $x$ は、 $0 \sim 1$ の範囲

50

であり、またXは、障壁層106を傾斜層とすることができますように、深さの関数とすることができる。HEMTの実施形態では、2次元電子ガス(2DEG)が、複数の半導体108と障壁層106の間のヘテロ界面に誘起される。

#### 【0022】

金属のソース電極110およびドレイン電極112が、障壁層106に接触して形成される。ゲート114が適当なレベルでバイアスをかけられると、電流が活性領域104を通ってソース電極110とドレイン電極112との間に流れることができる。ソース電極110およびドレイン電極112の形成は、上述した特許文献および刊行物に詳細に記載されている。ソース電極110およびドレイン電極112は、チタン、アルミニウム、金、またはニッケルの合金を含むが、それらに限定されないさまざまな材料で製作することができる。10

#### 【0023】

障壁層106の上面に、絶縁スペーサ層116、例えばSiNからなる層が施される。次いで、スペーサ層116内に、ゲート114用の開口がエッチングされる。次いで、ゲート114を構成する層が、電子ビーム蒸着によって堆積される。他の堆積プロセスを使用することもできる。ゲート114は、図2を参照して以下に説明するさまざまな材料で製作することができる。ゲート114は、さまざまな長さを有することができ、適切なゲート長は0.1から2.0ミクロン(μm)の範囲であるが、他のゲート長を使用することもできる。20

#### 【0024】

図1に示すように、スペーサ層116は、ゲート114とソース電極110との間、およびゲート114とドレイン電極112との間で、障壁層106を全て覆う。スペーサ層116は、誘電体層、または複数の誘電体層の組合せを備えることができる。SiN、SiO<sub>2</sub>、Si、Ge、MgO<sub>x</sub>、MgN<sub>x</sub>、ZnO、SiN<sub>x</sub>、SiO<sub>x</sub>、それらの合金または層シーケンスなどの、さまざまな誘電体材料を使用することができる。スペーサ層116は、さまざまな厚さにすることができ、厚さの適切な範囲は、約0.03μmから0.5μmである。20

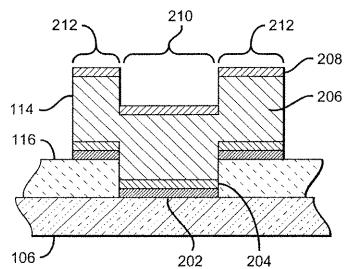

#### 【0025】

図2は、本発明によるゲート電極114の一実施形態を示す。ゲート電極114は、第1のスペーサ層116上に、ゲート114の一部分が障壁層106に接触した状態で形成される。この特定の実施形態では、ニッケル-クロム合金(NiCr)からなるコンタクト層202が、障壁層116に接触する。NiCrコンタクト層202の特性は、以下に詳細に説明する。コンタクト層202上に、拡散障壁204が形成される。拡散障壁204上に、側方導電層(lateral conduction layer)206が形成される。側方導電層206上に、保護層208が形成される。30

#### 【0026】

コンタクト層202は、活性領域の障壁層106に直接接触する。適切なコンタクト材料は、GaNまたはAlGaNなど、特定の半導体系と共に動作する際に、高ショットキー障壁(または、半導体-半導体系などの非ショットキー接合の場合、高電位障壁)を有すべきであり、高い動作電圧および温度において耐久性を呈すべきでもある。Pt、W、Mo、Cr、InN、およびさまざまなNiCr合金を含むがそれらに限定されないいくつかの材料が、III族窒化物系と共に使用される場合にこれらの基準を満たす。好ましいコンタクト層材料は、重量で80%のNi、および重量で20%のCrを有するNiCrである。NiCr(80-20重量%)が、デバイス上にコンタクト層202を形成するプロセスで使用することができる好ましいソース材料である。形成されるコンタクト層202を構成する材料の実際の組成は、ソース材料の組成とは異なってよい。例えば、NiCr(80-20重量%)ソース材料は、NiCr(50-50重量%)という組成を有するコンタクト層をもたらすことができる。NiCr(80-20重量%)は、(III族窒化物系において)Niに関連する高ショットキー障壁と、Crの高温耐久性とのどちらも有する。NiCr(80-20重量%)で形成されたコンタクト層は、GaNと共に4050

に使用される場合、0.51 eV の概略障壁高さを有する。障壁高さは、AlGaN HEMT 上では 0.6 ~ 1 eV に増大され、図 8 (以下に説明する) に示すように、340 の接合部温度で 120 時間動作しているとき、0.3 dB の出力電力の劣化があった。図 2 に示す実施形態では、NiCr コンタクト層は約 20 nm の厚さであるが、5 ~ 100 nm の範囲内で他の厚さを使用することもできる。

#### 【0027】

拡散障壁 204 は、コンタクト層 202 を側方導電層 206 から分離する。拡散障壁 204 の目的は、コンタクト層 202 および側方導電層 206 の内部拡散を防止または遅延させることである。理想的な拡散障壁は、それが分離する材料に対して不活性である。本実施形態では、拡散障壁 204 は、Pt からなる層を備える。例えば W、Mo、Ir、Ni および Cr を含む他の材料を、分離すべき金属に応じて拡散障壁として使用することができる。拡散層 204 は、図では、30 nm の概略厚さを有しているが、一般に 10 ~ 100 nm の範囲内で、他の厚さを使用することができる。

#### 【0028】

拡散障壁 204 上に、側方導電層 206 が形成される。側方導電層は、デバイス 100 の一端から他端に電流を導通させる。図 2 は、デバイスの断面を示すので、側方導電層 206 を通って電流が流れる方向は、主として断面の平面に垂直な (すなわち紙面から出る) 方向である。側方導電層 206 は、電流の流れを促進させるために、高い導電性および十分な厚さを有すべきである。図 2 は、Au を含む側方導電層 206 を示すが、高導電性を有する任意の材料を、隣接する材料を考慮して使用することができる。側方導電層 206 は、図では、400 nm の厚さを有しているが、一般に 100 ~ 2000 nm の範囲内で、他の厚さを使用することができる。

#### 【0029】

側方導電層 206 上に、保護層 208 が形成される。保護層 208 は、側方導電層 206 に損傷を与える恐れのあるプロセスからそれを遮蔽するのに必要な場合がある。いくつかの実施形態では、デバイスは、腐食性プロセスまたはその他の形で損傷を与えるプロセスで処理される。例えば、デバイスを、乾式エッチングプロセスを使用して処理することができる。保護層 208 は、側方導電層 206 を遮蔽するために使用することができる。例えばニッケルなどの材料が、この目的に適している。イオン衝撃プロセスおよび他の処理プロセスに耐性がある他の材料も、使用することができる。保護層 208 は、図 2 では、30 nm の厚さを有するように示されているが、一般に 10 ~ 100 nm の範囲内で、他の厚さを使用することもできる。

#### 【0030】

ゲート 114 が、図 2 では、乱平面構造 (split-level structure) を有するように示されている。ゲート 114 の中央領域 210 が障壁層 106 に接触し、中央領域の両側の外側領域 212 が、スペーサ層上に配設される。この特定の実施形態の構造は、外側領域 212 が、フィールドプレート構造として機能することができるようなものである。フィールドプレートについては、以下により詳細に説明する。

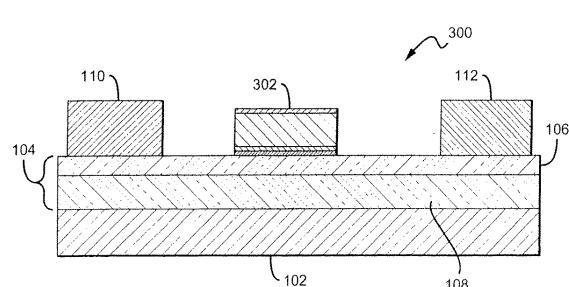

#### 【0031】

上述したゲートコントロクトの構造および組成は、さまざまなデバイスにおいて、さまざまな目的に使用することができる。例えば、図 3 は、本発明によるトランジスタデバイス 300 の一実施形態を示す。デバイス 300 は、デバイス 100 と類似の構造を有し、ソース電極 110、ドレイン電極 112、活性領域 104、障壁層 106、複数の半導体層 108、および基板 102 を含む、上述したいくつかの共通要素を共通に使う。1 つ異なるのが、ゲート 302 の構造である。ゲートは、乱平面構造を有していない。そうではなく、ゲート 302 全体が障壁層 106 上に配設される。この実施形態は、スペーサ層を含まない。その他の点では、デバイス 300 はデバイス 100 と同様に機能する。ゲート 302 は、ゲート 114 (図 2 に示す) と同じ層状構造を有し、コンタクト層、拡散障壁、側方導電層、および保護層を備える。

#### 【0032】

10

20

30

40

50

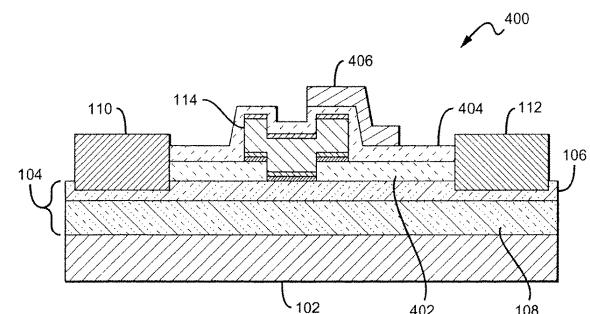

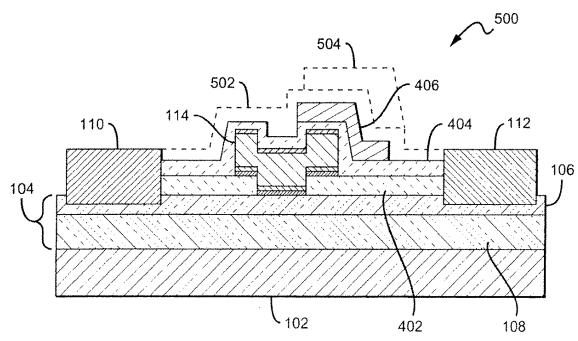

図4は、本発明によるFETデバイス400の一実施形態を示す。デバイス400は、トランジスタデバイス100に類似しており、基板102、活性領域104、障壁層106、複数の半導体層108、ソース電極110、ドレイン電極112、およびゲート電極114を含む、上述されたものと同じフィーチャを多く備える。この特定の実施形態は、第1のスペーサ層402および第2のスペーサ層404、ならびにフィールドプレート406を含む。エピタキシャル層が成長された後、障壁層106の上面に、第1の絶縁スペーサ層402が施される。スペーサ層402は、SiNまたは上述の他の適切な非導電性材料を含むことができる。次いで、第1のスペーサ層402内に、ゲート114用の開口がエッチングされ、次いでゲート114が堆積される。次いで、例えばSiNまたは別の適切な材料を含む第2の絶縁スペーサ層404が堆積され、ゲート114、および第1のスペーサ層402の表面の少なくとも一部分を覆う。次いで、第2のスペーサ層404上に、フィールドプレート406が堆積される。フィールドプレート406の典型的な組成は、Ni/Au/Niであるが、他の材料を使用することもできる。フィールドプレート406を、ソース電極110またはゲート電極114に接続することができる。上述したように、フィールドプレート406は、デバイス内の電界集中を低減させるように動作し、デバイスの性能および動作寿命を向上させる。

### 【0033】

図5は、本発明によるFETデバイス500の別の実施形態を示す。デバイス500は、デバイス400と同様に機能し、基板102、活性領域104、障壁層106、複数の半導体層108、ソース電極110、ドレイン電極112、ゲート電極114、第1のスペーサ層402および第2のスペーサ層404、ならびにフィールドプレート406を含む、上述したいくつかの共通要素を共通に使う。この特定の実施形態は、追加のスペーサ層502およびフィールドプレート504を含む。フィールドプレート504は、デバイス500内部の特定の箇所の電界をさらに低減させる働きをする。図5では、スペーサ層502およびフィールドプレート504が任意選択であることを示すために、それらの要素は破線要素として示されている。実際には、追加のスペーサ層/フィールドプレート対を、必要に応じて含むことができる。追加のフィールドプレートはそれぞれ、追加のスペーサ層によって、その前のフィールドプレートから分離することができる。

### 【0034】

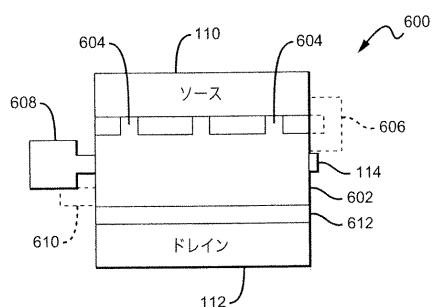

図6は、本発明によるFETデバイス600の一実施形態の上側面図を示す。フィールドプレート602を、ソース電極110またはゲート114に電気的に接続することができる。図6は、フィールドプレート602がソース電極110に接続された、本発明による一実施形態を示し、2つの代替接続構造を示す。スペーサ層612上に、フィールドプレート602とソース電極110との間に延びるように、第1の導電性バス604を形成することができる。さまざまな本数のバスを使用することができるが、使用されるバスが多くなるほど、バスによって導入され得る望ましくない容量が大きくなる。バス604は、FET活性領域をできるだけ少なく覆いながら、電流がソース電極110とフィールドプレート602との間で効果的に分散するように、十分な本数を有すべきである。バス604の適切な本数は、図6に示すように3本とすることができる。

### 【0035】

フィールドプレート602は、FET600の活性領域の外側を通ってソース電極110に接続される導電性経路606を介して、ソース電極110に電気的に接続することができる。図6に示すように、経路606は、ゲートコンタクト608とは反対側の縁部で、FET600の活性エリアの外側を通る。本発明による諸代替実施形態では、導電性経路は、ゲートコンタクト608側で、FETの活性エリアの外側を通過することができ、またはFET600は、FET600の片側または両側を通る2つ以上の導電性経路を含むことができる。一実施形態では、導電性経路604、606を、ソース電極110と同じ材料で製作することができ、他の実施形態では、それらを異なる材料で製作することができ、またソース電極110を形成した後に、製作プロセス中の別のステップで形成することができる。

## 【0036】

フィールドプレート602は、さまざまな方法によって、ゲート114に電気的に接続することもでき、2つの適切な方法が本明細書に記載される。第1に、フィールドプレートをゲート114に、FET600の活性領域の外側でフィールドプレート602とゲート114との間を通る第2の導電性経路610によって接続することができる。導電性経路610は、ゲートコンタクト608に、またはゲートコンタクト608の反対側にあるゲート114の一部分など、FET活性領域の外側にあるゲート114の一部分に接続することができる。あるいは、フィールドプレート602とゲート114を接続するために、2つ以上の導電性経路を使用することもできる。

## 【0037】

10

これに代わる接続構造が、導電性ビア (conductive via) (図示せず) の形をとる導電性経路を備え、導電性ビアは、第1のフィールドプレート602からスペーサ層612を貫通して通りゲート114まで形成することができる。ビアは、ゲート114と第1のフィールドプレート602との間の電気接続をもたらし、ビアを、まずスペーサ層612内に穴をエッチングなどにより形成し、次いでその穴を、別のステップにおいてまたはフィールドプレート602の形成中に、導電性材料で埋めることによって形成することができる。ビアは、ゲート114からフィールドプレート602への効果的な電流分散をもたらすために、フィールドプレート602の下方に周期的に配置することができる。

## 【0038】

20

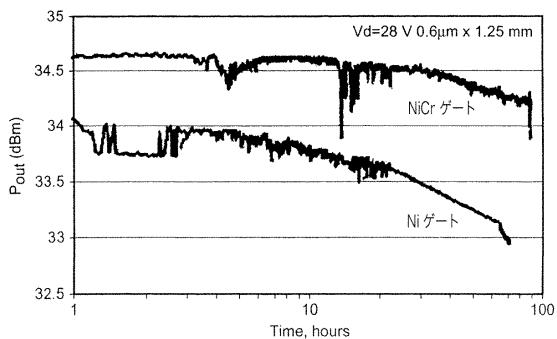

図7は、NiCr(80-20重量%)をコンタクト層として有するトランジスタデバイス、およびNiなどの典型的なコンタクト層材料を有するトランジスタデバイスの劣化を実験テストした結果を詳示するグラフを示す。グラフは、これらのデバイスのdBm単位の電力出力( $P_{out}$ )と、時間単位の時間との関係をプロットしたものである。両デバイスに28Vでバイアスをかけて加熱することにより、100時間近くの間、約350の推定接合部温度が生じた。指定条件下でデバイスにストレスをかけた後、グラフは、NiCrコンタクト層を有するデバイスに、約0.25dBmの電力出力の降下があったことを示している。Niコンタクト層を有するデバイスには、ストレスをかけた後に、1dBmを上回る電力出力の降下があった。

## 【0039】

30

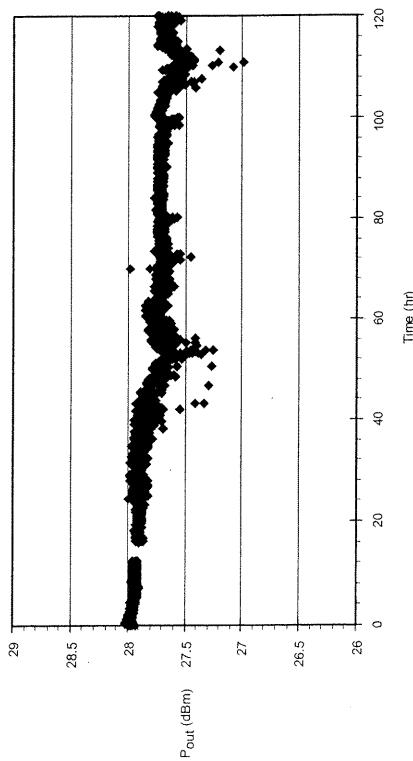

図8は、NiCr(80-20重量%)をコンタクト層として有するトランジスタデバイスの経時的劣化を実験テストした結果もたらされる、実験的データのグラフである。デバイスは、長さ0.6μm、幅246μmの概略寸法を有していた。グラフは、dBm単位の電力出力( $P_{out}$ )と、時間単位の時間との関係をプロットしたものである。デバイスに、約28Vのドレイン電圧でバイアスをかけて、加熱した。ベースプレート温度は約310であり、その結果、340に近い接合部温度が生じた。デバイスを、 $P_{out}$ を2分ごとにサンプリングした状態で、120時間加熱した。このテストは、4GHzで実施され、圧縮レベルは3dBであった。データは、指定条件下で120時間ストレスがかけられた後、デバイスに0.5dBm未満の $P_{out}$ の降下があったことを示す。

## 【0040】

40

以上、本発明を、そのいくつかの好ましい構成に即して詳細に説明してきたが、他のバージョンも可能である。したがって、本発明の趣旨および範囲は、上述のバージョンに限定されるものではない。

## 【図面の簡単な説明】

## 【0041】

【図1】本発明によるトランジスタデバイスの一実施形態の断面図である。

【図2】本発明によるトランジスタデバイスのゲートの一実施形態の断面図である。

【図3】本発明によるトランジスタデバイスの一実施形態の断面図である。

【図4】本発明によるFETの一実施形態の断面図である。

【図5】本発明によるFETの一実施形態の断面図である。

【図6】本発明によるトランジスタデバイスの上側面の平面図である。

50

【図7】2つの異なるゲート材料に関する、電力出力対時間のグラフである。

【図8】NiCrコンタクト部分を備えたゲート電極を有するトランジスタデバイスに関する、電力出力対時間のグラフである。

【図1】

【図3】

【図2】

【図4】

【図5】

【図7】

【図6】

【図8】

---

フロントページの続き

| (51)Int.Cl.             | F I                  |

|-------------------------|----------------------|

| H 01 L 29/47 (2006.01)  | H 01 L 29/48 D       |

| H 01 L 29/872 (2006.01) | H 01 L 21/28 3 0 1 B |

| H 01 L 21/28 (2006.01)  | H 01 L 29/06 3 0 1 F |

| H 01 L 29/06 (2006.01)  |                      |

(72)発明者 ウー イーフェン

アメリカ合衆国 9 3 1 1 7 カリフォルニア州 ゴレタ ファイアーサイド レーン 5 2 8

審査官 小田 浩

(56)参考文献 特開2005-086171(JP,A)

特開昭55-039636(JP,A)

特開昭51-129173(JP,A)

特開平08-255898(JP,A)

特開2000-183077(JP,A)

国際公開第2006/098801(WO,A1)

特表2008-533717(JP,A)

長倉三郎他編,岩波 理化学辞典,日本,岩波書店,1998年 4月24日,第5版,第992

頁,「ニクロム」

(58)調査した分野(Int.Cl., DB名)

H 01 L 21 / 338

H 01 L 21 / 28

H 01 L 21 / 337

H 01 L 29 / 06

H 01 L 29 / 47

H 01 L 29 / 778

H 01 L 29 / 808

H 01 L 29 / 812

H 01 L 29 / 872