(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2009-512090

(P2009-512090A)

(43) 公表日 平成21年3月19日(2009.3.19)

(51) Int.Cl.

G06F 7/76 (2006.01)

F 1

G06F 7/76 103

テーマコード(参考)

5B022

審査請求 未請求 予備審査請求 未請求 (全 15 頁)

(21) 出願番号 特願2008-536674 (P2008-536674)

(86) (22) 出願日 平成18年10月4日 (2006.10.4)

(85) 翻訳文提出日 平成20年4月16日 (2008.4.16)

(86) 國際出願番号 PCT/US2006/039180

(87) 國際公開番号 WO2007/047167

(87) 國際公開日 平成19年4月26日 (2007.4.26)

(31) 優先権主張番号 11/252,061

(32) 優先日 平成17年10月17日 (2005.10.17)

(33) 優先権主張国 米国(US)

(71) 出願人 504199127

フリースケール セミコンダクター イン

コーポレイテッド

アメリカ合衆国 78735 テキサス州

オースティン ウィリアム キャノン

ドライブ ウエスト 6501

(74) 代理人 100140109

弁理士 小野 新次郎

(74) 代理人 100089705

弁理士 社本 一夫

(74) 代理人 100075270

弁理士 小林 泰

(74) 代理人 100080137

弁理士 千葉 昭男

最終頁に続く

(54) 【発明の名称】埋め込み型マスキングを備える高速ローテータ及びその方法

## (57) 【要約】

オペランド・ローテータ(100)及びオペランドを回転させる方法が開示される。オペランド・ローテータ(100)は、オペランド・サイズのうちの1つを指示するオペランド・サイズを受け取る第1の入力と、回転量信号を受け取る第2の入力と、複数の制御信号を与える制御出力とを含む。オペランド・ローテータ(100)はまた、第1のデコーダ(102)の制御出力に結合された第1の入力と、データ・エレメントを受け取る第2の入力と、回転されたデータを与える出力を有するローテータ(104)を含む。ローテータ(104)は、複数の制御信号に応答して、複数のオペランド・サイズのうちの1つに対応するデータ・エレメントの一部を、回転量信号に対応する量だけ回転させる。

**【特許請求の範囲】****【請求項 1】**

複数のオペランド・サイズのうちの1つを指示するオペランド・サイズを受け取る第1の入力と、回転量信号を受け取る第2の入力と、複数の制御信号を与える制御出力とを有する第1のデコーダと、

前記第1のデコーダの制御出力に結合された第1の入力と、データ・エレメントを受け取る第2の入力と、出力とを有するローテータと、を備え、

前記ローテータが、前記複数の制御信号に応答して、前記複数のオペランド・サイズのうちの1つに対応するデータ・エレメントの一部を、前記回転量信号に対応する量だけ回転させる、オペランド・ローテータ。

10

**【請求項 2】**

前記第1のデコーダが更に、シフト・タイプを受け取る第3の入力を有し、

前記第1のデコーダが更に、前記シフト・タイプに応答して、前記複数の制御信号を与える

請求項1記載のオペランド・ローテータ。

**【請求項 3】**

前記ローテータが更に、前記複数の制御信号に応答して、回転されたデータ・エレメントに対してマスキング・オペレーションを実行して、シフトされたデータを前記ローテータの出力に与える請求項2記載のオペランド・ローテータ。

20

**【請求項 4】**

前記オペランド・サイズを受け取る第1の入力と、シフト量信号を受け取る第2の入力と、複数のマスキング制御信号を与える制御出力とを有する第2のデコーダと、

前記第2のデコーダの制御出力に結合された第1の入力と、前記ローテータの出力に結合された第2の入力と、シフトされたデータを与える出力とを有するマスキング・モジュールと、を更に備え、

前記マスキング・モジュールが、前記複数のマスキング制御信号に応答して、前記複数のオペランド・サイズのうちの1つに対応するデータ・エレメントの一部を、前記シフト量信号に対応する量だけシフトさせる

請求項1記載のオペランド・ローテータ。

**【請求項 5】**

前記第1のデコーダが、前記回転量信号の第1の部分を復号する第1の復号ロジックと、前記回転量信号の第2の部分を復号する第2の復号ロジックとを含む請求項1記載のオペランド・ローテータ。

30

**【請求項 6】**

前記ローテータが、前記第1の復号ロジックの出力に結合された第1の入力を有する第1段のマルチプレクサを含み、

前記第1段のマルチプレクサが、前記データ・エレメントを部分的にシフトさせる

請求項5記載のオペランド・ローテータ。

**【請求項 7】**

前記ローテータが、前記第2の復号ロジックの出力に結合された第1の入力と、前記第1段のマルチプレクサの出力に結合されて前記の部分的にシフトされたデータ・エレメントを受け取る第2の入力とを有する第2段のマルチプレクサを含み、

前記第2段のマルチプレクサが、前記の回転されたデータを与える

請求項6記載のオペランド・ローテータ。

40

**【請求項 8】**

前記複数のオペランド・サイズが、バイト・サイズ、ハーフ・ワード・サイズ及び1ワード・サイズを含む請求項1記載のオペランド・ローテータ。

**【請求項 9】**

前記複数のオペランド・サイズが、ダブル・ワード・サイズを含む請求項1記載のオペランド・ローテータ。

50

**【請求項 10】**

前記ローテータが、前記複数の制御信号に応答して、ベクトル・データの一部を左方向又は右方向へ回転させる請求項1記載のオペランド・ローテータ。

**【請求項 11】**

複数のオペランド・サイズのうちの1つを指示するオペランド・サイズを受け取る第1の入力と、回転量信号を受け取る第2の入力と、複数の制御信号を与える制御出力とを有するデコーダと、

前記デコーダの制御出力に結合された第1の入力と、データ・エレメントを受け取る第2の入力と、回転又はシフトされたデータを与える出力とを有するローテータ及びマスク・ロジック回路と、を備え、

前記ローテータ及びシフタが、前記複数の制御信号に応答して、前記複数のオペランド・サイズのうちの1つに対応するデータ・エレメントの一部を、前記回転量信号に対応する量だけ回転又はシフトさせる、オペランド・ローテータ。

**【請求項 12】**

前記ローテータ及びシフタが、前記複数の制御信号の第1の部分に応答して、前記データ・エレメントを部分的に回転又はシフトさせる第1段のマルチプレクサを含む請求項1記載のオペランド・ローテータ。

**【請求項 13】**

前記ローテータ及びシフタが更に、前記の部分的に回転されたデータ・エレメントを受け取って前記の部分的に回転又はシフトされたデータ・エレメントを与えて且つ前記データ・エレメントを更に回転又はシフトさせる第2段のマルチプレクサを含む請求項12記載のオペランド・ローテータ。

**【請求項 14】**

前記第1段のマルチプレクサが、符号拡張入力を含み、

前記第1段のマルチプレクサが、前記のシフト・タイプ信号に応答して、前記データ・エレメントを前記符号拡張入力に基づいてシフトさせる請求項12記載のオペランド・ローテータ。

**【請求項 15】**

データ・ユニットを回転させる方法であって、

第1のデコーダで第1回に複数のオペランド・サイズのうちの1つを指示する第1のオペランド・サイズを受け取るステップと、

前記第1のデコーダで回転量信号を受け取るステップと、

複数の制御信号を前記第1のデコーダからローテータへ与えるステップと、

前記第1のオペランド・サイズに対応する第1のデータ・エレメントの一部を、前記回転量信号に対応する量だけ回転させるステップとを備える方法。

**【請求項 16】**

前記第1のデコーダで第2回に複数のオペランド・サイズのうちの1つを指示する第2のオペランド・サイズを受け取るステップと、

前記第2のオペランド・サイズに対応する第2のデータ・エレメントの一部を、前記回転量信号に対応する量だけ回転させるステップと

を更に備える請求項15記載の方法。

**【請求項 17】**

前記第1のデコーダでシフト量信号を受け取るステップと、

前記複数のオペランド・サイズのうちの1つに対応するベクトル・データの一部を、前記シフト量信号に対応する量だけシフトさせるステップとを更に備える請求項15記載の方法。

**【請求項 18】**

前記ベクトル・データの一部が、代数的右シフト・オペレーションに相当する要領でシフトされる請求項17記載の方法。

**【請求項 19】**

前記複数のオペラント・サイズが、バイト・サイズ、ハーフ・ワード・サイズ及びワード・サイズを含む請求項15記載の方法。

**【請求項 20】**

前記複数のオペラント・サイズが、ダブル・ワード・サイズを含む請求項15記載の方法。

**【発明の詳細な説明】****【技術分野】****【0001】****[開示の分野]**

10

本発明は、一般的に、演算回路に関し、詳細には、集積回路においてオペラントを回転及びシフタさせるシステムに関する。

**【0002】****[背景]**

20

データ・プロセッサは、その命令セットを実行するため様々なシフト・オペレーションを必要とする。シフト・オペレーションは、左シフト、右シフト、及び回転を含み得る。シフトは、算術的又は論理的であることができ、それは、どのようにオペラントのいずれの端部でのビットが処理されるかを決定する。各シフト又は回転オペレーションは、可変長を有する。どのビットが所与のビット位置にシフトされるかは、シフト・オペレーションのタイプ及び回転量により決定される。

**【0003】**

30

幾つかの種類のシフタがある。単純なシフト・レジスタは、入力オペラントを並列に格納し、次いでそのオペラントを各クロック・サイクルに1ビット位置だけ逐次にシフトさせる。オペラントが所望のビット数だけシフトされたとき、その結果が、シフト・レジスタから並列に読み出される。別のタイプのシフタは、バレル・シフタである。バレル・シフタは、ソース・オペラントの各ビットからデスティネーション・オペラントの各ビットへの接続を含む。従って、バレル・シフタは、シフト命令を任意のビット位置数だけ実行することができる。バレル・シフタは、都合のよいことには、2つのレジスタを含み、当該2つのレジスタのそれぞれは、方向に応じてシフト・オペレーションのソース・レジスタ又はデスティネーション・レジスタのいずれかとして機能する。ソース・レジスタ及びデスティネーション・レジスタは、シフト・アレイに結合され、そのシフト・アレイは、本質的に、 $M \times M$ マトリックスのトランジスタである（なお、Mはオペラント・サイズである。）。バレル・シフタは、速いが、しかし大きい回路面積を必要とする。

**【0004】**

40

データ・プロセッサはまた、ベクトル・オペレーション（これは単一命令多重データ（S I M D）として知られている。）をサポートすることを要求される。そのようなオペレーションをサポートするため、データ・プロセッサは、ベクトル・オペラントに対するシフト及び回転オペレーションを含む算術及び論理演算を実行することを要求される。ベクトル・オペラントは、変化するサイズであることができる。ベクトル・プロセッサでシフトを実行する1つの既知の技術は、それぞれの可能性のあるベクトル・サイズをサポートする複数のシフタを並列に有する技術である。しかしながら、この技術は、複数のバレル・シフタ及び大きい回路面積を必要とする。

**【0005】**

この開示が、添付の図面を参照することにより、一層良く理解され、そしてその多数の特徴及び利点が、当業者に明らかにされるであろう。

**【0006】**

同じ参照番号の異なる図面での使用は、類似又は同一の構成要素を示す。

**【発明を実施するための最良の形態】****【0007】**

オペラントを回転させるシステム及び方法が、開示される。本システムは、複数のオペ

50

ランド・サイズのうちの 1 つを指示するオペランド・サイズを受け取る第 1 の入力と、回転量信号を受け取る第 2 の入力と、複数の制御信号を与える制御出力とを含む。本システムはまた、第 1 のデコーダの制御出力に接続された第 1 の入力と、データ・エレメントを受け取る第 2 の入力と、回転されたデータを与える出力とを有するローテータを含む。ローテータが、複数の制御信号に応答して、複数のオペランド・サイズのうちの 1 つに対応するデータ・エレメントの一部を、回転量信号に対応する量だけ回転させる。

【 0 0 0 8 】

特定の局面において、第 1 のデコーダが更に、シフト・タイプを受け取る第 3 の入力を有し、そして更にシフト・タイプに応答して複数の制御信号を与える。別の特定の局面において、ローテータが更に、複数の制御信号に応答して、回転されたデータ・エレメントに対してマスキング・オペレーションを実行して、シフトされたデータをローテータの出力に与える。

10

【 0 0 0 9 】

別の特定の局面において、本システムは、オペランド・サイズを受け取る第 1 の入力と、シフト量信号を受け取る第 2 の入力と、複数のマスキング制御信号を与える制御出力とを有する第 2 のデコーダを含む。本システムはまた、第 2 のデコーダの制御出力に結合された第 1 の入力と、ローテータ・モジュールの出力に結合された第 2 の入力と、シフトされたデータを与える出力とを有するマスキング・モジュールを含む。マスキング・モジュールは、複数のマスキング制御信号に応答して、複数のオペランド・サイズのうちの 1 つに対応するデータ・エレメントの一部を、シフト量信号に対応する量だけシフトさせる。

20

【 0 0 1 0 】

別の特定の局面において、第 1 のデコーダは、回転量信号の第 1 の部分を復号する第 1 の復号ロジックと、回転量信号の第 2 の部分を復号する第 2 の復号ロジックとを含む。

【 0 0 1 1 】

特定の局面において、ローテータは、第 1 の復号ロジックの出力に結合された第 1 の入力を有する第 1 段のマルチプレクサを含み、当該第 1 段のマルチプレクサは、データ・エレメントを部分的にシフトさせる。別の特定の局面において、ローテータは、第 2 の復号ロジックの出力に結合された第 1 の入力と、第 1 段のマルチプレクサの出力に結合されて、部分的にシフトされたデータ・エレメントを受け取る第 2 の入力とを有する第 2 段のマルチプレクサを含み、当該第 2 段のマルチプレクサが、前記の回転されたデータを与える。更に別の特定の局面において、デコーダは、回転量の第 3 の部分を復号する第 3 の復号ロジックを含み、そしてローテータは、第 3 段のマルチプレクサを含む。

30

【 0 0 1 2 】

更に別の特定の局面において、複数のオペランド・サイズは、バイト・サイズ、ハーフ・ワード・サイズ及びワード・サイズを含む。別の特定の局面において、複数のオペランド・サイズは、ダブル・ワード・サイズ、又は他の倍数のワード・サイズを含む。

【 0 0 1 3 】

特定の局面において、ローテータは、複数の制御信号に応答して、ベクトル・データの一部を左方向又は右方向へ回転させる。

40

【 0 0 1 4 】

特定の局面において、本システムは、複数のオペランド・サイズのうちの 1 つを指示するオペランド・サイズを受け取る第 1 の入力と、回転量信号を受け取る第 2 の入力と、複数の制御信号を与える制御出力とを有するデコーダを含む。本システムはまた、デコーダの制御出力に結合された第 1 の入力と、データ・エレメントを受け取る第 2 の入力と、回転又はシフトされたデータを与える出力とを有するローテータ及びマスク・ロジック回路を含み、当該ローテータ及びシフタは、複数の制御信号に応答して、複数のオペランド・サイズのうちの 1 つに対応するデータ・エレメントの一部を、回転量信号又はシフト量信号に対応する量だけ回転又はシフトさせる。

【 0 0 1 5 】

特定の局面において、ローテータ及びシフタは、複数の制御信号の第 1 の部分に応答し

50

て、データ・エレメントを部分的に回転又はシフトさせる第1段のマルチプレクサを含む。別の特定の局面において、ローテータ及びシフタは更に、部分的に回転されたデータ・エレメントを受け取り、部分的に回転又はシフトされたデータ・エレメントを与え、且つデータ・エレメントを更に回転又はシフトさせる第2段のマルチプレクサを含む。

【0016】

特定の局面において、第1段のマルチプレクサは、符号拡張入力を含み、そして第1段のマルチプレクサは、符号拡張入力に応答してデータ・エレメントをシフトさせる。

【0017】

本方法は、第1のデコーダで第1回に複数のオペランド・サイズのうちの1つを指示する第1のオペランド・サイズを受け取るステップと、第1のデコーダで回転量信号を受け取るステップとを含む。本方法はまた、複数の制御信号を前記第1のデコーダからローテータへ与えるステップと、複数のオペランド・サイズの1つに対応する第1のデータ・エレメントの一部を、回転量信号に対応する量だけ回転させるステップとを含む。

10

【0018】

特定の局面において、本方法は更に、第1のデコーダで第2回に第1のオペランド・サイズとは異なる第2のオペランド・サイズを受け取るステップを含む。この局面において、本方法はまた、第2のオペランド・サイズに対応するデータ・エレメントの一部を、回転量信号に対応する量だけ回転させるステップを含む。

【0019】

別の特定の局面において、本方法は、第1のデコーダでシフト量信号を受け取るステップと、複数のオペランド・サイズのうちの1つに対応するベクトル・データの一部を、シフト量信号に対応する量だけシフトさせるステップとを含む。更に別の特定の局面において、ベクトル・データの一部が、代数的右シフト・オペレーションに相当する要領でシフトされる。更に別の特定の局面において、複数のオペランド・サイズは、バイト・サイズ、ハーフ・ワード・サイズ及びワード・サイズを含む。特定の局面において、複数のオペランド・サイズは、ダブル・ワード・サイズ、又は他の倍数のワード・サイズを含む。

20

【0020】

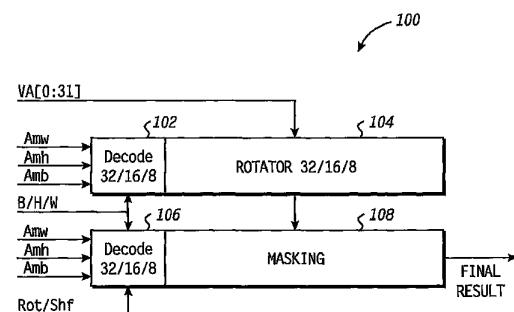

図1を参照すると、本発明に従ったオペランド・ローテータ100が示されている。オペランド・ローテータ100は、第1のデコーダ102、ローテータ104、第2のデコーダ106、及びマスキング・モジュール108を含む。第1のデコーダ102は、「A m w」、「A m h」及び「A m b」とラベルを付されたシフト量信号を受け取る第1の制御入力端子と、「B / H / W」とラベルを付されたオペランド・サイズ信号を受け取る第2の制御入力端子と、複数の制御出力端子を有する。ローテータ104は、「VA [0 : 31]」とラベルを付された入力オペランドを受け取るデータ入力と、第1のデコーダ102の制御出力端子のうちの対応の複数のものに接続された1組の制御入力端子と、回転されたデータ信号を与えるデータ出力端子とを有する。第2のデコーダ106は、シフト量信号A m w、A m h及びA m bを受け取る第1の制御入力端子と、「R o t / S h f」とラベルを付されたシフト・タイプ信号を受け取る第2の制御入力端子とを有する。「R o t / S h f」とラベルを付されたシフト・タイプ信号は、オペレーションがシフト又は回転オペレーション、左シフト又は右シフト・オペレーション、及び論理的シフト又は算術的シフト・オペレーションであるべきかどうかを指示する演算コードを含む。第2のデコーダ106はまた、複数の制御出力端子を含む。マスキング・モジュール108は、「最終結果」とラベルを付されたデータ出力信号を与えるデータ出力端子を有する。

30

【0021】

動作において、オペランド・ローテータ100は、異なるベクトル・フォーマットで表されることが可能であるオペランドに対して回転及びシフト・オペレーションを実行することが可能であるベクトル・ローテータである。図1に示される実施形態においては、オペランド・ローテータ100は、8ビット、16ビット及び32ビット（即ち、バイト、ハーフ・ワード、及びワード）に対するシフト又は回転をサポートする。ダブル・ワード・サイズ又は他の倍数のワード・サイズのような他のオペランド・サイズが、代替実施形

40

50

態においてサポートされることができる。

【0022】

その上、オペランド・ローテータ100は、ベクトル・オペランドの異なる部分を異なる量だけ回転させることができる。例えば、32ビット・オペランドについては、オペランド・ローテータ100は、ベクトル・オペランドの第1のハーフ・ワードを第1の量だけ、そしてベクトル・オペランドの第2のハーフ・ワードを第2の量だけシフトさせ得る。

【0023】

オペランド・ローテータ100は、シフトを実行し、そして2ステップで動作する。第1のステップで、ビットが、ローテータ104により回転オペレーションで回転される。第2のステップで、或る一定のビット位置が、マスキング・モジュール108によりマスキングされて、境界条件を処理して、単純な回転オペレーションを命令により決定されるような算術的シフト又は論理的シフトに変換される。回転オペレーションを実行するため、第1のデコーダ102は、制御信号A<sub>m w</sub>、A<sub>m h</sub>及びA<sub>m b</sub>並びにベクトル・サイズB/H/Wを復号する。復号された制御信号に基づいて、ローテータ104は、ベクトル・オペランドの各部分を適切な量だけ回転させる。

10

【0024】

オペランド・ローテータ100は、第2のデコーダ106及びマスキング・モジュール108を用いることにより単純な回転オペレーションをシフト・オペレーションに変換する。マスキング・モジュール108は、制御信号A<sub>m w</sub>、A<sub>m h</sub>及びA<sub>m b</sub>並びにシフト・タイプ信号R<sub>o</sub>t/S<sub>h</sub>fに応答して、実行されるべきシフトのタイプ及びシフトの境界条件を決定する。マスキング・モジュール108は、マスクを適用して、算術的シフト・オペレーション後の符号ビットのような、空けられたビット位置の中へ挿入されるべき値を決定する。

20

【0025】

回転量及びベクトル・サイズの両方を用いて追加の復号を実行することにより、ローテータ100は、制御信号を单一の32×32マトリックスで発生して、全てのサポートされたシフト量及びベクトル・サイズを処理することができる。従って、第1のデコーダ102が匹敵するバレル・シフタのそれより多少大きいとはいえ、ローテータ104のマトリックスは、32×32バレル・シフタに関して用いられるシフト・アレイとほぼ同じサイズである。更に、オペランド・ローテータ100は、それが全てのサポートされたベクトル・サイズのため用いられることができるので、ベクトル・プロセッサにおいて回路面積のかなりの大きさを節約し、そして特定のオペランドの異なる部分を独立にシフト又は回転し得る。その上、オペランド・ローテータ100は、電力を節約し、そして一部の他の解法より速い。

30

【0026】

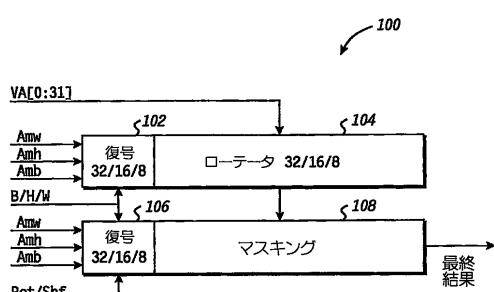

図2を参照すると、オペランド・ローテータ200の代替実施形態が示されている。オペランド・ローテータ200は、デコーダ202、ローテータ及びマスキング・モジュール204を備える。デコーダ202は、「A<sub>m w</sub>」、「A<sub>m h</sub>」及び「A<sub>m b</sub>」とラベルを付されたシフト量信号を受け取る第1の制御入力端子と、「B/H/W」とラベルを付されたオペランド・サイズ信号を受け取る第2の制御入力端子と、「R<sub>o</sub>t/S<sub>h</sub>f」とラベルを付されたシフト・タイプ信号を受け取る第3の制御入力端子と、複数の制御出力端子とを含む。ローテータ及びマスキング・モジュール204は、「VA[0:31]」とラベルを付された入力オペランドを受け取るデータ入力と、デコーダ202の制御出力端子のうちの対応の複数のものに接続された1組の制御入力端子と、「最終結果」とラベルを付されたデータ出力信号を与えるデータ出力端子とを有する。

40

【0027】

動作において、オペランド・ローテータ200は、異なるベクトル・フォーマットで表すことが可能であるオペランドに対して回転及びシフト・オペレーションを実行することが可能であるベクトル・ローテータである。オペランド・ローテータ100についてのよ

50

うに、オペランド・ローテータ200は、8ビット、16ビット及び32ビット（即ち、バイト、ハーフ・ワード及びワード）のベクトル・オペランドについてのシフト及び回転をサポートするが、しかしダブル・ワード・サイズのような他のオペランド・サイズが、代替実施形態でサポートされることができる。

#### 【0028】

回転オペレーションを実行するため、デコーダ202は、制御信号A m w、A m h及びA m b並びに制御信号B / H / W及びR o t / S h fを復号する。復号された制御信号に基づいて、ローテータ及びマスキング・モジュール204は、ベクトル・オペランドの各部分を適切な量だけ回転させ、そしてマスキングを実行して、様々なサポートされたシフト・オペレーションについての境界条件を処理する。

10

#### 【0029】

図1のオペランド・ローテータ100の利点に加えて、オペランド・ローテータ200は、回転及びマスキング機能を単一の回路の中に統合化し、従って、追加の回路面積及び追加の電力を節約し、そして追加の速度を与える。

#### 【0030】

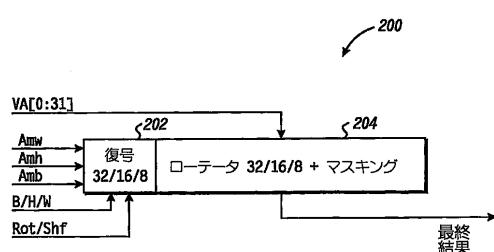

図3は、図2のデコーダ202及びローテータ及びマスキング・モジュール204の一部を形成する回路300をブロック図の形式で示す。回路300は、第1のデコーダ302と、第2のデコーダ304と、第1のマルチプレクサ306、第2のマルチプレクサ308、第3のマルチプレクサ310及びマルチプレクサ312を含む第1段のマルチプレクサとを含む。このシステムは更に、符号拡張モジュール314、第5のマルチプレクサ316、第6のマルチプレクサ318、第7のマルチプレクサ320、及び第8のマルチプレクサ322を含む。システムはまた、出力レジスタ324、及び入力レジスタ326、328及び330を含む。

20

#### 【0031】

第1のデコーダ302は、第2の入力レジスタ328に格納されている「I 1 R S - O P」とラベルを付されたシフト・タイプ信号を受け取る第1の制御入力端子と、第3の入力レジスタ330に格納されている「I 1 R S - V B」とラベルを付されたシフト量信号を受け取る第2の制御入力端子と、複数の制御出力端子とを有する。第2のデコーダ304はまた、「I 1 R S - O P」とラベルを付されたシフト量信号を受け取る第1の制御入力端子と、「I 1 R S - V B」とラベルを付されたシフト量信号を受け取る第2の制御入力端子と、複数の制御出力端子とを有する。符号拡張モジュール314は、「I 1 R S - O P」とラベルを付されたシフト・タイプ信号を受け取る制御入力と、「I 1 R S - V A」とラベルを付された4ビットの入力オペランドを受け取るデータ入力と、データ出力端子とを含む。

30

#### 【0032】

マルチプレクサ306、308、310及び312はそれぞれ、「M 0 A」、「M 0 B」、「M 1 A」、「M 1 B」、「M 2 A」、「M 2 B」、「M 3 A」及び「M 3 B」のそれぞれのラベルを付された2つのマルチプレクサから成る。マルチプレクサ306、308、310及び312のそれぞれは、「I 1 R S - V A」とラベルを付された入力オペランドを受け取る第1のデータ入力と、符号拡張モジュール314のデータ出力端子に対応する第2のデータ入力と、第1のデコーダ302の制御出力端子のうちの対応の複数のものに接続された複数の制御入力端子とを有する。第1のマルチプレクサ306は、「M 0 \_ r e s [ 0 : 15 ]」とラベルを付されたデータ出力信号を与えるデータ出力端子を含む。第2のマルチプレクサ308は、「M 1 \_ r e s [ 0 : 15 ]」とラベルを付されたデータ出力信号を与えるデータ出力端子を含む。第3のマルチプレクサ310は、「M 2 \_ r e s [ 0 : 15 ]」とラベルを付されたデータ出力信号を与えるデータ出力端子を含む。第4のマルチプレクサ312は、「M 3 \_ r e s [ 0 : 15 ]」とラベルを付されたデータ出力信号を与えるデータ出力端子を含む。

40

#### 【0033】

マルチプレクサ316、318、320及び322はそれぞれ、マルチプレクサ306

50

、308、310及び312のそれぞれの対応のデータ出力を受け取る第1のデータ入力と、第2のデコーダ304の制御出力端子のうちの対応の複数のものに接続された複数の制御入力端子とを有する。第5のマルチプレクサ316は、「R[0:7]」とラベルを付されたデータ出力信号を与えるデータ出力端子を含む。第6のマルチプレクサ318は、「R[8:15]」とラベルを付されたデータ出力信号を与えるデータ出力端子を含む。第7のマルチプレクサ320は、「R[16:23]」とラベルを付されたデータ出力信号を与えるデータ出力端子を含む。第8のマルチプレクサ322は、「R[24:31]」とラベルを付されたデータ出力信号を与えるデータ出力端子を含む。

【0034】

動作中に、第1のデコーダ302は、回転量信号、オペランド・サイズ及びシフト・タイプ信号のより高い即ち上位ビットを受け取る。第1のデコーダ302は、これらの受け取られたビットを復号して、制御信号を第1段のマルチプレクサに与える。第1段のマルチプレクサ306、308、310及び312は、第1のデコーダ302により与えられる制御信号に基づいて符号拡張モジュール314からのベクトル・データ・エレメント及び符号拡張信号を受け取り、そして上記の受け取られたデータ・エレメントに基づいて、シフトされた出力を与える。

【0035】

第1段のマルチプレクサは、粗いシフト・オペレーションを実行する。詳細には、第1段のマルチプレクサは、データ・エレメントの粗い部分に対してシフト・オペレーションを実行するよう動作する。例えば、データ・エレメントが32ビット長である場合、第1段のマルチプレクサは、データ・エレメントを備える各バイト又はワードをシフトさせる。

【0036】

その上、マルチプレクサは、データを符号拡張モジュール314から受け取る。符号拡張モジュール314を用いて、マスキング又はシフト・オペレーションを第1段のマルチプレクサに適用する。例えば、符号拡張モジュール314を用いて、回転オペレーションをシフト・オペレーションに変更するためマスキング・オペレーションをデータ・エレメントに対して実行するように1又は0をデータ・エレメントに置くことができる。

【0037】

第2のデコーダ304は、回転量の下位3ビットを復号する。第2のデコーダ304はまた、オペランド・サイズ及びシフト・タイプを受け取る。これらの入力に基づいて、第2のデコーダ304は、制御信号を第2段のマルチプレクサ316、318、320及び322を与える。

【0038】

第2段のマルチプレクサは、第1段のマルチプレクサの出力を受け取る。次いで、第2段のマルチプレクサは、第1段のマルチプレクサの出力を、第2のデコーダ304により与えられる制御信号に基づいて回転させる。第2段のマルチプレクサは、「微細な」シフト・オペレーションを実行する。詳細には、マルチプレクサ316、318、320、322のそれぞれは、16ビットを第1段のマルチプレクサから受け取り、そしてその受け取られたビットに対してシフト又は回転オペレーションを実行する。ビットが回転された後で、その回転されたビットは、出力レジスタ324で単一のオペランドの中に統合化される。次いで、出力レジスタ324は、上記の回転及びシフトされた結果を格納する。

【0039】

図示されるように「粗い」及び「微細な」構成で2つの段のマルチプレクサを使用することにより、オペランドの個々の部分が、独立に且つ異なる回転量だけ回転される。その上、符号拡張モジュール314の使用は、オペランドの統合化されたマスキングを可能にする。これは、ローテータにより必要とされる回路面積量を低減する。更に、回路300は、異なる回転及びシフト量をサポートし、回転及びシフト・オペレーションのため必要とされる全体の回路を低減し、その結果、より少ない電力しか用いないでしかもより高速である回路をもたらすことが可能である。

10

20

30

40

50

## 【0040】

他のマルチプレクサの形態が可能である。例えば、回転及びシフト・オペレーションは、單一段のマルチプレクサを用いて実行され得る。また、3段以上の段数のマルチプレクサを用いることもできる。更に、マルチプレクサは、第1及び第2のデコーダを逆にするように構成してもよい。

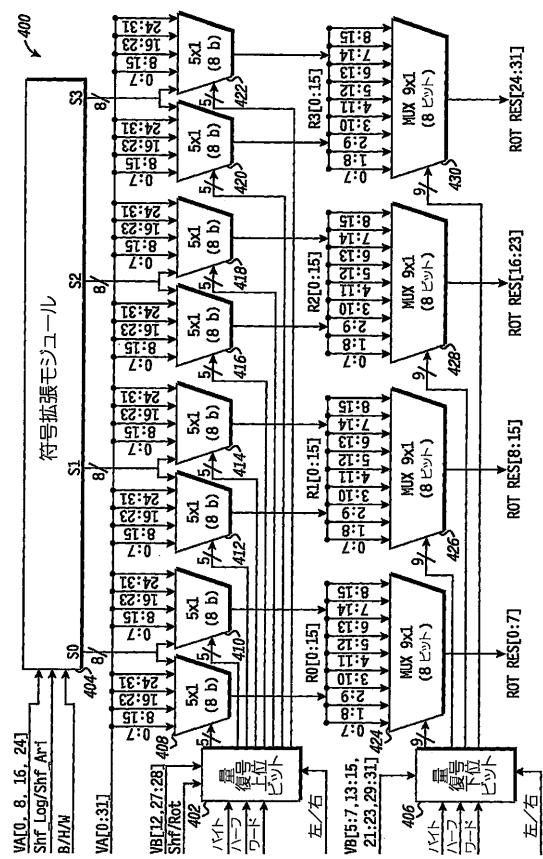

## 【0041】

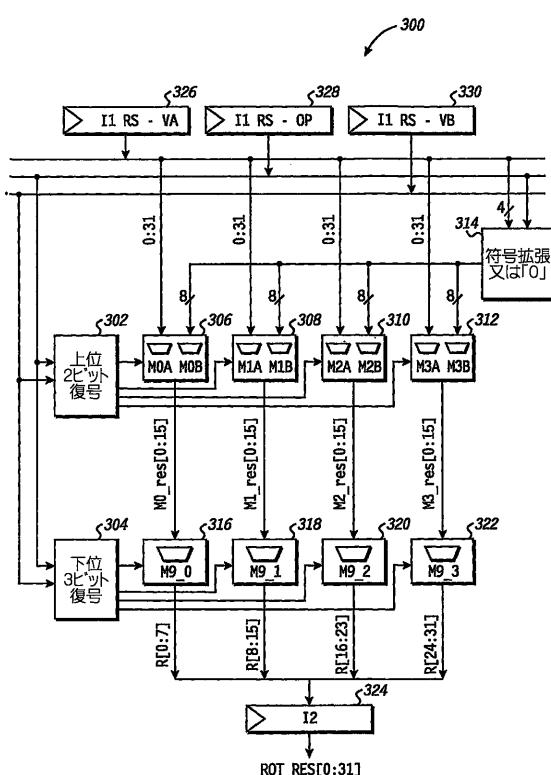

図4は、図3の回路300をより詳細に示す回路400をブロック図形式で示す。回路400を用いて、図3の回転回路300を実現することができる。回路400は、第1のデコーダ・モジュール402、第2のデコーダ・モジュール406、及び符号拡張モジュール404を含む。このシステムはまた、マルチプレクサ408、410、412、414、416、418、420及び422から成る第1段のマルチプレクサを含む。システム400は更に、マルチプレクサ424、426、428及び430から成る第2段のマルチプレクサを含む。

10

## 【0042】

第1のデコーダ・モジュール402は、「V B [ 1 2 , 2 7 : 2 8 ]」とラベルを付されたシフト量信号を受け取る第1の制御入力端子と、「S h f / R o t」とラベルを付されたシフト・タイプ信号を受け取る第2の制御入力端子と、「バイト」、「ハーフ」及び「ワード」とラベルを付されたオペランド・サイズを受け取る第3の制御入力端子と、「左/右」とラベルを付されたシフト方向信号を受け取る第4の制御入力端子とを含む。第1のデコーダ・モジュール402は更に、制御信号を与える複数の制御出力を含む。第2のデコーダ・モジュール406は、「V B [ 5 : 7 , 1 3 : 1 5 , 2 1 : 2 3 , 2 9 : 3 1 ]」とラベルを付されたシフト量信号を受け取る第1の制御入力端子と、「バイト」、「ハーフ」及び「ワード」とラベルを付されたオペランド・サイズを受け取る第2の制御入力端子と、「左/右」とラベルを付されたシフト方向信号を受け取る第3の制御入力端子とを含む。第2のデコーダ・モジュール406は更に、制御信号を与える複数の制御出力を含む。

20

## 【0043】

システム400は、「V A [ 0 : 3 1 ]」とラベルを付された入力オペランドを受け取る。マルチプレクサ408、410、412、414、416、418、420及び422を含む第1段のマルチプレクサのそれぞれは、入力オペランドに基づいて複数のデータ入力を受け取る。例えば、マルチプレクサ408は、それが入力オペランドを備えるビットの一部分を含む複数のデータ入力を受け取る。従って、図示されるように、マルチプレクサ408は、入力オペランドのビット0ないし7から成る「0 : 7」とラベルを付されたデータ入力を受け取る。第1段のマルチプレクサに含まれる他のマルチプレクサは、類似のデータ入力を受け取る。

30

## 【0044】

その上、符号拡張モジュール404は、「V A [ 0 , 8 , 1 6 , 2 4 ]」とラベルを付された複数の符号ビットを受け取る第1のデータ入力と、「S h f \_ L o g / S h f \_ A r i」とラベルを付されたシフト・タイプ信号を受け取る第1の制御入力と、「B / H / W」とラベルを付されたオペランド・サイズを受け取る第2の制御入力端子とを含む。符号拡張モジュール404はまた、「S 0」、「S 1」、「S 2」及び「S 3」とラベルを付された複数のデータ出力を含む。第1段のマルチプレクサのそれぞれは、符号拡張モジュール404のデータ出力のうちの対応の1つに接続されたデータ入力を含む。従って、マルチプレクサ408及び410のそれぞれは、符号拡張モジュール404の「S 0」データ出力に対応するデータ入力を含む。同様に、マルチプレクサ412及び414のそれぞれは、符号拡張モジュール404の「S 1」データ出力に対応するデータ入力を含み、マルチプレクサ416及び418のそれぞれは、符号拡張モジュール404の「S 2」データ出力に対応するデータ入力を含み、そしてマルチプレクサ420及び422のそれぞれは、符号拡張モジュール404の「S 3」データ出力に対応するデータ入力を含む。更に、第1段のマルチプレクサのそれぞれは、第1のデコーダ・モジュール402の制御出

40

50

力のうちの対応の複数のものに接続されている複数の制御入力を含む。第1段のマルチブレクサのそれぞれはまた、データ出力を含む。

【0045】

マルチブレクサ424、マルチブレクサ426、マルチブレクサ428及びマルチブレクサ430を含む第2段のマルチブレクサのそれぞれは、第1段のマルチブレクサの1又はそれより多いマルチブレクサのデータ出力に基づいた複数のデータ入力を含む。従って、マルチブレクサ424のデータ入力は、マルチブレクサ408及びマルチブレクサ410のデータ出力は、「R0[0:15]」とラベルを付された16ビット・ハーフ・ワードを形成する。マルチブレクサ424への入力は、或る一定ビットのハーフ・ワードR0[0:15]に基づいている。例えば、図示されるように、マルチブレクサ424の第1の入力は、ハーフ・ワードR0[0:15]のビット0:7から成り、一方第2の入力は、ハーフ・ワードR0[0:15]のビット1:8から成る。マルチブレクサ426、428及び430は、第1段のマルチブレクサの異なる出力に基づいて、類似の要領で構成されている。また、第2段のマルチブレクサのそれぞれは、第2のデコーダ・モジュール406の制御出力の対応の複数のものに接続された複数の制御入力を含む。

10

【0046】

更に、第2段のマルチブレクサのそれぞれは、データ出力を含む。例えば、マルチブレクサ424は、「ROTRES[0:7]」とラベルを付されたデータ出力を与える。マルチブレクサ424、426、428及び430のそれぞれの出力は、32ビット・レジスタに置かれるような、適切な要領で統合化されて、回転結果を生成する。

20

【0047】

動作中に、第1のデコーダ・モジュール402は、受け取られたシフト量、シフト・タイプ、オペランド・サイズ及びシフト方向の信号を復号して、第1段のマルチブレクサのための制御信号を生成する。これらの制御信号に基づいて、第1段のマルチブレクサのそれぞれは、複数の入力のうちの1つを選択して、出力として与える。従って、例えば、マルチブレクサ414は、入力0:7、8:15、16:23及び23:31のいずれかを選択して、出力として与えることができる。このようにして、第1段のマルチブレクサのそれぞれは、入力オペランドVA[0:31]に対して粗いシフトを実行する。その上、符号拡張モジュール404は、データを第1段のマルチブレクサに、その符号拡張モジュール404に与えられた制御信号に基づいて与える。符号拡張モジュール404により与えられたデータは、第1段のマルチブレクサの各マルチブレクサにより選択されて、シフト・タイプ、シフト方向及び他の制御信号に従って適切な境界条件を適用する。従って、第1段のマルチブレクサのそれぞれの出力は、各マルチブレクサに与えられた複数の入力及び符号拡張モジュール404により与えられたデータのうちの1つに基づく。

30

【0048】

第2のデコーダ・モジュール406は、受け取られたシフト量、オペランド・サイズ及びシフト方向の信号を復号して、第2段のマルチブレクサのための制御信号を生成する。これらの制御信号に基づいて、第2段のマルチブレクサのそれぞれは、上記の複数の入力のうちの1つを選択して、出力として与える。従って、例えば、マルチブレクサ424は、入力0:7、1:8、2:9、3:10、4:11、5:12、6:13、7:14及び8:15のうちのいずれかを選択して出力として与えることができる。このようにして、第2段のマルチブレクサのそれぞれは、第1段のマルチブレクサの対応の出力に対して微細なシフトを実行する。第2段のマルチブレクサの出力は、統合化されて、回転又はシフトされた最終結果を形成する。

40

【0049】

上記で説明したように、「粗い」回転段及び「微細な」回転段の使用は、より小さく、より高速で且つ電力の使用のより少ない回路をもたらす。その上、より少ない或いはより多い段数のマルチブレクサが、様々な応用に用いられることができる。

【0050】

50

図4のシステムがベクトル・エレメントに対するオペレーションに関する説明がなされたが、このシステムはまた、スカラ・エレメントに対するオペレーションを実行するよう構成することができる。その場合、スカラ・オペランドは常に同じサイズであると仮定して、デコーダは、オペランド・サイズを与えられない。更に、別のデータ入力が、第2段のマルチプレクサのそれぞれに与えられる。これらのデータ入力は、ビットを符号拡張モジュール又は他の適切なソースから注入して、第2のマスキング・オペレーションを実行する。この第2のマスキング・オペレーションは、システムが「注入されたマスキング」オペレーション又は他のオペレーションを実行して、スカラ命令セットのため適切なシフトを実行する。この構成においては、新しいデータ入力に適応するため、第2段のマルチプレクサは、図4に示されるそれより大きくなるが、しかし第1段は、単純化され、そして図4で用いられるマルチプレクサの半分プラス1だけを有することができる。

10

## 【0051】

本発明の原理が特定の装置に関して上記で説明したが、この説明は、単に例示してのもので、本発明の範囲を限定しないものとして行われていることが明らかに理解される筈である。

## 【図面の簡単な説明】

## 【0052】

【図1】図1は、本発明に従ったローテータ・システムのブロック図である。

【図2】図2は、本発明の別の実施形態に従ったローテータ・システムのブロック図である。

20

【図3】図3は、図2のデコーダとローテータ及びマスキング・モジュールの一部を形成する回路をブロック図形式で示す。

【図4】図4は、図3の回路300をより詳細に示す回路400をブロック図形式で示す。

## 【図1】

## 【図2】

## 【図3】

【 図 4 】

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                               | International application No.<br>PCT/US 08/39180 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b><br>IPC(8): G06F 7/00 (2007.01)<br>USPC: 708/209<br>According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                               |                                                  |

| <b>B. FIELDS SEARCHED</b><br>Minimum documentation searched (classification system followed by classification symbols)<br>USPC : 708/209                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                               |                                                  |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched<br>USPC: 708/209, 490                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                               |                                                  |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)<br>PubWEST(USPTO, PGPB, EPAB, JPAB); DialogPRO; WIPO, EPO, CITESEER, Google patents, Google scholar<br>Search Terms Used: rotator shifter mask arithmetic logical decoder shift                                                                                                                                                                                                                                                                                                           |                                                                                                                               |                                                  |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                               |                                                  |

| Category*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Citation of document, with indication, where appropriate, of the relevant passages                                            | Relevant to claim No.                            |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | US 5,729,482 A (WORRELL) 17 March 1998 (17.03.1998) entire document especially Fig 1-2, abstract, col 1, ln 8 to col 2, ln 67 | 1-20                                             |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | US 6,393,446 B1 (DHONG et al.) 21 May 2002 (21.05.2002) entire document                                                       | 1-20                                             |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | US 4,396,994 A (KANG et al.) 2 August 1983 (02.08.1983) entire document                                                       | 1-20                                             |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | US 5,634,065 A (GUTTAG et al.) 27 May 1997 (27.05.1997) entire document                                                       | 1-20                                             |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | US 5,696,854 A (GUTTAG et al.) 9 December 1997 (09.12.1997) entire document                                                   | 1-20                                             |

| <input type="checkbox"/> Further documents are listed in the continuation of Box C. <input type="checkbox"/>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                               |                                                  |

| * Special categories of cited documents:<br>"A" document defining the general state of the art which is not considered to be of particular relevance<br>"E" earlier application or patent but published on or after the international filing date<br>"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>"O" document referring to an oral disclosure, use, exhibition or other means<br>"P" document published prior to the international filing date but later than the priority date claimed |                                                                                                                               |                                                  |

| Date of the actual completion of the international search<br>12 July 2007 (12.07.2007)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Date of mailing of the international search report<br><b>28 NOV 2007</b>                                                      |                                                  |

| Name and mailing address of the ISA/US<br>Mail Stop PCT, Attn: ISA/US, Commissioner for Patents<br>P.O. Box 1450, Alexandria, Virginia 22313-1450<br>Facsimile No. 571-273-3201                                                                                                                                                                                                                                                                                                                                                                                                                                        | Authorized officer:<br>Lee W. Young<br>PCT Helpdesk: 571-272-4300<br>PCT OSP: 571-272-7774                                    |                                                  |

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LS,MW,MZ,NA,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IS,IT,LT,LU,LV,MC,NL,PL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BW,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,HN,HR,HU,ID,IL,IN,IS,JP,KE,KG,KM,KN,KP,KR,KZ,LA,L,C,LK,LR,LS,LT,LU,LY,MA,MD,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PG,PH,PL,PT,RO,RS,RU,SC,SD,SE,SG,SK,SL,SM,SV,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,ZA,ZM,ZW

(74)代理人 100096013

弁理士 富田 博行

(72)発明者 ヌニュース, リンカーン・アール

アメリカ合衆国テキサス州 78613, シダー・パーク, レイクライン・オーツ・ドライブ 2

026

(72)発明者 ダニシュ, アルバート・エヌ

アメリカ合衆国テキサス州 78729, オースティン, カヒル・ドライブ 8518

F ターム(参考) 5B022 AA02 BA10 DA01 FA03