(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5823717号

(P5823717)

(45) 発行日 平成27年11月25日(2015.11.25)

(24) 登録日 平成27年10月16日(2015.10.16)

(51) Int.Cl.

G05F 1/56 (2006.01)

F 1

G05F 1/56 310B

請求項の数 2 (全 7 頁)

(21) 出願番号 特願2011-75592 (P2011-75592)

(22) 出願日 平成23年3月30日 (2011.3.30)

(65) 公開番号 特開2012-208868 (P2012-208868A)

(43) 公開日 平成24年10月25日 (2012.10.25)

審査請求日 平成26年1月16日 (2014.1.16)

(73) 特許権者 000002325

セイコーインスツル株式会社

千葉県千葉市美浜区中瀬1丁目8番地

(74) 代理人 100154863

弁理士 久原 健太郎

(74) 代理人 100142837

弁理士 内野 則彰

(74) 代理人 100123685

弁理士 木村 信行

(72) 発明者 ヘイン ソチエット

千葉県千葉市美浜区中瀬1丁目8番地 セイコーインスツル株式会社内

審査官 神山 貴行

最終頁に続く

(54) 【発明の名称】ボルテージレギュレータ

## (57) 【特許請求の範囲】

## 【請求項 1】

基準電圧を出力する基準電圧回路と、

出力トランジスタと、

前記基準電圧と前記出力トランジスタの出力する電圧を分圧した分圧電圧との差を増幅して出力し、前記出力トランジスタのゲートを制御する差動増幅回路と、

突入電流防止回路と、

出力電圧検出回路と、を備えたボルテージレギュレータにおいて

前記出力電圧検出回路は、

反転入力端子が前記差動増幅回路の非反転入力端子に接続され、非反転入力端子が前記基準電圧回路に接続され、電源端子が第一のトランジスタのドレインに接続され、出力端子が第二のトランジスタのゲートに接続されたアンプと、 10

出力が容量と前記第一のトランジスタのゲートと前記第二のトランジスタのドレインと前記突入電流防止回路の制御端子に接続された第一の定電流回路と、を備え

電源起動後に、前記第一のトランジスタがオン、前記第二のトランジスタがオフして、前記突入電流防止回路が動作して、

前記出力電圧検出回路が前記容量の電圧によって前記突入電流防止回路を停止させると、前記第一のトランジスタがオフして前記出力電圧検出回路を停止させる、ことを特徴としたボルテージレギュレータ。

## 【請求項 2】

10

20

基準電圧を出力する基準電圧回路と、

出力トランジスタと、

前記基準電圧と前記出力トランジスタの出力する電圧を分圧した分圧電圧との差を増幅して出力し、前記出力トランジスタのゲートを制御する差動增幅回路と、

突入電流防止回路と、

出力電圧検出回路と、を備えたボルテージレギュレータにおいて

前記出力電圧検出回路は、

ゲートが前記出力電圧検出回路の出力端子に接続された第一のトランジスタと、

ドレンが前記出力電圧検出回路の出力端子に接続された第二のトランジスタと、

出力が容量と前記出力電圧検出回路の出力端子に接続された第一の定電流回路と、

10

入力が前記第一のトランジスタのドレンに接続された第二の定電流回路と、

第三の定電流回路と、

ゲートが前記第二の定電流回路の入力に接続され、ドレンが前記第三の定電流回路の出力と接続され、ソースが前記第二のトランジスタのゲートに接続された第三のトランジスタと、

ゲートが前記差動增幅回路の非反転入力端子に接続され、ドレンが前記第二のトランジスタのゲートに接続された第四のトランジスタと、を備え

電源起動後に、前記第一のトランジスタがオン、前記第二のトランジスタがオフして、前記突入電流防止回路が動作して、

前記出力電圧検出回路が前記容量の電圧によって前記突入電流防止回路を停止させると、前記第一のトランジスタがオフして前記出力電圧検出回路を停止させる、ことを特徴としたボルテージレギュレータ。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、出力電圧検出回路を備えたボルテージレギュレータに関し、より詳しくは起動後に突入電流防止回路の動作を止めるため、出力電圧が立ち上がった事を検出し信号を出力する出力電圧検出回路に関する。

##### 【背景技術】

##### 【0002】

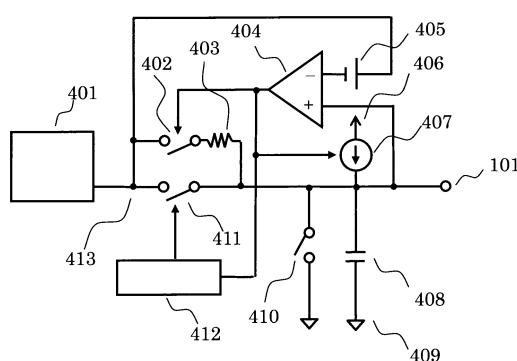

従来のボルテージレギュレータについて説明する。図3は、従来のボルテージレギュレータの回路図である。この基準電圧回路は、定電圧源401とソフトスタート回路からなっている。ソフトスタート回路は、コンパレータ404と遅延回路412と定電流源407と容量408と抵抗403とスイッチ402、410、411を備えている。

##### 【0003】

定電流源407と容量408の接点は、基準電圧回路の出力端子101に接続される。コンパレータ405は、非反転入力端子に出力端子101が接続され、反転入力端子に定電圧源401の出力端子がオフセット電圧405を介して接続されている。コンパレータ404の出力端子は、スイッチ402と定電流源407と遅延回路412に接続されている。遅延回路412の出力端子はスイッチ411に接続されている。

##### 【0004】

容量408は、定電流源407から定電流Icの電流を受けて充電される。コンパレータ404は、定電圧源401の出力電圧413から所定のオフセット電圧405を引いた電圧と、定電流源407と容量408の接点の電圧とを比較して、その比較結果に応じた出力電圧を出力する。定電圧源401の出力電圧413から所望のオフセット電圧405を引いた電圧よりも、定電流源407と容量408の接点の電圧が高くなると、スイッチ402はオンして、定電流源407は停止して、遅延回路412が動作を始める。スイッチ402がオンすると、定電圧源401から抵抗403を介して容量408にRCの時定数に合わせて充電される。遅延回路412の出力はスイッチ411に接続されていて、遅延回路412が動作を開始してから所定の時間が経過した後にスイッチ411をオンする

10

20

30

40

50

。スイッチ 411 がオンすると、定電圧源 401 の出力電圧 413 が直接、基準電圧 101 に接続される。

#### 【0005】

従来の基準電圧回路の動作について説明する。スイッチ 410 がオンしている状態では、基準電圧回路は動作を停止していて、出力端子 101 の基準電圧は 0V となっている。スイッチ 410 がオフすると、基準電圧回路は動作を開始する。定電流源 407 から定電流  $I_c$  の電流を受けて、容量 408 に定電流充電が開始される。この時、基準電圧 101 は、定電流  $I_c$  と容量 408 に応じて、直線的に上昇する。容量 408 に充電された電圧が、定電圧源 401 の電圧 413 をオフセット電圧 405 で引いた電圧を超えると、コンパレータ 404 の出力信号が反転するので、スイッチ 402 がオンし、定電流源 407 は停止し、遅延回路 412 が動作を始める。定電流源 407 が停止したことで、定電圧源 401 の出力電圧 413 から、抵抗 403 を介して容量 408 に充電が行われる。

10

#### 【0006】

遅延回路 412 が動作を始めてから所定の時間が経過した後に、スイッチ 411 がオンすることによって、定電圧源 401 の出力電圧 413 が直接、基準電圧 101 となる。(例えば、特許文献 1 図 2 参照)。

#### 【先行技術文献】

#### 【特許文献】

#### 【0007】

【特許文献 1】特開 2000-56843 号公報

20

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0008】

しかしながら従来の技術では、出力電圧が立ち上がったあとタイミングよくソフトスタート回路を切り離さなければならないという課題があった。

#### 【0009】

本発明では、上記課題に鑑みてなされ、ボルテージレギュレータが起動直後に、高速でかつタイミングよく突入電流防止回路の動作を止め消費電流を削減できるボルテージレギュレータを提供する。

#### 【課題を解決するための手段】

30

#### 【0010】

基準電圧を出力する基準電圧回路と、出力トランジスタと、基準電圧と出力トランジスタの出力する電圧を分圧した分圧電圧との差を増幅して出力し、出力トランジスタのゲートを制御する第一の差動増幅回路と、ドレインが出力トランジスタのゲートに接続され、ゲートが制御信号端子に接続され、ソースが制限トランジスタのドレインに接続された第一スイッティングトランジスタと、突入電流防止回路と、出力電圧検出回路とを備えたボルテージレギュレータにおいて、出力電圧検出回路は、反転入力端子が第一の差動増幅回路の非反転入力端子に接続され、反転入力端子が基準電圧回路に接続され、電源端子が第一のトランジスタのドレインに接続され、出力端子が第二のトランジスタのゲートに接続されたアンプと、出力が容量と第二のトランジスタのドレインに接続された定電流回路とを備える。

40

#### 【発明の効果】

#### 【0011】

本発明の出力電圧検出回路を備えたボルテージレギュレータは、ボルテージレギュレータの基準電圧とフィードバック電圧  $V_{fb}$  を比較するコンパレータを使用することで、高速でかつタイミングよく突入電流防止回路を切り離すことができる。

#### 【図面の簡単な説明】

#### 【0012】

【図 1】第一の実施形態のボルテージレギュレータを示す回路図である。

【図 2】第二の実施形態のボルテージレギュレータを示す回路図である。

50

【図3】従来のボルテージレギュレータを示す回路図である。

【発明を実施するための形態】

【0013】

本発明を実施するための形態について、図面を参照して説明する。

【実施例1】

【0014】

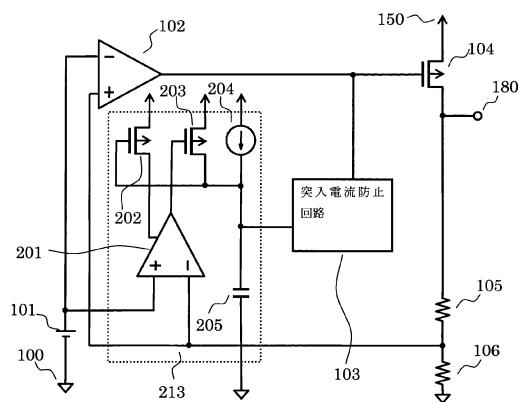

図1は、第一の実施形態のボルテージレギュレータの回路図である。第一の実施形態のボルテージレギュレータは、基準電圧回路101と、差動増幅回路102と、出力トランジスタ104と、分圧回路の抵抗105と106と、突入電流防止回路103と、出力電圧検出回路213で構成されている。10 出力電圧検出回路213はPMOSトランジスタ202、203と、定電流回路204と、オフセット付きアンプ201と、容量205で構成されている。

【0015】

第一の本実施形態のボルテージレギュレータの接続について説明する。差動増幅回路102は、反転入力端子は基準電圧回路101に接続され、非反転入力端子は抵抗105と106の接続点に接続され、出力端子はPMOSトランジスタ104のゲート及び突入電流防止回路103の出力に接続される。基準電圧回路101のもう一方はグラウンド端子100に接続される。オフセット付きアンプ201は、非反転入力端子は基準電圧回路101の正極に接続され、反転入力端子は抵抗105と106の接続点に接続され、出力端子はPMOSトランジスタ203のゲートに接続される。20 PMOSトランジスタ203は、ドレインは突入電流防止回路103の入力に接続され、ソースは電源端子150に接続される。PMOSトランジスタ202は、ゲートは突入電流防止回路103の入力に接続され、ドレインはオフセット付きアンプ201の電源端子に接続され、ソースは電源端子150に接続される。定電流回路204は、一方は突入電流防止回路103の入力および容量205に接続され、もう一方は電源端子150に接続される。容量205のもう一方はグラウンド端子100に接続される。

【0016】

次に、第一の本実施形態ボルテージレギュレータの動作について説明する。抵抗105と106は、出力端子180の電圧である出力電圧 $V_{out}$ を分圧し、分圧電圧 $V_{fb}$ を出力する。差動増幅回路102は、基準電圧回路101の出力電圧 $V_{ref}$ と分圧電圧 $V_{fb}$ とを比較し、出力電圧 $V_{out}$ が一定になるよう出力トランジスタ104のゲート電圧を制御する。出力電圧 $V_{out}$ が所定電圧よりも高いと、分圧電圧 $V_{fb}$ が基準電圧 $V_{ref}$ よりも高くなる。そして、差動増幅回路102の出力信号（出力トランジスタ104のゲート電圧）が高くなり、出力トランジスタ104はオフしていく、出力電圧 $V_{out}$ は低くなる。こうして、出力電圧 $V_{out}$ を一定になるように制御する。また、出力電圧 $V_{out}$ が所定電圧よりも低いと、上記と逆の動作をして、出力電圧 $V_{out}$ は高くなる。こうして、出力電圧 $V_{out}$ が一定になるように制御する。突入電流防止回路103は出力トランジスタ104に突入電流が流れた事を検出して出力トランジスタ104のゲート電圧を $H_i$ になるように制御する。30

【0017】

電源起動後、出力電圧検出回路213の出力はグラウンドレベルのためPMOSトランジスタ202がオンしてオフセット付きアンプ201に電源を供給する。分圧電圧 $V_{fb}$ は出力電圧 $V_{out}$ が立ち上がってないため基準電圧 $V_{ref}$ より低い電圧にあり、オフセット付きアンプ201に $H_i$ を出力させる。そして、PMOSトランジスタ203をオフさせ、定電流回路204の電流が容量205を充電して徐々に出力電圧検出回路213の出力を立ち上げて行く。突入電流防止回路103は出力電圧検出回路213の $L_o$ の信号を受けている間起動し、突入電流を防止するように動作する。出力電圧検出回路213の出力の立ち上げ時間は定電流回路204の電流値と容量205の容量値で決まり、ボルテージレギュレータの起動時間より長くしボルテージレギュレータの起動中に突入電流防止回路103の動作が停止しないように設定する。出力電圧検出回路213の出力があ4050

る程度立ち上がると、突入電流防止回路 103 は動作を止めボルテージレギュレータの起動後に電流を消費する事を止める。さらに、PMOSトランジスタ 202 がオフし、オフセット付きアンプ 201 の動作を止めボルテージレギュレータの起動後に電流を消費する事を止める。

#### 【0018】

オフセット付きアンプ 201 は非反転入力端子にオフセットをつけて分圧電圧  $V_{fb}$  を基準電圧  $V_{ref}$  より高くなるようにする。こうして、分圧電圧  $V_{fb}$  が基準電圧  $V_{ref}$  近辺まで立ち上がったときに突入電流防止回路 103 と出力電圧検出回路 213 の動作がオンオフを繰り返す事を防止できる。

#### 【0019】

以上により、第一の実施形態のボルテージレギュレータは高速でかつタイミングよく突入電流防止回路を切り離すことが可能となる。また、突入電流防止回路を切り離したあと出力電圧検出回路の電源供給を止めるため低消費電力化を行うことができる。

#### 【実施例 2】

#### 【0020】

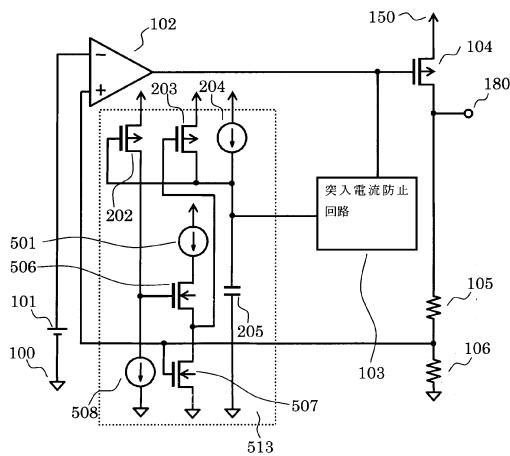

図 2 は、第二の実施形態のボルテージレギュレータの回路図である。図 1 との違いは、出力電圧検出回路 513 のオフセット付きアンプの構成を別構成にした点である。

#### 【0021】

次に第二の実施形態のボルテージレギュレータの接続について説明する。PMOSトランジスタ 203 は、ドレインは突入電流防止回路 103 の入力に接続され、ソースは電源端子 150 に接続され、ゲートはNMOSトランジスタ 506 のソースおよびNMOSトランジスタ 507 のドレインに接続される。PMOSトランジスタ 202 は、ゲートは突入電流防止回路 103 の入力に接続され、ドレインはNMOSトランジスタ 506 のゲートおよび定電流回路 508 に接続され、ソースは電源端子 150 に接続される。定電流回路 508 のもう一方はグラウンド端子 100 に接続される。定電流回路 204 は、一方は突入電流防止回路 103 の入力および容量 205 に接続され、もう一方は電源端子 150 に接続される。容量 205 のもう一方はグラウンド端子 100 に接続される。NMOSトランジスタ 506 のドレインは定電流回路 501 に接続され、定電流回路 501 のもう一方は電源端子 150 に接続される。NMOSトランジスタ 507 は、ゲートは差動増幅回路 102 の非反転入力端子に接続され、ソースはグラウンド端子 100 に接続される。

#### 【0022】

次に、第二の実施形態のボルテージレギュレータの動作について説明する。定電流源 501 と NMOSトランジスタ 507 でシングルエンドアンプが構成されている。このシングルエンドアンプの反転しきい値をフィードバック電圧  $V_{fb}$  よりも若干低く設ける。電源が投入されると PMOSトランジスタ 202 のゲート電圧はグラウンドレベルとなり PMOSトランジスタ 202 をオンさせる。そして、NMOSトランジスタ 506 のゲート電圧は  $H_i$  となり NMOSトランジスタ 506 をオンさせる。

#### 【0023】

フィードバック電圧  $V_{fb}$  はシングルエンドアンプの反転しきい値より低いため、シングルエンドアンプの出力がハイとなり、PMOSトランジスタ 203 はオフさせる。そして、定電流回路 204 の電流が容量 205 を充電して徐々に出力電圧検出回路 513 の出力を立ち上げて行く。突入電流防止回路 103 は出力電圧検出回路 513 の  $L_o$  の信号を受けている間起動し、突入電流を防止するように動作する。出力電圧検出回路 513 の出力の立ち上げ時間は定電流回路 204 の電流値と容量 205 の容量値で決まり、ボルテージレギュレータの起動時間より長くしボルテージレギュレータの起動中に突入電流防止回路 103 の動作が停止しないように設定する。

#### 【0024】

出力端子 180 の電圧がさらに立ち上がると、フィードバック電圧  $V_{fb}$  がシングルエンドアンプの反転しきい値を超えるため、シングルエンドアンプの出力が反転し  $L_o$  の信号を出力する。すると、PMOSトランジスタ 503 がオンして容量 205 を充電し、出

10

20

30

40

50

力電圧検出回路 513 の出力を電源電圧 150 にして突入電流防止回路 103 をオフさせる。同時に PMOS ランジスタ 202 もオフされ、定電流回路 508 により NMOS ランジスタ 206 のゲートがグラウンドプルダウンされる。そして、NMOS ランジスタ 506 をオフさせ出力電圧検出回路 513 の出力に LO 出力し出力電圧検出回路 513 の消費電流を遮断する。

【 0 0 2 5 】

以上により、第二の実施形態のボルテージレギュレータは高速でかつタイミングよく突入電流防止回路を切り離すことが可能となる。また、突入電流防止回路を切り離したあと出力電圧検出回路の電源供給を止めるため低消費電力化を行うことができる。

## 【符号の説明】

【 0 0 2 6 】

100 グラウン

150 電源端子

## 1 8 0 出力端子

101 基準電圧回路

## 1 0 2 差動增幅回路

## 1.0.3 突入電流防止回路

2 1 3、 5 1 3 出力電圧横出回路

2 2 4、 5 2 1 5 3 3 実電流回路

204、501

10

〔 四 1 〕

( 3 )

【 図 2 】

---

フロントページの続き

(56)参考文献 米国特許出願公開第2004/0201369(US,A1)

特開2009-169785(JP,A)

特開2009-266121(JP,A)

特開2008-276477(JP,A)

(58)調査した分野(Int.Cl., DB名)

G05F 1/56