(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5983236号

(P5983236)

(45) 発行日 平成28年8月31日(2016.8.31)

(24) 登録日 平成28年8月12日(2016.8.12)

(51) Int.Cl.

F 1

G 11 C 16/02

(2006.01)

G 11 C 16/06

17/00

6 1 1 F

G 11 C 16/06

(2006.01)

G 11 C 16/04

17/00

6 3 5

G 11 C 16/04

(2006.01)

G 11 C 16/04

17/00

6 2 2 A

請求項の数 5 (全 29 頁)

(21) 出願番号

特願2012-210399 (P2012-210399)

(22) 出願日

平成24年9月25日 (2012.9.25)

(65) 公開番号

特開2014-67461 (P2014-67461A)

(43) 公開日

平成26年4月17日 (2014.4.17)

審査請求日

平成27年5月27日 (2015.5.27)

(73) 特許権者 514315159

株式会社ソシオネクスト

神奈川県横浜市港北区新横浜2丁目10番

23

(74) 代理人 100092152

弁理士 服部 豊

(72) 発明者 竹内 淳

神奈川県横浜市港北区新横浜2丁目10番

23 富士通セミコンダクター株式会社内

審査官 後藤 彰

最終頁に続く

(54) 【発明の名称】半導体記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

ワード線群とビット線群の交差位置にそれぞれ配置され、共通のソース線に接続されたメモリセル群を含む複数のメモリブロックであって、前記複数のメモリブロック間で前記ワード線群を共有し、前記複数のメモリブロック毎に分離された複数の前記ソース線を備える複数のメモリブロックと、

プログラム動作時に、前記複数のメモリブロックのうち、プログラムするメモリセルが含まれるメモリブロックの前記ソース線に第1電圧を供給し、前記プログラムするメモリセルが含まれないメモリブロックの前記ソース線に前記第1電圧と異なる第2電圧を供給する回路部と、

を備え、

前記メモリセル群は、Pチャネル型トランジスタであることを特徴とする半導体記憶装置。

## 【請求項 2】

前記第2電圧は、前記第1電圧よりも高い電圧であることを特徴とする請求項1に記載の半導体記憶装置。

## 【請求項 3】

1回の前記プログラム動作時に、前記プログラムするメモリセルが、前記ワード線群を共有する前記複数のメモリブロックのうち、いずれか1つのメモリブロックから選択されることを特徴とする請求項1又は2に記載の半導体記憶装置。

**【請求項 4】**

1回の前記プログラム動作時に、前記プログラムするメモリセルの情報を含むデータを上位ビットデータと下位ビットデータに分割し、前記上位ビットデータを、前記複数のメモリブロックのうち、第1のメモリブロックに対応させ、前記下位ビットデータを、前記複数のメモリブロックのうち、第2のメモリブロックに対応させて、前記プログラム動作を行うことを特徴とする請求項1又は2に記載の半導体記憶装置。

**【請求項 5】**

前記回路部は、前記プログラム動作時に、前記複数のメモリブロックのうち、前記プログラムするメモリセルが含まれないメモリブロックの前記ソース線に、当該メモリブロックのウェルと当該メモリブロック内のメモリセルのソース接合との容量結合によって昇圧された前記第2電圧を供給することを特徴とする請求項1に記載の半導体記憶装置。10

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体記憶装置に関する。

**【背景技術】****【0002】**

半導体記憶装置として、フラッシュメモリ、E P R O M (Erasable Programmable Read Only Memory)、E E P R O M (Electrically Erasable Programmable Read Only Memory)等のメモリが知られている。このような半導体記憶装置では、データの書き込み(プログラム)を、メモリセルの電荷蓄積層にチャネルホットエレクトロンを注入することで行う方式が知られている。このほか、データのプログラムを、バンド間トンネル現象によってドレイン付近に誘起されるホットエレクトロンを注入することで行う方式が知られている。20

**【0003】**

半導体記憶装置に関し、それに設けられるメモリセルアレイを、複数のメモリセルを含む複数のブロックに分割する形態が知られている。更に、ブロック内の一方向に配列されるメモリセル群を共通のワード線に接続し、別方向に配列されるメモリセル群を共通のビット線に接続し、ブロック内の全メモリセルを共通のソース線に接続する形態が知られている。また、プログラム動作時に、そのような各ブロックの又は異なるブロック間のソース線電圧を制御する技術が知られている。30

**【先行技術文献】****【特許文献】****【0004】**

【特許文献1】特開2006-156925号公報

【特許文献2】特開2009-212992号公報

【特許文献3】特開2004-39091号公報

【特許文献4】特開2001-291392号公報

【特許文献5】特開2003-123493号公報

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

上記のようなブロックを含む半導体記憶装置では、プログラム動作時に、ブロック内のプログラム対象のメモリセルと同じワード線に接続されたプログラム非対象のメモリセルが、ゲートディスターブの影響を受ける。そのブロックのソース線電圧を高くするように制御すると、プログラム対象のメモリセルと同じワード線に接続されたプログラム非対象のメモリセルのゲートディスターブ耐性が改善される。しかし、このようにブロックのソース電圧を高くすると、そのブロック内のプログラム対象のメモリセルと同じビット線に接続されたプログラム非対象のメモリセルに流れる電流が増加する。

**【課題を解決するための手段】**

10

20

30

40

50

## 【0006】

本発明の一観点によれば、ワード線群とビット線群の交差位置にそれぞれ配置され、共通のソース線に接続されたメモリセル群を含む複数のメモリブロックであって、前記複数のメモリブロック間で前記ワード線群を共有し、前記複数のメモリブロック毎に分離された複数の前記ソース線を備える複数のメモリブロックと、プログラム動作時に、前記複数のメモリブロックのうち、プログラムするメモリセルが含まれるメモリブロックの前記ソース線に第1電圧を供給し、前記プログラムするメモリセルが含まれないメモリブロックの前記ソース線に前記第1電圧と異なる第2電圧を供給する回路部と、を備え、前記メモリセル群は、Pチャネル型トランジスタである半導体記憶装置が提供される。

## 【発明の効果】

10

## 【0007】

開示の技術によれば、プログラム動作時に、プログラム非対象メモリセルのソースに流れるリーク電流の増加を抑えつつ、プログラム非対象メモリセルへのゲートディスターブによる閾値電圧  $V_{th}$  の変化を抑制することのできる半導体記憶装置が実現可能になる。

## 【図面の簡単な説明】

## 【0008】

【図1】メモリ内蔵マイコンの構成例を示す図である。

【図2】フラッシュメモリの構成例を示す図である。

【図3】メモリコアの構成例を示す図である。

【図4】ワード線選択回路の一例を示す図である。

20

【図5】ビット線選択回路の一例を示す図である。

【図6】グローバルビット線選択回路の一例を示す図である。

【図7】リードアンプの一例を示す図である。

【図8】ライトアンプの一例を示す図である。

【図9】リード動作波形の一例を示す図である。

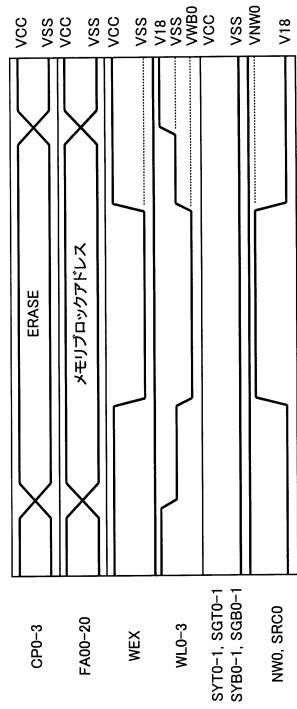

【図10】イレース動作波形の一例を示す図である。

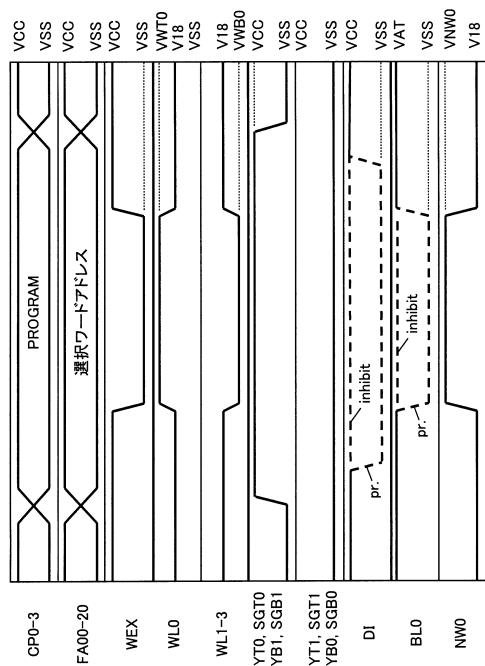

【図11】プログラム動作波形の一例を示す図である。

【図12】電圧の設定例を示す図である。

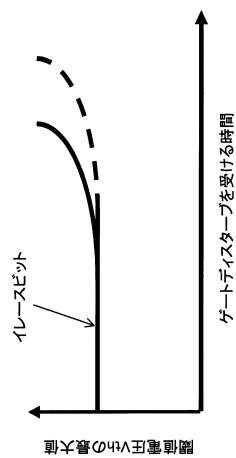

【図13】ディスターブの説明図である。

【図14】ゲートディスターブを受ける時間と閾値電圧の関係の説明図である。

30

【図15】閾値電圧分布の説明図である。

【図16】第1の実施の形態に係るメモリブロック領域の構成例を示す図である。

【図17】第1の実施の形態に係るソース線スイッチ及びソース選択線駆動回路の一例を示す図である。

【図18】第1の実施の形態に係るプログラム動作波形の一例を示す図である。

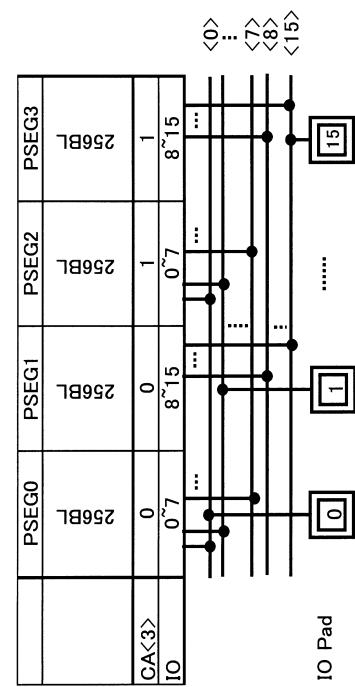

【図19】プログラムセグメントに分割しないメモリブロック領域におけるビット線選択の説明図である。

【図20】第1の実施の形態に係るメモリブロック領域におけるビット線選択の説明図である。

【図21】第2の実施の形態に係るソース線スイッチ及びソース選択線駆動回路の一例を示す図である。

40

【図22】第2の実施の形態に係るプログラム動作波形の一例を示す図である。

【図23】第3の実施の形態に係るメモリブロック領域の構成例を示す図である。

【図24】第4の実施の形態に係るメモリブロック領域の構成例を示す図である。

【図25】アドレス割り付けの一例を示す図（その1）である。

【図26】アドレス割り付けの一例を示す図（その2）である。

【図27】選択ビット線の割り付け例を示す図である。

【図28】第5の実施の形態に係るアドレス割り付けの一例を示す図である。

【図29】第5の実施の形態に係るソース線スイッチ及びソース選択線駆動回路の一例を示す図である。

50

## 【発明を実施するための形態】

## 【0009】

以下、フラッシュメモリを例に、図面を参照して詳細に説明する。

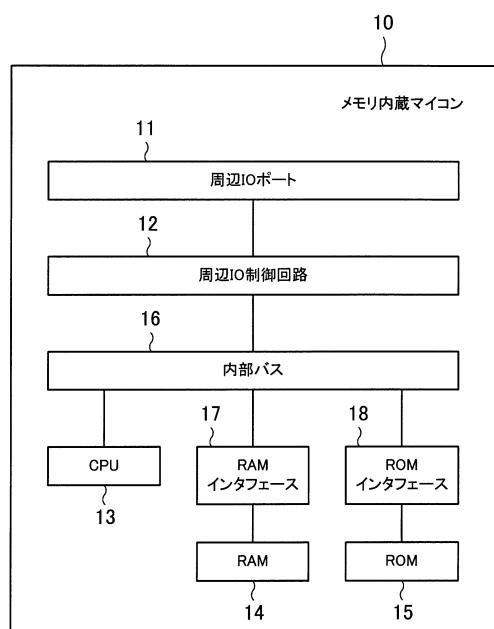

図1はメモリ内蔵マイコンの構成例を示す図である。

メモリ内蔵マイコン10は、周辺I/O (Input/Output) ポート11、周辺I/O制御回路12、CPU (Central Processing Unit) 13、RAM (Random Access Memory) 14及びROM (Read Only Memory) 15を含む。

## 【0010】

メモリ内蔵マイコン10は、CPU13によって制御される。CPU13には、内部バス16を介してRAMインターフェース17が接続され、RAMインターフェース17にRAM14が接続されている。また、CPU13には、内部バス16を介してROMインターフェース18が接続され、ROMインターフェース18にROM15が接続されている。内部バス16には、周辺I/Oポート11に接続された周辺I/O制御回路12が接続されている。

## 【0011】

フラッシュメモリは、このようなメモリ内蔵マイコン10のROM15として使用され得る。尚、フラッシュメモリは、このほか、単体のメモリチップとしても使用され得る。

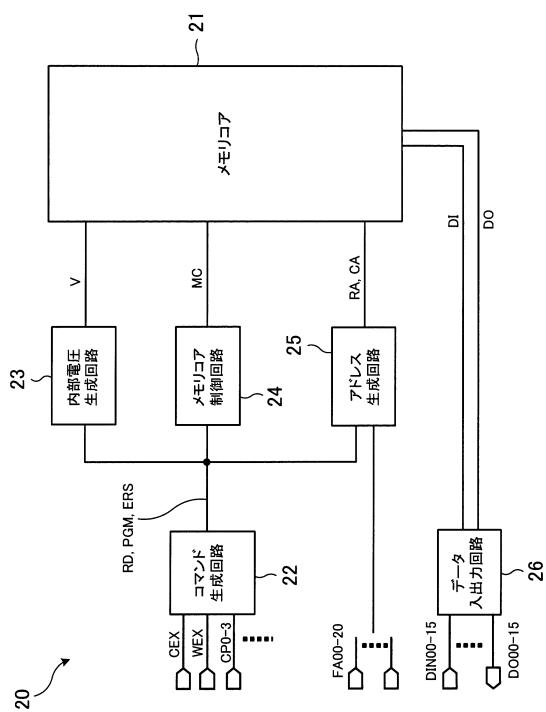

図2はフラッシュメモリの構成例を示す図である。

## 【0012】

フラッシュメモリ20は、メモリセル (メモリセルトランジスタ) を含むメモリコア21、及び周辺回路を含む。周辺回路は、コマンド生成回路22、内部電圧生成回路23、メモリコア制御回路24、アドレス生成回路25及びデータ入出力回路26を含む。

## 【0013】

コマンド生成回路22は、チップイネーブルピンC CXから入力される信号 (チップイネーブル信号) によって活性化され、メモリコア21を制御する各種コマンドを生成する。コマンド生成回路22は、コントロールピンCP0-3から入力される信号 (コントロール信号) と、ライトイネーブルピンWE Xから入力される信号 (ライトイネーブル信号)との組み合わせに基づき、コマンドを生成する。コマンド生成回路22は、コントロール信号及びライトイネーブル信号を用いて、読み出し (リード (READ))、書き込み (プログラム (PROGRAM))、消去 (イレース (ERASE)) の各動作モードを指示するモード信号RD、PGM、ERSを生成する。

## 【0014】

内部電圧生成回路23は、モード信号RD、PGM又はERSに基づき、それが示す動作モードでメモリコア21に必要となる内部電圧Vを生成する。例えば、メモリコア21内のメモリセルに接続されるワード線、ビット線、ソース線に印加する電圧、メモリセルのウェルに印加する電圧、ビット線及びグローバルビット線をプリチャージする際の電圧等を生成する。

## 【0015】

メモリコア制御回路24は、モード信号RD、PGM又はERSに基づき、メモリコア21を制御するメモリコア制御信号MCを生成する。

アドレス生成回路25は、アドレスピンFA00-20から入力されるアドレスに基づき、モード信号RD、PGM又はERSに応じて、ロウアドレスRA、カラムアドレスCAを生成する。ロウアドレスRAは、ワード線及びソース線の選択に用いられる。カラムアドレスCAは、ビット線及びグローバルビット線の選択に用いられる。

## 【0016】

データ入出力回路26は、入力データピンDIN00-15及び出力データピンD000-15を介して、フラッシュメモリ20外部とのデータのやり取りを行う。データ入出力回路26は、プログラム動作時には、入力データピンDIN00-15から入力される信号DIをメモリコア21に出力し、リード動作時には、メモリコア21から読み出される信号DOを出力データピンD000-15に出力する。

10

20

30

40

50

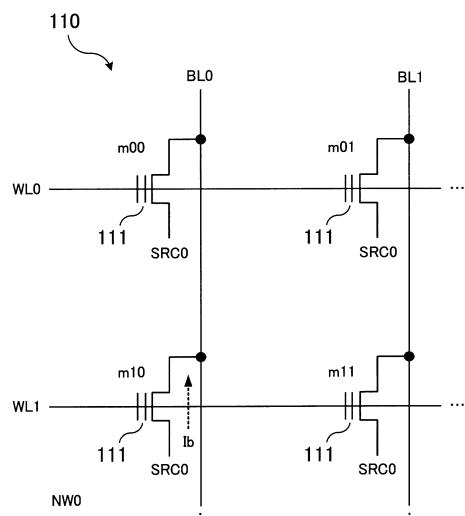

## 【0017】

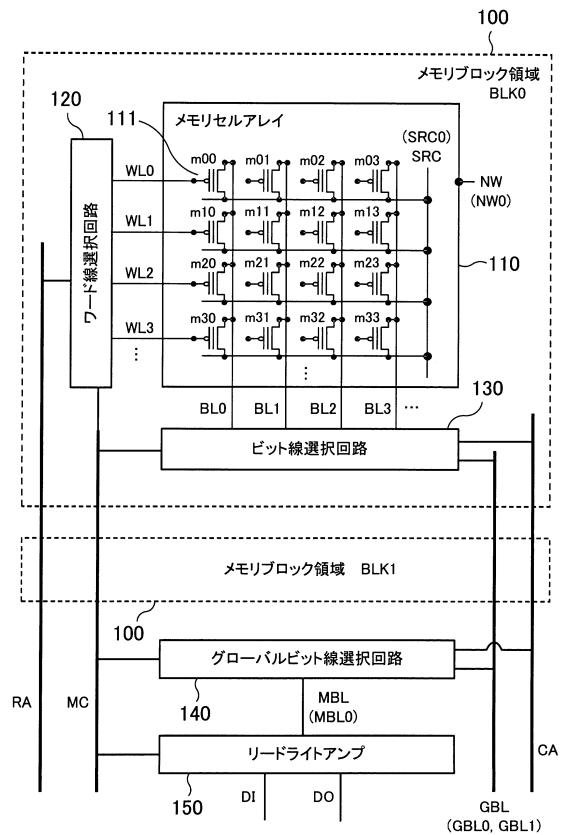

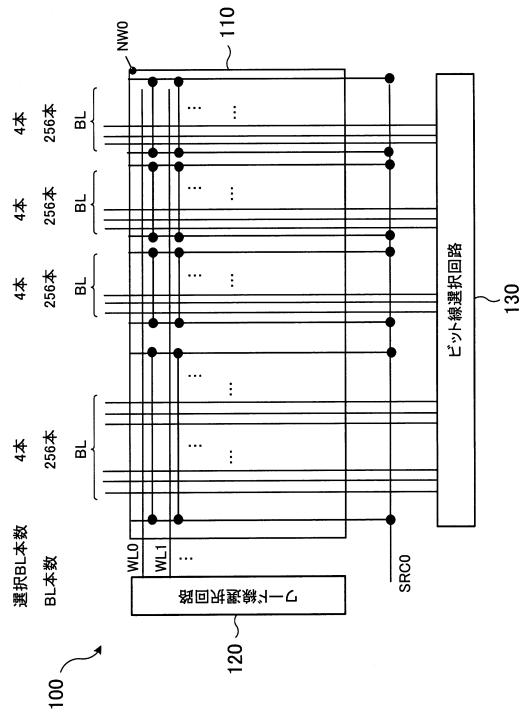

図3はメモリコアの構成例を示す図である。

メモリコア21は、メモリブロック領域100を含む。メモリブロック領域100は、メモリセルアレイ110、ワード線選択回路120及びビット線選択回路130を含む。尚、メモリコア21は、このようなメモリブロック領域100を複数（この例ではBLK0とBLK1の2つ）、含む場合がある。ここでは、BLK0を例に、メモリブロック領域100の構成について説明する。

## 【0018】

メモリブロック領域100に含まれるメモリセルアレイ110は、ワード線WL（この例ではWL0-3）とビット線BL（この例ではBL0-3）の交差位置にそれぞれ配置された複数のメモリセル111（この例ではm00-33）を含んでいる。メモリセルアレイ110内の全メモリセル111は、共通のソース線SRC（この例ではSRC0）に接続されている。

## 【0019】

メモリセル111は、例えば、Pチャネル型MOS（Metal Oxide Semiconductor）トランジスタ（PMOS）とされる。このようなPMOSのメモリセル111は、半導体基板上にゲート電極、P型ソース領域及びP型ドレイン領域を形成して得ることができる。メモリセルアレイ110内のメモリセル111は、半導体基板に設けた同一の又は互いに電気的に接続されたN型ウェルNW（この例ではNW0）に形成される。

## 【0020】

図3に示すワード線選択回路120は、メモリコア制御信号MC及びロウアドレスRAに基づき、ワード線を選択する。

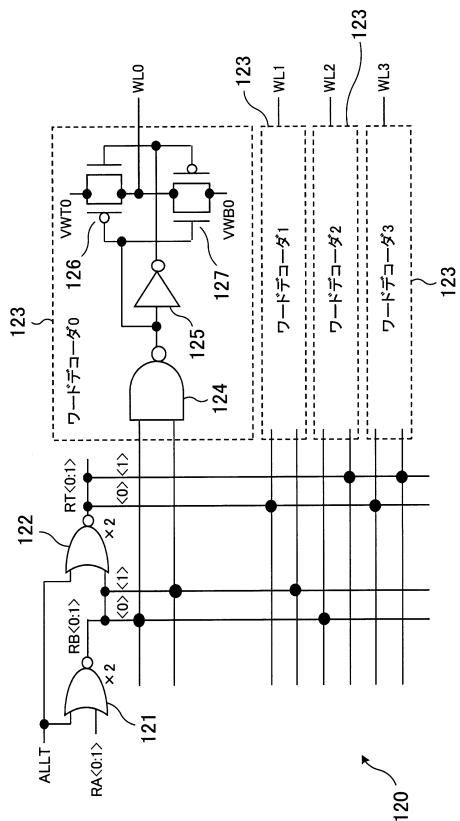

図4はワード線選択回路の一例を示す図である。

## 【0021】

この図4のワード線選択回路120では、ロウアドレスRA<0:1>及び信号ALLTに従って、ワード線WL0-3のいずれかが選択される。ワード線選択回路120は、NORゲート121、NORゲート122、及び各ワード線WL0-3に対応したワードデコーダ123（ワードデコーダ0-3）を含む。各ワードデコーダ123は、NANDゲート124、NOTゲート125、CMOSトランスファゲート126及びCMOSトランスファゲート127を含んでいる。

## 【0022】

NORゲート121は、信号ALLT及びロウアドレスRA<0:1>を入力とし、信号RB<0:1>を出力する。NORゲート122は、信号ALLT及び信号RB<0:1>を入力とし、信号RT<0:1>を出力する。ワード線WL0に対応するワードデコーダ123のNANDゲート124には、信号RB<0>及び信号RB<1>が入力される。同様に、ワード線WL1に対応するワードデコーダ123のNANDゲートには、信号RT<0>及び信号RB<1>が入力される。ワード線WL2に対応するワードデコーダ123のNANDゲートには、信号RT<0>及び信号RB<1>が入力される。ワード線WL3に対応するワードデコーダ123のNANDゲートには、信号RT<0>及び信号RB<1>が入力される。ワードデコーダ123のNANDゲート124の出力信号、及びその出力信号のNOTゲート125による反転信号は、CMOSトランスファゲート126、CMOSトランスファゲート127に入力される。

## 【0023】

ワード線選択の際、NORゲート121の入力信号ALLTはLow（L）レベルとされる。例えば、ワード線WL0が選択される場合、ロウアドレスRA<0>、RA<1>はLレベルで、ワードデコーダ123のNANDゲート124の2入力はHigh（H）レベルとなり、その出力はLレベルとなる。その結果、ワード線WL0は、電圧VWT0と接続される。選択されないワード線WL1-3に対応するワードデコーダ123のNANDゲート124の2入力は、一方がLレベルで他方がHレベル、又はいずれもLレベルとなり、その結果、電圧VWB0に接続される。尚、イレース動作時には、信号ALLT

10

20

30

40

50

がHレベルとなり、全てのワード線W L 0 - 3が電圧V W B 0に接続される。

【0024】

電圧V W T 0と電圧V W B 0の値は、動作モードに従って設定される。例えば、プログラム動作モードでは、電圧V W T 0が9V、電圧V W B 0が0Vに設定される。リード動作モードでは、電圧V W T 0が-3V、電圧V W B 0が1.8Vに設定される。イレース動作モードでは、電圧V W T 0が0V、電圧V W B 0が-9Vに設定される。電圧V W T 0及び電圧V W B 0は、入力信号と論理素子出力の振幅の中にV W T 0及びV W B 0が含まれるように設定される。

【0025】

続いて、図3に示すビット線選択回路130及びグローバルビット線選択回路140について述べる。ビット線選択回路130は、メモリコア制御信号M C及びカラムアドレスC Aに基づき、ビット線B L 0 - 3を選択する。ビット線選択回路130は、選択されたビット線を、メモリコア制御信号M C及びカラムアドレスC Aに基づきグローバルビット線選択回路140により選択される所定電圧のグローバルビット線G B L (G B L 0, G B L 1)と接続する。

【0026】

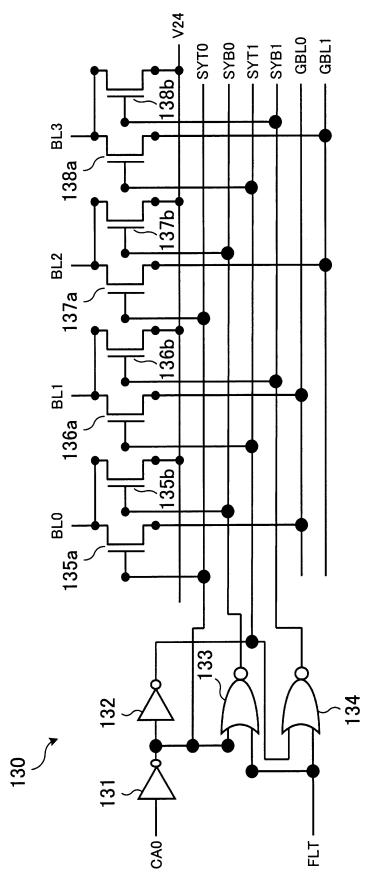

図5はビット線選択回路の一例を示す図、図6はグローバルビット線選択回路の一例を示す図である。

図5に示すビット線選択回路130は、NOTゲート131、NOTゲート132、N ORゲート133及びN ORゲート134を含む。NOTゲート131は、カラムアドレスC A 0を入力とし、その反転信号がNOTゲート132及びN ORゲート133に入力されると共に、選択信号S Y T 0とされる。N ORゲート133には、更に信号F L Tが入力され、その出力は選択信号S Y B 0とされる。NOTゲート132の出力は、N ORゲート134に入力されると共に、選択信号S Y T 1とされる。N ORゲート134には、更に信号F L Tが入力され、その出力が選択信号S Y B 1とされる。

【0027】

ビット線B L 0は、Nチャネル型MOSトランジスタ(NMOS)135aを介してグローバルビット線G B L 0に接続され、NMOS135bを介して電源線V 2 4(電圧2.4V)に接続されている。NMOS135aのゲートには選択信号S Y T 0が入力され、NMOS135bのゲートには選択信号S Y B 0が入力される。ビット線B L 1は、NMOS136aを介してグローバルビット線G B L 0に接続され、NMOS136bを介して電源線V 2 4に接続されている。NMOS136aのゲートには選択信号S Y T 1が入力され、NMOS136bのゲートには選択信号S Y B 1が入力される。ビット線B L 2は、NMOS137aを介してグローバルビット線G B L 1に接続され、NMOS137bを介して電源線V 2 4に接続されている。NMOS137aのゲートには選択信号S Y T 0が入力され、NMOS137bのゲートには選択信号S Y B 0が入力される。ビット線B L 3は、NMOS138aを介してグローバルビット線G B L 1に接続され、NMOS138bを介して電源線V 2 4に接続されている。NMOS138aのゲートには選択信号S Y T 1が入力され、NMOS138bのゲートには選択信号S Y B 1が入力される。

【0028】

この図5に例示するビット線選択回路130は、ビット線B L 0とビット線B L 1のいずれかをグローバルビット線G B L 0に接続し、ビット線B L 2とビット線B L 3のいずれかをグローバルビット線G B L 1に接続する。信号F L TがLレベルの時、非選択ビット線(グローバルビット線と接続されないビット線)は、電源線V 2 4に接続される。プログラム動作モードでは、非選択ビット線の電圧をこのような電源線V 2 4の電圧に設定する。一方、信号F L TがHレベルの時、非選択ビット線は電源線V 2 4とは接続されず、ハイインピーダンス(H i Z)状態になる。リード動作モード、イレース動作モードでは、非選択ビット線をこのようなH i Z状態に設定する。

【0029】

10

20

30

40

50

また、図6に示すグローバルビット線選択回路140は、上記ビット線選択回路130と同様に、NOTゲート141、NOTゲート142、NORゲート143及びNORゲート144を含む。NOTゲート141は、カラムアドレスCA1を入力とし、その反転信号がNOTゲート142及びNORゲート143に入力されると共に、選択信号SGT0とされる。NORゲート143には、更に信号FLTが入力され、その出力は選択信号SGB0とされる。NOTゲート142の出力は、NORゲート144に入力されると共に、選択信号SGT1とされる。NORゲート144には、更に信号FLTが入力され、その出力が選択信号SGB1とされる。

#### 【0030】

グローバルビット線GBL0は、NMOS145aを介してメインビット線MBL0に接続され、NMOS145bを介して電源線V24に接続されている。NMOS145aのゲートには選択信号SGT0が入力され、NMOS145bのゲートには選択信号SGB0が入力される。グローバルビット線GBL1は、NMOS146aを介してメインビット線MBL0に接続され、NMOS146bを介して電源線V24に接続されている。NMOS146aのゲートには選択信号SGT1が入力され、NMOS146bのゲートには選択信号SGB1が入力される。

#### 【0031】

この図6に例示するグローバルビット線選択回路140は、グローバルビット線GBL0とグローバルビット線GBL1のいずれかをメインビット線MBL0に接続する。

続いて、図3に示すリードライトアンプ150について述べる。リードライトアンプ150は、リードアンプ及びライトアンプを含み、このリードライトアンプ150に、グローバルビット線選択回路140がメインビット線MBLを介して接続されている。リードアンプは、グローバルビット線GBLを介して接続されたメモリセル111に流れる電流に従って、そのメモリセル111のデータを読み出し、それを基に信号DOを出力する。ライトアンプは、入力される信号DIに基づき、グローバルビット線GBLに所定電圧を印加する。

#### 【0032】

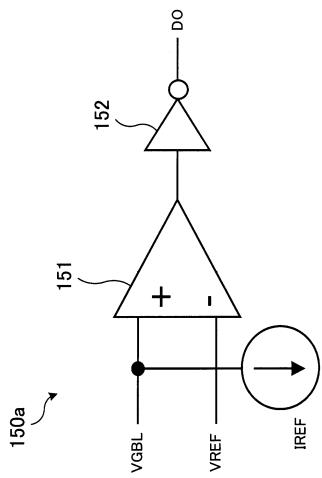

図7はリードアンプの一例を示す図、図8はライトアンプの一例を示す図である。

図7に示すリードアンプ150aは、グローバルビット線GBLの電圧VGBLとリファレンス電圧VREFを入力とするコンパレータ151、及びコンパレータ151の出力の反転信号を信号DOとして出力するNOTゲート152を含む。

#### 【0033】

リードアンプ150aは、リード動作モードで活性化する。リード対象として選択されたメモリセル111が閾値電圧Vthの高いプログラム状態にあると、メモリセル111に電流が流れ、グローバルビット線GBLに電荷が供給される。この時のグローバルビット線GBLの電圧VGBLはHレベルとされ、リードアンプ150aからはLレベルの信号DOが outputされる。一方、リード対象として選択されたメモリセル111が閾値電圧Vthの低いイレース状態にあると、メモリセル111に電流が流れず、グローバルビット線GBLの電圧VGBLはLレベルとされ、リードアンプ150aからはHレベルの信号DOが outputされる。

#### 【0034】

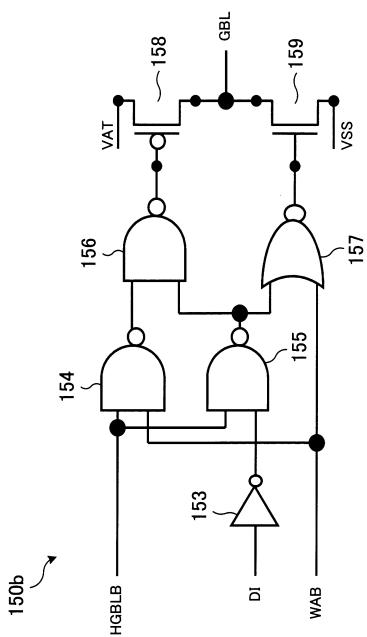

図8に示すライトアンプ150bは、NOTゲート153、NANDゲート154、NANDゲート155、NANDゲート156、NORゲート157、PMOS158及びNMOS159を含む。

#### 【0035】

NOTゲート153には、信号DIが入力される。NANDゲート154には、信号HGBLBと信号WABが入力される。NANDゲート155には、信号HGBLBと、NOTゲート153の出力即ち信号DIの反転信号が入力される。NANDゲート154の出力及びNANDゲート155の出力は、NANDゲート156に入力され、その出力は、PMOS158のゲートに入力される。NANDゲート155の出力及び信号WABは

10

20

30

40

50

、N O R ゲート 1 5 7 に入力され、その出力は、N M O S 1 5 9 のゲートに入力される。

【0036】

信号H G B L B がL レベルの時、N A N D ゲート 1 5 6 の出力はL レベルとなり、グローバルビット線G B L は電圧V A T ( 電源線V 2 4 ( 2 . 4 V ) ) に接続される。リード動作モードにおけるリード前 ( センス前 ) のグローバルビット線G B L のプリチャージでは、このような状態とされる。信号H G B L B がH レベルで信号W A B がH レベルの時、グローバルビット線G B L はH i Z 状態になる。リード動作モードにおけるリード時 ( センス時 ) には、このような状態とされる。プログラム動作モード時には、信号W A B がL レベルになり、グローバルビット線G B L は信号D I と同じ極性になる。信号D I がL レベルの時は、グローバルビット線G B L は電圧V S S ( 接地線 ) に接続され、信号D I がH レベルの時は、グローバルビット線G B L は電圧V A T に接続される。 10

【0037】

続いて、上記図3～図8に示したようなメモリコア21を含むフラッシュメモリ20のリード、イレース、プログラムの各動作について述べる。

まず、リード動作について説明する。ここでは、図3に示したメモリブロック領域B L K 0 のメモリセルアレイ110に含まれるメモリセル111のうち、m 0 0 のメモリセル111に対してリード動作を行う場合を例にして説明する。

【0038】

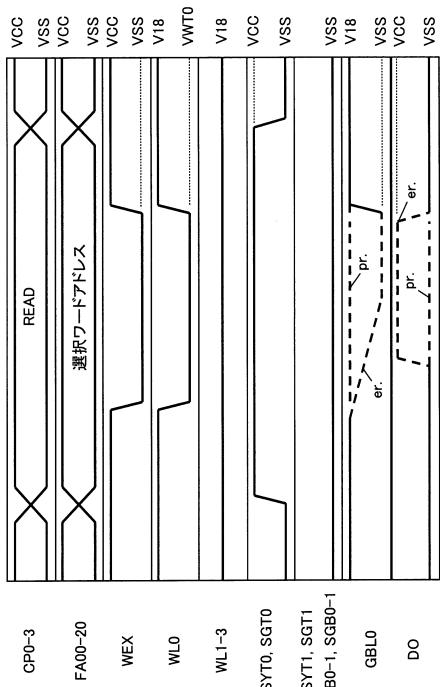

図9はリード動作波形の一例を示す図である。

リード動作では、コントロールピンC P 0 - 3 にリードコマンドを設定してリード動作モードにエントリし、同時にアドレスピンF A 0 0 - 2 0 にロウとカラムを指定する選択ワードアドレスを設定する。ライトイネーブルピンW E X に入力されるライトイネーブル信号を下げる時、ロウアドレスR A に従ってワード線、ここではワード線W L 0 が選択され、電圧V 1 8 ( 1 . 8 V ) から負電位の電圧V W T 0 ( 例えは - 3 V ) になる。非選択のワード線W L 1 - 3 は、電圧V 1 8 に保持される。尚、ソース線S R C 0 は、非選択のワード線W L 1 - 3 と同じ電圧V 1 8 とされている。 20

【0039】

リード動作モードにエントリし、アドレスを設定すると、カラムアドレスC A に従って、ビット線選択回路130の選択信号S Y T 0 、及びグローバルビット線選択回路140の選択信号S G T 0 がL レベル ( V S S ) からH レベル ( V C C ) になる。それ以外の選択信号S Y T 1 , S G T 1 , S Y B 0 - 1 , S G B 0 - 1 は、いずれもL レベル ( V S S ) を保持する。これにより、選択されたメモリセル111 ( m 0 0 ) に繋がるビット線B L 0 がグローバルビット線G B L 0 に接続され、グローバルビット線G B L 0 がメインビット線M B L 0 を介してリードアンプ150aに接続される。 30

【0040】

グローバルビット線G B L 0 は、ライトイネーブルピンW E X に入力されるライトイネーブル信号がH レベルの時、ソース線S R C 0 と同じ電圧V 1 8 に設定される。ワード線W L 0 が電圧V 1 8 から電圧V W T 0 に下がると、メモリセル111の状態によって、グローバルビット線G B L 0 の電圧が変化する。即ち、メモリセル111が閾値電圧V t h の高いプログラム状態 ( p r . ) にある場合、メモリセル111に電流が流れ、グローバルビット線G B L 0 はH レベル ( V 1 8 ) になる。メモリセル111が閾値電圧V t h の低いイレース状態 ( e r . ) にある場合、メモリセル111には電流が流れず、グローバルビット線G B L 0 は、リードライトアンプ150のリードアンプ150aの電流源によって引き抜かれ、L レベル ( V S S ) になる。 40

【0041】

このようなグローバルビット線G B L 0 の状態を受けて、信号D O が変化する。即ち、メモリセル111がプログラム状態 ( p r . ) にあり、グローバルビット線G B L 0 がH レベルの場合、信号D O はL レベル ( V S S ) になる。メモリセル111がイレース状態 ( e r . ) にあり、グローバルビット線G B L 0 がL レベルの場合、信号D O はH レベル ( V C C ) になる。 50

## 【0042】

次に、イレース動作について説明する。ここでは、図3に示したメモリブロック領域B L K 0のメモリセルアレイ110に含まれるメモリセル111に対してイレース動作を行う場合を例にして説明する。

## 【0043】

図10はイレース動作波形の一例を示す図である。

イレース動作では、コントロールピンC P 0 - 3にイレースコマンドを設定してイレース動作モードにエントリし、同時にアドレスピンF A 0 0 - 2 0にメモリブロック領域100を指定するメモリブロックアドレスを設定する。選択されたメモリブロック領域100のワード線W L 0 - 3は、一旦電圧V S Sに設定され、ライトイネーブルピンW E Xに10

入力されるライトイネーブル信号を下げるとき、負電位の電圧V W B 0（例えば-9V）になる。

## 【0044】

ビット線選択回路130及びグローバルビット線選択回路140の全ての選択信号S Y T 0 - 1, S G T 0 - 1, S Y B 0 - 1, S G B 0 - 1は、Lレベル(V S S)を保持する。これにより、選択されたメモリブロック領域100のビット線B L 0 - 3を、グローバルビット線G B L及び電源線V 2 4から切り離す。

## 【0045】

選択されたメモリブロック領域100のワード線W L 0 - 3が電圧V W B 0に下がると、そのメモリブロック領域100のN型ウェルN W 0及びソース線S R C 0が、9V程度の高い電圧V N W 0に設定される。これにより、そのメモリブロック領域100の全メモリセル111のデータが一括で消去される。

## 【0046】

次に、プログラム動作について説明する。ここでは、図3に示したメモリブロック領域B L K 0のメモリセルアレイ110に含まれるメモリセル111のうち、m 0 0のメモリセル111に対してプログラム動作を行う場合を例にして説明する。

## 【0047】

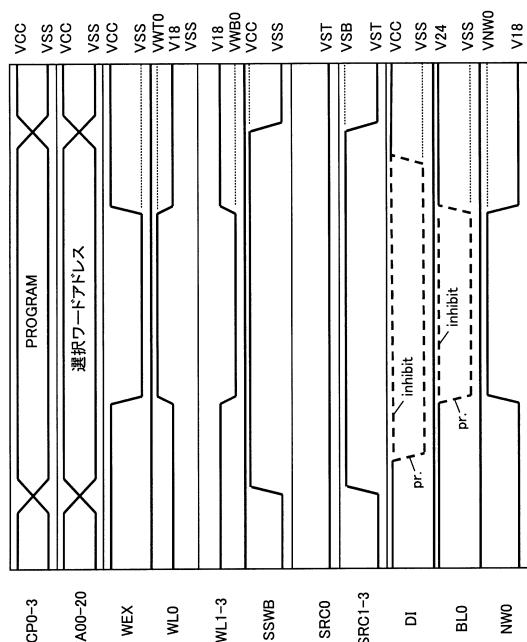

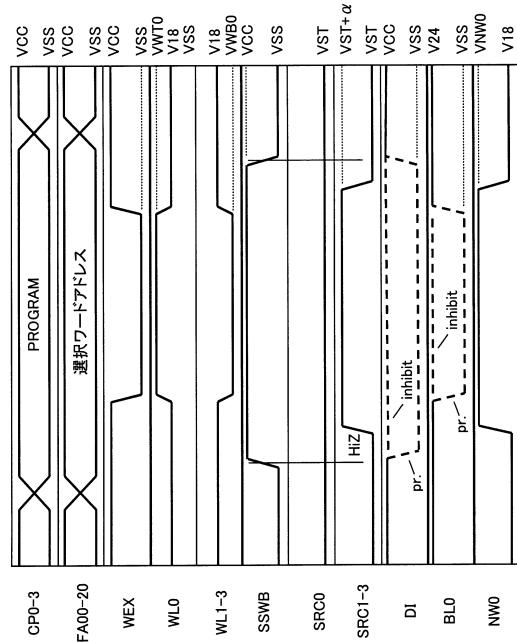

図11はプログラム動作波形の一例を示す図である。

プログラム動作では、コントロールピンC P 0 - 3にプログラムコマンドを設定してプログラム動作モードにエントリし、同時にアドレスピンF A 0 0 - 2 0にロウとカラムを指定する選択ワードアドレスを設定する。ライトイネーブルピンW E Xに入力されるライトイネーブル信号を下げるとき、ロウアドレスR Aに従ってワード線、ここではワード線W L 0が選択され、電圧V 1 8 (1.8V)から正電位の電圧V W T 0（例えば9V）になる。非選択のワード線W L 1 - 3は、電圧V W B 0（例えば0V）になる。

## 【0048】

プログラム動作モードにエントリし、アドレスを設定すると、カラムアドレスC Aに従って、ビット線選択回路130の選択信号S Y T 0, S Y B 1、及びグローバルビット線選択回路140の選択信号S G T 0, S G B 1がLレベル(V S S)からHレベル(V C C)になる。それ以外の選択信号S Y T 1, S G T 1, S Y B 0, S G B 0は、いずれもLレベル(V S S)を保持する。これにより、選択されたメモリセル111(m 0 0)に繋がるビット線B L 0がグローバルビット線G B L 0に接続され、グローバルビット線G B L 0がメインビット線M B L 0を介してライトアンプ150bに接続される。

## 【0049】

入力された信号D Iに従って、ライトイネーブルピンW E Xに入力されるライトイネーブル信号が下がると、ライトアンプ150bがグローバルビット線G B L 0の電圧を設定する。プログラムするメモリセル111の場合(p r .)、Lレベル(V S S)の信号D Iが入力され、ビット線B L 0が電圧V S S (0V)になる。プログラムするメモリセル111でない場合(i n h i b i t)、Hレベル(V C C)の信号D Iが入力され、ビット線B L 0が電圧V A T (インヒビット電圧V 2 4 (2.4V))になる(非選択のメモリセル111に繋がるビット線B Lが電圧V A Tになる)。

10

20

30

40

50

## 【0050】

プログラム動作モードでライトイネーブルピンW E Xに入力されるライトイネーブル信号がLレベルになると、N型ウェルNW0は、5V程度の電圧VNW0に設定される。プログラム動作モードでは、ソース線SRC0は1.8Vに設定される。

## 【0051】

上記のようなリード、イレース、プログラムの各動作時のワード線WL(WL0-3)、ビット線BL(BL0-3)、ソース線SRC(SRC0)及びN型ウェルNW(NW0)の電圧の設定例を図12にまとめて示す。

## 【0052】

ここで、上記のようなプログラム動作時にメモリセルアレイ110内のメモリセル111が受けるディスターブについて説明する。

図13はディスターブの説明図である。

## 【0053】

例えば、図3及び図13に示すメモリセルアレイ110内のm00のメモリセル111にプログラムする場合、そのメモリセル111のゲートに繋がるワード線WL0が選択され、ワード線WL0が高い電圧、例えば9Vに設定される。m00のメモリセル111に繋がるソース線SRC0は、例えば1.8Vに設定され、ドレインに繋がるビット線(選択ビット線)BL0は、例えば0Vに設定される。他のビット線(非選択ビット線)BL1-3は、例えば2.4Vに設定される。

## 【0054】

この時、メモリセルアレイ110内のメモリセル111のうち、ゲートがワード線WL0につながり、ドレインが非選択ビット線BL1-3に繋がる非選択のメモリセル111は、ゲートディスターブを受ける。即ち、プログラムしないm01, m02, m03(図13にはm01のみ図示)のメモリセル111において、ゲートディスターブを受け、その閾値電圧Vthが変化する可能性が生じる。また、これらの非選択のメモリセル111に接続されるソース線SRC0、ビット線BL1-3の電圧が低いと、閾値電圧Vthが変化し易くなる。

## 【0055】

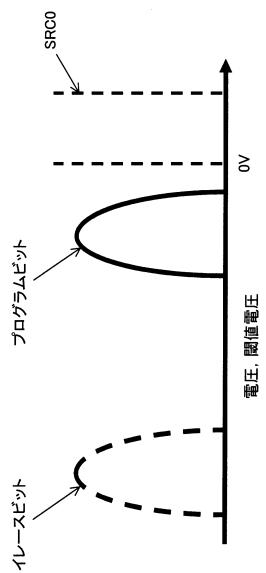

図14はゲートディスターブを受ける時間と閾値電圧の関係の説明図である。図14には、プログラム動作時に、プログラムされていないイレース状態のメモリセル111(イレースビット)の閾値電圧Vthが、ゲートディスターブを受ける時間によってどのように変化するかを示している。横軸はイレースビットがゲートディスターブを受ける時間、縦軸はイレースビットの閾値電圧Vth分布の最大値を示している。また、図15は閾値電圧分布の説明図である。

## 【0056】

図14の実線に示すように、ゲートディスターブを受ける時間が長くなると、イレースビットの閾値電圧Vthが上昇し始める。イレースビットは、その閾値電圧Vthが上昇し、図15に示すようなプログラム状態のメモリセル111(プログラムビット)の閾値電圧Vthに近くなると、リード動作時にプログラムビットと判定される虞がある。

## 【0057】

ソース線SRC0の電圧を高くすると、図14の点線に示すように、閾値電圧Vthが上昇し始めるまでの時間が長くなる。つまりゲートディスターブ耐性が改善する。しかし、このようにソース線SRC0の電圧を高くすると、ソース線SRC0はメモリセルアレイ110内の全メモリセル111に接続されているため、選択ビット線BL0に接続されたメモリセル111のソース・ゲート間電圧Vsgが大きくなる。そのため、m10, m20, m30(図13にはm10のみ図示)のメモリセル111において、ソース線SRC0から選択ビット線BL0へのリーク電流Ibが増える、或いは発生する。これらm10, m20, m30のメモリセル111が、閾値電圧Vthの高いプログラム状態になっている場合には、リーク電流Ibの量が大きくなる。

## 【0058】

10

20

30

40

50

以上のような点に鑑み、フラッシュメモリ20のメモリコア21に、以下に実施の形態として示すような構成を採用する。

まず、第1の実施の形態について説明する。

#### 【0059】

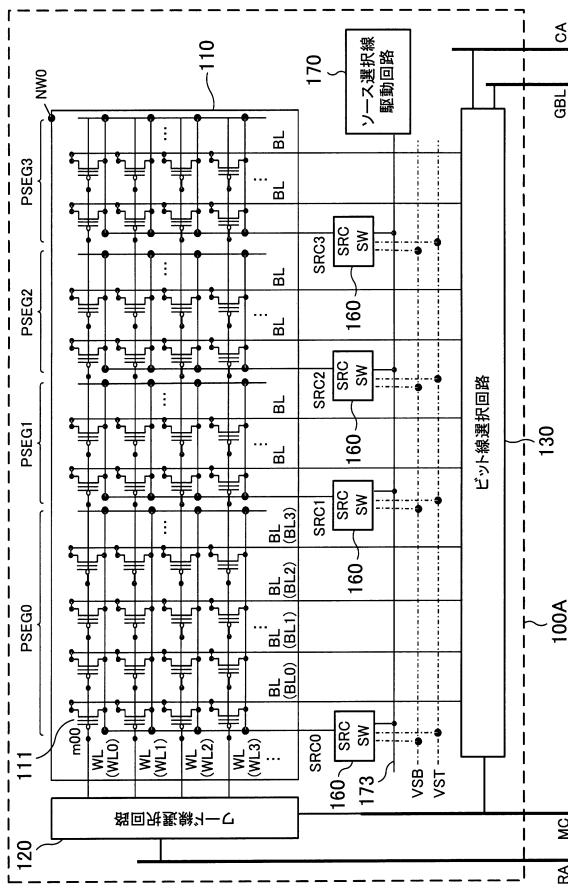

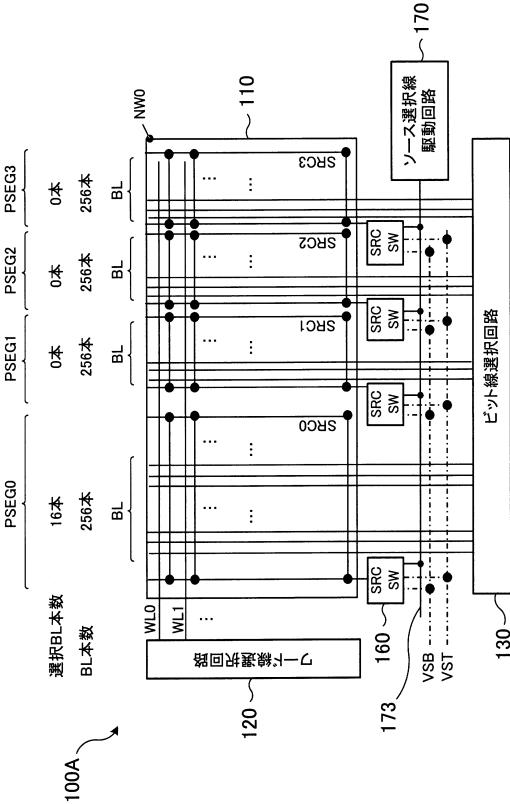

図16は第1の実施の形態に係るメモリblock領域の構成例を示す図である。

図16に示すメモリblock領域100Aは、上記のメモリblock領域100と同様に、ワード線選択回路120及びビット線選択回路130を有する。図16に示すメモリblock領域100Aでは、メモリセルアレイ110が、所定本数（例えば256本）のビット線BLに接続されるメモリセル111群毎に、複数のblockに分割される。このように分割された各blockをメモリblock又はプログラムセグメントPSSEGと呼ぶ。図16には一例として、4つのプログラムセグメントPSSEG0-3を図示している。

#### 【0060】

プログラムセグメントPSSEG0を例に、プログラムセグメントPSSEGの構成について説明する。ワード線WL（この例ではWL0-3）とビット線BL（この例ではBL0-3）の交差位置にそれぞれ、N型ウェルNW（この例ではNW0）に形成されたPMOSが、メモリセル111として配置されている。このようなPMOSのメモリセル111のゲートがワード線WLに接続され、ドレンがビット線BLに接続されている。このプログラムセグメントPSSEG0に含まれるPMOSのメモリセル111のソースは、共通のソース線SRC0に接続されている。

#### 【0061】

他のプログラムセグメントPSSEG1-3も、このプログラムセグメントPSSEG0と同様の構成を有し、プログラムセグメントPSSEG1-3に含まれるメモリセル111は、それぞれ共通のソース線SRC1-3に接続されている。プログラムセグメントPSSEG0-3のソース線SRC0-3は、互いに分離されており、互いに直接接続されない。ソース線SRC0-3は、それぞれソース線スイッチ（SRC SW）160によって、電圧VST（例えば1.8V）又は電圧VSB（例えば2.4V）に設定される。各ソース線スイッチ160は、ソース選択線173を介してソース選択線駆動回路170に接続されている。また、ワード線WLは、プログラムセグメントPSSEG0-3の間で共有されている。

#### 【0062】

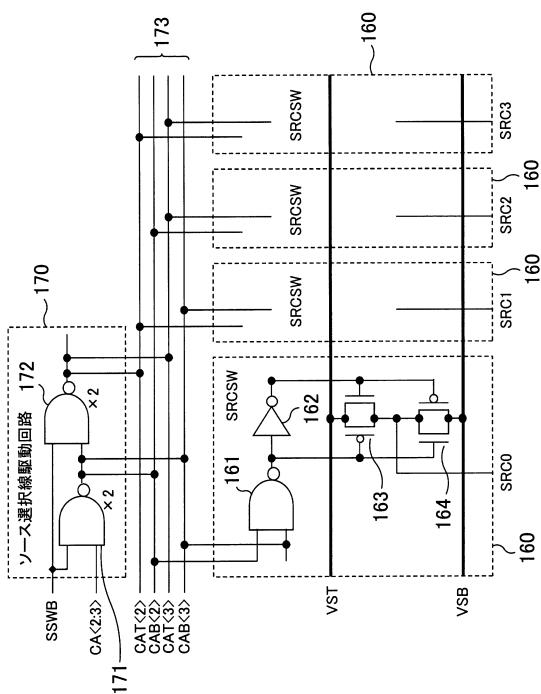

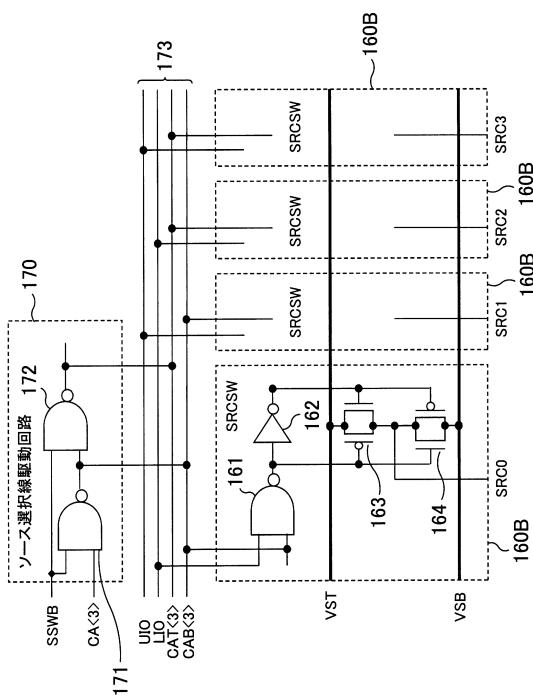

図17は第1の実施の形態に係るソース線スイッチ及びソース選択線駆動回路の一例を示す図である。

ここでは、ソース線スイッチSRC SWの構成を、プログラムセグメントPSSEG0のソース線SRC0に接続されるソース線スイッチ160を例にして説明する。図17では、プログラムセグメントPSSEG1-3のソース線SRC1-3に接続されたソース線スイッチ160の内部構成の図示を省略している。

#### 【0063】

ソース線スイッチ160は、NANDゲート161、NOTゲート162、CMOSトランスマニアゲート163及びCMOSトランスマニアゲート164を含む。ソース選択線駆動回路170は、NANDゲート171及びNANDゲート172を含む。

#### 【0064】

プログラム動作時、ソース選択線駆動回路170のNANDゲート171には、信号SSWB、及びプログラムセグメントPSSEGを指定するカラムアドレスCA<2:3>が入力される。NANDゲート172には、信号SSWB、及びNANDゲート171から出力される信号CAB<2:3>が入力され、信号CAT<2:3>が出力される。ソース線SRC0に接続されたソース線スイッチ160のNANDゲート161には、ソース選択線駆動回路170から出力される信号CAB<2>及び信号CAB<3>が入力される。NANDゲート161の出力信号、及びその出力信号のNOTゲート162による反転信号は、CMOSトランスマニアゲート163、CMOSトランスマニアゲート164に入力される。

10

20

30

40

50

## 【0065】

尚、ソース線SRC1に接続されたソース線スイッチ160には、ソース選択線駆動回路170から出力される信号CAT<2>及び信号CAB<3>が入力される。ソース線SRC2に接続されたソース線スイッチ160には、ソース選択線駆動回路170から出力される信号CAB<2>及び信号CAT<3>が入力される。ソース線SRC3に接続されたソース線スイッチ160には、ソース選択線駆動回路170から出力される信号CAT<2>及び信号CAT<3>が入力される。これらのソース線スイッチ160においても、上記ソース線SRC0に接続されたソース線スイッチ160と同様の流れで信号の処理が行われる。

## 【0066】

10

例えば、プログラム動作において、プログラムセグメントPSEG0-3のうち、プログラムセグメントPSEG0を選択する場合、そのプログラムセグメントPSEG0に設けられたソース線SRC0が選択され、そのソース線SRC0が電圧VSTに設定される。非選択のプログラムセグメントPSEG1-3のソース線SRC1-3は、電圧VSBに設定される。電圧VSBは、電圧VSTよりも高く設定され、例えば、電圧VSTは1.8V、電圧VSBは電圧2.4Vに設定される。

## 【0067】

メモリブロック領域100Aにおいて、プログラムするメモリセル111は、プログラムセグメントPSEG0-3のうち、いずれか1つから選択される。

図18は第1の実施の形態に係るプログラム動作波形の一例を示す図である。

20

## 【0068】

ここでは、図16に示したメモリブロック領域100AのプログラムセグメントPSEG0に含まれるメモリセル111のうち、ワード線WL0とビット線BL0に接続されたメモリセル111(m00)に対してプログラム動作を行う場合を例にして説明する。

## 【0069】

メモリブロック領域100Aにおいて、ソース線SRC0-3の選択動作以外の動作は、上記図11に示した動作と同じである。

プログラム動作モードにエントリし、アドレスを設定すると、信号SSWBがHレベルとなり、カラムアドレスCAに従って、選択されるプログラムセグメントPSEG0のソース線SRC0が電圧VST(ここでV18(1.8V))に設定される。非選択のプログラムセグメントPSEG1-3のソース線SRC1-3は電圧VSB(ここでV24(2.4V))に設定される。

30

## 【0070】

このようにメモリブロック領域100Aでは、選択プログラムセグメントPSEG0のソース線SRC0が電圧VSTに設定され、非選択プログラムセグメントPSEG1-3のソース線SRC1-3がより高い電圧VSBに設定される。そのため、非選択プログラムセグメントPSEG1-3の、選択ワード線WL0に繋がるメモリセル111のソース電圧は、選択プログラムセグメントPSEG0のメモリセル111のソース電圧よりも高くなる。その結果、非選択プログラムセグメントPSEG1-3の、選択ワード線WL0に繋がるメモリセル111は、ゲートディスターブによる閾値電圧Vthの変動が起こり難くなる。

40

## 【0071】

更に、メモリブロック領域100Aでは、非選択プログラムセグメントPSEG1-3からは、プログラムするメモリセル111を選択しない(選択ビット線BLが存在しない)ようとする。これにより、非選択プログラムセグメントPSEG1-3において、ソース線SRC1-3からビット線BLへのリーコ電流の増加或いは発生を抑制することができるようになる。

## 【0072】

一方、メモリブロック領域100Aでは、選択プログラムセグメントPSEG0の、選択ワード線WL0に繋がるメモリセル111は、電圧VSTのソース線SRC0に接続さ

50

れ、非選択プログラムセグメント PSEG1 - 3 のメモリセル 111 よりも、ソース電圧が低い状態にある。そのため、選択プログラムセグメント PSEG0 の、選択ワード線 WL0 に繋がるメモリセル 111 は、ゲートディスターブの影響を受け得る。しかし、たとえ影響を受けるとしても、ゲートディスターブを受ける時間は、メモリセルアレイ 110 の全メモリセル 111 を共通のソース線に接続したもの（上記メモリブロック領域 100）に比べ、4 分の 1 になる。その結果、ゲートディスターブによる閾値電圧 Vth の変動を抑制することができる。

#### 【0073】

メモリブロック領域 100A では、このように選択プログラムセグメント PSEG0 のソース線 SRC0 を電圧 VST とし、選択プログラムセグメント PSEG0 のメモリセル 111 のソース電圧を低い状態にしている。そのため、ソース線 SRC0 から選択ビット線 BL0 へのリリーク電流の増加或いは発生を抑制することができる。

10

#### 【0074】

このようにメモリブロック領域 100A では、ソース線 SRC0 から選択ビット線 BL0 へリリーク電流が増えるのを抑えつつ、選択ワード線 WL0 に繋がるメモリセル 111 のゲートディスターブによる閾値電圧 Vth の変動抑制が可能になる。

#### 【0075】

メモリブロック領域 100A では、上記のように、プログラムするメモリセル 111 が、プログラムセグメント PSEG0 - 3 のうち、いずれか 1 つから選択される。

ここで、図 19 はプログラムセグメントに分割しないメモリブロック領域におけるビット線選択の説明図、図 20 は第 1 の実施の形態に係るメモリブロック領域におけるビット線選択の説明図である。

20

#### 【0076】

図 19 には便宜上、プログラムセグメント PSEG0 - 3 に分割しない上記メモリブロック領域 100（図 3）を、メモリセル 111 の図示を省略し、簡略化して図示している。ここでは、1024 本のビット線 BL に繋がるメモリブロック領域 100 を例示している。このようなメモリブロック領域 100 においては、複数本のビット線 BL が選択される（複数のメモリセル 111 にプログラムされる）場合がある。例えば、16 本のビット線 BL が選択される場合、256 本のビット線 BL あたり 4 本のビット線 BL が選択される。

30

#### 【0077】

図 20 には便宜上、256 本のビット線 BL 毎に 4 つのプログラムセグメント PSEG0 - 3 に分割した上記メモリブロック領域 100A を、メモリセル 111 の図示を省略し、簡略化して図示している。このようなメモリブロック領域 100A において、プログラム動作時に、複数本のビット線 BL を選択する（複数のメモリセル 111 にプログラムする）場合には、それら複数本のビット線 BL を、1 つのプログラムセグメント PSEG から選択する。この図 20 には、16 本のビット線 BL が、プログラムセグメント PSEG0 のみから選択される場合を例示している。

#### 【0078】

このようにすることで、残りのプログラムセグメント PSEG1 - 3 を非選択とし、ソース線 SRC1 - 3 の電圧を、選択プログラムセグメント PSEG0 のソース線 SRC0 の電圧よりも高くすることができる。これにより、上記のようにソース線 SRC0 から選択ビット線 BL0 へリリーク電流が増えるのを抑えつつ、選択ワード線 WL0 に繋がるメモリセル 111 のゲートディスターブによる閾値電圧 Vth の変動抑制を実現することができる。

40

#### 【0079】

以上述べたメモリブロック領域 100A において、リード動作時、イレース動作時には、ソース選択線駆動回路 170 に入力される信号 SSWB（図 17）が L レベルとされ、全ソース線 SRC0 - 3 が電圧 VST に設定される。電圧 VST は、リード動作時、イレース動作時にそれぞれ 1.8V、9V に設定される。メモリブロック領域 100A 内の各

50

メモリセル111に対するリード動作、及びメモリブロック領域100A内の全メモリセル111に対するイレース動作（一括消去）は、上記図9及び図10に示した動作と同じとすることができる。

#### 【0080】

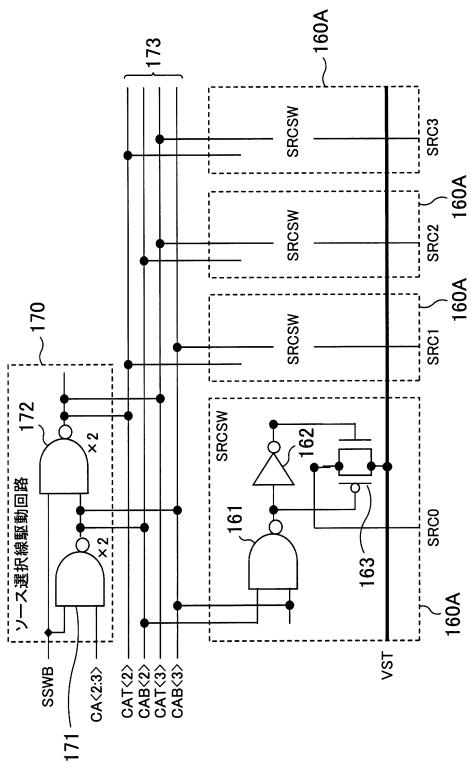

次に、第2の実施の形態について説明する。

第2の実施の形態は、ソース線スイッチSRC SWに、以下に示すようなものを用いる点で、上記第1の実施の形態と相違する。

#### 【0081】

図21は第2の実施の形態に係るソース線スイッチ及びソース選択線駆動回路の一例を示す図である。

10

ここでは、ソース線スイッチSRC SWの構成を、プログラムセグメントPSEG0のソース線SRC0に接続されるソース線スイッチ160Aを例にして説明する。図21では便宜上、プログラムセグメントPSEG1-3のソース線SRC1-3に接続されたソース線スイッチ160Aの内部構成の図示を省略している。

#### 【0082】

図21に示すソース線スイッチ160Aは、非選択のソース線SRCを上記のように電圧VSB(V24)には接続せず、N型ウェルNWと、メモリセル111のソース接合との容量結合によって、非選択のソース線SRCの電圧を昇圧する機能を有する。ソース線スイッチ160Aは、NANDゲート161、NOTゲート162及びCMOSトランスマニアゲート163を含む。尚、ソース選択線駆動回路170は、上記図17と同じ構成とすることができる。

20

#### 【0083】

ソース線SRC0に接続されたソース線スイッチ160AのNANDゲート161には、ソース選択線駆動回路170から出力される信号CAB<2>及び信号CAB<3>が入力される。NANDゲート161の出力信号、及びその出力信号のNOTゲート162による反転信号は、CMOSトランスマニアゲート163に入力される。

#### 【0084】

尚、ソース線SRC1に接続されたソース線スイッチ160Aには、信号CAT<2>及び信号CAB<3>が入力される。ソース線SRC2に接続されたソース線スイッチ160Aには、信号CAB<2>及び信号CAT<3>が入力される。ソース線SRC3に接続されたソース線スイッチ160Aには、信号CAT<2>及び信号CAT<3>が入力される。これらのソース線スイッチ160Aにおいても、上記ソース線SRC0に接続されたソース線スイッチ160Aと同様の流れで信号の処理が行われる。

30

#### 【0085】

図22は第2の実施の形態に係るプログラム動作波形の一例を示す図である。

ここでは、図16に示したメモリブロック領域100AのプログラムセグメントPSEG0に含まれるメモリセル111のうち、ワード線WL0とビット線BL0に接続されたメモリセル111(m00)に対してプログラム動作を行う場合を例にして説明する。

#### 【0086】

上記のようなソース線スイッチ160Aを用いたメモリブロック領域100Aにおいて、ソース線SRC0-3の選択動作以外の動作は、上記図18に示した動作と同じである。

40

#### 【0087】

プログラム動作モードにエントリした後、N型ウェルNW0の電圧を上げる前に、全ソース線SRC0-3は、信号SSWBがLレベルとされて電圧VST(V18(1.8V))に設定され、プリチャージされる。所定時間の経過後（全ソース線SRC0-3のプリチャージ後）、信号SSWBがHレベルとされ、カラムアドレスCAに従って、選択されたソース線SRC0が電圧VSTに設定される。選択されないソース線SRC1-3は、HiZ状態になる。その後、N型ウェルNW0を、電圧V18から電圧VNW0に上げると、メモリセル111のソース接合との容量結合によって、HiZ状態にある非選択の

50

ソース線 S R C 1 - 3 が、電圧 V S T から昇圧された電圧 V S T + に昇圧される。プログラム後、N型ウェル N W 0 の電圧は、電圧 V 1 8 に下がり、容量結合によって非選択のソース線 S R C 1 - 3 の電圧が下がる。その後、全ソース線 S R C 0 - 3 は、信号 S S W B が L レベルとされて電圧 V S T に設定される。

【 0 0 8 8 】

プログラムセグメント P S E G 0 - 3 に分割しない上記メモリブロック領域 1 0 0 (図 3 の B L K 0 ) では、その中の全メモリセル 1 1 1 が共通のソース線 S R C 0 に接続される。そのため、N型ウェル N W と、メモリセル 1 1 1 のソース接合との容量結合によってそのソース線 S R C 0 を昇圧すると、ソース線 S R C 0 から選択ビット線 B L 0 へのリーク電流によって、昇圧後の電圧が保持されない可能性がある。

10

【 0 0 8 9 】

これに対し、プログラムセグメント P S E G 0 - 3 に分割した上記メモリブロック領域 1 0 0 A の場合、非選択のソース線 S R C 1 - 3 が設けられているプログラムセグメント P S E G 1 - 3 には、選択されて 0 V になっているビット線 B L が存在しない。そのため、昇圧されたソース線 S R C 1 - 3 の電圧が、メモリセル 1 1 1 でのリーク電流によって下がるのを抑えることができる。

【 0 0 9 0 】

以上述べたソース線スイッチ 1 6 0 A を用いたメモリブロック領域 1 0 0 A において、リード動作時、イレース動作時には、ソース選択線駆動回路 1 7 0 に入力される信号 S S W B (図 2 1 ) が L レベルとされ、全ソース線 S R C 0 - 3 が電圧 V S T に設定される。電圧 V S T は、リード動作時、イレース動作時にそれぞれ 1 . 8 V 、 9 V に設定される。メモリブロック領域 1 0 0 A 内の各メモリセル 1 1 1 に対するリード動作、及びメモリブロック領域 1 0 0 A 内の全メモリセル 1 1 1 に対するイレース動作 (一括消去) は、上記図 9 及び図 1 0 に示した動作と同じとすることができます。

20

【 0 0 9 1 】

尚、第 2 の実施の形態において、入力信号と論理素子の H レベルの出力電圧、 P M O S のバックバイアスは、昇圧された電圧よりも高くなるように設定される。

次に、第 3 の実施の形態について説明する。

【 0 0 9 2 】

上記第 1 の実施の形態では、1つのメモリブロック領域 1 0 0 A につきビット線 B L が 1 0 2 4 本である場合に、2 5 6 本のビット線 B L 每に、4つプログラムセグメント P S E G に分割する例を示した。分割するプログラムセグメント P S E G の数は、上記の例に限定されるものではない。

30

【 0 0 9 3 】

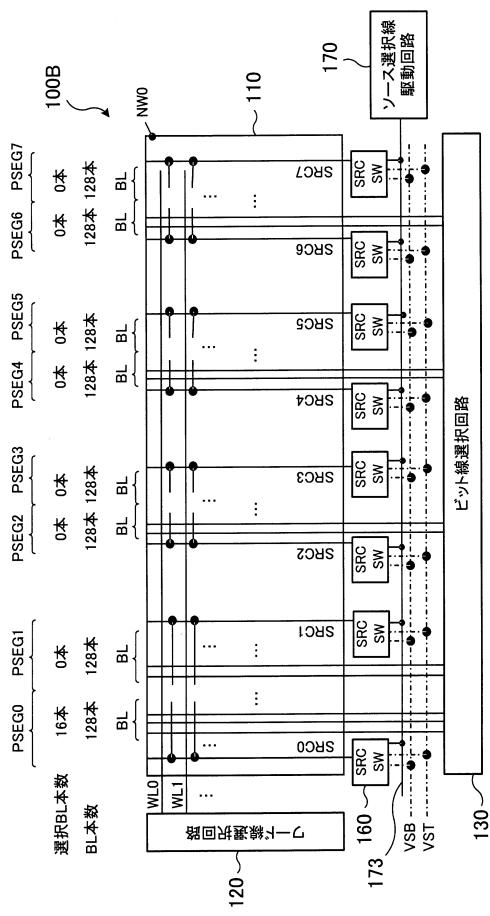

図 2 3 は第 3 の実施の形態に係るメモリブロック領域の構成例を示す図である。

図 2 3 には、1 2 8 本のビット線 B L 每に、8つのプログラムセグメント P S E G 0 - 7 に分割したメモリブロック領域 1 0 0 B を例示している。尚、図 2 3 には便宜上、メモリブロック領域 1 0 0 B を、ワード線 W L とビット線 B L の交差位置に配置されるメモリセル 1 1 1 の図示を省略し、簡略化して図示している。

40

【 0 0 9 4 】

プログラムセグメント P S E G 0 を例に、プログラムセグメント P S E G の構成について説明する。プログラムセグメント P S E G 0 内の各メモリセル 1 1 1 のゲート、ドレインは、それぞれワード線 W L 、ビット線 B L に接続されている。プログラムセグメント P S E G 0 内のメモリセル 1 1 1 のソースは、共通のソース線 S R C 0 に接続されている。

【 0 0 9 5 】

他のプログラムセグメント P S E G 1 - 7 も、このプログラムセグメント P S E G 0 と同様の構成を有し、プログラムセグメント P S E G 1 - 7 内のメモリセル 1 1 1 は、それぞれ共通のソース線 S R C 1 - 7 に接続されている。プログラムセグメント P S E G 0 - 7 のソース線 S R C 0 - 7 は、互いに分離されている。ソース線 S R C 0 - 7 は、それぞれソース線スイッチ ( S R C S W ) 1 6 0 によって、電圧 V S T ( 例えれば 1 . 8 V ) 又は

50

電圧 VSB (例えば 2.4V) に設定される。各ソース線スイッチ 160 は、ソース選択線 173 を介してソース選択線駆動回路 170 に接続されている。また、ワード線 WL は、プログラムセグメント PSEG0-7 の間で共有されている。

#### 【0096】

メモリブロック領域 100B に対するプログラム動作、リード動作、イレース動作は、上記第 1 の実施の形態と同様に行うことができる。尚、メモリブロック領域 100B において、上記第 2 の実施の形態で述べたソース線スイッチ 160A を用いることもできる。

#### 【0097】

この第 3 の実施の形態に係るメモリブロック領域 100B では、各プログラムセグメント PSEG のビット線 BL の本数が、上記メモリブロック領域 100A の場合の 2 分の 1 10 となっている。これにより、プログラム動作時に、選択ワード線 WL に繋がるメモリセル 111 がゲートディスターブを受ける時間は、上記メモリブロック領域 100A の 2 分の 1、プログラムセグメント PSEG に分割しない上記メモリブロック領域 100 の 8 分の 1 になる。

#### 【0098】

また、メモリブロック領域 100B において、プログラム動作時には、プログラムするメモリセル 111 を、プログラムセグメント PSEG0-7 のうち、いずれか 1 つから選択する。例えば、プログラム動作時に 16 本のビット線 BL を選択する場合、図 23 に示すように、それら 16 本のビット線 BL を、プログラムセグメント PSEG0 のみから選択する。これにより、残るプログラムセグメント PSEG1-7 のソース線 SRC1-7 の電圧を、プログラムセグメント PSEG0 のソース線 SRC0 の電圧よりも高くすることができる。 20

#### 【0099】

メモリブロック領域 100B によれば、リーク電流が増えるのを抑えつつ、ゲートディスターブによるメモリセル 111 の閾値電圧 Vth の変動を、効果的に抑制することができる。

#### 【0100】

尚、プログラムセグメント PSEG に分割するうえでのビット線 BL の本数 (分割単位) は、上記のような 256 本や 128 本とは異なる本数としたり、64 本や 16 本といった更に少ない本数としたりすることも可能である。或いは、プログラムセグメント PSEG 每にビット線 BL の本数を変えることも可能である。 30

#### 【0101】

次に、第 4 の実施の形態について説明する。

メモリブロック領域 100 を、上記実施の形態のように複数のプログラムセグメント PSEG に分割する場合、各プログラムセグメント PSEG のソース線 SRC は、メモリブロック領域 100 に元々存在する、ビット線 BL と平行なソース線 SRC を利用して形成可能である。但し、プログラムセグメント PSEG の分割数によっては (例えば 16 本のビット線 BL 每に分割する場合等)、このようなソース線とは別に、ビット線と平行なソース線を更に準備する必要が生じる場合がある。

#### 【0102】

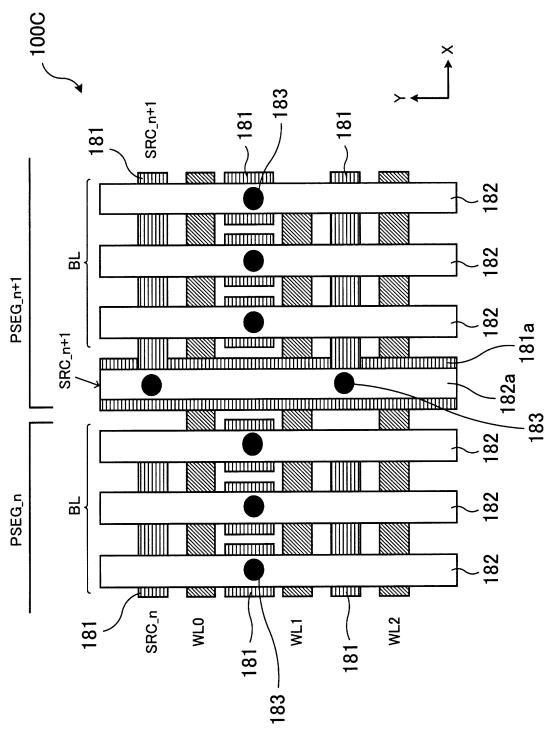

図 24 は第 4 の実施の形態に係るメモリブロック領域の構成例を示す図である。尚、図 24 には、メモリブロック領域の一部のワード線 WL、ビット線 BL 及びソース線 SRC のレイアウトの一例を図示している。 40

#### 【0103】

図 24 に示すメモリブロック領域 100C では、メモリセル 111 のゲートに接続されるワード線 WL0-2 が第 1 方向 X に延在されている。ワード線 WL0 の両側、ワード線 WL1 の両側に、メモリセル 111 のドレイン、ソースに接続されるメタル配線 181 が配置されている。ソースに接続されるメタル配線 181 がプログラムセグメント PSEG\_n のソース線 SRC\_n 及びプログラムセグメント PSEG\_n+1 のソース線 SRC\_n+1 となる。ドレインに接続されるメタル配線 181 は、コンタクト 183 を通じて 50

、第2方向Yに延在配置されたメタル配線182に接続されている。このドレインに繋がるメタル配線182がビット線BLとなる。

【0104】

プログラムセグメントPSEG\_nのソース線SRC\_nと、プログラムセグメントPSEG\_n+1のソース線SRC\_n+1とは、互いに分離されている。ワード線WL0-2は、プログラムセグメントPSEG\_nとプログラムセグメントPSEG\_n+1で共有されている。

【0105】

メモリブロック領域100Cでは、ドレイン、ソースに接続されるメタル配線181と同層で、第2方向Yに延在されるメタル配線181aが配置される。このメタル配線181aにソース線SRC\_n+1のメタル配線181が接続され、メタル配線181aは、更にコンタクト183を通じて、ビット線BLのメタル配線182と同層で第2方向Yに延在されたメタル配線182aに接続される。

【0106】

プログラムセグメントPSEGの分割数によっては、この図24に示すように、隣接するプログラムセグメントPSEG間に、ソースに繋がるメタル配線181a、コンタクト183及びメタル配線182aを設ける。このようなレイアウトを採用することで、様々なプログラムセグメントPSEGの分割数に対応することが可能になる。

【0107】

次に、第5の実施の形態について説明する。

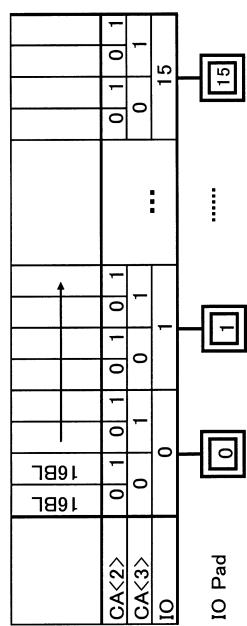

この第5の実施の形態では、アドレスの割り付け手法について説明する。そこで、まず上記のメモリブロック領域100及びメモリブロック領域100Aにおけるアドレス割り付けの一例を図25及び図26にそれぞれ示す。

【0108】

上記メモリブロック領域100では、図25に示すように、カラムアドレスCA<2>及びCA<3>の組み合わせ毎に16本(16BL)、計64本のビット線BLの組が、IOパッド(IO Pad)毎に(IO<0:15>のデータ毎に)配置されている。64本のビット線BLの各組から、カラムアドレスに従って、1つずつIOのデータが選択される。カラムアドレスCA<2:3>によって、16本のビット線BLが選択される。

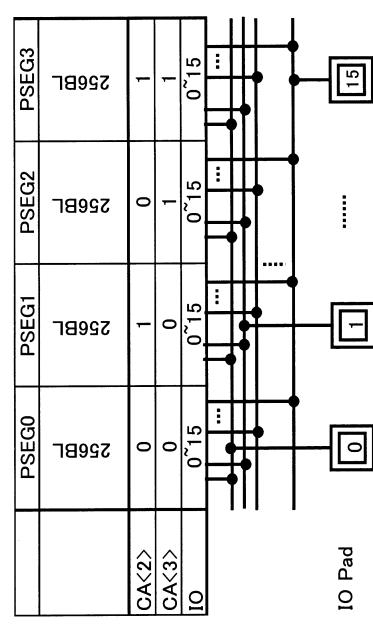

【0109】

また、上記メモリブロック領域100Aでは、図26に示すように、256本のビット線BL(256BL)毎にプログラムセグメントPSEG(PSEG0~3)が設定されている。これらのプログラムセグメントPSEGから、カラムアドレスCA<2:3>に従って、1つのプログラムセグメントPSEGが選択される。IO<0:15>のデータは、選択されたプログラムセグメントPSEGの256本のビット線BLから、他のカラムアドレスによって選択される。

【0110】

ここで、メモリブロック領域100Aにおいて、2つのプログラムセグメントPSEGに対して選択ビット線BLが割り付けられる場合を考える。

図27は選択ビット線の割り付け例を示す図である。

【0111】

この図27の例では、16ビットの信号DIについて、下位(Lower)のビット(0~7)をプログラムセグメントPSEG0に、上位(Upper)のビット(8~15)をプログラムセグメントPSEG1に、それぞれ割り付ける。プログラムセグメントPSEG0及びPSEG1から、それぞれ8本のビット線が選択される。

【0112】

この場合において、16ビットの信号DIをまとめてプログラムする方法と、8ビット毎に2回に分けてプログラムする方法とを比較する。16ビットの信号DIをまとめてプログラムする場合、ソース線SRCの電圧が低い状態(非選択ソース線SRCの電圧VSB(2.4V)よりも低い電圧VST(1.8V)に設定されている状態)でプログラム

10

20

30

40

50

される回数は、 $512 / 16 = 32$ 回である。一方、8ビット毎に2回に分けてプログラムする場合、2つのプログラムセグメントPSEG0及びPSEG1のソース線SRCを選択し、低い電圧VSTに設定すると、ソース線SRCの電圧が低い状態でプログラムされる回数は、 $512 / 8 = 64$ 回になる。このようにプログラム回数が増えると、ゲートディスターブを受ける時間が長くなる。

#### 【0113】

そこで、以下のようなアドレスの割り付け手法を適用する例を、第5の実施の形態として説明する。

図28は第5の実施の形態に係るアドレス割り付けの一例を示す図である。

#### 【0114】

図28に示す例では、カラムアドレスCA<3>によって、2つのプログラムセグメントPSEG(例えばPSEG0とPSEG1)が選択される。下位のIO<0:7>のデータは、選択された一方のプログラムセグメントPSEGから、他のカラムアドレスによって選択される。上位のIO<8:15>のデータは、選択されたもう一方のプログラムセグメントPSEGから、他のカラムアドレスによって選択される。

#### 【0115】

尚、8ビットのIOデータにプログラムを示すビットがない場合、対応するプログラムセグメントPSEGは選択されず、そのソース線SRCの電圧は高くなる。

図29は第5の実施の形態に係るソース線スイッチ及びソース選択線駆動回路の一例を示す図である。

#### 【0116】

ここでは、ソース線スイッチSRC\_SWの構成を、プログラムセグメントPSEG0のソース線SRC0に接続されるソース線スイッチ160Bを例にして説明する。図29では便宜上、プログラムセグメントPSEG1-3のソース線SRC1-3に接続されたソース線スイッチ160Bの内部構成の図示を省略している。

#### 【0117】

図29に示すソース線スイッチ160Bでは、プログラム動作時、ソース選択線駆動回路170のNANDゲート171に、信号SSWB、及びプログラムセグメントPSEGを指定するカラムアドレスCA<3>が入力される。NANDゲート172には、信号SSWB、及びNANDゲート171から出力される信号CAB<3>が入力され、信号CAT<3>が出力される。

#### 【0118】

信号UIOは、プログラム動作時に、上位のIO<8:15>のデータのうち、いずれかのビットがLレベルなら、Hレベルになる信号である。信号LIOは、プログラム動作時に、下位のIO<0:7>のデータのうち、いずれかのビットがLレベルなら、Hレベルになる信号である。

#### 【0119】

ソース線SRC0に接続されたソース線スイッチ160BのNANDゲート161には、ソース選択線駆動回路170から出力される信号CAB<3>及び信号LIOが入力される。NANDゲート161の出力信号、及びその出力信号のNOTゲート162による反転信号は、CMOSトランスファゲート163、CMOSトランスファゲート164に入力される。

#### 【0120】

尚、ソース線SRC1に接続されたソース線スイッチ160Bには、信号UIO及び信号CAT<3>が入力される。ソース線SRC2に接続されたソース線スイッチ160Bには、信号LIO及び信号CAT<3>が入力される。ソース線SRC3に接続されたソース線スイッチ160Bには、信号UIO及び信号CAT<3>が入力される。これらのソース線スイッチ160Bにおいても、上記ソース線SRC0に接続されたソース線スイッチ160Bと同様の流れで信号の処理が行われる。

10

20

30

40

50

## 【0121】

プログラム動作時には、プログラムセグメント PSEG を指定するカラムアドレス CA <3> と、信号 UIO 及び信号 LIO に従って、ソース線 SRC に設定される電圧が切り替えられる。選択されるプログラムセグメント PSEG では、そのソース線 SRC が電圧 VST (1.8V) に設定され、非選択のプログラムセグメント PSEG では、そのソース線 SRC が電圧 VSB (2.4V) に設定される。プログラム動作時の、ソース線 SRC の選択動作以外の動作は、上記図 18 に示した動作と同じとすることができる。

## 【0122】

ソース線スイッチ 160B では、信号 DI の下位の IO <0:7> のデータ又は上位の IO <8:15> のデータのうち、1 ビットでもプログラムを示すビットがあった場合、それに対応するプログラムセグメント PSEG のソース線 SRC が選択され、電圧 VST に設定される。下位の IO <0:7> のデータ又は上位の IO <8:15> のデータにプログラムを示すビットがない場合、それに対応するプログラムセグメント PSEG のソース線 SRC は選択されず、より高い電圧 VSB に設定される。これにより、ソース線 SRC の電圧が低い状態（非選択ソース線 SRC の電圧 VSB よりも低い電圧 VST に設定されている状態）でプログラムされる回数を、 $256 / 8 = 32$  回にすることができる。2 つのプログラムセグメント PSEG0 及び PSEG1 のソース線 SRC を選択して低い電圧 VST に設定するよりも、ゲートディスターブを受ける時間を短くすることができる。

## 【0123】

尚、この第 5 の実施の形態で述べたような手法は、上記第 2 ~ 第 4 の実施の形態で述べたようなメモリブロック領域 100A ~ 100C に同様に適用可能である。

以上、フラッシュメモリを例にして説明したが、上記のようなプログラム動作に関する手法は、EEPROM、EEPROM 等の半導体メモリにも同様に適用可能である。

## 【0124】

以上説明した実施の形態に関し、更に以下の付記を開示する。

（付記 1）ワード線群とビット線群の交差位置にそれぞれ配置され、共通のソース線に接続されたメモリセル群を含む複数のメモリブロックであって、前記複数のメモリブロック間で前記ワード線群を共有し、前記複数のメモリブロック毎に分離された複数の前記ソース線を備える複数のメモリブロックと、

プログラム動作時に、前記複数のメモリブロックのうち、プログラムするメモリセルが含まれるメモリブロックの前記ソース線に第 1 電圧を供給し、前記プログラムするメモリセルが含まれないメモリブロックの前記ソース線に前記第 1 電圧と異なる第 2 電圧を供給する回路部と、

を備えることを特徴とする半導体記憶装置。

## 【0125】

（付記 2）前記第 2 電圧は、前記第 1 電圧よりも高い電圧であることを特徴とする付記 1 に記載の半導体記憶装置。

（付記 3）1 回の前記プログラム動作時に、前記プログラムするメモリセルが、前記ワード線群を共有する前記複数のメモリブロックのうち、いずれか 1 つのメモリブロックから選択されることを特徴とする付記 1 又は 2 に記載の半導体記憶装置。

## 【0126】

（付記 4）1 回の前記プログラム動作時に、前記プログラムするメモリセルの情報を含むデータを上位ビットデータと下位ビットデータに分割し、前記上位ビットデータを、前記複数のメモリブロックのうち、第 1 のメモリブロックに対応させ、前記下位ビットデータを、前記複数のメモリブロックのうち、第 2 のメモリブロックに対応させて、前記プログラム動作を行うことを特徴とする付記 1 又は 2 に記載の半導体記憶装置。

## 【0127】

（付記 5）前記回路部は、前記複数のメモリブロック毎に分離された前記ソース線にそれぞれ接続された複数のスイッチ回路を含み、

10

20

30

40

50

前記複数のスイッチ回路がそれぞれ、接続されている前記ソース線に供給する電圧を前記第1電圧又は前記第2電圧に切り替えることを特徴とする付記1乃至4のいずれかに記載の半導体記憶装置。

【0128】

(付記6) 前記メモリセル群は、電気的にプログラム可能な不揮発性メモリセルであることを特徴とする付記1乃至5のいずれかに記載の半導体記憶装置。

(付記7) 前記メモリセル群は、pチャネル型トランジスタであることを特徴とする付記1乃至6のいずれかに記載の半導体記憶装置。

【0129】

(付記8) 前記回路部は、プログラム動作時に、前記複数のメモリブロックのうち、前記プログラムするメモリセルが含まれないメモリブロックの前記ソース線に、当該メモリブロックのウェルと当該メモリブロック内のメモリセルのソース接合との容量結合によって昇圧された前記第2電圧を供給することを特徴とする付記7に記載の半導体記憶装置。

10

【0130】

(付記9) 前記複数のメモリブロックのそれぞれの前記メモリセル群が接続される前記ビット線の本数が同数あることを特徴とする付記1乃至8のいずれかに記載の半導体記憶装置。

【0131】

(付記10) 前記複数のメモリブロックの中に、前記メモリセル群が接続される前記ビット線の本数が互いに異なるメモリブロックが含まれることを特徴とする付記1乃至8のいずれかに記載の半導体記憶装置。

20

【符号の説明】

【0132】

10 メモリ内蔵マイコン

11 周辺I/Oポート

12 周辺I/O制御回路

13 CPU

14 RAM

15 ROM

16 内部バス

17 RAMインタフェース

18 ROMインタフェース

20 フラッシュメモリ

21 メモリコア

22 コマンド生成回路

23 内部電圧生成回路

24 メモリコア制御回路

25 アドレス生成回路

26 データ入出力回路

100, 100A, 100B, 100C メモリブロック領域

110 メモリセルアレイ

111, m00 - m33 メモリセル

120 ワード線選択回路

121, 122, 133, 134, 143, 144, 157 NORゲート

123 ワードデコーダ

124, 154, 155, 156, 161, 171, 172 NANDゲート

125, 131, 132, 141, 142, 152, 153, 162 NOTゲート

126, 127, 163, 164 CMOSトランスファゲート

130 ビット線選択回路

30

40

50

1 3 5 a , 1 3 5 b , 1 3 6 a , 1 3 6 b , 1 3 7 a , 1 3 7 b , 1 3 8 a , 1 3 8 b

, 1 4 5 a , 1 4 5 b , 1 4 6 a , 1 4 6 b , 1 5 9 N M O S

1 4 0 グローバルビット線選択回路

1 5 0 リードライトアンプ

1 5 0 a リードアンプ

1 5 0 b ライトアンプ

1 5 1 コンパレータ

1 5 8 P M O S

1 6 0 , 1 6 0 A , 1 6 0 B ソース線スイッチ

1 7 0 ソース選択線駆動回路

1 7 3 ソース選択線

1 8 1 , 1 8 1 a , 1 8 2 , 1 8 2 a メタル配線

1 8 3 コンタクト

W L , W L 0 - 3 ワード線

B L , B L 0 - 3 ビット線

G B L , G B L 0 - 1 グローバルビット線

S R C , S R C 0 - 7 ソース線

N W , N W 0 N型ウェル

P S E G , P S E G 0 - 7 プログラムセグメント

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

|       | READ | ERASE  | PROGRAM |

|-------|------|--------|---------|

| WL0-3 | 選択   | -3V    | 9V      |

|       | 非選択  | 1.8V   | ...     |

|       |      | ...    | 0V      |

| BL0-3 | 選択   | 0~1.8V | HiZ     |

|       | 非選択  | HiZ    | HiZ     |

|       |      | 2.4V   |         |

| SRC0  | 1.8V | 9V     | 1.8V    |

| NW0   | 1.8V | 9V     | 5V      |

【図 1 3】

【図 1 4】

【図15】

【図16】

### 【 図 1 7 】

【 図 1 8 】

【図19】

【 図 20 】

【図21】

## 【 図 2 2 】

【図23】

【図24】

【図25】

【図26】

【図27】

|        | PSEG0 | PSEG1 | PSEG2 | PSEG3 |

|--------|-------|-------|-------|-------|

| BL本数   | 256   | 256   | 256   | 256   |

| 選択BL本数 | 8     | 8     | 0     | 0     |

| DI     | Lower | Upper | 0     | 0     |

【図28】

【図29】

---

フロントページの続き

(56)参考文献 特開平09-180478(JP, A)

特開2009-212292(JP, A)

特開2006-156925(JP, A)

特表2002-540601(JP, A)

米国特許出願公開第2011/0134694(US, A1)

(58)調査した分野(Int.Cl., DB名)

G 11 C 16/02 - 16/06