(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5311851号

(P5311851)

(45) 発行日 平成25年10月9日(2013.10.9)

(24) 登録日 平成25年7月12日(2013.7.12)

|                        |                 |

|------------------------|-----------------|

| (51) Int.Cl.           | F 1             |

| HO1L 21/336 (2006.01)  | HO1L 29/78 371  |

| HO1L 29/788 (2006.01)  | HO1L 27/10 434  |

| HO1L 29/792 (2006.01)  | HO1L 27/10 481  |

| HO1L 21/8247 (2006.01) | HO1L 29/78 613B |

| HO1L 27/115 (2006.01)  |                 |

請求項の数 2 (全 54 頁) 最終頁に続く

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2008-68736 (P2008-68736)    |

| (22) 出願日     | 平成20年3月18日 (2008.3.18)        |

| (65) 公開番号    | 特開2008-270766 (P2008-270766A) |

| (43) 公開日     | 平成20年11月6日 (2008.11.6)        |

| 審査請求日        | 平成23年2月28日 (2011.2.28)        |

| (31) 優先権主張番号 | 特願2007-77930 (P2007-77930)    |

| (32) 優先日     | 平成19年3月23日 (2007.3.23)        |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 野田 耕生<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 佐藤 奈々絵<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内  |

審査官 加藤 俊哉

最終頁に続く

(54) 【発明の名称】 半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

不揮発性半導体メモリ素子を有する半導体装置であり、

前記不揮発性半導体メモリ素子は、

ソース領域、ドレイン領域、およびチャネル形成領域を有する半導体領域と、

前記半導体領域上に形成され、前記チャネル形成領域と重なる導電膜と、

前記半導体領域と前記導電膜の間に形成され、前記チャネル形成領域と重なる第1絶縁膜と、

前記半導体領域と前記導電膜の間に形成され、前記第1絶縁膜上に形成された第1窒化シリコン膜と、

前記半導体領域と前記導電膜の間に形成され、前記第1窒化シリコン膜上に形成された第2窒化シリコン膜と、を有し、

前記第2窒化シリコン膜は、N-H結合の濃度に対するSi-X結合(Xはハロゲン元素)の濃度の比が、前記第1窒化シリコン膜よりも大きいことを特徴とする半導体装置。

## 【請求項 2】

不揮発性半導体メモリ素子を有する半導体装置であり、

前記不揮発性半導体メモリ素子は、

ソース領域、ドレイン領域、およびチャネル形成領域を有する半導体領域と、

前記半導体領域上に形成され、前記チャネル形成領域と重なる導電膜と、

前記半導体領域と前記導電膜の間に形成され、前記チャネル形成領域と重なる第1絶

10

20

縁膜と、

前記半導体領域と前記導電膜の間に形成され、前記第1絶縁膜上に形成された第1窒化シリコン膜と、

前記半導体領域と前記導電膜の間に形成され、前記第1窒化シリコン膜上に形成された第2窒化シリコン膜と、を有し、

前記第2窒化シリコン膜は、N-H結合の濃度に対するSi-H結合とSi-X結合(Xはハロゲン元素)の濃度の和の比が、前記第1窒化シリコン膜よりも大きいことを特徴とする半導体装置。

#### 【発明の詳細な説明】

##### 【技術分野】

10

##### 【0001】

本発明は、書き込み、読み出しおよび消去が可能な不揮発性半導体メモリ素子を有する半導体装置に関する。

##### 【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用して機能しうる装置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

##### 【背景技術】

##### 【0003】

不揮発性半導体メモリ素子は、電気的に書き換えが可能であり、電源を切ってもデータを記憶しておくことのできる半導体素子である。不揮発性半導体メモリ素子として、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)と類似の構造を有する不揮発性メモリトランジスタは電荷蓄積手段の違いにより2種類に大別される。一方は、電荷蓄積手段が、チャネル形成領域とゲート電極の間の導電層でなるFG(Floating Gate)型である。他方は、電荷蓄積手段に、電荷トラップ層を用いた、MONOS(Metal-Oxide-Nitride-Oxide-Silicon)型およびMNOS(Metal-Nitride-Oxide-Silicon)型である。

20

##### 【0004】

MONOS型およびMNOS型のメモリトランジスタの多くは、電荷トラップを多く含む窒化シリコン膜が電荷蓄積手段に用いられている。MONOS型およびMNOS型のメモリトランジスタの電荷保持特性を向上させるために、窒化シリコン膜について研究がされている。

30

##### 【0005】

例えば、特許文献1~4には、窒化シリコン膜を組成または組成比の異なる2層構造とすることで、メモリトランジスタの保持特性を向上させることが記載されている。また、特許文献5には、組成比の異なる3層構造の窒化シリコン膜を形成することで、保持特性を向上させることが記載されている。

##### 【0006】

特許文献1(特公平2-59632号公報)では、下層にSi-H結合を含む窒化シリコン膜を形成し、上層にSi-H結合を殆ど含まない窒化シリコン膜を形成している。このような2層構造の窒化シリコン膜の形成は、SiH<sub>4</sub>およびNH<sub>3</sub>を原料にしたCVD法を用い、窒化シリコン膜の形成温度を下層の形成時には700~900とし、上層の形成時には900以上とすることで、行っている。

40

##### 【0007】

特許文献2(特公昭59-24547公報)では、下層にSiを多く含む窒化シリコン膜を形成し、上層にNを多く含む窒化シリコン膜を形成している。このような2層構造の窒化シリコン膜を形成するために、SiH<sub>4</sub>およびNH<sub>3</sub>を原料にしたCVD法が用いられ、流量比NH<sub>3</sub>/SiH<sub>4</sub>を下層の形成時には50~150とし、上層の形成時には300を超えるようにしている。

##### 【0008】

50

特許文献3（特開昭63-205965号公報）では、下層に比較的電気伝導度の高い窒化シリコン膜を形成し、上層に比較的電気伝導度の低い窒化シリコン膜をCVD法で形成している。このような2層構造の窒化シリコン膜を形成するための条件として、加熱温度が700～800であり、SiH<sub>2</sub>Cl<sub>2</sub>とNH<sub>3</sub>を原料にして、流量比NH<sub>3</sub>/SiH<sub>2</sub>Cl<sub>2</sub>を下層の形成時には0.1～150とし、上層の形成時には10～1000とすることが記載されている。

#### 【0009】

特許文献4（特開2002-203917号公報）には、電荷トラップ密度を上層の方を高くした2層構造の窒化シリコン膜をCVD法で形成している。このような2層構造の窒化シリコン膜を形成するために、上層を形成するときのシリコンソースガスに、下層の形成に用いたシリコンソースガスよりも塩素の組成比が低いSiH<sub>4</sub>やSiH<sub>2</sub>Cl<sub>2</sub>などを用いることが記載されている。特許文献4では、シリコンソースガスの塩素組成比を変えることで、下層にSi-H結合よりもSi-C结合を多く含む窒化シリコン膜を形成し、上層にSi-H結合を多く含む窒化シリコン膜を形成している。10

#### 【0010】

特許文献5（特開平3-9571号公報）には、3層構造の窒化シリコン膜が記載されており、第2層目の窒化シリコン膜を、他の層と比較して、電荷トラップ準位密度を高くし、かつSiリッチにしている。このような3層構造の窒化シリコン膜を形成するために、第2層目の形成時にSiH<sub>2</sub>Cl<sub>2</sub>の流量を上昇させている。

【特許文献1】特公平2-59632号公報20

【特許文献2】特公昭59-24547号公報

【特許文献3】特開昭63-205965号公報

【特許文献4】特開2002-203917号公報

【特許文献5】特開平3-9571号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0011】

本発明は、不揮発性半導体メモリ素子の電荷保持特性を向上させることを課題の1つとする。

#### 【課題を解決するための手段】

#### 【0012】

本発明の1つは、不揮発性半導体メモリ素子を有する半導体装置である。不揮発性半導体メモリ素子は、半導体であり、ソース領域、ドレイン領域、およびチャネル形成領域を有する半導体領域と、チャネル形成領域と重なる導電膜を有する。電荷トラップを形成するため、半導体領域と導電膜の間に少なくとも、チャネル形成領域と重なる第1絶縁膜、第1絶縁膜上に形成された第1窒化シリコン膜、第1窒化シリコン膜上に形成された第2窒化シリコン膜を有する。更に、不揮発性半導体メモリ素子は、半導体領域と導電膜の間に第2窒化シリコン膜の上に形成された第2絶縁膜を有することもできる。

#### 【0013】

本発明は、窒化シリコン中のHの結合状態に着目してなされたものである。本発明の1つは、N-H結合の濃度を第1窒化シリコン膜の方を第2窒化シリコン膜よりも高くすることにより、不揮発性半導体メモリ素子の保持特性を改善するものである。40

#### 【0014】

また、本発明において、第2窒化シリコン膜は、Si-H結合又はSi-X結合（Xはハロゲン元素）を第1窒化シリコン膜よりも多く含む膜であることが好ましい。

#### 【0015】

また、第2窒化シリコン膜のN-H結合の濃度に対するSi-H結合の濃度の比（Si-H/N-H）が、第1窒化シリコン膜よりも大きいことが好ましい。または、第2窒化シリコン膜のN-H結合の濃度に対するSi-X結合（Xはハロゲン元素）結合の濃度の比（Si-X/N-H）が、第1窒化シリコン膜よりも大きいことが好ましい。或いは、50

第2窒化シリコン膜は、N-H結合の濃度に対して、Si-H結合とSi-X結合(Xはハロゲン元素)結合の濃度の和の比((Si-H)+(Si-X)/N-H)が、第1窒化シリコン膜よりも大きいことが好ましい。

#### 【0016】

また、第2窒化シリコン膜が、第1窒化シリコン膜よりも化学量論的に $\text{Si}_3\text{N}_4$ に近い膜であることが好ましい。

#### 【0017】

本発明において、第1窒化シリコン膜および第2窒化シリコン膜は、化学気相成長(Chemical Vapor Deposition: CVD)法により形成される。このCVD法としては、減圧CVD法、プラズマCVD法、熱CVD法、およびCat-CVD法(Catalytic Chemical Vapor Deposition)法などを用いることができる。10

#### 【0018】

N-H結合の濃度の異なる第1窒化シリコン膜および第2窒化シリコン膜を形成するため、第1窒化シリコン膜の原料となる窒素ソースガスには、N-H結合を含む窒化水素ガスを用いる。他方、第2窒化シリコン膜の窒素ソースガスには、N-H結合を実質的に含まないガス、つまり組成に実質的に水素を含まないガスを用いる。

#### 【0019】

第1窒化シリコン膜の窒素ソースガスには、アンモニア( $\text{NH}_3$ )を用いることが好ましい。アンモニア( $\text{NH}_3$ )の替わりに、ヒドラジン( $\text{NH}_2\text{H}_2\text{N}$ )を用いることもできる。第2窒化シリコン膜の窒素ソースガスには、窒素( $\text{N}_2$ )ガスを用いることが好ましい。20

#### 【0020】

第1窒化シリコン膜および第2窒化シリコン膜の形成に用いられるシリコンソースガスは、水素又はハロゲンを組成に含むガスを用いることができる。シリコンソースガスには、 $\text{SiH}_4$ 、 $\text{Si}_2\text{H}_6$ 、 $\text{SiCl}_4$ 、 $\text{SiHCl}_3$ 、 $\text{SiH}_2\text{Cl}_2$ 、 $\text{SiH}_3\text{Cl}_3$ 、 $\text{SiF}_4$ などがある。第1窒化シリコン膜と第2窒化シリコン膜では、シリコンソースガスが同じでも、異なっていてもよい。

#### 【0021】

本発明の不揮発性半導体メモリ素子において、データの書き込み方法および消去方法は、ファウラー-ノルドハイム(Fowler-Nordheim: F-N)トンネル電流を用いる方法、ダイレクトトンネル電流を用いる方法、又はホットキャリアを用いる方法のいずれかの方法を用いることができる。30

#### 【発明の効果】

#### 【0022】

本発明により、不揮発性半導体メモリ素子の電荷保持特性を向上させることができ、高信頼のデータ記憶性能を備えた半導体装置を提供することができる。

#### 【発明を実施するための最良の形態】

#### 【0023】

以下に、本発明を説明する。ただし、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨およびその範囲から逸脱することなく、その形態および詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は実施の形態の記載内容に限定して解釈されるものではない。40

#### 【0024】

##### (実施の形態1)

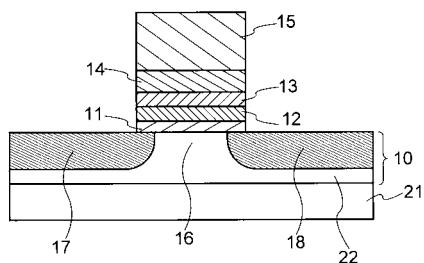

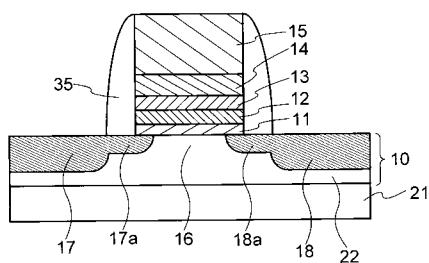

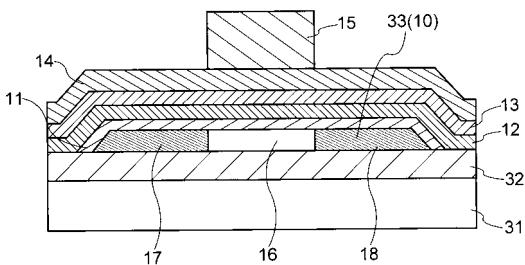

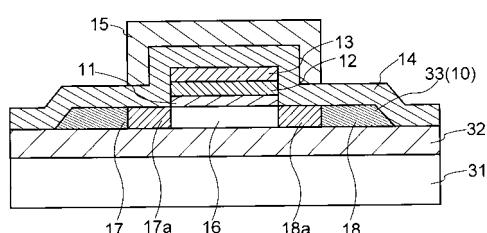

本実施の形態では、本発明に、不揮発性メモリ素子として、不揮発性メモリトランジスタを適用した例を説明する。まず、図1を用いて、本発明の不揮発性メモリトランジスタの構成および作製方法を説明する。

#### 【0025】

図1は、MONOS型の不揮発性メモリトランジスタの主要な構成を説明するための断

50

面図である。図1の不揮発性メモリトランジスタは、半導体領域10およびウェル22が形成された半導体基板21を有する。半導体基板21にウェル22を形成することで、メモリトランジスタが形成される半導体領域10が規定される。半導体領域10には、チャネル形成領域16、並びにチャネル形成領域16を挟んで高濃度不純物領域17と高濃度不純物領域18が形成されている。高濃度不純物領域17、18は、メモリトランジスタのソース領域またはドレイン領域となる領域である。

#### 【0026】

半導体基板21がp型の基板である場合、半導体基板21に、イオン注入法などによりリン(P)またはヒ素(As)などのn型不純物を添加することで、ウェル22が形成される。半導体基板21がn型の基板である場合は、ボロン(B)などのp型不純物を添加することで、ウェル22が形成される。ウェル22のn型またはp型不純物の濃度は $5 \times 10^{15} \text{ cm}^{-3}$ ~ $1 \times 10^{16} \text{ cm}^{-3}$ 程度である。また、ウェル22は必要に応じて適宜形成される。10

#### 【0027】

半導体領域10上には、第1絶縁膜11、第1窒化シリコン膜12、第2窒化シリコン膜13、第2絶縁膜14、および導電膜15がこの順序で積層されている。これらの膜11~15は、半導体領域10のチャネル形成領域16と重なっている。

#### 【0028】

導電膜15がメモリトランジスタのゲート電極として機能する。第1窒化シリコン膜12および第2窒化シリコン膜13が電荷蓄積層として用いられる。電荷蓄積層への電荷の出し入れの方法(不揮発性メモリトランジスタの書き込み方法、消去方法)には、F-Nトンネル電流を用いる方法、ダイレクトトンネル電流を用いる方法、およびホットキャリアを用いる方法がある。本実施の形態の不揮発性メモリトランジスタは、書き込み方法、消去方法に、これらの方法から適宜選択して用いることができる。20

#### 【0029】

第1絶縁膜11は電荷が通過するように薄く形成され、第1絶縁膜11の厚さは1nm以上 $10 \text{ nm}$ 以下が好ましく、その厚さは1nm以上5nm以下がより好ましい。第1絶縁膜11は、酸化シリコン、酸化窒化シリコン(SiO<sub>x</sub>N<sub>y</sub>)、酸化アルミニウム、酸化タンタル、酸化ジルコニウム、および酸化ハフニウムから選ばれた絶縁材料でなる単層膜で形成することができる。また、酸化シリコン膜上に、酸化窒化シリコン(SiO<sub>x</sub>N<sub>y</sub>)、酸化アルミニウム、酸化タンタル、酸化ジルコニウム、および酸化ハフニウムから選ばれた絶縁膜を積層した2層構造とすることもできる。30

#### 【0030】

例えば、酸化シリコン膜を形成する方法には、半導体基板21を熱酸化する、プラズマ処理により酸素ラジカルを発生させて半導体基板21を酸化する、プラズマCVD法などのCVD法により酸化シリコン膜を形成する方法などがある。また、酸化窒化シリコン膜の形成方法には、熱酸化処理やプラズマ処理により半導体基板21を酸化して酸化シリコン膜を形成し、この酸化シリコン膜を熱窒化処理またはプラズマ処理により窒化することで形成する方法、プラズマCVD法などのCVD法により酸化窒化シリコン膜を形成する方法等がある。酸化アルミニウムなどの金属の酸化物でなる膜はスパッタ法、有機金属気相成長(Metal-Organic Chemical Vapor Deposition: MOCVD)法等で形成することができる。40

#### 【0031】

第1窒化シリコン膜12は、減圧CVD法、プラズマCVD法、熱CVD法、およびCat-CVD法等のCVD法で形成される。プラズマCVD法を用いることで、加熱温度を600以下とすることができます。第1窒化シリコン膜12の原料となる窒素ソースガスには、N-H結合を含む窒化水素ガスを用いる。具体的には、この窒素ソースガスにアンモニア(NH<sub>3</sub>)を用いることが好ましく、アンモニア(NH<sub>3</sub>)の替わりに、ヒドラジン(NH<sub>2</sub>H<sub>2</sub>N)を用いることもできる。

#### 【0032】

10

20

30

40

50

第1窒化シリコン膜12の原料となるシリコンソースガスは、水素又はハロゲンを組成に含むガスが用いられる。このようなガスとして、 $\text{SiH}_4$ 、 $\text{Si}_2\text{H}_6$ 、 $\text{SiCl}_4$ 、 $\text{SiHCl}_3$ 、 $\text{SiH}_2\text{Cl}_2$ 、 $\text{SiH}_3\text{Cl}_3$ 、 $\text{SiF}_4$ などがある。

#### 【0033】

シリコンソースガスに対する窒素ソースガスの流量比( Nソースガス / Siソースガス )は、0.1以上1000以下とすることができ、この流量比は1以上400以下がより好ましい。

#### 【0034】

第1窒化シリコン膜を形成するときのCVDのプロセスガスには、原料となる窒素ソースガスおよびシリコンソースガス以外のガスを添加することができ、このようなガスとしては、He、Ar、Xe等の希ガスや、水素( $\text{H}_2$ )ガス等がある。

10

#### 【0035】

第2窒化シリコン膜13は、減圧CVD法、プラズマCVD法、熱CVD法、およびCat-CVD法等のCVD法で形成される。プラズマCVD法を用いることで、加熱温度を600以下とすることができます。第2窒化シリコン膜の原料となる窒素ソースガスには、実質的にN-H結合を含まないガスを用いる。具体的には、この窒素ソースガスは窒素( $\text{N}_2$ )ガスが好ましい。

#### 【0036】

第2窒化シリコン膜13の原料となるシリコンソースガスは、第1窒化シリコン膜12と同様、 $\text{SiH}_4$ 、 $\text{Si}_2\text{H}_6$ 、 $\text{SiCl}_4$ 、 $\text{SiHCl}_3$ 、 $\text{SiH}_2\text{Cl}_2$ 、 $\text{SiH}_3\text{Cl}_3$ 、 $\text{SiF}_4$ から選ばれたガスを用いることができる。

20

#### 【0037】

第2窒化シリコン膜13を形成するときのCVDのプロセスガスには、原料となる窒素ソースガスおよびシリコンソースガス以外のガスを添加することができ、このようなガスとしては、He、Ar、Xe等の希ガスや、水素( $\text{H}_2$ )ガス等がある。また、 $\text{N}_2$ ガスの電離を促進するため、He、Ar、Xe等の希ガスを原料ガスに添加することができる。

#### 【0038】

シリコンソースガスに対する窒素ソースガスの流量比( Nソースガス / Siソースガス )は、0.1以上1000以下とすることができ、この流量比は1以上400以下がより好ましい。

30

#### 【0039】

プロセスガスの流量、および種類を調節することで、CVD装置の同じ反応室で、第1窒化シリコン膜12と第2窒化シリコン膜13とを連続的に形成することができる。このようにすることで、第1窒化シリコン膜12と第2窒化シリコン膜13の界面を大気に曝すことなく形成できるので、界面に不安定な電荷トラップ準位が形成されることを防ぐことができる。また、複数の反応室を持つCVD装置を用い、CVD装置から基板を取り出すことなく、別々の反応室で第1窒化シリコン膜12と第2窒化シリコン膜13を形成しても、同様に界面の汚染を防ぐことができる。

#### 【0040】

第1窒化シリコン膜12と第2窒化シリコン膜13とは、電荷蓄積層として機能する。窒素ソースガスの違いにより、第1窒化シリコン膜は第2窒化シリコン膜よりもN-H結合を多く含む。第1窒化シリコン膜12の方が、シリコンソースガスに由来するSi-H結合またはSi-X結合(Xはハロゲン元素)の濃度が第2窒化シリコン膜13よりも低くなる。

#### 【0041】

また、第1窒化シリコン膜12および第2窒化シリコン膜13の厚さは、それぞれ、1nm以上20nm以下にすることができ、その厚さは、それぞれ、5nm以上15nm以下がより好ましい。また、第1窒化シリコン膜12と第2窒化シリコン膜13の厚さの合計が15nm以下であることが好ましい。

50

## 【0042】

第2絶縁膜14は1nm以上20nm以下の厚さで形成することができる。第2絶縁膜14の厚さは5nm以上10nm以下が好ましい。第2絶縁膜14は、酸化シリコン、酸化窒化シリコン(SiO<sub>x</sub>N<sub>y</sub>)、窒化シリコン、酸化アルミニウム、酸化タンタル、酸化ジルコニウム、および酸化ハフニウムから選ばれた絶縁材料でなる単層膜、または2層以上の多層膜で形成することができる。第2絶縁膜14を構成する絶縁膜は、熱酸化、CVD法、スパッタ法で形成することができる。例えば、第2絶縁膜14を多層構造とする場合、第2窒化シリコン膜13を熱酸化し、かかる後、CVD法またはスパッタ法で、上記の絶縁材料でなる膜を堆積させる方法を用いることができる。

## 【0043】

導電膜15は不揮発性メモリトランジスタのゲート電極を構成し、単層膜、2層以上の多層膜とすることができます。導電膜15を構成する導電性材料としては、タンタル(Ta)、タンゲステン(W)、チタン(Ti)、モリブデン(Mo)、クロム(Cr)、ニオブ(Nb)等から選択された金属、又はこれらの金属を主成分とする合金若しくは化合物(例えば金属窒化物、シリサイド)、リン等の不純物元素を添加した多結晶シリコンを用いることができる。例えば、導電膜15は一層又は複数層の金属窒化物と、その上の単体金属でなる層の多層構造とすることができます。この金属窒化物としては、窒化タンゲステン、窒化モリブデン、窒化チタンを用いることができる。第2絶縁膜14に接して金属窒化物層を形成することにより、その上の金属層の剥離を防止することができる。また、窒化タンタルなどの金属窒化物は仕事関数が高いので、第2絶縁膜14との相乗効果により、第1絶縁膜11を厚くすることができる。

10

## 【0044】

また、半導体領域10に形成された高濃度不純物領域17、18は、膜11～15である積層膜をマスクにして、イオン注入法により、半導体基板21に不純物を添加することにより、自己整合的に形成される。ウェル22がp型である場合は、高濃度不純物領域17、18にはn型不純物が添加され、n型である場合は、高濃度不純物領域17、18にはp型不純物が添加される。

20

## 【0045】

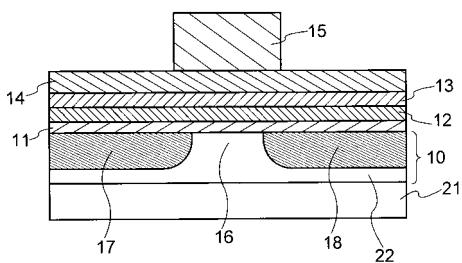

図1の不揮発性メモリトランジスタは、半導体基板に半導体領域が形成されているメモリ素子である。絶縁膜上の半導体膜を半導体領域とすることも可能である。図2に、このような半導体領域を有する不揮発性メモリトランジスタの断面図を示す。

30

## 【0046】

基板31には、ガラス基板、石英基板、サファイア基板、セラミック基板、ステンレス基板、金属基板などを用いることができる。また、基板31は不揮発性メモリトランジスタの製造時に用いた基板とは異なる基板でもよい。この場合、基板31にはプラスチックフィルムを用いることもできる。

## 【0047】

基板31上に下地絶縁膜32が形成され、下地絶縁膜32上に、半導体領域10となる半導体膜33が形成されている。下地絶縁膜32を形成することで、基板31側の半導体膜33の界面準位を良好にする、基板31からアルカリ金属などの汚染物質が半導体膜33に侵入することを防ぐことができる。下地絶縁膜32は形成しなくともよい。下地絶縁膜32は、酸化シリコン、窒化シリコン、酸化窒化シリコン等の絶縁材料の単層膜または積層膜で形成することができる。

40

## 【0048】

半導体膜33は結晶性半導体膜であり、非単結晶半導体膜の場合、多結晶半導体で形成されたものが好ましい。半導体材料としては、シリコンが好ましく、その他にシリコンゲルマニウム、およびゲルマニウムを用いることもできる。半導体膜の結晶化法としては、レーザ結晶化法、瞬間熱アニール(RTA)又はファーネスアニール炉を用いた熱処理による結晶化法、結晶化を助長する金属元素を用いる結晶化法又はこれら方法を組み合わせて行う方法を採用することができる。半導体膜33の形成方法の一例を説明する。下地絶

50

縁膜32上に、プラズマCVD法により非晶質シリコン膜を厚さ10nm～100nm形成する。次に、レーザ光を照射して、非晶質シリコン膜を結晶化し、多結晶シリコン膜を形成する。多結晶シリコン膜をエッチングして、所望の形状の半導体膜33を形成する。図2の場合、素子分離の目的から、半導体領域10は島状の半導体膜33に形成されている。

#### 【0049】

なお、図2の不揮発性メモリトランジスタにおいて、第1窒化シリコン膜12および第2窒化シリコン膜13と同じ形状に第1絶縁膜11を加工するのではなく、図13の不揮発性メモリトランジスタと同様に、第1絶縁膜11を半導体膜33を覆うように形成することもできる。

10

#### 【0050】

図2の不揮発性メモリトランジスタは半導体領域10を島状に分離することで形成される。このようにすることで、同一の基板上にメモリセルアレイとロジック回路を形成した場合にも、バルク状の半導体基板を用いるよりも効果的に素子分離をすることができる。すなわち、10V～20V程度の電圧で書き込みや消去を行う必要のあるメモリセルアレイと、3V～7V程度の電圧で動作してデータの入出力や命令の制御を主として行うロジック回路を同一基板上に形成した場合でも、各素子に印加する電圧の違いによる相互の干渉を防ぐことができる。

#### 【0051】

不揮発性メモリトランジスタの書き換え回数を多くするため第1絶縁膜11には高い絶縁耐圧性が求められる。しかしながら基板31が、ガラス基板のように、歪み温度が630～750程度と半導体基板21に比べて低い基板の場合、加熱温度が基板の歪み温度で制約される。そのため、第1絶縁膜11を熱酸化、熱窒化で形成しても、絶縁耐圧性にすぐれた膜を形成することが非常に困難である。また、第1絶縁膜11を基板の歪み点以下の加熱温度で、CVD法やスパッタ法により堆積することもできる。このような方法で形成した絶縁膜は、膜の内部に欠陥を含んでいるため絶縁耐圧性が十分でない。またCVD法やスパッタ法で1nm～10nm程度に薄く形成された絶縁膜は、ピンホール等の欠陥が生じやすい。また、CVD法やスパッタ法による成膜方法は、熱酸化などの成膜方法に比べて段差被覆性に劣る。

20

#### 【0052】

そのため、歪み温度が750以下の中板を用いる場合、高絶縁耐圧の第1絶縁膜11の形成には、プラズマによる固相酸化若しくは固相窒化を行うことが非常に好ましい。半導体（代表的にはシリコン）を、プラズマ処理により酸化又は窒化することにより形成された絶縁膜は、その形成時の加熱温度が500以下でも、緻密で絶縁耐圧が高く信頼性に優れた膜であるからである。

30

#### 【0053】

また、CVD法やスパッタ法により絶縁膜を堆積し、プラズマによりこの絶縁膜を固相酸化処理若しくは固相窒化処理することで、第1絶縁膜11を形成することで、その絶縁耐圧性を高めることができる。

#### 【0054】

40

プラズマ処理による固相酸化処理若しくは固相窒化処理として、マイクロ波（代表的な周波数は2.45GHz）で励起され、電子密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上 $1 \times 10^{13} \text{ cm}^{-3}$ 以下、且つ電子温度が0.5eV以上1.5eV以下の高密度プラズマを利用することが好ましい。高密度プラズマを用いることで、500以下の加熱温度で、実用的な反応速度で緻密な絶縁膜を形成することができるためである。つまり、マイクロ波を用いたプラズマ処理では、プラズマで励起した活性なラジカルを有効に使うことにより、基板加熱温度が500以下の低温で固相反応による酸化、窒化をすることができる。

#### 【0055】

この高密度プラズマ処理で酸化処理を行う場合には、酸素を組成に含むガス（例えば、酸素(O<sub>2</sub>)又は一酸化二窒素(N<sub>2</sub>O)）と共に、希ガス(He、Ne、Ar、Kr、

50

Xeの少なくとも一つを含む)導入して、酸素ラジカルを生成する。希ガスの励起種により酸素ラジカルを効率良く生成することができる。また、酸素を組成に含むガスと水素(H<sub>2</sub>)ガス、および希ガスを反応室に導入して、酸素ラジカル(OHラジカルを含む場合もある)を生成する。

#### 【0056】

また、高密度プラズマ処理により窒化処理を行う場合には、窒素(N<sub>2</sub>)と共に、希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)を反応室に導入して、窒素ラジカルを生成する。希ガスの励起種により窒素ラジカルを効率良く生成することができる。また、窒素ガスと共に水素ガスも反応室に導入することもできる。また、アンモニア(NH<sub>3</sub>)を反応室に導入して、窒素ラジカル(NHラジカルを含む)を生成することもできる。この場合、希ガスを反応室に導入することもできる。例えば、窒素とアルゴンを用いる場合、反応室に、窒素を流量20~2000sccmで、アルゴンを流量100~10000sccmで導入することが好ましい。例えば、窒素の流量を200sccmとし、アルゴンの流量を1000sccmとする。

10

#### 【0057】

高密度プラズマ処理による第1絶縁膜11の形成方法の一例を説明する。まず、酸素ラジカルを発生させる高密度プラズマ処理により半導体膜33を酸化して、3nm~6nmの厚さの酸化シリコン膜を形成する。次に、窒素ラジカルを発生させる高密度プラズマ処理により、この酸化シリコン膜を窒化する。高密度プラズマ処理を用いることによって、基板加熱温度が500以下でも、信頼性の高い第1絶縁膜11を形成することができる。これは、高密度プラズマ処理では、被形成面がプラズマに直接に曝されないこと、電子温度が低いことから、形成される膜にプラズマによる損傷が少ないためである。特に、酸化処理し、かかる後窒化処理を行うことで、不揮発性メモリトランジスタに適した第1絶縁膜11を形成することができる。

20

#### 【0058】

また、図2の不揮発性トランジスタにおいて、膜12~14を形成するのに、CVD法を用いる場合、実用的な成膜速度であること、および基板加熱温度を600以下とできることからプラズマCVD法を用いることが好ましい。また、プラズマCVD法を用いることで、基板加熱温度を500以下とすることも可能である。

#### 【0059】

30

以下、実験データを参照して、第1窒化シリコン膜12および第2窒化シリコン膜13の積層構造により、不揮発性メモリトランジスタの電荷保持特性が改善されることを説明する。合わせて、加熱温度が500以下の条件で、プラズマCVD法で形成された第1窒化シリコン膜12および第2窒化シリコン膜13により、電荷保持特性が改善されることを説明する。

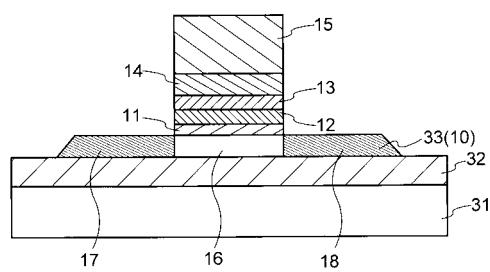

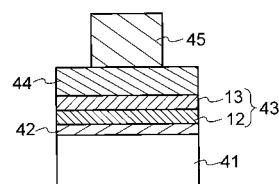

#### 【0060】

本発明の第1窒化シリコン膜12および第2窒化シリコン膜13を評価するために、シリコン基板を用いて、MOS型容量素子を作製した。図3は、作製した容量素子の断面図である。この容量素子を「素子1」と呼ぶことにする。素子1は、シリコン基板41上に、第1絶縁膜42、窒化シリコン層43、第2絶縁膜44、電極45の順に積層されている。シリコン基板41は、p型単結晶シリコン基板である。窒化シリコン層43は、第1窒化シリコン膜12と第2窒化シリコン膜13の2層構造である。素子1は、次のように作製した。

40

#### 【0061】

第1絶縁膜42を形成するため、まず、シリコン基板41の表面を、マイクロ波によりプラズマを生成するプラズマ処理により酸化し、酸化シリコン膜を形成した。この酸化プラズマ処理は、基板温度400、圧力106Paとし、Arガスを流量900sccm、O<sub>2</sub>ガスを流量5sccmで反応室に供給しながら、周波数2.45GHzのマイクロ波を反応室内に導入し、プラズマを励起させた。厚さ3nmの酸化シリコン膜が形成されるように、プラズマ処理の時間を調節した。

50

**【 0 0 6 2 】**

次に、この酸化シリコン膜をマイクロ波によりプラズマを生成するプラズマ処理により窒化した。この窒化プラズマ処理は以下のように行った。基板温度400<sup>10</sup>、反応圧力12Paとし、Arガスを流量1000sccmで、N<sub>2</sub>ガスを流量200sccmで反応室に供給しながら、周波数2.45GHzのマイクロ波を反応室内に導入し、プラズマを励起させた。また、プラズマ処理時間は90秒とした。以上的方法で第1絶縁膜42を形成した。

**【 0 0 6 3 】**

次に、第1絶縁膜42上に窒化シリコン層43を形成する。まず、第1絶縁膜42上に第1窒化シリコン膜12をプラズマCVD法で形成した。窒素ソースガスとしてNH<sub>3</sub>を用い、シリコンソースガスとしてSiH<sub>4</sub>を用いた。基板温度400<sup>10</sup>、反応圧力40Paとし、SiH<sub>4</sub>を流量2sccmで、NH<sub>3</sub>を流量400sccmで反応室に供給した。また、電極間距離を30mm、RFパワーを100Wとした。

**【 0 0 6 4 】**

次に、第1窒化シリコン膜12上に第2窒化シリコン膜13をプラズマCVD法で形成した。窒素ソースガスとしてN<sub>2</sub>を用い、シリコンソースガスとしてSiH<sub>4</sub>を用い、さらに、プロセスガスとして、N<sub>2</sub>の電離を促進するためArを用いた。SiH<sub>4</sub>を流量2sccmで、N<sub>2</sub>を流量400sccmで、Arを流量50sccmで反応室に供給した。また、第1窒化シリコン膜12の形成時と同じく、基板温度400<sup>20</sup>、反応圧力40Pa、電極間距離30mm、RFパワー100Wとした。

**【 0 0 6 5 】**

ここでは、第1窒化シリコン膜12と第2窒化シリコン膜をプラズマCVD装置の同じ反応室で、連続的に形成した。また、第1窒化シリコン膜12と第2窒化シリコン膜13の厚さは、それぞれ5nmとした。

**【 0 0 6 6 】**

次に、第2窒化シリコン膜13上に、第2絶縁膜44を形成した。ここでは、プラズマCVD法で、原料ガスにSiH<sub>4</sub>、N<sub>2</sub>Oを用いて、厚さ10nmの酸化窒化シリコン膜を形成した。次に、第2絶縁膜44上に、スパッタ装置により、厚さ400nmのAl-Ti合金膜を形成し、エッチングによりAl-Ti合金膜を所定の形状に加工して、電極45を形成した。以上により、素子1が完成した。

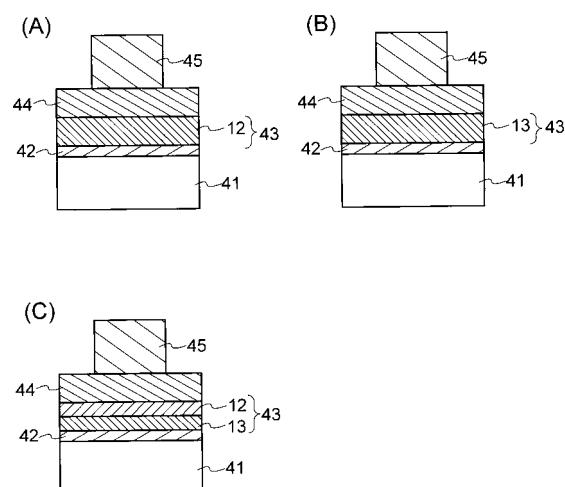

**【 0 0 6 7 】**

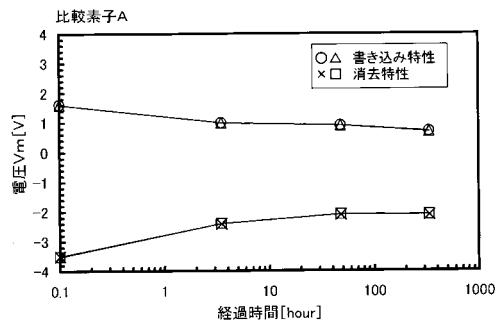

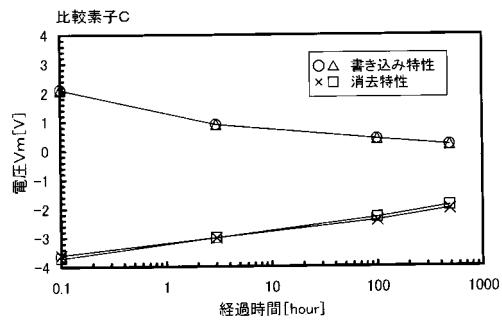

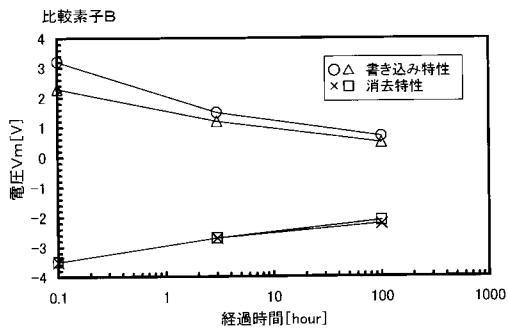

素子1との比較のため、3種類のMOS型容量素子を作製した。図4(A)～(C)は、これらの断面図である。図4(A)～(C)に示す容量素子をそれぞれ比較素子A、比較素子B、比較素子Cと呼ぶこととする。

**【 0 0 6 8 】**

比較素子A～Cは、素子1とは、窒化シリコン層43の構造のみが異なり、窒化シリコン層43の厚さは素子1と同じく10nmである。比較素子Aは、窒化シリコン層43が厚さ10nmの第1窒化シリコン膜12の単層膜である。比較素子Bは、窒化シリコン層43が厚さ10nmの第2窒化シリコン膜13の単層膜である。比較素子Cは、窒化シリコン層43の積層順序が素子1と逆であり、下層に厚さ5nmの第2窒化シリコン膜13が形成され、上層に厚さ5nmの第1窒化シリコン膜12が形成されている。

**【 0 0 6 9 】**

また、比較素子A～Cは、素子1と同じ方法で作製した。つまり、素子1の第1窒化シリコン膜12と、比較素子Aおよび比較素子Cの第1窒化シリコン膜12のとは同じ条件で形成した。素子1の第2窒化シリコン膜13と、比較素子Bおよび比較素子Cの第2窒化シリコン膜13は同じ条件で形成した。

**【 0 0 7 0 】**

各素子の窒化シリコン層43の電荷保持特性を評価するため、各素子の容量-電圧特性を測定した。測定は以下のように行った。データの書き込み後の電荷保持特性を評価するため、メタルハライドランプ光を照射しながら電極45に電圧17Vを10ミリ秒間印加

10

20

30

40

50

し、窒化シリコン層43に電子を注入した。なお、シリコン基板41がp型であるため、電子は少数キャリアである。そこで、メタルハライドランプ光をシリコン基板41に照射して、電子を誘起させている。しかる後、ホットプレートにより、シリコン基板41を150℃に加熱した状態を維持した。書き込み動作前、書き込み動作直後、書き込み動作後所定の時間経過後に、容量-電圧特性を測定した。

#### 【0071】

また、書き込んだデータを消去した後の電荷保持特性を評価するため、まず、上記と同じ書き込み動作を行った。次いで、消去動作を行うため、電極45に電圧-15Vを10ミリ秒間印加し、窒化シリコン層43にホールを注入した。しかる後、ホットプレートにより、シリコン基板41を150℃に加熱した状態を維持した。書き込み動作前、書き込み動作直後、消去動作直後、消去動作から所定の期間経過後に、容量-電圧特性を測定した。

10

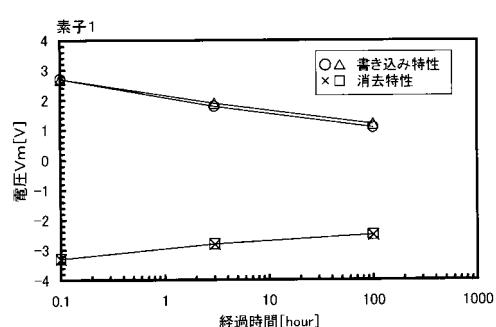

#### 【0072】

書き込み動作後の容量-電圧特性、および書き込みおよび消去動作後の容量-電圧特性から、素子1、および比較素子A～Cのリテンション特性を求めた。測定結果を図5～図8のグラフに示す。図5は素子1のリテンション特性である。また、図6、図7および図8には、それぞれ、比較素子A、B、およびCのリテンション特性を示す。図5～図8の横軸は、書き込み動作および消去動作からの経過時間を示す。なお、横軸の目盛が対数である都合、書き込み動作を行った時点、消去動作を行った時点を、それぞれ、0.1時間としている。縦軸の電圧Vmは、容量-電圧特性の測定結果から算出した電圧値であり、容量-電圧特性のグラフに対する接線のうち、その傾きが最大になる接線において、容量値が最大値の半値を取るときの電圧値である。

20

#### 【0073】

図5～図8のリテンション特性のグラフから、各素子の書き込み状態のしきい値電圧と、消去状態のしきい値電圧の差分（しきい値電圧ウインドウ）を求めた。表1に、各素子の保持期間1000時間のしきい値電圧ウインドウ（以下、「Vthウインドウ」と呼ぶ。）を示す。

ここでは、書き込み状態のしきい値電圧および消去状態のしきい値電圧は、それぞれ、書き込み特性の電圧Vmおよび消去特性の電圧Vmとし、経過時間1000時間の書き込み特性の電圧Vmと、経過時間1000時間の消去特性の電圧Vmとの差分から、保持期間1000時間のVthウインドウを求めた。

30

なお、1000時間後の書き込み特性の電圧Vmは、書き込み特性のグラフを外挿して算出した。他方、1000時間後の消去特性の電圧Vmは、消去動作から1000時間後に素子が初期状態（書き込み動作前）に戻ると仮定して、初期状態（経過時間0時間）の電圧Vmの値とした。なお、初期状態の書き込み特性の電圧Vmは、素子1、比較素子Aは約-0.8Vであり、比較素子B、Cは約-0.9Vである。

#### 【0074】

表1は、素子1のVthウインドウが最も大きいことを示している。また、表1は、窒化シリコン層43を単層の第1窒化シリコン膜12または第2窒化シリコン膜13で形成するよりも、素子1のような積層構造とすることで、電荷保持特性が向上することを示している。一方で、第1窒化シリコン膜12と第2窒化シリコン膜13の積層順序を素子1と逆にすると、単層構造の窒化シリコン層43よりも電荷保持特性が悪くなることが分かった。

40

#### 【0075】

## 【表1】

|       | V <sub>th</sub> ウィンドウ[V] |

|-------|--------------------------|

| 素子1   | 2.15                     |

| 比較素子A | 1.36                     |

| 比較素子B | 1.27                     |

| 比較素子C | 1.01                     |

## 【0076】

そこで、NH<sub>3</sub>を窒素ソースガスに用いた第1窒化シリコン膜12と、N<sub>2</sub>を窒素ソースガスに用いた第2窒化シリコン膜13の組成および組成比をラザフォード後方散乱分析法(RBS: Rutherford Backscattering Spectrometry)、および水素前方散乱分析法(HFS: Hydrogen Forward scattering Spectrometry)を用いて測定した。 10

## 【0077】

ここでは、反応ガス、流量が異なる3種類の第1窒化シリコン膜12、および2種類の第2窒化シリコン膜13を、それぞれ、単結晶シリコン基板上に厚さ100nm形成した。ここでは、3種類の第1窒化シリコン膜12を区別するため、窒化シリコン膜12-a、12-b、12-cと呼ぶことにし、2種類の第2窒化シリコン膜13を窒化シリコン膜13-a、13-bと呼ぶことにする。 20

## 【0078】

窒化シリコン膜12-a、12-b、12-c、13-aおよび13-bを形成するために用いたプロセスガスとその流量を表2に示す。

## 【0079】

比較のため、シリコンソースガスは全ての窒化シリコン膜でSiH<sub>4</sub>とし、その流量を2sccmとしている。窒化シリコン膜12-a、12-b、12-c、13-aおよび13-bはプラズマCVD法で形成され、成膜時に、基板温度400°C、反応圧力40Paとし、電極間距離を30mmとした。窒化シリコン膜12-aは、素子1、比較素子Aおよび比較素子Cの第1窒化シリコン膜12と同じ条件で成膜された膜である。また、窒化シリコン膜13-aは、素子1、比較素子Bおよび比較素子Cの第2窒化シリコン膜13と同じ条件で成膜された膜である。 30

## 【0080】

## 【表2】

| 窒化シリコン膜 | プロセスガスとその流量 [sccm] |                 |                |     |                |

|---------|--------------------|-----------------|----------------|-----|----------------|

|         | SiH <sub>4</sub>   | NH <sub>3</sub> | N <sub>2</sub> | Ar  | H <sub>2</sub> |

| 12-a    | 2                  | 400             |                |     |                |

| 12-b    | 2                  | 100             |                |     | 400            |

| 12-c    | 2                  | 100             |                | 400 |                |

| 13-a    | 2                  |                 | 400            | 50  |                |

| 13-b    | 2                  |                 | 100            | 400 |                |

## 【0081】

窒化シリコン膜12-a、12-b、12-c、13-aおよび13-bのRBSおよびHFSの測定結果を表3に示す。なお、酸素濃度は検出下限以下の値であった。

## 【0082】

【表3】

| 空化シリコン膜 | 濃度 [atomic%] |      |      | 組成比<br>Si/N | 密度                    |                   |

|---------|--------------|------|------|-------------|-----------------------|-------------------|

|         | H            | Si   | N    |             | atoms/cm <sup>3</sup> | g/cm <sup>3</sup> |

| 12-a    | 21.4         | 30.4 | 48.2 | 0.63        | $8.10 \times 10^{22}$ | 2.1               |

| 12-b    | 17.3         | 33.9 | 48.8 | 0.69        | $7.90 \times 10^{22}$ | 2.2               |

| 12-c    | 20.7         | 31.3 | 48.0 | 0.65        | $8.00 \times 10^{22}$ | 2.1               |

| 13-a    | 10.3         | 38.5 | 51.2 | 0.75        | $7.50 \times 10^{22}$ | 2.2               |

| 13-b    | 9.7          | 38.2 | 52.1 | 0.73        | $7.50 \times 10^{22}$ | 2.2               |

## 【0083】

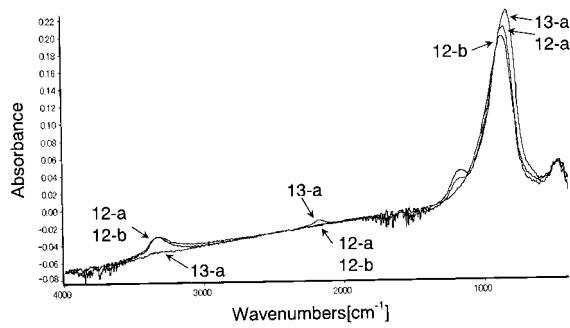

10

さらに、窒化シリコン膜12-a、12-bおよび13-aについて、FTIR（ Fourier Transform Infrared Spectroscopy）により、各膜を構成する元素の結合状態を分析した。図9は、窒化シリコン膜12-a、12-bおよび13-aのFTIRによる吸収スペクトルである。また、図9の吸収スペクトルからN-H結合およびSi-H結合の濃度を定量化した。その濃度を表4に示す。

## 【0084】

【表4】

| 窒化シリコン膜 | 濃度 [atoms/cm <sup>3</sup> ] |                       |                       | 濃度比<br>Si-H/N-H       |

|---------|-----------------------------|-----------------------|-----------------------|-----------------------|

|         | N-H                         | Si-H                  | N-H+Si-H              |                       |

| 12-a    | $9.10 \times 10^{21}$       | $2.00 \times 10^{20}$ | $9.30 \times 10^{21}$ | $2.20 \times 10^{-2}$ |

| 12-b    | $7.54 \times 10^{21}$       | $2.18 \times 10^{20}$ | $7.76 \times 10^{21}$ | $2.89 \times 10^{-2}$ |

| 13-a    | $2.29 \times 10^{21}$       | $3.25 \times 10^{21}$ | $5.54 \times 10^{21}$ | 1.42                  |

## 【0085】

表3および表4の測定データは、第2窒化シリコン膜13は、窒素の濃度が第1の窒化シリコン膜よりも高いが、N-H結合の濃度は第1の窒化シリコン膜12の方が高いことを示している。つまり、これらのデータは、水素と結合している状態の窒素をより多く含む第1窒化シリコン膜を下層に設けることで、素子1の電荷保持特性が向上することを示している。

30

## 【0086】

また、Si-H結合の濃度は第1窒化シリコン膜12の方が低く、第1窒化シリコン膜12のSi-H結合の濃度は、第2窒化シリコン膜13の1/10程度である。また、N-H結合の濃度に対するSi-H結合の濃度の比(Si-H/N-H)は、第2窒化シリコン膜13が第1窒化シリコン膜12の100倍程度となっている。従って、濃度比(Si-H/N-H)が高い窒化シリコン膜を上層に、つまり、チャネル形成領域から離れた側に形成すること、かつ、この濃度比が低い窒化シリコン膜をチャネル形成領域側に形成することで、素子1の電荷保持特性を向上することができる。

40

## 【0087】

また、表3の組成比Si/Nに着目すると、第2窒化シリコン膜13の方が第1窒化シリコン膜12よりも、化学量論的にSi<sub>3</sub>N<sub>4</sub>に近い膜となっている。

## 【0088】

なお、シリコンソースガスにハロゲンを含むガス(例えば、SiCl<sub>4</sub>、SiHCl<sub>3</sub>、SiH<sub>2</sub>Cl<sub>2</sub>、SiH<sub>3</sub>Cl<sub>3</sub>、SiF<sub>4</sub>など)を用いた場合は、窒化シリコン膜はSi-X結合(Xはハロゲン元素)を含むこととなる。Si-X結合の濃度は窒素ソースガスの種類に影響されるため、窒化シリコン膜を、そのSi-X結合の濃度が表4のSi-H結合と同様の傾向になるように形成することができる。

## 【0089】

従って、シリコンソースガスに水素又はハロゲンを含むガス(例えば、SiH<sub>4</sub>、Si

50

$\text{Cl}_4$ 、 $\text{SiF}_4\text{SiHCl}_3$ 、 $\text{SiH}_2\text{Cl}_2$ 、 $\text{SiH}_3\text{Cl}_3$ )を用いた場合は、 $\text{Si}-\text{X}$ 結合と $\text{Si}-\text{H}$ 結合濃度の和は、第2窒化シリコン膜13の方が高く、 $\text{N}-\text{H}$ 結合の濃度に対する $\text{Si}-\text{X}$ 結合と $\text{Si}-\text{H}$ 結合濃度の和の比( $\text{Si}-\text{H} + \text{Si}-\text{X} / \text{N}-\text{H}$ )は、第2窒化シリコン膜13の方が高くすることができる。

#### 【0090】

また、第1窒化シリコン膜12および第2窒化シリコン膜13のシリコンソースガスが共に、 $\text{SiCl}_4$ 、 $\text{SiF}_4$ のような組成にハロゲンを含み、かつ水素を含まないガスである場合は、 $\text{Si}-\text{X}$ 結合の濃度は、第2窒化シリコン膜13の方を高くすることができる。また、この場合、 $\text{N}-\text{H}$ 結合の濃度に対する $\text{Si}-\text{X}$ 結合の濃度の比( $\text{Si}-\text{X} / \text{N}-\text{H}$ )も、第2窒化シリコン膜13の方を高くすることができる。10

#### 【0091】

従って、 $\text{N}-\text{H}$ 結合をより多く含む第1窒化シリコン膜12をチャネル形成領域16側に設け、 $\text{N}-\text{H}$ 結合が少ない第2窒化シリコン膜13を導電膜15側に設けることで、不揮発性半導体メモリ素子の電荷保持特性を向上させることができる。

#### 【0092】

表2に示した第1窒化シリコン膜12と第2窒化シリコン膜13は、加熱温度を500以下とし、プラズマCVD法で形成した膜であり、これらの窒化シリコン膜は、ガラス基板のような、歪み温度が750以下の基板上に形成できる膜であることを付記する。20

#### 【0093】

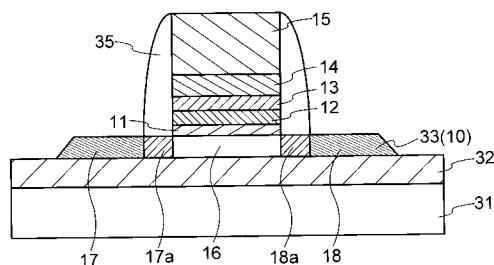

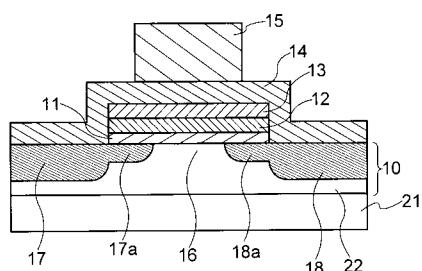

次に、図10～図17を用いて、図1、図2と異なる断面構造を有する不揮発性メモリトランジスタを説明する。図1、図2と同じ符号は、同じ構成要素を示し、その繰り返しの説明は省略する。20

#### 【0094】

図10、図11は、不揮発性メモリトランジスタの他の構成例を示す断面図である。図10、および図11の不揮発性メモリトランジスタには、第1絶縁膜11、第1窒化シリコン膜12、第2窒化シリコン膜13、第2絶縁膜14および導電膜15でなる積層膜の側壁に、絶縁膜でなるスペーサ35が形成されている。スペーサ35はサイドウォールとも呼ばれる。スペーサ35を形成することで、第2窒化シリコン膜13に蓄積されている電荷が導電膜15へ漏れることを防ぐ効果がある。また、このスペーサ35を利用して、チャネル形成領域16に隣接して、低濃度不純物領域17a、および低濃度不純物領域18aが自己整合的に形成することができる。30

#### 【0095】

低濃度不純物領域17a、および低濃度不純物領域18aは低濃度ドレイン(LDD)として機能する。低濃度不純物領域17a、18aを設けることにより、読み出し動作の繰り返しによる、第1絶縁膜11の劣化を抑制することができる。

#### 【0096】

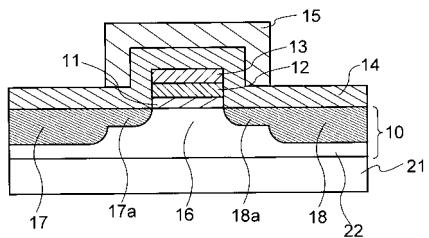

図12、図13は、不揮発性メモリトランジスタの他の構成例を示す断面図である。図12、図13に示す不揮発性メモリトランジスタは、第1絶縁膜11、第1窒化シリコン膜12、第2窒化シリコン膜13および第2絶縁膜14が、導電膜15と同じ形状に加工されていないことが、図1および図2と異なる点である。40

#### 【0097】

図12、図13の構造では、隣接するメモリトランジスタで、第1絶縁膜11、第1窒化シリコン膜12、および第2窒化シリコン膜13および第2絶縁膜14が高濃度不純物領域17、18を覆うように形成されている。この場合、作製プロセスにおいて、膜11～15をエッチングにより除去して、半導体領域10を露出させることがないため、半導体領域10に与えるダメージを軽減することが可能となる。また、膜11～15のエッチング工程が無いことからスループットを向上させることができる。

#### 【0098】

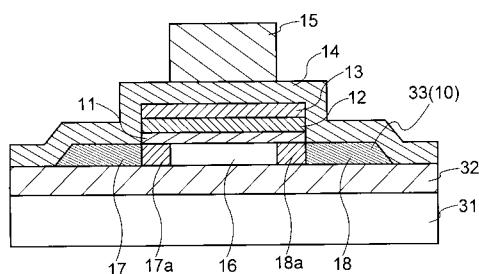

図14、図15は、不揮発性メモリトランジスタの他の構成例を示す断面図である。図14、図15の不揮発性メモリトランジスタは、第1絶縁膜11、第1窒化シリコン膜150

2 および第 2 室化シリコン膜 13 でなる積層膜のチャネル長方向の幅が、導電膜 15 よりも長くされている。第 2 絶縁膜 14 は、膜 11 ~ 13 でなる積層膜、および高濃度不純物領域 17、18 を覆うように形成されている。

#### 【 0 0 9 9 】

膜 11 ~ 13 でなる積層膜および導電膜 15 を図 14、図 15 のような構造とすることで、半導体領域 10 に、チャネル形成領域 16、高濃度不純物領域 17、18、および低濃度不純物領域 17a、18a を自己整合的に形成することができる。導電膜 15、および膜 11 ~ 13 でなる積層膜をマスクとして、n 型又は p 型の不純物を半導体領域 10 に添加することで、半導体領域 10 にチャネル形成領域 16、高濃度不純物領域 17、18、および低濃度不純物領域 17a、18a が自己整合的に形成される。そのため、第 1 絶縁膜 11、第 1 室化シリコン膜 12 および第 2 室化シリコン膜 13 は、低濃度不純物領域 17a、18a と重なる。

10

#### 【 0 1 0 0 】

なお、図 15において、第 1 室化シリコン膜 12 および第 2 室化シリコン膜 13 と同じ形状に、第 1 絶縁膜 11 を加工するのではなく、図 13 のように、第 1 絶縁膜 11 を半導体膜 33 を覆うように形成することもできる。

#### 【 0 1 0 1 】

図 16、図 17 は、不揮発性メモリトランジスタの他の構成例を示す断面図である。チャネル長方向の幅がチャネル長よりも長くなるように、導電膜 15 が形成されている。第 2 絶縁膜 14 は、第 1 室化シリコン膜 12 とおよび第 2 室化シリコン膜 13 を覆うよう形成されている。

20

#### 【 0 1 0 2 】

第 1 室化シリコン膜 12 と第 2 室化シリコン膜 13 膜および導電膜 15 を図 16、図 17 のような構造とすることで、半導体領域 10 に、チャネル形成領域 16、高濃度不純物領域 17、18、および低濃度不純物領域 17a、18a を自己整合的に形成することができる。

#### 【 0 1 0 3 】

半導体領域 10 上に、第 1 絶縁膜 11、第 1 室化シリコン膜 12、第 2 室化シリコン膜 13 および第 2 絶縁膜を図 16、図 17 に示すように形成する。導電膜 15 を形成する前に、第 1 室化シリコン膜 12 および第 2 室化シリコン膜 13 をマスクにして、n 型又は p 型の不純物を半導体領域 10 に低濃度に添加して、低濃度不純物領域を形成する。しかる後、図 16、図 17 のような構造の導電膜 15 を形成する。次に、導電膜 15 をマスクとして、半導体領域 10 に n 型又は p 型の不純物を高濃度に添加する。この不純物の添加工程により、半導体領域 10 に、チャネル形成領域 16、高濃度不純物領域 17、18、および低濃度不純物領域 17a、18a が自己整合的に形成される。

30

#### 【 0 1 0 4 】

なお、図 17 の不揮発性メモリトランジスタにおいて、第 1 室化シリコン膜 12 および第 2 室化シリコン膜 13 と同じ形状に第 1 絶縁膜 11 を加工するのではなく、図 13 のように、第 1 絶縁膜 11 を半導体膜 33 を覆うように形成することもできる。

#### 【 0 1 0 5 】

図 1、図 10、図 12、図 14、および図 17において、半導体基板 21 として、バルク状の単結晶又は多結晶シリコン基板（シリコンウェハー）、単結晶または多結晶シリコングルマニウム基板、単結晶または多結晶ゲルマニウム基板を用いることができる。また、S O I ( S i - O n - I n s u l a t o r ) 基板を用いることもできる。S O I 基板として、鏡面研磨ウェハーに酸素イオンを注入した後、高温アニールすることにより、表面から一定の深さに酸化層を形成させるとともに、表面層に生じた欠陥を消滅させて作られた所謂 S I M O X ( S e p a r a t i o n b y I M p l a n t e d O X y g e n ) 基板を用いることができる。また、S O I 基板を用いた場合は、基板中に形成された酸化層上の薄いシリコン層に半導体領域 10 が形成され、ウェル 22 を形成しなくとも、素子分離をすることができる。また、S O I 基板と同様に、S G O I ( S i l i c o n - G e

40

ermanium on Insulator) 基板又はGOI(Germanium on Insulator)基板を用いることもできる。

#### 【0106】

また、図1、図2および図10～図17を参照して、不揮発性半導体メモリ素子の例として、MONOS型の不揮発性メモリトランジスタを説明したが、MNOS構造の不揮発性メモリトランジスタを本発明の不揮発性半導体メモリ素子に適用することもできる。図1、図2および図10～図17のMONOS型不揮発性メモリトランジスタにおいて、第2絶縁膜14を形成せず、第2窒化シリコン膜13上に接して導電膜15を形成することで、MNOS構造の不揮発性メモリトランジスタを作製することができる。

#### 【0107】

(実施の形態2)

本実施の形態では、本発明に係る半導体装置として、不揮発性半導体記憶装置について説明する。

#### 【0108】

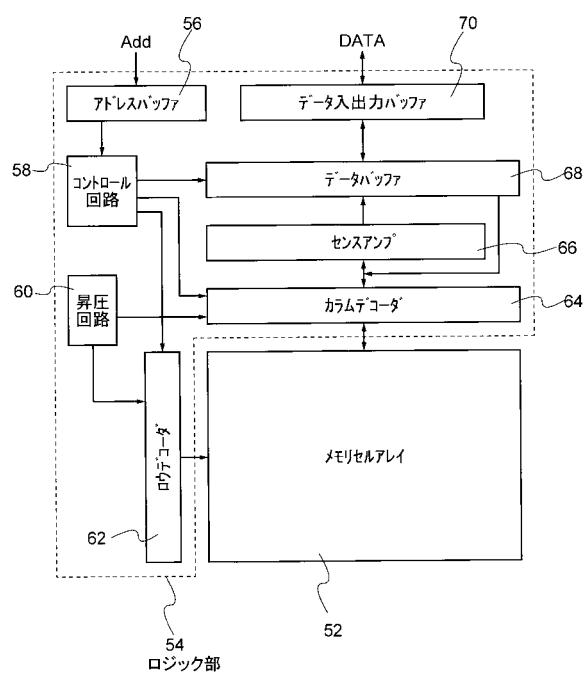

図18は、不揮発性半導体記憶装置の構成例を示すブロック図である。図18の不揮発性半導体記憶装置は、メモリセルアレイ52と、メモリセルアレイ52に接続され、書き込み動作、消去動作および読み出し動作などを制御するロジック部54が同一の基板上に形成されている。メモリセルアレイ52は、複数のワード線WLと、ワード線WLと交差して形成された複数のビット線BL、およびワード線WLおよびビット線BLに接続された複数のメモリセルMCを有する。メモリセルMCのデータの蓄積手段として、実施の形態1で説明した不揮発性メモリトランジスタが用いられる。そのため、電荷保持特性に優れ、信頼性の高い不揮発性半導体記憶装置を得ることができる。

#### 【0109】

ロジック部54の構成は以下の通りである。ワード線選択のためにロウデコーダ62と、ビット線選択のためにカラムデコーダ64が、メモリセルアレイ52の周囲に設けられている。アドレスは、アドレスバッファ56を介してコントロール回路58に送られ、内部ロウアドレス信号および内部カラムアドレス信号がそれぞれロウデコーダ62およびカラムデコーダ64に転送される。

#### 【0110】

データ書き込みおよび消去には、電源電位を昇圧した電位が用いられる。このため、コントロール回路58により動作モードに応じて制御される昇圧回路60が設けられている。昇圧回路60の出力はロウデコーダ62やカラムデコーダ64を介して、メモリセルアレイ52に形成されているワード線WLやビット線BLに供給される。センスアンプ66はカラムデコーダ64から出力されたデータが入力される。センスアンプ66により読み出されたデータは、データバッファ68に保持され、コントロール回路58からの制御により、データがランダムアクセスされ、データ出入力バッファ70を介して出力されるようになっている。書き込みデータは、データ出入力バッファ70を介してデータバッファ68に一旦保持され、コントロール回路58の制御によりカラムデコーダ64に転送される。

#### 【0111】

メモリセルアレイ52では、電源電位とは異なる電位を用いる必要がある。そのため、少なくともメモリセルアレイ52とロジック部54の間は、電気的に絶縁分離されていることが望ましい。実施の形態3乃至実施の形態6で説明するように、不揮発性メモリ素子および周辺回路のトランジスタを絶縁膜上に形成した半導体膜で形成することにより、容易に絶縁分離をすることができる。それにより、誤動作を無くし、消費電力の低い不揮発性半導体記憶装置を得ることができる。

#### 【0112】

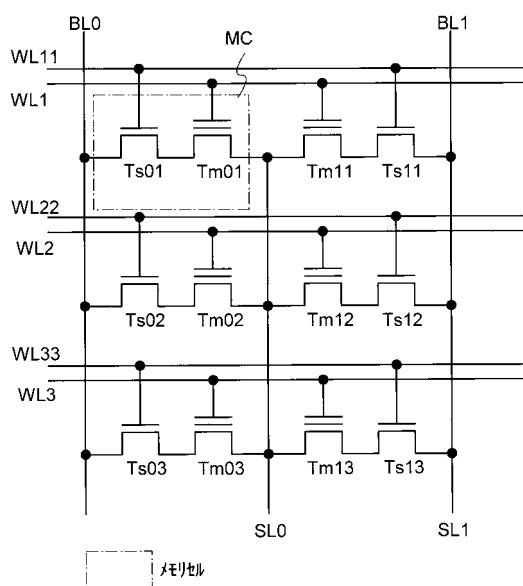

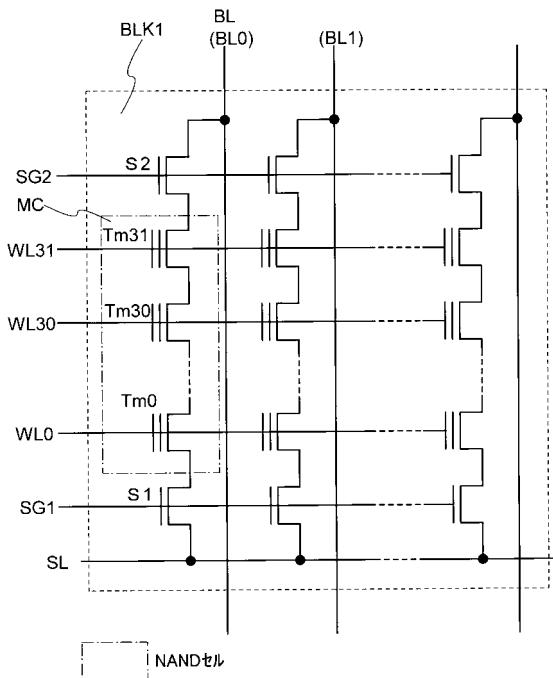

以下、図19～図21を用いて、メモリセルアレイの構成例を説明する。図19は、メモリセルアレイ52の構成例を示す回路図である。メモリセルMCが行列状に配置されている。図19では、3行×2列のメモリセルMCを示している。各メモリセルMCは1ビ

10

20

30

40

50

ットの情報を記憶し、直列に接続されたスイッチング用トランジスタT<sub>s</sub>、不揮発性メモリトランジスタT<sub>m</sub>を有する。メモリセルアレイ52は、列ごとに、ビット線B<sub>L</sub>0、B<sub>L</sub>1、ソース線S<sub>L</sub>0、S<sub>L</sub>1が設けられている。また、行ごとに、第1ワード線W<sub>L</sub>1～W<sub>L</sub>3および第2ワード線W<sub>L</sub>11～W<sub>L</sub>13が設けられている。

#### 【0113】

ビット線B<sub>L</sub>0および第1ワード線W<sub>L</sub>1で特定されるメモリセルMCに着目すると、スイッチング用トランジスタT<sub>s</sub>01は、ゲートが第2ワード線W<sub>L</sub>11に接続され、ソースまたはドレインの一方がビット線B<sub>L</sub>0に接続され、他方が不揮発性メモリトランジスタT<sub>m</sub>01に接続されている。不揮発性メモリトランジスタT<sub>m</sub>01は、ゲートが第1ワード線W<sub>L</sub>1に接続され、ソースまたはドレインの一方がスイッチング用トランジスタT<sub>s</sub>01に接続され、他方がソース線S<sub>L</sub>0に接続されている。

10

#### 【0114】

スイッチング用トランジスタT<sub>s</sub>と不揮発性メモリトランジスタT<sub>m</sub>（以下、「メモリトランジスタT<sub>m</sub>」と呼ぶこともある。）と共にnチャネル型とした場合、ビット線B<sub>L</sub>0および第1ワード線W<sub>L</sub>1で特定されるメモリセルMCにデータを書き込むには、第2ワード線W<sub>L</sub>11とビット線B<sub>L</sub>0の電位をハイレベル（以下、「Hレベル」とよぶ。）、ビット線B<sub>L</sub>1の電位をロウレベル（以下、「Lレベル」とよぶ。）として、第2ワード線W<sub>L</sub>11に高電圧を印加する。これにより、不揮発性メモリトランジスタT<sub>m</sub>01の電荷蓄積層に電荷が注入される。不揮発性メモリトランジスタT<sub>m</sub>01からデータを消去するには、第1ワード線W<sub>L</sub>1およびビット線B<sub>L</sub>0の電位をHレベルとし、第2ワード線W<sub>L</sub>11に負の高電圧を印加する。

20

#### 【0115】

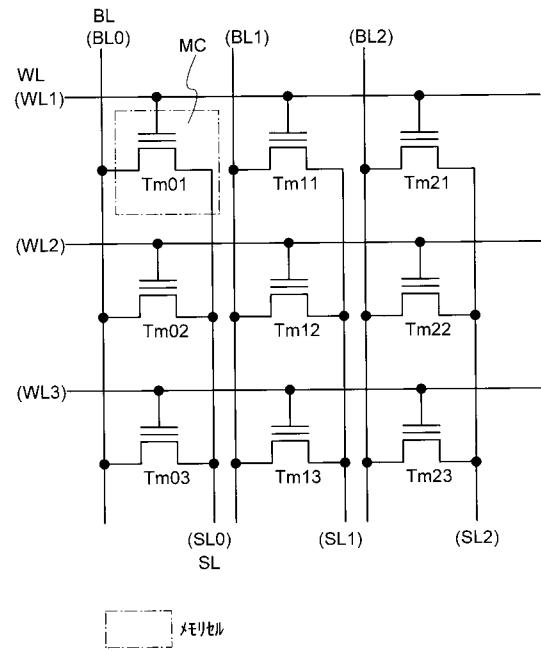

図20は、メモリセルアレイ52の他の構成例を示す回路図である。図20において、メモリセルMCは、スイッチング用トランジスタT<sub>s</sub>がなく、不揮発性メモリトランジスタT<sub>m</sub>のソースまたはドレインの一方がスイッチング素子を介さずに、ビット線B<sub>L</sub>に電気的に接続している点が、図19と異なる。そのため、図20のメモリセルアレイ52では、第2ワード線W<sub>L</sub>11、W<sub>L</sub>22、W<sub>L</sub>33を設けていない。

#### 【0116】

不揮発性メモリトランジスタT<sub>m</sub>を共にnチャネル型とした場合、ビット線B<sub>L</sub>0および第1ワード線W<sub>L</sub>1で特定されるメモリセルMCへのデータ書き込みの一例は、次の通りである。ソース線S<sub>L</sub>の電位をLレベル（例えば0V）とし、第1ワード線W<sub>L</sub>1に高電圧を与え、ビット線B<sub>L</sub>にはデータ”0”又は”1”に応じた電位を与える。例えば、”0”と”1”に対して、ビット線B<sub>L</sub>の電位をHレベル、Lレベルの電位にする。”0”データを書き込むため、ドレインにHレベルの電位が与えられた不揮発性メモリトランジスタT<sub>m</sub>01ではドレイン近傍でホットエレクトロンが発生し、これが電荷蓄積層に注入される。つまりF-Nトンネル電流により、電荷蓄積層に電子が注入される。”1”データを書き込む場合この様な電子注入は生じない。

30

#### 【0117】

”0”データが与えられたメモリセルMCでは、ドレインとソースとの間の強い横方向電界により、ドレインの近傍でホットエレクトロンが生成され、これが電荷蓄積層に注入される。これにより、電荷蓄積層に電子が注入されることで、しきい値電圧が高くなった状態が”0”である。”1”データの場合はホットエレクトロンが生成されず、電荷蓄積層に電子が注入されずしきい値電圧の低い状態が保持される。すなわち消去状態が保持される。

40

#### 【0118】

データを消去するときは、ソース線S<sub>L</sub>0の電位を正の高電位（例えば、10V程度の正電位）とし、ビット線B<sub>L</sub>0は浮遊状態とする。そして第1ワード線W<sub>L</sub>1の電位を負の高電位とする。このことにより、不揮発性メモリトランジスタT<sub>m</sub>01の電荷蓄積層から電子が、半導体領域に引き抜かれる。これにより、データ”1”的消去状態になる。

#### 【0119】

10

20

30

40

50

データの読み出しは、例えば、次のように行う。ソース線 S L 0 の電位を 0 V、ビット線 B L 0 の電位を 0 . 8 V 程度とし、第 1 ワード線 W L 1 の電位に、データ " 0 " と " 1 " に相当するしきい値電圧の中間値に設定された読み出し電位を与える。この時、不揮発性メモリトランジスタ T m からビット線 B L 0 に流れる電流の有無を、ビット線 B L 0 に接続されるセンスアンプ 6 6 で判定する。

#### 【 0 1 2 0 】

図 2 1 は、メモリセルアレイ 5 2 の他の構成例を示す回路図である。図 2 1 は、メモリセル M C を N A N D 型のメモリセルとした等価回路を示す。複数の N A N D セルが集まってブロック B L K 1 を構成している。図 2 1 で示すブロック B L K 1 のワード線は 3 2 本である（ワード線 W L 0 ~ W L 3 1 ）。メモリセル M C は直列に接続された複数の不揮発性メモリトランジスタ T m でなる。10

#### 【 0 1 2 1 】

ビット線 B L 0 で特定される 1 つのメモリセル M C において、不揮発性メモリトランジスタ T m 0 ~ T m 3 1 のゲートは、それぞれ、互いに異なる第 1 ワード線 W L 0 ~ W L 3 1 に接続され、第 1 行目の不揮発性メモリトランジスタ T m 0 のソース又はドレインには第 1 選択トランジスタ S 1 が接続され、第 3 2 行目の不揮発性メモリトランジスタ T m 3 1 には第 2 選択トランジスタ S 2 が接続されている。第 1 選択トランジスタ S 1 は、第 1 選択ゲート線 S G 1 およびビット線 B L 0 に接続され、第 2 選択トランジスタ S 2 は、第 2 選択ゲート線 S G 2 およびビット線 B L 0 に接続されている。20

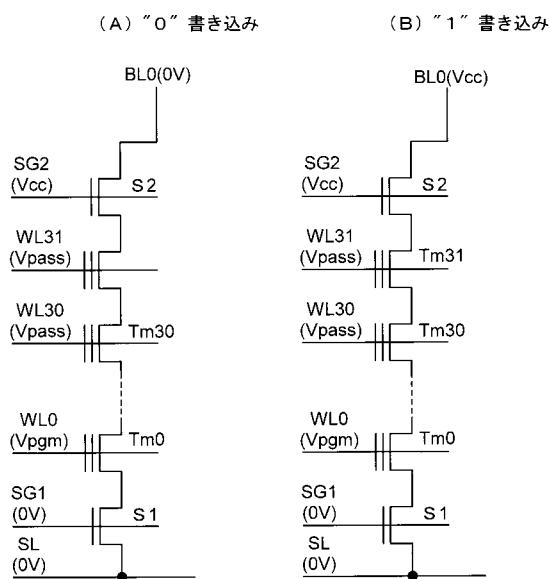

#### 【 0 1 2 2 】

ここでは、不揮発性メモリトランジスタ T m 0 ~ T m 3 1 、第 1 選択トランジスタ S 1 、および第 2 選択トランジスタ S 2 が、n チャネル型として、書き込み動作および消去動作を説明する。N A N D 型のメモリセルでは、メモリセル M C を消去状態にしてから、書き込み動作を行う。消去状態とは、メモリセル M C の各メモリトランジスタ T m 0 ~ T m 3 1 のしきい値電圧が負電圧値である状態をいう。20

#### 【 0 1 2 3 】

図 2 2 ( A ) は、図 2 1 のメモリトランジスタ T m 0 に " 0 " を書き込む動作の一例を説明する回路図であり、図 2 2 ( B ) は、" 1 " を書き込む動作の一例を説明する回路図である。" 0 " を書き込むには、ビット線 B L 0 を 0 V ( 接地電位 ) にして、第 2 選択ゲート線 S G 2 に例えば V c c ( 電源電位 ) を印加し第 2 選択トランジスタ S 2 をオン状態にする。他方、第 1 選択ゲート線 S G 1 は 0 V にして、第 1 選択トランジスタ S 1 はオフ状態にする。次に、ワード線 W L 0 の電位を高電位 V p g m ( 2 0 V 程度 ) にし、その他のワード線の電位を中間電位 V p a s s ( 1 0 V 程度 ) にする。ビット線 B L 0 の電位は 0 V なので、選択されたメモリセル M 0 のチャネル形成領域の電位は 0 V となる。ワード線 W L 0 とチャネル形成領域との電位差が大きいため、不揮発性メモリトランジスタ T m 0 の電荷蓄積層には F - N トンネル電流により電子が注入される。これにより、不揮発性メモリトランジスタ T m 0 のしきい値電圧が正電圧となり、" 0 " が書き込まれた状態となる。30

#### 【 0 1 2 4 】

不揮発性メモリトランジスタ T m 0 に " 1 " を書き込む場合は、図 2 2 ( B ) に示すように、ビット線 B L 0 の電位を例えば電源電位 V c c にする。第 2 選択ゲート線 S G 2 の電位が V c c であるため、第 2 選択トランジスタ S 2 がカットオフする。従って、不揮発性メモリトランジスタ T m 0 のチャネル形成領域はフローティング状態となる。次に、ワード線 W L 0 の電位を正の高電位である書き込み電位 V p g m ( 2 0 V ) とし、それ以外のワード線 W L の電位を中間電位 V p a s s ( 1 0 V ) とする。各ワード線 W L 0 ~ W L 3 1 と、とチャネル形成領域との容量カップリングにより、チャネル形成領域の電圧が V c c - V t h よりも高くなり、例えば 8 V 程度となる。そのため、ワード線 W L 0 とチャネル形成領域の電位差が小さくなる。したがって、メモリトランジスタ T m 0 の浮遊ゲートには、F - N トンネル電流による電子注入が起こらない。よって、不揮発性メモリトランジスタ T m 0 のしきい値電圧値は負の電圧値をとり、" 1 " が書き込まれた状態になる4050

。

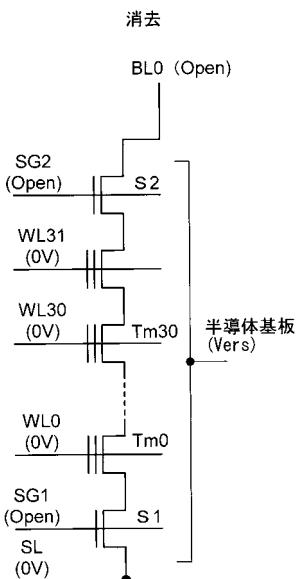

**【0125】**

図23は、消去動作の一例を説明する回路図である。図21のメモリセルアレイ52では、同じブロックBLK1に含まれる複数の不揮発性メモリトランジスタTmのデータが同時に消去される。図23に示すように、選択されたブロック全てのワード線WL0～WL31の電位を0Vにし、半導体基板のp型ウェルの電位を負の高電位である消去電位V<sub>ers</sub>にし、ビット線BL、ソース線SLの電位をフローティング状態にする。これにより、ブロックBLK1に含まれる全てのメモリトランジスタTmの電荷蓄積層から、電子がトンネル電流により半導体基板に放出され、メモリトランジスタTmのしきい値電圧が負方向にシフトする。

10

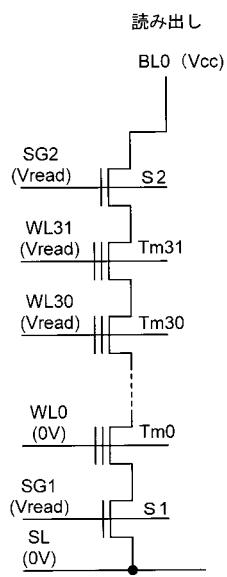

**【0126】**

図24は、図21のメモリトランジスタTm0からデータを読み出すための読み出し動作の一例を説明する回路図である。読み出し動作では、第1ワード線WL0の電位を読み出し電位V<sub>r</sub>（例えば0V）とし、非選択のメモリセルのワード線WL1～31および選択ゲート線SG1、SG2を電源電位V<sub>cc</sub>より少し高い読み出し用中間電位V<sub>read</sub>とする。この結果、メモリトランジスタTm0以外のメモリトランジスタTm1～Tm31はトランスファートランジスタとして機能し、図18のセンスアンプ66において、ビット線BL0に流れる電流を検出することで、メモリトランジスタTm0に電流が流れるか否かを検出することができる。メモリトランジスタTm0に記憶されたデータが”0”の場合、メモリトランジスタTm0はオフ状態であるので、ビット線BL0に電流が流れない。一方、”1”的場合、メモリトランジスタTm0はオン状態であるので、ビット線BL0に電流が流れる。

20

**【0127】**

本実施の形態の不揮発性半導体記憶装置は、電荷保持特性が向上された不揮発性半導体メモリ素子を有することで、記憶性能の信頼性が向上される。

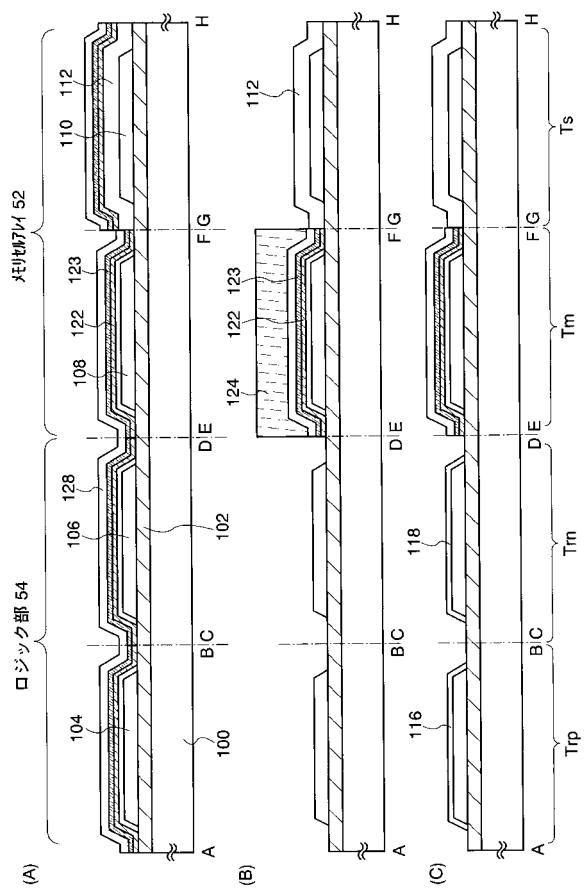

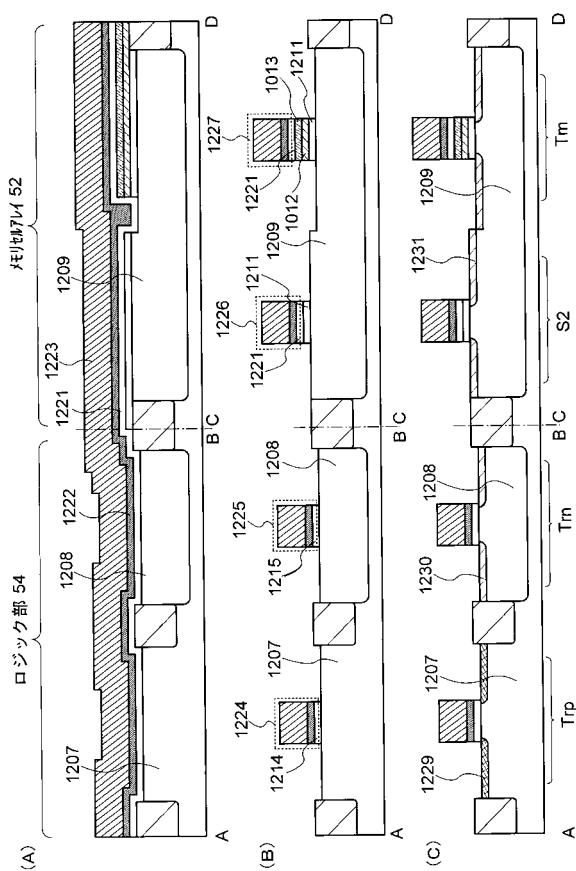

**【0128】****(実施の形態3)**

本実施の形態では、半導体装置の作製方法として、不揮発性半導体記憶装置の作製方法について説明する。不揮発性半導体記憶装置において、メモリセルアレイのトランジスタは、ロジック部のトランジスタと比較して駆動電圧が高いため、メモリセルアレイのトランジスタとロジック部のトランジスタは、それぞれ、駆動電圧によって構造を変えることが好ましい。例えば、駆動電圧が小さく、しきい値電圧値のばらつきを小さくしたい場合にはゲート絶縁膜を薄くすることが好ましい。駆動電圧が大きくゲート絶縁膜の絶縁耐圧性が求められる場合にはゲート絶縁膜を厚くすることが好ましい。

30

**【0129】**

そこで、本実施の形態では、ゲート絶縁膜の厚さが異なるトランジスタを同一基板上に作製する方法を説明する。また、本実施の形態では、トランジスタおよび不揮発性メモリトランジスタを薄膜トランジスタで作製する方法を説明する。また、本実施の形態では、不揮発性半導体記憶装置として図18の装置を例に、またそのメモリセルアレイ52を図19に示す回路で構成した場合を例に、不揮発性半導体装置の作製方法を説明する。後述する実施の形態4乃至8の不揮発性半導体記憶装置もこの点は同様である。

40

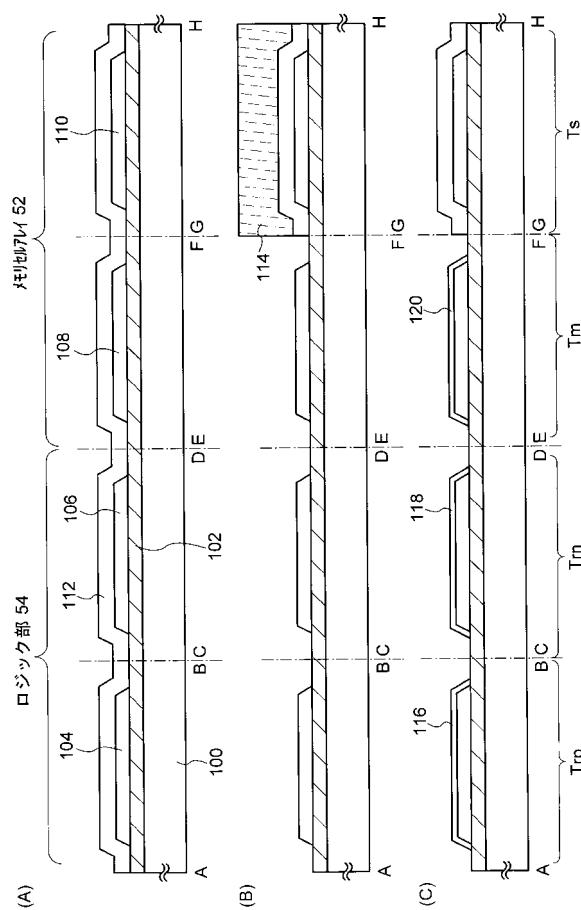

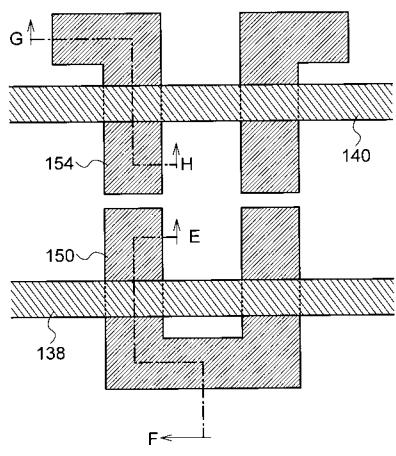

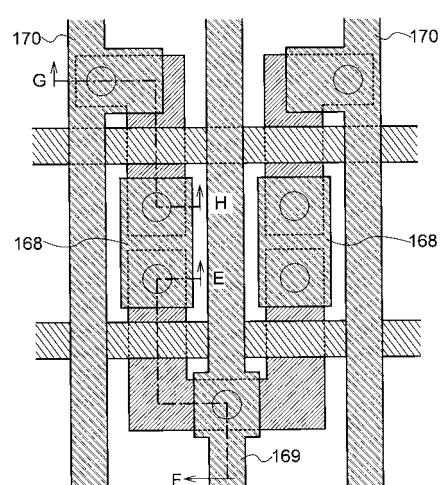

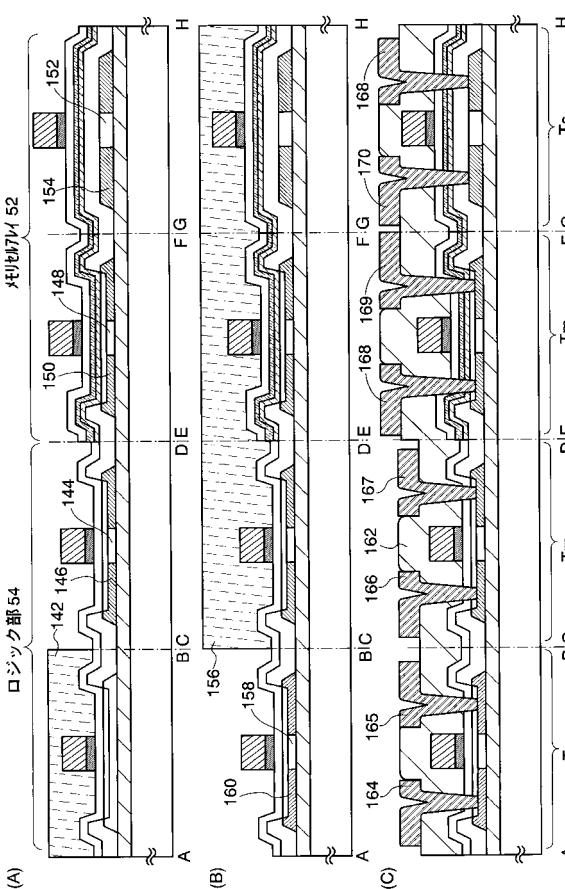

**【0130】**

図25～図28は、本実施の形態の作製工程を説明するための断面図である。図25～図28において、A-B間にロジック部54に設けられるpチャネル型トランジスタTr<sub>p</sub>の断面を示し、およびC-D間にロジック部54に設けられるnチャネル型トランジスタTr<sub>n</sub>の断面を示す。また、E-F間にメモリセルMCに設けられる不揮発性メモリトランジスタTmの断面を示し、G-H間にメモリセルMCのスイッチング用トランジスタTsの断面を示す。また、図29～図31は、本実施の形態の作製工程を説明するための上面図である。図29～図31の一点鎖線A-B、C-D、E-FおよびG-Hで切った断面図が、図25～図28に対応する。

50

## 【0131】

まず、図25(A)に示すように、基板100上に下地絶縁膜102を形成する。基板100は、ガラス基板、石英基板、金属基板(例えばセラミック基板またはステンレス基板など)を用いることができる。下地絶縁膜102は、CVD法やスパッタ法等を用いて、酸化シリコン、窒化シリコン、酸化窒化シリコン等の絶縁材料を用いて形成することができる。例えば、下地絶縁膜102を2層構造とする場合、第1層目の絶縁層として、窒素濃度が酸素濃度よりも高い酸化窒化シリコン(SiO<sub>x</sub>N<sub>y</sub>、x < y)層を形成し、第2層目の絶縁層として酸素濃度が窒素濃度よりも高い酸化窒化シリコン層(SiO<sub>x</sub>N<sub>y</sub>、x > y)を形成するとよい。また、第1層目の絶縁層として窒化シリコン層を形成し、第2層目の絶縁層として酸化シリコン層を形成してもよい。このように、ブロッキング層として機能する下地絶縁膜102を形成することによって、基板100からNaなどのアルカリ金属やアルカリ土類金属が、この上に形成する素子に悪影響を与えることを防ぐことができる。10

## 【0132】

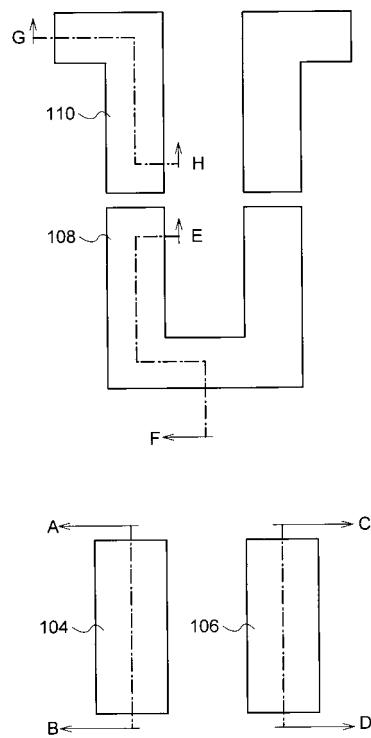

次に、下地絶縁膜102上に、島状の半導体膜104、106、108、110を形成する。図29が島状の半導体膜104、106、108、110の上面図である。島状の半導体膜104、106、108、110の形成は、次の通りに行うことができる。スパッタ法、LPCVD法、プラズマCVD法等を用いて、シリコン(Si)を主成分とする非晶質半導体膜を形成し、非晶質半導体膜を結晶化させて、結晶性半導体膜を形成する。結晶性半導体膜をエッチングして、島状の半導体膜104、106、108、110を形成する。なお、非晶質半導体膜として、非晶質シリコン膜、非晶質ゲルマニウムまたは非晶質シリコンゲルマニウム膜などを形成することができる。また非晶質半導体膜の結晶化は、レーザ結晶化法、RTA又はファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法またはこれら方法を組み合わせた方法等により行うことができる。20

## 【0133】

また、基板100として、SOI基板を用いることもできる。この場合、SOI基板の半導体層を、エッチングして、島状の半導体膜104、106、108、110を形成することができる。または、半導体層を部分的に酸化して、酸化させない領域を島状の半導体膜104、106、108、110とすることができる。SOI基板の代わりに、GOI基板、SGOI基板を用いることもできる。30

## 【0134】

次に、図25(A)に示すように、島状の半導体膜104、106、108、110を覆うように絶縁膜112を形成する。絶縁膜112は、LPCVD法、プラズマCVD法により、酸化シリコン、窒化シリコン、酸化窒化シリコンでなる単層膜または2層以上の多層膜で形成される。絶縁膜112は、メモリセルMCのトランジスタTsのゲート絶縁膜として機能する。そのため、10nm~50nmの厚さに形成される。

## 【0135】

次に、図25(B)に示すように、絶縁膜112を選択的に除去し、半導体膜104、106、108の表面を露出させる。ここでは、メモリ部に設けられた半導体膜110を選択的にレジスト114で覆い、半導体膜104、106、108上に形成された、絶縁膜112をエッチングすることによって除去する。40

## 【0136】

レジスト114を除去し、図25(C)に示すように、半導体膜104、106、108上に絶縁膜116、118、120をそれぞれ形成する。絶縁膜120はメモリトランジスタTmの第1絶縁膜を構成する。絶縁膜116、118、120の厚さは、1~10nmが好ましく、1~5nmがより好ましい。なお、絶縁膜116、および118は後の工程で除去される。

## 【0137】

絶縁膜116、118、120は、半導体膜104、106、108を熱処理又は高密50

度プラズマ処理等によって形成することができる。例えば、図2の不揮発性メモリトランジスタの第1絶縁膜111と同様に、高密度プラズマ処理により、半導体膜104、106、108に酸化処理、窒化処理又は酸化窒化処理を行うことによって、半導体の酸化物、窒化物又は酸化窒化物でなる絶縁膜116、118、120を形成する。半導体膜104、106、108がシリコン膜でなる場合、高密度プラズマ処理により半導体膜104、106、108の酸化処理、窒化処理、酸化窒化処理を行った場合、それぞれ、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層を形成することができる。また、酸化処理を行って酸化シリコン層を形成した後に、窒化処理を行うこともできる。この場合、窒化処理時間などを調節することにより、表層が窒化された酸化シリコン層、酸化窒化シリコン層、または窒化シリコン層を形成することができる。

10

## 【0138】

ここでは、まず、反応室内に酸素( $O_2$ )とアルゴン(Ar)との混合ガスを導入し、高密度プラズマにより酸素ラジカルを発生させて、半導体膜104、106、108に酸化処理を行い、半導体膜104、106、108の表面に3nm～6nm程度の厚さの酸化シリコン層を形成する。プロセスガスの流量は、酸素は0.1～100sccm、アルゴンは100～500sccmとすることができる。

## 【0139】

続けて、酸化処理を行った反応室内に、窒素( $N_2$ )とアルゴン(Ar)との混合ガスを導入し、高密度プラズマにより窒素ラジカルを発生させて、酸化シリコン層を窒化処理する。例えば、窒化処理時間を調節することで、窒素濃度が20～50atomic%程度の厚さ1nm程度の層を酸化シリコン層に形成することができる。また、この際に、半導体膜110上に形成された絶縁膜112の表面も酸化又は窒化され、酸化窒化シリコン層が形成される場合がある。プロセスガスの流量は、窒素は20～2000sccm、アルゴンは100～1000sccmとすることができる。

20

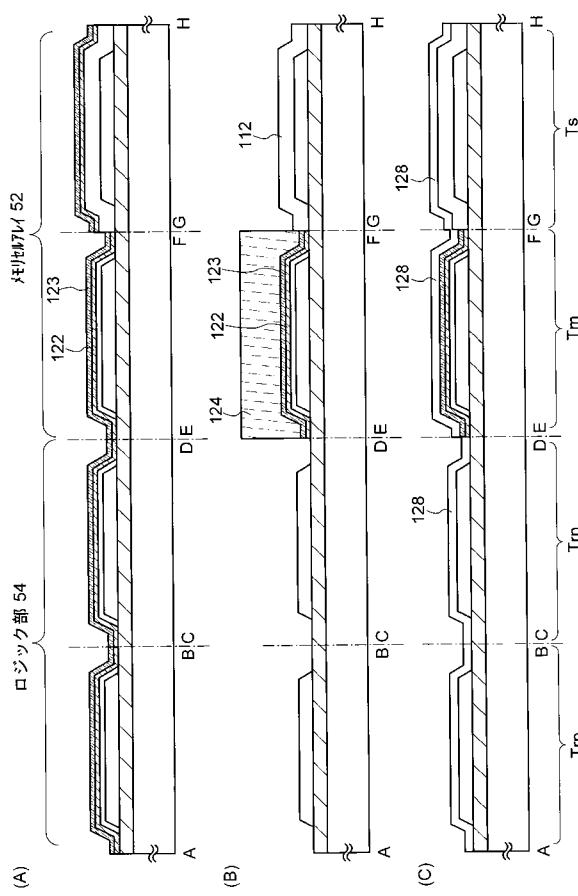

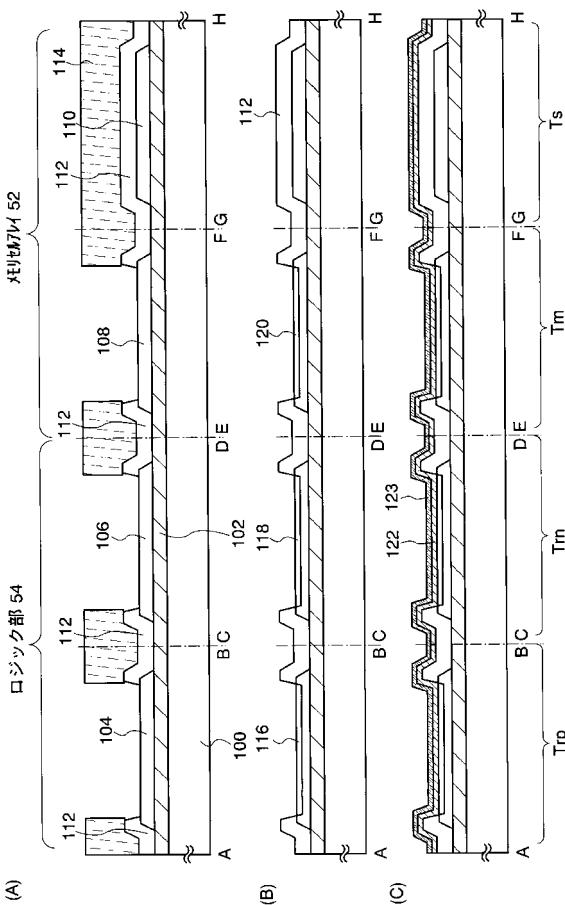

## 【0140】

次に、図26(A)に示すように、絶縁膜112、絶縁膜116、118、120を覆うように電荷蓄積層となる第1窒化シリコン膜122、および第2窒化シリコン膜123を形成する。第1窒化シリコン膜122は実施の形態1の第1窒化シリコン膜12と同様に形成することができ、第2窒化シリコン膜123は実施の形態1の第2窒化シリコン膜13と同様に形成することができる。例えば、プラズマCVD装置の反応室に、 $NH_3$ および $SiH_4$ を導入し、基板温度400で第1窒化シリコン膜122を形成する。同じ反応室に、 $N_2$ 、 $SiH_4$ およびArを導入し、基板温度400で第2窒化シリコン膜123を形成する。

30

## 【0141】

次に、図26(B)に示すように、レジスト124を形成し、エッチングにより絶縁膜116、118、第1窒化シリコン膜122および第2窒化シリコン膜123を部分的に除去して、半導体膜104、106の上面および、半導体膜108上の絶縁膜120上面を露出させ、メモリトランジスタTmとなる半導体膜108上に第1窒化シリコン膜122および第2窒化シリコン膜123を残す。

## 【0142】

40

レジスト124を除去し、図26(C)に示すように基板100上に絶縁膜128を形成する。この絶縁膜128はロジック部54のトランジスタTrpおよびTrnのゲート絶縁膜を構成し、メモリトランジスタTmの第2絶縁膜を構成する。絶縁膜128は、CVD法やスパッタ法等を用いて、酸化シリコン、窒化シリコン、酸化窒化シリコン等でなる絶縁材料を堆積することで、形成される。絶縁膜128は单層膜又は2層以上の多層膜で形成される。例えば、絶縁膜128を单層で設ける場合には、CVD法により酸化窒化シリコン層を5～50nmの厚さで形成する。また、絶縁膜128を3層構造で設ける場合には、第1層目の絶縁層として酸化窒化シリコン層を形成し、第2層目の絶縁層として窒化シリコン層を形成し、第3層目の絶縁層として酸化窒化シリコン層を形成する。

## 【0143】

50

次に、図27(A)に示すように、絶縁膜128上に導電膜130を形成し、導電膜130上に導電膜132を形成する。導電膜130と導電膜132でなる積層膜は、トランジスタTrp、Trn、TsおよびメモリトランジスタTmのゲート電極を構成する。もちろん、ゲート電極は単層構造の導電膜で形成することができる。

#### 【0144】

なお、メモリトランジスタTmをMNOS型とする場合は、導電膜130を形成する工程の前に、エッチングにより、メモリトランジスタTmが形成される領域から絶縁膜128を除去する。

#### 【0145】

導電膜130、132は単層構造または2層以上の多層構造とすることができます。導電膜130、132を構成する導電性材料には、タンタル(Ta)、タングステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ニオブ(Nb)等から選択された単体金属、これらの金属を主成分とする合金、および化合物材料、並びにリン等の不純物元素をドーピングした多結晶シリコン等を用いることができる。例えば金属化合物としては、金属窒化物、シリサイド等がある。

#### 【0146】

例えば、導電膜130を窒化タンタル膜で形成し、導電膜132をタングステン膜で形成する。また、導電膜130を窒化タングステン、窒化モリブデン又は窒化チタンから選ばれた導電材料の単層膜又は積層膜で形成し、導電膜132を、タンタル、モリブデン、チタンから選ばれた導電材料の単層膜は積層膜で形成することができる。

10

20

#### 【0147】

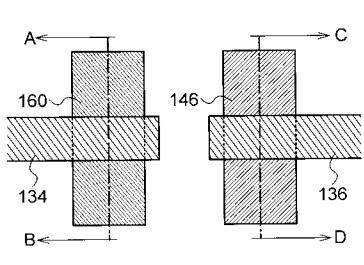

次に、図27(B)に示すように、導電膜130、132でなる積層膜をエッチングして、半導体膜104、106、108、110に重なる導電膜134、136、138、140を形成する。この状態の上面図が図30である。導電膜134、136は、それぞれ、トランジスタTrp、Trnゲート電極として機能する。導電膜138は、第2ワード線WLを構成し、スイッチング用トランジスタTsのゲート電極として機能する。導電膜140は第1ワード線WLを構成し、スイッチング用トランジスタTsのゲート電極として機能する。

#### 【0148】

次に、図27(C)に示すように、半導体膜104を覆うレジスト142を選択的に形成する。導電膜136、138、140をマスクとして半導体膜106、108、110にn型不純物を添加し、n型の高濃度不純物領域146、150、154を形成する。高濃度不純物領域146、150、154は、ソース領域又はドレイン領域を構成する。このn型不純物の添加により、半導体膜106、108、110に、チャネル形成領域144、148、152が自己整合的に形成される。

30

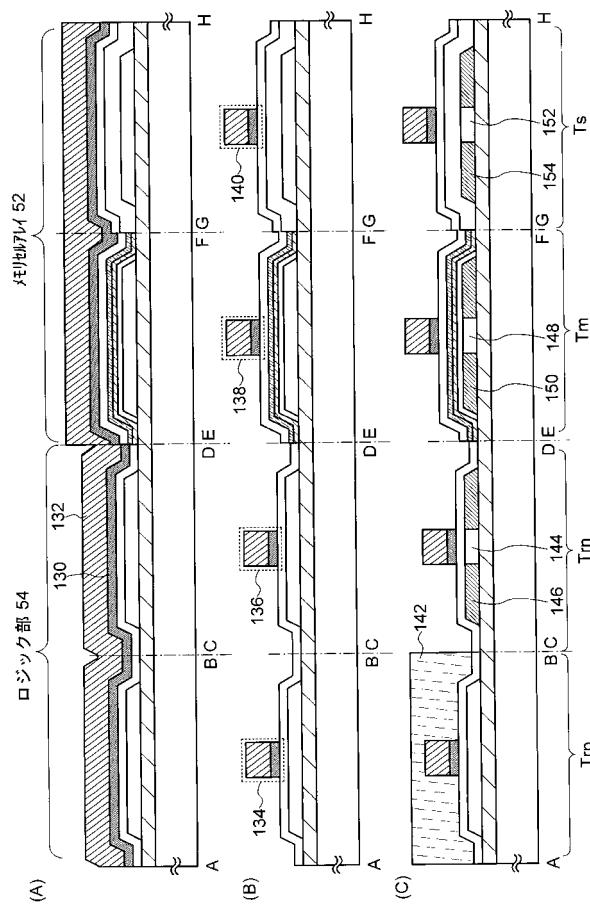

#### 【0149】

レジスト142を除去する。次に、図28(A)に示すように、半導体膜106、108、110を覆うレジスト156を形成する。導電膜134をマスクとして半導体膜104にp型不純物を添加し、p型の高濃度不純物領域160を形成する。高濃度不純物領域160は、ソース領域又はドレイン領域を構成する。このp型不純物の添加により、半導体膜104に、チャネル形成領域158が自己整合的に形成される。

40

#### 【0150】

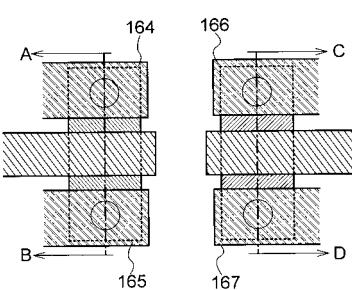

レジスト156を除去する。次に、図28(B)に示すように、導電膜134、136、138、140を覆うように絶縁膜162を形成する。絶縁膜162に、高濃度不純物領域146、150、154、160に達する開口部を形成する。絶縁膜162上に半導体膜104、106、108、110にそれぞれ形成された高濃度不純物領域146、150、154、160に電気的に接続する導電膜164～170を形成する。この状態の上面図が図31である。導電膜164および導電膜165は、pチャネル型トランジスタTrpのソース電極またはドレイン電極を構成する。導電膜166および導電膜167は、nチャネル型トランジスタTrnのソース電極またはドレイン電極を構成する。導電膜

50

168はスイッチング用トランジスタT<sub>s</sub>とメモリトランジスタT<sub>m</sub>を接続する電極を構成し、導電膜169はビット線BLを構成し、導電膜170はソース線SLを構成する。

#### 【0151】

絶縁膜162は単層構造または積層構造とすることができます。絶縁膜162を構成する絶縁膜として、CVD法やスパッタ法等により、酸化シリコン、窒化シリコン、酸化窒化シリコン、 DLC(ダイヤモンドライクカーボン)等の無機絶縁膜で形成することができる。また、エポキシ、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル等の有機材料でなる膜、シロキサン樹脂等のシロキサン材料からなる膜を用いることができる。

#### 【0152】

導電膜164は単層構造または積層構造とすることができます。導電膜164を構成する導電性材料には、CVD法やスパッタ法等により、アルミニウム(A1)、タンゲステン(W)、チタン(Ti)、タンタル(Ta)、モリブデン(Mo)、ニッケル(Ni)、白金(Pt)、銅(Cu)、金(Au)、銀(Ag)、マンガン(Mn)、ネオジム(Nd)から選択された単体金属元素、又はこれらの元素を主成分とする合金材料若しくは化合物材料を用いることができる。例えば、アルミニウムを主成分とする合金材料とは、例えば、アルミニウムとニッケルの合金、ニッケルと、炭素シリコンの一方又は両方とを含むアルミニウム合金などがある。アルミニウムやアルミニウムシリコンは抵抗値が低く、安価であるため、導電膜164を形成する材料に適している。

#### 【0153】

例えば、3層構造の導電膜164として、バリア層とアルミニウムシリコン(A1-Si)層とバリア層の積層膜、バリア層とアルミニウムシリコン(A1-Si)層と窒化チタン層とバリア層の積層膜などがある。なお、バリア層は、チタン、チタンの窒化物、モリブデン、又はモリブデンの窒化物からなる薄膜で形成される。上層と下層のバリア層を設けると、アルミニウムやアルミニウムシリコンのヒロックの発生を防止することができる。また、還元性の高い元素であるチタンからなるバリア層を形成すると、結晶質半導体層上に薄い自然酸化膜ができていたとしても、この自然酸化膜を還元し、結晶質半導体層と良好なコンタクトをとることができる。

#### 【0154】

以上の工程により、メモリセルアレイ52およびロジック部54が同一基板100上に集積された不揮発性半導体装置を作製することができる。

#### 【0155】

##### (実施の形態4)

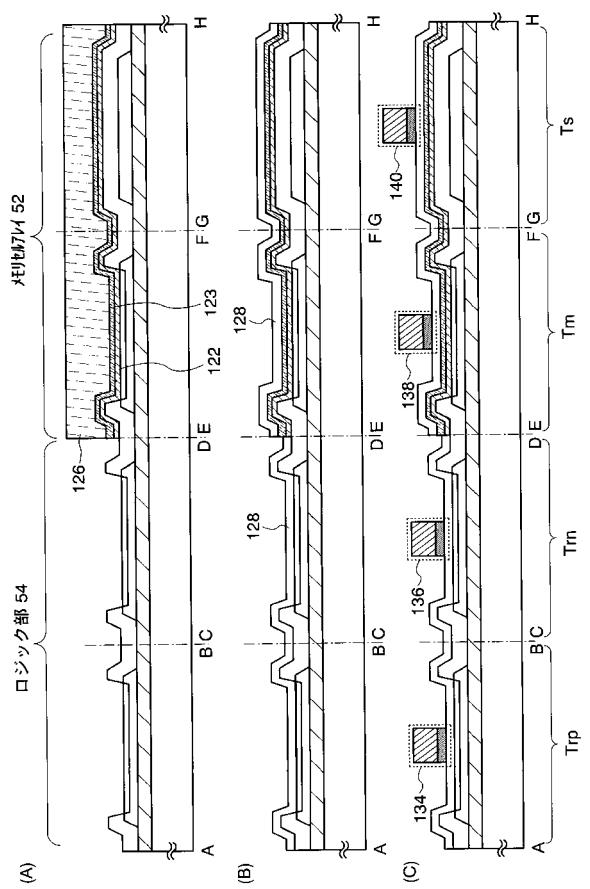

実施の形態3では、メモリセルMCに形成される不揮発性メモリ素子のコントロール絶縁膜として機能する絶縁層とロジック部に形成される薄膜トランジスタのゲート絶縁膜を同時に形成する作製方法を説明したが、不揮発性半導体記憶装置の作製方法はこれに限られない。例えば、図32に示すように形成することもできる。

#### 【0156】

まず、実施の形態3の作製方法により、図26(A)のプロセスまでを行う。そして、図32(A)に示すように、同様に形成した後、第1窒化シリコン膜122および第2窒化シリコン膜123上に絶縁膜128を形成する。

#### 【0157】

次に、図32(B)に示すように、半導体膜108を覆うようにレジスト124を選択的に形成した後、半導体膜104、106、110の上方に形成された第1窒化シリコン膜122、第2窒化シリコン膜123および絶縁膜128を除去し、半導体膜104、106および絶縁膜112を露出させる。

#### 【0158】

次に、実施の形態3と同様に高密度プラズマ処理により、図32(C)示すように、半導体膜104、106の表面に絶縁膜116、118を形成する。この結果、ロジック部54に形成されるトランジスタTrpおよびTrnのゲート絶縁膜と、メモリセルMCに

10

20

30

40

50

形成される不揮発性メモリトランジスタTmの第2絶縁膜とを異なる厚さ、異なる材料で形成することができる。

#### 【0159】

実施の形態3の図27(A)以降のプロセスを行うことで、不揮発性半導体記憶装置を作製することができる。

#### 【0160】

##### (実施の形態5)

本実施の形態では、半導体装置の作製方法について説明する。本実施の形態でも、実施の形態3および4と同様に、不揮発性半導体記憶装置の作製方法について説明する。

#### 【0161】

図33～図35は、本実施の形態の作製方法を示す断面図であり、実施の形態3と同様に、ロジック部54のトランジスタTrp、Trn、およびメモリセルアレイ52の不揮発性メモリトランジスタTmおよびスイッチング用トランジスタTsの断面図を示す。本実施の形態でも、メモリセルアレイ52は、実施形態3と同様、図19に示す回路で構成されている。なお、本実施の形態の作製方法は、図25～図28と同じ符号の構成要素を作製するプロセスには実施の形態3のプロセスを適用することが可能であるため、その詳細な説明は実施の形態3の説明を援用することとする。

10

#### 【0162】

まず、実施の形態3で説明した図25(A)までのプロセスを行う。次に、絶縁膜112上にレジスト114を形成する。このレジスト114を用いて、エッチングにより、レジスト114に覆われていない領域の絶縁膜112を除去する(図33(A)参照)。

20

#### 【0163】

このエッチングにより、半導体膜104、106、108の端部が絶縁膜112に覆われた構造となる。これは、半導体膜104、106、108上に形成された絶縁膜112をエッチングにより全て除去した場合に、半導体膜104、106、108の端部と下地絶縁膜102との部分において下地絶縁膜102に凹部(ザグリ)が形成されるのを防止するためである。下地絶縁膜102に凹部が形成されると、その後に半導体膜104、106、108を覆う絶縁層等を形成した場合に被覆不良等の問題が生じる。このような問題を回避するためには、半導体膜104、106、108の端部を絶縁膜112で覆うことが効果的である。

30

#### 【0164】

レジスト114を除去する。図33(B)に示すように、実施の形態3と同様に、高密度プラズマ処理により、半導体膜104、106、108上に絶縁膜116、118、120を形成する。次に、図33(C)に示すように、実施の形態3と同様に、第1窒化シリコン膜122および第2窒化シリコン膜123を形成する。

#### 【0165】

次に、図34(A)に示すように半導体膜108、半導体膜110をレジスト126で覆い、レジスト126で覆われていない領域に形成された第1窒化シリコン膜122および第2窒化シリコン膜123をエッチングによって除去する。レジスト126を除去し、図34(B)に示すように、絶縁膜128を形成する。絶縁膜128の形成方法は、実施の形態3と同様に行うことができる。例えば、絶縁膜128として、プラズマCVD法により酸化窒化シリコン層を5～50nmの厚さに形成する。

40

#### 【0166】

次に、図34(C)に示すように、半導体膜104、106、108、110の上方に、ゲート電極として機能する導電膜134、136、138、140を形成する。なお、メモリ部に設けられた半導体膜108の上方に形成される導電膜138は、第2ワード線WLを構成し、かつ不揮発性メモリトランジスタTmにおいて制御ゲートとして機能する。また、導電膜134、136は、それぞれ、トランジスタTrp、Trnのゲート電極として機能する。導電膜140は第1ワード線WLを構成し、スイッチング用トランジスタTsのゲート電極として機能する。

50

**【0167】**

なお、メモリトランジスタTmをMNO<sub>5</sub>型とする場合は、導電膜134、136、138、140を形成する工程の前に、エッチングにより、メモリトランジスタTmが形成される領域から絶縁膜128を除去する。

**【0168】**

次に、図35(A)に示すように、半導体膜104を覆うようにレジスト142を選択的に形成し、レジスト142、導電膜136、138、140をマスクとして半導体膜106、108、110にn型不純物元素を添加する。このn型不純物元素の添加工程により、半導体膜106、108、110に高濃度不純物領域146、150、154、チャネル形成領域144、148、152が自己整合的に形成される。

10

**【0169】**

レジスト142を除去し、次に、図35(B)に示すように、半導体膜106、108、110を覆うレジスト156を形成する。導電膜134をマスクとして半導体膜104にp型不純物元素を導入することによって、半導体膜104に高濃度不純物領域160およびチャネル形成領域158が自己整合的に形成する。

**【0170】**

レジスト156を除去する。次に、図35(C)に示すように、導電膜134、136、138、140を覆う絶縁膜162を形成し、高濃度不純物領域146、150、154、160に達する開口部を形成する。絶縁膜162上に半導体膜104、106、108、110にそれぞれ形成された高濃度不純物領域146、150、154、160に電気的に接続する導電膜164～170を形成する。以上のプロセスを経て、メモリセルアレイ52およびロジック部54を同一基板100上に集積した不揮発性半導体記憶装置が作製される。

20

**【0171】****(実施の形態6)**

本実施の形態では、半導体装置の作製方法について説明する。本実施の実施でも、実施の形態3～5と同様に、不揮発性半導体記憶装置の作製方法について説明する。

**【0172】**

図36～図38は、本実施の形態の作製方法を示す断面図であり、実施の形態3と同様に、ロジック部54のトランジスタTrp、Trn、およびメモリセルアレイの不揮発性メモリトランジスタTmおよびスイッチング用トランジスタTsの断面図を示す。本実施の形態でも、メモリセルアレイ52は、実施形態3と同様、図19に示す回路で構成されている。また、本実施の形態の作製方法において、図25～図28と同じ符号の構成要素を作製するプロセスは、実施の形態3とプロセスを適用することが可能であるため、その詳細な説明は実施の形態3の説明を援用することとする。

30

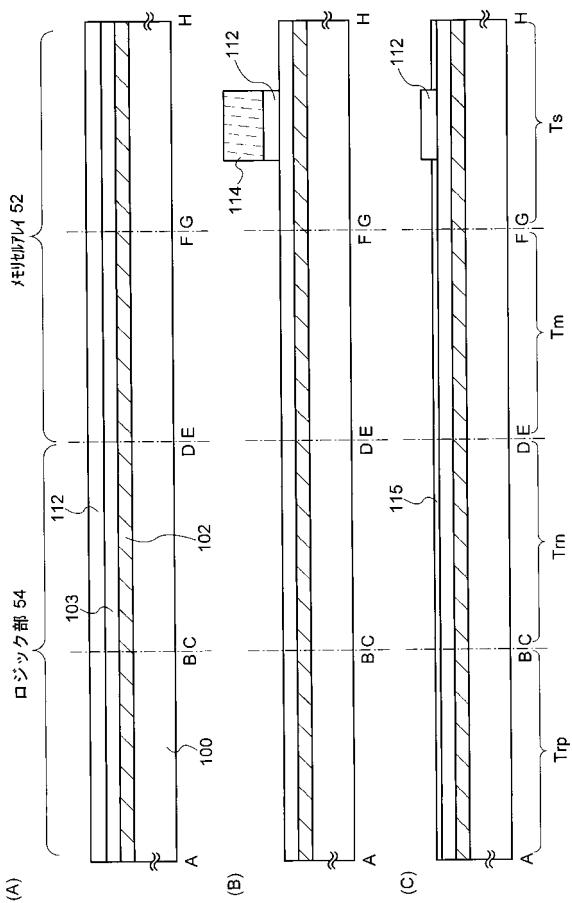

**【0173】**

まず、図36(A)に示すように、基板100上に下地絶縁膜102を形成し、下地絶縁膜102上に半導体膜103を形成し、半導体膜103上に絶縁膜112を形成する。

**【0174】**

半導体膜103の形成方法として、次の方法を用いることができる。スパッタ法、LPCVD法、プラズマCVD法等を用いて、シリコン、シリコンゲルマニウム、又はゲルマニウムでなる非晶質半導体膜を形成し、非晶質半導体膜を結晶化させて、結晶性半導体膜を形成する。非晶質半導体膜の結晶化は、レーザ結晶化法、RTA又はファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法またはこれら方法を組み合わせた方法等により行うことができる。

40

**【0175】**

次に、絶縁膜112上にレジスト114を形成する。図36(B)に示すように、レジスト114をマスクとして絶縁膜112をエッチングする。レジスト114を除去し、図36(C)に示すように、露出した半導体膜103を高密度プラズマ処理して、絶縁膜115を形成する。絶縁膜115の形成は、実施の形態3の絶縁膜116、118と同様の

50

方法を用いることができる。

**【0176】**

次に、図37(A)に示すように、絶縁膜115、112上に第1窒化シリコン膜122を形成し、第1窒化シリコン膜122上に第2窒化シリコン膜123を形成する。

**【0177】**

次に、レジスト125を形成する。レジスト125をマスクとして、図37(B)に示すように、絶縁膜115、第1窒化シリコン膜122および第2窒化シリコン膜123をエッティングする。G-H間の第1窒化シリコン膜122および第2窒化シリコン膜123は、スイッチング用トランジスタのゲート絶縁膜として機能する。G-H間の第1窒化シリコン膜122および第2窒化シリコン膜123は除去することもできる。

10

**【0178】**

レジスト125を除去する。次に、図37(C)に示すように、レジストマスクを用いて半導体膜103をエッティングして島状の半導体膜104、106、108、110を形成する(図37(C)参照)。

**【0179】**

次に、図38(A)に示すように、半導体膜104、106、108、110を覆う、絶縁膜128を形成する。次に、図38(B)に示すように半導体膜104、106、108、110の上方にそれぞれゲート電極として機能する導電膜134、136、138、140を形成する。

**【0180】**

20

なお、メモリトランジスタTmをMNOS型とする場合は、導電膜134、136、138、140を形成する工程の前に、エッティングにより、メモリトランジスタTmが形成される領域から絶縁膜128を除去する。

**【0181】**

次に、実施の形態3の図27(C)および図28(A)のプロセスを行い、図38(C)に示すように、半導体膜104、106、108、110にチャネル形成領域158、144、148、152、および高濃度不純物領域160、146、150、154を形成する。次に、絶縁膜162を形成し、絶縁膜162に高濃度不純物領域160、146、150、154に達する開口を形成する。次に、絶縁膜162上に半導体膜104、106、108、110にそれぞれ形成された高濃度不純物領域160、146、150、154に電気的に接続する導電膜164～170を形成する。

30

**【0182】**

以上のプロセスを経て、メモリセルアレイ52およびロジック部54を同一基板100上に集積した不揮発性半導体記憶装置が作製される。

**【0183】**

(実施の形態7)

本実施の形態では、半導体装置の作製方法として、半導体基板を用いた不揮発性半導体記憶装置の作製方法について説明する。

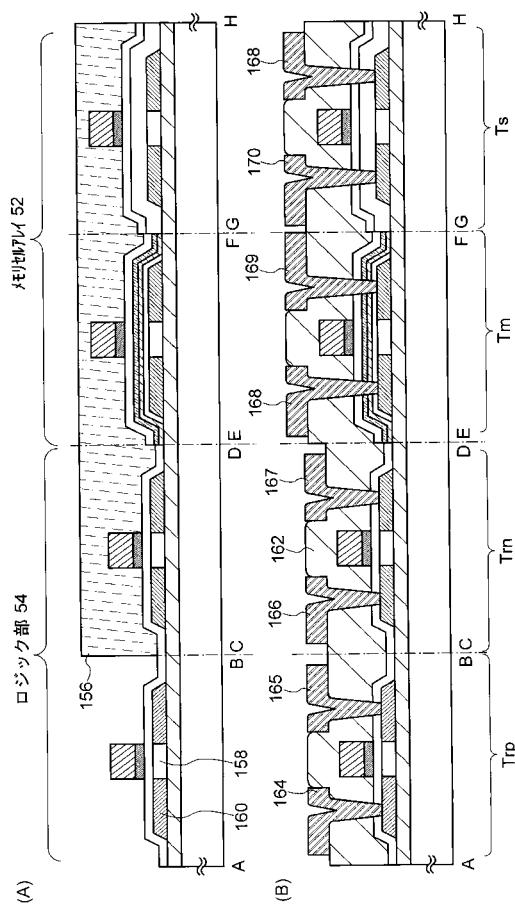

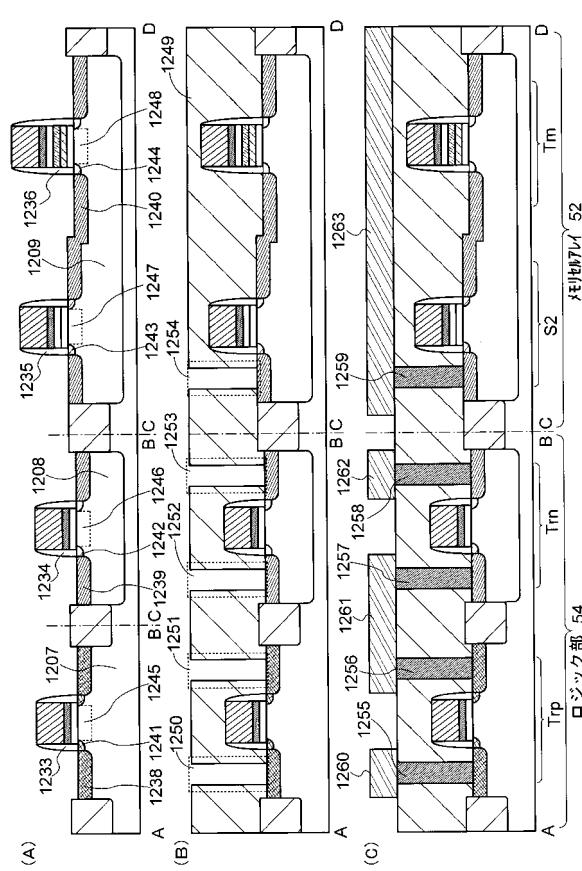

**【0184】**

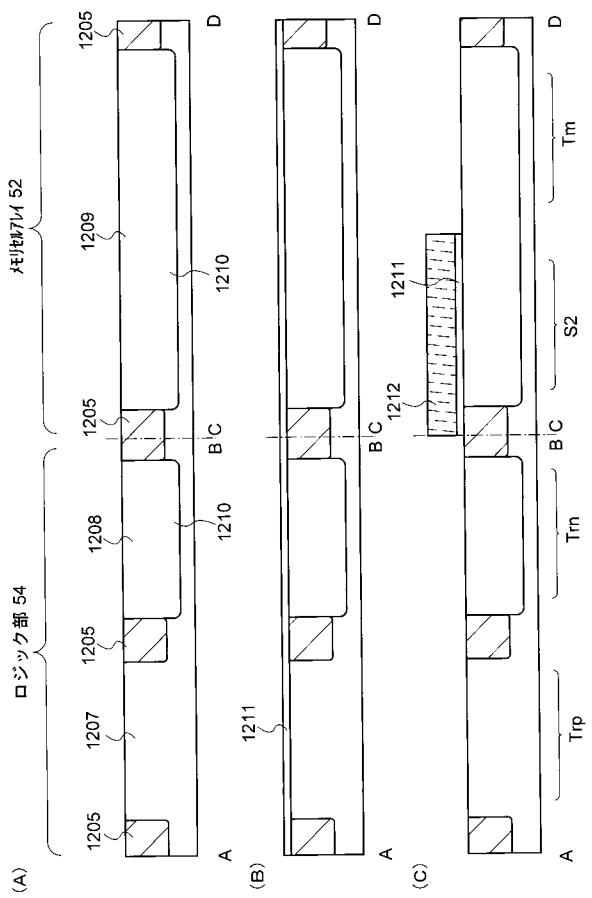

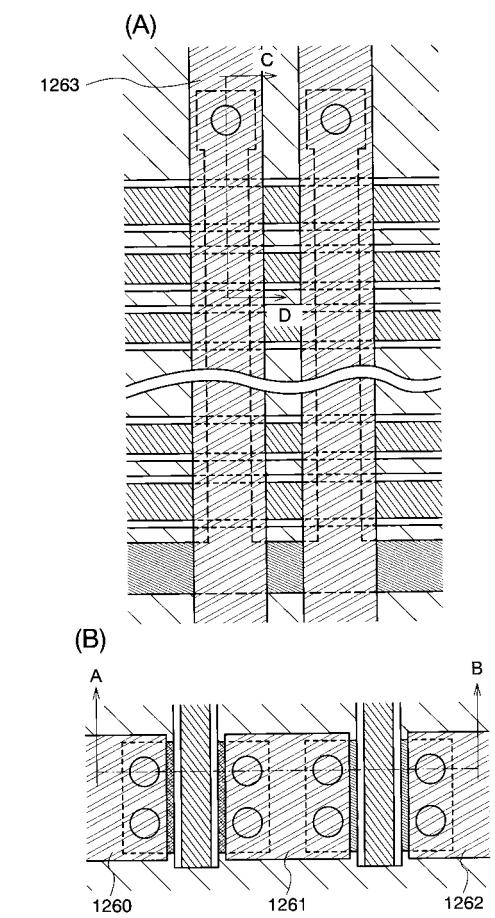

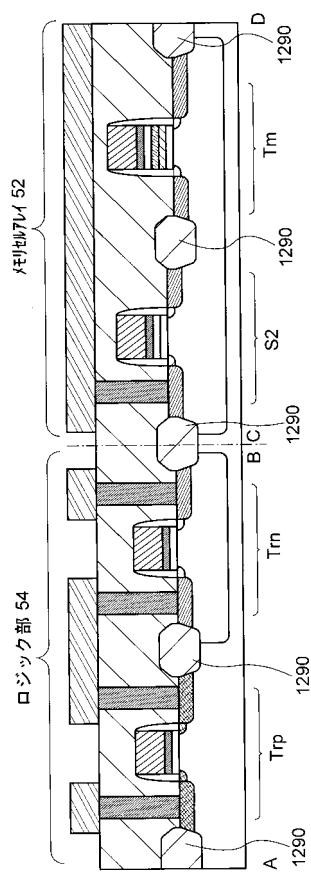

図39～図43は、本実施の形態の不揮発性半導体記憶装置の作製工程を説明するための断面図である。本実施の形態ではメモリセルアレイ52は、図21のようなNAND型のメモリセルで構成することにする。図39～図43において、A-B間にはロジック部54に設けられるpチャネル型トランジスタTrpおよびnチャネル型トランジスタTrnの断面を示す。また、C-D間にはメモリセルアレイ52に設けられる不揮発性メモリトランジスタTmおよび第2選択トランジスタS2の断面を示す。また、図44～図46は、本実施の形態の作製工程を説明するための上面図である。図44～図46の、一点鎖線A-BおよびC-Dで切った断面図が、図39～図43に対応する。

40

**【0185】**

まず、図39(A)に示すように、半導体基板1200を用意する。n型の導電型を有する単結晶Siウエハを半導体基板1200として用いる。半導体基板1200上に絶縁

50

膜 1201 を形成する。絶縁膜 1201 の形成方法には、熱酸化処理により、半導体基板 1200 上面を酸化して、酸化シリコンを形成する方法を用いることができる。絶縁膜 1201 上に CVD 法を用いて窒化シリコン膜 1202 を形成する。また、窒化シリコン膜 1202 は、絶縁膜 1201 を形成した後に高密度プラズマ処理により絶縁膜 1201 を窒化することで形成できる。

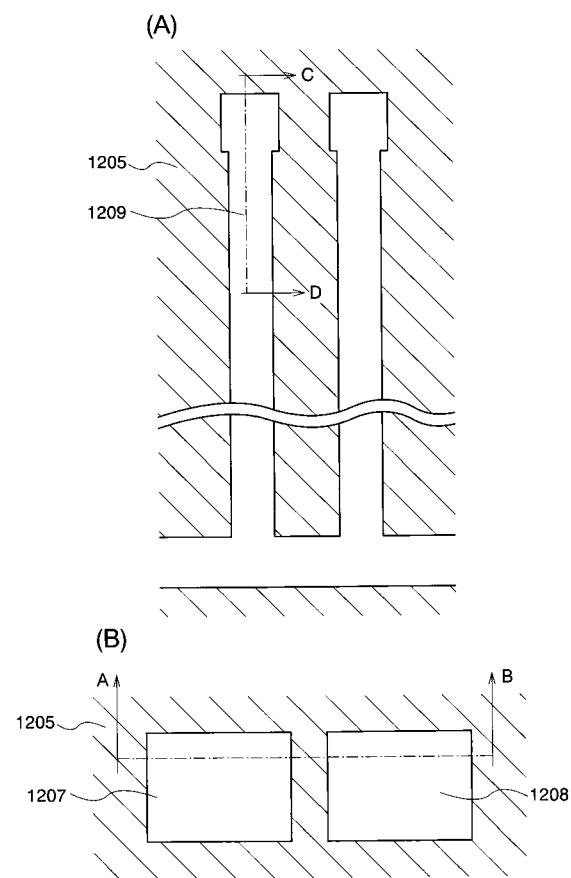

#### 【0186】

次に、図 39 (B) に示すように、窒化シリコン膜 1202 上にレジスト 1203 のパターンを形成する。レジスト 1203 をマスクとして、窒化シリコン膜 1202、絶縁膜 1201 および半導体基板 1200 をエッチングすることによって、半導体基板 1200 に凹部 1204 を形成する。このエッチングはプラズマを利用したドライエッチングにより行うことができる。

10

#### 【0187】

レジスト 1203 を除去する。次に、図 39 (C) に示すように、半導体基板 1200 に形成された凹部 1204 を埋める絶縁膜 1205 を形成する。絶縁膜 1205 は、CVD 法やスパッタ法等を用いて、酸化シリコン、窒化シリコン、酸素を含む窒化シリコン、窒素を含む酸化シリコン等の絶縁材料を用いて形成する。ここでは、絶縁膜 1205 として、常圧 CVD 法または減圧 CVD 法により TEOS (テトラエチルオルソシリケート) ガスを用いて酸化シリコンを形成する。

#### 【0188】

次に、研削処理、研磨処理又は CMP (Chemical Mechanical Polishing) 処理を行うことによって、図 40 (A) に示すように、絶縁膜 1205、窒化シリコン膜 1202、および絶縁膜 1201 を除去し、半導体基板 1200 の表面を露出させる。この処理により、半導体基板 1200 の凹部 1204 に残った絶縁膜 1205 間に半導体領域 1207 ~ 1209 が設けられる。続いて、p 型の不純物元素を選択的に半導体基板 1200 に添加することによって、p ウェル 1210 を形成する。この状態の上面図が図 44 (A)、図 44 (B) である。

20

#### 【0189】

なお、本実施の形態では、半導体基板 1200 として n 型の導電型を有する半導体基板を用いているため、半導体領域 1207 には不純物元素の導入を行っていないが、n 型を示す不純物元素を導入することにより半導体領域 1207 に n ウェルを形成することもできる。なお、p 型の半導体基板を用いる場合には、n ウェルを形成することで半導体領域 1207 を形成する。半導体領域 1208、1209 は p ウェルで形成しても、形成しなくともいずれでもよい。

30

#### 【0190】

次に、図 40 (B) に示すように、半導体基板 1200 の上面に絶縁膜 1211 を形成する。この絶縁膜 1211 は、実施の形態 3 の絶縁膜 112 と同様に形成することができる。ここでは、絶縁膜 1211 として、プラズマ CVD 法により酸化窒化シリコン膜を形成する。なお、半導体領域 1209 に形成された絶縁膜 1211 は、スイッチング用トランジスタ T<sub>s</sub> のゲート絶縁膜を構成する。

#### 【0191】

次に、図 40 (C) に示すように、レジスト 1212 を形成する。レジスト 1212 を用いて、半導体基板 1200 の半導体領域 1207、1208 に形成された絶縁膜 1211 を除去する。

40

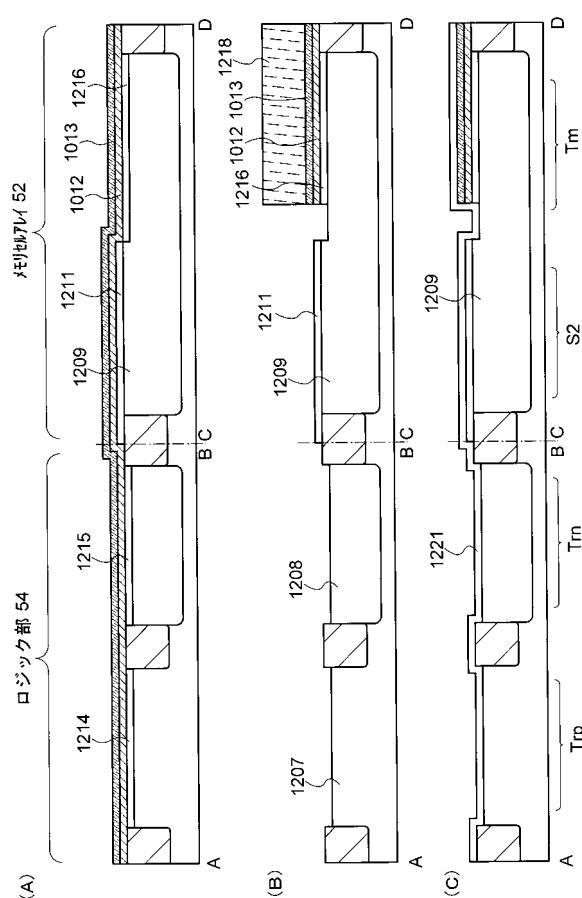

#### 【0192】

レジスト 1212 を除去した後、図 41 (A) に示すように半導体領域 1207 の上面に絶縁膜 1214 を形成し、半導体領域 1208 の上面に絶縁膜 1215 を形成する。半導体領域 1209 には、絶縁膜 1216 を形成する。次に、絶縁膜 1214 ~ 1216 を覆うように第 1 窒化シリコン膜 1012 を形成し、第 1 窒化シリコン膜 1012 上に第 2 窒化シリコン膜 1013 を形成する。

#### 【0193】

10

20

30

40

50

絶縁膜 1214～1216は、半導体基板 1200を高密度プラズマ処理により、酸化し、さらに窒化処理を行うことで形成することができる。高密度プラズマ処理は、実施の形態3と同様に行うことができる。絶縁膜 1214～1216は、熱酸化、熱窒化によつても形成することができる。

#### 【0194】

次に、図41(B)に示すように、レジスト1218を形成し、レジスト1218をマスクにして、第2窒化シリコン膜1013、第1窒化シリコン膜1012、絶縁膜1214～1216をエッティングする。ここでは、半導体領域1207、1208から、第2窒化シリコン膜1013、第1窒化シリコン膜1012および絶縁膜1214、絶縁膜1215を除去する。半導体領域1209においては、不揮発性メモリトランジスタTmが形成される領域に、第2窒化シリコン膜1013、第1窒化シリコン膜1012および絶縁膜1216を残し、他の領域からはこれらの絶縁膜を除去する。

10

#### 【0195】

レジスト1218を除去した後、図41(C)に示すように、半導体領域1207～1209を覆う絶縁膜1221を形成する。絶縁膜1221は単層膜又は積層膜のいずれでもよい。絶縁膜1221を構成する絶縁膜は、CVD法やスパッタ法等を用いて、酸化シリコン、窒化シリコン、酸化窒化シリコン等の絶縁材料を用いて形成することができる。ここでは、絶縁膜1221として、SiH<sub>4</sub>、N<sub>2</sub>Oを原料にして、プラズマCVD法により酸化窒化シリコン膜を形成する。

#### 【0196】

次に、図42(A)に示すように、絶縁膜1221上に導電膜1222を形成し、導電膜1222上に導電膜1223を形成する。導電膜1222、1223は、実施の形態3の導電膜130、132と同様に形成することができる。ここでは、窒化タンタルで導電膜1222を形成し、タンゲステンで導電膜1223を形成する。

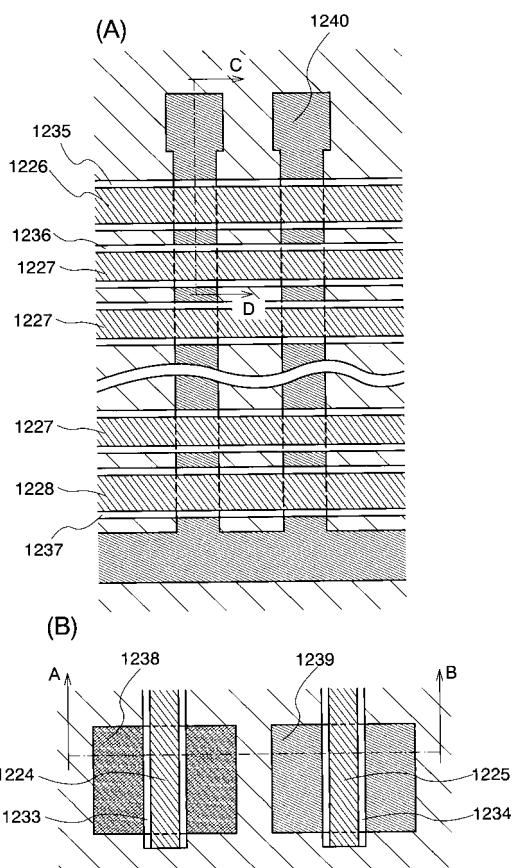

20

#### 【0197】

次に、導電膜1222、1223をエッティングして、図42(B)および図45に示すように、ゲート電極として機能する導電膜1224～1228を形成する。また、このエッティング工程により、半導体領域1207～1209において、導電膜1224～1228と重ならない領域の表面を露出させる。導電膜1226は、第2選択ゲート線を構成し、導電膜1227はワード線を構成し、導電膜1228は、第1選択ゲート線を構成する。

30

#### 【0198】

次に、図42(C)に示すように半導体領域1207～1209に不純物元素を選択的に導入し、低濃度不純物領域1229～1231を形成する。導電膜1225～1227をマスクとして、半導体領域1208、1209にn型の不純物を導入して、n型の低濃度不純物領域1230、1231を形成する。半導体領域1207には、導電膜1224をマスクとしてp型の不純物を添加して、p型の低濃度不純物領域1229を形成する。

#### 【0199】

次に、導電膜1224～1228の側面に接する絶縁膜でなるスペーサ1233～1237(サイドウォールともよばれる)を形成する(図43(A)、図45参照)。具体的には、プラズマCVD法やスパッタ法等により、シリコン、酸化シリコン又は窒化シリコン等の無機材料や、有機樹脂などの有機材料で、単層構造または2層以上の多層構造の絶縁膜を形成する。そして、この絶縁膜を、垂直方向を主体とした異方性エッティング処理することで、導電膜1224～1227の側面に接するスペーサ1233～1237が形成される。

40

#### 【0200】

次に、図43(A)に示すように、スペーサ1233～1237、導電膜1224～1228をマスクにして半導体領域1207～1209に不純物元素を導入することで、ソース領域又はドレイン領域として機能する高濃度不純物領域1238～1240を形成する。図43(A)の上面図が図45(A)、(B)に対応する。

50

**【0201】**

半導体領域1207には、高濃度不純物領域1238、LDD領域を形成する低濃度不純物領域1241、およびチャネル形成領域1245が形成される。また、半導体領域1208には、高濃度不純物領域1239、LDD領域を形成する低濃度不純物領域1242、およびチャネル形成領域1246が形成される。また、半導体領域1209には、高濃度不純物領域1240、LDD領域を形成する低濃度不純物領域1243、1244、およびチャネル形成領域1247、1248が形成される。半導体領域1207～1209に形成された高濃度不純物領域1238～1240は、ソース領域又はドレイン領域を構成する。

**【0202】**

10

なお、本実施の形態では、導電膜1224～1228と重ならない半導体領域1207～1209を露出させた状態で不純物元素の導入を行っている。従って、半導体領域1207～1209にそれぞれ形成されるチャネル形成領域1245～1248は、導電膜1224～1228に対して自己整合的に形成することができる。

**【0203】**

次に、図43(B)に示すように絶縁膜1249を形成し、絶縁膜1249に開口部1250～1254を形成する。絶縁膜1249は、実施の形態3の絶縁膜162と同様に形成することができる。ここでは、ポリシラザンを用いて形成する。

**【0204】**

20

次に、開口部1250～1254に導電膜1255～1259を形成し、導電膜1255～1259と電気的に接続するように絶縁膜1249上に導電膜1260～1263を選択的に形成する。導電膜1255～1259、1260～1263は、実施例の形態3に示す導電膜164と同様に形成することができる。また、導電膜1255～1259はCVD法によりタンゲステン(W)を選択成長することにより形成することができる。図43(C)の上面図が図46(A)、図46(B)に対応する。導電膜1259および導電膜1263はピット線を構成する。

**【0205】**

以上の工程により、半導体基板1200の半導体領域1207に形成されたp型のトランジスタTrpと、半導体領域1208に形成されたn型のトランジスタTrnと、半導体領域1209に形成されたn型の第2選択トランジスタS2、および不揮発性メモリトランジスタTmが集積された不揮発性半導体記憶装置が作製される。

30

**【0206】**

なお、凹部1204および絶縁膜1205は素子分離のために形成されるが、凹部1204および絶縁膜1205を形成する代わりに、図47に示すように、選択酸化法(Local Oxidation of Silicon)法)により、素子分離領域として絶縁膜1290を形成することができる。

**【0207】****(実施の形態8)**

本実施の形態では、半導体装置の作製方法として、不揮発性半導体記憶装置の作製方法について説明する。本実施の形態では、実施の形態7と同様、半導体基板を用いた不揮発性半導体記憶装置の作製方法について説明する。

40

**【0208】**

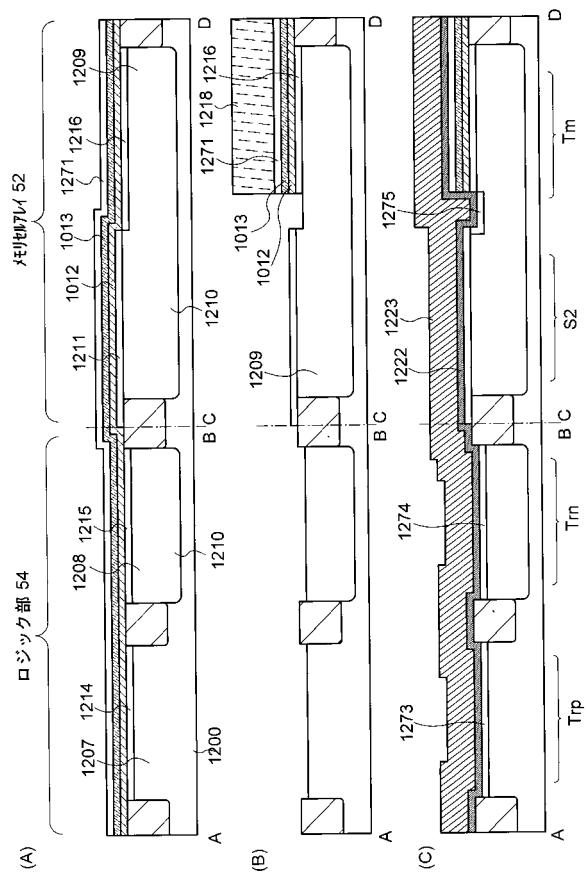

図48および図49は、本実施の形態の作製方法を示す断面図であり、図39～図43と同様に、ロジック部54のトランジスタTrp、Trn、およびメモリセルアレイ52の不揮発性メモリトランジスタTmおよび第2選択トランジスタS2の断面図を示す。なお、本実施の形態において、図39～図43と同じ符号の構成要素を作製するプロセスは、実施の形態7のプロセスを適用することが可能であり、その詳細な説明は実施の形態7の説明を援用することとする。

**【0209】**

実施の形態7で説明した図39(A)～図41(A)までの工程を行う。次に、図48

50

(A)に示すように、第2窒化シリコン膜1013上に、絶縁膜1271を形成する。絶縁膜1271は、実施の形態6の絶縁膜1221と同様に形成することができる。

#### 【0210】

次に、絶縁膜1271上にレジスト1218を形成する。レジスト1218をマスクにして、絶縁膜1271、第2窒化シリコン膜1013、第1窒化シリコン膜1012、絶縁膜1214～1216をエッチングする。図48(B)に示すように、半導体領域1209のメモリトランジスタTmが形成される領域上に、絶縁膜1216、第1窒化シリコン膜1012、第2窒化シリコン膜1013および絶縁膜1271でなる積層膜が形成される。他の領域からは第1窒化シリコン膜1012、第2窒化シリコン膜1013および絶縁膜1271、絶縁膜1216、1214、1215は除去され、半導体領域1207、半導体領域1208、絶縁膜1211が露出され、半導体領域1209はその一部が露出される。

10

#### 【0211】

レジスト1218を除去した後、半導体領域1207～1209の露出された部分を酸化処理または窒化処理して、図48(C)に示すように、絶縁膜1273～1275を形成する。絶縁膜1273～1275は実施の形態7の絶縁膜1214、1215と同様の方法で形成することができる。絶縁膜1273、1274は、ロジック部54に形成されるトランジスタTrpおよびTrnのゲート絶縁膜を構成する。例えば、絶縁膜1273～1275の形成は、半導体基板1200の表面を高密度プラズマにより酸化処理を行い、連続して、高密度プラズマにより窒化処理を行うことで形成することができる。

20

#### 【0212】

次に、図48(C)に示すように、半導体基板1200上に導電膜1222を形成し、導電膜1222上に導電膜1223を形成する。

#### 【0213】

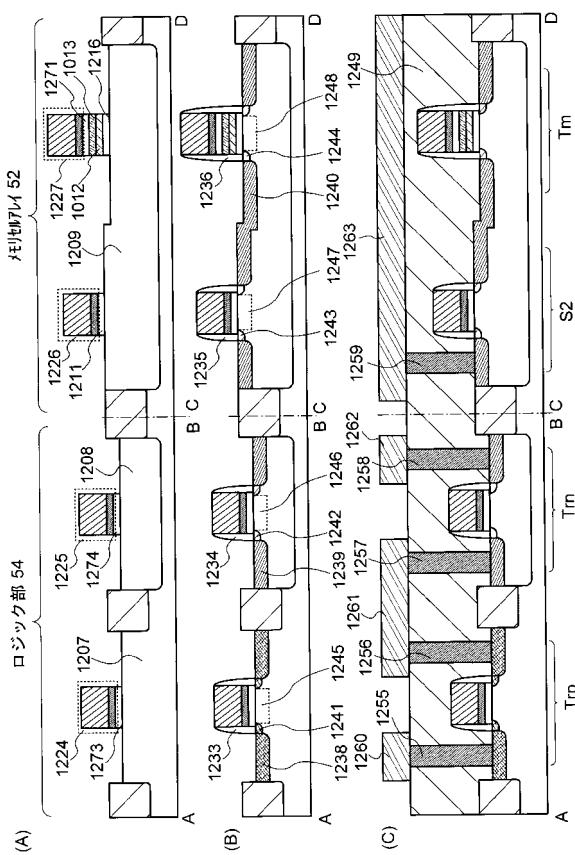

次に、導電膜1222と導電膜1223でなる積層膜をエッチングして、導電膜1224～1228を形成する(図49(A)、図45参照)。さらに、導電膜1224～1227をマスクにして、図49(A)に示すように、これら導電膜1224～1227の下方に形成されている絶縁膜をエッチングする。

#### 【0214】

半導体領域1207上の絶縁膜1273はトランジスタTrpのゲート絶縁膜を構成する。半導体領域1208上の絶縁膜1274はトランジスタTrnのゲート絶縁膜を構成する。半導体領域1209上の絶縁膜1211は第2選択トランジスタS2のゲート絶縁膜を構成する。半導体領域1209上の絶縁膜1216はメモリトランジスタTmの第1絶縁膜を構成し、第1窒化シリコン膜1012および第2窒化シリコン膜1013はその電荷蓄積層を構成し、絶縁膜1271はその第2絶縁膜を構成する。

30

#### 【0215】

次に、実施の形態7と同様に、半導体領域1207～1209に不純物元素を低濃度に添加し、低濃度不純物領域を形成し、次に、導電膜1224～1228の側面に接する絶縁膜でなるスペーサ1233～1237を形成する。そして、半導体領域1207～1209に不純物元素を高濃度に添加し、高濃度不純物領域を形成する。

40

#### 【0216】

この工程を行うことで、図49(B)に示すように、半導体領域1207には、高濃度不純物領域1238、低濃度不純物領域1241、チャネル形成領域1245が自己整合的に形成される。半導体領域1208には、高濃度不純物領域1239、低濃度不純物領域1242、チャネル形成領域1246が自己整合的に形成される。半導体領域1209には、高濃度不純物領域1240、低濃度不純物領域1243、1244、チャネル形成領域1247、1248が自己整合的に形成される。この状態の上面図が図45である。

#### 【0217】

実施の形態7と同様の工程を行い、図49(C)に示すように、絶縁膜1249、導電膜1255～1259、導電膜1260～1263を形成する。図49(C)の上面図が

50

図46(A)、図46(B)に示されている。

**【0218】**

以上の工程により、半導体基板1200上に、ロジック部54およびメモリセルアレイ52が集積された不揮発性半導体記憶装置を得ることができる。

**【0219】**

(実施の形態9)

本実施の形態では、非接触でデータの入出力が可能である半導体装置について説明する。半導体装置に、不揮発性半導体記憶装置が用いられる。本実施の形態で説明する半導体装置は利用の形態によっては、RFIDタグ、IDタグ、ICタグ、ICチップ、RFタグ、無線タグ、電子タグまたは無線チップともよばれる。

10

**【0220】**

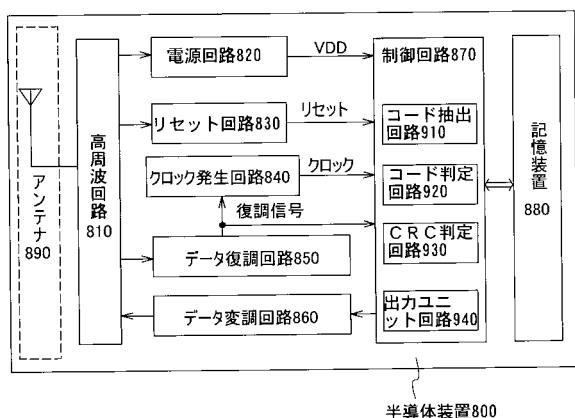

図50は非接触でデータの入出力が可能である半導体装置の構成例を示すブロック図である。図44に示すように、半導体装置800は、非接触でデータを交信する機能を有し、高周波回路810、電源回路820、リセット回路830、クロック発生回路840、データ復調回路850、データ変調回路860、半導体装置800に含まれる回路の制御を行う制御回路870、記憶装置880およびアンテナ890を有している。

**【0221】**

高周波回路810はアンテナ890より信号を受信して、データ変調回路860より受信した信号をアンテナ890から出力する回路であり、電源回路820は受信信号から電源電位を生成する回路であり、リセット回路830はリセット信号を生成する回路であり、クロック発生回路840はアンテナ890から入力された受信信号を基に各種クロック信号を生成する回路であり、データ復調回路850は受信信号を復調して制御回路870に出力する回路であり、データ変調回路860は制御回路870から受信した信号を変調する回路である。

20

**【0222】**

また、制御回路870としては、例えばコード抽出回路910、コード判定回路920、CRC判定回路930および出力ユニット回路940が設けられている。なお、コード抽出回路910は制御回路870に送られてきた命令に含まれる複数のコードをそれぞれ抽出する回路であり、コード判定回路920は抽出されたコードとリファレンスに相当するコードとを比較して命令の内容を判定する回路であり、CRC判定回路930は判定されたコードに基づいて送信エラー等の有無を検出する回路である。

30

**【0223】**

記憶装置880は、実施の形態1~8で説明した不揮発性半導体装置と、書き替えが不可能なROMを有する。本発明の不揮発性半導体記憶装置は、駆動電圧を低くすることができるため、通信距離が伸び、また高品位の通信が可能となる。

**【0224】**

リーダ/ライタなどの通信機器から半導体装置800に信号を送り、半導体装置800から送られてきた信号を通信機器で受信することによって、半導体装置800のデータを読み取ることが可能となる。次に、半導体装置800の通信動作について説明する。アンテナ890により無線信号が受信される。無線信号は高周波回路810を介して電源回路820に送られ、高電源電位(以下、VDDと記す)が生成される。VDDは半導体装置800が有する各回路に供給される。なお、半導体装置800を構成する複数の回路は、低電源電位(以下、VSS)を共通であり、VSSは接地電位(GND)とすることができる。

40

**【0225】**

高周波回路810を介してデータ復調回路850に送られた信号は復調される(以下、復調信号)。さらに、高周波回路810を介してリセット回路830およびクロック発生回路840を通った信号および復調信号は制御回路870に送られる。制御回路870に送られた信号は、コード抽出回路910、コード判定回路920およびCRC判定回路930等によって解析される。そして、解析された信号にしたがって、記憶装置880内に

50

記憶されている半導体装置 800 の情報が出力される。出力された半導体装置 800 の情報は出力ユニット回路 940 を通って符号化される。さらに、符号化された半導体装置 800 の情報はデータ変調回路 860 を通って、アンテナ 890 により無線信号に載せて送信される。

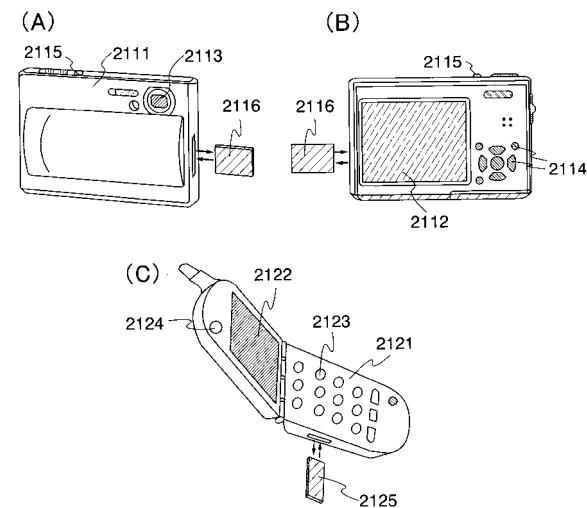

#### 【0226】

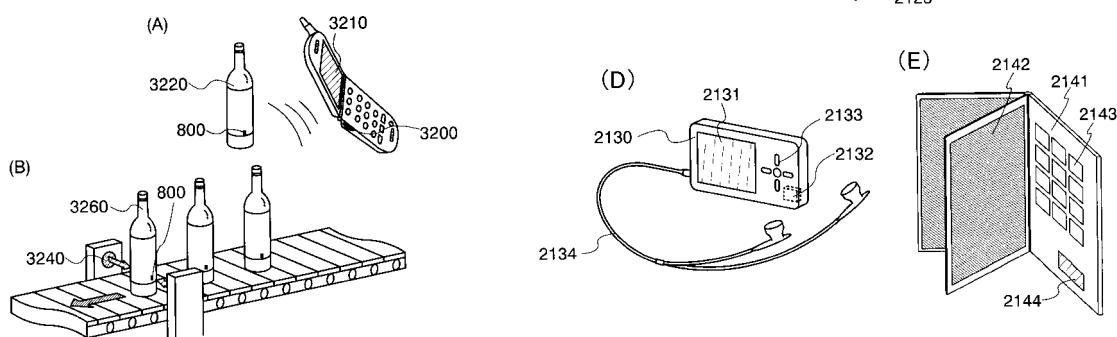

図 51 (A) および図 51 (B) を用いて、半導体装置 800 の使用形態の一例について説明する。図 51 (A) に示すように、表示部 3210 を含む携帯電話等の携帯端末の側面には、リーダ / ライタ 3200 が設けられている。他方、品物 3220 の側面には半導体装置 800 が取り付けられている (図 51 (A))。半導体装置 800 にリーダ / ライタ 3200 をかざすと、半導体装置 800 から記憶されている情報送信され、リーダ / ライタで受信される。その結果、携帯端末の表示部 3210 に品物の原材料や原産地、生産工程ごとの検査結果や流通過程の履歴等、更に商品の説明等の商品に関する情報が表示される。

#### 【0227】

また、図 51 (B) に示すように、商品 3260 をベルトコンベアにより搬送する際に、リーダ / ライタ 3240 と、商品 3260 に取り付けられた半導体装置 800 を用いて、該商品 3260 の検品を行うことができる。このような検品システムに、無線通信が可能な半導体装置 800 を利用することで、商品 3260 に直接表示できない多種多様な情報の取得を簡単に行うことができる。

#### 【0228】

##### (実施の形態 10)

本実施の形態では、半導体装置として、不揮発性半導体記憶装置を具備した電子機器について説明する。本発明は、記憶装置として不揮発性半導体記憶装置を具備したあらゆる分野の電子機器に用いることが可能である。例えば、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ (ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置 (カーオーディオ、オーディオコンポ等)、コンピュータ、ゲーム機器、携帯情報端末 (モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置 (具体的には DVD (d i g i t a l v e r s a t i l e d i s c) 等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置) などが挙げられる。それら電子機器の具体例を図 52 に示す。

#### 【0229】

図 52 (A)、(B) は、デジタルカメラを示している。図 52 (B) は、図 52 (A) の裏側を示す図である。図 52 (A) および図 52 (B) に示すデジタルカメラは、筐体 2111、表示部 2112、レンズ 2113、操作キー 2114、シャッターボタン 2115、不揮発性半導体記憶装置を具備する記憶媒体 2116 等を備えている。また、筐体 2111 は、使用者が記憶媒体 2116 を取り出すことができる構造となっている。デジタルカメラでは、撮影した静止画像、動画像や、録音された音声データを記憶媒体 2116 に記憶できる。実施の形態 2 ~ 8 で説明した不揮発性半導体記憶装置が記憶媒体 2116 に適用されている。

#### 【0230】

図 52 (C) は、携帯電話の外観図である。携帯電話は携帯端末の 1 つの代表例である。携帯電話は筐体 2121、表示部 2122、操作キー 2123 などを含む。また、携帯電話は、不揮発性半導体記憶装置を具備する記憶媒体 2125 を備えており、筐体 2121 は、記憶媒体 2125 が取り出し可能な構造となっている。記憶媒体 2125 は、携帯電話の電話番号等のデータ、映像、音楽、音声データ等を記憶し、携帯電話において、記憶媒体 2125 に記憶された映像、音楽、音声データを再生することができる。実施の形態 2 ~ 8 で説明した不揮発性半導体記憶装置が記憶媒体 2125 に適用されている。

#### 【0231】

図 52 (D) は、デジタルプレーヤーの外観図である。デジタルプレーヤーはオーディオ装置の 1 つの代表例である。デジタルプレーヤーは、本体 2130、表示部 2131、

10

20

30

40

50

操作部 2133、イヤホン 2134 等を含む。なお、イヤホン 2134 の代わりにヘッドホンや無線式イヤホンを用いることができる。また、デジタルプレーヤーは、不揮発性半導体記憶装置を具備する記憶媒体 2132 が本体 2130 に内蔵されている。実施の形態 2~8 で説明した不揮発性半導体記憶装置が記憶媒体 2132 に適用されている。本体 2130 を使用者が記憶媒体 2132 を取り出すことができる構造としてもよい。

#### 【0232】

記憶媒体 2132 には、例えば、記録容量が 20~200 ギガバイト (GB) の NAND 型不揮発性半導体記憶装置を用いることができる。操作部 2133 を操作することにより、静止画像、動画像、音声、音楽などのデータを記憶媒体 2132 に記憶し、また記憶されているデータを再生することができる。

10

#### 【0233】

図 52 (E) は、電子ブック (電子ペーパーともいう) の外観図である。電子ブックは、本体 2141、表示部 2142、操作キー 2143、記憶媒体 2144 を含んでいる。またモデムが本体 2141 に内蔵されてもよいし、無線で情報を送受信できる構成としてもよい。記憶媒体 2144 には、実施の形態 2~8 で説明した不揮発性半導体記憶装置を適用することができ、例えば、記録容量が 20~200 ギガバイト (GB) の NAND 型の不揮発性半導体記憶装置を用いることができる。操作キー 2143 を操作することにより、静止画像、動画像、音声、音楽などのデータを記憶媒体 2144 に記録することができ、また、記憶されているデータを再生することができる。なお、本体 2141 は、使用者が記憶媒体 2144 を取り出すことができる構造としてもよい。

20

#### 【0234】

以上のように、本発明の半導体装置の適用範囲は極めて広く、記憶媒体を有するものであればあらゆる分野の電子機器に用いることが可能である。電荷保持特性が向上された不揮発性の記憶媒体を備えることで、電子機器の記憶性能の信頼性も向上させることができる。

#### 【実施例 1】

#### 【0235】

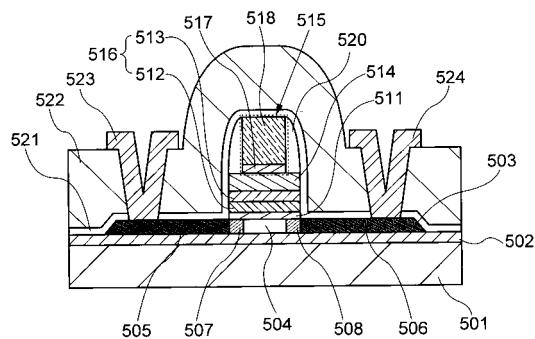

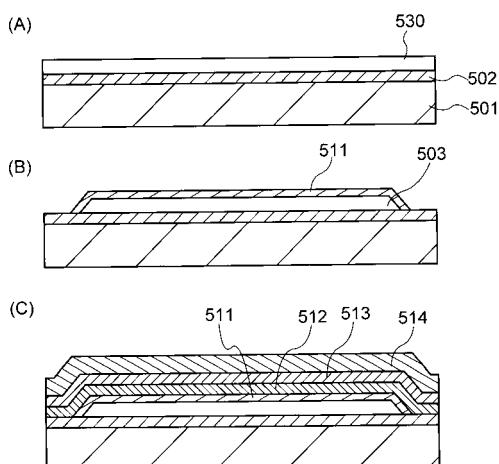

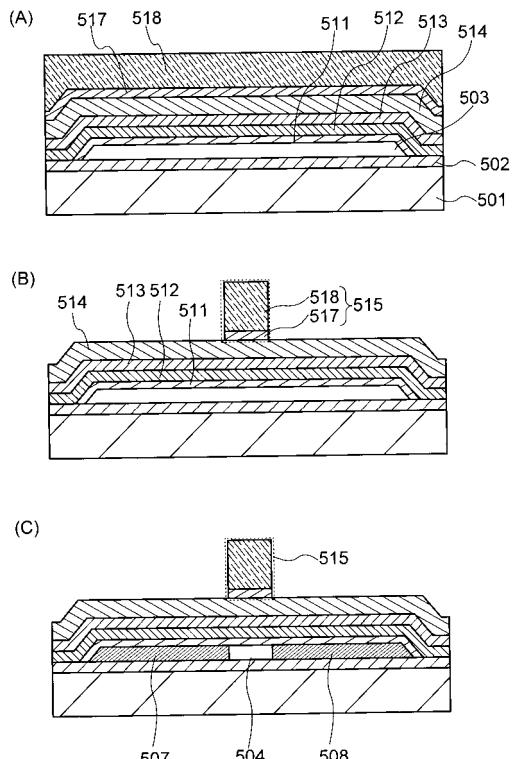

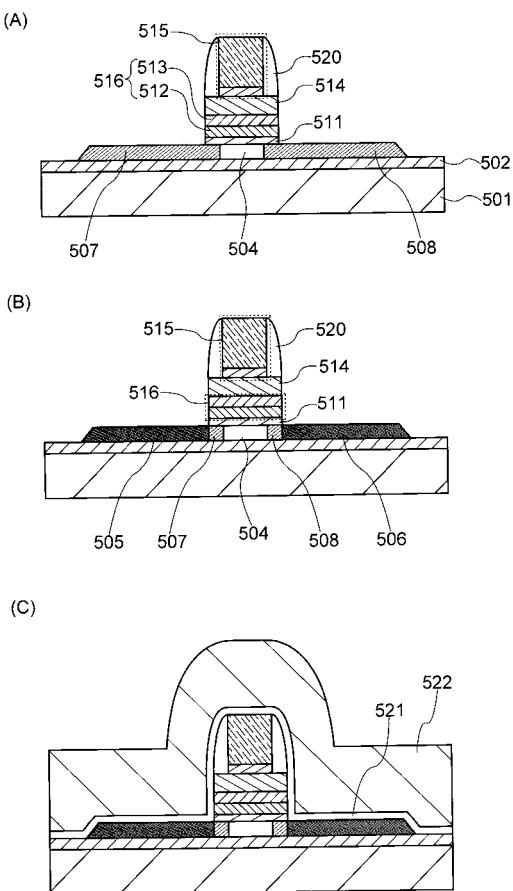

本実施例では、本発明に係るメモリトランジスタの電荷保持特性について説明する。図 53 は、本発明に係る不揮発性メモリトランジスタの断面図である。この不揮発性メモリトランジスタを「メモリトランジスタ TM-1」と呼ぶことにする。

30

#### 【0236】

メモリトランジスタ TM-1 はガラス基板 501 上に形成されている。ガラス基板 501 上に下地絶縁膜 502 が形成され、この下地絶縁膜 502 上に半導体領域を構成するシリコン膜 503 が形成されている。シリコン膜 503 には、チャネル形成領域 504、ソース領域 505、ドレイン領域 506、低濃度不純物領域 507、および低濃度不純物領域 508 が形成されている。各領域 505~508 は、n 型の不純物領域であり、メモリトランジスタ TM-1 は n チャネル型のトランジスタである。

#### 【0237】

シリコン膜 503 上には、第 1 絶縁膜 511、第 1 室化シリコン膜 512、第 2 室化シリコン膜 513、第 2 絶縁膜 514、およびゲート電極 515 が積層されている。第 1 室化シリコン膜 512 と第 2 室化シリコン膜 513 との積層膜が電荷蓄積層 516 を構成する。また、ゲート電極 515 は、室化タンタル膜 517、タングステン膜 518 の 2 層構造の導電膜で形成されている。

40

#### 【0238】

さらに、メモリトランジスタ TM-1 において、ゲート電極 515 の側面には、絶縁膜であるスペーサ 520 が形成されている。さらに、ガラス基板 501 上には、シリコン膜 503、第 1 絶縁膜 511、電荷蓄積層 516、第 2 絶縁膜 514、ゲート電極 515 およびスペーサ 520 を覆う絶縁膜 521 および絶縁膜 522 が形成されている。絶縁膜 522 上には、ソース領域 505 に接続されるソース電極 523、およびドレイン領域 506 に接続されるドレイン電極 524 が形成されている。

50

## 【0239】

メモリトランジスタTM-1において、第1窒化シリコン膜512は窒素ソースガスにNH<sub>3</sub>を用いてプラズマCVD法で形成された膜であり、第2窒化シリコン膜513はソースガスにN<sub>2</sub>を用いてプラズマCVD法で形成された膜である。つまり、第1窒化シリコン膜512はN-H結合を多く含む膜であり、第2窒化シリコン膜513はN-H結合が少ない膜である。

## 【0240】

さらに、比較例として、電荷蓄積層516が異なる3種類の不揮発性メモリトランジスタを作製した。1つは、電荷蓄積層516が第1窒化シリコン膜512のみでなる不揮発性メモリトランジスタである。このメモリトランジスタを「比較メモリトランジスタTM-A」と呼ぶ。第2は、電荷蓄積層516が第2窒化シリコン膜513のみでなる不揮発性メモリトランジスタである。このメモリトランジスタを「比較メモリトランジスタTM-B」と呼ぶ。第3は、電荷蓄積層516が、第2窒化シリコン膜513、第1窒化シリコン膜512の順に積層された不揮発性メモリトランジスタである。このメモリトランジスタを「比較メモリトランジスタTM-C」と呼ぶ。

10

## 【0241】

次に、図54～57を参照して、メモリトランジスタTM-1の作製方法を説明する。まず、図54(A)に示すように、ガラス基板501上に下地絶縁膜502を形成し、下地絶縁膜502上に結晶性シリコン膜530をする。ここでは、下地絶縁膜502を2層構造とする。1層目にプラズマCVD法によりSiH<sub>4</sub>、NH<sub>3</sub>、およびN<sub>2</sub>Oをプロセスガスとして、厚さ50nmの酸化窒化シリコン膜を形成し、2層目に、SiH<sub>4</sub>、およびN<sub>2</sub>Oをプロセスガスとして、厚さ100nmの酸化窒化シリコン膜を形成する。1層目の酸化窒化シリコン膜は、酸素よりも窒素を多く含み、2層目の酸化窒化シリコン膜は、窒素よりも酸素を多く含む。

20

## 【0242】

結晶性シリコン膜530は、非晶質シリコン膜を結晶化した膜である。まず、下地絶縁膜502上に、SiH<sub>4</sub>をプロセスガスに用い、プラズマCVD法により、非晶質シリコン膜を厚さ66nm形成する。次に、連続発振方式のNd:YVO<sub>4</sub>レーザー(基本波1064nm)の第2高調波(532nm)を照射することにより非晶質シリコン膜を結晶化し、結晶性シリコン膜530を形成する。次に、メモリトランジスタTM-1のしきい値電圧値を制御するため、イオンドーピング装置により、ボロンを結晶性シリコン膜530にドープする。

30

## 【0243】

結晶性シリコン膜530上にレジストマスクを形成し、このレジストマスクを用いて、結晶性シリコン膜530を所望の形状にエッチングし、シリコン膜503を形成する。レジストマスクを除去した後、第1絶縁膜511を形成する(図54(B)参照)。マイクロ波によりプラズマを生成する高密度プラズマ処理装置で、シリコン膜503に対して、固相酸化処理および固相窒化処理を行うことで、第1絶縁膜511が形成される。

## 【0244】

次に、第1絶縁膜511上に、同じプラズマCVD装置において、厚さ5nmの第1窒化シリコン膜512、厚さ5nmの第2窒化シリコン膜513および厚さ10nmの第2絶縁膜514を連続して形成する(図54(C)参照)。

40

## 【0245】

第1窒化シリコン膜512の形成には、窒素ソースガスとしてNH<sub>3</sub>を用い、シリコンソースガスとしてSiH<sub>4</sub>を用いる。SiH<sub>4</sub>を流量2sccmで、NH<sub>3</sub>を流量400scmで反応室に供給する。また、基板温度400℃、反応圧力40Paとし、電極間距離を30mm、RFパワーを100Wにする。

## 【0246】

第2窒化シリコン膜513の形成には、窒素ソースガスとしてN<sub>2</sub>を用い、シリコンソースガスとしてSiH<sub>4</sub>を用い、さらに、プロセスガスにArを添加する。SiH<sub>4</sub>を流

50

量 2 s c c m で、 N<sub>2</sub> を流量 4 0 0 s c c m で、 A r を流量 5 0 s c c m で反応室に供給する。また、第 1 室化シリコン膜 5 1 2 の形成時と同じく、基板温度 4 0 0 °C 、反応圧力 4 0 P a 、電極間距離 3 0 m m 、 R F パワー 1 0 0 W にする。

#### 【 0 2 4 7 】

第 2 絶縁膜 5 1 4 は、全てのメモリトランジスタにおいて、窒素よりも酸素を多く含む厚さ 1 0 n m の酸化窒化シリコン膜であり、プロセスガスに S i H<sub>4</sub> および N<sub>2</sub>O が用いられている。 S i H<sub>4</sub> を流量 1 s c c m で、 N<sub>2</sub>O を流量 8 0 0 s c c m で反応室に供給する。また、基板温度 4 0 0 °C 、反応圧力 4 0 P a とし、電極間距離を 2 8 m m 、 R F パワーを 1 5 0 W にする。

#### 【 0 2 4 8 】

また、図 5 4 ( C ) の工程において、比較メモリトランジスタ T M - A では、厚さ 1 0 n m の第 1 室化シリコン膜 5 1 2 および第 2 絶縁膜 5 1 4 を連続して形成し、比較メモリトランジスタ T M - B では、厚さ 1 0 n m の第 2 室化シリコン膜 5 1 3 および第 2 絶縁膜 5 1 4 を連続して形成する。比較メモリトランジスタ T M - C では、厚さ 5 n m の第 2 室化シリコン膜 5 1 3 、厚さ 5 n m の第 1 室化シリコン膜 5 1 2 および厚さ 1 0 n m の第 2 絶縁膜 5 1 4 を連続して形成する。各比較メモリトランジスタ T M - A 、 T M - B および T M - C の作製は、図 5 4 ( C ) の工程の他の工程は、メモリトランジスタ T M - 1 の作製工程と同様に行っている。

#### 【 0 2 4 9 】

また、比較メモリトランジスタ T M - A および比較メモリトランジスタ T M - C において、第 1 室化シリコン膜 5 1 2 の成膜条件はメモリトランジスタ T M - 1 と共にあり、比較メモリトランジスタ T M - B および比較メモリトランジスタ T M - C において、第 2 室化シリコン膜 5 1 3 の成膜条件はメモリトランジスタ T M - 1 と共にある。表 5 に、各メモリトランジスタの電荷蓄積層 5 1 6 の構成を示す。

#### 【 0 2 5 0 】

#### 【 表 5 】

|                      | プロセスガスと<br>その流量 [sccm]                           | メモリトランジスタ  |         |         |            |

|----------------------|--------------------------------------------------|------------|---------|---------|------------|

|                      |                                                  | T M - 1    | T M - A | T M - B | T M - C    |

| 第 1 室化シリコン膜<br>5 1 2 | S i H <sub>4</sub> /N H <sub>3</sub> =2/400      | 5 n m (下層) | 10 n m  |         | 5 n m (上層) |

| 第 2 室化シリコン膜<br>5 1 3 | S i H <sub>4</sub> /N <sub>2</sub> /A r=2/400/50 | 5 n m (上層) |         | 10 n m  | 5 n m (下層) |

#### 【 0 2 5 1 】

次いで、第 2 絶縁膜 5 1 4 上に、厚さ 3 0 n m の窒化タンタル膜 5 1 7 を形成し、次に、厚さ 3 7 0 n m のタングステン膜 5 1 8 を形成する(図 5 5 ( A ) 参照)。窒化タンタル膜 5 1 7 およびタングステン膜 5 1 8 はスパッタ装置で形成する。

#### 【 0 2 5 2 】

次に、窒化タンタル膜 5 1 7 およびタングステン膜 5 1 8 の積層膜をエッチングして、ゲート電極 5 1 5 を形成する。まず、タングステン膜 5 1 8 上にレジストマスクを形成する。このレジストマスクを用いて、タングステン膜 5 1 8 をエッチングする。タングステン膜 5 1 8 のエッチングはプラズマエッチング装置で行い、エッチングガスには、 C F<sub>4</sub> 、 C l<sub>2</sub> および O<sub>2</sub> が用いられる。レジストマスクを除去した後、エッチングされたタングステン膜 5 1 8 をマスクにして窒化タンタル膜 5 1 7 をエッチングする。窒化タンタル膜 5 1 7 のエッチングはプラズマエッチング装置で行い、エッチングガスには C l<sub>2</sub> が用いられる。以上により、ゲート電極 5 1 5 が形成される(図 5 5 ( B ) 参照)。

#### 【 0 2 5 3 】

次に、メモリトランジスタ T M - 1 に高抵抗不純物領域を形成するため、ゲート電極 5 1 5 をマスクとして、シリコン膜 5 0 3 にリンを添加する。この工程は、プラズマドーピング装置で行う。プロセスガスは P H<sub>3</sub> であり、ドーズ量は 1 × 1 0<sup>-3</sup> i o n s / c m<sup>2</sup>

10

20

30

40

50

<sup>2</sup> である。この工程で、シリコン膜 503 には、チャネル形成領域 504、低濃度不純物領域 507 および低濃度不純物領域 508 が自己整合的に形成される(図 55(C))。

#### 【0254】

次いで、図 56(A)に示すように、ゲート電極 515 の側面に、それぞれ、スペーサ 520 を形成する。スペーサ 520 の形成はゲート電極 515、第2絶縁膜 514、電荷蓄積層 516、第1絶縁膜 511 およびシリコン膜 503 を覆って、スペーサ 520 を構成する絶縁膜を形成し、この絶縁膜をエッチングすることで形成される。ここでは、スペーサ 520 を構成する絶縁膜を 2 層形成する。1 層目に、プラズマ CVD 法で酸化窒化シリコン膜を厚さ 100 nm 形成し、2 層目に、減圧 CVD 法で酸化シリコン膜を厚さ 200 nm 形成する。スペーサ 520 を形成するエッチング処理で、第2絶縁膜 514、第2窒化シリコン膜 513 および第1窒化シリコン膜 512 もエッチングされ、図 56(A)示すように、第1窒化シリコン膜 512 及び第2窒化シリコン膜 513 でなる電荷蓄積層 516 が形成される。

10

#### 【0255】

次いで、ソース領域 505 およびドレイン領域 506 を形成するため、ゲート電極 515 およびスペーサ 520 をマスクとして、シリコン膜 503 にリンを添加する。この工程は、プラズマドーピング装置を用い、プロセスガスに PH<sub>3</sub> を用い、ドーズ量は 3 × 10<sup>15</sup> ions/cm<sup>2</sup> である。この工程で、シリコン膜 503 には、ソース領域 505 およびドレイン領域 506 が自己整合的に形成される(図 56(B) 参照)。

20

#### 【0256】

次いで、ガラス基板 501 全面に、絶縁膜 521 および絶縁膜 522 を形成する(図 56(C))。絶縁膜 521 として、厚さ 100 nm の水素を含む酸化窒化シリコン膜を形成する。この酸化窒化シリコン膜の形成は、プラズマ CVD 装置で行い、プロセスガスに SiH<sub>4</sub>、NH<sub>3</sub>、および N<sub>2</sub>O が用いられる。絶縁膜 522 として、プラズマ CVD 法により、厚さ 600 nm の酸化窒化シリコン膜を形成する。この酸化窒化シリコン膜のプロセスガスには、SiH<sub>4</sub> および N<sub>2</sub>O が用いられる。

20

#### 【0257】

絶縁膜 522 を形成した後、加熱炉によりシリコン膜 503 を熱処理する。この熱処理は、シリコン膜 503 に添加したボロンおよびリンを活性化するため、および、絶縁膜 521 に含まれる水素によりシリコン膜 503 を水素化するための処理である。

30

#### 【0258】

次いで、絶縁膜 521 および絶縁膜 522 に、ソース領域 505 およびドレイン領域 506 に達するコンタクトホールを形成する。そして、絶縁膜 522 上に、ソース電極 523 及びドレイン電極 524 を構成する導電膜を形成する。ここでは、導電膜を 4 層構造とする。1 層目は、厚さ 60 nm のチタン膜であり、2 層目は、厚さ 40 nm の窒化チタン膜であり、3 層目は厚さ 300 nm の純アルミニウム膜であり、4 層目は厚さ 100 nm の窒化チタン膜である。この導電膜をエッチングして、ソース電極 523 及びドレイン電極 524 を形成する(図 53)。以上により、メモリトランジスタ TM-1 が完成する。また、比較メモリトランジスタ TM-A、TM-B および TM-C も同様に作製する。

40

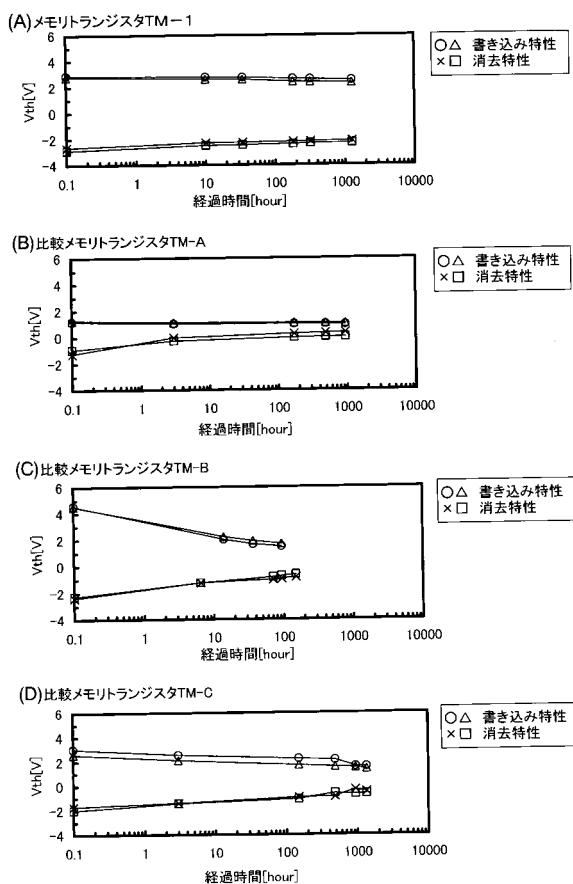

#### 【0259】

各メモリトランジスタの電荷保持特性を評価するため、書き込み動作後のソース・ドレン間電流 I<sub>DS</sub> - ゲート・ソース間電圧 V<sub>GS</sub> 特性(以下、I<sub>DS</sub> - V<sub>GS</sub> 特性と呼ぶ。)、および消去動作後の I<sub>DS</sub> - V<sub>GS</sub> 特性を測定し、この測定結果から、それぞれのリテンション特性を求めた。図 57(A) はメモリトランジスタ TM-1 のリテンション特性のグラフである。また、図 57(B) ~ 図 57(D) は比較例のリテンション特性のグラフである。図 57(B) は比較メモリトランジスタ TM-A であり、図 57(C) は比較メモリトランジスタ TM-B であり、図 57(D) は比較メモリトランジスタ TM-C である。グラフの横軸は、書き込み動作および消去動作からの経過時間を示す。なお、横軸の目盛が対数である都合、書き込み動作を行った時点、消去動作を行った時点を 0.1 時間としている。縦軸は I<sub>DS</sub> - V<sub>GS</sub> 特性の測定結果から算出した各メモリトランジ

50

スタのしきい値電圧  $V_{th}$  である。

#### 【0260】

書き込み動作は、ソース電極 523 およびドレイン電極 524 の電位を 0V とし、ゲート電極 515 に 1ミリ秒、書き込み電圧  $W_r$  を印加することで、電荷蓄積層 516 に電子を注入することで行う。また、消去動作は、メモリトランジスタにおいて、ソース電極 523 およびドレイン電極 524 の電位を 0V とし、ゲート電極 515 に 1ミリ秒、消去電圧  $E_r$  を印加した。また、各メモリトランジスタへの書き込み電圧  $W_r$ 、および消去電圧  $E_r$  の印加は、Agilent 社製パルス発生器エキスパンダー (SMU and Pulse Generator Expander、モデル：41501B) を用いた。また、各メモリトランジスタの書き込み電圧  $W_r$ 、および消去電圧  $E_r$  は、以下の通りである。

10

メモリトランジスタ TM - 1 :  $W_r = 18V$ 、 $E_r = -18V$

比較メモリトランジスタ TM - A :  $W_r = 18V$ 、 $E_r = -18V$

比較メモリトランジスタ TM - B :  $W_r = 18.5V$ 、 $E_r = -18.5V$

比較メモリトランジスタ TM - C :  $W_r = 17V$ 、 $E_r = -17V$

#### 【0261】

メモリトランジスタの書き込み動作後の  $I_{DS} - V_{GS}$  特性の測定は次のように行った。まず、メモリトランジスタにデータを書き込む書き込み動作を行う。次に書き込み状態のメモリトランジスタをホットプレートにより 85℃ に加熱された状態を維持し、書き込み動作から所定の時間経過後に、各メモリトランジスタの  $I_{DS} - V_{GS}$  特性を測定した。また、消去動作後の  $I_{DS} - V_{GS}$  特性の測定は次のように行った。書き込み動作によりメモリトランジスタにデータを書き込んだ後、消去動作を行った。消去状態のメモリトランジスタをホットプレートにより 85℃ に加熱した状態を維持し、そして、消去動作から所定の時間経過後に、各メモリトランジスタの  $I_{DS} - V_{GS}$  特性を測定した。

20

#### 【0262】

$I_{DS} - V_{GS}$  特性の測定は、Agilent 社製半導体パラメータ・アナライザ (Semiconductor Parameter Analyzer、モデル：4155C) を用いた。測定時には、ソース電極 523 の電位を 0V に、ドレイン電極 524 の電位を 1V に保持し、ゲート電極 515 の電位を -6V から +6V まで変化させ、ゲート・ソース間電圧  $V_{GS}$  に対するソース・ドレイン間電流  $I_{DS}$  の変化を測定した。なお、メモリトランジスタ TM - 1 は、チャネル長  $L = 4 \mu m$ 、チャネル幅  $W = 8 \mu m$  であり、比較メモリトランジスタ TM - A、TM - B および TM - C は、それぞれ、チャネル長  $L = 4 \mu m$ 、チャネル幅  $W = 4 \mu m$  である。

30

#### 【0263】

図 57(A) ~ 図 57(D) に示すグラフは、 $V_{th}$  ウィンドウはメモリトランジスタ TM - 1 が最大であることを示している。つまり、NH<sub>3</sub> が窒素ソースガスである窒化シリコン膜と N<sub>2</sub> が窒素ソースガスである窒化シリコン膜を積層した電荷蓄積層を設けることで、不揮発性メモリトランジスタの電荷保持特性を向上することができる。別言すると、N - H 結合を多く含む窒化シリコン膜と、N - H 結合が少ない窒化シリコン膜を積層した電荷蓄積層を設けることで、不揮発性メモリトランジスタの電荷保持特性を向上することができる。

40

#### 【図面の簡単な説明】

#### 【0264】

【図 1】不揮発性メモリトランジスタの断面図。

【図 2】不揮発性メモリトランジスタの断面図。

【図 3】本発明の不揮発性半導体メモリ素子の保持特性を評価するために作製した容量素子（素子 1）の断面図。

【図 4】比較例の不揮発性半導体メモリ素子の保持特性を評価するために作製した容量素子の断面図。（A）比較素子 A、（B）比較素子 B、（C）比較素子 C

【図 5】素子 1 のリテンション特性を示すグラフ。

- 【図 6】比較素子 A のリテンション特性を示すグラフ。

【図 7】比較素子 B のリテンション特性を示すグラフ。

【図 8】比較素子 C のリテンション特性を示すグラフ。

【図 9】窒化シリコン膜の FTIR の吸収スペクトル。

【図 10】不揮発性メモリトランジスタの断面図。

【図 11】不揮発性メモリトランジスタの断面図。

【図 12】不揮発性メモリトランジスタの断面図。

【図 13】不揮発性メモリトランジスタの断面図。

【図 14】不揮発性メモリトランジスタの断面図。

【図 15】不揮発性メモリトランジスタの断面図。

【図 16】不揮発性メモリトランジスタの断面図。

【図 17】不揮発性メモリトランジスタの断面図。

【図 18】半導体装置の構成例を示すブロック図。

【図 19】メモリセルアレイの構成例を示す回路図。

【図 20】メモリセルアレイの構成例を示す回路図。

【図 21】メモリセルアレイの構成例を示す回路図。

【図 22】メモリセルアレイの書き込み動作を説明する回路図。

【図 23】メモリセルアレイの消去動作を説明する回路図。

【図 24】メモリセルアレイの読み出し動作を説明する回路図。

【図 25】半導体装置の作製方法を示す断面図。

【図 26】半導体装置の作製方法を示す断面図。

【図 27】半導体装置の作製方法を示す断面図。

【図 28】半導体装置の作製方法を示す断面図。

【図 29】半導体装置の作製方法を示す上面図。

【図 30】半導体装置の作製方法を示す上面図。

【図 31】半導体装置の作製方法を示す上面図。

【図 32】半導体装置の作製方法を示す断面図。

【図 33】半導体装置の作製方法を示す断面図。

【図 34】半導体装置の作製方法を示す断面図。

【図 35】半導体装置の作製方法を示す断面図。

【図 36】半導体装置の作製方法を示す断面図。

【図 37】半導体装置の作製方法を示す断面図。

【図 38】半導体装置の作製方法を示す断面図。

【図 39】半導体装置の作製方法を示す断面図。

【図 40】半導体装置の作製方法を示す断面図。

【図 41】半導体装置の作製方法を示す断面図。

【図 42】半導体装置の作製方法を示す断面図。

【図 43】半導体装置の作製方法を示す断面図。

【図 44】半導体装置の作製方法を示す上面図。

【図 45】半導体装置の作製方法を示す上面図。

【図 46】半導体装置の作製方法を示す上面図。

【図 47】半導体装置の作製方法を示す断面図。

【図 48】半導体装置の作製方法を示す断面図。

【図 49】半導体装置の作製方法を示す断面図。

【図 50】非接触でデータの伝送が可能な半導体装置の構成例を示すブロック図。

【図 51】非接触でデータの伝送が可能な半導体装置の使用形態を示す図。

【図 52】不揮発性半導体記憶装置を有する電子機の外観図。

【図 53】実施例の不揮発性メモリトランジスタの構成を説明する断面図。

【図 54】不揮発性メモリトランジスタの作製方法を説明するための断面図。

【図 55】不揮発性メモリトランジスタの作製方法を説明するための断面図。

10

20

30

40

50

【図56】不揮発性メモリトランジスタの作製方法を説明するための断面図。

【図57】実施例および比較例のメモリトランジスタのリテンション特性を示すグラフ。

【符号の説明】

【0265】

|             |               |    |

|-------------|---------------|----|

| B L         | ビット線          |    |

| S L         | ソース線          |    |

| S G 1、S G 2 | 選択ゲート線        |    |

| W L         | ワード線          |    |

| M C         | メモリセル         |    |

| T m         | 不揮発性メモリトランジスタ | 10 |

| T s         | スイッチング用トランジスタ |    |

| S 1、S 2     | 選択トランジスタ      |    |

| 1 0         | 半導体領域         |    |

| 1 1         | 第1絶縁膜         |    |

| 1 2         | 第1窒化シリコン膜     |    |

| 1 3         | 第2窒化シリコン膜     |    |

| 1 4         | 第2絶縁膜         |    |

| 1 5         | 導電膜           |    |

| 1 6         | チャネル形成領域      |    |

| 1 7、1 8     | 高濃度不純物領域      | 20 |

| 1 7 a、1 8 a | 低濃度不純物領域      |    |

| 2 1         | 半導体基板         |    |

| 2 2         | ウェル           |    |

| 3 5         | スペーサ          |    |

| 4 1         | シリコン基板        |    |

| 4 2         | 第1絶縁膜         |    |

| 4 3         | 窒化シリコン層       |    |

| 4 4         | 第2絶縁膜         |    |

| 4 5         | 電極            |    |

| 5 2         | メモリセルアレイ      | 30 |

| 5 4         | ロジック部         |    |

| 5 6         | アドレスバッファ      |    |

| 5 8         | コントロール回路      |    |

| 6 0         | 昇圧回路          |    |

| 6 2         | ロウデコーダ        |    |

| 6 4         | カラムデコーダ       |    |

| 6 6         | センスアンプ        |    |

| 6 8         | データバッファ       |    |

| 7 0         | データ入出力バッファ    |    |

| 1 0 0       | 基板            | 40 |

| 1 0 2       | 下地絶縁膜         |    |

| 1 0 3       | 半導体膜          |    |

| 1 0 4       | 半導体膜          |    |

| 1 0 6       | 半導体膜          |    |

| 1 0 8       | 半導体膜          |    |

| 1 1 0       | 半導体膜          |    |

| 1 1 2       | 絶縁膜           |    |

| 1 1 4       | レジスト          |    |

| 1 1 5       | 絶縁膜           |    |

| 1 1 6       | 絶縁膜           | 50 |

|               |           |    |

|---------------|-----------|----|

| 1 1 8         | 絶縁膜       |    |

| 1 2 0         | 絶縁膜       |    |

| 1 2 1         | レジスト      |    |

| 1 2 2         | 第1窒化シリコン膜 |    |

| 1 2 3         | 第2窒化シリコン膜 |    |

| 1 2 4 ~ 1 2 6 | レジスト      |    |

| 1 2 8         | 絶縁膜       |    |

| 1 3 0         | 導電膜       |    |

| 1 3 2         | 導電膜       |    |

| 1 3 4         | 導電膜       | 10 |

| 1 3 6         | 導電膜       |    |

| 1 3 8         | 導電膜       |    |

| 1 4 0         | 導電膜       |    |

| 1 4 2         | レジスト      |    |

| 1 4 4         | チャネル形成領域  |    |

| 1 4 6         | 高濃度不純物領域  |    |

| 1 4 8         | チャネル形成領域  |    |

| 1 5 0         | 高濃度不純物領域  |    |

| 1 5 2         | チャネル形成領域  |    |

| 1 5 4         | 高濃度不純物領域  | 20 |

| 1 5 6         | レジスト      |    |

| 1 5 8         | チャネル形成領域  |    |

| 1 6 0         | 高濃度不純物領域  |    |

| 1 6 2         | 絶縁膜       |    |

| 1 6 4 ~ 1 7 0 | 導電膜       |    |

| 5 0 1         | ガラス基板     |    |

| 5 0 2         | 下地絶縁膜     |    |

| 5 0 3         | シリコン膜     |    |

| 5 0 4         | チャネル形成領域  |    |

| 5 0 5         | ソース領域     | 30 |

| 5 0 6         | ドレイン領域    |    |

| 5 0 7         | 低濃度不純物領域  |    |

| 5 0 8         | 低濃度不純物領域  |    |

| 5 1 1         | 第1絶縁膜     |    |

| 5 1 2         | 第1窒化シリコン膜 |    |

| 5 1 3         | 第2窒化シリコン膜 |    |

| 5 1 4         | 第2絶縁膜     |    |

| 5 1 5         | ゲート電極     |    |

| 5 1 6         | 電荷蓄積層     |    |

| 5 1 7         | 窒化タンタル膜   | 40 |

| 5 1 8         | タンゲステン膜   |    |

| 5 2 0         | スペーサ      |    |

| 5 2 1         | 絶縁膜       |    |

| 5 2 2         | 絶縁膜       |    |

| 5 2 3         | ソース電極     |    |

| 5 2 4         | ドレイン電極    |    |

| 5 3 0         | 結晶性シリコン膜  |    |

| 8 0 0         | 半導体装置     |    |

| 8 1 0         | 高周波回路     |    |

| 8 2 0         | 電源回路      | 50 |

|                   |            |    |

|-------------------|------------|----|

| 8 3 0             | リセット回路     |    |

| 8 4 0             | クロック発生回路   |    |

| 8 5 0             | データ復調回路    |    |

| 8 6 0             | データ変調回路    |    |

| 8 7 0             | 制御回路       |    |

| 8 8 0             | 記憶装置       |    |

| 8 9 0             | アンテナ       |    |

| 9 1 0             | コード抽出回路    |    |

| 9 2 0             | コード判定回路    |    |

| 9 3 0             | C R C 判定回路 | 10 |

| 9 4 0             | 出力ユニット回路   |    |

| 1 0 1 2           | 第1窒化シリコン膜  |    |

| 1 0 1 3           | 第2窒化シリコン膜  |    |

| 1 2 0 0           | 半導体基板      |    |

| 1 2 0 1           | 絶縁膜        |    |

| 1 2 0 2           | 窒化シリコン膜    |    |

| 1 2 0 3           | レジスト       |    |

| 1 2 0 4           | 凹部         |    |

| 1 2 0 5           | 絶縁膜        |    |

| 1 2 0 7 ~ 1 2 0 9 | 半導体領域      | 20 |

| 1 2 1 0           | pウェル       |    |

| 1 2 1 1           | 絶縁膜        |    |

| 1 2 1 2           | レジスト       |    |

| 1 2 1 4 ~ 1 2 1 6 | 絶縁膜        |    |

| 1 2 1 8           | レジスト       |    |

| 1 2 2 1           | 絶縁膜        |    |

| 1 2 2 2           | 導電膜        |    |

| 1 2 2 3           | 導電膜        |    |

| 1 2 2 4 ~ 1 2 2 8 | 導電膜        |    |

| 1 2 2 9 ~ 1 2 3 1 | 低濃度不純物領域   | 30 |

| 1 2 3 3 ~ 1 2 3 7 | スペーサ       |    |

| 1 2 3 8 ~ 1 2 4 0 | 高濃度不純物領域   |    |

| 1 2 4 1 ~ 1 2 4 4 | 低濃度不純物領域   |    |

| 1 2 4 5 ~ 1 2 4 8 | チャネル形成領域   |    |

| 1 2 4 9           | 絶縁膜        |    |

| 1 2 5 0           | 開口部        |    |

| 1 2 5 5 ~ 1 2 5 9 | 導電層        |    |